11) Número de publicación: 2 328 503

51 Int. CI.:

**H03J 5/02** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA MODIFICADA TRAS OPOSICIÓN

**T5**

(86) Fecha de presentación y número de la solicitud internacional: 26.09.2005 PCT/EP2005/054816

(87) Fecha y número de publicación internacional: 06.04.2006 WO06035015

(96) Fecha de presentación y número de la solicitud europea: 26.09.2005 E 05789530 (2)

(97) Fecha y número de publicación de la concesión europea modificada tras oposición: 21.03.2018 EP 1794883

(54) Título: Dispositivo de filtro electrónico para la recepción de señales de TV

(30) Prioridad:

27.09.2004 EP 04447213

(45) Fecha de publicación y mención en BOPI de la traducción de la patente modificada: 29.06.2018

(73) Titular/es:

UNITRON (100.0%) Frankrijklaan 27 8970 Poperinge, BE

(72) Inventor/es:

**DELEU, STEPHEN**

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

### **DESCRIPCIÓN**

Dispositivo de filtro electrónico para la recepción de señales de TV

#### Campo Técnico

5

45

La presente invención se refiere a un dispositivo de filtro electrónico para la recepción de señales de TV según el preámbulo de la reivindicación 1.

### **Técnica Anterior**

En los años 1980, se usaba ordinariamente un filtro fijado para filtrar y combinar diferentes señales aéreas sobre un cable. Fijado, significa que el instalador necesitaba sustituir el filtro por un filtro totalmente nuevo si las frecuencias de los canales (o simplemente la aplicación completa) cambiaban.

- 10 En los años 1990 aparecieron los filtros programables en el mercado, los cuales podían ser reprogramados por el instalador en el lugar para que sirviesen para diferentes frecuencias o nuevas aplicaciones, evitando la necesidad de su sustitución por nuevos filtros. El filtro era adecuado para todas las posibles aplicaciones en aquel tiempo, de modo que no existía la necesidad de desarrollar, producir y almacenar diferentes versiones.

- Un ejemplo de ese tipo de filtro se describe en el documento GB-A-2272341. Para filtrar los canales de TV deseados de la señal entrante, el dispositivo comprende una pluralidad de elementos que determinan la frecuencia (principalmente (cápsulas variables de regulación) que pueden ser establecidas por medio de tensiones de establecimiento analógicas. Para generar estas tensiones, los valores de la tensión almacenados digitalmente son convertidos en tensiones analógicas por medio de Convertidores de Digital en Analógico (DAC), que son componentes caros. Para limitar el número de DACs, se usa un algoritmo especial en el dispositivo de GB-A-2272341: una cantidad menor de DACs genera más tensiones analógicas multiplexando cada salida de DAC en varios "lugares de memoria analógicos" (que son por ejemplo circuitos de retención y muestreo) en una "memoria dinámica", en la que las tensiones analógicas son almacenadas y pasadas sobre los elementos que determinan la frecuencia.

- El dispositivo conocido por el documento GB-A-2272341 tiene no obstante el inconveniente de que, para mantener las tensiones en la memoria dinámica en el nivel deseado, es necesario un algoritmo de reactivación continua para conectar la salida del DAC a intervalos de tiempo regulares a los lugares de memoria analógica. Esta reactivación continua de las tensiones analógicas exige una porción enorme de recursos del microcontrolador. Esto origina la necesidad de sobredimensionar el microcontrolador, lo cual aumenta de nuevo el coste del dispositivo.

# Descripción de la Invención

Un objeto de la presente invención es proporcionar un dispositivo de filtro electrónico para la recepción de señales de TV con circuitos de conversión alternativos para DAC, con lo cual la necesidad de un microcontrolador sobredimensionado puede ser evitada.

Este objeto se consigue según la invención con un dispositivo de filtro electrónico que muestra las características técnicas de la primera reivindicación.

- El dispositivo de filtro electrónico para la recepción de señales de TV según la invención comprende una pluralidad de elementos de determinación de la frecuencia que son establecidos por medio de una tensión de establecimiento analógica. El dispositivo comprende además una memoria en la cual se almacenan valores digitales representativos de las tensiones de establecimiento analógicas y circuitos de conversión para convertir los valores digitales en tensiones de establecimiento analógicas. El dispositivo se caracteriza porque el circuito de conversión comprende una primera parte para generar una señal modulada digitalmente para cada valor digital, teniendo la señal modulada digitalmente una característica representativa del valor digital, y una segunda parte para convertir cada una de las señales moduladas digitalmente en tensiones de establecimiento analógicas.

- Las señales moduladas digitalmente, que son generadas por la primera parte del circuito de conversión del dispositivo según la invención, son señales digitales cuyo valor binario cambia entre '0' y '1' en un cierto modo, por ejemplo según un modelo regular, en el que la señal transporta una característica que representa el valor digital a partir del cual se origina la señal y que puede ser interpretado. La característica puede ser por ejemplo un ciclo de trabajo, es decir, el tiempo en que la señal es '1' o el tiempo en el que la señal es '0', dividido por el periodo, o una frecuencia a la cual la señal cambia entre '1' y '0' y en sentido contrario, o de cualquier otra característica que pueda ser modulada digitalmente.

- 50 En el dispositivo de filtro electrónico de la invención, se usa un desvío para convertir las tensiones de establecimiento analógicas a partir de las señales digitales. El modo evidente sería el de usar DACs (uno para cada tensión que haya de ser generada), pero como se ha mencionado esto es indeseable a la vista de su coste. Según la invención, los valores digitales son convertidos primero en señales moduladas digitalmente, las cuales son a su vez convertidas en las tensiones de establecimiento analógicas. La primera parte del circuito de conversión añade

algunos componentes digitales al dispositivo, pero estos son generalmente económicos y las señales moduladas generadas digitalmente por ellos son convertibles en tensiones de establecimiento analógicas por medio de componentes menos caros que los DACs, tales como por ejemplo resistores y condensadores. Como un resultado de la utilización del desvío, cada una de las tensiones analógicas puede ser generada por medio de su propia parte dedicada a ello del circuito de conversión, ya no existe la necesidad de compartir diferentes tensiones analógicas sobre la misma línea, como ocurre en el dispositivo de la técnica anterior sobre la salida de los DACs, ni de usar un conmutador dinámico para conectar la tensión derecha al lugar de almacenamiento derecho en la memoria dinámica. Esto elimina la necesidad de un algoritmo de reactivación y un microcontrolador sobredimensionado.

Además, puesto que ya no existe la necesidad de compartir diferentes tensiones analógicas sobre la misma línea, como ocurre en el dispositivo de la técnica anterior sobre la salida de los DACs, ni de usar un conmutador dinámico para conectar la tensión derecha al lugar de almacenamiento analógico derecho en la memoria dinámica, estos componentes bastante caros pueden ser dispensados también, lo cual puede implicar además una reducción en el coste del dispositivo. La eliminación de la reactivación continua de las tensiones analógicas tiene también la ventaja de que las tensiones ya no muestran una fluctuación, la cual está siendo distribuida sobre una gran parte de la placa de circuito impreso que está siempre presente sobre las tensiones que necesitan ser reactivadas continuamente. De esta manera la necesidad de componentes de filtración adicionales para eliminar la fluctuación de las tensiones y evitar que un residuo de la fluctuación aparezca sobre la imagen de TV se evita también, lo cual puede reducir además el coste del dispositivo de la invención.

Todavía más, puesto que la primera parte del circuito de conversión puede ser completamente digital, la integración de componentes resulta una opción y todos o al menos algunos de los componentes pueden ser integrados en un chip único. Esto puede reducir más el número de componentes separados y consecuentemente reducir más su precio.

25

30

35

40

En el dispositivo de filtro electrónico de la invención, la primera parte del circuito de conversión comprende una pluralidad de comparadores, uno para cada señal modulada digitalmente, para comparar una de las señales digitales con un valor de contador, siendo suministrado el valor de contador por un contador que se proporciona para que cuente repetidamente a través de un margen de valores predeterminado que comprende todos los valores digitales posibles. En esta invención, cada comparador genera un '0' mientras su condición de comparación no es satisfecha, y un '1' cuando su condición de comparación es satisfecha, o viceversa. Por consiguiente, una señal modulada digitalmente es generada como se defina anteriormente con un indicativo del ciclo de trabajo del valor digital en la entrada del comparador, y por tanto indicativo de la tensión de establecimiento analógica. Esta invención tiene la ventaja de ser una solución simple y directa para generar las señales moduladas digitalmente a partir de los valores digitales.

El contador puede contar hacia delante o hacia atrás a través de su gama de valores. Para obtener el recuento repetido a través de la gama de valores, este puede ser restablecido periódicamente por un microcontrolador del dispositivo o este puede funcionar en un bucle sin fin. La condición de comparación puede ser "x menor que y", "x igual o menor que y", "x mayor que y" o "x igual o mayor que y". En vez del contador o contadores y los comparadores, pueden ser usados también otros componentes para generar las señales moduladas digitalmente a partir de los valores digitales.

El contador es preferiblemente común para todos los comparadores, de modo que solamente es necesario generar un valor de contador. Soluciones alternativas son que cada comparador tenga su propio contador o que los contadores sean proporcionados para grupos de comparadores. Cuando la anchura de bits de los valores digitales almacenados en la memoria del dispositivo es N, los comparadores son al menos de N bits de anchura y el contador es proporcionado para que cuente repetidamente entre 0 y al menos 2<sup>N</sup>-1 para cubrir todos los valores digitales posibles.

La primera parte del circuito de conversión comprende preferiblemente un registro común para almacenar copias de los valores digitales almacenados en la memoria. De esta manera se mantiene la memoria separada del circuito de conversión y pueden ser evitados los cambios no intencionados. El registro es preferiblemente común para todos los comparadores, pero son posibles también registros separados para un comparador o grupos de comparadores. Una alternativa más es que los comparadores estén acoplados directamente a la memoria.

En una realización preferida del dispositivo de la invención, la primera parte del circuito de conversión está integrada en una Ordenación de Compuertas Programables de Campo (FPGA), un Dispositivo Lógico Programable (PLD), un Dispositivo Lógico Programable Complejo (CPLD), un Circuito Integrado Concreto de Aplicación (ASIC), o cualquier otro circuito integrado programable similar conocido por la persona experta en la técnica. El FPGA es preferido por las razones de que es el mejor compromiso disponible entre precio y facilidad de integración y porque está llegando a ser extensamente usado en el campo.

Uno o más de los siguientes componentes opcionales del dispositivo de la invención pueden ser integrados junto con la primera parte del circuito de conversión dentro del mismo chip: un microcontrolador, una interfaz de PC, un circuito de detección de RF y/o lógica de interfaz de usuario. La memoria en la que se almacenan los valores digitales puede ser integrada también dentro de este chip.

La segunda parte del circuito de conversión comprende una pluralidad de integradores, uno para cada señal modulada digitalmente, Estos integradores, que pueden ser convenientemente incorporados en la forma de redes de RC, generando las deseadas tensiones de establecimiento analógicas a partir de las señales moduladas digitalmente. Los integradores son preferidos por las razones de que son de baja complejidad y económicos.

La memoria en la que los valores digitales están almacenados es preferiblemente una memoria no volátil, tal como por ejemplo una EEPROM, de modo que el dispositivo puede ser reprogramado en el lugar. Para permitir la reprogramación en el lugar el dispositivo comprende una interfaz de usuario para permitir que un usuario reprograme los valores digitales.

### Breve descripción de los dibujos

10 La invención será explicada mejor por medio de la descripción siguiente y las Figuras que se añaden.

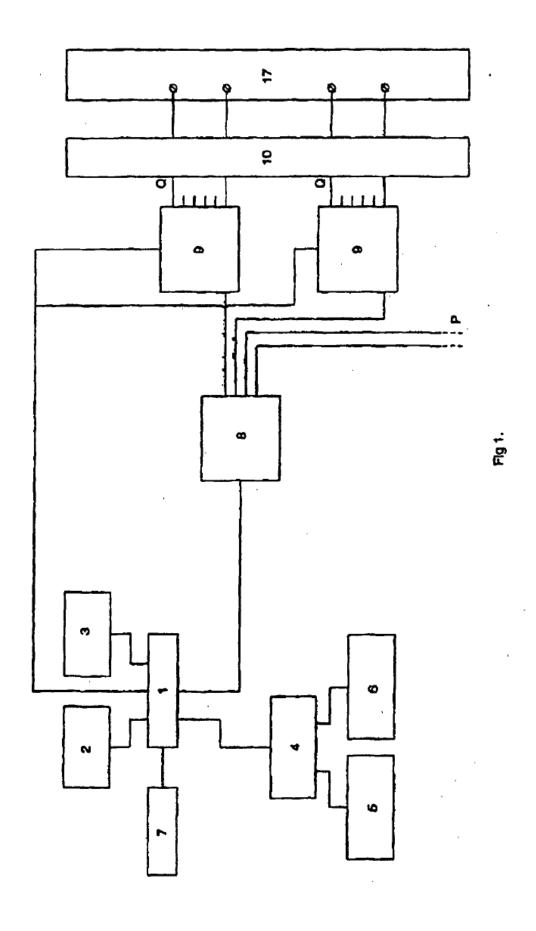

La Figura 1 muestra un dispositivo de filtro electrónico de la técnica anterior.

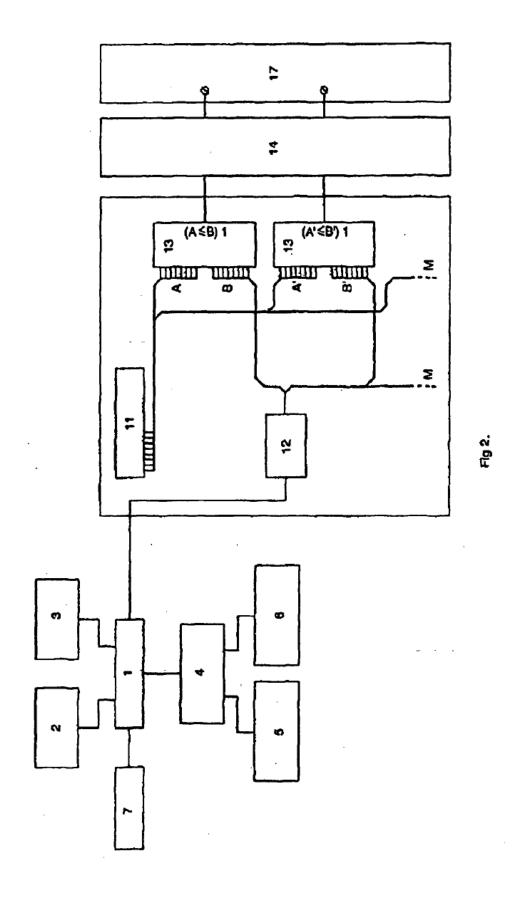

La Figura 2 muestra una primera realización preferida del dispositivo de filtro electrónico de la invención.

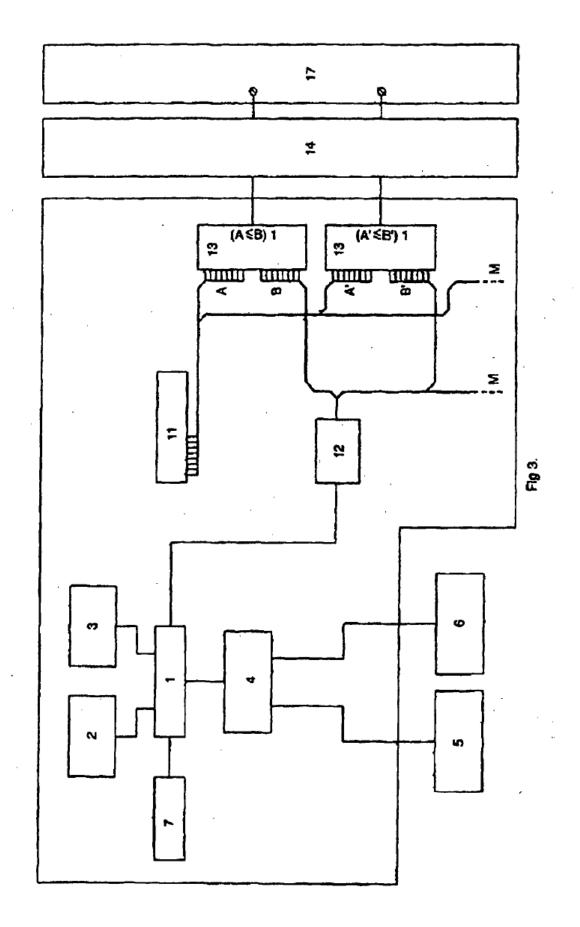

La Figura 3 muestra una segunda realización preferida del dispositivo de filtro electrónico de la invención.

#### Modos de poner en práctica la invención

- 15 El dispositivo de técnica anterior de la Figura 1 es el que se conoce por el documento GB-A-2272341. Comprende un microcontrolador 1, una memoria (NVM) no volátil 2 para almacenar datos de fábrica y reglajes efectuados en el campo por el instalador, una interfaz 3 de PC, por ejemplo para grados más altos de microprogramación cableada o cambio de los reglaies del dispositivo, una lógica 4 de interfaz de usuario con dispositivos 5 de entrada de interfaz de usuario y dispositivos 6 de salida de interfaz de usuario, un circuito 7 de detección de RF para detectar el nivel de RF 20 necesario para una función de compensación automática, una pluralidad de DACs 8 para generar tensiones analógicas, una pluralidad de conmutadores 9 (o multiplexores dinámicos), y una memoria dinámica 10 con "lugares de almacenamiento analógicos" para almacenar tensiones analógicas. Las tensiones analógicas son suministradas por un banco 17 de salidas de tensión y son usadas para establecer elementos de determinación de las frecuencias del circuito de RF. En la Figura 1, la cantidad de DACs es P, la cantidad de conmutadores dinámicos es también P y 25 el número de salidas por conmutador dinámico es Q. Un algoritmo dinámico complejo controlado por el microcontrolador, es activo continuamente y sincroniza el funcionamiento de los DACs y los conmutadores dinámicos. En la ranura 1 de tiempo, los DACs están generando las tensiones analógicas para la salida 1 y todos los conmutadores dinámicos están establecidos en la salida 1. En la ranura de tiempos 2, los DACs están generando las tensiones analógicas para la salida 2 y todos los conmutadores dinámicos están establecidos en la salida 2. Esto 30 continúa hasta que en la ranura Q de tiempos son generadas las últimas tensiones analógicas y dirigidas a las últimas salidas. El resultado es que la memoria dinámica contiene ahora todas las tensiones analógicas P×Q en P×Q lugares de almacenamiento, que están conectados a las P×Q salidas en el banco 17. Como la memoria dinámica no es perfecta y hay consumo en las tensiones analógicas, el algoritmo dinámico tiene que reactivar todos los valores de P×Q repitiendo de modo continuo las acciones efectuadas desde la ranura 1 de tiempo hasta la ranura Q de tiempo. Es evidente que este algoritmo complejo y sin detenciones consume gran cantidad de recursos del 35 microcontrolador. Otro inconveniente es la distribución no deseada de señales de alta frecuencia, que se originan desde el algoritmo complejo, entre los DACs y los conmutadores dinámicos. No hay posibilidad de filtrar estas señales no deseadas fuera, pues esto destruiría completamente el algoritmo complejo, pero no obstante ellas están presentes en una gran parte del PCB.

- 40 En la Figura 2, se muestra una primera posible realización del dispositivo de la invención. Esta realización comprende los componentes siguientes que son similares a los del dispositivo de la técnica anterior de la Figura 1: un microcontrolador 1, una memoria 2 no volátil para almacenar todos los datos de factoría y todos los reglajes hechos en el campo por el instalador, una interfaz 3 de PC, por ejemplo grados superiores de microprogramación cableada o cambio de reglajes del dispositivo, una lógica 4 de interfaz de usuario con dispositivos 5 de entrada de 45 interfaz de usuario y dispositivos 6 de salida de interfaz de usuario, donde los artículos 4 a 6 se usan por ejemplo para cambiar los reglajes, para mostrar una función de igualación automática, y cualquiera de otras posibles funciones, y un circuito 7 de detección de RF para detectar el nivel de RF necesitado para la función de igualación automática. El dispositivo de la Figura 2 difiere del de la Figura 1 en el circuito de conversión, que comprende un contador 11 de N bits, un registrador 12 que comprende al menos M×N bits, M comparadores 13 (al menos de N bits 50 de ancho), un banco integrador 14 con M integradores (uno para cada comparador), y un banco 17 de salida en el que las M tensiones analógicas son presentadas para ser usadas en el circuito de RF (no mostrado) del dispositivo. Los integradores 14 pueden ser aplicados convenientemente como redes de RC, pero son posibles otras aplicaciones. Las tensiones analógicas que son generadas son usadas al menos para la frecuencia que determinan los elementos del circuito de RF (no mostrado), pero pueden ser usadas también para algunos otros circuitos de 55 entrada o salida y posiblemente también otros componentes.

En la realización mostrada en la Figura 2, la interfaz 4-6 de usuario es parte del dispositivo de filtro electrónico. Alternativamente, la interfaz de usuario puede ser también desconectada del dispositivo.

El contador 11, el registrador 12 y los comparadores 13 forman una primera parte del circuito de conversión que se proporciona para convertir los valores digitales almacenados en la memoria 2 en señales moduladas digitalmente que tienen un ciclo de trabajo indicativo del valor digital y por tanto el valor de establecimiento analógico.

La primera parte del circuito de conversión funciona como sigue. El contador 11 de N bits está contando en un bucle sin fin entre 0 y 2<sup>N</sup>-1 e incrementa cada vez mediante 1 en el régimen del reloi. Cuando este llega a 2<sup>N</sup>-1, empieza de nuevo en 0 en un procedimiento repetitivo sin detenciones. Al mismo régimen que el reloj, este valor del contador de N bits es aplicado a las entradas A, A', ... de todos los M comparadores 13. El registrador 12 contiene al menos M×N bits enviados una vez desde la memoria 2 no volátil por el microcontrolador 1 tras la reiniciación o reprogramación del dispositivo, que puede ser disparada mediante un instalador por medio de la interfaz 4-6 de usuario. Por tanto el registrador 12 almacena una copia de los valores digitales almacenados en la memoria 2 no volátil. El registrador 12 a su vez aplica estos datos a la entrada B, B',... del comparador 13 respectivo. Como un resultado, cada comparador 13 tiene 2 señales de anchura de N bits que el compara al régimen del reloj. Se supone que la condición que es considerada por cada comparador 13 es "A menor que o igual a B". El primer comparador 13 emitirá entonces un '1' binario tan largo como el valor sobre la entrada A, es decir, el valor de contador; es menor que o igual al valor sobre la entrada B, es decir uno de los valores digitales. Una vez que el valor sobre la entrada A llega a ser mayor que el valor sobre la entrada B, el comparador generará un '0' binario. DE este modo una señal modulada digitalmente es generada con un ciclo de trabajo que es una representación del valor digital que se origina desde el NVM 2. Por tanto el ciclo de trabajo es una característica modulada digitalmente que está enlazada con el valor digital almacenado. Como una alternativa, la condición de comparación puede ser también "A menor que B", "A mayor que B" o "A mayor que o igual a B". En vez del contador (s) y los comparadores, pueden ser usados también otros componentes para generar las señales moduladas digitalmente de los valores digitales.

10

15

20

25

40

45

50

55

Los integradores 14 forman una segunda parte del circuito de conversión y se proporcionan para convertir las señales moduladas digitalmente en las tensiones de establecimiento analógicas. En vez de los integradores 14, pueden ser usados filtros también o cualquier otro circuito que pueda establecer una relación entre el ciclo de trabajo de la señal modulada digitalmente y le tensión analógica.

En la realización de la Figura 2, el registrador 12 y el contador 11 funcionan de modo autónomo, sin necesidad de control por parte del microcontrolador 1. Solamente en momentos discretos, tales como el arranque, o después de un cambio de los reglajes, el microcontrolador 1 se dirige al registrador 12. Como un resultado, el microcontrolador 1 no necesita recursos para ejecutar un algoritmo continuo de refresco como en la técnica anterior.

La descripción anterior es un ejemplo, pero seguramente no es la única solución posible. En vez de un contador único, también puede ser usado un cierto número de contadores. De modo similar, también puede ser usado un cierto número de registradores en vez de uno único. En el caso extremo, son usados, un contador y un registrador por comparador, donde los contadores pueden funcionar independientemente y no sincronizados uno con otro. El número de integradores de filtros puede ser igual al número de comparadores, pero también puede ser menor. El contador o contadores no tienen necesidad de funcionar en un bucle sin fin; son posibles otros modos de funcionamiento, tales como por ejemplo un reestablecimiento periódico por el microcontrolador.

En una realización alternativa (no mostrada), son generadas señales moduladas digitalmente por medio de convertidores de frecuencia en tensión. En esta realización la NVM puede por ejemplo almacenar una relación de divisor de un régimen horario para cada tensión que sea generada, cuya relación de divisor se usa entonces para generar una señal de oscilación, en sincronización con la señal horaria. Esta señal de oscilación puede ser generada por medio de una primera parte completamente digital del circuito de conversión. La señal de oscilación se suministra entonces a los convertidores de frecuencia en tensión, que forman una segunda parte del circuito de conversión. En esta realización la relación de divisor almacenada es por tanto también un valor digital representativo de la tensión analógica que ha de ser generada. La señal de oscilación es una señal modulada digitalmente como se define anteriormente, siendo su frecuencia la característica modulada que es enlazada con el valor digital almacenado y por tanto con la tensión que ha de ser generada. Además, son factibles realizaciones alternativas.

Como un resultado de usar los comparadores 13, el registrador 12 y el contador 11, la necesidad de DACs expansivos, y los conmutadores dinámicos y la memoria dinámica que consumen espacio son eliminados. Además, la integración de los componentes llega a ser una opción. Como ahora hay un circuito completamente digital que sustituye a los DACs, el camino está abierto hacia la integración de la mayoría de los circuitos digitales. Esto puede hacerse en un PLD (Dispositivo Lógico Programable), un CPLD (Dispositivo Lógico Programable Complejo), una FPGA (Ordenación de Compuertas Programable de Campo), o un ASIC (Circuito Integrado Específico de Aplicación) u otros circuitos integrados equivalentes. Hay circuitos disponibles tales que tienen recursos suficientes para integrar todos los comparadores así como el registrador y el contador, que es lo que se hace en la realización de la Figura 2. Por ejemplo, en una realización en la que se necesitan 64 tensiones eléctricas de establecimiento analógicas, el contador 11 de N bits, el registrador 12 con al menos 64 palabras de N bits y al menos 64 comparadores 13 pueden estar integrados dentro de una única FPGA para generar estas tensiones. El número de tensiones eléctricas y consecuentemente el tamaño del registrador y el número de circuitos comparadores pueden por supuesto variar dependiendo de las necesidades y circunstancias.

Cuando se usa una FPGA para la integración, son posibles diferentes realizaciones. En la primera realización que se muestra en la Figura 2, la FPGA 15 es de tipo volátil, siendo así porque una NVM 2 separada se incluye para almacenar los bits de configuración para configurar la FPGA 15. Esta NVM 2 es también la memoria en la que los datos de fabricación y los valores digitales representativos de las tensiones de establecimiento analógicas están almacenados, pero una NVM separada por los bits de configuración es también posible. Durante el arranque la FPGA 15 se configura ella misma descargando su programa de la NVM.

5

20

25

30

55

En una realización alternativa que se muestra en la Figura 3, la FPGA 16 es del tipo no volátil, lo que significa que tiene una NVM incorporada de modo que no hay necesidad de almacenar los bits de configuración en una NVM separada. En esta realización, incluso el resto de los datos puede ser almacenado dentro de la FPGA 16.

En la realización de la Figura 3 incluso más datos están integrados dentro de la FPGA 16, es decir la lógica 4 de la interfaz de usuario, a la cual ambos dispositivos 5, 6 de entrada y salida pueden estar conectados, ya sea permanentemente o de modo desmontable, el microcontrolador 1, el circuito 7 de detección de RF y la interfaz 3 de PC. Los componentes digitales además pueden estar integrados también dentro de la FPGA. En la Figura 3, todos los circuitos digitales están integrados, incluso los circuitos con entradas o salidas analógicas que conducen a un dispositivo de filtro electrónico que puede ser fabricado con un coste muy bajo.

Las ventajas del dispositivo de las Figuras 2 ó 3 en comparación con el de la Figura 1 son numerosas. Como ya se ha mencionado, un primer beneficio es la eliminación del algoritmo de reactivación complejo, que ha sido sustituido por un algoritmo directo más simple. El microcontrolador 1 ya no está trabajando de modo continuo sobre el algoritmo, el único tiempo que el microcontrolador necesita para coordinar la generación de las tensiones analógicas, es el arranque o cuando los reglajes del dispositivo de filtro electrónico están siendo cambiados. Esto puede hacerse por medio de un microcontrolador 1 con muchos menos recursos, por consiguiente mucho más económico.

Una segunda ventaja es que los cambios en el diseño pueden hacerse de modo mucho más fácil que con la técnica anterior. En el dispositivo de las Figuras 2 y 3, el microcontrolador 1 está acoplado principalmente con la comunicación disparada por un evento discontinuo, como un instalador que cambia los reglajes. En el dispositivo de la técnica anterior de la Figura 1 el microcontrolador tenía que organizar ambos procedimientos, los continuos (de algoritmo completo) y los no continuos (como un cambio de los reglajes). Cuando se produjo un evento y el microcontrolador necesitaba por ejemplo vigilar el dispositivo de interfaz de usuario de entrada, el algoritmo complejo estaba todavía en marcha, haciendo la microprogramación cableada dentro del microcontrolador compleja y difícil de cambiar. Como un resultado de la eliminación del algoritmo de reactivación, los cambios en el producto (mejoras, actualizaciones, nuevas versiones,...) pueden ser introducidos con mayor rapidez y facilidad.

Una ventaja más es la posibilidad de integración de múltiples componentes, que conduce a diseños más económicos. Esto funciona de dos maneras: por una parte el número de componentes se reduce y por otra parte se economiza espacio. Menos espacio ocupado significa menores PCBs, menores alojamientos,..., productos más económicos y comercialmente más atractivos.

Debido a la ausencia del conmutador dinámico en los dispositivos de las Figuras 2 y 3, ya no hay una fuente que origine interferencias que puedan conducir a perturbaciones en la señal de RF. En el dispositivo de la técnica anterior de la Figura 1, se tenía que poner atención especial en este tema de EMC, pues el algoritmo dinámico con sus transiciones de alta frecuencia estaba distribuido sobre una gran parte del PCB, originando que este radiase. En los dispositivos de las Figuras 2 y 3, el algoritmo dinámico responsable de una parte sustancial de los problemas de EMC es eliminado y sustituido por un algoritmo (estático) que funciona dentro del componente de la FPGA facilitando la filtración de todos los impulsos indeseables directamente en la salida del componente. Cualquier radiación está contenida dentro del componente y sustancialmente no influenciará la señal de RF. Como una ventaja adicional (si es necesaria) el microcontrolador 1 (responsable también por una parte de la radiación) puede funcionar a una frecuencia de reloj más lenta disminuyendo el riesgo de perturbar la radiación.

Los dispositivos de las Figuras 2 y 3 muestran además una gradabilidad superior incrementada. Sobre el nivel de software, estos dispositivos son al menos tan flexibles como el dispositivo de la técnica anterior de la Figura 1; nuevas regulaciones de la frecuencia determinan elementos de los filtros cableados que pueden ser obtenidos cambiando las tensiones eléctricas establecidas. Pero en los dispositivos de las Figuras 2 y 3, las características de hardware pueden ser modificadas; nuevas características pueden ser añadidas, pueden ser instalados microcontroladores más robustos, puede obtenerse una mayor exactitud incrementando el número de bits en el contador, registro y comparadores, y así sucesivamente.

Una ventaja más es un tiempo reducido para generar los datos de fabricación en la etapa de producción. El DAC y el algoritmo de reactivación dinámico del dispositivo de técnica anterior de la Figura 1 retardaban este procedimiento porque unos pocos DACs, a través del sistema de transmisión simultánea tenían que suministrar una gran cantidad de tensiones analógicas. Con los dispositivos de las Figuras 2 y 3, la velocidad puede ser incrementada pues todas las tensiones analógicas pueden ser generadas simultáneamente. Un enorme beneficio de esta velocidad incrementada radica en la calibración de la NVM en la etapa de producción. La velocidad del equipo de ensayo en la etapa de producción ya no está limitada por la velocidad de los DACs y el algoritmo de transmisión simultánea, pudiendo reducir el tiempo de producción y originar una reducción de los gastos de producción.

# ES 2 328 503 T5

## Lista de Referencia

- 1. Microcontrolador

- 2. Memoria no volátil

- 3. Interfaz de PC

- 5 4. Lógica de interfaz de usuario

- 5. Dispositivos de entrada de la interfaz de usuario

- 6. Dispositivos de salida de la interfaz de usuario

- 7. Circuito de detección de RF

- 8. DAC

- 10 9. Conmutador dinámico

- 10. Memoria dinámica

- 11. Contador de N bits

- 12. Registrador (N×M bits)

- 13. Comparador de N bits

- 15 14. Banco integrador

- 15. FPGA

- 16. FPGA

- 17. Banco de salidas de tensión analógicas.

#### REIVINDICACIONES

- 1. Un dispositivo de filtro electrónico para la recepción de señales de TV, que comprende un circuito de RF que tiene una pluralidad de elementos de determinación de frecuencias para filtrar una pluralidad de canales de TV deseados de una señal entrante, siendo cada elemento de determinación de la frecuencia ajustable por medio de una tensión de establecimiento analógica, una memoria (2) de almacenamiento de valores digitales representativos de los valores de las tensiones de establecimiento analógicas y un circuito (11-14) de conversión para convertir los valores digitales en las tensiones de establecimiento analógicas, **caracterizado porque** el circuito de conversión comprende:

- una primera parte completamente digital (11-13) integrada en un chip único, que comprende un contador (11) de N bits, un registrador (12) que comprende al menos M×N bits, y M comparadores (13), que es al menos de N bits de ancho para generar una señal modulada digitalmente para cada valor digital, teniendo la señal modulada digitalmente una característica modulada representativa del valor digital,

- siendo la característica modulada un ciclo de trabajo que está enlazado con el valor digital almacenado y, por lo tanto, a la tensión a generar;

- y una segunda parte (14) para convertir cada una de las señales moduladas digitalmente en las tensiones de establecimiento analógicas, comprendiendo la segunda parte del circuito de conversión un banco integrador (14) con integradores M, uno para cada señal modulada digitalmente, implementándose los integradores en forma de redes RC proporcionadas para generar las tensiones analógicas deseadas a partir de las señales moduladas digitalmente, y un banco de salida (17) donde se presentan las tensiones de establecimiento analógicas,

- 20 de modo que todas las tensiones de establecimiento analógicas se pueden generar simultáneamente.

25

- 2. Un dispositivo de filtro electrónico según la reivindicación 1, **caracterizado porque** el contador (11) es común para un cierto número de, o todos, los comparadores (13).

- 3. Un dispositivo de filtro electrónico según una cualquiera de las reivindicaciones precedentes, **caracterizado porque** la primera parte (11-13) del circuito de conversión está integrada en una ordenación (15; 16) de compuertas programable.

- 4. Un dispositivo de filtro electrónico según la reivindicación 3, **caracterizado porque** la ordenación (15; 16) de compuertas programable integra además uno o más de los siguientes: un microcontrolador (1), una interfaz (3) de PC, un circuito (7) de detección de RF, lógica (4) de interfaz de usuario y/o la memoria (2) en la cual están almacenados los valores digitales.

- 5. Un dispositivo de filtro electrónico según una cualquiera de las reivindicaciones precedentes, **caracterizado porque** la memoria (2) es una memoria no volátil y porque el dispositivo comprende una interfaz (5, 6) de usuario para permitir a un usuario reprogramar los valores digitales.