① Número de publicación: 2 346 396

21 Número de solicitud: 201030475

(51) Int. Cl.:

H01L 21/02 (2006.01) H01L 21/76 (2006.01)

# (12) PATENTE DE INVENCIÓN CON EXAMEN PREVIO

B2

- 22 Fecha de presentación: 30.03.2010

- 43 Fecha de publicación de la solicitud: 14.10.2010

Fecha de la concesión: 29.08.2011

- 45) Fecha de anuncio de la concesión: 08.09.2011

- 45) Fecha de publicación del folleto de la patente: 08.09.2011

- Titular/es: Universidad Politécnica de Madrid c/ Ramiro de Maeztu, 7 28040 Madrid, ES

- 12 Inventor/es: Fuentes Iriarte, Gonzalo

- (74) Agente: Carvajal y Urquijo, Isabel

- 54 Título: Método de fabricación de sustratos de circuitos integrados basados en tecnología CMOS.

- (57) Resumen:

Método de fabricación de sustratos de circuitos integrados basados en tecnología CMOS.

Método de fabricación de sustratos (1) de circuitos integrados basados en tecnología CMOS que comprende:

- una primera etapa de depósito de una capa de material aislante (3) sobre al menos un soporte (2, 6),

- una segunda etapa de modelado de la capa de material aislante dando lugar a al menos un foso (4) en dicha capa aislante (3),

- una tercera etapa de depósito de una capa de semiconductor (5) sobre los fosos (4) obtenidos en la etapa anterior, de manera que el material semiconductor rellene los fosos (4) totalmente,

- una cuarta etapa de planarización mecánico-química (CMP) que remueve la capa de semiconductor (5), depositado en la segunda etapa, hasta el nivel del borde superior de la capa aislante (3) dando lugar a un sustrato (1) que permite la fabricación de circuitos integrados basados en tecnología CMOS interconexionados tridimensionalmente.

Aviso: Se puede realizar consulta prevista por el art. 40.2.8 LP.

#### DESCRIPCIÓN

Método de fabricación de sustratos de circuitos integrados basados en tecnología CMOS.

#### Campo de la invención

15

Esta invención se relaciona con la nanotecnología. Más particularmente, esta invención pertenece al ámbito de sistemas que utilizan transistores de circuitos integrados (transistores IC), los elementos constitutivos de nuestra sociedad basada en la información.

#### Antecedentes de la invención

La fabricación de dispositivos semiconductores es el proceso usado para crear los circuitos integrados (chips de silicio) que se encuentran en los dispositivos eléctricos y electrónicos presentes en nuestra vida diaria. Es una secuencia múltiple de los pasos de proceso fotolitográficos y químicos durante los cuales los circuitos electrónicos se crean gradualmente en una oblea hecha de material semiconductor puro. El silicio (junto con varios semiconductores compuestos) es el material más usado en general hoy en día en la industria de semiconductores. Una oblea típica se fabrica partiendo de silicio extremadamente puro que se crece en lingotes cilíndricos mono-cristalinos (boules) de hasta 300 milímetros (algo menos de 12 pulgadas) de diámetro usando el proceso de Czochralski. Una vez fabricados, estos lingotes se rebanan en obleas de cerca de 0.75 milímetros de grueso y se pulen para obtener una superficie muy regular y plana.

Una vez las obleas están preparadas, son necesarios muchos pasos de procesado para obtener el circuito integrado de semiconductor. Los pasos se pueden agrupar generalmente en dos áreas.

- 1. "Front-end" de la línea de proceso (FEOL, por sus siglas en inglés): se refiere a la formación de transistores directamente en el silicio. La oblea cruda es procesada con el crecimiento por epitaxia de una capa de gran pureza (virtualmente sin defectos) de silicio. En los dispositivos de lógica más avanzados, antes del paso de epitaxia de silicio, se realizan trucos para mejorar el funcionamiento de los transistores que se fabricarán posteriormente. Un método implica introducir un "paso de estiramiento" en el cual una variante del silicio tal como "silicio-germanio" (SiGe) es depositada. Una vez se deposite el silicio epitaxial, el enrejado cristalino se estira levemente, resultando en una movilidad electrónica mejorada. Otro método, llamado tecnología de "silicio sobre aislante" implica la inserción de una capa de aislamiento entre la oblea de silicio cruda y la capa delgada de epitaxia subsecuente al silicio. Este método da lugar a la creación de transistores con menos efectos parásitos.

- 2. "Back-end" de la línea proceso (BEOL, por sus siglas en inglés): una vez se han fabricado los varios dispositivos semiconductores, estos deben ser interconectados para formar los circuitos eléctricos. Este "Back-end" de la línea proceso (BEOL la parte final del proceso de fabricación del circuito integrado, no confundir con el "Back-end" de la fabricación del chip que se refiere a las etapas de encapsulado y comprobación), implica crear interconexiones de metal que son aislados mediante dieléctricos.

Las nano-estructuras funcionales han estado en uso durante muchos años. Tal uso incluye la fabricación de transistores bipolares, inversores complementarios usando dispositivos basados en tecnología CMOS (Complementary Metal Oxide Semiconductor) o superredes de nanohilos (Nano-códigos de barras, LEDs a nano escala). Estos sistemas generalmente incorporan una nano-estructura (nano-puerta, nanohilo, nanocolumna, nanotubos) para fabricar el dispositivo.

Dentro de lo que hoy es considerado como "nanotecnología", se encuentran los bien conocidos circuitos integrados basados en tecnología CMOS (complementary metal oxide semiconductor), que se fabrican de manera localizada y a gran escala desde hace unas décadas. Algunos nuevos dispositivos próximos como "Fin-FETs" también pueden ser fabricados de forma localizada permitiendo la producción en masa.

La fabricación de otros transistores para circuitos integrados basados en nano-estructuras electrónicamente funcionales (nanohilos, nanocolumnas, nanotubos del carbón) es hoy en día incompatible con la producción en gran volumen propia de la tecnología del silicio. Por lo tanto, no se están produciendo en masa hoy.

El estado de la técnica de la tecnología de silicio basada en CMOS para fabricar circuitos integrados (ICs) utiliza como sustrato obleas de silicio mono-cristalinas. Solamente se utiliza la zona superior (unas pocas micras de profundidad) de la superficie de la oblea de silicio. El resto funciona solamente como soporte mecánico y no tiene ninguna funcionalidad electrónica.

Así, el estado de la técnica de los transistores basados en tecnología CMOS se fabrica exclusivamente sobre tales sustratos de silicio mono-cristalino. Esto supone un gran inconveniente para la fabricación tridimensional de transistores basados en tecnología ya que la fabricación de sustratos de silicio mono-cristalino requiere temperaturas, por encima de 1000°C, que destruirían los transistores IC basados en tecnología CMOS.

US 7,476,963, divulga un método de fabricación de circuitos integrados a partir de sustratos depositados por slipchip. Sin embargo esta tecnología "flip-chip" o de soldadura que es más costosa y requiere más pasos de fabricación que el método de la presente invención.

Por otro lado US 7,419,902 divulga un método de fabricación de circuitos integrales inteconexionados. Sin embargo este método no puede utilizarse conjuntamente con tecnología CMOS (complementary metal oxide semiconductor) va existente.

Así mismo US7,563,669 divulga la fabricación de condensadores sobre circuitos integrados. Por lo tanto este método se refiere a la fabricación de otros tipos de componentes electrónicos presentes en circuitos integrados tales como condensadores. Al tratarse de otros tipos de componentes electrónicos (condensadores en vez de transistores), los pasos de fabricación que se presentan son distintos de los de esta invención y el problema que resuelve esta invención no permite la fabricación de circuitos integrados 3D sino solo la fabricación de condensadores y en una dimensión  $(1\bar{D})$ .

Por lo tanto, existe una necesidad de un método de fabricación simple y rentable de sustratos para transistores (IC) basados en nano-estructuras o en tecnología CMOS:

- que permita la síntesis localizada y a gran escala de transistores, es decir, permitiendo una producción de gran volumen.

- que permita la integración de transistores tridimensional (3D),

- que no exceda las limitaciones térmicas requeridas para garantizar el funcionamiento y la durabilidad de dichos transistores.

- que utilice las herramientas y los procesos de la fabricación estándares en la tecnología de silicio para sintetizar los transistores IC basados en silicio a gran escala, es decir, permitiendo un alto volumen de producción.

#### Descripción de la invención

La invención se refiere a un método de fabricación de sustratos de transistores de circuitos integrados, basados en nano-estructuras o tecnología CMOS, de una manera fácil y rentable que permiten la fabricación de circuitos integrados con transistores interconexionados tridimensionalmente.

El método de fabricación de sustratos de transistores basados en tecnología CMOS de la invención comprende:

- Una primera etapa de depósito de una capa de material aislante sobre un soporte. Este soporte inicialmente comprende diversas obleas de soporte duro, tal como Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, o blando tal como polímeros u orgánicos, es decir, no sólo sustratos de oblea de silicio.

- una segunda etapa de modelado de la capa de material aislante dando lugar a fosos en dicha capa aislante,

- una tercera etapa de depósito de una capa de semiconductor sobre los fosos obtenidos en la etapa anterior, de manera que el material semiconductor rellene los fosos totalmente, 45

- una cuarta etapa de planarización mecánico-química (CMP) que remueve la capa de semiconductor, depositado en la segunda etapa, hasta el nivel del borde superior de la capa aislante

- de tal manera que se obtiene un sustrato para circuitos integrados con CMOS dando lugar a un circuito integrado que puede interaccionar tridimensionalmente con otro, por aplicación de las etapas primera a cuarta de obtención del sustrato de manera cíclica, sobre dicho circuito integrado que actúa como soporte sobre el que se deposita el material aislante de la primera etapa.

- Una vez obtenido el nuevo sustrato sobre el circuito integrado basado en tecnología CMOS, se le aplica tecnología CMOS para la obtención de un nuevo circuito integrado, y así se repite la secuencia de manera que se obtienen circuitos integrados interconexionados uno sobre otro, hasta obtener el número de circuitos integrados interconexionados tridimensionalmente deseado.

#### Breve descripción de los dibujos

A continuación se pasa a describir de manera muy breve una serie de dibujos que ayudan a comprender mejor la invención y que se relacionan expresamente con una realización de dicha invención que se presenta como un ejemplo no limitativo de ésta.

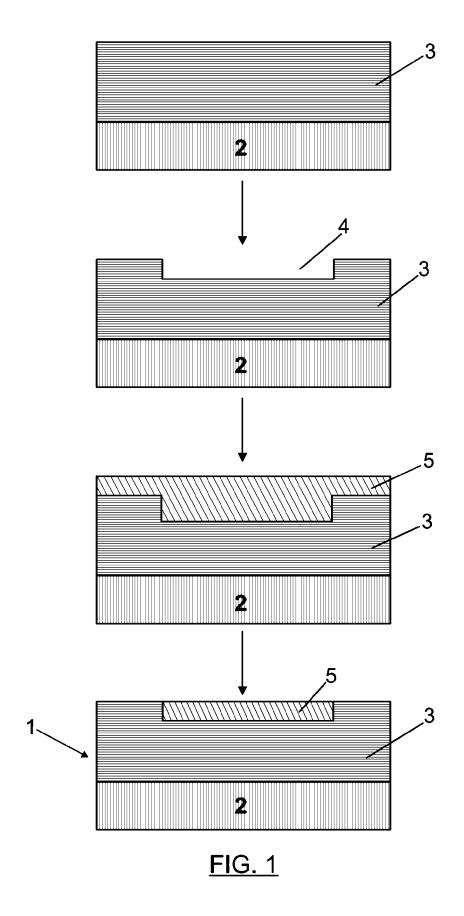

La Figura 1 muestra un esquema de las etapas del procedimiento de fabricación de los sustratos semiconductores de la invención.

3

15

20

25

35

50

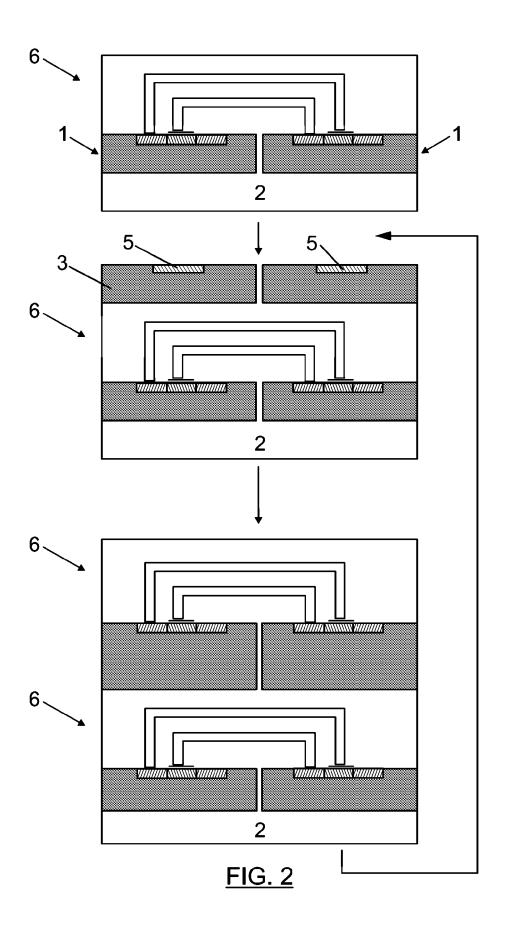

La Figura 2 muestra un esquema de las etapas del procedimiento de fabricación de circuitos integrados con transistores interconexionados tridimensionalmente a partir de circuitos integrados obtenidos por tecnología CMOS a partir de los sustratos obtenidos por el procedimiento de la figura 1.

- En las figuras anteriormente citadas se identifican una serie de referencias que corresponden a los elementos indicados a continuación, sin que ello suponga carácter limitativo alguno:

- 1.- Sustrato para circuitos integrados con tecnología CMOS

- 10 2.- Oblea

- 3.- Capa aislante

- 4.- Foso

15

- 5.- Material semiconductor depositado por CVD

- 6.- Circuito integrado

## O Descripción detallada de un modo de realización

El objeto de la invención es la fabricación de sustratos para la fabricación de circuitos integrados basados en tecnología CMOS. Este procedimiento permite fabricar circuitos integrados con interconexiones en tres dimensiones. Por otro lado, como producto final, un circuito integrado (o un circuito integrado 3D) puede ser un microprocesador de un ordenador, una memoria, parte de una pantalla de televisión.

Ejemplo de descripción de una realización preferida:

A continuación se procede a describir un procedimiento de obtención de un circuito integrado basado en tecnología CMOS con los transistores interconexionados tridimensionalmente como el indicado en la figura 2:

- una primera etapa de depósito de una capa de material aislante (3) (Si02) sobre una oblea de soporte (2) duro de Si.

- una segunda etapa de modelado de la capa de material aislante dando lugar a al menos un foso (4) en dicha capa aislante.

- una tercera etapa de depósito de una capa de semiconductor (5) sobre los fosos obtenidos en la etapa anterior, por deposición en fase vapor químico (CVD, "Chemical Vapor Deposition"), de manera que el material semiconductor (polisilicio) rellena los fosos totalmente,

- una cuarta etapa de planarización mecánico-química (CMP, "Chemical Mechanical Polishing") que remueve la capa de semiconductor, depositado en la tercera etapa, hasta el nivel del borde superior de la capa aislante, obteniendose así el sustrato (1) del circuito integrado con tecnología CMOS,

- una quinta etapa de fabricación del circuito integrado (6) con tecnología CMOS sobre el sustrato (1) obtenido en la etapa anterior,

- una sexta etapa repetición de las etapas primera a la cuarta para la obtención de nuevos sustratos (1) sobre el circuito integrado (6) ya fabricado en la quinta etapa, en vez de sobre la oblea de soporte (2) duro de Si.

- una séptima etapa de fabricación de un circuito integrado (6) con tecnología CMOS adicional, sobre el sustrato (1) fabricado en la sexta etapa obteniendo la fabricación de circuitos integrados unos sobre otros o 3D

- una octava etapa de repetición de las etapas sexta y séptima tantas veces como se desee para seguir fabricando circuitos integrados 3D.

60

40

45

50

65

#### REIVINDICACIONES

- Método de fabricación de sustratos (1) de circuitos integrados basados en tecnología CMOS caracterizado por comprender:

- una primera etapa de depósito de una capa de material aislante (3) sobre al menos un soporte seleccionado entre oblea de silicio (2) o circuito integrado (6),

- una segunda etapa de modelado de la capa de material aislante dando lugar a al menos un foso (4) en dicha capa aislante (3),

- una tercera etapa de depósito de una capa de semiconductor (5) sobre los fosos (4) obtenidos en la etapa anterior, de manera que el material semiconductor rellene los fosos (4) totalmente,

- una cuarta etapa de planarización mecánico-química (CMP) que remueve la capa de semiconductor (5), depositado en la segunda etapa, hasta el nivel del borde superior de la capa aislante (3).

- 2. Método de fabricación circuitos integrados basados en tecnología CMOS **caracterizado** por comprender las etapas primera a cuarta de fabricación del sustrato (1) de la reivindicación 1, en las que en la primera etapa, el material aislante (3) se deposita en al menos una oblea (2) de soporte seleccionado entre duro o blando.

- 3. Método de fabricación según reivindicación 2 **caracterizado** porque la oblea es una oblea de soporte duro seleccionado entre Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub> o Si<sub>3</sub>N<sub>4</sub>.

- 4. Método de fabricación según reivindicación 2 **caracterizado** porque la oblea es una oblea de soporte blando seleccionado entre material polimérico o compuesto orgánico.

- 5. Método de fabricación circuitos integrados interconexionados tridimensionalmente **caracterizado** por comprender las etapas primera a cuarta de fabricación del sustrato (1) de la reivindicación 1 sobre el que se fabrica el nuevo circuito integrado con tecnología CMOS, en las que en la primera etapa, el material aislante (3) se deposita en al menos un circuito integrado (6) con tecnología CMOS.

35

10

15

40

45

50

55

60

65

① ES 2 346 396

(21) Nº de solicitud: 201030475

22 Fecha de presentación de la solicitud: 30.03.2010

32 Fecha de prioridad:

# INFORME SOBRE EL ESTADO DE LA TÉCNICA

| (51) | Int. Cl.: | <b>H01L 21/02</b> (2006.01) |

|------|-----------|-----------------------------|

|      |           | H01L 21/76 (2006.01)        |

## **DOCUMENTOS RELEVANTES**

| Categoría                                      | 66)                                                                                                        | Documentos citados F                                                                                               | Reivindicaciones<br>afectadas |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Α                                              | US 2006071316 A1 (GARTH párrafos [0005],[0029]-[0032]                                                      |                                                                                                                    | 1-5                           |

| Α                                              | US 2009011592 A1 (UNO, S figura 14.                                                                        | ., et al.) 08.01.2009, resumen;                                                                                    | 1-5                           |

| Α                                              | US 2007267670 A1 (CHITTII columna 2, líneas 29-57; figu                                                    | PEDDI, S., et al.) 22.11.2007, resumen; ra 1.                                                                      | 1-5                           |

| A                                              | US 5084419 A (SAKAO, M.)<br>líneas 20-63; figuras 5-9.                                                     | 28.01.1992, resumen; columna 2,                                                                                    | 1-5                           |

| X: de part<br>Y: de part<br>misma              | ía de los documentos citados<br>icular relevancia<br>icular relevancia combinado con otro/s d<br>categoría | O: referido a divulgación no escrita  P: publicado entre la fecha de prioridad y la de prese  de la solicitud      |                               |

| El prese                                       | el estado de la técnica  nte informe ha sido realizado todas las reivindicaciones                          | E: documento anterior, pero publicado después de la de presentación de la solicitud  para las reivindicaciones nº: | а геспа                       |

| Fecha de realización del informe<br>28.09.2010 |                                                                                                            | <b>Examinador</b><br>M. García Poza                                                                                | Página<br>1/4                 |

# INFORME SOBRE EL ESTADO DE LA TÉCNICA

$N^{\circ}$  de solicitud: 201030475

| Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación)                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| H01L                                                                                                                                       |

| Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) |

| INVENES, EPODOC, WPI                                                                                                                       |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

#### **OPINIÓN ESCRITA**

Nº de solicitud: 201030475

Fecha de Realización de la Opinión Escrita: 28.09.2010

#### Declaración

Novedad (Art. 6.1 LP 11/1986) Reivindicaciones 1-5 SÍ

Reivindicaciones NO

Actividad inventivaReivindicaciones1-5SÍ(Art. 8.1 LP 11/1986)ReivindicacionesNO

Se considera que la solicitud cumple con el requisito de **aplicación industrial.** Este requisito fue evaluado durante la fase de examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986).

## Base de la Opinión:

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como ha sido publicada.

**OPINIÓN ESCRITA**

$N^{\circ}$  de solicitud: 201030475

#### 1. Documentos considerados:

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

| Documento | Número Publicación o Identificación | Fecha Publicación |

|-----------|-------------------------------------|-------------------|

| D01       | US 2006071316                       | 06-04-2006        |

| D02       | US 2009011592                       | 08-01-2009        |

| D03       | US 2007267670                       | 22-11-2007        |

| D04       | US 5084419                          | 28-01-1992        |

# 2. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración

El objeto de la invención es un método de fabricación de sustratos para circuitos integrados.

El documento D01 divulga un método de fabricación de circuitos integrados a partir de circuitos depositados por "flip-chip" o tecnología de soldadura (resumen; párrafos: [0005], [0029]-[0032] y figs. 3, 11). En este procedimiento primero se fabrican los circuitos que posteriormente se sueldan.

El documento D02 divulga un método de fabricación de circuitos integrados en el que para hacer las interconexiones metálicas depositan capas de material aislante sobre los circuitos, en las que hacen las trincheras, que posteriormente rellenan con los metales (resumen y fig. 14).

El documento D03 divulga la fabricación de condensadores para lo cual se hace una trinchera en el semiconductor que se rellena primero con un material dieléctrico (aislante) y después con dos capas de silicio policristalino dopado (material semiconductor) (resumen; columna 2, líneas 29-57 y fig. 1).

El documento D04 divulga un método de fabricación de un dispositivo semiconductor en el que la etapa de pulido mecánicoquímico de la capa de silicio depositada en las trincheras de la capa aislante es la ventaja sobre el estado de la técnica para la fabricación de un dispositivo semiconductor, pero no es la preparación de un sustrato (resumen; columna 2, líneas 20-63 y figs. 5-9).

Ninguno de los documentos citados divulga un procedimiento de fabricación de sustratos que comprende: una etapa de depositar una capa aislante sobre un soporte, una segunda etapa de formación de fosos en la capa aislante, una tercera etapa de depositar una capa de semiconductor sobre los fosos, y una etapa final de planarización mecánico-química del semiconductor hasta el borde superior de la capa de aislante. Tampoco sería obvio para el experto en la materia llegar a este procedimiento a partir de la información divulgada en el estado de la técnica. Por lo tanto, el método de fabricación de la invención recogido en las reivindicaciones 1 a 5 se considera nuevo y con actividad inventiva (Art. 6.1 y 8.1 LP).