OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

① Número de publicación: 2 356 912

(51) Int. Cl.:

H03M 13/11 (2006.01) H03M 13/29 (2006.01) G11B 20/18 (2006.01) H03M 13/15 (2006.01)

| (12) | TRADUCCIÓN DE PATENTE EUROPEA |

|------|-------------------------------|

|      |                               |

Т3

- 96 Número de solicitud europea: 04735346 .1

- 96 Fecha de presentación : 28.05.2004

- 97 Número de publicación de la solicitud: **1524771** 97 Fecha de publicación de la solicitud: 20.04.2005

- 🗿 Título: Método de decodificación, dispositivo de decodificación, programa dispositivo de grabación/reproducción y método, y método y dispositivo de reproducción.

- (30) Prioridad: **30.05.2003 JP 2003-153927**

- Titular/es: SONY CORPORATION 7-35, Kitashinagawa 6-chome Shinagawa-ku, Tokyo 141-0001, JP

- (45) Fecha de publicación de la mención BOPI: 14.04.2011

- (12) Inventor/es: Kikuchi, Atsushi; Hattori, Masayuki; Miyauchi, Toshiyuki; Watanabe, Kazuo y Kan, Makiko

- 45) Fecha de la publicación del folleto de la patente: 14.04.2011

- (74) Agente: Curell Aguilá, Marcelino

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

## **CAMPO TÉCNICO**

5

La presente invención se refiere a un método de decodificación y a un decodificador, a un programa, a un aparato y a un método de grabación-y-reproducción, y a un aparato y a un método de reproducción, y se refiere, particularmente, a un método de decodificación y a un decodificador, a un programa, a un aparato y a un método de grabación-y-reproducción, y a un aparato y a un método de reproducción que son adecuados para decodificar datos codificados cuya codificación se ha realizado usando un código lineal sobre un anillo R.

10

## ANTECEDENTES DE LA TÉCNICA

15

En los últimos años, mientras se han estado estudiando, con avances considerables, el campo de las comunicaciones, tales como las comunicaciones móviles y las comunicaciones en el espacio profundo, y el campo de la radiodifusión, tal como la radiodifusión por ondas terrestres y la radiodifusión digital por satélite, se ha estudiado activamente, por ejemplo, la teoría de la codificación para aumentar la eficacia de la codificación y decodificación de corrección de errores.

20

Como límites teóricos del rendimiento de un código se conoce el límite de Shannon presentado por el teorema denominado de codificación de las vías de comunicación de Shannon (C.E. Shannon). La teoría de la codificación se estudia para desarrollar un código que presente un rendimiento que se aproxime al límite de Shannon descrito anteriormente. En los últimos años, se ha desarrollado, como método de codificación que presenta un rendimiento que se aproxima al límite de Shannon, un método al que se hace referencia como la denominada turbocodificación que incluye códigos convolucionales concatenados en paralelo (PCCC), códigos convolucionales concatenados en serie (SCCC), y otros. Además, aparte de los turbocódigos que están siendo desarrollados, se está prestando atención a un método de codificación conocido, es decir, los códigos de comprobación de paridad de baja densidad (a los que se hará referencia en lo sucesivo como códigos LDPC).

25

30

El código LDPC fue sugerido por primera vez en, "Low Density Parity Check Codes", de R. G. Gallager, Cambridge, Massachusetts: M.I.T.Press, 1963 por R. G. Gallager. A continuación, el código LDPC ha recibido atención adicional por parte de D.J.C. MacKay, "Good error correcting codes based on very sparse matrices", presentado en IEEE Trans. Inf. Theory, IT-45, págs. 399 a 431, 1999, "Analysis of low density codes and improved designs using irregular graphs", de M. G. Luby, M. Mitzenmacher, M. A. Shokrollahi y D. A. Spielman, en *Proceedings of ACM Symposium on Theory of Computing*, págs. 249 a 258, 1998, y otros.

35

Según estudios de los últimos años, el rendimiento del código LDPC se aproxima al límite de Shannon con aumentos en la longitud del código. Además, como la distancia mínima del código LDPC es proporcional a la longitud del código, el código LDPC presenta, como características propias, las siguientes ventajas. Es decir, el código LDPC presenta características de una probabilidad alta de errores de bloque y apenas provoca el fenómeno denominado suelo de error que se observa en las características de los turbocódigos de decodificación o similares.

40

Se describirá detalladamente el código LDPC descrito anteriormente, según la manera expuesta a continuación. El código LDPC es un código lineal y no necesariamente binario. No obstante, en esta memoria descriptiva, el mismo se describirá suponiendo que el código LDPC es binario.

45

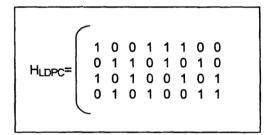

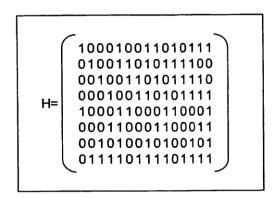

La característica principal del código LDPC es que una matriz de comprobación de paridad que define el código LDPC es poco densa. En este caso, la matriz poco densa indica una matriz que incluye muy pocos componentes cuyos valores son "1". La matriz de comprobación poco densa se designa mediante el carácter de referencia H. La matriz de comprobación poco densa incluye la H<sub>LDPC</sub> mostrada en la Fig. 1, donde el peso Hamming (el número de "1") de cada fila es "2" y el de cada columna es, por ejemplo, "4".

50

De este modo, al código LDPC definido por una matriz de comprobación H, en donde el peso Hamming de cada una de las filas y columnas es constante, se le hace referencia como código LDPC regular. Por otro lado, a un código LDPC definido por una matriz de comprobación H en donde el peso Hamming de cada una de las filas y columnas no es constante se le hace referencia como código LDPC irregular.

60

55

La codificación usando el código LDPC descrito anteriormente se logra mediante una matriz de generación G basada en la matriz de comprobación H y generando una palabra de código mediante la multiplicación de la matriz de generación G por un mensaje de datos binarios. Más específicamente, en primer lugar, un codificador destinado a realizar la codificación por el código LDPC calcula la matriz de generación G, en donde se cumple una ecuación GH<sup>T</sup>=0, entre la matriz de comprobación H y una matriz transpuesta H<sup>T</sup>. Cuando la matriz de generación G es una matriz de k x n, el codificador multiplica la matriz de generación G por un mensaje de datos de k bits (vector u) y genera una palabra de código de n bits c (= uG). En la palabra de código generada por el codificador, de un bit de código cuyo valor es "0" se establece una correspondencia con "+1", y de un bit de código cuyo valor es "1" se establece una correspondencia con "1". A continuación, la palabra de código se transmite y es recibida en el lado de recepción a través de una vía de comunicación predeterminada.

La decodificación del código LDPC se puede realizar usando un algoritmo propuesto por Gallager, y cuyo nombre fue designado por este último, como decodificación probabilística, es decir, un algoritmo de paso de mensajes por propagación de confianza (belief propagation) sobre una gráfica denominada de Tanner que incluye un modo variable (al que en ocasiones se hace referencia como nodo de mensaje) y un nodo de comprobación. En lo sucesivo, al nodo variable y al nodo de comprobación se les hará referencia simplemente como nodos, según se requiera.

5

10

15

20

25

30

35

40

45

50

55

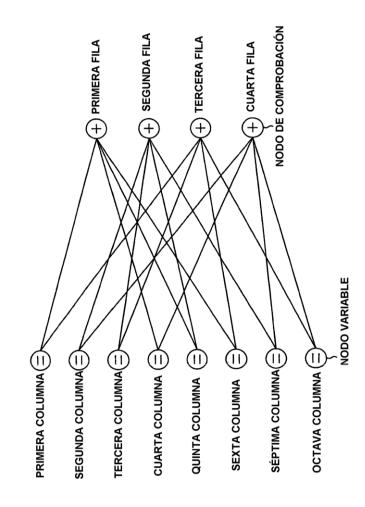

Por ejemplo, la matriz de comprobación de paridad  $H_{LDPC}$  mostrada en la Fig. 1 se expresa mediante una gráfica de Tanner mostrada en la Fig. 2. En la gráfica de Tanner mostrada en la Fig. 2, se determina que cada columna de la matriz de comprobación de paridad  $H_{LDPC}$  mostrada en la Fig. 1 es un nodo variable y se determina que cada fila es un nodo de comprobación. Además, el nodo variable j-ésimo y el nodo de comprobación i-ésimo están conectados a un elemento cuyo valor es "1" en la fila i-ésima y la columna j-ésima de la matriz de comprobación de paridad  $H_{LDPC}$ , como bordes.

No obstante, cuando se realiza la decodificación probabilística, el valor de un mensaje transmitido entre los nodos se proporciona en forma de un número real. Posteriormente, existe una necesidad de realizar un seguimiento de la distribución de probabilidad de mensajes que tienen valores consecutivos para una solución analítica, lo cual resulta extremadamente difícil. Por lo tanto, Gallager propuso los algoritmos A y B, como algoritmo para decodificar el código LDPC.

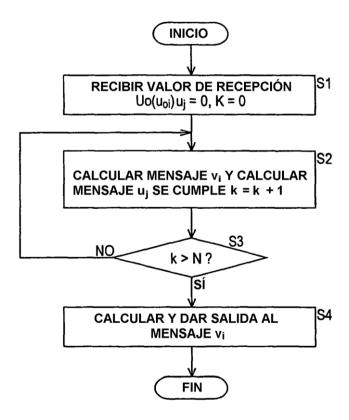

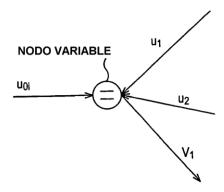

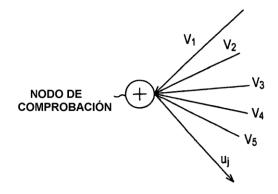

Habitualmente, la decodificación del código LDPC se logra realizando los procedimientos mostrados en la Fig. 2. Aquí, en este caso, se determina que un valor de recepción (una secuencia de código recibida) es  $U_0(u_{0i})$ , se determina que un mensaje transmitido desde el nodo de comprobación es  $u_j$ , y se determina que un mensaje transmitido desde el nodo variable es vi. Además, en este caso, el mensaje es un valor de número real que indica la probabilidad de que el valor sea "0", en forma de una denominada razón de verosimilitud logarítmica.

Habitualmente, la decodificación del código LDPC se logra realizando los procedimientos mostrados en la Fig. 3. Aquí, en este caso, se determina que el valor de recepción (la secuencia de código recibida) es  $U_0(u_{0i})$ , se determina que el mensaje transmitido desde el nodo de comprobación es  $u_j$ , y se determina que el mensaje transmitido desde el nodo variable es  $v_i$ , además, en este caso, el mensaje es el valor de un número real que indica la probabilidad de que el valor sea "0", en forma de la denominada razón de verosimilitud logarítmica.

En primer lugar, para decodificar el código LDPC, se recibe un valor de recepción  $U_0(u_{0i})$ , un mensaje  $u_i$  se inicializa a "0", y una variable k que es un entero que funciona como contador de un procesado de repetición se inicializa a "0", en la etapa S1, y el procesado avanza hacia la etapa S2, tal como se muestra en la Fig. 3. En la etapa S2, se obtiene el mensaje  $v_i$  ejecutando el cálculo mostrado por la Ecuación (1) (cálculo de nodo variable) sobre la base del valor de recepción  $U_0(u_{0i})$ , y se obtiene el mensaje  $u_j$  ejecutando el cálculo mostrado en la Ecuación (2) (cálculo de nodo de comprobación) sobre la base del mensaje  $v_i$ .

$$v_i = u_{0i} + \sum_{j=1}^{d_v - 1} u_j$$

Ecuación (1)

$$\tanh\left(\frac{u_j}{2}\right) = \prod_{i=1}^{d_c-1} \tanh\left(\frac{v_i}{2}\right)$$

Equación (2)

En este caso, la  $d_v$  y la  $d_c$  mostradas en las Ecuaciones (1) y (2) son parámetros que indican el número de "1" a lo largo de la dirección vertical (columnas) y la dirección horizontal (filas) de la matriz de comprobación H y que se pueden seleccionar, de forma respectiva, arbitrariamente. Por ejemplo, en el caso de un código (3, 6), se cumplen las ecuaciones  $d_v=3$  y  $d_c=6$ .

Además, en los cálculos mostrados por las Ecuaciones (1) y (2), como parámetro de operación de suma u operación de producto no se usa un mensaje introducido desde un borde para dar salida a mensajes (una línea que conecta el nodo variable al nodo de comprobación). De este modo, se determina que el área de la operación de suma o producto es de 1 a  $d_v$  – 1, o de 1 a  $d_c$  – 1. Además, el cálculo mostrado en la Ecuación (2) se realiza en realidad generando una tabla de una función  $R(v_1, v_2)$  mostrada en la Ecuación (3) definida por una salida para dos entradas v1 y v2 de antemano, y usando la tabla consecutivamente (de forma recursiva), tal como se muestra en la Ecuación (4).

$$x=2\tanh^{-1} \{\tanh (v_1/2) \tanh (v_2/2)\} = R(v_1, v_2)$$

Ecuación (3)

$$u_j = R(v_1, R(v_2, R(v_3, \dots R(v_{d_c-2}, v_{d_c-1}))))$$

Ecuación (4)

Además, en la etapa S2, la variable k se incrementa en "1", y el procesado avanza hacia la etapa S3. En la etapa S3, se determina si la variable k es mayor o no que un número de decodificación de repetición predeterminado N. Cuando se determina que la variable k no es mayor que N, en la etapa S3, el procesado vuelve a la etapa S2, y seguidamente se repite el mismo procesado.

Además, cuando se determina que la variable k es mayor que N, en la etapa S3, el procesado avanza hacia la etapa S4, de manera que se realiza el cálculo mostrado en la Ecuación (5), con lo cual se obtiene y se da salida al mensaje v<sub>i</sub>, en forma de un resultado de decodificación obtenido finalmente a la salida. A continuación, finaliza la decodificación del código LDPC.

$$v_i = u_{0i} + \sum_{j=1}^{d_v} u_j$$

Ecuación (5)

En este caso, a diferencia del cálculo mostrado en la Ecuación (1), el cálculo mostrado en la Ecuación (5) se realiza usando mensajes introducidos desde todos los bordes conectados al nodo variable.

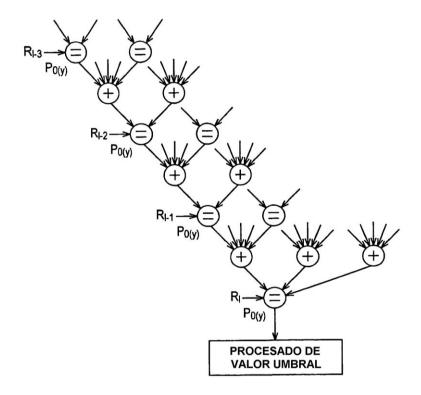

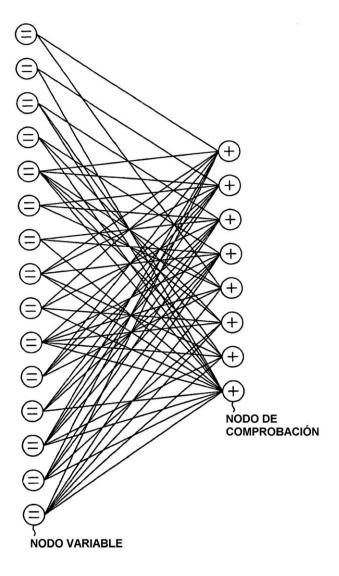

Cuando la decodificación del código LDPC se realiza usando el código (3, 6), por ejemplo, se transmiten mensajes entre los nodos, tal como se muestra en la Fig. 4. Además, el cálculo mostrado en la Ecuación (1) se realiza en nodos indicados por signos "=" (nodos variables) mostrados en la Fig. 4, y el cálculo mostrado en la Ecuación (2) se realiza en nodos indicados por signos "+" (nodos de comprobación). Particularmente, en el caso de un algoritmo A, los mensajes se dividen en dos y se ejecuta una operación OR exclusiva para  $d_c - 1$  mensajes de entrada en los nodos indicados por los signos "+". Cuando todos los valores de bit de los  $d_v - 1$  mensajes de entrada son diferentes entre sí para un valor de recepción R en los nodos indicados por signos "=", el código se invierte y se da salida al mismo.

En los últimos años, aparte de la tecnología descrita anteriormente, se han estudiado métodos para montar la decodificación de los códigos LDPC. En primer lugar, se describirá esquemáticamente la decodificación de los códigos LDPC antes de describir el método de montaje.

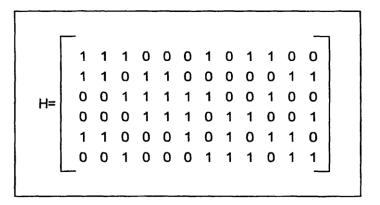

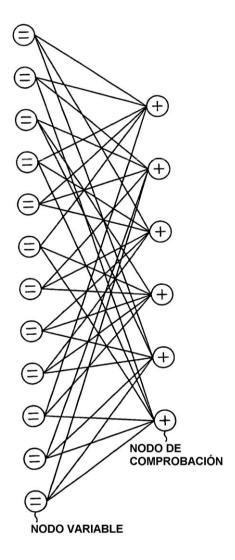

La Fig. 5 es una matriz ejemplificativa de comprobación de paridad del código LDPC (3, 6) (en el que la relación de codificación es 1/2 y la longitud del código es 12). La matriz de comprobación de paridad del código LDPC se puede escribir a través de una gráfica de Tanner, tal como se muestra en la Fig. 6. En este caso, en la Fig. 6, los nodos de comprobación se indican mediante signos "+" y los nodos variables se indican mediante signos "=". Los nodos de comprobación y los nodos variables se corresponden con las filas y columnas, respectivamente, de la matriz de comprobación de paridad. Las conexiones entre los nodos de comprobación y los nodos variables son bordes y se corresponden con "1" de la matriz de comprobación de paridad. Es decir, cuando un componente en la fila j-ésima y la columna i-ésima de la matriz de comprobación de paridad es uno, el nodo variable i-ésimo (un nodo indicado mediante el signo "+") desde la parte superior y el nodo de comprobación j-ésimo (un nodo indicado mediante el signo "+") desde la parte superior se conectan entre sí por el borde, tal como se muestra en la Fig. 6. El borde indica que un bit de código correspondiente al nodo variable tiene una condición de restricción correspondiente al nodo de comprobación. Además, la Fig. 6 muestra la gráfica de Tanner de la matriz de comprobación de paridad mostrada en la Fig. 5.

Como método de decodificación del código LDPC se puede usar un algoritmo de suma producto (Remitirse a Tadashi Wadayama, "Low density parity check code and sum-product algorithm", [online], 22 de junio, 2001, Okayama Prefectural University, [buscado el 19 de Mayo de 2003], Internet <a href="URL:http://vega.c.oka-pu.ac.jp/wadayama/pdf/LDPC.pnf"">URL:http://vega.c.oka-pu.ac.jp/wadayama/pdf/LDPC.pnf</a>", por ejemplo).

Según el algoritmo de suma producto, la operación del nodo variable y la operación del nodo de comprobación se realizan de manera repetitiva.

En el nodo variable, se realiza la operación mostrada en la Ecuación (1) (la operación del nodo variable), tal como se muestra en la Fig. 7. Es decir, según la Fig. 7, el mensaje  $v_i$  correspondiente a un borde para el cual se va a realizar un cálculo se calcula usando mensajes  $u_1$  y  $u_2$  transmitidos desde los otros bordes conectados al nodo variable y los datos de recepción  $u_{0i}$ . Los mensajes correspondientes a los otros bordes se calculan de la misma manera.

A continuación, se rescribe la Ecuación (2) usando la relación expresada mediante la ecuación a x b=  $exp{ln(lal) + ln(lbl)} x sign(a) x sign(b), tal como se muestra mediante la Ecuación (6), antes de describir la operación del nodo de comprobación. En este caso, cuando se cumple la expresión <math>x \ge 0$ , la sign(x) es uno, y cuando se cumple la expresión x < 0, la sign(x) es uno negativo.

5

10

15

20

25

30

35

40

45

50

$$\begin{split} u_{j} &= 2 tanh^{-1} \left( \prod_{i=1}^{d_{c}-1} tanh \left( \frac{v_{i}}{2} \right) \right) \\ &= 2 tanh^{-1} \left[ exp \left\{ \sum_{i=1}^{d_{c}-1} ln \left( \left| tanh \left( \frac{v_{i}}{2} \right) \right| \right) \right\} \times \prod_{i=1}^{d_{c}-1} sign \left( tanh \left( \frac{v_{i}}{2} \right) \right) \right] \\ &= 2 tanh^{-1} \left[ exp \left\{ - \left( \sum_{i=1}^{d_{c}-1} - ln \left( tanh \left( \frac{\left| v_{i} \right|}{2} \right) \right) \right) \right\} \right] \times \prod_{i=1}^{d_{c}-1} sign \left( v_{i} \right) \end{split}$$

#### Ecuación (6)

Además, cuando se cumple la expresión  $x\ge 0$  y  $\varphi(x)$  se define  $\ln(\tanh(x/2))$ , se cumple la expresión  $\varphi^{-1}(x)=2\tanh^{-1}(e^{-x})$ . Por lo tanto, las Ecuaciones (6) se pueden escribir, tal como se muestra mediante la Ecuación (7).

$$u_{j} = \phi^{-1} \left( \sum_{i=1}^{d_{c}-1} \phi(|v_{i}|) \right) \times \prod_{i=1}^{d_{c}-1} \operatorname{sign}(v_{i})$$

Ecuación (7)

Tal como se muestra en la Fig. 8, en el nodo de comprobación, se realiza la operación mostrada en la Ecuación (7) (operación del nodo de comprobación). Es decir, en la Fig. 8, el mensaje  $u_j$  correspondiente a un borde para el cual se va a realizar un cálculo se calcula usando mensajes  $v_1$ ,  $v_2$ ,  $v_3$ ,  $v_4$ , y  $v_5$  transmitidos desde los otros bordes conectados al nodo de comprobación. Los mensajes correspondientes a los otros bordes se calculan de la misma manera.

Además, la función  $\Phi(x)$  se puede expresar como la ecuación  $\varphi(x) = \ln((e^x + 1)/(e^x - 1))$ . Además, la función  $\Phi(x)$  se puede expresar como la ecuación  $\varphi(x) = \varphi^{-1}(x)$ , en donde se cumple la expresión x>0. Las funciones  $\varphi(x)$  y  $\varphi^{-1}(x)$  se montan frecuentemente en hardware usando una LUT (tabla de consulta). Se puede usar la misma LUT para las dos funciones.

Cuando el algoritmo de suma producto se monta en hardware, es necesario realizar de manera repetitiva la operación de nodo variable mostrada en la Ecuación (1) y la operación del nodo de comprobación mostrada en la Ecuación (7) usando un circuito con un tamaño adecuado y a frecuencias de funcionamiento adecuadas.

Además, son ampliamente conocidos los métodos para calcular el coste de la operación de código LDPC usando el algoritmo descrito anteriormente de suma producto (remitirse, por ejemplo, a Matthew C. Davey, David J C MacKay "Low Density Parity Check Codes over GF(q)"").

Para obtener una calidad alta de decodificación usando el algoritmo de suma producto (SPA) según se ha descrito anteriormente, la densidad de la matriz de comprobación de paridad debe ser baja.

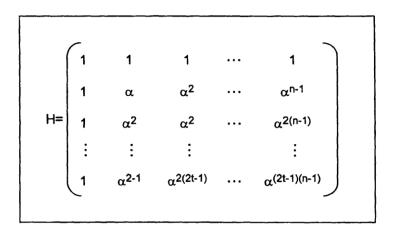

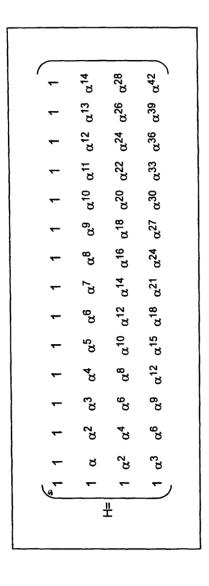

Además, la Fig. 9 muestra una matriz de comprobación de paridad H del otro código lineal corriente, tal como un código Reed-Solomon, en donde se determina que la raíz primitiva de un campo de definición es a. Habitualmente, la densidad de la matriz de comprobación de paridad H de un código lineal no es baja, tal como se muestra en la Fig. 9. Para el código Reed-Solomon cuya densidad no es baja, se realiza una decodificación usando el algoritmo de Euclides o similares (a la que se hará referencia en lo sucesivo como decodificación corriente).

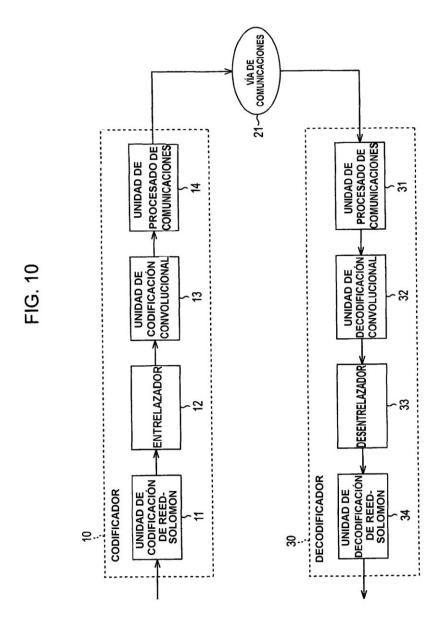

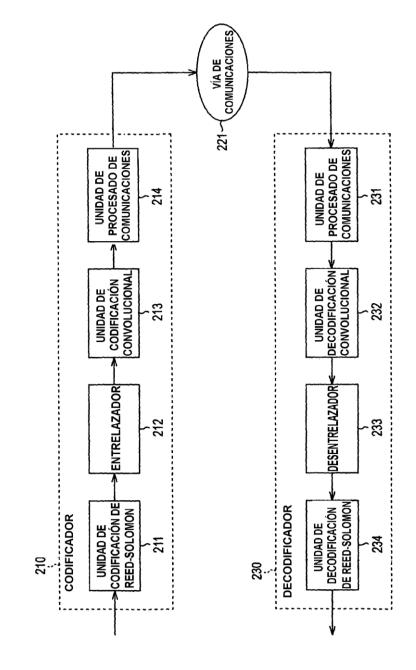

La Fig. 10 es un diagrama de bloques que ilustra la configuración de un sistema ejemplificativo de corrección de errores para ejecutar una corrección de errores usando el código de Reed-Solomon. El sistema de corrección de errores mostrado en la Fig. 10 es un sistema usado para un sistema de comunicaciones digitales tal como, por ejemplo, una TV digital.

En el sistema de corrección de errores mostrado en la Fig. 10, datos digitales transmitidos desde un codificador 10 en el lado de transmisión se transmiten hacia un decodificador 30 en el lado de recepción a través de una vía de comunicaciones 21, tal como, por ejemplo, Internet.

El decodificador 10 incluye una unidad de codificación de Reed-Solomon 11 para codificar datos digitales transmitidos externamente, con vistas a su transmisión, usando el código de Reed-Solomon, un entrelazador 12 para reordenar los datos digitales codificados, una unidad de codificación convolucional 13 para realizar la codificación convolucional, y una unidad de procesado de comunicaciones 14 para comunicarse con el decodificador 30 a través de la vía de comunicaciones 21.

10

15

20

25

30

35

40

45

Además, el decodificador 30 incluye una unidad de procesado de comunicaciones 31 para obtener una palabra de transmisión transmitida a través de la vía de comunicaciones 21, una unidad de decodificación convolucional 32 para realizar una decodificación convolucional para la palabra de transmisión obtenida, un desentrelazador 33 para reinicializar los datos reordenados en el orden original, y una unidad de decodificación de Reed-Solomon 34 para realizar una decodificación de Reed-Solomon (decodificación corriente).

Los datos digitales de transmisión transmitidos desde fuera del codificador 10 se codifican en un código de Reed-Solomon a través de la unidad de codificación de Reed-Solomon 11 del decodificador 10 y se transmiten hacia el entrelazador 12. El entrelazador 12 realiza un reordenamiento (entrelazado) de los datos para difuminar ráfagas de errores que se producen principalmente en la vía de comunicaciones 21. Puesto que el código de Reed-Solomon ejecuta una corrección de errores, en donde una pluralidad de bits se considera como un único símbolo, el entrelazador 12 realiza un entrelazado de símbolos para difuminar las ráfagas de errores por símbolo.

Los datos digitales de transmisión reordenados se someten adicionalmente a una codificación convolucional a través de la unidad de codificación convolucional 13 sobre la base de una pluralidad de bloques de datos de manera que se determinan secuencias de código de forma secuencial. Por ejemplo, tras recibir los datos digitales para cada bloque de datos de k bits desde el entrelazador 12, la unidad de codificación convolucional 13 con una longitud de restricción K codifica los datos digitales en un bloque de código de n bits sobre la base, no solamente del bloque de datos transmitido en ese momento, sino también de K bloques de datos que incluyen bloques de datos que habían sido proporcionados.

A continuación, los datos digitales codificados de manera convolucional se convierten en datos que se pueden transmitir a través de la unidad de procesado de comunicaciones 14 y se transmiten hacia el decodificador 30 a través de la vía de comunicaciones 21.

El decodificador 30 obtiene la palabra de transmisión transmitida a través de la vía de comunicaciones 21 de manera alámbrica o inalámbrica en la unidad de procesado de comunicaciones 31. La palabra de transmisión obtenida se somete a una decodificación convolucional a través de la unidad de decodificación convolucional 32. Tras recibir los datos decodificados de manera convolucional, el desentrelazador 33 realiza un procesado para reinicializar los datos reordenados en el orden original (desentrelazado) a través del reordenamiento de los datos según un método correspondiente al entrelazado realizado por el entrelazador 12 del codificador. La unidad de decodificación de Reed-Solomon 34 ejecuta una decodificación de Reed-Solomon mediante una decodificación corriente para los datos digitales reinicializados en el orden original, reconstruye los datos digitales en el estado previo en el que no se ha realizado todavía la codificación de Reed-Solomon, y transmite los datos hacia fuera del decodificador 30.

Según la manera descrita anteriormente, el sistema de corrección de errores mostrado en la Fig. 10 corrige errores que se producen durante las comunicaciones y ejecuta las comunicaciones de la manera más precisa nunca conseguida.

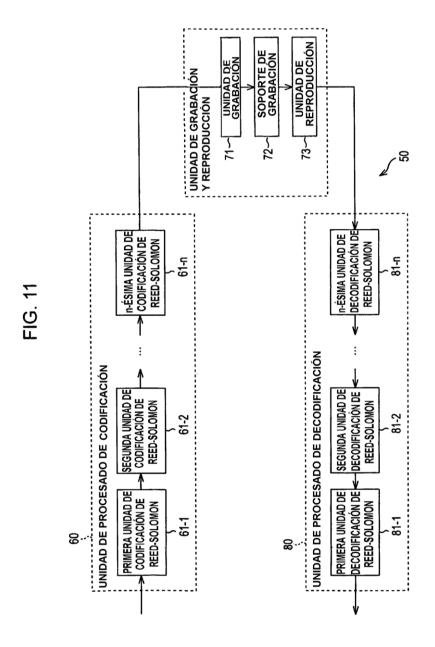

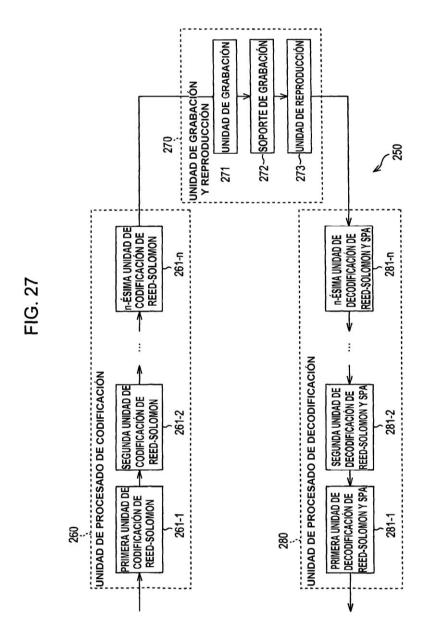

La Fig. 11 es un diagrama de bloques que ilustra la configuración de un aparato ejemplificativo de grabación-y-reproducción que usa el sistema de corrección de errores para realizar la corrección de errores usando el código de Reed-Solomon. El aparato de grabación-y-reproducción mostrado en la Fig. 11 es un aparato de grabación-y-reproducción en soporte de grabación-digital, tal como, por ejemplo, un reproductor de discos DVD (Disco Versátil Digital).

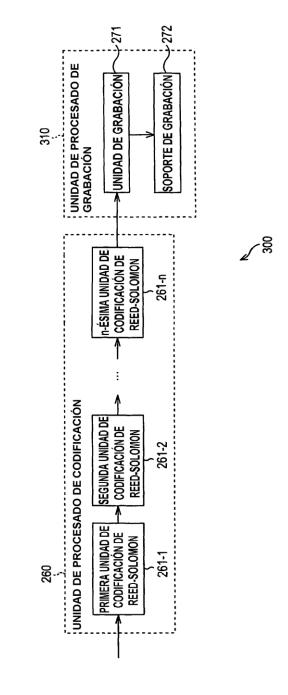

El aparato de grabación-y-reproducción 50 mostrado en la Fig. 11 codifica los datos digitales transmitidos externamente, a través de la unidad de procesado de codificación 60 y graba los datos digitales sobre un soporte de grabación 72 en una unidad de grabación-y-reproducción 70. Además, el aparato de grabación-y-reproducción 50 reproduce los datos digitales grabados sobre el soporte de grabación 72 en la unidad de grabación-y-reproducción 70, obtiene los datos digitales originales a través de la ejecución de una decodificación en una unidad de decodificación 80, y da salida externamente a los datos.

La unidad de procesado de codificación 60 incluye de una primera a una n-ésima unidades de codificación de Reed-Solomon 61-1 a 61-n para ejecutar la codificación de Reed-Solomon para los datos digitales, en donde la codificación de Reed-Solomon se refiere a grados que son diferentes entre sí.

La unidad de grabación-y-reproducción 70 incluye una unidad de grabación 71 para grabar los datos transmitidos desde la unidad de procesado de codificación 60 sobre el soporte de grabación 72, tal como, por ejemplo, un disco óptico, y una unidad de reproducción 73 para reproducir los datos grabados sobre el soporte de grabación 72.

Además, la unidad de procesado de decodificación 80 es un decodificador correspondiente a la unidad de procesado de codificación 60 e incluye de una primera a una n-ésima unidades de decodificación de Reed-Solomon 81-1 a 81-n para ejecutar una decodificación de Reed-Solomon (decodificación corriente) referente a grados que son diferentes entre sí para los datos digitales.

6

5

10

15

20

25

30

35

40

45

50

55

60

Los datos digitales transmitidos desde el exterior de la unidad de procesado de codificación 60 se someten a una codificación de Reed-Solomon referente al grado uno en la primera unidad de codificación de Reed-Solomon 61-1. A continuación, los datos digitales se someten secuencialmente a una codificación de Reed-Solomon referente a cada uno de los grados dos a n en las unidades de codificación de Reed-Solomon segunda a n-ésima 61-2 a 61-n. Cuando la unidad n-ésima de codificación de Reed-Solomon 61-n finaliza la codificación, la unidad de procesado de codificación 60 transmite los datos digitales codificados hacia la unidad de grabación-y-reproducción 70. La unidad de grabación 71 de la unidad de grabación-y-reproducción 70 graba los datos digitales transmitidos desde la unidad de procesado de codificación 60 en el soporte de grabación 72.

La unidad de reproducción 73 de la unidad de grabación-y-reproducción 70 reproduce los datos digitales grabados sobre el soporte de grabación 72 (los datos digitales codificados) y transmite los datos digitales hacia la unidad de procesado de decodificación 80.

La unidad de procesado de decodificación 80 ejecuta una decodificación de Reed-Solomon (decodificación corriente) en relación con cada grado para los datos digitales transmitidos desde la unidad de reproducción 73 en las unidades primera a n-ésima de decodificación de Reed-Solomon 81-1 a 81-n y reconstruye los datos digitales originales. Además, la unidad de procesado de decodificación 80 ejecuta una decodificación que es la inversa de la decodificación realizada por la unidad de procesado de codificación 60. En primer lugar, la unidad de procesado de decodificación 80 ejecuta una decodificación de Reed-Solomon 81-n, y posteriormente ejecuta la decodificación de Reed-Solomon en el orden decreciente de los grados, es decir, desde el grado n-1 al grado n-2. Finalmente, la unidad de procesado de decodificación 80 ejecuta una decodificación referente al primer grado. La unidad de procesado de decodificación 80 da salida a los datos digitales originales reconstruidos hacia el exterior del aparato de grabación-y-reproducción 50.

Tal como se ha descrito, el aparato de grabación-y-reproducción 50 mostrado en la Fig. 11 corrige errores de datos que se producen durante la grabación o reproducción de datos.

La decodificación corriente para el código de Reed-Solomon descrito anteriormente, un código BCH (Bose-Chaudhuri-Hocquenghem), y otros, es un método de decodificación usado para una palabra de recepción de decisión rígida en donde se estima que un valor de recepción es solamente "0" ó "1".

No obstante, cuando se obtiene una palabra de recepción de decisión flexible y cuando un código de Reed-Solomon se somete a la decodificación corriente en un sistema que puede obtener la palabra de recepción de decisión flexible, la calidad de la decodificación es baja. Esto es debido a que la calidad de decodificación obtenida mediante el uso de la palabra de recepción de decisión rígida es habitualmente menor que en el caso en el que se usa la palabra de recepción de decisión flexible.

Posteriormente, se considera el método descrito anteriormente para decodificación usando el algoritmo de suma producto. No obstante, como, en la mayoría de los casos, la densidad de una matriz de comprobación de paridad de un código lineal ampliamente usado no es baja, la calidad de la decodificación no aumenta. Además, si la densidad de una matriz de comprobación de paridad, proporcionada, fuera baja, la configuración de un algoritmo de suma producto sobre un campo finito grande resultaría muy complicada, lo cual haría que aumentase el coste de la operación.

#### **EXPOSICIÓN DE LA INVENCIÓN**

"On Iterative Soft-Decisions Decoding of Linear Binary Block Codes and Product Codes" de Rainer Lucas, Martin Bossert y Markus Breitback, IEEE Journal on Selected Areas in Communications, Volumen 16/2, febrero de 1998, describe la decodificación iterativa de códigos de bloque. El algoritmo de decodificación propuesto usa únicamente vectores de comprobación de paridad de peso mínimo.

Por consiguiente, la presente invención se proporciona para ejecutar de manera sencilla una decodificación de alto rendimiento en el caso en el que, como método para decodificar un código lineal corriente, se usa un algoritmo de suma producto.

La invención se define en las reivindicaciones adjuntas.

### **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

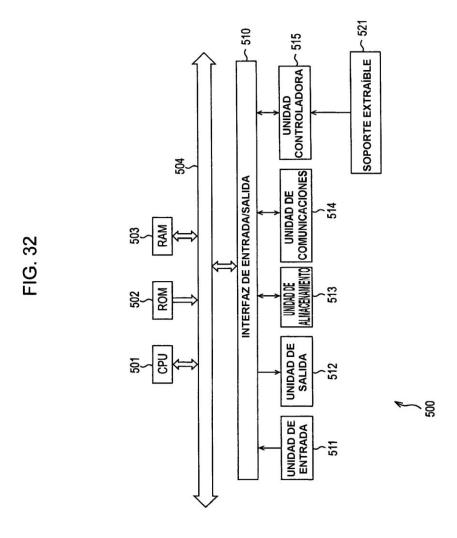

La Fig. 1 ilustra una matriz ejemplificativa de comprobación de paridad de baja densidad.

La Fig. 2 ilustra una gráfica de Tanner correspondiente a la matriz de comprobación de paridad mostrada en la Fig. 1.

La Fig. 3 es un diagrama de flujo que ilustra procesos para decodificar un código LDPC.

La Fig. 4 ilustra el flujo de un mensaje.

7

5

10

15

20

25

30

35

40

45

50

55

60

00

|    | La Fig. 5 ilustra una matriz de comprobación ejemplificativa del código LDPC.                                                                                         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | La Fig. 6 ilustra una gráfica de Tanner de la matriz de comprobación.                                                                                                 |

| 5  | La Fig. 7 muestra un nodo variable.                                                                                                                                   |

|    | La Fig. 8 muestra un nodo de comprobación.                                                                                                                            |

| 10 | La Fig. 9 ilustra una matriz de comprobación de un código de Reed-Solomon.                                                                                            |

|    | La Fig. 10 ilustra la configuración de un sistema conocido y ejemplificativo de corrección de errores.                                                                |

| 15 | La Fig. 11 ilustra la configuración de un aparato conocido y ejemplificativo de grabación-y-reproducción.                                                             |

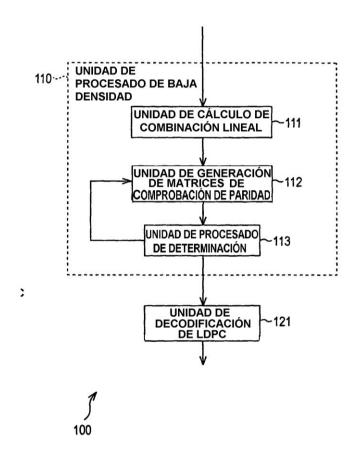

| 13 | La Fig. 12 ilustra la configuración de un decodificador ejemplificativo que usa la presente invención.                                                                |

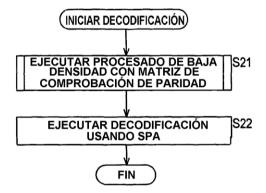

| 20 | La Fig. 13 es un diagrama de flujo que ilustra el procesado de decodificación ejecutado por el decodificador mostrado en la Fig. 12.                                  |

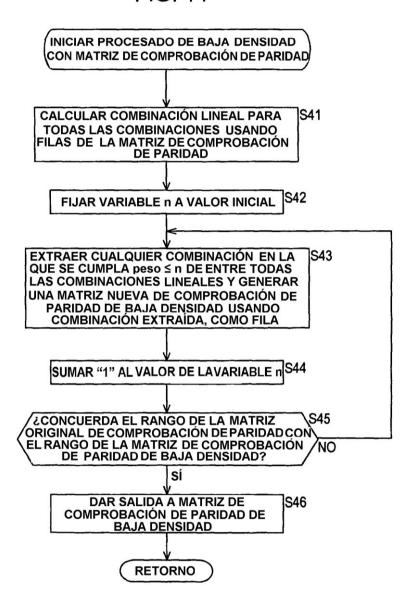

| 20 | La Fig. 14 es un diagrama de flujo que ilustra el procesado de baja densidad con matriz de comprobación de paridad, ejecutado en la etapa S21 mostrada en la Fig. 13. |

| 25 | La Fig. 15 ilustra una matriz ejemplificativa de comprobación de paridad de un código BCH.                                                                            |

| 20 | La Fig. 16 ilustra una gráfica de Tanner correspondiente a la matriz de comprobación de paridad mostrada en la Fig. 15.                                               |

| 30 | La Fig. 17 ilustra una matriz ejemplificativa de comprobación de paridad, expandida.                                                                                  |

| 30 | La Fig. 18 ilustra una gráfica de Tanner correspondiente a la matriz de comprobación de paridad mostrada en la Fig. 17.                                               |

| 35 | La Fig. 19 es una gráfica que muestra comparaciones de decodificaciones.                                                                                              |

|    | La Fig. 20 ilustra la configuración de otro decodificador ejemplificativo que usa la presente invención.                                                              |

| 40 | La Fig. 21 es un diagrama de flujo que muestra un procesado de decodificación ejecutado por el decodificador mostrado en la Fig. 20.                                  |

| .0 | La Fig. 22 ilustra una matriz ejemplificativa de comprobación de paridad del código de Reed-Solomon.                                                                  |

|    | La Fig. 23 ilustra otra matriz ejemplificativa de comprobación de paridad, expandida.                                                                                 |

| 45 | La Fig. 24 es otra gráfica que muestra comparaciones de decodificaciones.                                                                                             |

|    | La Fig. 25 es un diagrama de bloques que ilustra la configuración de un sistema ejemplificativo de corrección de errores que usa la presente invención.               |

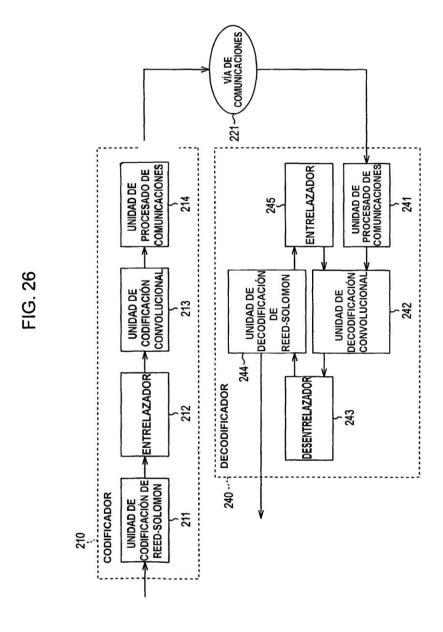

| 50 | La Fig. 26 es un diagrama de bloques que ilustra la configuración de otro sistema ejemplificativo de corrección de errores que usa la presente invención.             |

| 55 | La Fig. 27 es un diagrama de bloques que ilustra la configuración de un aparato ejemplificativo de grabación-y-reproducción que usa la presente invención.            |

| 33 | La Fig. 28 es un diagrama de bloques que muestra la configuración de un aparato de grabación ejemplificativo.                                                         |

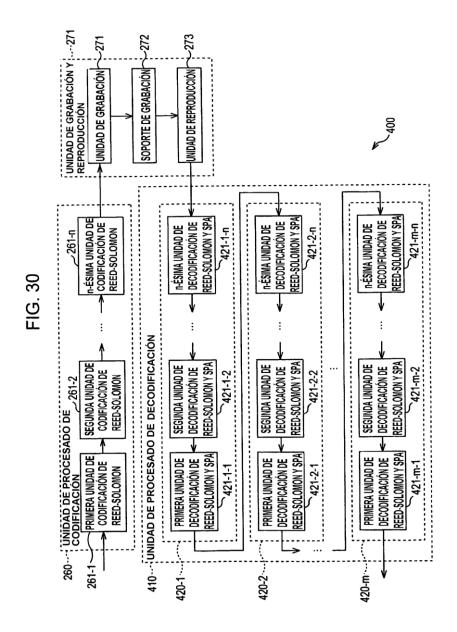

| 60 | La Fig. 29 es un diagrama de bloques que muestra la configuración de un aparato de reproducción ejemplificativo que usa la presente invención.                        |

|    | La Fig. 30 es un diagrama de bloques que ilustra la configuración de otro aparato ejemplificativo de grabación-y-reproducción que usa la presente invención.          |

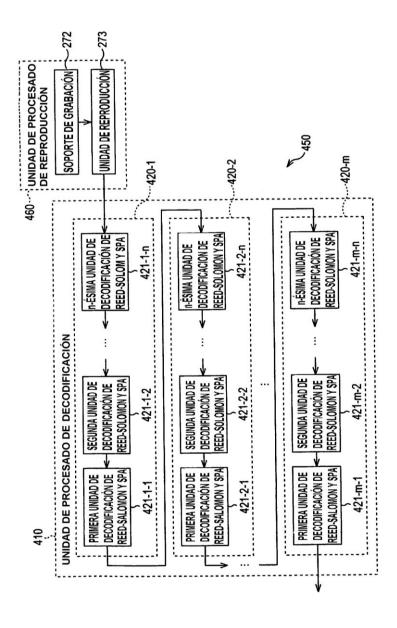

| 65 | La Fig. 31 es un diagrama de bloques que muestra la configuración de otro aparato de reproducción ejemplificativo que usa la presente invención.                      |

La Fig. 32 es un diagrama de bloques que ilustra la configuración de un ordenador según una forma de realización de la presente invención.

#### MEJOR MODO DE PONER EN PRÁCTICA LA INVENCIÓN

Se describirán según se indica a continuación formas de realización de la presente invención. En primer lugar, se describirá una tecnología ejemplificativa que usa la presente invención.

La Fig. 12 es un diagrama de bloques que ilustra la configuración ejemplificativa de un decodificador ejemplificativo que hace uso de la presente invención.

En la Fig. 12, un decodificador 100 es un decodificador que se puede usar, por ejemplo, para un código BCH, y que incluye una unidad de procesado de baja densidad 110 para convertir una matriz de comprobación de paridad de por lo menos una palabra de recepción sobre un anillo R (o un campo finito) en una matriz cuya densidad es suficientemente baja, y una unidad de decodificación de LDPC 121 para decodificar la palabra de recepción usando la matriz de comprobación de paridad de baja densidad.

La unidad de procesado de baja densidad 110 incluye una unidad de cálculo de combinación lineal 111 para calcular una combinación lineal de filas de la matriz de comprobación de paridad, una unidad de generación de matrices de comprobación de paridad 112 para generar una matriz de comprobación de paridad suficientemente poco densa mediante el uso de las filas combinadas linealmente, y una unidad de determinación 113 para determinar si el rango de la matriz de comprobación de paridad original.

La unidad de cálculo de combinación lineal 111 calcula la combinación lineal de filas de una matriz de comprobación de paridad incluida en una palabra de recepción obtenida, para todas las combinaciones. Es decir, la unidad de cálculo de combinación lineal 111 calcula 2<sup>n</sup> maneras de combinación lineal para una matriz de comprobación de paridad que tiene n filas. La unidad de cálculo de combinación lineal 111 transmite el resultado del cálculo y las palabras de recepción hacia la unidad de generación de matrices de comprobación de paridad 112.

La unidad de generación de matrices de comprobación de paridad 112 extrae filas del resultado del cálculo transmitido desde la unidad de cálculo de combinación lineal 111, es decir, las filas combinadas linealmente, a partir de criterios predeterminados, y genera una matriz de comprobación de paridad que incluye las filas extraídas. La unidad de generación de matrices de comprobación de paridad 112 fija criterios predeterminados de manera que la densidad de la matriz de comprobación de paridad generada resulte baja. Por ejemplo, se puede disponer que se extraiga una fila predeterminada de entre las filas combinadas linealmente, en la que el número de elementos cuyos valores son "1" sea menor que un número predeterminado. A continuación, la unidad de generación de matrices de comprobación de paridad 112 extrae por lo menos una fila que cumple los criterios. La unidad de generación de matrices de comprobación de paridad 112 transmite la matriz de comprobación de paridad generada y la palabra de recepción hacia la unidad de determinación 113. Además, tal como se describirá posteriormente, cuando la unidad de determinación 113 determina que el rango de la matriz de comprobación de paridad generada es diferente al de la matriz de comprobación de paridad original, la unidad de generación de matrices de comprobación de paridad 112 ejecuta nuevamente la extracción de filas, y genera una nueva matriz de comprobación de paridad. En ese momento, la unidad de generación de matrices de comprobación de paridad 112 cambia los criterios para la extracción previa de filas y genera una matriz de comprobación de paridad que incluye filas diferentes a las de la matriz de comprobación de paridad generada previamente.

La unidad de determinación 113 determina si el rango de la matriz de comprobación de paridad generada por la unidad de generación de matrices de comprobación de paridad 112 concuerda o no con el de la matriz de comprobación de paridad original. Cuando se determina que los rangos concuerdan entre sí, la unidad de determinación 113 transmite la palabra de recepción y la matriz de comprobación de paridad generada hacia la unidad de decodificación de LDPC 121. Cuando se determina que los rangos no concuerdan entre sí, la unidad de determinación 113 cambia el procesado de vuelta hacia la unidad de generación de matrices de comprobación de paridad 112, de manera que la unidad de generación de matrices de comprobación de paridad 112 genera otra matriz nueva de comprobación de paridad.

Tal como se ha descrito, la unidad de procesado de baja densidad 110 reduce la densidad de la matriz de comprobación de paridad del código BCH incluido en la palabra de recepción y transmite la matriz de comprobación de paridad de baja densidad y la palabra de recepción hacia la unidad de decodificación de LDPC 121.

La unidad de decodificación de LDPC 112 decodifica las palabras de recepción según un algoritmo de suma producto usando la matriz obtenida de comprobación de paridad de baja densidad y da salida externamente a la palabra de recepción decodificada fuera del decodificador 100.

Tal como se ha descrito anteriormente, la unidad de procesado de baja densidad 110 reduce la densidad de la matriz de comprobación de paridad de las palabras de recepción, con lo cual la unidad de decodificación de LDPC 121 puede ejecutar la decodificación que usa el algoritmo de suma producto usando la matriz de

5

15

10

20

25

30

35

40

45

50

55

60

comprobación de paridad de baja densidad. A continuación, se puede ejecutar la decodificación de alto rendimiento. Además, puesto que la unidad de procesado de baja densidad 110 reduce la densidad de la matriz de comprobación de paridad de la palabra de recepción a través de la combinación lineal, la unidad de decodificación de LDPC 121 puede ejecutar la decodificación sobre un subcampo y reducir el coste de la operación. Es decir, como la densidad de la matriz de comprobación de paridad se reduce a través de la combinación lineal antes de ejecutar la decodificación que usa el algoritmo de suma producto, el decodificador 100 puede ejecutar de manera sencilla la decodificación de alto rendimiento.

A continuación, se describirá, haciendo referencia a un diagrama de flujo mostrado en la Fig. 13, la decodificación ejecutada por el decodificador descrito anteriormente.

En primer lugar, la unidad de procesado de baja densidad 110 del decodificador 100 ejecuta un procesado de baja densidad con matriz de comprobación de paridad, en la etapa S21, para reducir la densidad de una matriz de comprobación de paridad incluida en una palabra de recepción obtenida. Los detalles del procesado de baja densidad con matriz de comprobación de paridad se describirán posteriormente haciendo referencia a un diagrama de flujo de la Fig. 14.

A continuación, en la etapa S22, la unidad de decodificación de LDPC 121 ejecuta una decodificación que usa el algoritmo de suma producto (SPA) utilizando la matriz de comprobación de paridad cuya densidad se reduce a través del procesado en la etapa S21. Cuando ha finalizado el procesado en la etapa S22, la unidad de decodificación de LDPC 121 termina la decodificación para la palabra de recepción. Además, el decodificador 100 ejecuta la decodificación descrita anteriormente para cada palabra de recepción (cada bloque).

Seguidamente, se describirán, haciendo referencia al diagrama de flujo de la Fig. 14, los detalles del procesado de baja densidad con matriz de comprobación de paridad realizado en la etapa S21 mostrada en la Fig. 13.

En primer lugar, en la etapa S41, la unidad de cálculo de combinación lineal 111 de la unidad de procesado de baja densidad 110 combina linealmente las filas de la matriz de comprobación de paridad incluida en la palabra de recepción obtenida, de todas las maneras posibles, y calcula el resultado de la combinación.

Después de calcular la combinación lineal, la unidad de cálculo de combinación lineal 111 fija el valor de una variable n que funciona como criterios de extracción de filas, según se describirá posteriormente, a un valor inicial tal como "1", en la etapa S42. A continuación, una unidad de cálculo de combinación lineal 111 transmite la palabra de recepción, el resultado de cálculo de la combinación lineal, y la variable n hacia la unidad de generación de matrices de comprobación de paridad 112, de manera que el procesado avanza hacia la etapa S43.

En la etapa S43, la unidad de generación de matrices de comprobación de paridad 112 calcula un peso que indica el número de elementos cuyos valores se determina que es "1" para cada uno de los resultados obtenidos de la combinación lineal, extrae filas con el peso predeterminado de entre todos los resultados de la combinación lineal, en las que el peso extraído que indica el número de elementos cuyos valores se han determinado que son "1" es menor que la variable n, y genera una matriz de comprobación de paridad de baja densidad que incluye las filas extraídas.

Es decir, la unidad de generación de matrices de comprobación de paridad 112 extrae un subconjunto de vectores con pesos inferiores, en donde el subconjunto forma un espacio complementario de código, de entre el conjunto de vectores obtenidos a través de la combinación lineal calculada por la unidad de cálculo de combinación lineal 111, y genera una nueva matriz de comprobación de paridad que incluye todos los vectores del subconjunto de vectores, en los que los vectores funcionan como elementos de fila.

Después de generar la matriz nueva de comprobación de paridad, la unidad de generación de matrices de comprobación de paridad 112 hace avanzar el procesado hacia la etapa S44, suma (1) al valor de la variable n, y transmite la palabra de recepción, la matriz generada de comprobación de paridad, y la variable n hacia la unidad de determinación 113.

Tras recibir la palabra de recepción, la matriz generada de comprobación de paridad, y la variable n, la unidad de determinación 113 determina si el rango de la matriz original de comprobación de paridad concuerda o no con el rango de la matriz de comprobación de paridad de baja densidad basándose en información referente a la matriz original de comprobación de paridad incluida en la palabra de recepción, en la etapa S45.

Por ejemplo, cuando se determina que el rango de la matriz de comprobación de paridad de baja densidad es bajo y no concuerda con el de la matriz original de comprobación de paridad, la unidad de determinación 113 vuelve a la etapa S43 y repite el procesado desde allí en adelante. Es decir, la unidad de determinación 113 transmite su resultado de determinación hacia la unidad de generación de matrices de comprobación de paridad 112 y hace que la unidad de generación de matrices de comprobación de paridad 112 vuelva a generar una matriz de comprobación de paridad de baja densidad. En ese momento, el valor de la variable n que funciona como criterios de extracción a partir del resultado de la combinación lineal es diferente al del procesado previo. Por lo

5

15

10

20

25

30

35

40

45

50

55

60

tanto, la unidad de generación de matrices de comprobación de paridad 112 puede generar una matriz de comprobación de paridad de baja densidad que tiene filas diferentes a las del procesado previo (elementos diferentes a los del procesado previo).

5

Cuando se determina que el rango de la matriz original de comprobación de paridad concuerda con el de la matriz de comprobación de paridad de baja densidad, en la etapa S45, la unidad de determinación 113 avanza hacia la etapa S46, transmite las palabras de recepción y la matriz generada de comprobación de paridad de baja densidad hacia la unidad de decodificación de LDPC 121, y vuelve a la etapa S22 mostrada en la Fig. 13.

10

Mediante la realización de la decodificación y el procesado de baja densidad de la matriz de comprobación de paridad según la manera descrita anteriormente, el decodificador 100 reduce la densidad de la matriz de comprobación de paridad a través de una combinación lineal antes de realizar la decodificación que usa el algoritmo de suma producto. Por lo tanto, el decodificador 100 puede realizar de forma sencilla una decodificación de alto rendimiento.

15

A continuación, se describirá detalladamente una reducción de densidad ejemplificativa que hace uso del decodificador descrito anteriormente 100.

20

En el siguiente ejemplo, se determina que un campo finito es un campo finito GF  $(2^4)$  cuyos elementos son potencias de números primos (un campo de extensión de grado 4 de GF(2)), un código lineal se indica mediante C, y se decodifica un código BCH (15, 7) del cual se determina que su longitud de código y longitud de datos son quince y siete.

25

Tal como se muestra en la Fig. 15, se proporciona por ejemplo una matriz de comprobación de paridad H del código lineal C. La matriz de comprobación de paridad H mostrada en la Fig. 15 es una matriz que incluye ocho filas y quince columnas. Tal como se muestra en la Fig. 16, se proporciona una gráfica de Tanner correspondiente a la matriz de comprobación de paridad H. En la gráfica de Tanner mostrada en la Fig. 16, cada columna de la matriz de comprobación de paridad H se muestra como un nodo variable indicado mediante "=" y cada fila se muestra como un nodo de comprobación indicado mediante "+". La densidad de bordes que conectan los nodos variables a los nodos de comprobación es alta, lo cual muestra que la matriz de comprobación de paridad H mostrada en la Fig. 15 no es una matriz de baja densidad.

30

35

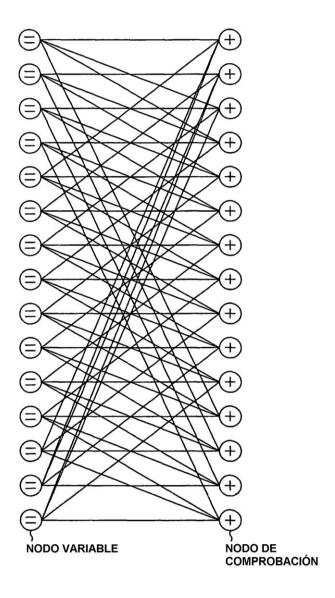

Tal como se ha descrito anteriormente, la unidad de procesado de baja densidad 110 mostrada en la Fig. 12 realiza una combinación lineal usando las ocho filas descritas anteriormente y genera 2<sup>8</sup>=256 segmentos de vectores de fila cuya densidad de "1" es baja. A continuación, la unidad de procesado de baja densidad 110 extrae quince segmentos de vectores de fila, en los que el número de "1" es cuatro o menos, y genera una matriz nueva H<sub>sp4</sub> que incluye vectores de quince elementos alineados verticalmente, tal como se muestra en la Fig. 17. La Fig. 18 muestra una gráfica de Tanner correspondiente a la matriz H<sub>sp4</sub> mostrada en la Fig. 17. Puesto que tanto el número de filas como el número de columnas de la matriz H<sub>sp4</sub> mostrada en la Fig. 17 es quince, el número de nodos variables así como el número de nodos de comprobación de la gráfica de Tanner mostrada en la Fig. 18 es quince. Es decir, la densidad de bordes que conectan los nodos variables a los nodos de comprobación es menor que en el caso de la Fig. 16.

40

La unidad de procesado de baja densidad 110 determina que la matriz descrita anteriormente H<sub>sp4</sub> es una matriz de comprobación de paridad y transmite la matriz H<sub>sp4</sub> hacia la unidad de decodificación de LDPC 121. La unidad de decodificación de LDPC 121 decodifica la palabra de recepción usando el algoritmo de suma producto mediante la utilización de la matriz de comprobación de paridad de baja densidad H<sub>sp4</sub> mostrada en la Fig. 17.

45

La Fig. 19 es una gráfica que muestra una comparación entre el caso en el que se decodifica el código BCH que incluye la matriz de comprobación de paridad descrita anteriormente siguiendo un procedimiento de máxima verosimilitud a través de una decodificación de Viterbi y el caso en el que el código BCH se decodifica usando el algoritmo de suma producto mediante la utilización de la matriz de comprobación de paridad de baja densidad H<sub>S04</sub> mostrada en la Fig. 17.

55

50

En la Fig. 19, una curva 131 muestra la tasa de errores de bit (BER) del resultado de la decodificación mediante el uso del algoritmo de suma producto (SPA) ((2) bch 15 7(peso4) SPA BER) y una curva 132 indica la tasa de errores de bit (BER) del resultado de la decodificación obtenido mediante una decodificación de Viterbi ((1) bch 15 7 ML BER). Además, los datos representados por un punto 133 indican una tasa de errores de trama (FER) del resultado de la decodificación usando el algoritmo de suma producto ((2) bch 15 7(peso4) SPA FER) y los datos representados por un punto 134 indican una tasa de errores de trama (FER) del resultado de la decodificación obtenido mediante una decodificación de Viterbi ((1) bch 15 7 ML FER).

60

La decodificación de máxima verosimilitud (la curva 132 mostrada en la Fig. 19) indica el límite del rendimiento obtenido en el caso en el que se usa una decodificación de probabilidad tal como el algoritmo de suma producto. La curva 131 que usa la presente invención indica un rendimiento que se aproxima al límite del rendimiento, tal como se muestra en la Fig. 19.

Tal como se ha descrito anteriormente, el decodificador 100 reduce la densidad de la matriz de comprobación de paridad a través de una combinación lineal antes de decodificar el código BCH usando el algoritmo de suma producto. Posteriormente, el decodificador 100 puede realizar de forma sencilla una decodificación de alto rendimiento.

5

Aunque se ha descrito la decodificación del código BCH, se puede usar cualquier método de códigos sin limitarse al mismo, siempre que se use un código lineal ampliamente utilizado, tal como un código de Reed-Solomon. A continuación se describirá, según la manera que se expone seguidamente, el caso en el que la señal de Reed-Solomon se decodifica usando el algoritmo de suma producto.

10

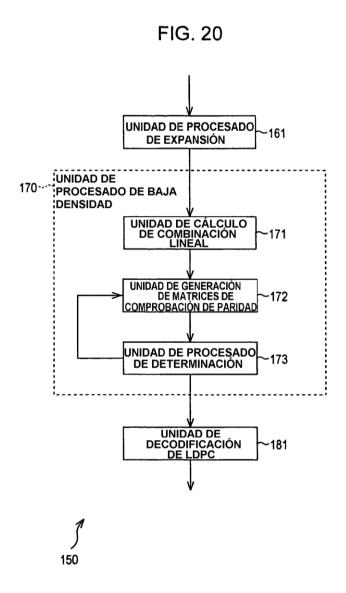

La Fig. 20 es un diagrama de bloques que muestra la configuración de otro decodificador ejemplificativo que usa la presente invención.

15

En la Fig. 20, un decodificador 150 es un decodificador compatible con el código de Reed-Solomon, por ejemplo, e incluye una unidad de expansión 161 para expandir la matriz de comprobación de paridad de una palabra de recepción, una unidad de procesado de baja densidad 170 para convertir la matriz expandida de comprobación de paridad en una matriz cuya densidad es suficientemente baja, y una unidad de decodificación de LDPC 181 para decodificar la palabra de recepción usando la matriz de comprobación de paridad de baja densidad.

20

La unidad de procesado de expansión 161 expande cada uno de los elementos de una matriz de comprobación de paridad incluidos en una palabra de recepción obtenida, en un grado predeterminado de acuerdo con el grado de un campo finito de la matriz, como preprocesado del procesado de baja densidad para la matriz de comprobación de paridad. Es decir, la unidad de procesado de expansión 161 expande la matriz de comprobación de paridad sobre el campo finito cuyos elementos son potencias de números primos en un subcampo del campo finito en grados predeterminados. La unidad de procesado de baja densidad 161 transmite la matriz expandida de comprobación de paridad y la palabra de recepción hacia la unidad de procesado de baja densidad 170.

25

30

El procesado de baja densidad 170 incluye una unidad de cálculo de combinación lineal 171 para calcular una combinación lineal de filas de la matriz de comprobación de paridad, una unidad de generación de matrices de comprobación de paridad 172 para generar una matriz de comprobación de paridad suficientemente poco densa usando las filas combinadas linealmente, y una unidad de determinación 173 para determinar si el rango de la matriz de comprobación de paridad generada es o no el mismo que el de la matriz original de comprobación de paridad. Puesto que la configuración y las operaciones de cada una de las unidades descritas anteriormente son las mismas que las de la unidad de procesado de baja densidad 110 del decodificador 100 mostrado en la Fig. 12, se omite su descripción. Es decir, las unidades que incluyen la unidad de cálculo de combinación lineal 171 a la unidad de determinación 173 de la unidad de procesado de baja densidad 170 se corresponden con las que incluyen desde la unidad de cálculo de combinación lineal 111 al límite de determinación 113 mostrados en la Fig. 12. No obstante, la unidad de procesado de baja densidad 170 ejecuta un procesado de baja densidad para la matriz expandida de comprobación de paridad transmitida desde la unidad de expansión 161.

35

La unidad de procesado de baja densidad 170 reduce la densidad de la matriz de comprobación de paridad del código de Reed-Solomon expandida por la unidad de procesado de expansión 161 y transmite la matriz de comprobación de paridad de baja densidad y la palabra de recepción hacia la unidad de decodificación de LDPC 181.

45

40

La unidad de decodificación de LDPC 181 decodifica la palabra de recepción a través del algoritmo de suma producto usando la matriz obtenida de comprobación de paridad de baja densidad, y da salida a la palabra de recepción decodificada al exterior del decodificador 150.

50

De este modo, puesto que la unidad de procesado de expansión 161 expande la matriz de comprobación de paridad antes de que la unidad de procesado de baja densidad 170 reduzca la densidad de la matriz de comprobación de paridad, el coste de operación de la decodificación realizada por la unidad de decodificación de LDPC 181 a través del algoritmo de suma producto mediante el uso de la matriz de comprobación de paridad de baja densidad H<sub>sp24</sub> se reduce a aproximadamente un cuarto del coste de operación en el caso en el que la decodificación se realiza a través del algoritmo de suma producto usando la matriz de comprobación de paridad H incluida en la palabra de recepción, tal como se muestra en la Ecuación (8) que se presenta a continuación.

55

# {SPA ON $H_{sp24}$ } ~ 1/4{SPA ON H} Ecuación (8)

60

Seguidamente, el decodificador 150 puede ejecutar de forma sencilla una decodificación de alto rendimiento.

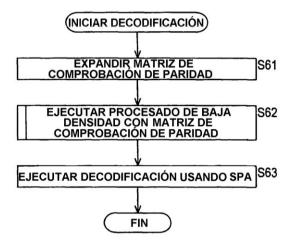

A continuación, se describirá, haciendo referencia a un diagrama de flujo mostrado en la Fig. 21, la decodificación ejecutada por el decodificador descrito anteriormente 150.

En primer lugar, la unidad de procesado de expansión 161 del decodificador 150 expande una matriz de comprobación de paridad incluida en una palabra de recepción obtenida, según el grado del campo finito de la misma, en la etapa S61. A continuación, la unidad de procesado de expansión 161 transmite la matriz expandida de comprobación de paridad y la palabra de recepción hacia la unidad de procesado de baja densidad 170, de manera que el procesado avanza hacia la etapa S62.

5

10

15

20

25

30

35

40

45

50

55

60

La unidad de procesado de baja densidad 170 ejecuta el procesado de baja densidad de la matriz de comprobación de paridad, en la etapa S62, de manera que se reduce la densidad de la matriz expandida de comprobación de paridad. Puesto que los detalles del procesado de baja densidad de la matriz de comprobación de paridad son los mismos que los descritos haciendo referencia al diagrama de flujo mostrado en la Fig. 14, se omite la descripción detallada. No obstante, en el procesado descrito anteriormente de baja densidad de la matriz de comprobación de paridad, la unidad de procesado de baja densidad 170 reduce la densidad de la matriz de comprobación de paridad expandida por la unidad de procesado de expansión 161 según la manera descrita anteriormente.

A continuación, en la etapa S63, la unidad de decodificación de LDPC 181 ejecuta la decodificación a través del algoritmo de suma producto (SPA) usando la matriz de comprobación de paridad cuya densidad se reduce a través del procesado ejecutado, en la etapa S62. Después de finalizar el procesado en la etapa S63, la unidad de decodificación de LDPC 121 termina la decodificación para la palabra de recepción. El decodificador 150 ejecuta la decodificación descrita anteriormente para cada palabra de recepción (cada bloque).

Ejecutando la decodificación según la manera descrita anteriormente, el decodificador 150 expande cada elemento de la matriz de comprobación de paridad antes de realizar la reducción de la densidad. Seguidamente, el decodificador 150 puede ejecutar de manera sencilla una decodificación de alto rendimiento.

A continuación, se describirá detalladamente una expansión ejemplificativa realizada a través del decodificador descrito anteriormente 150.

En el siguiente ejemplo, se determina que un campo finito es  $GF(2^4)$ , un código lineal se indica mediante C, y se decodifica un código de Reed-Solomon (15, 11) cuya longitud de código se ha determinado que es quince y la longitud de datos se ha determinado que es once. Además, se determina que la raíz primitiva de  $GF(2^4)$  es a, se proporciona un polinomio primitivo que incluye la raíz primitiva a, como Ecuación (9), y se proporciona un polinomio generador de código, como Ecuación (10).

$$\alpha^4 + \alpha + 1 = 0$$

Ecuación(9)

$$g(x) := (x+1)(x+\alpha)(x+\alpha^2)(x+\alpha^3)$$

Ecuación (10)

Tal como se muestra en la Fig. 22, se proporciona una matriz de comprobación de paridad del código lineal C en ese momento. La matriz de comprobación de paridad H mostrada en la Fig. 22 es una matriz que incluye cuatro filas y quince columnas. Puesto que el campo finito GF(2<sup>4</sup>) es un campo de extensión de grado cuatro de GF(2), todos los elementos y columnas sobre el campo finito GF(2<sup>4</sup>) se pueden expandir en grado cuatro. La unidad de procesado de expansión 161 del decodificador 150 expande y convierte la matriz de comprobación de paridad H mostrada en la Fig. 22 en una matriz de comprobación de paridad H<sub>exp</sub> que tiene dieciséis filas y sesenta columnas, tal como se muestra en la Fig. 23. En ese caso, la unidad de procesado de expansión 161 expande cada elemento de la matriz de comprobación de paridad H mostrada en la Fig. 22 en un grupo de 4 por 4 elementos, con lo cual se genera la matriz de comprobación de paridad H<sub>exp</sub> mostrada en la Fig. 23.

La unidad de procesado de baja densidad 170 del decodificador 150 ejecuta una reducción de densidad para la matriz expandida de comprobación de paridad  $H_{\text{exp}}$ . La unidad de decodificación de LDPC 181 ejecuta una decodificación a través del algoritmo de suma producto usando la matriz de comprobación de paridad de baja densidad  $H_{\text{exp}}$ .

La Fig. 24 es una gráfica que muestra una comparación entre el rendimiento de la decodificación obtenido cuando un código de Reed-Solomon que incluye la matriz descrita anteriormente de comprobación de paridad se decodifica a través de una decodificación corriente y el obtenido cuando el código de Reed-Solomon se decodifica a través del algoritmo de suma producto usando la matriz de comprobación de paridad H<sub>sp24</sub> obtenida mediante la reducción de la densidad de la matriz expandida de comprobación de paridad H<sub>exp</sub> mostrada en la Fig. 23.

En la Fig. 24, una curva 191 muestra una tasa de errores de bit (BER) del resultado de la decodificación realizada a través del algoritmo de suma producto (SPA) usando la matriz de comprobación de paridad de baja densidad H<sub>sp24</sub> ((4) RS peso24 SPA BER) y una curva 192 indica una tasa de errores de bit (BER) del resultado de una decodificación corriente ((3) RS ORD BER). Además, los datos representados por un punto 193 indican una tasa de errores de trama (FER) del resultado de una decodificación realizada a través del algoritmo de suma

producto usando la matriz de comprobación de paridad de baja densidad  $H_{sp24}$  ((4) RS peso24 SPA FER) y los datos representados por un punto 194 indican una tasa de errores de trama (FER) del resultado de una decodificación corriente ((3) RS ORD FER).

5

La curva 191 (el punto 193) que indica el resultado de la decodificación usando la presente invención muestra un rendimiento mayor que el de la curva 192 (el punto 194) que indica el resultado de una decodificación corriente, según se muestra en la Fig. 24.

10

Tal como se ha descrito, el decodificador 150 reduce la densidad de la matriz de comprobación de paridad a través de una combinación lineal antes de decodificar el código de Reed-Solomon usando el algoritmo de suma producto. Por lo tanto, el decodificador 150 puede lograr de forma sencilla una decodificación de alto rendimiento. Además, el decodificador 150 expande cada uno de los elementos y columnas de la matriz de comprobación de paridad antes de reducir la densidad de la matriz de comprobación de paridad. Subsiguientemente, se puede reducir el coste de la operación.

15

La Fig. 25 es un diagrama de bloques que muestra la configuración de un sistema ejemplificativo de corrección de errores usando un código de Reed-Solomon. El sistema de corrección de errores mostrado en la Fig. 25 es un sistema usado para un sistema de comunicaciones digitales, tal como, por ejemplo, una TV digital.

20

En el sistema de corrección de errores mostrado en la Fig. 25, datos digitales transmitidos desde un codificador 210 en el lado de transmisión se transmiten hacia un decodificador 230 en el lado de recepción a través de una vía de comunicaciones 221, tal como, por ejemplo, Internet.

25

El codificador 210 incluye una unidad de codificación de Reed-Solomon 211 para codificar datos digitales transmitidos externamente con vistas a su transmisión, usando el código de Reed-Solomon, un entrelazador 212 para reordenar los datos digitales codificados, una unidad de codificación convolucional 213 para ejecutar una codificación convolucional, y una unidad de comunicaciones 214 para comunicarse con el decodificador 230 a través de la vía de comunicaciones 221.

30

La unidad de codificación de Reed-Solomon 211 codifica los datos digitales transmitidos desde el exterior del codificador 210 usando el código de Reed-Solomon y transmite los datos digitales codificados hacia el entrelazador 212. El entrelazador 212 reordena los datos digitales codificados (entrelazado) para difuminar ráfagas de errores que se producen principalmente en la vía de comunicaciones 221. Puesto que el código de Reed-Solomon ejecuta una corrección de errores, en la que se reordena una pluralidad de bits, en forma de un único símbolo, el entrelazador 212 ejecuta un entrelazado de símbolos para difuminar ráfagas de errores en símbolos. Después de finalizar el reordenamiento de los datos, el entrelazador 212 transmite los datos digitales reordenados hacia la unidad de codificación convolucional 213.

35

La unidad de codificación convolucional 213 remite a datos que fueron codificados en el pasado para los datos digitales reordenados y ejecuta una codificación convolucional basándose en una pluralidad de bloques de datos, con lo cual una secuencia de código se fija en orden. Por ejemplo, tras recibir los datos digitales para cada bloque de datos de k bits desde el entrelazador 212, la unidad de codificación convolucional 213 con una longitud de restricción K codifica los datos digitales en un bloque de código de n bits basándose, no solamente en el bloque de datos transmitido en ese momento, sino también en K bloques de datos que incluyen bloques de datos que habían sido proporcionados. Después de finalizar la codificación convolucional, la unidad de codificación convolucional 213 transmite los datos digitales codificados convolucionalmente hacia la unidad de comunicaciones

40

45

214.

La unidad de comunicaciones 214 ejecuta un procesado de control de comunicaciones y transmite hacia el decodificador 230 los datos digitales transmitidos, en forma de una palabra de transmisión a través de la vía de comunicaciones 221 sobre la base de un protocolo predeterminado.

50

Los datos digitales transmitidos desde el codificador 210 se transmiten hacia el decodificador 230 a través de la vía de comunicaciones 221.

55

El decodificador 230 incluye una unidad de comunicaciones 231 para recibir los datos digitales transmitidos a través de la vía de comunicaciones 221, en forma de una palabra de recepción, una unidad de decodificación convolucional 232 para ejecutar una decodificación convolucional para la palabra de recepción obtenida por la unidad de comunicaciones 231, un desentrelazador 233 para reordenar la palabra de recepción decodificada convolucionalmente en su orden original, y una unidad de decodificación de SPA y Reed-Solomon 234 para decodificar los datos digitales reordenados en el orden original a través del algoritmo de suma producto y reconstruir los datos digitales en el estado previo en el que no se ha realizado todavía la codificación de Reed-Solomon.

60

La unidad de comunicaciones 231 se comunica con la unidad de comunicaciones 214 del codificador 210 a través de la vía de comunicaciones 221 y obtiene los datos digitales transmitidos desde la unidad de comunicaciones 214, en forma de una palabra de recepción, sobre la base de un protocolo predeterminado. La

unidad de comunicaciones 231 transmite la palabra de recepción obtenida hacia la unidad de decodificación convolucional 232.

La unidad de decodificación convolucional 232 decodifica la palabra de recepción transmitida desde la unidad de transmisión 231 según un método que se corresponde con el método de codificación ejecutado por la unidad de codificación convolucional 213 del codificador 210. Es decir, la unidad de decodificación convolucional 232 ejecuta una decodificación de decisión flexible para la palabra de recepción usando el algoritmo de BCJR (Bahl, Cocke, Jelinek, y Raviv), el SOVA (algoritmo de Viterbi de salida flexible), y otros, con el fin de lograr una decodificación de Probabilidad máxima a posteriori (por ejemplo, decodificación MAP). A continuación, la unidad de decodificación convolucional 232 transmite la palabra de recepción decodificada por decisión flexible hacia el desentrelazador 233.

5

10

15

20

25

30

35

40

45

50

55

60

65

El desentrelazador 233 ejecuta un reordenamiento de datos para la palabra de recepción transmitida, según un método que se corresponde con el entrelazado ejecutado por el entrelazador 212 del codificador 210, ejecuta un procesado para reinicializar los datos reordenados al orden original (desentrelazado), y transmite la palabra de recepción reordenada en el orden original hacia la unidad de decodificación de SPA y Reed-Solomon 234.

Básicamente, la unidad de decodificación de SPA y Reed-Solomon 234 está configurada y funciona tal como el caso del decodificador 150 mostrado en la Fig. 20. Además, el diagrama de bloques mostrado en la Fig. 20 y el diagrama de flujo mostrado en la Fig. 21 se pueden usar para la unidad de decodificación de SPA y Reed-Solomon 234. Por lo tanto, se omitirá su descripción.

La unidad de decodificación de SPA y Reed-Solomon 234 expande la matriz de comprobación de paridad de la palabra de recepción sometida a la codificación de Reed-Solomon y reduce la densidad de la matriz de comprobación de paridad de la misma. A continuación, la unidad de decodificación de SPA y Reed-Solomon 234 ejecuta la decodificación a través del algoritmo de suma producto usando la matriz de comprobación de paridad y reconstruye los datos digitales al estado previo en el que no se ha realizado todavía la codificación. La unidad de decodificación de SPA y Reed-Solomon 234 transmite los datos digitales decodificados hacia el exterior del decodificador 230.

Tal como se ha descrito anteriormente, el sistema de corrección de errores mostrado en la Fig. 25 puede realizar de forma sencilla una decodificación de alto rendimiento y ejecutar las comunicaciones de la forma más precisa nunca lograda. Además, puesto que el decodificador 230 expande cada elemento y columna de la matriz de comprobación de paridad antes de reducir la densidad de la matriz de comprobación de paridad, el coste de operación para la decodificación se puede reducir.

Además, en la forma de realización descrita anteriormente, el sistema de corrección de errores se usa para decodificar el código de Reed-Solomon. No obstante, el sistema de corrección de errores puede decodificar códigos BCH, por ejemplo, sin limitarse a la forma de realización descrita anteriormente.

La Fig. 26 es un diagrama de bloques que muestra la configuración de otro sistema ejemplificativo de corrección de errores que usa un código de Reed-Solomon según la presente invención. El sistema de corrección de errores mostrado en la Fig. 26 es un sistema usado para el sistema de comunicaciones digitales tal como, por ejemplo, la TV digital. Las partes iguales que las mostradas en la Fig. 25 se designan por medio de las mismas referencias numéricas y se omitirá su descripción.

En el sistema de corrección de errores mostrado en la Fig. 26, datos digitales codificados por el codificador 210 en el lado de transmisión se transmiten a un decodificador 240 en el lado de recepción a través de la vía de comunicaciones 221 tal como, por ejemplo, Internet.

El decodificador 240 incluye una unidad de comunicaciones 241 para recibir los datos digitales transmitidos a través de la vía de comunicaciones 221, en forma de una palabra de recepción, una unidad de decodificación convolucional 242 para ejecutar la decodificación convolucional para la palabra de recepción obtenida por la unidad de comunicaciones 241, un desentrelazador 243 para reordenar la palabra de recepción decodificada de forma convolucional, en el orden original, una unidad de decodificación de SPA y Reed-Solomon 244 para ejecutar una decodificación a través del algoritmo de suma producto para los datos digitales reinicializados al orden original, con el fin de reconstruir los datos digitales al estado previo en el que no se ha realizado todavía la codificación de Reed-Solomon, y un entrelazador 245 para reordenar los datos digitales, tal como el caso del entrelazador 212 del codificador 210.

Tal como se produce con la unidad de comunicaciones 231 mostrada en la Fig. 25, la unidad de comunicaciones 241 se comunica con la unidad de comunicaciones 214 del codificador 210 a través de la vía de comunicaciones 221 y obtiene los datos digitales transmitidos desde la unidad de comunicaciones 214, en forma de una palabra de recepción, sobre la base de un protocolo predeterminado. La unidad de comunicaciones 241 transmite la palabra de transmisión obtenida hacia la unidad de decodificación convolucional 242.

La unidad de decodificación convolucional 242 decodifica la palabra de recepción transmitida desde la unidad de transmisión 241 según un método que se corresponde con el método de codificación ejecutado por la unidad de codificación convolucional 213 del codificador 210. Es decir, la unidad de decodificación convolucional 242 ejecuta una decodificación de decisión flexible para la palabra de recepción usando el algoritmo de BCJR, el SOVA, y otros. A continuación, la unidad de decodificación convolucional 242 transmite la palabra de recepción decodificada por decisión flexible hacia el desentrelazador 243. Además, la palabra de recepción que se había sometido a una decodificación a través del algoritmo de suma producto se reordena nuevamente y se transmite desde el entrelazador 256 hacia la unidad de decodificación convolucional 242. La unidad de decodificación convolucional 242 ejecuta una decodificación de decisión flexible para la palabra de recepción usando el algoritmo de BCJR, el SOVA, y otros, tal como el caso de la palabra de recepción transmitida desde la unidad de comunicaciones 241, y transmite la palabra de recepción hacia el desentrelazador 243.

5

10

15

20

25

30

35

40

45

50

55

60

Tal como el caso del desentrelazador 233 mostrado en la Fig. 25, el desentrelazador 243 realiza un reordenamiento de los datos para la palabra de recepción transmitida desde la unidad de decodificación convolucional al 242 según un método que se corresponde con el entrelazado realizado por el entrelazador 212 del codificador 210, ejecuta un procesado para reinicializar los datos reordenados en el orden original (desentrelazado), y transmite la palabra de recepción reordenada en el orden original hacia la unidad de decodificación de SPA y Reed-Solomon 244. Además, tal como se ha descrito anteriormente, la palabra de recepción transmitida desde la unidad de decodificación convolucional 242 incluye una palabra de recepción transmitida desde el desentrelazador 245 a través de la unidad de decodificación convolucional 242 que es diferente a la palabra de recepción transmitida desde la unidad de comunicaciones 241 a través de la unidad de decodificación convolucional 242.

Básicamente, la unidad de decodificación de SPA y Reed-Solomon 244 está configurada y funciona tal como en el caso del decodificador 150 mostrado en la Fig. 20, igual que la unidad de decodificación de SPA y Reed-Solomon 244 mostrada en la Fig. 25. El diagrama de bloques mostrado en la Fig. 20 y el diagrama de flujo mostrado en la Fig. 21 se pueden usar para la unidad de decodificación de SPA y Reed-Solomon 244, tal como en el caso del decodificador 150.