OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

$\odot$  Número de publicación:  $2\ 357\ 307$

(51) Int. Cl.:

H01P 1/213 (2006.01)

| $\overline{}$ | ,                             |

|---------------|-------------------------------|

| 12)           |                               |

| 12)           | TRADUCCIÓN DE PATENTE EUROPEA |

| 1-/           |                               |

Т3

- 96 Número de solicitud europea: 07733104 .9

- 96 Fecha de presentación : **07.06.2007**

- 97 Número de publicación de la solicitud: 2030283 97 Fecha de publicación de la solicitud: 04.03.2009

- 54 Título: Multiplexor conmutado de banda ancha.

- (30) Prioridad: **09.06.2006 GB 0611445** 04.07.2006 GB 0613215

- 73 Titular/es: TELEDYNE DEFENCE LIMITED Airedale House Royal London Industrial Estate Acorn Park Charlestown Shipley, West Yorkshire BD17 7SW, GB

- Fecha de publicación de la mención BOPI: 25.04.2011

- (72) Inventor/es: Hardcastle, Peter, William

- 45) Fecha de la publicación del folleto de la patente: 25.04.2011

- (74) Agente: Carpintero López, Mario

ES 2 357 307 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

La presente invención se refiere a un multiplexor conmutado de banda ancha. De manera más particular, aunque no exclusiva, la presente invención se refiere a un multiplexor conmutado de banda ancha que tienen bandas de paso de entrada y salida entrelazadas, siendo al menos algunas de las bandas de paso de entrada suficientemente anchas para solapar las bandas de paso de salida en cualquier lado.

#### INTRODUCCIÓN

Los sistemas de guerra electrónica operan sobre espectros de frecuencia de múltiples octavas. En el campo de batalla moderno actual, el espectro de microondas se está volviendo cada vez más denso como resultado del aumento de fuentes de transmisores de microondas tanto en plataformas (problemas de equipos en una misma ubicación (cosite)), y dentro del entorno litoral. Esto puede provocar problemas significativos para que el sistema de banda ancha detecte satisfactoriamente las amenazas, particularmente en el caso de sistemas de alta probabilidad de intercepción (HPI). Se han desarrollado muchas soluciones para minimizar estos problemas, que van desde filtros conmutados sencillos, filtros de eliminación de banda / paso banda sintonizables, hasta limitadores, incluyendo la forma selectiva en frecuencia. Sin embargo, todas las soluciones limitan generalmente la eficacia operativa global del sistema de una manera u otra. La patente US-4 736 171 da a conocer un multiplexor conmutado de banda ancha.

El multiplexor conmutado según la invención trata de superar estos problemas. Es particularmente adecuado para su uso en aplicaciones de adelgazamiento de señal en entornos de señales densas que no pueden lograrse mediante los sistemas conocidos.

Por consiguiente, la presente invención proporciona un multiplexor conmutado de banda ancha que comprende un demultiplexor de banda ancha de entrada que comprende un puerto de entrada de banda ancha para recibir una señal de banda ancha de entrada y al menos un puerto de salida que tiene una banda de paso; un multiplexor de banda ancha de salida que comprende al menos dos puertos de entrada y un puerto de salida de banda ancha, teniendo cada puerto de entrada una banda de paso diferente, solapando cada banda de paso de puerto de entrada una parte diferente de la banda de paso de puerto de salida del demultiplexor; estando el puerto de salida del demultiplexor en comunicación eléctrica con los puertos de entrada del multiplexor mediante trayectos de señal, teniendo cada trayecto de señal un conmutador para abrir y cerrar el trayecto en el mismo.

Preferiblemente, el demultiplexor de banda ancha de entrada tiene una pluralidad de puertos de salida que tienen, cada uno, una banda de paso diferente; el multiplexor de banda ancha de salida tiene una pluralidad de puertos de entrada que tienen, cada uno, una banda de paso diferente; y, las bandas de paso se disponen de manera que cada una de las bandas de paso de puerto de entrada solapa al menos parcialmente una banda de paso de puerto de salida, solapando al menos algunas de las bandas de paso de puerto de entrada dos bandas de paso de puerto de salida.

Preferiblemente, los centros de las bandas de paso de puerto de entrada y las bandas de paso de puerto de salida están entrelazadas, siendo al menos algunas de las bandas de paso de puerto de entrada suficientemente anchas para solapar las bandas de paso de puerto de salida en cualquier lado.

Preferiblemente, al menos algunas de las bandas de paso de puerto de salida son suficientemente anchas para solapar las bandas de paso de puerto de entrada en cualquier lado.

Preferiblemente, las bandas de paso de puerto de entrada y de salida se solapan para formar una cadena de bandas de paso de puerto de entrada y de salida solapadas alternas.

Los centros de al menos una de las bandas de paso de puerto de entrada y las bandas de paso de puerto de salida pueden espaciarse de manera equidistante.

El demultiplexor puede tener n puertos de salida, estando dispuestas las bandas de paso de puerto de entrada y de salida de manera que haya o bien 2n o bien 2(n-2)+2 canales de tránsito de bandas de paso de puerto de entrada y de salida solapadas.

Los conmutadores en los trayectos de señal pueden ser no reflectores.

Al menos un trayecto de señal puede comprender un limitador de señal.

Preferiblemente, al menos uno del multiplexor o el demultiplexor es un multiplexor/demultiplexor de banda ancha en cascada Hi/Lo.

Al menos una línea de señal puede incluir un atenuador.

Preferiblemente, el multiplexor conmutado de banda ancha comprende además al menos un divisor de potencia colocado en un trayecto de señal para dividir una señal recibida desde el puerto de salida correspondiente en al menos dos partes, recibiéndose al menos una de las partes por un puerto de entrada que tiene una banda de paso que solapa la del puerto de salida.

2

10

5

15

20

25

30

35

40

45

Preferiblemente, el multiplexor conmutado de banda ancha comprende una pluralidad de divisores de potencia, estando adaptado cada divisor de potencia para dividir una señal procedente de un puerto de salida asociado en al menos dos partes, recibiéndose al menos una parte de cada señal por al menos un puerto de entrada.

Preferiblemente, el multiplexor conmutado de banda ancha comprende además medios de medición de frecuencia, los medios de medición de frecuencia, estando adaptados los medios de medición de frecuencia para recibir partes de señal desde una pluralidad de divisores de potencia.

El multiplexor conmutado de banda ancha puede comprender además medios de conmutación entre los divisores de potencia y los medios de medición de frecuencia, estando adaptados los medios de conmutación para conectar los medios de medición de frecuencia a diferentes divisores de potencia.

Preferiblemente, al menos un divisor de potencia divide la señal procedente de un puerto de salida en dos partes, recibiéndose las dos partes por dos puertos de entrada, teniendo los puertos de entrada bandas de paso que solapan la del puerto de salida conectado al divisor de potencia.

Preferiblemente, el multiplexor conmutado de banda ancha comprende además al menos un combinador de potencia para combinar señales procedentes de al menos dos puertos de salida y proporcionar la señal combinada a un puerto de entrada, solapando la banda de paso del puerto de entrada las bandas de paso de los puertos de salida.

El al menos un combinador de potencia puede estar adaptado para combinar señales divididas procedentes de dos divisores de potencia diferentes y proporcionar la señal combinada a un puerto de entrada.

Una pluralidad de trayectos de señal de puertos de salida asociados pueden comprender medios de medición de amplitud, preferiblemente DLVA.

Los medios de medición de amplitud pueden ser medios de medición de amplitud de banda estrecha con respecto al demultiplexor de banda ancha.

Cada medio de medición de amplitud puede estar adaptado para abrir o cerrar su trayecto de señal asociado entre puertos de salida y entrada dependiendo de la señal medida por los medios de medición de amplitud.

Preferiblemente, el multiplexor conmutado de banda ancha comprende además medios de medición de frecuencia conectados al puerto de banda ancha de salida del multiplexor de banda ancha de salida.

Los medios de medición de frecuencia pueden ser medios de medición de frecuencia de banda estrecha con respecto al multiplexor de banda ancha.

El multiplexor conmutado de banda ancha puede comprender además un convertidor reductor de frecuencia entre el multiplexor de banda ancha y los medios de medición de frecuencia, estando adaptado el convertidor reductor de frecuencia para desfasar la frecuencia de la señal recibida desde el puerto de salida de banda ancha del multiplexor en un factor que depende de qué trayecto de señal entre el demultiplexor de entrada y el multiplexor de salida esté abierto.

El multiplexor conmutado de banda ancha puede comprender un receptor superheterodino conectado al puerto de banda ancha de salida del multiplexor de banda ancha de salida.

Preferiblemente, el multiplexor conmutado de banda ancha comprende además al menos un multiplexor de banda ancha de salida adicional, teniendo el multiplexor de banda ancha de salida una pluralidad de puertos de entrada y un puerto de salida de banda ancha, teniendo al menos algunos de los divisores de potencia una salida conectada a un puerto de entrada del multiplexor de banda ancha de salida adicional.

El puerto de banda ancha de salida de un multiplexor de banda ancha de salida puede conectarse a medios de medición de frecuencia y el puerto de banda ancha de salida del multiplexor de banda ancha adicional puede conectarse a un receptor superheterodino.

A continuación se describirá la presente invención a modo de ejemplo únicamente, y no en un sentido limitativo, con referencia a los dibujos adjuntos en los que

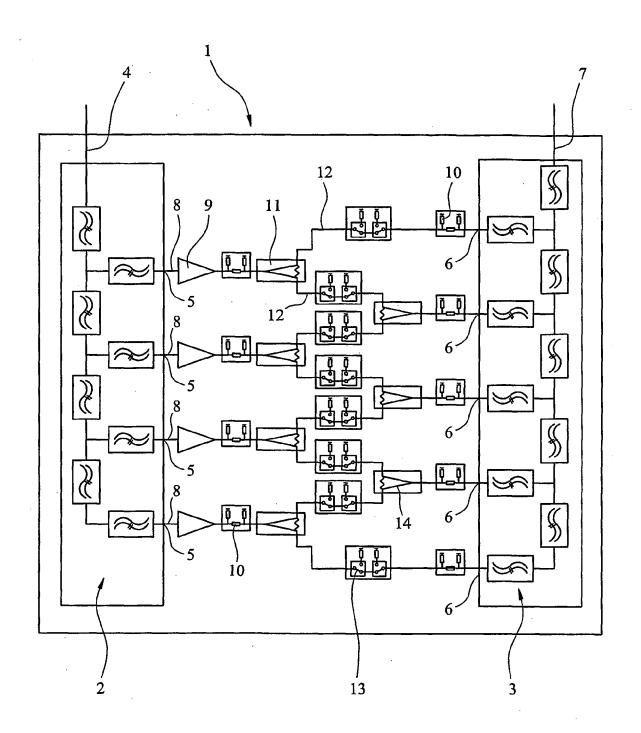

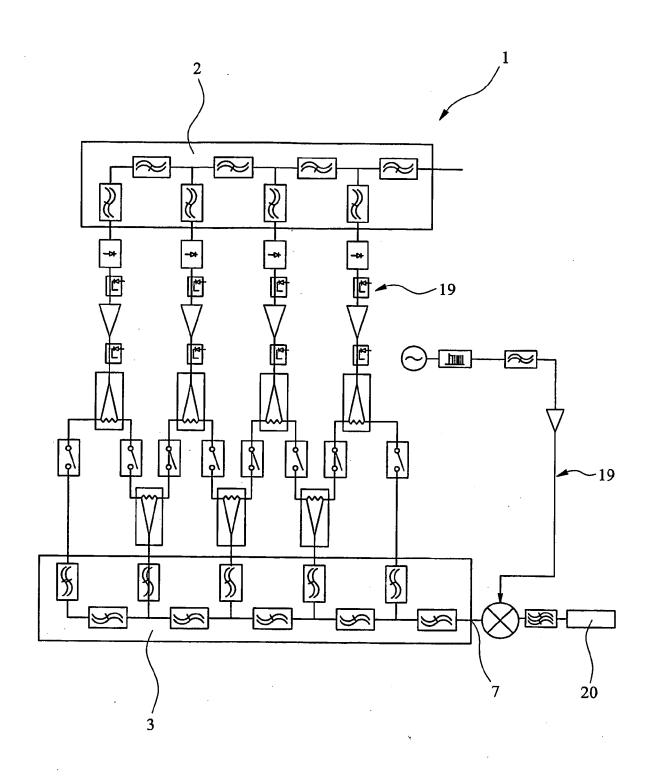

la figura 1 muestra en forma esquemática el multiplexor según la invención;

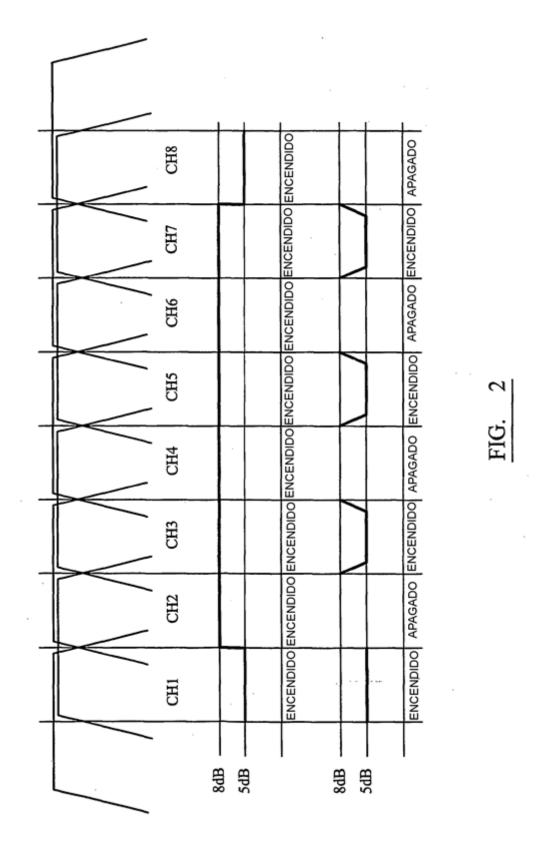

la figura 2 muestra en forma esquemática las bandas de paso de los puertos de entrada y salida;

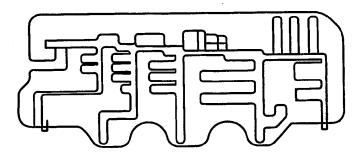

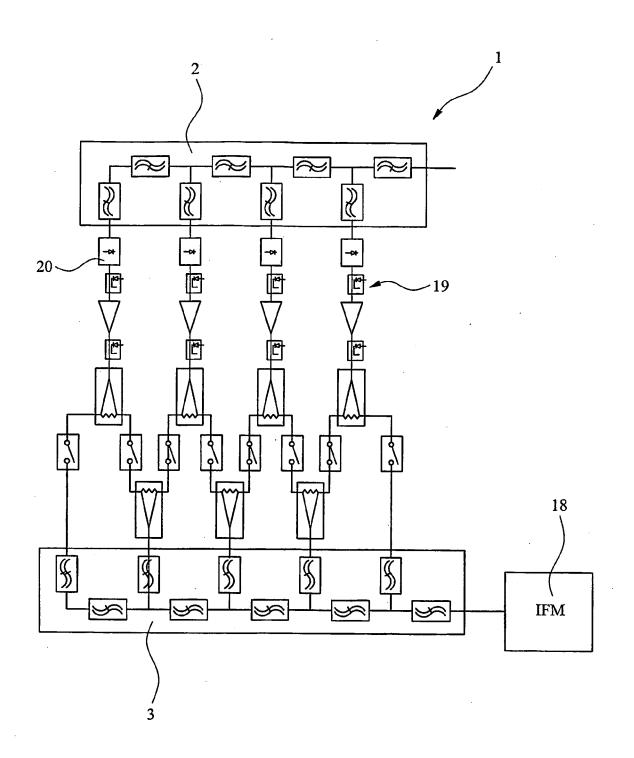

la figura 3 muestra el diseño del multiplexor o demultiplexor del multiplexor conmutado según la invención;

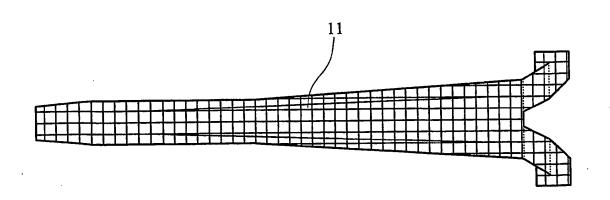

la figura 4 muestra un divisor de potencia usado en el multiplexor conmutado según la invención;

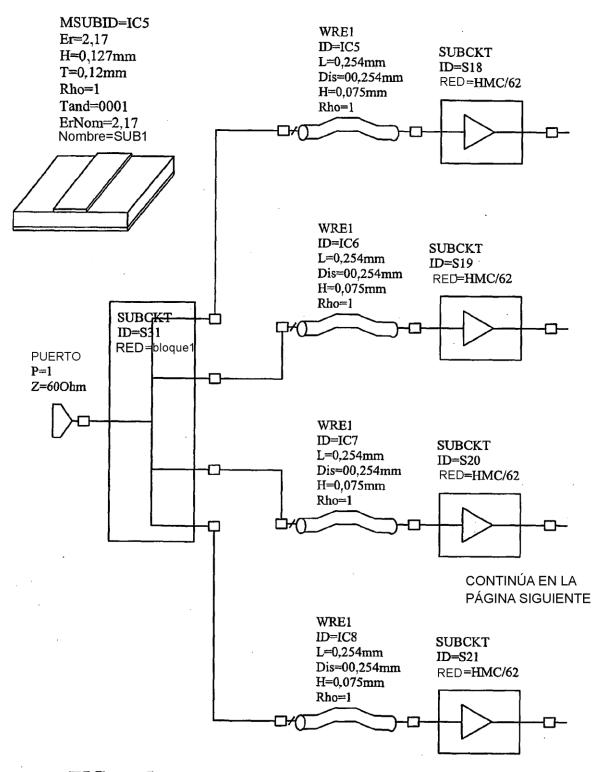

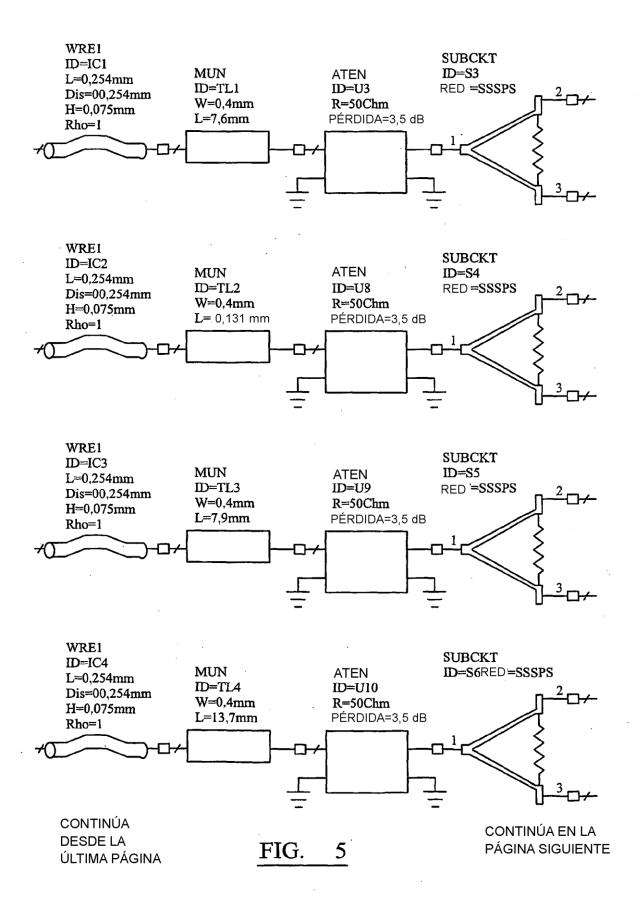

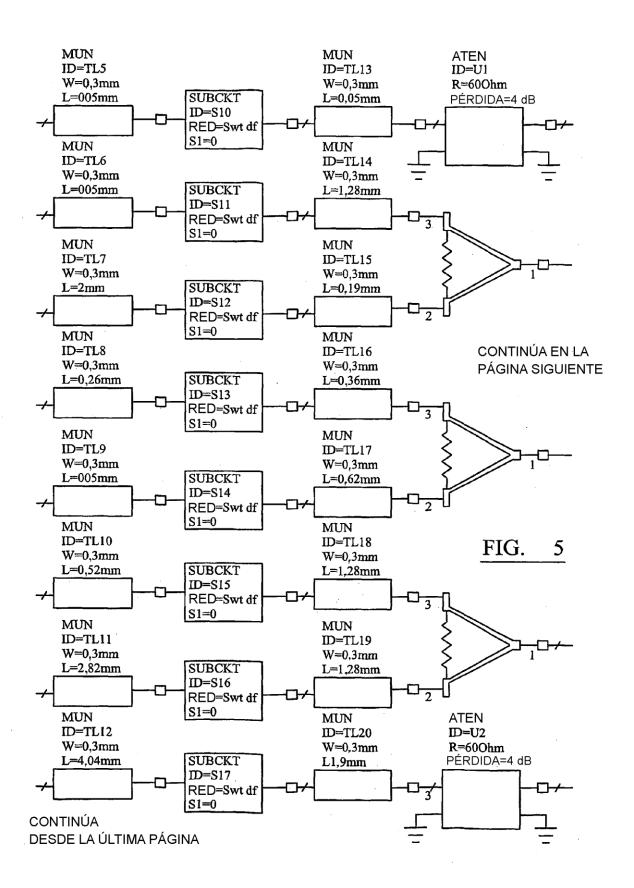

la figura 5 muestra un modelo de sistema de trabajo completo del multiplexor conmutado según la invención;

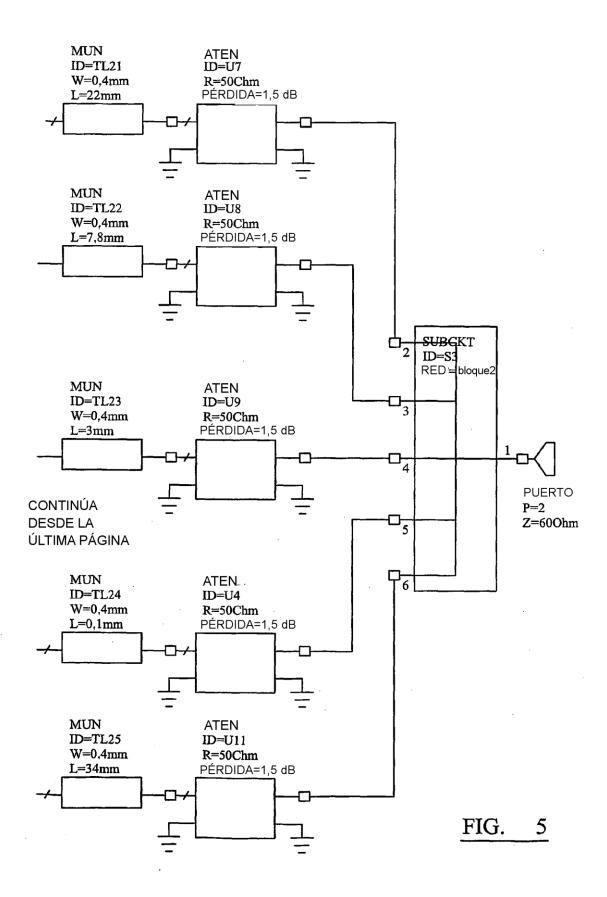

la figura 6 muestra el rendimiento del modelo simulado;

15

10

5

20

25

30

35

40

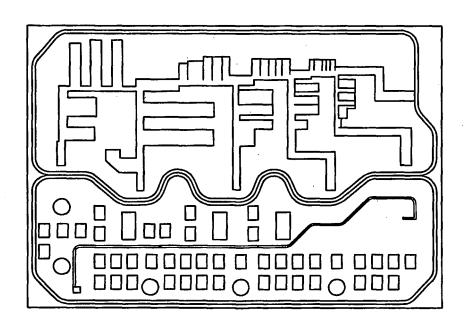

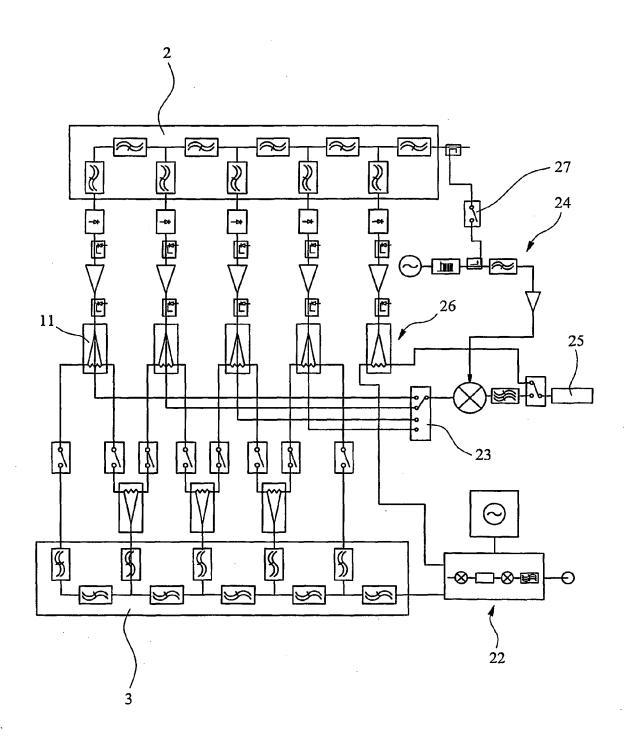

las figuras 7 y 8 muestran un multiplexor conmutado según la invención;

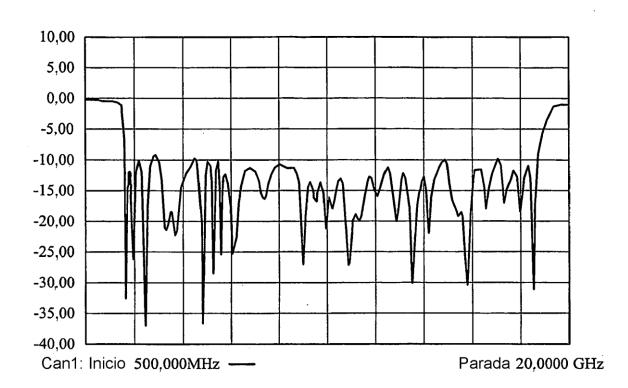

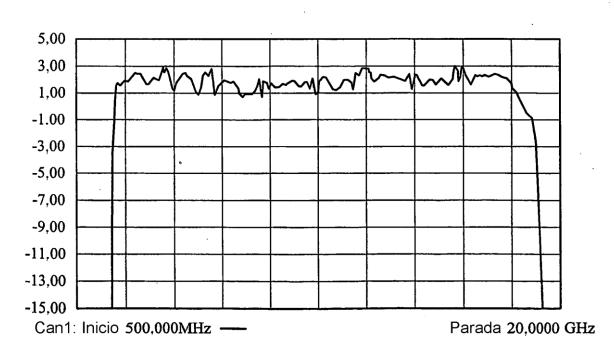

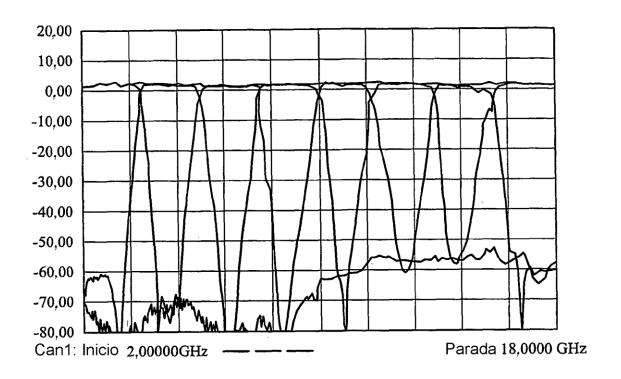

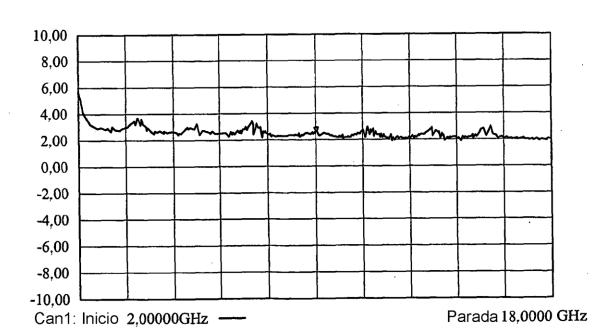

las figuras 9 a 12 muestran el rendimiento del multiplexor conmutado de las figuras 7 y 8;

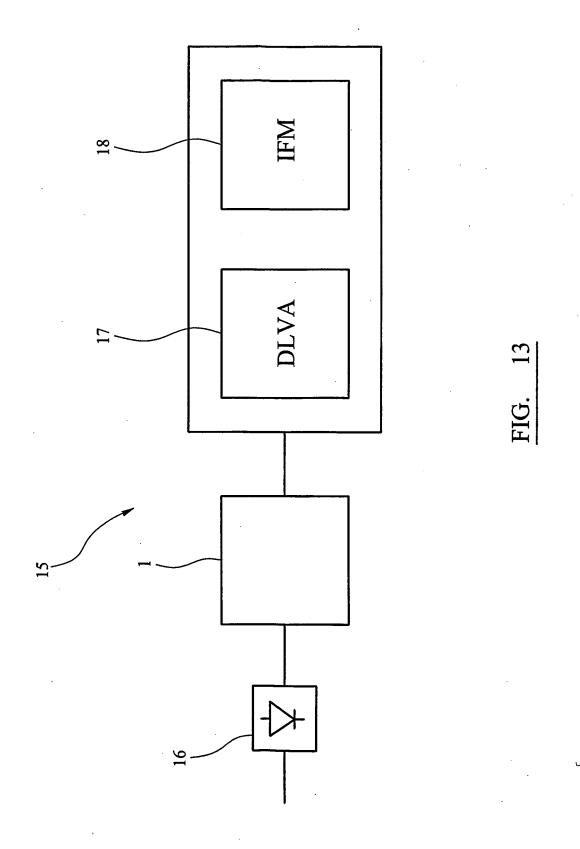

la figura 13 muestra un receptor que incluye el multiplexor conmutado de banda ancha según la invención;

la figura 14 muestra una realización adicional de un multiplexor conmutado de banda ancha según la invención;

la figura 15 muestra una realización adicional de un multiplexor conmutado de banda ancha según la invención;

la figura 16 muestra una realización adicional de un multiplexor conmutado de banda ancha según la invención;

У

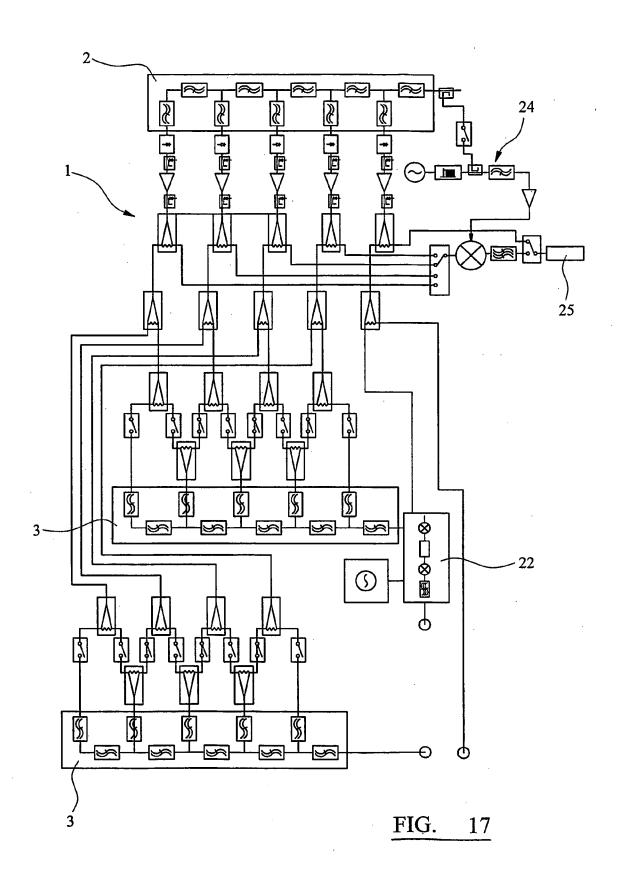

la figura 17 muestra una realización adicional de un multiplexor conmutado de banda ancha según la invención.

10

5

Artículos previos han descrito una metodología para obtener un rendimiento de multiplexor conmutado verdaderamente de banda estrecha usando prototipos paso banda únicos con características de fase optimizadas para permitir la recombinación global de señales. La multiplexación se realiza generalmente usando bancos pares e impares no contiguos para simplificar la alineación. La incapacidad de estas estructuras para mantener características con respecto a anchos de banda amplios da como resultado la necesidad de considerar un planteamiento de filtrado paso bajo / paso alto.

15

Se muestra en la figura 1 en forma esquemática un multiplexor 1 conmutado de banda ancha según la invención que comprende un demultiplexor 2 en cascada banda baja / banda alta de banda ancha de entrada y un multiplexor 3 banda baja / banda alta de banda ancha de salida. El demultiplexor 2 de banda ancha de entrada tiene un puerto 4 de banda ancha de entrada para recibir una señal de banda ancha de entrada y una pluralidad de puertos 5 de salida. Cada puerto 5 de salida tiene una función de banda de paso de salida diferente en función de la frecuencia. De manera similar, el multiplexor 3 comprende una pluralidad de puertos 6 de entrada que tienen una banda de paso diferente y un puerto 7 de banda ancha de salida.

20

25

Hay un trayecto 8 de señal que se extiende desde cada puerto de salida. En cada trayecto 8 de señal hay un amplificador 9 para capturar el factor de ruido (NF) pronto en la estructura. A continuación en la línea hay un atenuador para ajustar la magnitud de la señal. Tras el atenuador 10, un divisor 11 de potencia divide la señal en dos trayectos 12 separados. Conmutadores 13 no reflectores en los trayectos 12 separados conectan/desconectan estos trayectos 12 de señal separados respecto a la segunda mitad del multiplexor conmutado, según se muestra. La segunda mitad del multiplexor conmutado es simétrica con respecto a la primera (excepto por los amplificadores 9). Un combinador 14 de potencia (divisores de potencia conectados de modo inverso) en la segunda mitad del circuito combina las señales separadas en trayectos de señal hacia los puertos 6 de entrada del multiplexor 3.

30

En la figura 2, se muestra en forma esquemática el funcionamiento del multiplexor 1 conmutado según la invención. La línea superior de la figura muestra las bandas de paso de los puertos 5, 6 de entrada y salida. Los centros de las bandas de paso de los puertos 5, 6 de entrada y salida están entrelazados y espaciados de manera equidistante. Las bandas de paso son suficientemente anchas de modo que las bandas de paso de entrada y salida se solapan según se muestra.

35

Cuando todos los conmutadores 13 están cerrados, el multiplexor 1 conmutado tiene una banda de paso ancha compuesta por una pluralidad de canales de tránsito en los que las bandas de paso de entrada y salida se solapan. Al abrir uno o más de los conmutadores 13, puede eliminarse uno o más de los canales de tránsito alterando así la banda de paso del multiplexor 1 conmutado. En esta realización, los canales de tránsito están formados por las semibandas combinadas de los puertos 5, 6 de entrada y salida del multiplexor / demultiplexor 2, 3, según se muestra. También son posibles otras disposiciones.

40

Recombinación.

El uso de filtros LP/HP de alta selectividad en el multiplexor / demultiplexor 2, 3 de banda ancha da como resultado de forma inherente que la región de cruce presente una rápida tasa de cambio de fase con la frecuencia. Si se considera el prototipo Chebychev convencional;

Fcheb=senl

$$\left(\frac{1}{\text{Grado}} \cdot \text{asenl}\left(\frac{1}{\frac{Lr}{10^{10}-1}}\right)\right)$$

Frespuestan) = c.

$$\prod_{m=1}^{2} \left[ -\omega^{2} + \left[ 2 \operatorname{Fcheb} \left( \cos \left( \pi \frac{2 \cdot m - 1}{2 \cdot \operatorname{Grado}} \right) \right) \right] \cdot j\omega + \operatorname{Fcheb}^{2} + \left[ \operatorname{sen} \left[ \frac{\pi}{2 \cdot \operatorname{Grado}} \cdot (2 \cdot m - 1) \right] \right]^{2} \right]$$

La pérdida de cruce debe ser de 6 dB (debido a que los divisores de potencia disipan la mitad de la potencia cuando están en banda) y cada trayecto debe estar en fase para la recombinación. La ec. 3 describe la recombinación de cruce;

S21(

$$\omega$$

) = Frespuesta  $\left(\frac{\omega}{\omega l p}\right) \cdot \lambda(\theta)$  + Frespuesta  $\left(\frac{-\omega h p}{\omega}\right)$

Frespuesta

$$\left(\frac{\omega_{x\_over}}{\omega lp}\right)$$

= Frespuesta  $\left(\frac{-\omega hp}{\omega_{x\_over}}\right)$  = 0,5

Donde  $\lambda(\theta)$  es un vector unitario de fase arbitraria. Puede demostrarse que esta arquitectura es relativamente tolerante a errores de fase, con distorsiones mínimas respecto al prototipo y la pérdida de cruce, pueden albergarse errores de fase de cierta magnitud, y lograrse una recombinación excepcional.

# 10 Factor de ruido y retardo de grupo

5

15

En este sistema, las señales se someten a trayectos paralelos; en la banda media hay dos fuentes de ruido de combinación, y un único trayecto de señal, del que el elemento de división absorbe la mitad de su potencia. En el cruce, existen también dos fuentes de ruido, pero dos trayectos de señal de combinación de potencia igual pero de un cuarto (con respecto a la señal en banda), por tanto, el NF sigue siendo relativamente uniforme a través de la banda (véanse la figura 2b, figura 2c). El NF se aproxima por tanto mediante;

# Banda media (5)

Mux1NF, Mux1pérdida son de banda media en ambos casos.

El GD también se somete a trayectos paralelos en la recombinación, por tanto, puede estimarse el GD máximo simplemente calculando el diferencial de fase en el punto de cruce de 6 dB.

# 5 Ecualización de amplitud

Como con la mayoría de los sistemas de banda ancha, la pérdida pasiva, y las funciones de transferencia de componentes requieren un grado de ecualización de amplitud. Debido al nivel de canalización, pueden aplicarse atenuadores 10 fijos para la ecualización basta a través de la banda completa. Es ventajoso añadir estos atenuadores 10 al puerto común de todos los divisores 11 de potencia. Aunque esto da como resultado que cada atenuador 10 cubre dos bandas simultáneamente, casi cualquier respuesta de ecualizador es posible. También es ventajoso desviar la atenuación hacia el multiplexor 3 de salida ya que es inherentemente reflector dentro de su banda adyacente, lo que puede aumentar la ondulación recombinada si no coinciden lo suficiente.

## DISEÑO

10

15

20

25

30

35

### Multiplexores

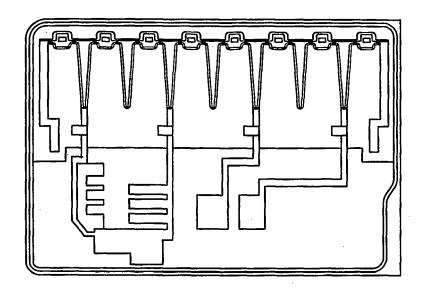

Los diseños de filtro LP/HP de los multiplexores/demultiplexores 2, 3 del multiplexor 1 conmutado según la invención se basan en la forma generalizada del prototipo Chebychev, ligeramente modificado para un rendimiento de pérdida de retorno en cascada mejorado. Estos se sintetizan directamente como redes de línea de cinta de sustrato suspendido (SSS), usando software propietario de Filtronic. Se realizó un análisis, y una configuración inicial, usando AWR Microwave con una biblioteca de modelos propietaria dedicada para las estructuras SSS, según se muestra en la figura 3.

# Divisores de potencia.

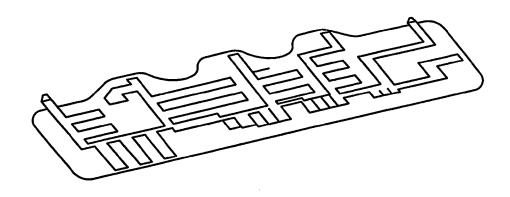

El diseño del divisor 11 de potencia usado en la invención también se realiza en tecnología SSS como una estructura de línea de sección decreciente con una capa de tinta resistiva. Para compactar el tamaño, se usa una estructura de diente de sierra para aumentar la velocidad de fase de modo impar, a expensas tan sólo del aislamiento y la coincidencia. Intuitivamente, se sabe que  $\lambda$ =F(Vpe,Vpo), por tanto, la reducción de tamaño es factible. El diseño final se modeló usando un simulador EM. Se fabricó un prototipo inicial de este componente, ya que este elemento se incorporaría eventualmente en la configuración final. La figura 4 ilustra el diseño. A través de 2-180 Hz, tanto RL como el aislamiento medían 12 dB en el peor caso, con una longitud de cuarto de onda equivalente a 4 GHz.

## **MMIC**

Los conmutadores 13 MMIC son conmutadores no reflectores de FET, DC-20 GHz, de Filtronic Compound Semiconductors. Los amplificadores usados son MMIC de 2-18 GHz, HMC462 de Hittite. Ambos se montan según un planteamiento de "chip-in-duroid".

Modelo de sistema de trabajo completo.

#### **RESULTADOS SIMULADOS FINALES**

El modelo eléctrico se actualiza teniendo en cuenta el diseño mecánico realizable, incluyendo análisis EM incorporado para todas las transiciones de microondas, y las longitudes eléctricas finales añadidas. Finalmente, los multiplexores 2, 3 se vuelven a optimizar para la recombinación. La figura 6 muestra el rendimiento simulado del modelo

realizable final; la representación gráfica ilustra la respuesta recombinada prevista con todos los canales seleccionados.

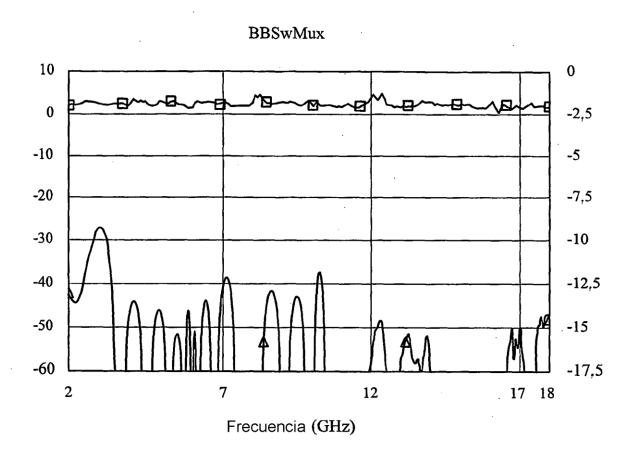

#### REALIZACIÓN MECÁNICA

Para hacer un uso óptimo del espacio, se adopta un planteamiento mecánico de doble lado. La línea de pliegue en el modelo eléctrico se toma a partir de los conmutadores 13 MMIC; los divisores 11 de salida se intercalan en el mismo plano de microondas. Transiciones de RF verticales pasan señales al lado inferior del alojamiento en el que se monta el multiplexor 3 de salida directamente por debajo del multiplexor 2 de entrada. Esto permite que la PCB de acondicionamiento de suministro y control se sitúe por debajo de la red de divisores y el conjunto de MMIC para mayor facilidad de distribución de las señales de control sin afectar adversamente a la configuración de microondas. Las figuras 7 y 8 muestran los dos lados del conjunto final.

#### RENDIMIENTO MEDIDO

5

10

15

20

25

30

35

40

45

50

55

Las figuras 9 a 12 son representaciones gráficas tomadas usando un analizador vectorial de PNA de Agilent.

En resumen, la ganancia de pequeña señal (SSG) lograda es de manera nominal de 2 dB con una variación típica de +/-1 dB. La VSWR de entrada es de 2:1 en el peor caso con una coincidencia de salida de 2,5:1 (no mostrado). Se logran más de 50 dB de rechazo en centros de bandas adyacentes y más alejadas. El retardo de grupo es de 4 ns como máximo, con una variación nominal de +/- 1 ns a través del ancho de banda completo (nota: el GD de banda de paso y la VSWR de entrada/salida permanecen inalterados cuando se deseleccionan las bandas).

#### MAYORES NIVELES DE INTEGRACIÓN Y ABSORCIÓN DEL SISTEMA

El diseño proporciona un sistema de banda ancha con un preselector de extremo frontal versátil con excelentes características de respuesta de todos los parámetros eléctricos clave. Sin embargo, la mayoría de los sistemas de EW requieren generalmente no sólo un funcionamiento de banda amplia para HPI, sino que también realizan canalización en una etapa temprana, para mejorar el rango dinámico a través del ruido, y la supresión espúrea para el procesamiento detallado. La invención realiza canalización inherentemente en toda la arquitectura antes de la recombinación. Si se sustituyen los divisores 11 de potencia de entrada por verdaderas estructuras de línea de sección decreciente de 3 vías utilizando la tecnología SSS, pueden pasarse estos canales fuera para el procesamiento de banda estrecha con NF excepcionalmente bajo, para el procesamiento o bien conmutado, o bien paralelo. Además, podrían añadirse limitadores de PIN antes de los amplificadores para una protección de alta potencia (los multiplexores de entrada son estructuras pasivas de "Q" alta que pueden manejar potencia relativamente alta), esto daría como resultado una interferencia de alta potencia que limita sólo la banda en la que aparecen, proporcionando así el efecto de una limitación selectiva en frecuencia basta.

El multiplexor 1 conmutado de banda ancha según la invención permite que se use una única alimentación de antena para múltiples aplicaciones. Además, puede mejorarse la arquitectura, ampliando el número de bandas de 8 a 16, para aumentar la resolución de preselección. Añadir un canal de 0,5-2 GHz también podría considerarse valioso para algunos sistemas, con un aumento pequeño en la complejidad.

En la realización de la invención mostrada anteriormente, cada banda de paso de puerto de entrada se solapa con dos bandas de paso de puerto de salida y viceversa. Son posibles otras disposiciones, por ejemplo una única banda de paso de puerto de salida podría solapar tres o más bandas de paso de puerto de entrada o viceversa.

Además, es posible espaciar las bandas de paso de puerto de entrada y salida de distinta manera al espaciado equidistante.

Son posibles otros esquemas de entrelazamiento para las bandas de paso de puerto de entrada y salida. Por ejemplo, podría haber una pluralidad de bandas de paso de puerto de salida entre bandas de paso de puerto de entrada adyacentes o viceversa.

En la figura 13 se muestra un receptor 15 que incorpora un multiplexor 1 conmutado de banda ancha según la invención. Se requiere un simple limitador 16 en el extremo frontal para proteger el sistema frente a una recepción de alta potencia (normalmente desde transmisores de a bordo). El multiplexor 1 conmutado de banda ancha según la invención permite la canalización, el funcionamiento completamente abierto o la capacidad para eliminar mediante filtro de muesca cualquier señal caracterizada. El DLVA/IFM 17, 18 permite el análisis de esquema de modulación sencilla, frecuencia y amplitud. Esta arquitectura ofrece en esencia un rendimiento mejorado con respecto a los esquemas conocidos en el sentido de que ofrece la capacidad para detectar más de una señal simultánea por medio de eliminación mediante filtro de muesca de la señal de mayor potencia presentada (con la condición de que la señal secundaria no esté dentro de la misma banda). Esta solución también elimina la necesidad de encaminar señales de vídeo y RF a través de la plataforma de instalación, es decir la salida puede ser una palabra digital de descriptor de impulso completo, encaminada como datos en serie de alta velocidad como USB, Firewire o Ethernet de alta velocidad.

Sin embargo, todavía existen limitaciones, en primer lugar, el sistema sigue siendo ciego cuando se activa el limitador 16. En segundo lugar, múltiples señales a niveles de potencia similares dentro de la misma banda darán lugar a resultados erróneos. Más dañino es el efecto de la sensibilidad del sistema. Para sistemas conocidos, el factor de

ruido de extremo frontal antes de la medición de vídeo está definido por el NF del sistema hasta el DLVA 17, entonces se mejora la sensibilidad del sistema mediante la canalización, que limita el ruido de banda ancha presentado al DLVA. Un NF típico es del orden de 7 dB, con una ganancia en banda típica de 10 dB antes del DLVA 17, con un BW de ruido de 4 GHz. Para una comparación similar con el receptor para la figura 13, debe considerarse el NF hasta el DLVA/IFM 17, 18. La figura 2 ilustra el rendimiento de NF del multiplexor 1 conmutado de banda ancha según la invención. El aumento de ruido en la región de banda central en pasa todo se debe a la contribución de ruido de banda ancha de amplificadores de canales adyacentes (NOTA: la banda 1 y la banda 8 tienen contribución sólo de un amplificador). Cuando se desconectan canales adyacentes, mejora el NF, sin embargo, la región de cruce da como resultado una disminución del nivel de señal en la salida, y por tanto, un NF degradado, sin embargo, esto sigue siendo similar a los receptores actuales.

5

10

15

20

25

30

35

40

45

50

55

60

Cuando el sistema está operando en modo pasa todo (BW de ruido de 16 GHz), la sensibilidad del sistema se degrada significativamente en la medición de amplitud y el rango dinámico del IFM, es decir, habría que desconectar la mayoría de los canales para lograr la misma sensibilidad que con los receptores actuales, perdiendo así todas las ventajas del multiplexor 1 conmutado de banda ancha según la invención. En sistemas de EW, la sensibilidad es posiblemente el parámetro del sistema más significativo. Esta cuestión por sí sola hace que el multiplexor 1 conmutado de banda ancha según la invención sea esencialmente inadecuado como bloque estructural de extremo frontal.

En la figura 14 se muestra una realización adicional de un multiplexor 1 conmutado de banda ancha según la invención. En esta realización, se incluyen medios 19 de medición de amplitud que comprenden DLVA en los trayectos de señal, según se muestra. Esto mejora la sensibilidad en comparación con el sistema original ya que el NF en este punto de medición es excepcionalmente bajo, además, dado que la fase 2 de entrada es puramente pasiva, y puede manejar alta potencia, puede moverse el limitador 16 desde el extremo frontal al limitador 20 dentro de los trayectos de señal, según se muestra.

Esta arquitectura elimina la mayor parte de las limitaciones analizadas previamente. El NF hasta el DLVA 19 es inferior a 3 dB, y la potencia de ruido generada por el DLVA 19 también está limitada en banda. Utilizando estos DLVA 10 como discriminadores por capas basto permite que se desconecten los demás canales, dando como resultado una menor potencia de ruido aplicada al IFM 18 (SNR mejorada). Además, cualquier señal de alta potencia sólo afectará a la banda en la que se encuentre dejando el resto del espectro de frecuencia totalmente funcional. Puede ser posible usar una conmutación analógica para dirigir las salidas de un diodo detector de alta potencia a un único amplificador logarítmico de vídeo para la medición de amplitud exacta, reduciendo además el coste. Si es posible, estos conmutadores analógicos pueden usarse para interrumpir el vídeo antes de que los circuitos de restauración de línea base midan la amplitud de CW; esto elimina la necesidad de introducir conmutadores de RF en las entradas de DLVA, según se usa en el sistema actual.

La realización de la figura 14 utiliza un único IFM 18 debido al coste de la unidad. En la figura 15 se muestra una realización adicional de un multiplexor 1 conmutado de banda ancha según la invención. Esta realización comprende un IFM 20 de banda baja (LBIFM) conectado al puerto 7 de banda ancha de salida del multiplexor 3 de banda ancha de salida a través de un convertidor 21 reductor de frecuencia. Los medios 19 de medición de amplitud de esta realización actúan como disparadores umbral que abren o cierran sus trayectos 8 de señal asociados en respuesta a la señal recibida. El convertidor 21 reductor de frecuencia reduce la señal procedente del puerto 7 de banda ancha de salida en un factor que depende de qué trayectos 8 de señal estén abiertos. De esta manera, la señal proporcionada al LBIFM 20 siempre está en un intervalo de frecuencia aceptable para el LBIFM 20 incluso aunque el intervalo de frecuencias aceptable para el LBIFM 20 sea más estrecho que el proporcionado por el multiplexor 3 de salida de banda ancha.

En la figura 16 se muestra una realización adicional de esta invención. En esta realización, un receptor 22 superheterodino está conectado al puerto 7 de salida de banda ancha del multiplexor 3 de salida. Un puerto de salida de cada uno de la pluralidad de divisores 11 de potencia está conectado a medios 23 de conmutación que tienen una pluralidad de puertos de entrada para las salidas de los divisores de potencia y, un puerto de salida. La salida de los medios 23 de conmutación está conectada a un convertidor 24 reductor de frecuencia que está conectado a su vez a un LBIFM 25. El conmutador 23 está adaptado para conmutar entre las salidas de diferentes divisores 11 de potencia dependiendo de la señal recibida. El convertidor 24 reductor garantiza que la frecuencia recibida por el LBIFM 25 está dentro de un intervalo adecuado según se describió previamente.

Características adicionales añadidas al presente documento incluyen una canalización 26 de extremo frontal de 0,5 a 2 GHz, que tiene su propia detección de actividad y monitorización de amplitud, pero que se encamina directamente al LBIFM 25 y también se encamina independientemente al receptor 22 superheterodino de salida (puesto que la mayoría de los diseños de receptor superheterodino requieren que el segmento de banda baja emprenda esquemas de mezclado alternativos para un mínimo rendimiento espúreo).

También se añade un acoplador 27 débil a la entrada principal que desacopla la potencia procedente del generador combinado para su uso para la funcionalidad BIT de extremo a extremo con un coste y una complejidad bajos. Si se usa un acoplamiento lo suficientemente débil, la alta potencia no supondrá una amenaza en términos de supervivencia. Esta arquitectura ofrece actividad de detección completamente independiente, operación de NBRx y WBRx, es decir, pueden notificarse de manera continua frecuencias usando el LBIFM de varias bandas diferentes, al

tiempo que mantiene enganchado y sujeto a cualquier canal de RF mientras se monitoriza simultáneamente la detección de actividad.

En la figura 17 se muestra un ejemplo adicional de un multiplexor 1 conmutado de banda ancha según la invención. Esta realización comprende un multiplexor 3 de banda ancha de salida adicional que puede usarse para añadir funcionalidad adicional.

#### REIVINDICACIONES

Un multiplexor conmutado de banda ancha que comprende

5

10

15

un demultiplexor (2) de banda ancha de entrada que comprende un puerto (4) de entrada de banda ancha para recibir una señal de banda ancha de entrada y al menos un puerto (5) de salida que tiene una banda de paso;

un multiplexor (3) de banda ancha de salida que comprende al menos dos puertos (6) de entrada y un puerto (7) de salida de banda ancha, teniendo cada puerto de entrada una banda de paso diferente, solapando cada banda de paso de puerto de entrada una parte diferente de la banda de paso de puerto de salida del demultiplexor;

estando el puerto de salida del demultiplexor en comunicación eléctrica con los puertos de entrada del multiplexor mediante trayectos de señal, teniendo cada trayecto de señal un conmutador para abrir y cerrar el trayecto en el mismo.

2. Un multiplexor conmutado de banda ancha según la reivindicación 1,

teniendo el demultiplexor de banda ancha de entrada una pluralidad de puertos de salida que tienen, cada uno, una banda de paso diferente;

teniendo el multiplexor de banda ancha de salida una pluralidad de puertos de entrada que tienen, cada uno, una banda de paso diferente;

estando dispuestas las bandas de paso de manera que cada una de las bandas de paso de puerto de entrada solapa al menos parcialmente al menos una banda de paso de puerto de salida, solapando al menos algunas de las bandas de paso de puerto de entrada dos bandas de paso de puerto de salida.

- 20 3. Un multiplexor conmutado de banda ancha según la reivindicación 2, en el que los centros de las bandas de paso de puerto de entrada y las bandas de paso de puerto de salida están intercalados, siendo al menos algunas de las bandas de paso de puerto de entrada suficientemente anchas para solapar las bandas de paso de puerto de salida en cualquier lado.

- 4. Un multiplexor conmutado de banda ancha según cualquiera de las reivindicaciones 2 ó 3, en el que al menos algunas de las bandas de paso de puerto de salida son suficientemente anchas para solapar las bandas de paso de puerto de entrada en cualquier lado.

- 5. Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 2 a 4, en el que las bandas de paso de puerto de entrada y de salida se solapan para formar una cadena de bandas de paso de puerto de entrada y de salida solapadas alternas.

- 30 6. Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 2 a 5, en el que el demultiplexor tiene n puertos de salida, estando dispuestas las bandas de paso de puerto de salida de manera que haya o bien 2n o bien 2(n-2)+2 canales de tránsito de bandas de paso de puerto de entrada y de salida solapadas.

- 7. Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 1 a 6, que comprende además al menos un divisor de potencia colocado en un trayecto de señal para dividir una señal recibida desde el puerto de salida correspondiente en al menos dos partes, recibiéndose al menos una de las partes por un puerto de entrada que tiene una banda de paso que solapa la del puerto de salida.

- 8. Un multiplexor conmutado de banda ancha según la reivindicación 7, que comprende una pluralidad de divisores de potencia, estando adaptado cada divisor de potencia para dividir una señal procedente de un puerto de salida asociado en al menos dos partes, recibiéndose al menos una parte de cada señal por al menos un puerto de entrada.

- 9. Un multiplexor conmutado de banda ancha según la reivindicación 8, que comprende además medios de medición de frecuencia, estando adaptados los medios de medición de frecuencia para recibir partes de señal desde una pluralidad de divisores de potencia.

- Un multiplexor conmutado de banda ancha según la reivindicación 9, que comprende además medios de conmutación entre los divisores de potencia y los medios de medición de frecuencia, estando adaptados los medios de conmutación para conectar los medios de medición de frecuencia a diferentes divisores de potencia.

- Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 7 a 10, en el que al menos un divisor de potencia divide la señal procedente de un puerto de salida en dos partes, recibiéndose las dos partes por dos puertos de entrada, teniendo los puertos de entrada bandas de paso que solapan la del puerto de salida conectado al divisor de potencia.

- 12. Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 2 a 11, que comprende además al menos un combinador de potencia para combinar señales procedentes de al menos dos puertos de salida y proporcionar la señal combinada a un puerto de entrada, solapando la banda de paso del puerto de entrada las bandas de paso de los puertos de salida.

- Un multiplexor conmutado de banda ancha según la reivindicación 12, cuando depende de una cualquiera de las reivindicaciones 7 a 11, en el que al menos un combinador de potencia está adaptado para combinar señales divididas procedentes de dos divisores de potencia diferentes y proporcionar la señal combinada a un puerto de entrada.

- Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 2 a 13, en el que una pluralidad de trayectos de señal de puertos de salida asociados comprenden medios de medición de amplitud, preferiblemente DLVA.

- 15. Un multiplexor conmutado de banda ancha según la reivindicación 14, en el que los medios de medición de amplitud son medios de medición de amplitud de banda estrecha con respecto al demultiplexor de banda ancha.

- Un multiplexor conmutado de banda ancha según cualquiera de las reivindicaciones 14 ó 15, en el que cada medio de medición de amplitud está adaptado para abrir o cerrar su trayecto de señal asociado entre puertos de salida y entrada dependiendo de la señal medida por los medios de medición de amplitud.

- 17. Un multiplexor conmutado de banda ancha según una cualquiera de las reivindicaciones 1 a 16, que comprende además medios de medición de frecuencia conectados al puerto de banda ancha de salida del multiplexor de banda ancha de salida.

- 20 18. Un multiplexor conmutado de banda ancha según la reivindicación 17, en el que los medios de medición de frecuencia son medios de medición de frecuencia de banda estrecha con respecto al multiplexor de banda ancha.

25

- 19. Un multiplexor conmutado de banda ancha según cualquiera de las reivindicaciones 17 ó 18, que comprende además un convertidor reductor de frecuencia entre el multiplexor de banda ancha y los medios de medición de frecuencia, estando adaptado el convertidor reductor de frecuencia para desfasar la frecuencia de la señal recibida desde el puerto de salida de banda ancha del multiplexor en un factor que depende de qué trayecto de señal entre el demultiplexor de entrada y el multiplexor de salida esté abierto.

- 20. Un multiplexor conmutado de banda ancha según la reivindicación 8, que comprende al menos un multiplexor de banda ancha de salida adicional, teniendo el multiplexor de banda ancha de salida una pluralidad de puertos de entrada y un puerto de salida de banda ancha, teniendo al menos algunos de los divisores de potencia una salida conectada a un puerto de entrada del multiplexor de banda ancha de salida adicional.

- 21. Un multiplexor conmutado de banda ancha según la reivindicación 20, en el que el puerto de banda ancha de salida de un multiplexor de banda ancha de salida se conecta a medios de medición de frecuencia y el puerto de banda ancha de salida del multiplexor de banda ancha adicional se conecta a un receptor superheterodino.

FIG. 1

# FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 10

FIG. 11

FIG. 12

FIG. 14

FIG. 15

FIG. 16