OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

① Número de publicación: 2 358 417

(51) Int. Cl.:

B60T 8/00 (2006.01) **B60T 8/88** (2006.01) G06F 11/00 (2006.01) G06F 11/08 (2006.01)

(12) TRADUCCIÓN DE PATENTE EUROPEA Т3

- 96 Número de solicitud europea: 03017980 .8

- 96 Fecha de presentación : **18.04.2001**

- 97 Número de publicación de la solicitud: 1380483 97) Fecha de publicación de la solicitud: 14.01.2004

- 54) Título: Sistema de frenos controlado electrónicamente.

- (30) Prioridad: **28.04.2000 JP 2000-130803**

- (73) Titular/es: **DENSO CORPORATION** 1-1, Showa-cho Kariya-city, Aichi-pref, 448-8661, JP

- (45) Fecha de publicación de la mención BOPI: 10.05.2011

- 72 Inventor/es: Kidokoro, Hiroyasu; Kabune, Hideki y Kumabe, Hajime

- (45) Fecha de la publicación del folleto de la patente: 10.05.2011

- (74) Agente: Elzaburu Márquez, Alberto

ES 2 358 417 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

La presente invención se refiere a un método y aparato para monitorizar un microordenador proporcionado en una unidad de control electrónico.

Un microordenador proporcionado en una unidad de control electrónico (ECU) para vehículos generalmente se monitoriza para detectar si el microordenador está funcionando normalmente o no, si una entrada al microordenador es normal o no, o si la operación aritmética en el microordenador es llevada a cabo exactamente o no.

La monitorización se lleva a cabo, por ejemplo, ejecutando la monitorización de perro guardián (WD) para detectar si el periodo de cálculo aritmético en un circuito integrado (IC) de monitorización está en el periodo correcto o no introduciendo el periodo de cálculo aritmético para el IC de monitorización desde el microordenador. También se puede llevar a cabo comparando el resultado del cálculo aritmético de cada microordenador usando el microordenador adicional de la misma estructura como el microordenador para llevar a cabo la operación de cálculo aritmético.

No obstante, la monitorización de WD provoca que la capacidad de monitorización sea insuficiente debido a que los contenidos de la monitorización son limitados. La monitorización mutua que usa una pareja de microordenadores provoca que no se pueda detectar un fallo si hay un error en los datos introducidos a una pareja de microordenadores y que el coste de monitorización llegue a ser alto porque se usa una pareja de microordenadores.

El documento DE 44 31 901 A1 describe un dispositivo de detección de fallos para un sistema de control de frenos antideslizamiento de un vehículo a motor. Allí se proporciona un microordenador principal para generar una señal de control de la presión hidráulica para el control de un elemento de actuación, que se diseña para la generación de fuerzas de frenado, que van a ser aplicadas a las ruedas del vehículo a motor. Adicionalmente, se proporciona un microordenador secundario para detectar la aparición de un fallo en el ordenador principal en base a la señal de control de la presión hidráulica. Un dispositivo de generación de la señal de prueba se proporciona en el microordenador principal o el microordenador secundario para la generación de una señal de prueba, y un dispositivo aritmético de control de frenos antideslizamiento en el ordenador principal genera una señal de control de la presión hidráulica en base a la señal de la velocidad de la rueda o la señal de prueba. Un dispositivo de monitorización de la señal de control de la presión hidráulica, que se proporciona en el microordenador secundario, monitoriza la señal de la presión hidráulica generada en respuesta a la señal de prueba para comprobar la validez de la señal de control de la presión hidráulica.

Es por lo tanto un objeto de la presente invención proporcionar un método de monitorización de un microordenador sin requerir una pareja de microordenadores.

El objeto se resuelve por los rasgos de la reivindicación independiente 1. Las reivindicaciones dependientes se dirigen a las realizaciones preferentes de la invención.

El anterior y otros objetos, rasgos y ventajas de la presente invención llegarán a ser más evidentes a partir de la siguiente descripción detallada hecha con referencia a los dibujos anexos. En los dibujos:

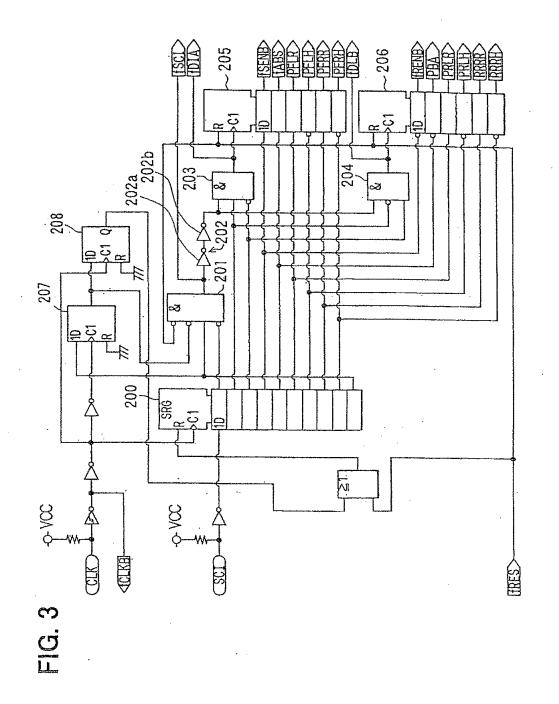

La Fig. 1 es un diagrama esquemático que ilustra un sistema de control del ABS controlado por una ECU para el control del ABS de acuerdo con una primera realización de la presente invención;

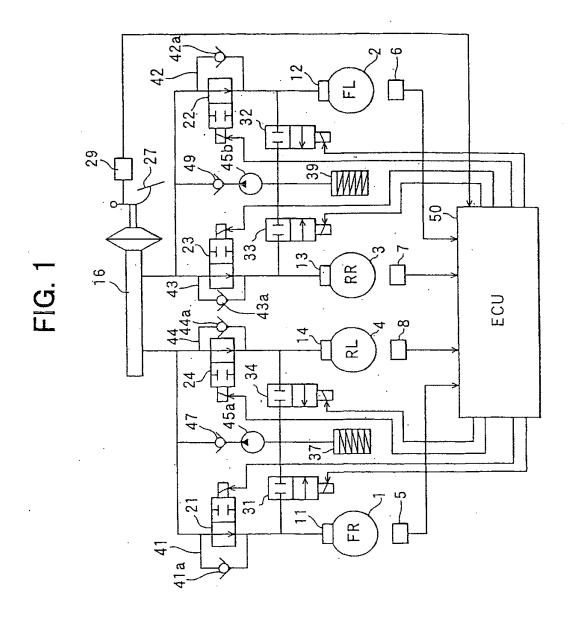

La Fig. 2 es un diagrama de bloques que ilustra la ECU para el control del ABS usado en la primera realización;

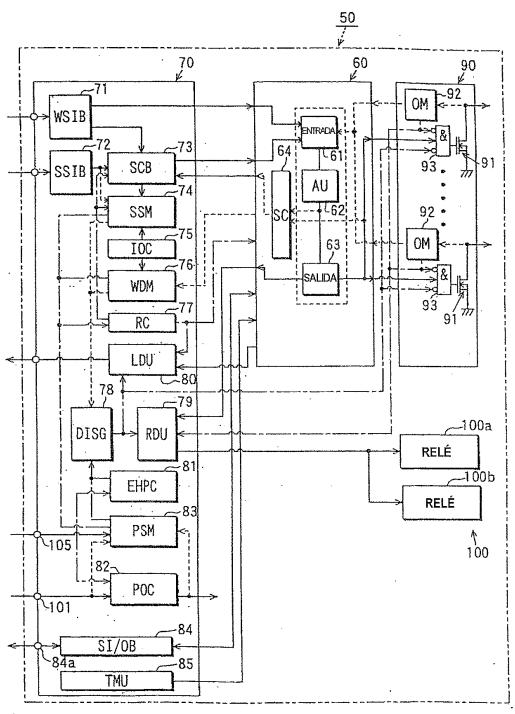

La Fig. 3 es un diagrama del circuito que ilustra una parte del almacenamiento temporal de la comunicación serie usado en la ECU mostrada en la Fig.2;

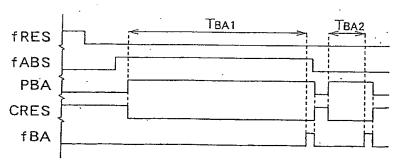

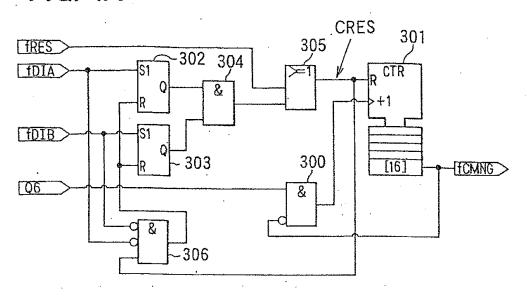

La FIG. 4A es un diagrama del circuito que ilustra un circuito lógico de monitorización del intervalo, y la Fig. 4B y la Fig. 4C son diagramas de tiempo que ilustran las señales producidas en el circuito lógico mostrado en la Fig. 4A;

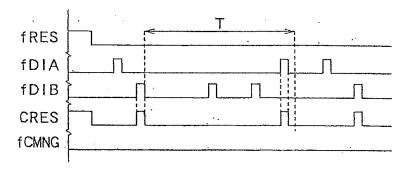

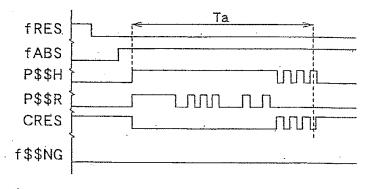

La FIG. 5A es un diagrama del circuito que ilustra un circuito lógico de monitorización de fallos del microordenador, y la Fig. 5B y 5C son diagramas de temporización que ilustran las señales producidas en el circuito lógico mostrado en la Fig. 5A;

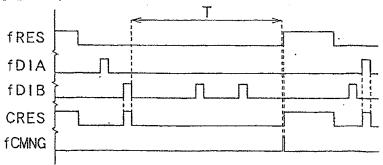

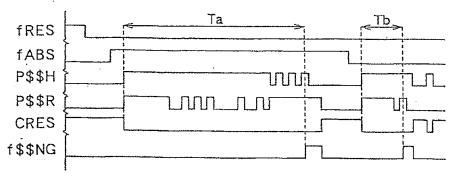

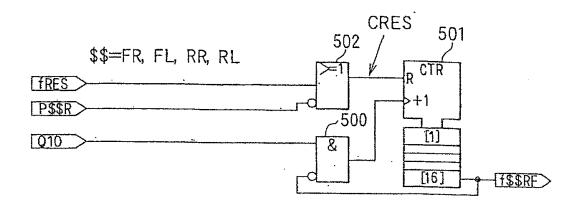

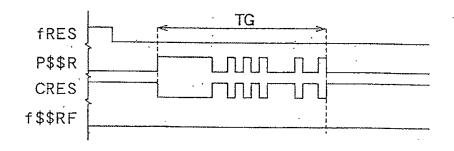

La FIG. 6A es un diagrama del circuito que ilustra un circuito lógico de monitorización de fallos del microordenador para el control del ABS, y la Fig. 6B y 6C son diagramas de temporización que ilustran las señales producidas en el circuito lógico mostrado en la Fig. 6A;

La FIG. 7A es un diagrama del circuito que ilustra un circuito lógico de monitorización de secuencias, y la Fig. 7B es un diagrama de temporización que muestra las señales producidas en el circuito lógico mostrado en la Fig. 7A;

2

15

5

10

20

25

30

35

40

45

La FIG. 8 es un diagrama del circuito que ilustra un circuito de monitorización del cálculo de la velocidad de la rueda de acuerdo con una segunda realización de la presente invención; y

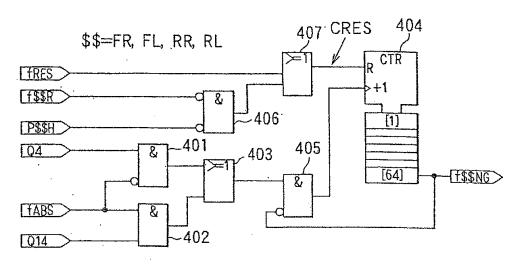

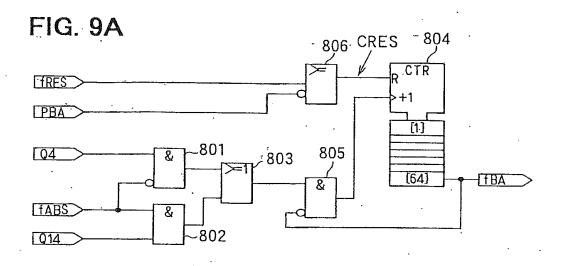

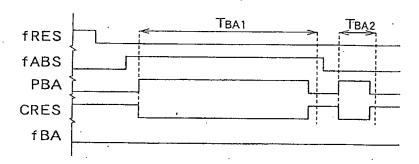

La FIG. 9A es un diagrama del circuito que ilustra un circuito lógico de monitorización de fallos del microordenador para un control de asistencia de frenos, y la Fig. 9B y Fig. 9C son diagramas de temporización que muestran las señales producidas en el circuito lógico mostrado en la Fig. 9A.

La presente invención se describirá en detalle con referencia a las realizaciones, que se dirigen a una unidad de control electrónico (ECU) para vehículos.

### (Primera Realización)

Con referencia primero a la Fig. 1 que muestra un sistema de control de frenado antibloqueo (ABS), se proporcionan una rueda delantera derecha (FR) 1, una rueda delantera izquierda (FL) 2, una rueda trasera derecha (RR) 3 y una rueda trasera izquierda (RL) 4 con unos sensores de velocidad de la rueda tipo de recolección electromagnética, unos tipo dispositivo de efecto magneto resistivo (MRE) o unos tipo dispositivo Hall 5 a 8, respectivamente. Estos sensores de velocidad de la rueda 5 a 8 generan señales de pulsos respectivas que dependen de la rotación de las ruedas 1 a 4.

Además, las ruedas 1 a 4 se proporcionan respectivamente con cilindros de rueda 11 a 14. Cuando un cilindro maestro 16 genera una presión del fluido del freno que depende de la cantidad de pisada del conductor de un pedal de freno 27, esta presión del fluido del freno se transfiere a los cilindros de las ruedas 11 a 14 a través de las válvulas de doble posición (válvulas de control de aumento de presión) 21 a 24 y a través de las tuberías de presión del fluido respectivas. El estado de pisado del pedal del freno 27 se detecta mediante un conmutador de 20 parada 29.

Además, los cilindros de rueda 11, 14 se conectan con un depósito 37 a través de las válvulas de doble posición (válvulas de control de reducción de presión) 31, 34, respectivamente. Los cilindros de las ruedas 12, 13 se conectan con un depósito 39 a través de las válvulas de doble posición (válvulas de control de reducción de presión) 32, 33, respectivamente.

Las válvulas de doble posición 21 a 24 y 31 a 34 cada una se componen de una válvula de doble posición de tipo de accionamiento del solenoide que incluye una posición de comunicación y una posición de corte. Estas posición de comunicación y posición de corte se pueden conmutar suministrado energía eléctrica al solenoide.

Por otra parte, la parte de más arriba y de más abajo de las válvulas de doble posición 21 a 24 se conectan con tuberías de desviación 41 y 44, respectivamente. Estas tuberías de desviación 41 a 44 se proporcionan con válvulas de no retorno 41a a 44a, respectivamente. Solamente la presión del fluido hacia el cilindro maestro 16 desde los cilindros de las ruedas 11 a 14 fluye hacia la tubería de desviación 41 a 44.

Los depósitos 37, 39 se conectan con unas tuberías de presión del fluido a través de las bombas 45a, 45b accionadas por motores no ilustrados y válvulas de no retorno 47, 49, respectivamente. Solamente, se permite fluir la presión del fluido hacia el cilindro maestro 16 desde los depósitos 37, 39.

Las señales de detección de los sensores de velocidad de las ruedas 5 a 8 y el conmutador de parada 29 se introducen a una ECU 50 para el control del ABS. La ECU de control del ABS 50 genera, en base a las señales de detección anteriores, las señales de control para las válvulas de doble posición 21 a 24 y 31 a 34 y las señales de control del motor para accionar las bombas 45a, 45b. En base a estas señales de control, se controlan las válvulas de doble posición 21 a 24 y 31 a 34 y el motor para el propósito del control del ABS o similar.

La Fig. 2 ilustra un diagrama de bloques que ilustra la estructura interna de la ECU de control del ABS 50. Como se ilustra en esta figura, la ECU de control del ABS 50 tiene una pluralidad de circuitos integrados que incluyen un microordenador 60, un IC periférico 70, un accionador del solenoide 90 y un relé semiconductor 100 o similar.

Los detalles de cada dispositivo estructural de la ECU de control del ABS 50 se describirán a continuación. Cada punta de la flecha en una línea continúa en la Fig. 2 indica una línea del sistema de control, cada punta de la flecha en una línea discontinua indica una línea del sistema de monitor, y cada punta de la flecha en una línea mixta de puntos y rayas indica una línea del sistema de inhibición/corte. La línea del sistema de control significa que el dispositivo en frontal de la punta de la flecha se controla en base a una señal de un dispositivo en la parte trasera de la punta de la flecha. Además, la línea del sistema de monitor significa que un dispositivo en el frontal de la punta de la flecha monitoriza si falla un dispositivo específico o no se basa en una señal de un dispositivo en la parte trasera de la punta de la flecha. Además, la línea del sistema de inhibición/corte significa que un dispositivo en el frontal de la punta de la flecha inhibe o corta un accionamiento de un dispositivo especificado en base a una señal de inhibición/corte desde un dispositivo en la parte trasera de la punta de la flecha.

Primero, el microordenador 60 consta de una unidad de entrada 61, una unidad aritmética 62, una unidad de salida 63. Cuando varios trozos de información tales como las señales de la velocidad de la rueda se introducen a la unidad de entrada 61, la unidad aritmética 62 realiza varias operaciones aritméticas usadas para que el control del ABS se base en tales varias entradas de información. La unidad de salida 63 genera las señales de control del

3

5

15

10

30

25

35

40

45

50

ABS, es decir, las señales de accionamiento del solenoide y las señales del accionamiento del motor en base a la operación aritmética. Además, el microordenador 60 también se proporciona con una unidad de comunicación serie 64. Cuando se introducen varias señales producidas en la operación aritmética de la unidad aritmética 62 (por ejemplo, la señal de control del ABS que indica el estado de control del ABS), estas varias señales se convierten a una señal serie y entonces se envían al IC periférico 70 como la señal serie.

5

10

15

20

25

35

40

45

50

55

60

Después, el IC periférico 70 consta de un almacenamiento temporal de entrada de la velocidad de la rueda 71, un almacenamiento temporal de entrada de la señal del conmutador (SW) 72, un almacenamiento temporal de la comunicación serie 73, una unidad de monitorización de la comunicación serie 74, un circuito oscilador interno 75, una unidad de monitorización de perro guardián (WD) 76, una unidad de control de reinicio 77, una unidad de generación de la señal de inhibición de accionamiento 78, una unidad de accionamiento del relé 79, un circuito de accionamiento de la lámpara 80, un circuito de protección de excesivo calentamiento 81, una unidad de monitorización de suministro de energía 82, un circuito de salida de suministro de energía 83, un almacenamiento temporal de entrada/salida de señal 84 y una unidad de monitorización de la temperatura 85. Cada circuito o unidad de dispositivo se integra en una pastilla para formar el IC periférico 70.

El almacenamiento temporal de entrada de la velocidad de la rueda 71 realiza la formación de la forma de onda para corregir las señales de detección transmitidas desde los sensores de velocidad de la rueda 5 a 8 de la Fig. 1 en una forma rectangular. La señal de la velocidad de la rueda formada en la forma de onda mediante este almacenamiento temporal de entrada de la velocidad de la rueda 71 es introducida a continuación en el microordenador 60 para varias operaciones aritméticas de las velocidades de la rueda y se estima la velocidad del conjunto usada para el control del ABS. Además, el almacenamiento temporal de entrada de la velocidad de la rueda 71 también detecta una rotura del hilo que conecta los sensores de velocidad de la rueda 5 a 8 y la ECU de control del ABS 50. Este almacenamiento temporal 71 transmite una señal de rotura del hilo que indica la rotura del hilo al almacenamiento temporal de la comunicación serie 73 cuando se detecta la rotura del hilo.

El almacenamiento temporal de entrada de la señal de SW 72 monitoriza la señal de ENCENDIDO/APAGADO del conmutador de parada 29 y una señal que indica que la energía se alimenta o no a los solenoides de las válvulas de doble posición 21 a 24, 31 a 34 (por ejemplo, un valor de voltaje aplicado sobre el solenoide) indicado en la Fig. 1. Por ello, se puede poner a la salida la señal de ENCENDIDO/APAGADO que indica si el pedal de freno 27 se pisa o no y la señal de ENCENDIDO/APAGADO que indica si la se suministra la energía eléctrica al solenoide o no.

El almacenamiento temporal de la comunicación serie 73 convierte una señal de rotura de hilo desde el almacenamiento temporal de entrada de la velocidad de la rueda 71 y la señal de ENCENDIDO/APAGADO desde el almacenamiento temporal de entrada de la señal de SW 72 a la señal serie, y entonces transmite la señal serie al microordenador 60. Una señal serie desde un microordenador 60 se transmite entonces a este almacenamiento temporal de la comunicación serie 73.

La unidad de monitorización de la señal serie 74 monitoriza el microordenador 60 en base a la señal serie desde el almacenamiento temporal de la comunicación serie 73. Más concretamente, el almacenamiento temporal de la comunicación serie 73 recibe el resultado de la operación aritmética desde el microordenador 60 en base a las señales desde el almacenamiento temporal de entrada de la velocidad de la rueda 71 y el almacenamiento temporal de la entrada de la señal de SW 72 para monitorizar si esta señal es normal o no. Por ejemplo, cuando la señal que indica que el estado del control del ABS se transmite desde la unidad de control serie 64 a pesar de que la señal APAGADO que indica que el conmutador de apagado 29 no se pisa se transmite desde el almacenamiento temporal de entrada de la señal de SW 72, se determina que la señal serie desde el microordenador 60 no es normal. Cuando la señal serie desde el microordenador 60 no es normal, se saca una señal de reinicio a la unidad de control de reinicio 77 descrita más tarde o se transmite una señal de inhibición al circuito de generación de la señal de inhibición del accionamiento 78.

La unidad del oscilador interno 75 forma un reloj interno usado en la unidad de monitorización de la señal serie 74 y la unidad de monitorización del WD 76 o similar. En esta unidad del oscilador interno 75, se generan una pluralidad de señales de reloj en distintos puntos de tiempo (temporizaciones) y la unidad de monitorización de la señal serie 74 y la unidad de monitorización del WD 76 seleccionan la señal de reloj de la temporización apropiada como una señal de monitor para realizar una función de monitorización.

La unidad de monitorización del WD 76 monitoriza si se realiza normalmente o no la operación aritmética en el microordenador 60 en base a los datos tales como el periodo de la operación aritmética producido desde el microordenador 60. Por ejemplo, dado que la señal de monitor de WD se produce como una señal que se invierte alternativamente cuando se realiza normalmente la operación aritmética, si la señal de monitor del WD no se invierte alternativamente, indica que la operación aritmética del microordenador 60 no se ejecuta normalmente. Cuando la operación aritmética del microordenador 60 no se ejecuta en el periodo normal, se saca una señal de reinicio a la unidad de control de reinicio 77 descrita más tarde o se transmite la señal de inhibición al circuito de generación de la señal de inhibición del accionamiento 78.

En el momento de la inicialización o cuando se introduce la señal de reinicio a la unidad de control de reinicio 77 desde la unidad de monitorización de la señal serie 74, la unidad de monitorización del WD 76 y la unidad

de monitorización del suministro de energía 83 descrita más tarde, la señal de reinicio se transmite al microordenador 60. Tras la recepción de esta señal de reinicio, el microordenador 60 fija los valores del mismo a un modo de un estado de reinicio predeterminado. Por ejemplo, el microordenador 60 para todas las operaciones aritméticas. Además, esta señal de reinicio también se transmite al almacenamiento temporal de la comunicación serie 73 y la unidad de monitorización de la señal serie 74 para el propósito de la inicialización en base a esta señal de reinicio.

5

10

15

20

25

30

35

40

45

50

55

60

La unidad de generación de la señal de inhibición de accionamiento 78 transmite una señal de inhibición de accionamiento del solenoide y una señal de inhibición de accionamiento del motor a la unidad de accionamiento del relé 79 en base a las señales de inhibición desde la unidad de monitorización de la señal serie 74, la unidad de monitorización del WD 76, el circuito de protección de excesivo calentamiento 81 y la unidad de monitorización de suministro de energía 83 descrita más tarde y también transmite directamente la señal de inhibición de accionamiento a un accionador de accionamiento del solenoide 90 sin ser a través del microordenador 60. Por lo tanto, cuando la señal de inhibición de accionamiento del solenoide se transmite desde la unidad de generación de la señal de inhibición de accionamiento 78, el accionamiento de los solenoides se inhibe incluso cuando el microordenador 60 está en funcionamiento.

La unidad de accionamiento del relé 79 controla la conmutación de una unidad de relé semiconductor 100 y también controla el suministro de potencia al motor para accionar los solenoides y las bombas 45a, 45b en base a las señales de accionamiento del solenoide y la señal de accionamiento del motor desde el microordenador 60. Además, cuando se introduce la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor desde la unidad de generación de la señal de inhibición del accionamiento 78 y la unidad de monitorización de salida 92 del accionador del solenoide 90, la unidad de accionamiento del relé 79 para el suministro de potencia a los solenoides y al motor con la unidad del relé semiconductor 100.

La unidad de accionamiento de la lámpara 80 pone a la salida bajo el estado normal el estado de funcionamiento del control del ABS en base a una señal de estado de control del ABS del microordenador 60. No obstante, pone a la salida un estado no operativo de control del ABS cuando se introduce la señal de reinicio desde la unidad de control de reinicio 77 o cuando la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor se introducen desde la unidad de generación de la señal de inhibición del accionamiento 78. La lámpara no ilustrada se ilumina al recibir la señal desde la unidad de accionamiento de la lámpara 80 para asegurar el estado de funcionamiento del control del ABS.

El circuito de protección de excesivo de calentamiento 81 detecta que la pastilla ha alcanzado una temperatura predeterminada para evitar que la pastilla que proporciona el IC periférico 70 alcance la temperatura predeterminada. Cuando la pastilla ha alcanzado la temperatura predeterminada, la unidad de generación de la señal de inhibición de accionamiento 78 provoca generar la señal de inhibición y para el suministro de voltaje al microordenador 60 en vistas de evitar la subida adicional de la temperatura.

El circuito de salida del suministro de energía 82 corresponde a un bloque monitorizado y se conecta a un terminal de suministro de energía (primer terminal de suministro de energía) 101 y un terminal de tierra (primer terminal de tierra) conectado a una fuente de alimentación externa asignada al exterior de la ECU 50. El circuito de salida de suministro de energía 82 saca un voltaje predeterminado (por ejemplo, 5V, 3,3V) en base al voltaje aplicado al terminal de la fuente de alimentación 101. Un voltaje de salida del circuito de salida de suministro de energía 82 se usa como un voltaje de la fuente de alimentación del microordenador 60, el IC periférico 70 y el accionador del solenoide 90 o similar.

La unidad de monitorización del suministro de energía 83 corresponde a un bloque de monitor y se conecta a un terminal de la fuente de alimentación (segundo terminal de la fuente de alimentación 101 conectado con el circuito de salida del suministro de energía 82 y un terminal de tierra (segundo terminal de tierra). La unidad de monitorización de suministro de energía 83 monitoriza si el voltaje de salida del circuito de salida de suministro de energía 82 es o no el valor predeterminado y también monitoriza si el voltaje aplicado al circuito de salida de suministro de energía 82 tiene en un voltaje excesivo o no. Por ejemplo, cuando el voltaje de salida del circuito de salida de suministro de energía 82 es menor que el voltaje predeterminado, se transmite una señal de reinicio a la unidad de control de reinicio 77. Cuando es mayor que el valor predeterminado, se transmite una señal de inhibición a la unidad de generación de la señal de inhibición de accionamiento 78. Además, el voltaje aplicado al circuito de salida de suministro de energía 82 es excesivo, la señal de inhibición se saca a la unidad de generación de la señal de inhibición del accionamiento 78 y suministrando el voltaje al microordenador 60 se para para evitar el excesivo calentamiento.

El almacenamiento temporal de entrada/salida de la señal 84 se conecta al terminal 84a para la comprobación para la diagnosis cuando un coche tiene un fallo y hace la comunicación con el microordenador 60 conectando un probador al terminal 84a. Además, el almacenamiento temporal de entrada/salida de la señal 84 se puede usar como un almacenamiento temporal de salida solamente, por ejemplo, como un almacenamiento temporal que pone a la salida la señal para indicar que una velocidad del vehículo visualizada en un medidor de velocidad del vehículo (por ejemplo, una señal que corresponde con la velocidad del vehículo estimada calculada a partir de la velocidad de la rueda).

La unidad de monitorización de la temperatura 85 siempre detecta la temperatura de la ECU 50. La unidad de monitorización de la temperatura 85 saca la señal que depende de la temperatura de la ECU 50 al microordenador 60 como una señal de detección de la temperatura. En base a esta señal de detección de la temperatura, el microordenador 60 realiza la operación aritmética para el control del ABS que depende de la temperatura detectada.

5

10

15

20

25

30

35

40

45

50

55

El accionador del solenoide 90 consta de transistores MOS 91 conectados a los solenoides, a las unidades de monitorización de salida 92 para monitorizar el estado del suministro del voltaje a los solenoides (transistores MOS 91) y a los circuitos AND 93 para el accionamiento del ENCENDIDO/APAGADO de los transistores MOS 91. Los transistores MOS 91 se conectan a los respectivos solenoides de las varias válvulas de control 21 a 24, 31 a 34 ilustradas en la Fig. 1 para ejecutar la conmutación para el suministro de voltaje.

Las unidades de monitorización de salida 92 se proporcionan en una base de una a una a los solenoides para monitorizar una salida de accionamiento a cada solenoide. Por ejemplo, monitoriza el estado de suministro de voltaje al solenoide en base al voltaje del drenador y la corriente del drenador del transistor MOS 91. Por ello, por ejemplo, se detecta si una corriente del drenador es excesiva o no y si un hilo de la fuente de alimentación al solenoide está abierto o no o la corriente tiene o no fugas, y además si el transistor MOS 91 tiene o no la temperatura excesivamente. Por ello, si se logra el resultado no adecuado para el accionamiento del solenoide, la unidad de monitorización de salida 92 transmite la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor a la unidad de accionamiento del relé 79 y también saca la señal de inhibición de accionamiento del solenoide al circuito AND 93

Al circuito AND 93, se le introducen una señal de salida del microordenador 60, una señal de salida desde la unidad de accionamiento del relé 79, una señal de salida desde la unidad de generación de la señal de inhibición de accionamiento 78 y una señal de salida desde la unidad de monitorización de salida 92. En el caso de esta realización, las señales de salida desde la unidad de accionamiento del relé 79, la unidad de generación de la señal de inhibición del accionamiento 78 y la unidad de monitorización de la salida 92 están normalmente a nivel bajo. No obstante, si ocurre un fallo, se pasa a nivel alto y la salida del circuito AND 93 llega a ser baja, es decir, el transistor MOS 91 se apaga.

De esta manera, el accionador del solenoide 90 no solamente corta el suministro de energía al solenoide en base a la señal desde el microordenador 60 y el IC periférico 70 sino que también corta el suministro de energía al solenoide en base a la señal desde la unidad de monitorización de salida 92 proporcionada dentro del accionador del solenoide 90 en sí mismo.

En la unidad de relé semiconductor 100, el suministro de energía a los solenoides se conmuta mediante un relé semiconductor 100a, mientras que el suministro de energía al motor para accionar las bombas 45a, 45b se conmuta mediante un relé semiconductor 100b. Estos relés semiconductores 100a, 100b se construyen para ser controlados en base a la señal desde la unidad de accionamiento del relé 79 para permitir normalmente el suministro de energía a los solenoides y los motores y deshabilitar el suministro de energía a los solenoides y los motores tras la recepción de la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor desde la unidad de accionamiento del relé 79.

Una parte del almacenamiento temporal de la comunicación serie 73 se muestra en la Fig. 3. Como se ilustra en la Fig. 3, una señal de reloj síncrono CLK se saca desde el microordenador 60, una señal serie SCI transmitida desde la unidad de comunicación serie 64 del microordenador 60 y una señal de reinicio fRES desde la unidad de control de reinicio 77 se introducen al almacenamiento temporal de la comunicación serie 73.

Los datos transmitidos junto con un número de ID A y los datos transmitidos junto con un número de ID B se almacenan respectivamente en los distintos registros 205, 206 proporcionados en el almacenamiento temporal de la comunicación serie 73 dando, por ejemplo, los números de ID A y B a la señal serie SCI transmitida desde la unidad de comunicación serie 64.

Cuando la señal serie SCI se transmite, se almacena en un registro de desplazamiento 200. Cuando la señal serie se almacena completamente en el registro de desplazamiento 200, una salida del dígito final llega a ser de nivel alto. Por ello, una salida del circuito AND 201 llega a ser de nivel alto y la señal de recepción fSCI que notifica la recepción de una cierta señal llaga a ser de nivel alto. Además, el nivel alto se pone a la salida de un circuito AND 203 y un circuito AND 204 a través de un circuito de retardo 202 formado por los circuitos del inversor 202a, 202b del número par.

Cuando esta señal se introduce, ambos circuitos AND 203 y 204 generan las salidas recibiendo las señales del segundo bit y del tercer bit del dígito del registro de desplazamiento 200. Es decir, cuando se reciben los datos que tienen el número de ID A, el circuito AND 203 pone a la salida el nivel alto mientras que el circuito AND 204 pone a la salida el nivel bajo. Cuando se reciben los datos que tienen el número de ID B, el circuito AND 203 pone a la salida el nivel bajo y el circuito AND 204 pone a la salida el nivel alto, respectivamente. Estas salidas de los circuitos AND 203 y 204 corresponden respectivamente a la señal fDIA que notifica si los datos del número de ID A se introducen o no y la señal fDIB que notifica si los datos del número de ID B se introducen o no.

Como se describió arriba, cuando se reciben los datos que tienen el número de ID A, el registro 205 recibe la salida de nivel alto desde el circuito AND 203 para almacenar el contenido almacenado en cada bit del registro de desplazamiento 200. Además, cuando se reciben los datos que tienen el número de ID B, el registro 206 recibe la salida de nivel alto desde el circuito AND 204 para acomodar los datos almacenados en cada bit del registro de desplazamiento 200.

5

10

15

20

25

30

35

40

45

50

55

Estos registros de desplazamiento 205, 206 generan salidas que dependen de los datos almacenados en cada bit para cada bit. Específicamente, el primer bit del dígito del registro 205 saca una señal de petición de cancelación fSENB de la señal de inhibición de accionamiento del solenoide a la unidad de generación de la señal de inhibición del accionamiento 78 y un segundo bit del dígito saca una señal fABS que notifica el estado del control del ABS. El tercer bit del dígito pone a la salida una señal PFLR que notifica el estado de accionamiento de la válvula de doble posición 32 de la rueda FL 2. Además, el cuarto bit del dígito pone a la salida una señal PFLH que notifica el estado de accionamiento de la válvula de doble posición de la rueda FL 2. Además, el quinto bit del dígito pone a la salida una señal PFRR que notifica el estado de accionamiento de la válvula de doble posición 31 de la rueda FR 1 y el sexto bit del dígito pone a la salida una señal PFRH que notifica el estado de accionamiento de la válvula de doble posición 21 de la rueda FR 1.

El primer bit del dígito del registro 206 pone a la salida una señal de reconocimiento fRENB que permite una salida de la unidad de accionamiento del relé 79, mientras que el segundo bit del dígito pone a la salida una señal fBA que notifica al estado de control de asistencia de freno, el tercer bit del dígito pone a la salida una señal PRLR que notifica el estado de accionamiento de la válvula de doble posición 34 de la rueda RL 4, el cuarto bit del dígito pone a la salida una señal PRLH que notifica el estado de accionamiento de la válvula de doble posición 24 de la rueda RL, el quinto bit del dígito pone a la salida una señal PRRR que notifica el estado de accionamiento de la válvula de doble posición 33 de la rueda RR 3 y el sexto bit del dígito pone a la salida una señal PRRH que notifica el estado del accionamiento de la válvula de doble posición 23 de la rueda RR 33.

Como se describió anteriormente, la señal serie SCI transmitida desde el microordenador 60 se recibe por el almacenamiento temporal de la comunicación serie 73 y varias señales que dependen de estos datos recibidos se sacan a la unidad monitora de la señal serie 74 desde el almacenamiento temporal de la comunicación serie 73.

Los circuitos biestables tipo D 207, 208 se proporcionan para establecer la temporización para transmitir los datos en el registro de desplazamiento 200 al registro 205 o 206. Una señal fRES es la señal de reinicio desde la unidad de control del reinicio 77 y se fija a un nivel alto cuando ocurre una avería o fallo durante la inicialización u otra operación (en el momento de la prueba de fallos).

Un circuito lógico para el procesamiento de la señal de entrada desde el almacenamiento temporal de entrada de la velocidad de la rueda 71 y la señal desde el almacenamiento temporal de entrada de la señal SW 72 no se describen. No obstante, este circuito lógico es el circuito lógico de comunicación serie bien conocido en el almacenamiento temporal de la comunicación serie 73, y forma las señales serie de una señal de detección de rotura del hilo desde el almacenamiento temporal de entrada de la velocidad de la rueda 71 y varias señales de conmutación desde el almacenamiento temporal de entrada de la señal SW 72 para transmitir por ello tales señales al microordenador 60 como las señales serie.

La unidad monitora de la señal serie 74 se muestra en la Fig. 4A a la Fig. 7A. El circuito lógico ilustrado en la Fig. 4A es un circuito lógico de monitorización del intervalo para monitorizar un intervalo de procesamiento en el microordenador 60.

Una señal Q6 ilustrada en esta figura es una de las varias señales de reloj puestas a la salida del circuito de oscilación interno 75. Cuando una salida de un circuito AND 300 llega a ser de nivel alto síncronamente con una subida de la señal Q6, un contador 301 recibe esta salida y cuenta hasta su cuenta. Además, cuando se introducen la señal fDIA que notifica la recepción de los datos que tienen el número de ID A y la fDIB que notifica la recepción de los datos que tienen el número de ID B, un circuito AND 304 pone a la salida un nivel alto recibiendo la salida del nivel alto desde los circuitos biestables RS 302, 303. Un circuito OR 305 también pone a la salida un nivel alto.

Por lo tanto, cuando el contador 301 está contando la señal que depende del pulso de la señal Q6, el contador 301 se reinicia y repite la cuenta y el reinicio que depende del pulso de la señal Q6 siempre y cuando se reciban normalmente la señal fDIA y la señal fDIB. Si la señal fDIA y la señal fDIB no se reciben normalmente, el contador 301 no se reinicia y cuenta hasta el dígito final de la señal.

Por lo tanto, se puede detectar el estado del fallo de la comunicación desde la señal fCMNG puesto a la salida desde el contador 301. En el caso de este circuito lógico, cuando se reciben normalmente las señales fDIA, fDIB, la señal fCMNG llega a ser de nivel bajo. Cuando ocurre el fallo de la comunicación, esta señal llega a ser de nivel alto.

Una salida del circuito OR 305 se introduce al circuito AND 306 y los circuitos biestables RS 302, 303 se reinician dependiendo de una salida desde el circuito AND 306. Es decir, cuando se reciben normalmente las señales fDIA, fDIB, se reinician los circuitos biestables RS 302, 303. Además, la señal fRES es la señal de reinicio desde la unidad de control de reinicio 77 y se fija al nivel alto cuando ocurre un fallo en el momento de la inicialización o en las operaciones.

Las Fig. 4B y 4C ilustran los diagramas de temporización en el caso en el que se reciben normalmente y no las señales fDIA, fDIB, respectivamente. Como se ilustra en la Fig. 4B, cuando se reciben normalmente las señales fDIA, fDIB durante un periodo T hasta la terminación de la cuenta del contador 301, la señal de salida CRES del circuito OR 305 llega a ser de nivel alto y la señal fCMNG no llega a ser de nivel alto. Por otra parte, como se ilustra en la Fig. 4C, si no se reciben normalmente las señales fDIA, fDIB durante el periodo T, la señal de salida CRES del circuito OR 305 se mantiene en el nivel bajo y por ello la cuenta del contador 301 continúa hasta el dígito final y la señal fCMNG llega a ser de nivel alto.

Como se describió anteriormente, es posible monitorizar el intervalo de las operaciones aritméticas en el microordenador 60 usando el circuito lógico ilustrado en la Fig. 4A.

El circuito lógico ilustrado en la Fig. 5A es uno de los circuitos lógicos de monitorización del resultado de la operación aritmética para monitorizar el resultado de las operaciones aritméticas en el microordenador 60. Aquí, se monitoriza si las válvulas de doble posición 21 a 24, 31 a 34 para las ruedas 1 a 4 (ruedas de control) como el objeto del control del ABS se accionan normalmente o no.

En la siguiente explicación, una señal que notifica el estado de accionamiento de las válvulas de control de aumento de la presión 21 a 24 entre las válvulas de doble posición 21 a 24, 31 a 34 que corresponden a las ruedas de control se definen como una señal P\$\$H, mientras que una señal que notifica el estado de accionamiento de las válvulas de control de disminución de la presión 31 a 34 se define como una señal P\$\$R. No obstante, \$\$ significa la rueda de control (FL, FR, RL, RR) y por ejemplo, una señal PFLH es una señal que notifica el estado de accionamiento de la válvula de control de aumento de la presión 22 cuando la rueda de control es la rueda RL 2. Además, las señales Q4, Q14 en la figura son respectivamente una de una pluralidad de señales de reloj puestas a la salida desde el circuito de oscilación interna 75 y una señal Q4 es una señal de reloj generada en un momento anterior al de la señal Q14.

(1) Se supone que el microordenador 60 está funcionando en el estado normal.

La señal fABS que notifica el estado de control del ABS llega a ser de nivel bajo cuando el control del ABS no se lleva a cabo. Por lo tanto, un circuito AND 401 pone a la salida un nivel alto que corresponde a una subida del pulso de la señal Q4, mientras que un circuito AND 402 pone a la salida un nivel bajo sin relación con la señal Q14.

Por lo tanto, un circuito OR 403 al que las salidas de los circuitos AND 401, 402 se introducen pone a la salida un nivel alto que depende de la subida del pulso de la señal Q4. Además, un contador 404 pone a la salida un nivel bajo porque la cuenta no se realiza recibiendo la señal fRES desde la unidad de control del reinicio 77 en el momento de la inicialización. Por lo tanto, un circuito AND 405 pone a la salida un nivel alto en base a la salida de nivel alto desde el circuito OR 403, es decir, dependiendo de la subida del pulso de la señal Q4. Por ello, el contador 404 ejecuta la cuenta.

Cuando la rueda de control no está en el estado de control del ABS, la señal de accionamiento del solenoide P\$\$H de las válvulas de control de aumento de la presión 21 a 24 de la rueda de control y la señal de accionamiento del solenoide P\$\$R de las válvulas de control de disminución de la presión 31 a 34 llegan a ser de nivel bajo y la salida del circuito AND 406 llega a ser de nivel alto. Por lo tanto, no en el estado de control del ABS, la señal de salida CRES del circuito OR llega a ser de nivel alto durante el periodo hasta el final de la cuenta del contador 404 y por ello el contador 404 se reinicia.

Mientras tanto, en el estado de control del ABS, la señal fABS que notifica el estado de control del ABS llega a ser de nivel alto. Por lo tanto, el circuito AND 402 pone a la salida el nivel alto dependiendo de la subida del pulso de la señal Q14 y el circuito AND 401 pone a la salida el nivel bajo sin relación con la señal Q4

Por lo tanto, el circuito OR 403 al que se introducen las salidas de los circuitos AND 401, 402 ponen a la salida el nivel alto dependiendo de la subida del pulso de la señal Q14. Dado que el contador 404 pone a la salida el nivel bajo en el momento de la inicialización, el circuito AND 405 pone a la salida el nivel alto en base a la salida de nivel alto desde el circuito OR 403, es decir, sube el pulso de la señal Q14. Por ello, el contador 404 inicia la operación de contar.

Por otra parte, cuando la rueda de control está en el estado de control del ABS, la señal de accionamiento del solenoide P\$\$H de las válvulas de control de aumento de la presión 21 a 24 de la rueda de control y la señal de accionamiento P\$\$R de las válvulas de control de disminución de la presión 31 a 34 se invierten respectivamente al nivel alto y nivel bajo considerando los intervalos de incremento y disminución de la presión del control del ABS y por ello también se invierte una salida del circuito AND 406 al nivel alto y nivel bajo.

Por lo tanto, incluso en el estado de control del ABS, la señal de salida CRES del circuito OR llega a ser de nivel alto durante el periodo hasta el final de la cuenta del contador 404 y por ello el contador 404 se reinicia.

50

5

10

15

20

25

30

35

40

45

(2) Se supone a continuación que el microordenador 60 está funcionando en el estado anormal.

Por ejemplo, cuando la señal (es decir, cualquiera de la señal P\$\$H, la señal P\$\$R está de nivel alto) que notifica el accionamiento del solenoide de las válvulas de doble posición 21 a 24, 31 a 34 que corresponden a la rueda de control mediante el microordenador 60 se pone a la salida incluso no en el estado de control del ABS, se supone que el resultado de la operación aritmética del microordenador 60 es errónea, provocando un fallo allí dentro.

5

10

15

25

30

35

40

45

50

55

En este caso, la señal fABS que notifica el estado de control del ABS llega a ser de nivel bajo y el contador 404 inicia la operación de cuenta que depende de la subida del pulso de la señal Q4 como se describió anteriormente.

Mientras tanto, la señal de accionamiento del solenoide P\$\$H de las válvulas de control de aumento de la presión 21 a 24 de la rueda de control y la señal de accionamiento del solenoide P\$\$R de las válvulas de control de disminución de la presión 31 a 34 se invierten a nivel alto y nivel bajo respectivamente en los intervalos de aumento y disminución de la presión del control del ABS y la salida del circuito AND 406 también se invierte al nivel alto y nivel bajo.

No obstante, dado que el contador 404 inicia la operación de contar con la subida del pulso de la señal Q4, inicia la cuenta más rápido que aquélla en el estado de control del ABS y por ello el contador 404 cuenta hasta el dígito final antes de que la salida del circuito AND 406 llegue a ser de nivel alto. Por lo tanto, se puede detectar un fallo del resultado de la operación aritmética del microordenador 60 a partir de la señal f\$\$NG puesta a la salida a partir del contador 404.

Cuando el intervalo de aumento de la presión no aparece incluso si el intervalo de incremento de la presión debería aparecer durante el control del ABS, por ejemplo, cuando el intervalo de aumento de la presión no aparece durante un periodo predeterminado, se supone que ocurre un fallo en la operación aritmética del microordenador 60.

En este caso, la señal fABS que notifica el estado de control del ABS llega a ser de nivel alto y el contador 404 también inicia la operación de cuenta que depende de la subida del pulso de la señal Q14 como se describió anteriormente.

Mientras tanto, cuando no hay intervalo de aumento de la presión del control del ABS, una salida del circuito AND 406 se mantiene a nivel bajo. Por lo tanto, incluso en este caso, se puede detectar un fallo del estado aritmético del microordenador 60 desde la señal f\$\$NG puesta a la salida desde el contador 404.

La Fig. 5B y la Fig. 5C ilustran los diagramas de temporización cuando el microordenador 60 está llevando a cabo la operación aritmética normal y no está llevando a cabo la operación aritmética normal, respectivamente.

Como se ilustra en la Fig. 5B, el contador 404 se reinicia siempre cuando el control del ABS no se ejecuta y el contador 404 se reinicia en el intervalo de disminución y aumento de la presión del control del ABS cuando se ejecuta el control del ABS. Como se ilustra en la Fig. 5C, si el intervalo de aumento de la presión no aparece incluso cuando el intervalo de aumento de la presión debería aparecer durante el estado de control del ABS, cuando el periodo Ta pasa, la señal f\$\$NG llega a ser de nivel alto. Además, cuando los solenoides de las válvulas de doble posición 21 a 24, 31 a 34 se accionan mientras que el control del ABS no se ejecuta, la señal f\$\$NG llega a ser de nivel alto después de que pase el periodo Tb.

En este circuito lógico, el periodo Tb se fija más corto que el periodo Ta para inhibir inmediatamente una salida del accionador de accionamiento del solenoide 90 debido a que se encuentra seguramente un fallo en el resultado de la operación aritmética del microordenador 60 cuando la señal de accionamiento del solenoide se pone a la salida en el periodo Tb incluso no en el estado de control del ABS. Como se describió anteriormente, ahora es posible monitorizar el resultado de la operación aritmética del microordenador usando el circuito lógico ilustrado en la Fig. 5A.

Un circuito lógico ilustrado en la Fig. 6A también es uno de los circuitos lógicos de monitorización del resultado de la operación aritmética para monitorizar el resultado de la operación aritmética del microordenador 60. Aquí se monitoriza si se accionan normalmente o no las válvulas de control de disminución de la presión 31 a 34 para la rueda de control bajo el control del ABS. A saber, incluso durante el estado de control del ABS, si el tiempo de disminución de la presión es demasiado largo, un conductor siente, incluso cuando el conductor pisa el pedal de freno abajo, un temor de insuficiente efectividad del freno. Por lo tanto, si el tiempo de disminución de la presión es demasiado largo, se define como que el microordenador 60 está en el estado de fallo.

Una señal Q10 ilustrada en la Fig. 6A es una de una pluralidad de señales de reloj puestas a la salida del circuito de oscilación interno 75. Cuando una salida de un circuito AND 500 llega a ser de nivel alto que corresponde a una subida del pulso de la señal Q10, un contador recibe esta salida de nivel alto para iniciar la operación de contar.

Cuando el periodo de disminución de la presión es normal, dado que la señal de accionamiento del solenoide P\$\$R de las válvulas de control de disminución de la presión 31 a 34 que corresponde a la rueda de control llega a ser de nivel bajo el contador 501 cuenta hasta el dígito final, una salida de un circuito OR 502 llega a

ser de nivel alto y por ello el contador 501 se reinicia. No obstante, si el periodo de disminución de la presión llega a ser excesivamente largo, el contador 501 cuenta hasta el dígito final antes de que la señal de accionamiento del solenoide P\$\$R de las válvulas de control de disminución de la presión 31 a 34 que corresponde a la rueda de control llegue a ser de nivel bajo. Por lo tanto, se puede detectar un fallo en el resultado de la operación aritmética del microordenador 60 a partir de la señal f\$\$RF puesta a la salida desde el contador 501.

5

10

15

20

25

30

35

40

45

50

55

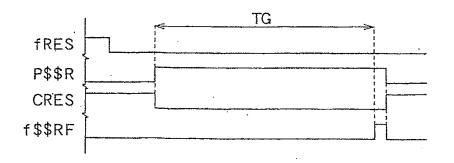

Las Fig. 6B y 6C ilustran los diagramas de tiempo cuando el periodo de disminución de la presión está en la longitud normal y está en la longitud excesivamente larga, respectivamente.

Como se ilustra en la Fig. 6B, cuando el periodo de disminución de la presión está en la longitud normal (más corta que el periodo  $T_G$  en la figura), la señal de salida CRES del circuito OR 502 llega a ser de nivel alto y la señal f\$\$RF no llega a ser de nivel alto antes de que el contador 501 cuente hasta el dígito final. Mientras tanto, como se ilustra en la Fig. 6C, cuando el periodo de disminución de la presión es excesivamente largo (más largo que un periodo  $T_G$  en la figura), dado que la señal de salida del circuito OR 502 es de nivel bajo hasta que el contador 501 cuente hasta el dígito final, la señal f\$\$RF llega a ser de nivel alto. Como se describió anteriormente, ahora es posible monitorizar el resultado de la operación aritmética del microordenador 60 usando el circuito lógico ilustrado en la Fig. 6.

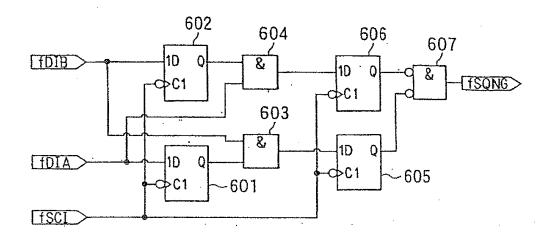

Un circuito lógico ilustrado en la Fig. 7A es un circuito lógico de monitorización de la secuencia para monitorizar la secuencia de los datos transmitidos desde el microordenador 60. Es decir, dado que se asume que la señal serie transmitida desde el microordenador 60 no se transmite exactamente si los datos que tienen el número de ID A y los datos que tienen el número de ID B no se reciben alternativamente, el microordenador 60 se asume que va a estar en el estado de fallo en este caso.

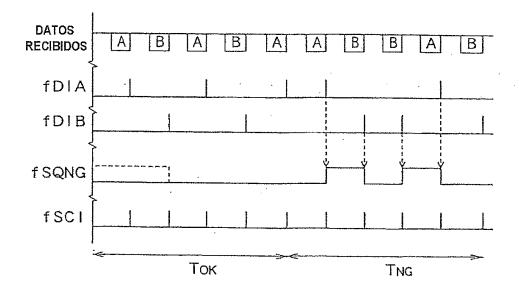

Como se ilustra en un periodo Tok en la Fig. 7B, se describirá la recepción alternativa de los datos que tienen el número de ID A y los datos que tienen el número de ID B.

Cuando se reciben los datos que tienen el número de ID A, la señal fSCI que notifica la recepción de una cierta señal y la señal fDIA que notifica la recepción del número de ID A llega a ser de nivel alto. Por lo tanto, una salida de un circuito biestable tipo D 601 llega a ser de nivel alto para almacenar que es introducida la señal fDIA.

Cuando se reciben los datos que tienen el número de ID B, la señal fSCI que notifica la recepción de una cierta señal y la señal fDIB que notifica la recepción del número de ID B llegan a ser de nivel alto. Por lo tanto, una salida de un circuito biestable tipo D 602 llega a ser de nivel alto para almacenar que es se introduce la señal fDIBA. Además, dado que el circuito biestable tipo D 601 ya ha puesto a la salida el nivel alto hasta este momento, una salida de un circuito AND 603 llega a ser de nivel alto cuando la señal fDIB llega a ser de nivel H. Es decir, el circuito AND 603 determina qué señales se reciben en la secuencia de la señal fDIA y la señal fDIB. Simultáneamente, una salida de un circuito biestable tipo D 605 llega a ser de nivel alto recibiendo la señal de nivel alto desde el circuito AND 603 y la señal de nivel alto fSCI y por ello el estado del circuito AND 603 se almacena. Cuando la señal fSCI llega a ser de nivel alto, la señal fDIA llega a ser de nivel bajo. Por lo tanto, una salida del circuito biestable tipo D 601 vuelve al nivel bajo.

Más tarde, cuando se reciben los datos que tienen un número de ID A, la señal fSCI y la señal fDIA llega a ser de nivel alto como se describió anteriormente. Por lo tanto, una salida del circuito biestable tipo D 601 se fija al nivel alto para almacenar que la señal fDIA es introducida. Además, dado que el circuito biestable tipo D 602 pone a la salida el nivel alto, una salida de un circuito AND 604 llega a ser de nivel alto cuando la señal fDIA llega a ser de nivel alto. Es decir, el circuito AND 604 determina la recepción de las señales en la secuencia de la señal fDIB y la señal fDIA. Simultáneamente, una salida de un circuito biestable tipo D 606 llega a ser de nivel alto recibiendo la salida de alto nivel desde el circuito AND 604 y la señal de nivel alto fSCI para almacenar el estado del circuito AND 604. Aquí, dado que la señal fDIB es de nivel bajo cuando la señal fSCI llega a ser de nivel alto, una salida del circuito biestable tipo D 602 vuelve al nivel bajo.

Por lo tanto, cuando se reciben los datos en la secuencia de la señal fDIA y a continuación la señal fDIB, una salida del circuito biestable tipo D 605 llega a ser de nivel alto y cuando se reciben los datos en la secuencia de la señal fDIB y a continuación la señal fDIA, una salida de un circuito biestable tipo D 606 llega a ser de nivel alto. Por lo tanto, cuando se reciben dos datos alternativamente, una salida de un circuito AND 607 llega a ser de nivel bajo.

Por otra parte, cuando se reciben los datos que tienen el número de ID A continuamente como el periodo T<sub>NG</sub> de la Fig. 7B, después de que la señal fDIA llega a ser de nivel alto y a continuación la señal fDIA llega a ser de nivel alto más tarde. Además, cuando se reciben continuamente los datos que tienen el número de ID B, la señal fDIB llega a ser de nivel alto y a partir de entonces la señal fDIB llega a ser de nivel H más tarde. Por lo tanto, ambas salidas del circuito AND 603 y el circuito AND 604 llegan a ser de nivel bajo.

Por consiguiente, las salidas de los circuitos biestables tipo D 605 y 606 llegan a ser de nivel bajo y la señal fSQNG puesta a la salida desde el circuito AND 607 llega a ser de nivel alto para detectar un fallo en la secuencia de transmisión de datos del microordenador 60 a partir de la señal fSQNG. Como se describió anteriormente, es posible monitorizar la secuencia del microordenador 60 usando el circuito lógico de la Fig. 7A.

Como se describió anteriormente, se pueden hacer varias operaciones de monitorización, tales como la monitorización de un fallo del resultado de la operación aritmética del intervalo de las operaciones aritméticas del microordenador 60 y la monitorización de la secuencia de los datos transmitidos desde el microordenador 60 a través de la comunicación de los datos desde el microordenador 60.

5 Como se describió anteriormente, se puede monitorizar fácilmente un fallo del microordenador 60 incluso si no se proporcionan dos microordenadores monitorizando si la comunicación de datos desde el microordenador 60 se ejecuta ciertamente o no o si el contenido de los datos transmitidos es o no exacto a través de la comunicación de los datos al IC periférico 70 desde el microordenador 60. Además, dado que se pueden realizar varias operaciones de monitorización a través de la comunicación de los datos desde el microordenador 60, se puede 10 lograr suficiente capacidad de monitorización en comparación con la operación de monitorización de WD.

Por lo tanto, se puede monitorizar fácil y efectivamente un fallo del microordenador 60 en base a la comunicación de los datos al IC periférico 70 desde el microordenador 60 y además se puede monitorizar el microordenador 60 con una estructura de más bajo coste.

El resultado de la monitorización de la unidad monitora de la señal serie 74 se transmite a la unidad de generación de la señal de inhibición de accionamiento 78 directamente o cuando la señal que notifica un fallo del microordenador 60 continúa durante un periodo predeterminado o durante una pluralidad de tiempos. Tras la recepción de este resultado de monitorización, la unidad de generación de la señal de inhibición de accionamiento 78 pone a la salida la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor.

#### (Segunda realización)

En la realización anterior, se ha descrito la comunicación en un sentido para la comunicación de los datos al IC periférico 70 desde el microordenador 60 pero esta realización explicará la comunicación en los dos sentidos que incluve la comunicación de los datos al microordenador 60 desde el IC periférico.

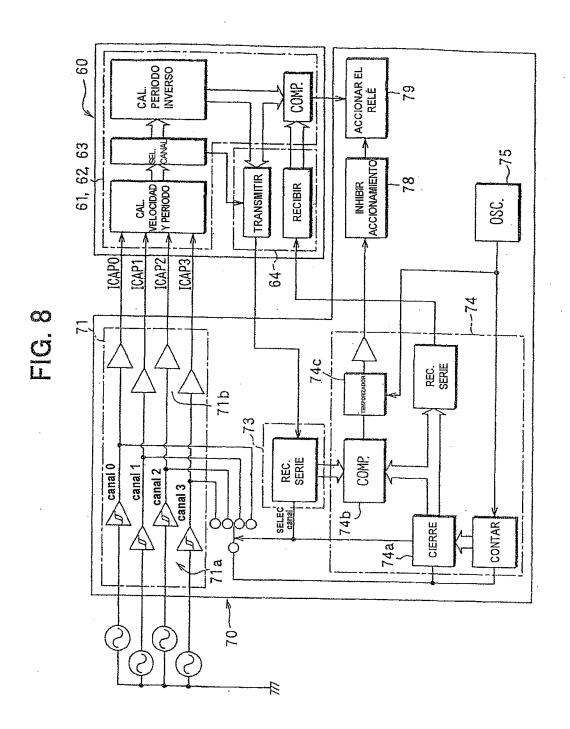

En esta realización, como ejemplo de comunicación en los dos sentidos, se describirá el método de 25 monitorización de la operación aritmética de la velocidad de la rueda llevada a cabo por el microordenador 60. La Fig. 8 ilustra una ECU para el control del ABS que va a ser usado para monitorizar las operaciones aritméticas de la velocidad de la rueda.

Cuando se introduce la señal de la velocidad de la rueda desde cada rueda 1 a 4 al almacenamiento temporal de entrada de la velocidad de la rueda 71 del IC periférico 70, la señal de la velocidad de la rueda de entrada se convierte a la forma de onda rectangular después de la cancelación de ruido mediante una unidad de conversión de onda rectangular 71a. Esta señal de la velocidad de la rueda convertida a la forma de onda rectangular se introduce al microordenador 60 a través del almacenamiento temporal 71b. El almacenamiento temporal 71b aísla la señal sacada al microordenador 60 a partir el pulso contado de la señal en el IC periférico 70.

El periodo de la señal de velocidad de la rueda introducido desde el microordenador 60 se mide y el resultado se convierte a los datos de la velocidad de la rueda para usar como el parámetro de control del sistema. Por otra parte, el microordenador 60 y el IC periférico 70 ejecuta el siguiente procesamiento para monitorizar la conversión normal a los datos de la velocidad de la rueda del microordenador 60.

(1) El microordenador 60 selecciona un canal (CH) de la rueda que va a ser monitorizada. Además, también ejecuta inversamente la operación aritmética durante un periodo de la señal de la velocidad de la rueda a partir de los datos de la velocidad de la rueda del canal seleccionado. Los datos del canal seleccionado y los datos del periodo calculado inversamente se transmiten al IC periférico 70 desde la unidad de comunicación serie 64.

(2) El IC periférico 70 mide el periodo del pulso rectangular convertido de la señal de la velocidad de la rueda seleccionada por los datos recibidos en serie del canal de selección con un circuito de medición del periodo 74d v asegura tales datos mediante un circuito de cierre 74a.

Los datos de cierre y los datos del periodo calculado inversamente y recibidos en serie se comparan si éstos están o no en el intervalo especificado con el circuito de comparación 74b. Cuando el resultado de la determinación no llega a ser normal dentro del periodo especificado de un temporizador 74c de la última etapa, el microordenador 60 determina la aparición de un fallo y transmite la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor a una unidad de accionamiento del relé 79 a través de una unidad de generación de la señal de inhibición de accionamiento 78.

Además, cuando se recibe la señal serie transmitida desde el IC periférico 70 por el microordenador 60, estos datos recibidos se comparan con los datos del periodo calculados inversamente. Si la diferencia especificada no se puede obtener dentro del periodo especificado, se define como un fallo del microordenador 60. Por ello la señal de inhibición de accionamiento del solenoide y la señal de inhibición de accionamiento del motor se transmiten a la unidad de accionamiento del relé 79.

20

15

30

35

40

45

55

Como se describió anteriormente, también es posible monitorizar si la medición del periodo y la operación aritmética de la rueda de velocidad se ejecuta exactamente o no tanto en el IC periférico 70 como en el microordenador 60 llevando a cabo la medición del periodo de la señal de la velocidad de la rueda tanto en el microordenador 60 como en el IC periférico 70.

En esta realización, se describen la medición del periodo y el cálculo de la velocidad de la rueda de la señal de velocidad de la rueda pero también es posible monitorizar las señales distintas de la señal de velocidad de la rueda cuando varía periódicamente de la misma manera en esta realización.

#### (Otras realizaciones)

5

10

15

20

25

30

35

40

45

50

En la primera y segunda realizaciones descritas anteriormente, la comunicación de los datos desde el microordenador 60 se ejecuta con la comunicación serie, pero tal comunicación de datos también se puede realizar con la comunicación paralelo.

Además, en las realizaciones primera y segunda anteriores, como se ilustra en la Fig. 2, se construye un circuito integrado con una pluralidad de pastillas, pero la estructura ilustrada en la Fig. 2 no siempre se requiere y cualquiera de una pluralidad de pastillas o todas las pastillas pueden estar formadas de una pastilla. En este caso, la parte para llevar a cabo el cálculo para el control corresponde al microordenador 60 y la parte asignada en el área periférica corresponde al IC periférico 70.

Además, en la primera realización, se describe la comunicación en un sentido para la comunicación de datos al IC periférico 70 desde el microordenador 60 y la comunicación en dos sentidos también es posible como se describió en la segunda realización. Por ejemplo, también es posible transmitir el resultado de la operación de monitorización en la unidad monitora de la señal serie 74 al microordenador 60.

Además, en la primera realización, se ha descrito en cuanto a si el cálculo para el control del ABS se lleva a cabo normalmente o no. No obstante, en el caso de la ECU usada para el aparato de freno que consta de una función de asistencia de freno, también se puede monitorizar si el microordenador 60 ejecuta normalmente el cálculo para la función de asistencia de freno o no. Por ejemplo, para la estructura ilustrada en la Fig. 1, se puede aplicar la primera realización a la ECU adaptada al aparato de freno que comprende las tuberías para conectar el cilindro maestro 16 o el depósito maestro y los laterales del puerto de entrada de las bombas 45a, 45b y las válvulas de control entre cada puerto del cilindro maestro y las válvulas de doble posición 21 a 24.

La Fig. 9a ilustra un circuito lógico usado para monitorizar si el cálculo para la función de asistencia de freno se lleva a cabo normalmente o no. Las Fig. 9B y 9C ilustran los diagramas de tiempo durante la operación de este circuito lógico.

Las señales Q4, Q14 ilustradas en esta figura son similares a aquélla de la Fig. 5A. Además, unos circuitos AND 801, 802, circuito OR 803, contador 804, circuito AND 805 para el procesamiento de las señales Q4, fABS, Q14 funcionan de la misma manera que los circuitos AND 401, 402, circuito OR 403, contador 404 y circuito AND 405 de la Fig. 5A.

(1) Cuando no se ejecuta el control de asistencia de freno, una señal PBA que notifica el estado del control de asistencia de freno, es decir, una señal de accionamiento del solenoide de las válvulas de control que se acciona durante la operación de asistencia de freno llega a ser de nivel bajo. Por ello, una salida del circuito OR 806 llega a ser de nivel alto. Por lo tanto, una señal de salida CRES del circuito OR 806 llega a ser de nivel alto durante el periodo hasta el final de la operación de contar del contador 804 y por ello el contador 804 se reinicia.

Por otra parte, cuando se ejecuta el control de asistencia de freno, se lleva a cabo un frenado instantáneo bajo el estado de control del ABS y por ello el contador 804 inicia la operación de contar en el intervalo de subida del pulso de la señal Q14. Dado que se ejecuta el control de asistencia de frenado, la señal PBA llega a ser de nivel alto pero la señal fBA llega a ser de nivel bajo y el contador 804 se reinicia debido a que el vehículo normalmente para si el control de asistencia de freno se lleva a cabo durante un cierto periodo de tiempo.

(2) Por ejemplo, si el control de asistencia de freno no se cancela incluso cuando el vehículo para, por ejemplo, con el control de asistencia de freno y el control del ABS, el control del ABS todavía continúa y por lo tanto el contador 804 realiza la operación de contar en el intervalo de subida del pulso de la señal Q14. Además, dado que se ejecuta el control de asistencia de freno, la señal PBA llega a ser de nivel alto. Dado que el control de asistencia de freno no está aún cancelado, la señal PBA se mantiene en el nivel alto y el contador 804 no se reinicia. Por lo tanto continúa la operación de contar hasta el dígito final.

Además, cuando el control de asistencia de freno no continúa incluso en el estado de control del ABS, dado que el control del ABS no es eficaz, el contador 804 ejecuta la operación de cuenta en el intervalo de subida del pulso de la señal Q4. Es decir, se ejecuta la operación de cuenta a la velocidad más alta que aquélla en el estado de control del ABS. Por lo tanto, cuando la señal PBA que notifica que el estado de control de asistencia de freno llega a ser de nivel alto, el contador 804 cuenta hasta el dígito final antes de que la señal PBA llegue a ser de bajo nivel.

Con referencia a las Fig. 9B y 9C, cuando la señal PBA llega a ser de nivel bajo normalmente durante el periodo T<sub>BA1</sub> bajo el estado de control del ABS como se ilustra en la Fig. 9B, la señal de salida CRES del circuito OR 806 llega a ser de nivel alto y el contador 804 se reinicia. Si la PBA no llega a ser de nivel bajo como se ilustra en la Fig. 9C, el contador 804 no se reinicia. Por lo tanto, la señal fBA llega a ser de nivel alto.

Además, cuando la señal PBA llega a ser de nivel alto durante el periodo T<sub>BA2</sub> no en el estado de control del ABS, el contador 804 ejecuta rápidamente la operación de contar y por ello la señal fBA llega a ser de nivel alto. No obstante, cuando la señal PBA llega a ser de nivel alto debido al ruido durante el periodo T<sub>BA2</sub> como se ilustra en la Fig. 9B, la señal fBA no llega a ser de nivel alto porque la señal PBA vuelve rápidamente al nivel bajo.

Por lo tanto, se puede detectar un fallo del estado de la operación aritmética del microordenador 60 a partir de la señal fBA puesta a la salida del contador 804.

10

La presente invención no debería ser limitada a las realizaciones y modificaciones reveladas, si no que puede ser implementada de otras varias formas.

### **REIVINDICACIONES**

1. Una unidad de control que consta de:

un microordenador (60); en donde

la unidad de control se aplica como una unidad de control electrónico para un sistema de control de frenos;

el sistema de control de frenos que incluye las fuentes de generación de la presión del fluido de frenos (16, 27) para generar una presión del fluido de frenos, los medios para generar la fuerza de freno de la rueda (11 a 14) para recibir una presión del fluido de frenos desde la fuente de generación de la presión del fluido de frenos para generar una fuerza de freno respectivamente a cada rueda, las tuberías proporcionadas entre la fuente de generación de la presión del fluido de frenos y los medios de generación de la fuerza de freno de la rueda, y una pluralidad de válvulas de control (21 a 24, 31 a 34) proporcionadas en las tuberías;

una pluralidad de válvulas de control (21 a 24, 31 a 34) se controlan respectivamente en base a un resultado de operación aritmética del microordenador (60) para la aplicación al control de la presión del fluido de frenos aplicada a los medios de generación de la fuerza de freno de la rueda (11 a 14);

### caracterizada porque

15

20

25

30

35

40

45

la unidad de control además comprende

un IC periférico (70),

en donde el microordenador (60) se construye para transmitir los datos al IC periférico (70);

el IC periférico (70) se construye para monitorizar un fallo del microordenador (60) en base a los datos recibidos desde el microordenador (60);

en donde

una señal que notifica un fallo al microordenador (60) se pone a la salida cuando una señal para aumentar la presión del fluido de frenos aplicada a los medios de generación de la fuerza de freno de la rueda (11 a 14) no se pone a la salida durante un periodo predeterminado de los datos recibidos por el IC periférico (70) bajo el estado de control antibloqueo de frenos o cuando, si tal señal se pone a la salida, esta señal se superpone en la señal para disminuir la presión del fluido de frenos aplicada a los medios de generación de la fuerza de frenado de la rueda (11 a 14).

2. La unidad de control como en la reivindicación 1, en donde:

el microordenador (60) detecta que cualquier rueda está en un estado de tipo deslizamiento para realizar un control antibloqueo de frenos para restringir la rueda del estado de tipo deslizamiento accionando la pluralidad de las válvulas de control (21 a 24, 31 a 34) de la rueda y controlando el aumento o disminución de una presión del fluido de frenos aplicada a los medios de generación de la fuerza de freno de la rueda (11 a 14); y

una señal que notifica el fallo del microordenador (60) es puesta a la salida, cuando se detecta una señal para accionar cualquier válvula de la pluralidad de válvulas de control (21 a 24, 31 a 34) desde los datos recibidos por el IC periférico (70) bajo una condición de que ninguna rueda se detecta como en el estado de tipo deslizamiento.

3. La unidad de control como en la reivindicación 1 ó 2, en donde:

una señal para notificar un fallo del microordenador (60) se pone a la salida cuando se detecta a partir de los datos recibidos por el IC periférico (70) bajo el estado de control antibloqueo de frenos que la señal para disminuir la presión del fluido de frenos aplicada a los medios de generación de la fuerza de freno de la rueda (11 a 14) se pone a la salida durante un periodo determinado.

4. La unidad de control como en cualquiera de las reivindicaciones 1 a 3, en donde:

se proporciona un accionador (90) para accionar respectivamente la pluralidad de las válvulas (21 a 24, 31 a 34); y

el IC periférico (70) pone a la salida una señal para el accionador (90) para inhibir el accionamiento de la pluralidad de las válvulas de control (21 a 24, 31 a 34) cuando se detecta un fallo del microordenador (60).

5. La unidad de control como en cualquiera de las reivindicaciones 1 a 4, en donde:

5

se proporcionan primero los medios de conmutación (100a) para controlar respectivamente el estado de ENCENDIDO/APAGADO de un suministro de voltaje de la pluralidad de las válvulas de control (21 a 24, 31 a 34); y

el IC periférico (70) pone a la salida una señal a los primeros medios de conmutación (100a) para desactivar el suministro de voltaje a la pluralidad de las válvulas de control (21 a 24, 31 a 34) mediante los primeros medios de conmutación (100a) cuando se detecta el fallo del microordenador (60).

FIG. 2

FIG. 4A

FIG. 4B

FIG. 4C

## FIG. 5A

### FIG. 5B

## FIG. 5C

FIG. 6A

# FIG. 6B

# FIG. 6C

FIG. 7A

FIG. 7B

### FIG. 9B

FIG. 9C