OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

Número de publicación: 2 359 919

(51) Int. Cl.:

H01L 21/48 (2006.01)

| $\overline{}$ | ,                             |

|---------------|-------------------------------|

| 12)           |                               |

| 12)           | TRADUCCIÓN DE PATENTE EUROPEA |

| 1-/           |                               |

Т3

- 96 Número de solicitud europea: 07726978 .5

- 96 Fecha de presentación : 16.03.2007

- 97 Número de publicación de la solicitud: 2002471 97 Fecha de publicación de la solicitud: 17.12.2008

- (54) Título: Interconexión de dispositivos electrónicos con conductores elevados.

- (30) Prioridad: 16.03.2006 IT MI06A0478

(73) Titular/es:

ELES SEMICONDUCTOR EQUIPMENT S.p.A. Fraz. Pian di Porto Zona Ind. le Bodoglie, 148/1/Z 06059 Todi, Perugia, IT RISE TECHNOLOGY S.R.L.

- Fecha de publicación de la mención BOPI: 30.05.2011

- (2) Inventor/es: Balucani, Marco

- (45) Fecha de la publicación del folleto de la patente: 30.05.2011

- (74) Agente: Curell Aguilá, Marcelino

ES 2 359 919 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## **DESCRIPCIÓN**

## **CAMPO TÉCNICO**

La presente invención se refiere en general al campo de la electrónica. Más en particular, la presente invención se refiere a la interconexión de dispositivos electrónicos.

5

## **ANTECEDENTES**

Los dispositivos electrónicos deben interconectarse generalmente entre sí, con el fin de llevar a cabo una serie de tareas. Un ejemplo es un módulo multichip (MCM), en el que una pluralidad de circuitos integrados en chips correspondientes de materiales semiconductores se empaquetan en un único montaje electrónico. Otro ejemplo es una tarjeta de sonda, que se utiliza para poner en contacto circuitos integrados a nivel de oblea para ponerlos a prueba.

10

Se han propuesto varias soluciones para conseguir el resultado deseado. En particular, una técnica específica conocida en la técnica se basa en la elevación de conductores flexibles, véase, por ejemplo, la patente US nº 5.763.941.

Por ejemplo, el documento EP-A-0 352 020 da a conocer un sistema para interconectar múltiples chips por

Una variación de la misma técnica se propone en el documento EP-A-0 870 325. En este caso, se emplea una

15

medio de un soporte semiconductor. Para ello, se conectan unas pastillas conductoras de cada chip a unas partes texturizadas correspondientes de unas pastillas conductoras previstas sobre el soporte (enfrentadas entre sí). Con el fin de aumentar la adaptabilidad mecánica de la estructura obtenida de este modo, el documento EP-A-0 352 020 enseña a disponer una capa localizada de material aislante entre cada chip y una parte de sus pastillas; el material aislante se selecciona para presentar relativamente poca o ninguna adhesión con las pastillas de chip. El chip se presiona contra el

20

soporte, conectando de este modo las partes de las pastillas de chip que se apoyan sobre el material aislante a las pastillas de soporte correspondientes; el chip se levanta entonces ligeramente para separarlo del soporte (por ejemplo, 2 mm). De esta manera, las pastillas de chip se desprenden de la capa aislante, extendiéndolas de ese modo entre el chip y el soporte (con el material aislante que también puede retirarse en el extremo). La estructura propuesta en el

capa que puede retirarse para facilitar la elevación de los conductores. Más específicamente, los conductores se forman

documento EP-A-0 352 020 permite resistir los esfuerzos provocados por tensiones mecánicas o térmicas.

25

sobre una lámina de múltiples capas (que consiste en una lámina dieléctrica intercalada entre dos capas de metal): cada conductor está conformado como una tira, que se extiende entre un extremo de punta y un extremo terminal. La capa de metal bajo los conductores se graba entonces, para separar las tiras de la lámina dieléctrica. Sin embargo, el extremo de punta de cada conductor es ligeramente más grande que su tira, de modo que el procedimiento de grabado deja un pequeño botón bajo el mismo; este botón proporciona una adhesión muy pequeña del extremo de punta a la capa

30

35

dieléctrica (justo lo suficientemente fuerte para retener el extremo de punta contra las fuerzas gravitacional y de aceleración en la manipulación normal). Por otro lado, el extremo terminal de cada conductor es mucho más grande, de tal modo que el mismo procedimiento de grabado deje un botón más grande bajo el mismo; este botón fija de manera segura el extremo terminal a la lámina de múltiples capas (conectando al mismo tiempo el conductor, a través de un orificio pasante, a un terminal correspondiente formado en su superficie opuesta). El componente obtenido de este modo está alineado con una oblea, y los extremos de punta están unidos a contactos correspondientes de la oblea. Tal como

entre las mismas (con los extremos de punta de los conductores que se desprenden fácilmente de la lámina de múltiples

capas)

En cualquier caso, los conductores utilizados en elementos de interconexión se protegen generalmente mediante un material dieléctrico (preferentemente del tipo elástico). Por ejemplo, el documento US-A-3.795.037 da a conocer un conector con conductores resilientes, que están incrustados en un material elastomérico: la estructura obtenida de este modo permite conectar dispositivos electrónicos, sin requerir ningún control preciso de los ocho conductores. El conector se produce definiendo los conductores en una serie de marcos (por ejemplo, mediante fresado químico). A continuación, se forma una pila formada por múltiples marcos con separadores interpuestos, y se sujeta entre dos placas. En este punto, se invecta un líquido elastomérico en la cavidad definida por las placas, y se cura; al final, las placas se retiran para obtener la estructura deseada.

se ha expuesto anteriormente, la lámina de múltiples capas y la oblea están separadas, para extender los conductores

45

40

La misma técnica se aplica también en el documento EP-A-0 870 325 mencionado anteriormente. En este caso (tras haber extendido los conductores), se inyecta un material fluido entre la lámina de múltiples capas y la oblea, para llenar el espacio disponible y para penetrar entre todos los conductores. Tal como se ha expuesto anteriormente, el material se cura entonces para incrustar los conductores en una capa dieléctrica elástica.

50

Sin embargo, las soluciones conocidas en la técnica no son completamente satisfactorias. De hecho, estas técnicas son relativamente complejas; por ejemplo, requieren la utilización de capas de sacrificio que afectan de manera adversa a los procedimientos de fabricación correspondientes.

55

Además, es muy difícil obtener un nivel aceptable de calidad. Por ejemplo, en la estructura dada a conocer en el documento EP-A-0 352 020 las pastillas de chip pueden desprenderse fácilmente del material aislante (antes de su conexión al soporte). Por otro lado, en el documento EP-A-0 870 325 se requiere una precisión muy elevada para obtener el tamaño correcto de los botones bajo los extremos de punta; de hecho, el procedimiento de fabricación correspondiente debe controlarse perfectamente para garantizar que los extremos de punta se retienen por la lámina de múltiples capas (antes de su conexión a la oblea), pero al mismo tiempo se desprenden fácilmente cuando deben extenderse los conductores.

5 <u>SUMARIO</u>

20

25

30

35

40

En general, la presente exposición se basa en la idea de tratar un sustrato en el que se forman los conductores.

En particular, diferentes aspectos de la invención proporcionan una solución tal como se expone en las reivindicaciones independientes. Formas de realización ventajosas de la invención se describen en las reivindicaciones subordinadas.

Más específicamente, un aspecto de la invención propone un procedimiento de fabricación de un elemento de interconexión (para poner en contacto dispositivos electrónicos). El procedimiento comienza con la etapa de formación de una pluralidad de conductores sobre una superficie principal de un primer sustrato; cada conductor presenta un primer extremo y un segundo extremo. El segundo extremo de cada conductor está acoplado con un segundo sustrato. El segundo sustrato y el primer sustrato se separan entonces entre sí, para extender los conductores entre el primer sustrato y el segundo sustrato. El procedimiento también incluye la etapa de tratamiento de la superficie principal antes de formar los conductores para controlar una adhesión de los conductores sobre la superficie principal.

En una forma de realización de la invención, este resultado se consigue por medio de una o más regiones de promoción de la adhesión sobre la superficie principal.

Preferentemente, estas regiones de promoción de la adhesión están realizadas en silicio poroso.

Una manera para mejorar adicionalmente la solución es reducir la porosidad de las regiones de silicio poroso a medida que se aleja de la superficie principal.

Además, se propone un intervalo sugerido de la porosidad.

Este resultado puede conseguirse reduciendo una densidad de corriente de un procedimiento anódico correspondiente en el tiempo.

También se sugiere un intervalo de la densidad de corriente.

En una puesta en práctica específica, las regiones de promoción de la adhesión se forman de manera selectiva en cada zona de contacto entre un conductor correspondiente y la superficie principal.

Una manera de mejorar adicionalmente la solución es reducir la adhesión a medida que se mueve desde el primer extremo hasta el segundo extremo de cada conductor.

También se propone un intervalo sugerido de esta variación.

Particularmente, el resultado deseado puede conseguirse reduciendo una concentración de las regiones de promoción de la adhesión.

Opcionalmente, es posible depositar una capa de metal sobre las regiones de silicio poroso.

Normalmente, se inyecta un material aislante fluido entre los dos sustratos y entonces se cura, para obtener una capa aislante correspondiente en la que estén incrustados los conductores.

En una forma de realización de la invención, los primeros extremos de los conductores se forman en ranuras correspondientes del primer sustrato.

Ventajosamente, los conductores están realizados en un material duro en las ranuras y de un material dúctil en otras partes.

También se propone una definición cuantitativa sugerida de estos materiales. Normalmente, entonces se elimina el primer sustrato.

Para ello, es posible emplear un procedimiento de grabado en húmedo hasta que se alcanza una capa de parada, seguido entonces por un procedimiento de grabado en seco.

En una forma de realización particular de la invención, se retira una parte de la capa aislante entre los dos sustratos.

También se propone un intervalo sugerido de la cantidad de capa aislante que debe retirarse.

El segundo sustrato también puede eliminarse al final del procedimiento de fabricación.

Otro aspecto de la invención propone un procedimiento de fabricación de un montaje electrónico basado en este elemento de interconexión.

Un aspecto adicional de la invención propone un procedimiento de fabricación de una tarjeta de prueba, basado en el mismo elemento de interconexión.

Un aspecto diferente de la invención propone un elemento de interconexión correspondiente.

Otro aspecto de la invención propone un montaje electrónico correspondiente.

Un aspecto adicional de la invención propone una tarjeta de prueba correspondiente.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

La propia invención, así como características adicionales y las ventajas de la misma, se comprenderán mejor 10 haciendo referencia a la siguiente descripción detallada, proporcionada únicamente a título de indicación no limitativa, para ser interpretada junto con los dibujos adjuntos. A este respecto, se entiende expresamente que las figuras no están necesariamente dibujadas a escala y que, a menos que se indique lo contrario, están concebidas únicamente para ilustrar conceptualmente las estructuras y los procedimientos descritos en la presente memoria. Particularmente:

las figuras 1a-1g muestran las diversas fases de un procedimiento de fabricación de un elemento de interconexión según diferentes formas de realización de la invención;

las figuras 2a-2b detallan una fase de este procedimiento de fabricación según unas formas de realización específicas de la invención;

las figuras 3a-3b son unas representaciones gráficas de un montaje electrónico según diferentes formas de realización de la invención; y

las figuras 4a-4f muestran las diversas fases de un procedimiento de fabricación de una tarjeta de prueba según diferentes formas de realización de la invención.

# **DESCRIPCIÓN DETALLADA**

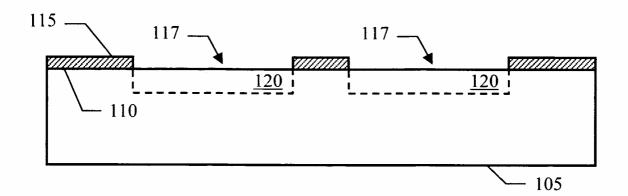

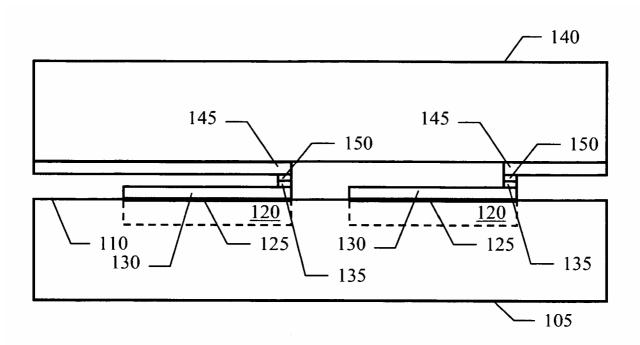

Haciendo referencia a continuación a las figuras 1a-1g, se ilustran las diversas fases de un procedimiento para fabricar un elemento de interconexión según diferentes formas de realización de la invención.

Considerando en particular la figura 1a, el procedimiento de fabricación comienza con una oblea de silicio monocristalino 105. Tal como se describe en detalle a continuación, la oblea 105 presenta un sustrato inferior para conductores de interconexión; más específicamente, los conductores están formados sobre una superficie frontal (principal) 110 del sustrato inferior 105 y a continuación se elevan.

Para ello, se forma una máscara fotorresistente 115 encima de la superficie frontal 110. La máscara fotorresistente 115 se obtiene depositando una capa de material fotorresistente y formando a continuación un patrón en el mismo a través de un procedimiento fotolitográfico; de esta manera, se abren múltiples ventanas en el material fotorresistente para exponer zonas de contacto correspondientes 117 de la superficie frontal 110 para los conductores deseados. Las zonas de contacto 117 pueden presentar cualquier forma y tamaño (según los conductores que vayan a formarse). Por ejemplo, cada conductor consiste en una tira alargada (tal como con una longitud de 0,1 a 150 mm y una anchura de 0.5 a 100 um). La tira puede ser recta, de tipo espiral, de tipo helicoidal, ondulada, etc.; además, la tira puede terminar con una o dos regiones ampliadas (tal como con una sección cuadrada, rectangular o circular).

El tipo de material fotorresistente que se utiliza depende del espesor de los conductores (tal como desde 1 µm hasta 500 µm). Por ejemplo, cuando los conductores presentan un espesor inferior a 50-80 µm, puede utilizarse cualquier tipo de material fotorresistente (ya sea positivo o negativo). A la inversa, cuando el espesor de los conductores es superior, es preferible utilizar un material fotorresistente negativo; de hecho, este material fotorresistente permite obtener ventanas con una razón aumentada entre su altura y anchura (hasta 50). Debe observarse que, cuando el espesor de los conductores es elevado, el material fotorresistente se deposita generalmente en dos fases (tal como por medio de un procedimiento de rotación). Se realizaron pruebas experimentales con diferentes materiales fotorresistentes. Por ejemplo, se utilizó el producto fotorresistente positivo AZ9260 para hacer conductores con una anchura de 5 µm y un espesor de 3 a 10 µm, y con una anchura de 10 µm y un espesor de 3 a 25 µm; en su lugar se utilizó el producto fotorresistente negativo SU-8 para fabricar conductores con una anchura de 10 µm y un espesor de

En la solución según una forma de realización de la presente invención, tal como se describe en detalle a continuación, se trata la superficie frontal 110 para controlar una adhesión de los conductores que se formarán sobre la misma.

De esta manera, es posible evitar cualquier desprendimiento no deseado de los conductores desde el sustrato inferior 105 (durante su formación o durante las siguientes fases del procedimiento de fabricación); al mismo tiempo,

40

5

15

20

25

30

35

45

esto no impide la elevación de los conductores desde el sustrato inferior 105 cuando sea necesario.

5

10

15

20

25

30

35

45

Debe observarse que el resultado deseado se consigue de una manera muy sencilla; particularmente, la solución propuesta no requiere ninguna capa de sacrificio (con un efecto beneficioso sobre la complejidad del procedimiento de fabricación).

Además, de esta manera es posible proporcionar un nivel mejorado de calidad; de hecho, la operación de tratar la superficie frontal 110 puede controlarse con una elevada precisión, para alcanzar la adhesión deseada con los conductores.

Los elementos de interconexión obtenidos de este modo proporcionan una elevada densidad de los conductores, incluso cuando son relativamente largos (tal como hasta 150 mm). Por ejemplo, es posible conseguir aproximadamente 5.000 conductores/cm $^2$  o 12.500 conductores/cm $^2$  en elementos de interconexión con un espesor de 1 mm y 0,4 mm, respectivamente (utilizando conductores con una anchura de 10  $\mu$ m). Además, la densidad de los conductores puede aumentarse adicionalmente reduciendo su anchura; por ejemplo, utilizando conductores con una anchura de 3  $\mu$ m es posible aumentar la densidad de los conductores en un factor superior a 3.

En una puesta en práctica específica, el control deseado de la adhesión de los conductores se consigue formando una capa de silicio poroso. Por ejemplo, el silicio poroso se forma en unas regiones 120 que se extienden desde las zonas de contacto 117 hasta el interior del sustrato inferior 105 (tal como con una profundidad de 0,1-5 µm). Para ello, el sustrato inferior 105 se somete a un procedimiento anódico. Particularmente, el sustrato inferior 105 se utiliza como ánodo en una celda electroquímica (que incluye un electrolito que es rico en ácido fluorhídrico, o HF). Cuando la densidad de corriente del procedimiento anódico es inferior a un valor crítico J<sub>PS</sub> (dependiendo de múltiples factores experimentales), el electrolito sólo reacciona con los orificios que alcanzan la superficie frontal 110 del sustrato inferior 105 (de manera que la reacción está limitada por la alimentación de los orificios y no por su difusión iónica al interior del electrolito). Naturalmente, esto requiere la disponibilidad de orificios (libres) en la superficie frontal 110. La disponibilidad de orificios es obvia si el sustrato inferior 105 es del tipo P. A la inversa, si el sustrato inferior 105 es del tipo N la superficie de contacto silicio-electrolito actúa como unión Schottkly con polarización inversa (es decir, con una región de agotamiento cuya anchura disminuye a medida que aumenta la concentración de impurezas del sustrato inferior 105). Por tanto, cuando el sustrato inferior 105 presenta una alta concentración de impurezas (N+) los orificios libres en el sustrato inferior 105 pueden atravesar la barrera de potencial de esta unión mediante el efecto túnel cuántico-mecánico; a la inversa, es necesario proporcionar energía a los orificios para permitir su paso a través de la barrera de potencial (por ejemplo, iluminando la superficie frontal 110).

El silicio poroso obtenido de este modo presenta una estructura compleja con una red aleatoria de pequeños poros. Las características del silicio poroso dependen de su morfología, que a su vez está en función de diferentes parámetros del procedimiento anódico (por ejemplo, la duración, la concentración y el tipo de impurezas del sustrato inferior 105, la densidad de corriente, el tipo de electrolito, y similares). A este respecto, las características del silicio poroso que se aprovechan son las mecánicas. Las características mecánicas del silicio poroso dependen enormemente de su porosidad, que se define con respecto al silicio monocristalino como:

$$P\% = \left(1 - \frac{\rho_{PS}}{\rho_{Si}}\right)\%$$

siendo  $\rho_{PS}$  es la densidad del silicio poroso y siendo  $\rho_{Si}$  la densidad del silicio monocristalino (es decir, 2,3 g/cm³). La densidad del silicio poroso  $\rho_{PS}$  puede medirse aplicando la siguiente fórmula:

$$\rho_{PS} = \rho_{Si} - \frac{P_s - P_e}{S \cdot d}$$

en la que los valores P<sub>s</sub> (peso inicial del sustrato inferior 105 antes del procedimiento anódico), P<sub>e</sub> (peso final del sustrato inferior 105 tras el procedimiento anódico) y d (profundidad de las regiones de silicio poroso 120) pueden medirse, mientras que el valor S (extensión de las zonas de contacto 117) se conoce.

La porosidad P% puede controlarse cambiando uno o más parámetros del procedimiento anódico; para ello, es muy práctico actuar sobre la densidad de corriente. Por ejemplo, los siguientes resultados experimentales se obtuvieron con una oblea del tipo N+ que presentaba una resistividad de 0,01  $\Omega$ cm, oblea que se sumergió en un electrolito HF- $C_2H_5OH$  (con una concentración de HF en volumen del 32% y el 12%, respectivamente); el procedimiento anódico se realizó a temperatura ambiente, aplicando las siguientes densidades de corriente:

| Densidad de corriente | Concentración de HF, 32% en volumen | Concentración de HF, 12% en volumen |

|-----------------------|-------------------------------------|-------------------------------------|

| 5 mA/cm <sup>2</sup>  | -                                   | P% ≈ 60%                            |

| 10 mA/cm <sup>2</sup> | P% ≈ 32%                            | P% ≈ 64%                            |

| 20 mA/cm <sup>2</sup> | P% ≈ 36%                            | P% ≈ 70%                            |

| 30 mA/cm <sup>2</sup> | P% ≈ 40%                            | P% ≈ 76%                            |

| 40 mA/cm <sup>2</sup> | P% ≈ 43%                            | P% ≈ 83%                            |

| 50 mA/cm <sup>2</sup> | P% ≈ 47%                            | P% ≈ 90%                            |

La adhesión de los conductores a las zonas de contacto 117 aumenta con la porosidad P% de las regiones de silicio poroso 120 (puesto que el número de puntos de anclaje de los conductores al sustrato inferior 105 es superior). Por tanto, es posible obtener la adhesión deseada de los conductores (normalmente dependiendo de su tamaño) controlando simplemente la porosidad P% (es decir, modulando la densidad de corriente del procedimiento anódico). Por ejemplo, se sometieron a prueba satisfactoriamente regiones de silicio poroso 120 con una profundidad de 0,2  $\mu$ m y una porosidad P% del 32% a 80% para formar conductores con una anchura de 2 a 100  $\mu$ m y un espesor de 2 a 25  $\mu$ m (conductores que se retuvieron por el sustrato inferior 105 durante las siguientes fases del procedimiento de fabricación sin impedir su elevación cuando fuera necesario).

Como mejora adicional, la porosidad P% de las regiones de silicio poroso 120 se modula reduciéndola a medida que se aleja de las zonas de contacto 117. De esta manera, es posible presentar una porosidad P% superior en la superficie frontal 110 (para aumentar la adhesión de los conductores) y una porosidad P% inferior dentro del sustrato inferior 105 (para garantizar su integridad). Preferentemente, la porosidad P% disminuye desde el 40%-90% (tal como el 45%-80%, como el 55%) en la superficie frontal 110 hasta el 0%-70% (tal como el 20%-50%, como el 30%) en su profundidad máxima. Por ejemplo, se utilizaron regiones de silicio poroso 120 con una profundidad de 0,25  $\mu$ m y una porosidad P% de desde el 90% hasta el 40% para obtener una adhesión de 200 MPa para conductores que presentan una anchura de 20  $\mu$ m.

El resultado deseado puede conseguirse modulando simplemente la densidad de corriente en el tiempo durante el procedimiento anódico. Preferentemente, para ello la densidad de corriente se reduce desde un valor inicial hasta un valor final en el intervalo del 5%-20% el valor inicial, y todavía más preferentemente en el intervalo del 7%-15% el valor inicial (tal como el 10% del mismo). Por ejemplo, se consiguió una reducción de la porosidad P% de desde el 90% hasta el 50% modulando la densidad de corriente desde 50 mA/cm² hasta 5 mA/cm² (en un electrolito HF-C<sub>2</sub>H<sub>5</sub>OH con una concentración de HF en volumen del 12%).

Debe observarse que el procedimiento anódico también puede llevarse a cabo antes de formar la máscara fotorresistente 115 (para obtener una única capa de silicio poroso, no mostrada en la figura, que se extiende por todo el sustrato inferior 105). En este caso, sin embargo, la capa de silicio poroso debe protegerse antes de cualquier procedimiento fotolitográfico; de hecho, la mayor superficie expuesta por la capa de silicio poroso (debido a su porosidad) magnifica la tasa de grabado de las disoluciones alcalinas que se utilizan generalmente para desarrollar los materiales fotorresistentes. Por tanto, la capa de silicio poroso se sometería a un grabado significativo durante la formación de la máscara fotorresistente 115 (grabado que por el contrario es insignificante cuando el sustrato inferior 105 está realizado completamente en un silicio monocristalino). Con el fin de evitar este problema, es posible proporcionar una capa protectora (delgada) sobre la capa de silicio poroso; por ejemplo, una capa protectora con un espesor de tan sólo 0,1 µm es suficiente para impedir cualquier grabado no deseado de la capa de silicio poroso. La capa protectora está realizada en un metal (tal como níquel, cobre, paladio u oro), que se deposita sobre la capa de silicio poroso por medio de un procedimiento de galvanoplastia en una disolución ácida.

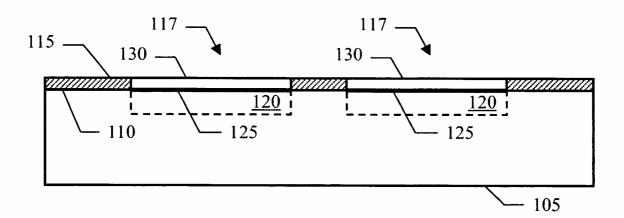

Haciendo referencia a continuación a la figura 1b, con el fin de aumentar la uniformidad de los conductores resultantes, se forma opcionalmente una capa precursora 125 sobre las zonas de contacto 117 (a través de las ventanas correspondientes de la máscara fotorresistente 115). Por ejemplo, la capa precursora 125 consiste en un metal (tal como cobre, oro o paladio), que se deposita por medio de un procedimiento no electrolítico. Particularmente, puede formarse una capa precursora 125 de cobre empleando una disolución en agua desionizada que incluye sulfato de cobre (para la deposición del cobre) y ácido fluorhídrico (para retirar cualquier óxido en los poros de las regiones de silicio poroso 120). Los resultados experimentales mostraron que es posible obtener una capa precursora 125 con un espesor que oscila desde 5 nm hasta 0,5 µm en 30 s, variando la concentración de sulfato de cobre desde 0,1 g hasta 10 g y la concentración de ácido fluorhídrico desde 1 ml hasta 10 ml por 100 ml de disolución (para tiempos de deposición más largos, el cobre depositado pasa a ser un polvo).

En este punto, se forman unos conductores 130 encima de la capa precursora 125. Normalmente, los conductores 130 consisten en una o más capas de metal, que se depositan por medio de un procedimiento de galvanoplastia. Por ejemplo, los conductores 130 están realizados en níquel, cobre, cromo, platino, plata, paladio, o cualquier aleación binaria y/o ternaria; alternativamente, los conductores 130 presentan una estructura de múltiples capas, tal como níquel-cobre-níquel, oro-cobre-oro o paladio-oro-níquel-cobre-níquel-oro-paladio. De esta manera, la corriente que se utiliza para implementar el procedimiento de galvanoplastia correspondiente pasa a través de las regiones de silicio poroso 120; como resultado, el metal se deposita dentro de los poros, para aumentar la adhesión de los conductores 130 al sustrato inferior 105.

Debe observarse que si las regiones de silicio poroso 120 no se protegían mediante la capa precursora 125, la deposición de los conductores 130 debía realizarse con una disolución ácida. Naturalmente, esto es necesario sólo para el primer procedimiento de deposición (cuando los conductores 130 presentan una estructura de múltiples capas). En cualquier caso, si ha de utilizarse una disolución alcalina para formar los conductores 130, es suficiente depositar una capa protectora delgada por adelantado con una disolución ácida (por ejemplo, que consiste en cobre o níquel y con un espesor de por lo menos 0,1 µm); esta capa protectora puede grabarse entonces al final del procedimiento (tras la retirada del sustrato inferior 105).

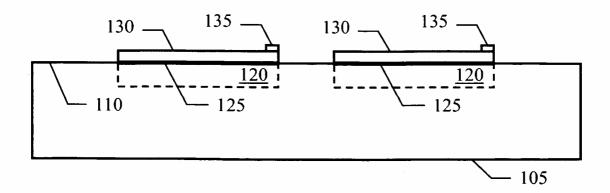

Tal como se muestra en la figura 1c, se forman un contacto de unión 135, que consiste en un material conductor, en un extremo de cada conductor 130. Por ejemplo, los contactos de unión 135 consisten en una aleación de soldadura (tal como SnPb, Sn, SnBi o SnAgCu); la aleación de soldadura se deposita de manera selectiva por medio de un procedimiento de galvanoplastia (a través de una máscara fotorresistente en la que se ha formado un patrón de manera adecuada), o por medio de un procedimiento de serigrafía. Alternativamente, es posible utilizar una pasta adhesiva, que se deposita por medio de un procedimiento de serigrafía. Además, los contactos de unión 135 pueden consistir en un metal (tal como oro y/o cobre); en este caso, los contactos de unión 135 se obtienen por medio de un procedimiento de película delgada o un procedimiento de galvanoplastia.

Continuando con la figura 1d, un sustrato superior 140, que consiste, por ejemplo, en otra oblea de silicio o una placa de circuito impreso (PCB), se utiliza para elevar los conductores 130. Para ello, se forman unas pistas conductoras 145 sobre una superficie inferior del sustrato superior 140 (enfrentado al sustrato inferior 105). Las pistas conductoras 145 están dotadas de un contacto de unión 150 para cada contacto de unión 135 del sustrato inferior 105; los contactos de unión 150 están realizados en el mismo material que los contactos de unión 135 (es decir, aleación de soldadura, pasta adhesiva o metal).

El sustrato superior 140 se coloca enfrente del sustrato inferior 105; los contactos de unión 150 se alinean con los contactos de unión 135, y entonces se conectan a los mismos. Para ello, es posible utilizar diferentes técnicas bien conocidas, por ejemplo, las empleadas comúnmente en el campo de las estructuras de silicio sobre aislante (SOI) o en el campo de las tecnologías MEMS. Cuando los contactos de unión 135 y 150 están realizados en metal, su conexión puede llevarse a cabo empleando máquinas de unión de oblea, que implementan un procedimiento de termocompresión o un procedimiento de soldadura anódica. Por ejemplo, si el metal es oro, es suficiente una temperatura de aproximadamente 200°C para obtener la soldadura oro-oro, mientras que si el metal es cobre se requiere una temperatura de aproximadamente 400°C para obtener la soldadura cobre-cobre. Por otro lado, cuando los contactos de unión 135 y 150 están realizados en soldadura o pasta adhesiva también es posible utilizar dos placas rectificadas simples que pueden soportar el sustrato inferior 105 y el sustrato superior 140 (por ejemplo, por medio de vacío o fuerza electrostática/magnética). Para ello, están disponibles comercialmente unas placas circulares o cuadradas con una alta planitud (por ejemplo, con un diámetro/lado de hasta 300 mm y un error de planitud inferior a 13 μm); estas placas pueden moverse de manera controlada con una precisión muy alta (del orden de algunos μm para movimientos de hasta 15-20 cm).

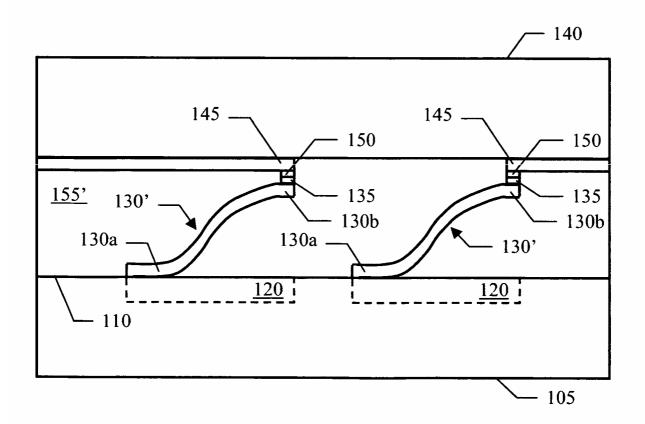

Una vez que los contactos de unión 150 se han soldado o pegado a los contactos de unión 135, el sustrato superior 140 y el sustrato inferior 105 se separan entre sí, tal como se muestra en la figura 1e. Para ello, las superficies libres opuestas del sustrato superior 140 y del sustrato inferior 105 se sujetan a placas planas correspondientes (por ejemplo, por medio de vacío o fuerza electrostática/magnética). Las placas se alejan entonces entre sí (normalmente, manteniendo una placa estacionaria y moviendo la otra). El movimiento presenta una componente vertical (perpendicular a la superficie frontal 110), para desplazar el sustrato superior 140 desde el sustrato inferior 105 una distancia predefinida (tal como desde 50 µm hasta 150 mm). De esta manera, una parte de cada conductor (comenzando desde su extremo con los contactos de unión 135, 150) se desprende del sustrato inferior 105 a medida que el sustrato superior 140 se eleva. Por tanto, los conductores se extenderán ahora entre el sustrato superior 140 y el sustrato inferior 105 (con los conductores extendidos, incluyendo sus capas precursoras, que se designan en conjunto como 130'). Particularmente, cada conductor (extendido) 130' presenta un extremo inferior 130a (opuesto a los contactos de unión 135,150), que permanece conectado al sustrato inferior 105; un extremo superior 130b del conductor 130' (con los contactos de unión 135,150) está conectado, en cambio, al sustrato superior 140 a través de las pistas conductoras 145. Debe observarse que las regiones de silicio poroso 120 permiten el pelado de los conductores 130', impidiendo al mismo tiempo su desprendimiento completo del sustrato inferior 105.

En una puesta en práctica diferente (no mostrada en la figura) también es posible proporcionar una componente horizontal del movimiento entre el sustrato superior 140 y el sustrato inferior 105 (paralela a la superficie

frontal 110), para deslizar el sustrato superior 140 con respecto al sustrato inferior 105; por ejemplo, los extremos superiores 130b de los conductores 130' pueden alinearse (en perpendicular a la superficie frontal 110) con los extremos inferiores 130a.

Resultados experimentales mostraron que un vacío del orden de 500 mTorr (que puede obtenerse fácilmente por medio de bombas de vacío giratorias disponibles comercialmente) es suficiente para elevar aproximadamente 1.000 conductores 130'. Para ello, debe aplicarse una fuerza de algunos kg a las placas para alejar entre sí el sustrato superior 140 y el sustrato inferior 105; este movimiento puede controlarse con una elevada precisión por medio de sistemas de manipulación disponibles comercialmente (por ejemplo, que pueden aplicar una fuerza de hasta 10 kg con una precisión de algunos nm para un recorrido incluso superior a 1 cm).

5

10

15

20

25

30

35

40

45

50

55

60

En este punto, se inyecta un material aislante fluido entre el sustrato superior 140 y el sustrato inferior 105 (por ejemplo, mediante colada o a presión). El material aislante puede ser silicona, una resina epoxídica, termoplástica o termoendurecible, o una cerámica colada; el material aislante también puede estar cargado con nanopartículas (por ejemplo, nanoesferas con un diámetro de 15-180 nm realizadas en Al<sub>2</sub>O<sub>3</sub>, AlN, BN, SiO<sub>2</sub> o Si<sub>3</sub>N<sub>4</sub>) con el fin de aumentar la rigidez y/o la conductividad térmica del material aislante. El material aislante debe presentar una baja viscosidad (por ejemplo, inferior a 500 St). Para ello, la estructura formada por el sustrato inferior 105 y el sustrato superior 140 también puede incluirse en un sistema de desgasificación, para impedir la formación de cualquier burbuja de aire que pueda aparecer durante la inyección del material aislante cuando su viscosidad es relativamente alta (por ejemplo, superior a 10 St). De esta manera, el material aislante llena todo el espacio entre el sustrato superior 140 y el sustrato inferior 105, rodeando de ese modo completamente los conductores 130'. El material aislante se cura para obtener una capa correspondiente 155, en la que están incrustados todos los conductores 130'. Según el material aislante que se inyecte entre el sustrato superior 140 y el sustrato inferior 105, la capa aislante 155 puede ser o bien elástica o bien rígida.

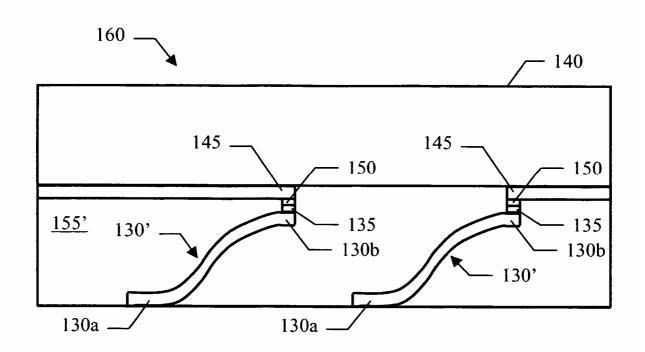

Haciendo referencia a continuación a la figura 1f, se elimina el sustrato inferior. Para ello, cuando la capa aislante 155 es rígida y no se adhiere sobre el sustrato inferior, una acción mecánica es suficiente para separar el sustrato inferior del resto de la estructura. A la inversa, la separación del sustrato inferior puede conseguirse por medio de un procedimiento de grabado en húmedo (ya sea del tipo anisotrópico o isotrópico). En cualquier caso, la operación expone los extremos inferiores 130a de los conductores 130'. La estructura obtenida de este modo se divide entonces en dados, para proporcionar una pluralidad de elementos de interconexión 160 (sólo se muestra uno en la figura); cada elemento de interconexión 160 incluye una pluralidad de conductores 130' (por ejemplo, desde 10 hasta 10.000). El elemento de interconexión puede utilizarse para conectar uno o más dispositivos electrónicos (no mostrados en la figura) a los extremos inferiores 130a, para acoplarlos con el sustrato superior 140 (a través de los conductores 130'). Para ello, también es posible formar una o más capas de metal (no mostradas en la figura) sobre los extremos inferiores 130a (por ejemplo, por medio de un procedimiento de película delgada o un procedimiento de película gruesa).

Alternativamente, tal como se muestra en la figura 1g, el sustrato superior también se retira (antes de la operación de división en dados). Por ejemplo, el sustrato superior puede consistir en otra oblea, sobre la que se han depositado las pistas conductoras correspondientes, por medio de un procedimiento de película delgada o un procedimiento de galvanoplastia (cuando se requiere un espesor superior a 2-3 µm); en este caso, las pistas conductoras también pueden sustituirse por una capa conductora uniforme (individual o múltiple) que se forma por toda la superficie del sustrato superior. Tal como se ha expuesto anteriormente, una o más regiones de silicio poroso se forman preferentemente sobre la superficie del sustrato superior para garantizar la adhesión deseada de la capa/las pistas conductoras sobre la misma. En cualquier caso, el sustrato superior se elimina con las mismas técnicas descritas anteriormente para el sustrato inferior (sin afectar sustancialmente a la capa/las pistas conductoras). Debe observarse que cuando se ha formado una capa conductora uniforme sobre el sustrato superior, las pistas conductoras 145 pueden obtenerse (tras la retirada del sustrato superior) por medio de un procedimiento de grabado en húmedo selectivo; para ello, las partes deseadas de la capa conductora se protegen mediante una máscara fotorresistente en la que se ha formado un patrón de manera adecuada (mientras que el material aislante 155 puede normalmente resistir el grabado durante el corto periodo requerido normalmente para formar el patrón de la capa conductora).

Tal como se ha expuesto anteriormente, la estructura obtenida de este modo se divide entonces en dados para proporcionar una pluralidad de elementos de interconexión, sólo se muestra uno en la figura (diferenciado por medio de una notación prima, es decir, 160'); cada elemento de interconexión 160' es o bien rígido o bien flexible (según las características de la capa aislante 155). El elemento de interconexión 160' puede utilizarse para acoplar cualquier dispositivo electrónico (no mostrado en la figura) entre las dos superficies principales opuestas de la capa aislante 155 a través de los conductores 130'; para ello, los dispositivos electrónicos se conectan a los extremos inferiores 130a de los conductores 130' o a las pistas conductoras 145 (acopladas con los extremos superiores 130b de los mismos conductores 130').

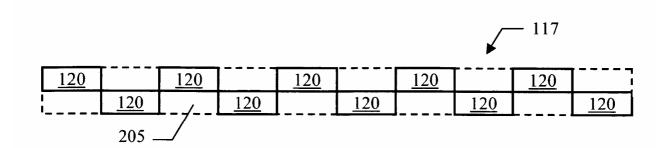

Considerando a continuación la figura 2a, la adhesión deseada de los conductores al sustrato inferior también puede conseguirse formando las regiones de silicio poroso 120 de manera selectiva en sus zonas de contacto 117 (sólo se muestra una en la figura). Más específicamente, en cada zona de contacto 117 las regiones de silicio poroso 120 (una o más) se forman en una parte seleccionada de la misma, mientras que una parte 205 (pasiva) restante de la zona de contacto 117 mantiene su estructura monocristalina. Para ello, la superficie frontal del sustrato inferior se cubre mediante una máscara fotorresistente correspondiente en la que se ha formado un patrón de manera adecuada (antes

de la formación de la utilizada para los conductores); esta máscara fotorresistente protege la parte 205 pasiva y expone la parte deseada de la zona de contacto 117, en la que las regiones de silicio poroso 120 se formarán entonces durante el procedimiento anódico correspondiente.

Las regiones de silicio poroso 120 pueden presentar cualquier forma (por ejemplo, un rectángulo, un cuadrado o un círculo). En una forma de realización de la invención (tal como se muestra en la figura), las regiones de silicio poroso 120 se distribuyen uniformemente por toda la zona de contacto 117. La concentración de las regiones de silicio poroso 120 en la zona de contacto 117 determina su adhesión (promedio) en conjunto. Por ejemplo, considerando un silicio poroso que proporcionaría una adhesión de 200 MPa en una zona de contacto 117 de 10<sup>4</sup> mm²; si el silicio poroso se forma sólo en cien regiones 120 cada una de 1 mm², la adhesión total de la zona de contacto 117 pasará a ser (200\*100)/10<sup>4</sup>=2 Mpa. El mismo resultado también puede conseguirse por medio de una única región de silicio poroso de 100 mm² (por ejemplo, que consiste en una tira estrecha que se extiende a lo largo de la zona de contacto 117).

5

10

15

20

25

30

35

40

45

50

55

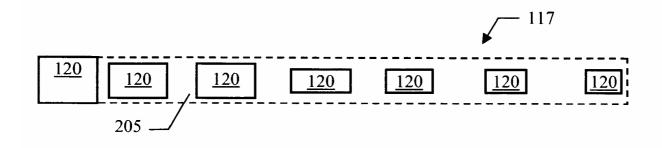

En una forma de realización diferente de la invención, tal como se muestra en la figura 2b, la concentración de las regiones de silicio poroso 120 en la zona de contacto 117 disminuye a medida que se mueve desde el extremo inferior del conductor correspondiente hasta el extremo superior del mismo. Preferentemente, la adhesión disminuye desde un valor máximo (en el extremo inferior del conductor) hasta un valor mínimo (en el extremo superior del conductor) igual al 0,01%-60% del valor máximo, y preferentemente igual al 0,1%-10% del valor máximo (tal como el 0,5%-1% del mismo). Por ejemplo, la adhesión en el extremo inferior del conductor puede ser de aproximadamente 100 MPa, mientras que la adhesión en el extremo superior del mismo puede ser de 0,1 MPa.

El resultado deseado se consigue reduciendo el número y/o el tamaño de las regiones de silicio poroso 120 (a medida que se mueve desde el extremo inferior hasta el extremo superior del conductor). Por ejemplo, en el caso en cuestión las regiones de silicio poroso 120 se contraen y se dispersan de derecha a izquierda. De esta manera, es posible que se presente una adhesión menor cerca del extremo superior del conductor, para facilitar su pelado; al mismo tiempo, se mantiene una adhesión alta cerca del extremo inferior del conductor, para evitar cualquier riesgo de desprendimiento.

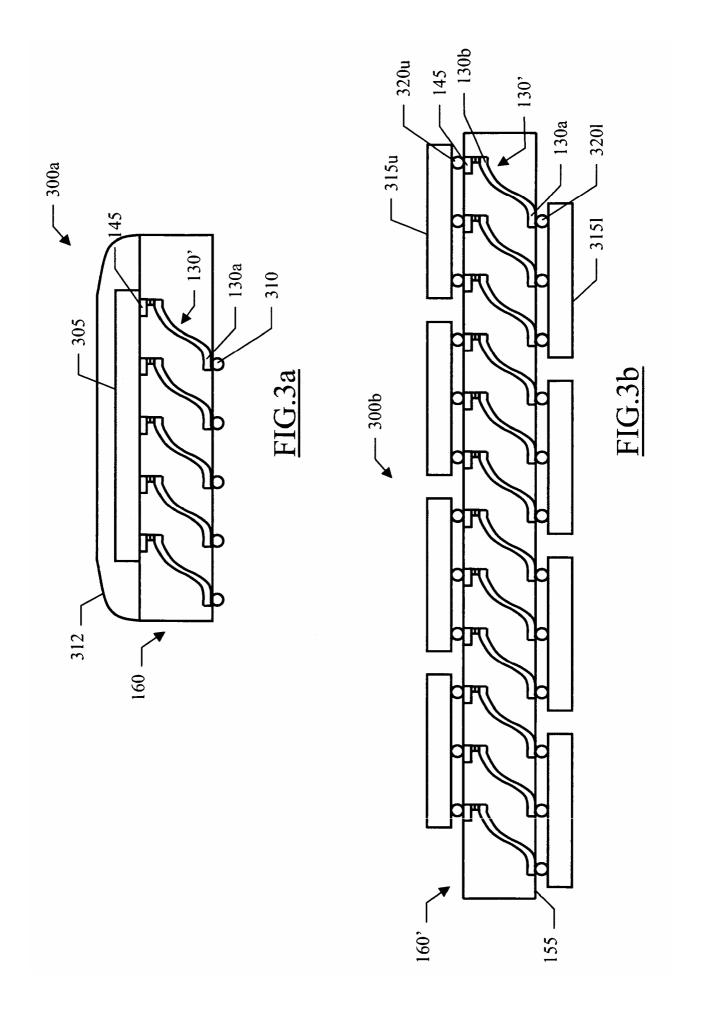

Una aplicación a título de ejemplo del elemento de interconexión 160 descrito anteriormente se ilustra en la figura 3a. Particularmente, la figura muestra una estructura que se utiliza para empaquetar un chip 305. El chip 305 se forma en una zona correspondiente de la oblea que presenta el sustrato superior (lo que proporciona una pluralidad de componentes idénticos tras su división en dados). En este caso, las pistas conductoras 145 presentan unos terminales del chip 305, que se conectan entonces a los conductores correspondientes 130' durante el procedimiento de fabricación del elemento de interconexión 160. En este punto, se sueldan o se depositan sobre los extremos inferiores 130a esferas conductoras 310. El chip 305 normalmente se cubre mediante una tapa 312 protectora (por ejemplo, de un material de plástico); la tapa 312 protectora se forma encima de la capa aislante 155, para rodear completamente el chip 305.

Una aplicación a título de ejemplo de la estructura de interconexión 160' se ilustra en su lugar en la figura 3b. Particularmente, la figura muestra un módulo 300b multichip. El módulo 300b multichip se utiliza para montar una pluralidad de chips 3151 y 315u (por ejemplo, circuitos integrados del tipo digital y/o del tipo de potencia). Más en particular, cada chip 3151 se dispone por debajo de la estructura de interconexión 160'; el chip 3151 está dotado de una pluralidad de terminales 320a (en forma de esferas en el ejemplo en cuestión), que están conectados a unos extremos inferiores correspondientes 130a de los conductores 130'; por otro lado, cada chip 315u se dispone por encima de la estructura de interconexión 160'; el chip 315u está provisto de una pluralidad de terminales similares 320u, que están conectados a unas pistas conductoras correspondientes 145 que están acopladas con los extremos superiores 130b de los conductores 130'. Esto permite obtener una estructura tridimensional (que se incrusta entonces normalmente en un paquete).

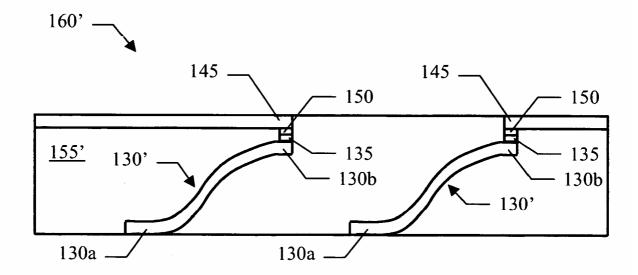

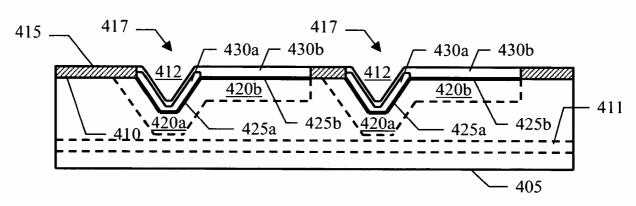

Haciendo referencia a continuación a las figuras 4a-4f, se ilustran las diversas fases de un procedimiento para fabricar una tarjeta de prueba según diferentes formas de realización de la invención. La tarjeta de prueba puede utilizarse para someter a prueba cualquier clase de dispositivos electrónicos, tales como chips a nivel de oblea (en este caso, denominada comúnmente tarjeta de sonda) o componentes en forma empaquetada. Para una mayor simplicidad, a continuación los elementos correspondientes a los mostrados en las figuras anteriores se designarán con referencias similares obtenidas cambiando su primer número de "1" a "4" (y se omitirá su explicación).

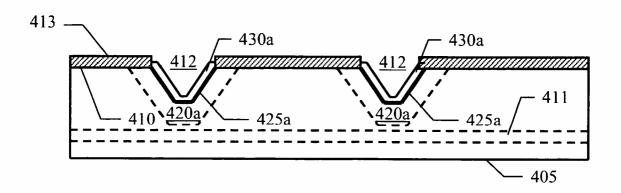

Considerando en particular la figura 4a, el procedimiento de fabricación comienza de nuevo con un sustrato inferior 405 (que consiste en una oblea de silicio monocristalino), sobre una superficie frontal del mismo 410 se forman los conductores que van a elevarse. El sustrato inferior 405 también incluye una capa de parada 411, cuyo propósito resultará evidente a continuación. La capa de parada 411 presenta una elevada concentración de impurezas del tipo P (tal como superior a 5-10<sup>19</sup> átomos/cm³); por ejemplo, la capa de parada 411 se obtiene por medio de una implantación o una difusión de impurezas de tipo P en el sustrato inferior 405. En este caso, tal como se describe en detalle a continuación, cada conductor se utilizará para definir una sonda correspondiente para poner en contacto terminales de los dispositivos electrónicos que van a someterse a prueba (por ejemplo, en forma de pastillas o esferas).

Para ello, se crean unas ranuras 412 (que se extienden desde la superficie frontal 410 hacia el interior del sustrato inferior 405). En el ejemplo mostrado en la figura, las ranuras 412 presentan una forma troncopiramidal con un perfil trapezoidal (para obtener sondas correspondientes que se utilizarán para poner en contacto resaltes de los

dispositivos electrónicos en prueba). Las ranuras 412 se definen por medio de un procedimiento de grabado en húmedo del tipo anisotrópico; por ejemplo, el resultado deseado puede conseguirse tal como se describe en el documento WO-A-2006/066620 (cuya descripción se incorpora en su totalidad a la presente memoria como referencia en la medida máxima admisible por ley).

5

10

15

20

25

30

35

40

45

50

55

60

Brevemente, el sustrato inferior 405 expone un plano cristalino que proporciona una alta tasa de grabado, por ejemplo, con una orientación cristalográfica definida por el índice de Miller <100>, de modo que un plano (111) cristalino forma un ángulo α= 54,7° con la superficie frontal 410. Se forma una máscara 413 sobre la superficie frontal 410, con ventanas que exponen zonas correspondientes a los extremos inferiores de los conductores que van a formarse (normalmente, con una forma rectangular o cuadrada); por ejemplo, la máscara 413 consiste en nitruro de silicio, vidrio de fosfosilicato dopado con boro (BPSG) o una estructura compuesta con una capa inferior de nitruro de silicio (con ventanas más grandes para las siguientes fases de fabricación) y una capa superior de BPSG (con las ventanas deseadas). El sustrato inferior 405 se sumerge entonces en una disolución química adecuada, para grabarlo a través de las ventanas de la máscara 413. El procedimiento es relativamente rápido hasta que se encuentra el plano (111) cristalino (después de eso la tasa de grabado puede considerarse insignificante); de esta manera, cada ranura 412 obtenida de este modo presentará superficies laterales que se extienden con el ángulo α desde la superficie frontal 410 y una superficie de base rectangular (cuyo tamaño depende de la duración del procedimiento de grabado). El mismo resultado también puede conseguirse proporcionando una capa de parada en el sustrato inferior 405 (no mostrada en la figura); esta capa de parada impide el grabado del sustrato inferior 405 (por ejemplo, gracias a una alta concentración de impurezas o a una orientación cristalográfica adecuada), para proporcionar la forma deseada de las ranuras 412 independientemente de la duración del procedimiento de grabado.

Alternativamente, las ranuras (no mostradas en la figura) presentan un perfil triangular, para obtener unas sondas correspondientes que se utilizarán para poner en contacto las pastillas de los dispositivos electrónicos a prueba; particularmente, las ranuras pueden consistir en un poliedro (con dos caras trapezoidales y dos caras triangulares que se unen en un borde) o en una pirámide (con cuatro caras triangulares que se unen en un vértice). Este resultado se consigue continuando con el grabado hasta que sólo las facetas del plano (111) cristalino permanecen expuestas, de modo que la base de cada ranura entra en el borde o el vértice (cuando las ventanas correspondientes son rectangulares o cuadradas, respectivamente).

La misma máscara 413, u otra máscara (no mostrada en la figura) con ventanas ligeramente mayores que las de la máscara 413 (por ejemplo, obtenidas simplemente retirando la capa de BPSG en el caso de la estructura compuesta mencionada anteriormente), se utiliza para formar unas regiones de silicio poroso 420a por medio de un procedimiento anódico; las regiones de silicio poroso 420a se extienden desde las superficies (lateral y de base) de las ranuras 412 hacia el interior del sustrato inferior 405, justo por encima de la capa de parada 411 (por ejemplo, a unos pocos µm de la misma). Una capa precursora 425a se deposita opcionalmente de manera no electrolítica sobre las superficies de las ranuras 412. Una capa 430a (o más) de un material conductor adecuado para formar las sondas se deposita de manera selectiva sobre la capa precursora 425a (por medio de un procedimiento de galvanoplastia). El material de la capa 430a debe ser relativamente duro, resistente a la abrasión y apenas oxidable. Preferentemente, la dureza de este material es superior a 200 Vickers, tal como del orden de 200-1.000 Vickers, y más preferentemente 400-600 Vickers, tal como 500 Vickers. Por ejemplo, la capa (dura) 430a consiste en un metal tal como níquel o sus aleaciones, aleación de cromo-molibdeno, aleación de paladio-cobalto, aleación de paladio-níquel, rodio o rutenio (con un espesor en el intervalo de desde 0,1 µm hasta 10 µm).

Haciendo referencia a continuación a la figura 4b, tal como se ha expuesto anteriormente se forma una máscara fotorresistente adicional 415 sobre la superficie frontal 410, con ventanas que exponen zonas de contacto 417 para los conductores deseados (incluyendo cada uno la ranura correspondiente 412 con la capa dura 430a). Se forman unas regiones de silicio poroso adicionales 420b por medio de otro procedimiento anódico a través de la máscara fotorresistente 415 (utilizando o bien los mismos parámetros o no con respecto al procedimiento anódico anterior). Las regiones de silicio poroso 420b se extienden hacia el interior del sustrato inferior 405 desde las partes expuestas de las zonas de contacto 417 (que no están cubiertas por la capa dura 430a). Debe observarse que el procedimiento anódico para la formación de las regiones de silicio poroso 420b es relativamente corto (por ejemplo, 30 s-300 s), de modo que no provoca ningún grabado apreciable de la capa dura 430a; como máximo, el procedimiento anódico genera una ligera rugosidad de la capa dura 430a, rugosidad que facilita la adhesión con la(s) siguiente(s) capa(s) utilizada(s) para completar los conductores. Tal como se ha expuesto anteriormente, una capa precursora 425b se deposita opcionalmente de manera no electrolítica sobre las partes expuestas de las zonas de contacto 417. En este punto, los conductores se completan por medio de una capa 430b (o más) de un material conductor adecuado para su elevación. La capa 430b se deposita de manera selectiva a través de la máscara fotorresistente 415 (es decir. sobre la capa dura 430a y la capa precursora 415b) por medio de un procedimiento de galvanoplastia. El material de la capa 430b debe ser un material dúctil, menos duro que el utilizado para la capa 430a (para proporcionar la flexibilidad requerida de los conductores). Preferentemente, la dureza de este material es inferior a 200 Vickers, tal como del orden de 20-150 Vickers, y más preferentemente 40-100 Vickers, tal como 50 Vickers. Por ejemplo, la capa (flexible) 430b está realizada en el (de los) mismo(s) material(es) tal como se indicó anteriormente para los conductores en conjunto.

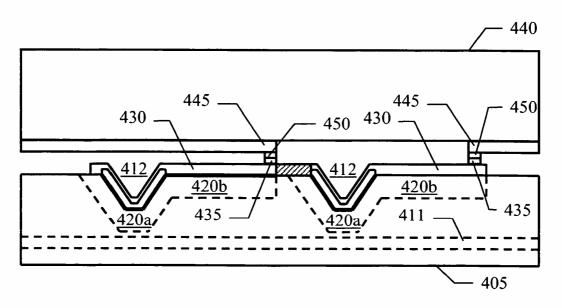

Tal como se muestra en la figura 4c, cada conductor así obtenido (designado en conjunto con 430) está dotado de un contacto de unión 435 en un extremo de la capa flexible 427 (opuesta a la ranura correspondiente 412). A

continuación, se acopla un sustrato superior 440 con el sustrato inferior 405. En este caso, el sustrato superior 440 consiste en un sustrato con circuitos (tal como una PCB mono o multicapa) para encaminar las señales deseadas en la tarjeta de prueba, con un elemento de interposición adaptable opcional para compensar cualquier alabeo de los dispositivos electrónicos a prueba. Tal como se ha expuesto anteriormente, el sustrato superior 440 está provisto de unas pistas conductoras 445, en las que se forman contactos de unión 450; el sustrato superior 440 se coloca enfrente del sustrato inferior 405, y los contactos de unión 450 se sueldan o pegan a los contactos de unión 435.

5

10

15

20

25

30

35

40

45

50

55

60

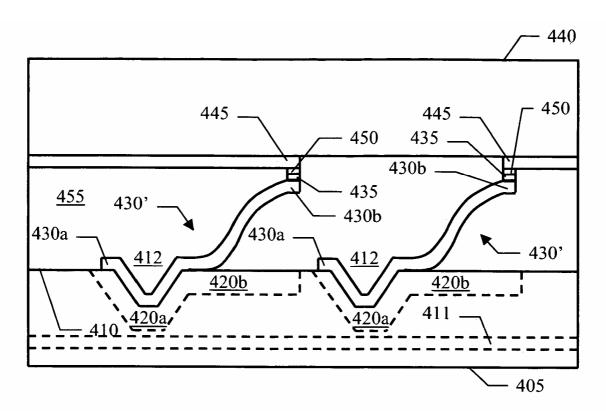

Haciendo referencia a la figura 4d, el sustrato superior 440 y el sustrato inferior 405 se separan entre sí, para elevar los conductores. Tal como anteriormente, cada conductor (extendido), diferenciado con una notación prima, es decir, 430', presenta un extremo inferior 430a (que incluye su parte troncopiramidal formada en la ranura correspondiente 412), que permanece conectado al sustrato inferior 405; un extremo superior 430b del conductor 430' (con los contactos de unión 435, 450) está conectado, en cambio, al sustrato superior 440 a través de las pistas conductoras 445. Las regiones de silicio poroso 420a, 420b permiten de nuevo el pelado de los conductores 430' impidiendo al mismo tiempo su desprendimiento completo desde el sustrato inferior 405. En este punto, se inyecta un material aislante fluido entre el sustrato superior 440 y el sustrato inferior 405, y entonces se cura para obtener una capa aislante correspondiente 455 (en la que están incrustados todos los conductores 430'), preferentemente del tipo elástico.

Haciendo referencia a la figura 4e, se retira el sustrato inferior. En este caso, cualquier daño a las partes (expuestas) de los conductores 430' que formarán las sondas debe evitarse (cuando la separación se realiza por medio de un procedimiento de grabado en húmedo). Por ejemplo, es preferible utilizar un procedimiento de grabado en húmedo del tipo anisotrópico (cuya tasa de grabado en los conductores 430' es insignificante). Además o como alternativa, el sustrato inferior se graba sólo parcialmente, sin alcanzar los conductores 4307, una parte restante del sustrato inferior se retira entonces por medio de un procedimiento de grabado en seco (que no daña los conductores 430'). Este resultado se consigue por medio de la capa de parada 411 (véase la figura 4d), que reduce enormemente la tasa de grabado (en un factor de aproximadamente 50). De esta manera, es posible aproximarse a los conductores 430' con una precisión muy alta (independientemente del tiempo de grabado). La capa restante del sustrato inferior puede retirarse entonces en un tiempo razonable por medio de un procedimiento de grabado por iones reactivos (RIE) convencional, incluso si proporciona una tasa de grabado relativamente baja (tal como 0,3-2 µm/minuto). Alternativamente, también es posible controlar la duración del procedimiento de grabado en húmedo para detenerlo antes de alcanzar los conductores 430' (sin utilizar ninguna capa de parada); por ejemplo, una capa del sustrato inferior con un espesor de 10 µm a 30 µm se mantiene por debajo de los conductores 430'. La capa (más gruesa) restante del sustrato inferior se retira ahora por medio de un procedimiento RIE profundo (por ejemplo, basado en SF<sub>2</sub>, CF<sub>4</sub>, O<sub>2</sub> o una combinación de los mismos), lo que proporciona una tasa de grabado mucho mayor (tal como de hasta 10 µm/minuto).

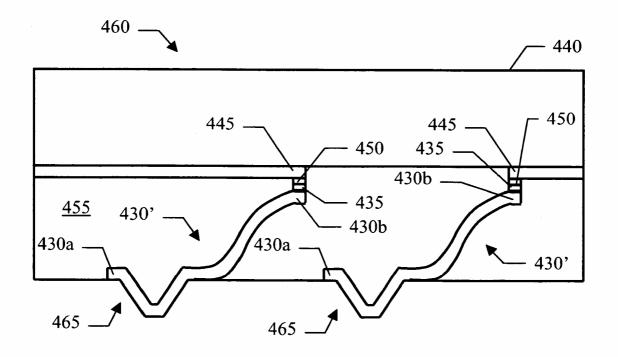

En cualquier caso, la operación expone los extremos inferiores 430a de los conductores 430', con sus partes piramidales que sobresalen hacia abajo desde la capa aislante 455. Esto genera una tarjeta de prueba 460, cuyas sondas 465 están definidas por los extremos inferiores expuestos 430a de los conductores 430'. La tarjeta de prueba 460 puede utilizarse para someter a prueba uno o más dispositivos electrónicos (no mostrados en la figura), que presentan una pluralidad de terminales que se ponen en contacto mediante las sondas 465 (en forma de esferas en el ejemplo en cuestión). Las sondas 465 presentan una estructura adaptable (gracias a la elasticidad de la capa aislante 455), para garantizar el contacto correcto de los dispositivos electrónicos a prueba; además, las sondas 465 se deforman para abarcar sus terminales (es decir, esferas). Alternativamente, cuando las sondas (no mostradas en la figura) terminan con un borde o un vértice, son muy adecuadas para limpiar cualquier capa de óxido nativa de los terminales de los dispositivos electrónicos a prueba (especialmente cuando están en forma de pastillas). En cualquier caso, la capa dura utilizada para formar los conductores 430' garantiza las características mecánicas requeridas de las sondas 465 (sin afectar de manera adversa a la elevación de los conductores gracias a su capa flexible).

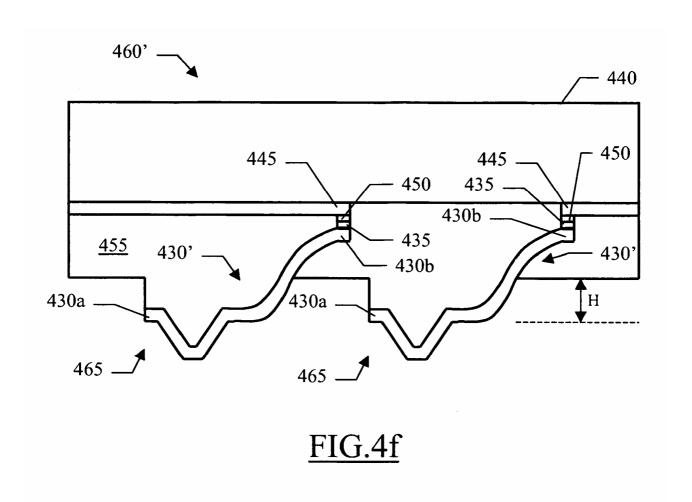

En una forma de realización diferente de la invención, tal como se muestra en la figura 4f, una parte externa de la capa aislante 455 (tal como realizada en silicona o cualquier otro polímero elástico) se retira adicionalmente. Normalmente, la capa aislante 455 se retira para una profundidad igual al 0,1%-70%, y más preferentemente igual al 5-60% (tal como el 50%) de un espesor total de la capa aislante (original) 455; por ejemplo, esta operación puede retirar desde 10 µm hasta 300 µm de la capa aislante 455.

Para ello, la capa aislante 455 se graba por medio de un procedimiento RIE, por ejemplo, basado en una mezcla de  $SF_6$ ,  $CF_4$ ,  $O_2$ ,  $CHF_3$  (lo que proporciona una tasa de grabado de la silicona del orden de  $20 \,\mu\text{m/hora}$ ) o basado en una mezcla de  $SF_6$ ,  $CHF_3$  y  $O_2$  (lo que proporciona una tasa de grabado de la silicona de hasta 30  $\,\mu\text{m/hora}$ ). El mismo resultado también puede conseguirse por medio de un procedimiento de ablación láser (en el que el material se retira a través de sublimación). Por ejemplo, con un láser pulsado que presenta una longitud de onda ultravioleta, la fluencia mínima para obtener la retirada de la silicona es de 140  $\,\text{mJ/cm}^2$ ; naturalmente, es posible aumentar la fluencia de láser, para obtener tasas de ablación superiores de la silicona (tal como 1  $\,\text{mm}$  por 100 disparos). En este caso, el láser también puede sustituirse por lámparas ultravioletas pulsadas (que proporcionan una fluencia superior al umbral mencionado anteriormente necesario para la ablación de la silicona). En cualquier caso, el procedimiento de eliminar la parte deseada de la capa aislante 455 es de alineación automática, con los extremos inferiores 430a de los conductores 430' que actúan como una máscara que permite la retirada de la capa aislante 455 sólo cuando no está protegida.

Esto genera una tarjeta de prueba diferente en la que cada sonda resultante (diferenciada con una notación

# ES 2 359 919 T3

prima, es decir, 460' y 465', respectivamente) puede moverse independientemente. Esto es particularmente ventajoso cuando la tarjeta de prueba 465' consiste en una tarjeta de sonda (utilizada para someter a prueba dispositivos electrónicos al nivel de oblea).

## Modificaciones

5

10

15

20

25

30

35

40

45

50

55

Naturalmente, con el fin de satisfacer los requisitos locales y específicos, un experto en la materia puede aplicar a la solución descrita anteriormente muchas modificaciones y alteraciones lógicas y/o físicas. Más específicamente, aunque la presente invención se ha descrito con un cierto grado de particularidad haciendo referencia a una(s) forma(s) de realización preferida(s) de la misma, debe entenderse que son posibles diversas omisiones, sustituciones y cambios en la forma y detalles así como otras formas de realización. Particularmente, la solución propuesta pueden incluso ponerse en práctica sin los detalles específicos (tal como los ejemplos numéricos) expuestos en la descripción anterior para proporcionar una comprensión más completa de la misma; a la inversa, características bien conocidas pueden haberse omitido o simplificado con el fin de no complicar la descripción con detalles innecesarios. Además, se pretende expresamente que elementos y/o etapas de procedimiento específicos descritos en relación con cualquier forma de realización dada a conocer de la invención pueden incorporarse en cualquier otra forma de realización como una cuestión de elección de diseño general.

Particularmente, la solución propuesta se puede poner en práctica con procedimientos equivalentes (utilizando etapas similares, eliminando algunas etapas que no son esenciales o añadiendo etapas opcionales adicionales); además, las etapas pueden realizarse en diferente orden, simultáneamente o de manera intercalada (al menos en parte). Consideraciones similares son válidas si los procedimientos de fabricación utilizan otros materiales, tecnologías, configuraciones, máscaras (diferentes en número y/o tipo), y similares.

Debe resultar fácilmente evidente que los conductores pueden presentar cualquier otra forma y/o tamaño; además, pueden estar realizados en uno o más materiales conductores diferentes. Además, puede utilizarse cualquier clase de sustrato para elevar los conductores (por ejemplo, una oblea, una PCB, un soporte para uno o más chips, y similares). Alternativamente, los conductores pueden acoplarse con el sustrato superior de cualquier otra manera (por ejemplo, con los contactos de unión sólo sobre el sustrato inferior o el sustrato superior). Se contempla cualquier otro movimiento relativo entre el sustrato superior y el sustrato inferior (tal como con dos componentes horizontales en direcciones opuestas).

En cualquier caso, se enfatiza que es posible cualquier combinación de las características descritas anteriormente; por ejemplo, pueden utilizarse elementos de interconexión fabricados sin las ranuras en el sustrato inferior para la tarjeta de pruebas, o también puede utilizarse el procedimiento de fabricación basado en las ranuras en el sustrato inferior para obtener elementos de interconexión para diferentes fines (tal como para los montajes electrónicos descritos anteriormente).

Alternativamente, las regiones de silicio poroso pueden sustituirse por regiones de promoción de la adhesión equivalentes (que pueden aumentar la adhesión de los conductores sobre la superficie frontal). Por ejemplo, nada impide la utilización de un sustrato inferior de un tipo diferente (tal como realizado en vidrio); la adhesión puede controlarse por medio de una capa adhesiva, una capa de metal delgada depositada a través de un procedimiento de película delgada (por ejemplo, realizada en V, Nb o Ti, con un espesor inferior a 200 nm, tal como 30-40 nm), o cualquier otro promotor de la adhesión. Más generalmente, la utilización de cualquier otra técnica para tratar la superficie frontal para controlar la adhesión de los conductores que van a elevarse está dentro del alcance de la invención.

Consideraciones similares son válidas si el silicio poroso (o bien en una sola capa o en múltiples regiones) se obtiene con procedimientos equivalentes.

La porosidad del silicio poroso puede modularse de cualquier otra manera (para reducirla a medida que se aleja de la superficie frontal del sustrato inferior). Sin embargo, se contempla la utilización de silicio poroso con una porosidad uniforme.

Naturalmente, los intervalos propuestos para los valores de la porosidad son meramente ilustrativos:

El resultado deseado puede conseguirse actuando sobre cualquier otro parámetro del procedimiento anódico (o una combinación de los mismos), tal como la temperatura.

En cualquier caso, la densidad de corriente puede actualizarse entre diferentes valores y/o con cualquier otro patrón de tiempo (por ejemplo, según una ley lineal o logarítmica).

La distribución descrita anteriormente de las regiones de silicio poroso en cada zona de contacto es meramente ilustrativa; consideraciones similares son válidas si las regiones de silicio poroso presentan un número diferente, u otro tamaño y/o forma. Naturalmente, nada impide proporcionar el silicio poroso por toda la extensión de cada zona de contacto

De manera similar, la adhesión puede reducirse a medida que se mueve a lo largo de los conductores de cualquier otra manera equivalente. También en este caso, sin embargo, no se excluye la utilización de siempre la misma adhesión.

Tal como se ha expuesto anteriormente, los intervalos propuestos para los valores de la adhesión son meramente ilustrativos.

También puede conseguirse el mismo resultado cambiando sólo el número de las regiones de silicio poroso (con el mismo tamaño) o sólo su tamaño (para el mismo número); alternativamente, también es posible reducir la porosidad del material a medida que se mueve a lo largo de los conductores.

Puede depositarse cualquier otro metal sobre el silicio poroso, o bien con un procedimiento no electrolítico o bien con un procedimiento de galvanoplastia, para mejorar la uniformidad de los conductores (incluso si esta característica puede omitirse en algunas implementaciones).

Consideraciones similares son válidas si se inyecta cualquier otro material aislante fluido entre el sustrato inferior y el sustrato superior; además, el material aislante puede curarse con cualquier técnica equivalente para obtener la capa deseada de material aislante. En cualquier caso, nada impide dejar los conductores extendidos expuestos en una puesta en práctica simplificada.

Las ranuras para los conductores pueden presentar cualquier otra forma y/o conformación; además, puede utilizarse cualquier otra técnica para su creación.

Las diferentes capas (duras y flexibles) de los conductores pueden consistir en materiales equivalentes, o pueden formarse con cualquier otra técnica. En cualquier caso, nada impide fabricar los conductores con una estructura uniforme (por ejemplo, sólo con el metal más duro cuando los conductores son rectos, de modo que no se produzca ningún problema durante su elevación).

Naturalmente, la definición cuantitativa de los materiales utilizados para formar las capas dura y flexible no debe interpretarse de manera limitativa.

También se contempla la posibilidad de mantener el sustrato inferior.

En cualquier caso, puede utilizarse cualquier otra técnica para retirar el sustrato inferior (incluso basada completamente en un procedimiento de grabado en húmedo).

Naturalmente, es posible utilizar técnicas equivalentes para eliminar la parte externa de la capa aislante.

También en este caso, los intervalos propuestos para la cantidad de capa aislante que va a retirarse son meramente ilustrativos.

Como se señaló anteriormente, el sustrato superior puede o bien mantenerse o bien retirarse (con cualquier otra técnica).

Consideraciones similares son válidas si los sistemas propuestos (es decir, los elementos de interconexión, los montajes electrónicos, basados en un solo chip o múltiples chips, y la tarjeta de pruebas) presentan una estructura diferente o incluyen componentes equivalentes. En cualquier caso, estos sistemas no son absolutos (pudiendo aplicarse la solución concebida en cualquier otro campo).

Particularmente, el elemento de interconexión propuesto puede utilizarse para acoplar cualquier clase de dispositivos electrónicos en la acepción más amplia del término, tal como chips, PCB flexibles o rígidas, paquetes (por ejemplo, del tipo BGA, CSP, QFP o en línea doble), etcétera; de manera similar, los dispositivos electrónicos pueden estar dotados de cualquier terminal tal como pastillas, resaltes, resaltes adaptables, resaltes en forma de borne, clavijas (por ejemplo, del tipo de ala de gaviota, J o sin patillas).

Se enfatiza que los montajes electrónicos descritos anteriormente pueden incluir cualquier número y/o tipo de dispositivos electrónicos, incluso combinados en una estructura multidimensional. En cualquier caso, los dispositivos electrónicos pueden acoplarse con el elemento de interconexión o bien durante su procedimiento de fabricación (cuando consisten en o están incluidos en el sustrato inferior, el sustrato superior o ambos) o tras haberse completado su producción.

Consideraciones similares son válidas si la tarjeta de prueba se utiliza para someter a prueba cualquier otro dispositivo electrónico (o bien al nivel de oblea o bien al nivel de paquete). También en este caso, los demás componentes de la tarjeta de prueba pueden acoplarse con el elemento de interconexión o bien durante su procedimiento de fabricación o bien después.

Debe resultar fácilmente evidente que los componentes propuestos pueden ser parte del diseño de circuitos integrados. El diseño también puede crearse en un lenguaje de programación; además, si el diseñador no fabrica chips o máscaras, el diseño puede transmitirse mediante medios físicos a otros. En cualquier caso, los componentes resultantes pueden distribuirse por su fabricante en forma de oblea sin procesar, como un dado sin revestir o en paquetes. Además, los componentes propuestos pueden combinarse con otros circuitos en la misma estructura, o pueden montarse en productos intermedios (tal como placas base). En cualquier caso, estos componentes son adecuados para utilizarse en sistemas complejos (tal como máquinas de prueba).

14

15

10

5

20

25

35

30

40

45

## **REIVINDICACIONES**

1. Procedimiento de fabricación de un elemento de interconexión (160; 160') para poner en contacto dispositivos electrónicos, incluyendo el procedimiento las etapas siguientes:

formar una pluralidad de conductores (130) sobre una superficie principal (110) de un primer sustrato (105) de silicio monocristalino tras tratar la superficie principal para controlar una adhesión de los conductores sobre la superficie principal, presentando cada conductor un primer extremo (130a) y un segundo extremo (130b),

acoplar el segundo extremo de cada conductor con un segundo sustrato (140), y

separar entre sí el segundo sustrato y el primer sustrato para extender los conductores (130') entre el primer sustrato y el segundo sustrato,

10 caracterizado porque

5

15

20

25

la etapa de tratamiento de la superficie principal incluye:

formar un conjunto de regiones de silicio poroso (120) que se extienden desde la superficie principal hacia el interior del primer sustrato.

2. Procedimiento según la reivindicación 1, en el que la etapa de formación de las regiones de silicio poroso (120) incluye:

modular la porosidad de las regiones de silicio poroso para que dicha porosidad disminuya a medida que se aleja de la superficie principal (110).

3. Procedimiento según la reivindicación 1 ó 2, en el que cada conductor (130) está en contacto con una zona de contacto (117) correspondiente de la superficie principal (110), incluyendo la etapa de formación de las regiones de silicio poroso (120):

formar las regiones de silicio poroso en por lo menos una parte seleccionada de cada zona de contacto.

- 4. Procedimiento según cualquiera de las reivindicaciones 1 a 3, en el que la etapa de tratamiento de la superficie principal incluye:

- reducir la adhesión a medida que se mueve desde el primer extremo (130a) hasta el segundo extremo (130b) de cada conductor (130).

- 5. Procedimiento según la reivindicación 4 cuando está subordinada a la reivindicación 3, en el que la etapa de reducción de la adhesión incluye:

reducir una concentración de las regiones de silicio poroso (210) a medida que se mueve desde el primer extremo (130a) hasta el segundo extremo (130b) de cada conductor (130).

30 6. Procedimiento según cualquiera de las reivindicaciones 1 a 5, en el que la etapa de tratamiento de la superficie principal (110) incluye además:

depositar una capa de metal (125) sobre las regiones de silicio poroso (120).

- 7. Procedimiento según cualquiera de las reivindicaciones 1 a 6, que incluye además las etapas siguientes:

- inyectar un material aislante fluido (155) entre el primer sustrato (105) y el segundo sustrato (140), y

- curar el material aislante para obtener una capa aislante (155) en la que están incrustados los conductores (130').

- 8. Procedimiento según cualquiera de las reivindicaciones 1 a 7, en el que la etapa de formación de los conductores (430') incluye:

- crear una pluralidad de ranuras (412) sobre la superficie principal (410), extendiéndose el primer extremo (430a) de cada conductor en una ranura correspondiente.

- 9. Procedimiento según la reivindicación 8, en el que la etapa de formación de los conductores (430') incluye además:

depositar por lo menos una capa de un material conductor duro (430a) en las ranuras (412), y depositar por lo menos una capa de un material conductor dúctil (430b) para finalizar los conductores.

- 10. Procedimiento según cualquiera de las reivindicaciones 1 a 9, que incluye además la etapa siguiente: eliminar el primer sustrato (105).

- 11. Procedimiento según la reivindicación 10, que incluye además la etapa siguiente: eliminar una parte externa de la capa aislante (455) que no está protegida por los conductores (430').

- 5 12. Procedimiento según la reivindicación 11, en el que la etapa de eliminación de la parte externa de la capa aislante (455) incluye:

eliminar la parte externa para una profundidad igual al 0,1%-70% del espesor de la capa aislante.

- 13. Procedimiento según cualquiera de las reivindicaciones 1 a 12, que incluye además la etapa siguiente: eliminar el segundo sustrato (140).

- 14. Procedimiento de fabricación de un montaje (300a) electrónico que incluye un conjunto de dispositivos electrónicos interconectados (3101, 310u), incluyendo el procedimiento la etapa siguiente:

- acoplar cada primer terminal (3201) de por lo menos un primer dispositivo electrónico (3101) con el primer extremo (130a) y/o cada segundo terminal (320u) de por lo menos un segundo dispositivo electrónico (310u) con el segundo extremo (130b) de un conductor (130') correspondiente del elemento de interconexión (160') fabricado realizando las etapas según cualquiera de las reivindicaciones 1 a 13.

- 15. Procedimiento de fabricación de una tarjeta de prueba (460; 460') que incluye una pluralidad de sondas (465) para poner en contacto terminales correspondientes de dispositivos electrónicos que van a someterse a prueba, incluyendo el procedimiento la etapa siguiente:

- acoplar una placa con circuitos (440) con los segundos extremos (430b) de los conductores (430') del elemento de interconexión fabricado realizando las etapas según cualquiera de las reivindicaciones 1 a 13, definiendo los primeros extremos (430a) de los conductores dichas sondas.

FIG.1a

FIG.1b

FIG.1c

FIG.1d

FIG.1e

FIG.1f

FIG.1g

FIG.2a

FIG.2b

FIG.4a

FIG.4b

FIG.4c

FIG.4d

FIG.4e