OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

1 Número de publicación:  $2\ 361\ 658$

(51) Int. Cl.:

G06F 13/00 (2006.01)

|      | ,                            |

|------|------------------------------|

| (12) | TRADUCCIÓN DE PATENTE EUROPE |

Т3

- 96 Número de solicitud europea: 98966117 .8

- 96 Fecha de presentación : **29.12.1998**

- Número de publicación de la solicitud: 1145129 97 Fecha de publicación de la solicitud: **17.10.2001**

- 54 Título: Sistema informático paralelo.

- Titular/es: Fifth Generation Computer Corporation 232-B East 68th Street New York, New York 10021, US

- (45) Fecha de publicación de la mención BOPI: 21.06.2011

- (72) Inventor/es: Maddox, James, L.

- (45) Fecha de la publicación del folleto de la patente: 21.06.2011

- (74) Agente: Curell Aguilá, Marcelino

ES 2 361 658 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## **DESCRIPCIÓN**

Sistema informático paralelo.

5 La presente invención se refiere en general a sistemas informáticos paralelos y, más en particular, a sistemas informáticos paralelos mejorados, dispuestos en una estructura de árbol binario.

#### Antecedentes de la invención

20

25

30

35

40

45

50

55

60

65

Son conocidos sistemas informáticos paralelos, en los que una pluralidad de elementos de procesado individuales, que incluyen cada uno de ellos un microprocesador, memoria asociada y un dispositivo de entrada/salida (I/O), están dispuestos en una configuración de árbol binario. Uno de los elementos de procesado, al cual se hace referencia como elemento de procesado "raíz", está conectado a un sistema anfitrión y a dos elementos de procesado "hijos". A su vez, cada uno de estos elementos de procesado hijos es un "padre" para dos elementos de procesado hijos conectados al mismo. A los elementos de procesado en los extremos del árbol se les hace referencia como elementos de procesado "hojas", y no tienen hijos adicionales. De este modo, en un ordenador de árbol binario, se puede conectar un número elevado de elementos de procesado de manera que cada elemento de procesado, exceptuando los situados en la raíz y las hojas del árbol, tenga un único padre y dos elementos de procesado hijos (derecho e izquierdo).

Las patentes US nº 4.860.201 y nº 4.843.540 concedidas a Stolfo, que están cedidas al titular de la presente invención, describen un sistema de este tipo.

Según la patente US nº 4.843.540, un sistema de procesado de datos en paralelo se forma como un árbol binario de elementos de procesado de datos. Cada uno de los elementos incluye una unidad de interfaz que presenta unos registros acoplados a registros en la unidad de interfaz de elementos adyacentes de orden superior e inferior en el árbol binario. Señales que comprenden instrucciones y datos para ser procesados en los elementos se difunden de forma general a los elementos a través de los registros acoplados para un procesado simultáneo en los elementos. Los resultados del procesado se comparan y se informa sobre los mismos a través de los registros en una operación de resolución/información.

Aunque el sistema descrito en las patentes US nº 4.860.201 y nº 4.843.540 representaba un paso adelante sustancial en la técnica, seguía existiendo una serie de problemas. El sistema requería el uso de lenguajes de programación especiales en paralelo y no se podía programar usando lenguajes convencionales, disponibles comercialmente. El sistema requería programadores entrenados especialmente, que en general no están disponibles, y los programas escritos no se podían compilar usando compiladores disponibles comercialmente. Son limitaciones significativas adicionales de dichos sistemas de ordenador anteriores el hecho de que los elementos de procesado consumen una parte sustancial de su tiempo tratando con comunicaciones de arriba abajo recorriendo el árbol, lo cual reduce el rendimiento del procesado del sistema, y que cada elemento de procesado debe tener conocimiento de su posición en el árbol, lo cual requiere un gasto de software. Estas dificultades han limitado sustancialmente hasta el momento el alcance de aplicación de los sistemas informáticos de árbol binario.

El documento EP 0 726 529 describe un sistema de reconfiguración en topología de procesador matricial y un método que permite que elementos de procesador en una matriz reconfiguren dinámicamente su interconexión mutua para el intercambio de resultados aritméticos entre los procesadores. Cada elemento de procesado incluye un conmutador de interconexión que es controlado por un decodificador de instrucciones en el procesador. Se difunden de forma general instrucciones a todos los procesadores en la matriz. Las instrucciones son interpretadas de manera exclusiva en cada procesador respectivo de la matriz, dependiendo de la identidad del procesador. La interpretación de la instrucción difundida de forma general comúnmente es realizada de forma exclusiva en cada procesador, combinando la identidad del procesador correspondiente al procesador ejecutante, con un valor en la instrucción. Las señales de control resultantes desde el decodificador de instrucciones hacia el conmutador de interconexión proporcionan un enlace personalizado entre el procesador ejecutante y otros procesadores de la matriz.

#### Sumario de la invención

Para afrontar este y otros problemas con sistemas informáticos conocidos de árbol binario, se proporciona según la invención un sistema de ordenador de árbol binario para su conexión a un ordenador anfitrión y para ser controlado por el mismo, que incluye N controladores de bus conectados en una configuración de árbol binario, en la que cada controlador de bus, excepto los situados en los extremos del árbol, están conectados a controladores de bus hijos izquierdo y derecho, siendo N un entero; uno de los controladores de bus es un controlador de bus raíz para conectar el árbol al ordenador anfitrión. El sistema de la invención incluye además N elementos de procesado, uno para cada uno de los controladores de bus y N+1 elementos de procesado conectados, dos cada uno, como hijos derecho e izquierdo a los controladores de bus en los extremos del árbol binario. Cada uno de los elementos de procesado incluye un microprocesador y una memoria, y cada uno de los controladores de bus incluye, para cada elemento de procesado conectado al mismo, una interfaz con memoria intermedia que conecta el elemento de procesado al controlador de bus para transmitir instrucciones y datos entre el controlador de bus y el elemento de

procesado conectado. Lo que es más importante, cada controlador de bus incluye además unos medios para escribir información en la memoria del elemento de procesado conectado sin involucrar al microprocesador del elemento de procesado.

5 En una forma de realización, cada controlador de bus puede incluir además unos medios para leer información desde dicha memoria del elemento de procesado conectado sin involucrar al microprocesador del elemento de procesado.

### Breve descripción de los dibujos

10

Estas y otras ventajas y características de la invención se pondrán más claramente de manifiesto haciendo referencia a la siguiente descripción de una forma de realización preferida de la invención, en la que:

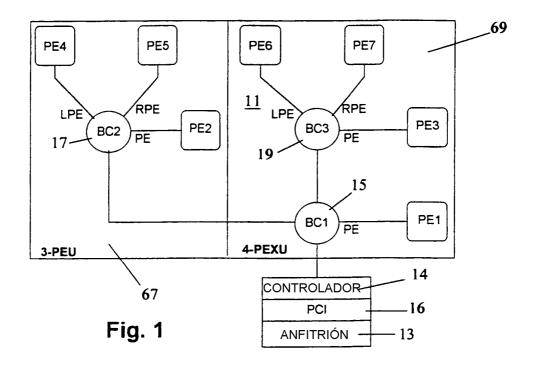

la figura 1 es un diagrama de bloques esquemático de una forma de realización, de siete procesadores, de un sistema informático paralelo de árbol binario según la presente invención.

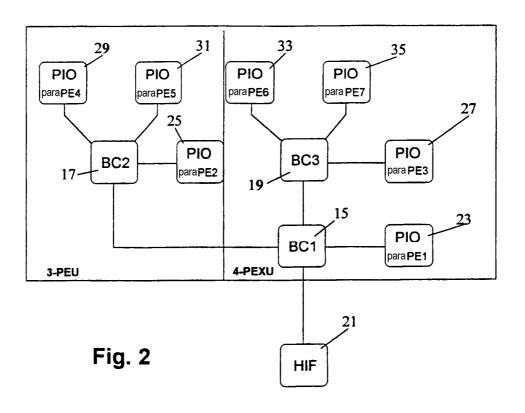

La figura 2 es un diagrama de bloques esquemático más detallado del bus de árbol binario del sistema informático de la figura 1.

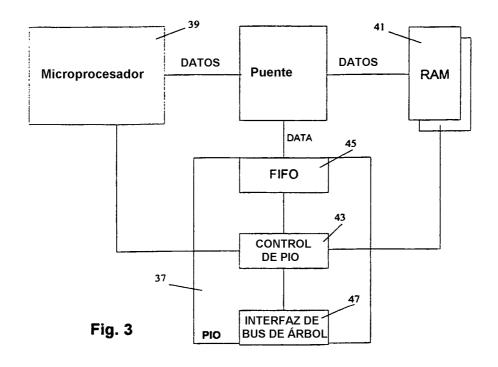

20 La figura 3 es un diagrama de bloques de una entrada/salida de procesador de un sistema informático según la forma de realización ilustrada de la invención.

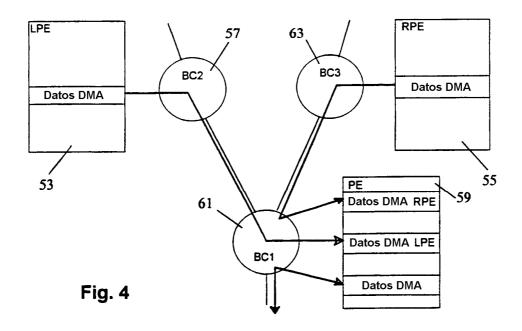

La figura 4 es un diagrama de bloques de una porción de la forma de realización ilustrada, que muestra caminos de datos durante la ejecución de una Llamada de Función particular.

25

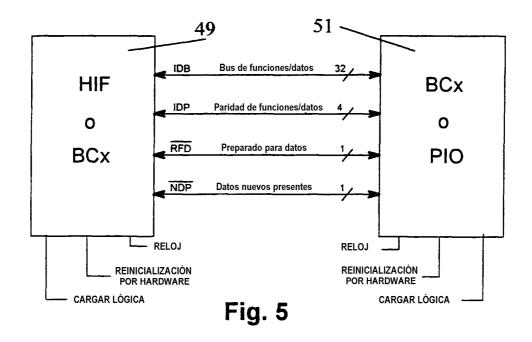

La figura 5 es un diagrama de bloques que muestra las líneas de señal en el bus de árbol de la forma de realización ilustrada de la invención.

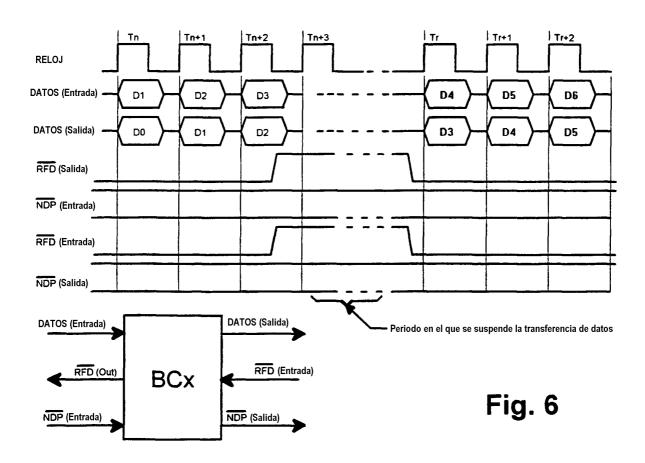

La figura 6 es un diagrama de temporización de flujo de datos en el bus del árbol.

30

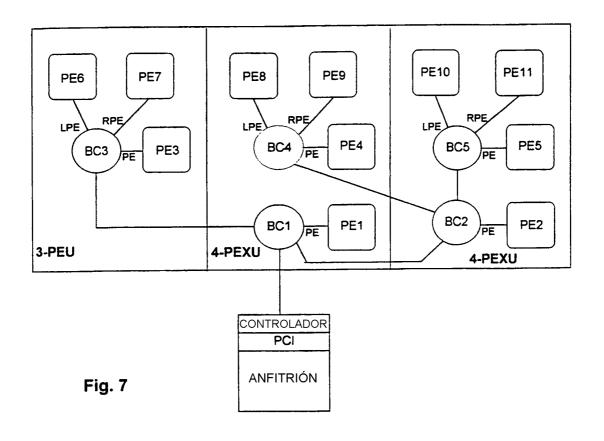

La figura 7 es un diagrama de bloques de una forma de realización de once procesadores de la invención.

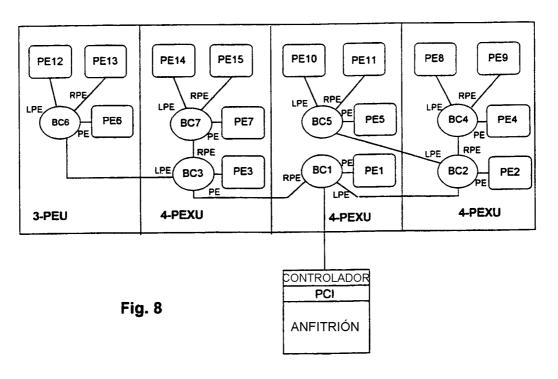

La figura 8 es un diagrama de bloques de una forma de realización de quince procesadores de la invención.

# 35 Descripción detallada

Haciendo referencia a la figura 1 de los dibujos, el sistema informático de árbol binario 11 de la invención interconecta una serie de Elementos de Procesador (PE) entre sí y con un ordenador anfitrión 13 a través de un bus de árbol binario. El bus de árbol del sistema ilustrado en la figura 1 consta de tres nodos de control de bus 15, 17 y 19 designados, respectivamente, como nodos BC1, BC2 y BC3. Los tres nodos conectan siete PE, designados como PE1 a PE7, al anfitrión 13. Todos los PE son idénticos y, en la forma de realización ilustrada, constan de un microprocesador, tal como un microprocesador de IBM Power PC 603e, y memoria RAM asociada con un circuito puente que interconecta los dos.

El nodo BC1 15 es el nodo raíz y une el árbol al anfitrión 13 a través de un controlador 14 y una interfaz, tal como un bus P.I. 16. El nodo BC1 15 está conectado a su propio PE, designado como PE1, y al nodo hijo izquierdo BC2 17 y al nodo hijo derecho BC3 19. Los nodos BC2 y BC3 están conectados cada uno de ellos a sus propios PE, PE2 y PE3 respectivamente, y a PE hijos izquierdos y derechos, PE4 y PE5, y PE6 y PE7, respectivamente. A PE4 y PE7 se les hace referencia como PE hojas ya que no tienen ningún otro hijo.

50

40

El sistema de la figura 1 ilustra la estructura básica del sistema informático paralelo de árbol binario de la invención. Cada nodo BCx está conectado aguas arriba a un nodo padre, excepto para el nodo raíz BC1, que está conectado al anfitrión. Cada nodo BCx está conectado también aguas abajo a su propio PE y o bien a dos nodos hijos BCx, o bien, en el caso de los nodos situados en los extremos del árbol, a PE hojas derecho e izquierdo.

55

60

65

hACIENDO referencia a la figura 2 de los dibujos, el bus de árbol binario de la forma de realización de la figura 1 incluye una interfaz de anfitrión (HIF) 21, tres nodos de control de bus de árbol BC1 15, BC2 17 y BC3 19 y siete entradas/salidas de procesador (PIO) 23, 25, 27, 29, 31, 33 y 35, una para cada PE. La HIF 21 comunica por interfaz el bus de árbol binario con el bus de conexión del Ordenador Anfitrión 13. En la forma de realización ilustrada de la invención, este bus es preferentemente un bus P.i., aunque podrían usarse otros. Los BCx actúan como repetidores con memoria intermedia que transfieren Llamadas de Función y datos desde el Ordenador Anfitrión hacia el (los) PE seleccionado(s), y datos con sus Mensajes de Fallo desde el PE seleccionado hacia el Ordenador Anfitrión. Las PIO transfieren datos entre sus PE respectivos y el bus de árbol binario en concordancia con los requisitos de las Llamadas de Función, y arbitran el acceso de la RAM asociada al PE respectivo entre las necesidades del microprocesador del PE y el bus de árbol binario.

Haciendo referencia a la figura 3 de los dibujos, la PIO 37 controla las lecturas/escrituras tanto del microprocesador de PE 39 como del bus de árbol binario con la RAM 41 del PE. Los datos fluyen entre el bus de árbol binario y la RAM 41 bajo el control del Control de PIO 43 de la PIO 37. La PIO 37 incluye también una memoria intermedia 45 que actúa para compensar retardos en la transferencia de datos, que pueden ser provocados por conflictos de arbitraje de memorias. La HIF 21 contiene por la misma razón una memoria intermedia similar.

En la forma de realización ilustrada, los datos en el bus de árbol binario tienen una amplitud de cuatro bytes más cuatro bits de paridad. Cuando están fluyendo hacia la RAM 41, los datos del bus de árbol son ensamblados por el Control de PIO 43 en ocho palabras de byte con bits de paridad asociados, en una memoria intermedia 45. Los datos son transmitidos desde la memoria intermedia 45 hacia la RAM 41 en modo de ráfagas, a no ser que se vaya a escribir solamente una palabra doble.

10

15

20

45

De forma similar, los datos son leídos desde la RAM 41 en modo de ráfagas y almacenados en la memoria intermedia 45 de la PIO 37. A continuación, los datos en la memoria intermedia 45 se desensamblan en un formato de cuatro bytes y son transmitidos sobre el bus de árbol a través de la interfaz de bus de árbol 47 bajo el control del nodo de control de bus de árbol binario BCx y el Control de PIO 43.

La HIF, los BCx y las PIO se implementan preferentemente cada uno de ellos con Matrices de Puertas Programables in situ (FPGA).

En la forma de realización ilustrada, para los datos se usa una longitud de palabra fija de ocho bytes (64 bits) más un bit de paridad impar por byte. Los datos se transfieren sobre el Bus de Árbol cuatro bytes en paralelo en cada señal de ciclo del reloj. La información de las Llamadas de Función es interpretada por el BCx.

- En el sistema informático de árbol binario de la forma de realización ilustrada de la invención, el ordenador anfitrión 13 genera instrucciones a las que se hace referencia como Llamadas de Función para controlar el funcionamiento del sistema. Las siguientes son las Llamadas de Función generadas por el ordenador Anfitrión en la forma de realización ilustrada de la invención:

- 30 La Llamada de Función ReinicializaciónS (Sreset) provoca la reinicialización de uno o la totalidad de los PE.

- La Llamada de Función Lfpga se usa para establecer controles lógicos usados por las Matrices de Puertas Programables in situ (FPGA) en los Nodos de Control de Bus de Árbol Binario (BCx), las PIO y la HIF.

- La Llamada de Función Inicialización provoca que los BCx establezcan la identificación (ID) de cada PE en el Sistema en función de la ID contenida en la Llamada de Función. A continuación, los BCx mantienen la identificación de los PE.

- La Llamada de Función Carga provoca que los Nodos de Control de Bus de Árbol Binario encaminen datos hacia el PE especificado por la ID y su PIO para cargar su memoria sin involucrar al microprocesador. No se ve involucrada ninguna interrupción de microprocesador.

- La Llamada de Función Examen provoca la transferencia de datos leídos desde la memoria de un PE hacia el anfitrión sin involucrar al microprocesador del PE.

- La Llamada de Función Liberación (reinicialización) le señaliza a cada microprocesador en el sistema que esté operativo.

- La Llamada de Función Escritura provoca que los nodos de Control de Bus de Árbol Binario encaminen datos y una especificación de tarea a un PE especificado y que los escriban en su memoria. La interrupción se usa para notificarle al microprocesador una tarea nueva y que sus datos están disponibles. El microprocesador confirma la aceptación de la tarea nueva. No obstante, el microprocesador puede continuar con la tarea que se está ejecutando cuando se realiza el acuse de recibo de la interrupción y a continuación, puede realizar la tarea nueva tal como se produce en una cola de tareas.

- La Llamada de Función Lectura usa una interrupción en el PE especificado para averiguar si los datos están preparados para ser leídos. Cuando se observa que están preparados, los datos se leen de la memoria del PE y se transfieren al ordenador anfitrión.

- 60 La Llamada de Función Difusión General provoca que datos y una especificación de tarea se transfieran simultáneamente desde el ordenador anfitrión a todos los PE. La interrupción se ve involucrada de la misma manera que la Escritura anterior.

- La Llamada de Función Resolución conlleva funciones de tipo tanto lectura como escritura con interrupción. Cuando están preparados, los datos se leen de los PE más alejados y se escriben en los PE en el siguiente nivel del bus del árbol hacia el ordenador anfitrión. En el caso de los PE hojas, los datos se leen hacia el PE del BC al que están

conectados. El PE en ese nivel selecciona los "mejores resultados", según unos criterios preescritos, de entre sus "mejores resultados" y los recibidos. A continuación, los "mejores resultados" se transfieren hacia el anfitrión al siguiente nivel del bus de árbol cuando se recibe una función de lectura desde ese nivel. Este proceso continúa hasta que los "mejores resultados" resueltos por PE1 son transferidos al ordenador anfitrión.

5

10

30

35

40

50

60

La figura 4 ilustra un ejemplo de la Llamada de Función Resolución. Los "mejores resultados" son calculados por el SPE 53 y el RPE 55 y son almacenados en su memoria asociada comenzando en la dirección "datos DMA". A continuación, los mejores resultados se transfieren desde la memoria del LPE 53 a través del BC2 57 hacia la memoria del PE 59, comenzando en la dirección Datos DMS LPE por parte del BC1 61. Seguidamente, los mejores resultados se transfieren desde la memoria del RPE 55, a través del BC3 63, hacia la memoria del PE 59 comenzando en la posición Datos DMA RPE por parte del BC1 61. Finalmente, el PE 59 selecciona los mejores resultados de entre los recibidos desde el LPE 53 y el RPE 55 y los que calculó el propio PE 59, y los resultados se almacenan en la memoria del PE 59 comenzando en la posición Datos DMA.

15 Los BC usan Tiempos Límite incluidos en Llamadas de Función involucradas en la transferencia de datos, para monitorizar tiempos de inactividad y evitar que el sistema se cuelque sin medios para reiniciarse. Los valores de los tiempos límite son fijados por el software del anfitrión y se pueden cambiar si la experiencia demuestra que los mismos son demasiado cortos o demasiado largos. Los Tiempos Límite son usados por los BC cuando se interrumpe el flujo de transferencia de datos o mientras se espera a que se complete una tarea. Existe un Contador 20 de Tiempos Límites en cada uno de los BC. El campo de Tiempo Límite en la Llamada de Función es un byte (8 bits), aunque el Contador de Tiempos Límites tiene una precisión de dos bytes (16 bits). El valor en el campo de Tiempo Límite de la Llamada de Función se compara con el byte más significativo del Contador de Tiempos Límites. El Contador de Tiempos Límites se reinicializa a todos ceros cada vez antes de ser usado. El Temporizador de Tiempos Límites se hace avanzar por medio de la señal de reloj usada para la transferencia de datos. Si se agota el 25 Tiempo Límite mientras se espera a que se produzca una transferencia de datos durante una función de lectura, el BC completa la transferencia de N palabras dobles llenadas con espacios en blanco con el Mensaje de Fallo añadido. Si el Tiempo Límite en la Llamada de Función se fija a todos ceros, los Tiempos Límite no se ejecutan. Si, durante una función, se produce más de un fallo de Tiempo Límite, se informa sobre el más próximo al ordenador Anfitrión.

Se añade un "Mensaje de Fallo" al final de cada flujo continuo de datos que se esté transfiriendo hacia el ordenador anfitrión. El mismo consta de cuatro bytes que contienen la ID del PE o BC en el que se ha detectado la condición de fallo, seguida por dos bytes que identifican la condición de fallo. Se añade también un Mensaje de Fallo cuando no se detecta ningún fallo para ser indicado como tal. El Mensaje de Fallo se origina en una PIO y puede ser corregido por un BC. Si se detecta más de una condición de fallo, se utiliza la más próxima al anfitrión. Si se ha detectado más de un fallo en una PIO o BC, se informa sobre el que se ha producido en último lugar.

La mayoría de secuencias de Llamadas de Función conllevan funciones alternas de "lectura" y "escritura". Sobre condiciones de Fallo detectadas durante una función de "escritura", se informa en la función de "lectura" posterior siempre que en las dos esté involucrado el mismo PE/BC. Las condiciones de fallo típicas en el sistema de la forma de realización ilustrada de la invención incluyen fallos de Llamadas de Función, tiempos límite, errores de paridad, transferencia incompleta de datos, dirección de memoria fuera de los límites y fallos de microprocesador.

Si en una Llamada de Función se produce un código no admisible, la condición es detectada habitualmente por el BC1 15. Un BC detecta una ID no existente en el nivel más alejado del ordenador anfitrión 13 cuando ninguna de sus ID hojas coincide con la ID.

Se pueden producir errores de paridad durante transferencias de Llamadas de Función o Datos en el bus del árbol. Asimismo, se pueden detectar errores de paridad durante transferencias de datos/direcciones en el microprocesador o en la memoria del PE.

Si no se transfiere un total de N palabras dobles, la PIO implicada indica un fallo.

Se declara un fallo de desbordamiento de datos si se pierden datos durante la transferencia de los mismos. Esto debería detectarse también si se transfiere algo que no sea N palabras.

La figura 5 de los dibujos ilustra las líneas de señal del bus de árbol. Dichas líneas de señal se ilustran de manera que están entre un bloque 49, que puede ser la HIF 21 o un BCx, y otro bloque 51, que puede ser otro BCx o una PIO conectada a un PE. Las líneas de señal del Bus de Árbol usadas para transferir Llamadas de Función y Datos están constituidas por:

IDB (Bus de Funciones/Datos) Treinta y dos líneas paralelas bidireccionales usadas para transferir información de datos y funciones.

65 IDP (Paridad de Funciones/Datos) Cuatro líneas bidireccionales usadas para transferir los bits de paridad impar para los bytes correspondientes en el bus IDB.

RFD (Preparado para Datos) La HIF, el BCx o la PIO está preparado para recibir los siguientes dos bytes de datos.

5 NDP (Datos Nuevos Presentes) La HIF, el BCx o la PIO tiene datos nuevos presentes para ser transferidos.

Señales adicionales usadas que no están en el Bus de Árbol incluyen Reloj para temporizar ciclos, Reinicialización a Nivel de Hardware, y Cargar Lógica.

Los Nodos de Control de Bus (BCx) funcionan como repetidores para actuar conjuntamente como una brigada de transferencia en cadena (*bucket brigade*) con el fin de transferir datos entre la HIF y los PE, y de PE a PE. Haciendo referencia al diagrama de temporización de la figura 6, esto se logra con el uso de las señales "Preparado para Datos" RFD y "Datos Nuevos Presentes" (NDP). Tal como se ilustra en la figura 6, se transfieren datos a través del BCx (ENTRADA DATOS y SALIDA DATOS) en ciclos de reloj consecutivos hasta que RFD (ENTRADA) es negada por el siguiente BC de aguas abajo en la cadena indicando que no está preparado para aceptar otra transferencia de datos. Esto provoca que el BCx niegue RFD (SALIDA) para provocar una pausa aguas arriba en la transferencia de datos. En este caso, RFD (ENTRADA) se vuelve a afirmar de tal manera que se puede reanudar la transferencia de datos. BCx retiene datos hasta que el proceso de transferencia continúa de manera que no se produce ninguna pérdida de datos cuando el flujo de transferencias se interrumpe momentáneamente.

20

25

30

50

55

Según un aspecto de la presente invención, el sistema informático de árbol binario se puede construir ventajosamente a partir de una pluralidad de subunidades. Por ejemplo, la versión de siete PE de la invención ilustrada en las figuras 1 y 2 de los dibujos está constituida por una unidad de tres PE (una "PEU") 67 conectada a una unidad de expansión de cuatro PE ("PEXU") 69.

El conjunto más pequeño de PE en un sistema de acuerdo con la invención es tres. En una configuración de este tipo, PE2 y PE3 se encuentran en las posiciones de hoja. Esta configuración se puede modificar a escala a siete PE usando una 3-PEU conjuntamente con una unidad de expansión 4-PEXU de cuatro que se pueden disponer adecuadamente en una sola placa de circuito impreso. En esta configuración, PE4 a PE7 son hojas gracias a que están situados en posiciones físicas de "hojas" sobre la placa de circuito impreso. Para aumentar la escala desde un sistema de 3-PEU a siete, el BC de la 3-PEU se conecta al primer BC de la 4-PEXU que está conectada a la interfaz de anfitrión.

Tal como se ilustra en la figura 7 de los dibujos, añadiendo una 4-PEXU adicional, se puede continuar con la expansión de la configuración hasta once PE. Esto da como resultado un árbol asimétrico, lo cual está permitido en la arquitectura. La configuración de once PE se puede expandir adicionalmente a la configuración de quince PE representada en la figura 8 mediante la adición de otra 4-PEXU. Este proceso puede continuar indefinidamente añadiendo otras 4-PEXU para construir un árbol binario del tamaño deseado. En general, un árbol construido de acuerdo con este aspecto de la invención se construirá a partir de una 3-PEU y de tantas 4-PEXU como sean necesarias. Por lo tanto, el árbol binario se puede expandir indefinidamente con solamente dos tipos de placa de circuito impreso, es decir, 3-PEU y 4-PEXU. La 4-PEXU tiene conexiones opcionales desde el primer BC. Por ejemplo, en las figuras 1 y 7, el BC1 está encaminado al BC2. En la figura 8, el BC1 se encamina al BC3 en la misma placa de circuito impreso.

Es significativo que, tal como se observa a partir de las figuras 1, 7 y 8, los PE posicionados a lo largo de un borde de las placas de circuito impreso son siempre PE hojas. Por lo tanto, los BCx saben qué PE unidos a los mismos son PE hojas.

El sistema informático de árbol binario de la presente invención resulta particularmente útil cuando se trata con aplicaciones tales como reconocimiento de voz o de otros patrones, en lo que una serie de unidades de datos se debe comparar con un número elevado de posibles valores con el fin de hallar la mejor coincidencia para cada unidad. En la resolución de dichos tipos de problemas, los datos de voz o de otros patrones que van a ser interpretados se descomponen en segmentos cortos que, a continuación, se comparan con respecto a una gran base de datos de valores normalizados para hallar la mejor coincidencia para cada uno. A continuación, las mejores coincidencias se ensamblan para identificar las palabras que están siendo pronunciadas. El sistema informático de árbol binario de la presente invención resulta particularmente adecuado para la solución de dichos problemas, puesto que los mismos implican un número muy elevado de cálculos y funciones de comparación similares que se pueden lograr de manera eficaz en paralelo con los mejores resultados devueltos al anfitrión.

El anfitrión en primer lugar distribuye a los PE, a través del bus de árbol, el software de comparación necesario y diferentes subconjuntos de los valores normalizados con respecto a los cuales se van a comparar segmentos de voz durante el proceso de reconocimiento. Usando la Llamada de Función *Difusión General*, el anfitrión a continuación difunde de forma general secuencialmente los segmentos de voz sucesivos a la totalidad de los PE en paralelo. Cada uno de los PE compara los segmentos de voz con la base de datos almacenada en su memoria asociada con el fin de determinar la coincidencia más afín y almacena una identificación y la afinidad de la coincidencia en una

posición predeterminada en su memoria asociada. Si no existe ninguna coincidencia a menos de una distancia de comparación definida, el PE meramente almacena una indicación de no coincidencia en dicha posición de memoria. A continuación, usando la Llamada de Función *Resolución*, el anfitrión provoca que los PE hojas izquierdo y derecho de cada BC en los extremos del árbol, según la manera descrita antes, transfieran sus resultados al propio PE del BC en donde se selecciona la más afín de la totalidad de las tres coincidencias y la misma se envía al siguiente nivel superior del árbol. Este proceso se repite en cada nivel hasta que el PE raíz calcula la coincidencia más afín determinada por cualquiera de los PE y la misma es reenviada al anfitrión. El ensamblaje de los segmentos reconocidos en palabras se realiza en el anfitrión.

- Una pluralidad de segmentos de voz se puede almacenar en la memoria de cada PE por parte del ordenador anfitrión sin interrumpir el PE. El PE realiza sus cálculos de comparación a su propia velocidad y almacena los resultados en las posiciones de memoria designadas sin tener que esperar al anfitrión u otros PE del árbol. A continuación, el bus del árbol desplaza los resultados hacia el anfitrión a una velocidad determinada por el anfitrión y el reloj del bus del árbol. De esta manera, los PE pueden funcionar con una eficacia máxima sin tener que esperar a otras partes del sistema, y se maximiza el rendimiento de este último. Las PIO arbitran cualesquiera demandas, en conflicto, de acceso a memoria por parte del BC y el microprocesador del PE.

- Si un BC del bus del árbol no está preparado para recibir o enviar información en sentido ascendente o descendente por el árbol, el mismo niega su señal RFD lo cual provoca que todos los BC en el camino de la información entren en pausa hasta que el BC señalizador esté preparado. De este modo, cualquier cuello de botella temporal en el sistema es absorbido por el bus del árbol en lugar de dejar que el mismo ralentice los PE.

### REIVINDICACIONES

1. Sistema de ordenador de árbol binario (11) para ser conectado a un ordenador anfitrión (13) y para ser controlado por el mismo, que comprende:

5

N controladores de bus (BC) conectados en una configuración de árbol binario, en la que cada controlador de bus, excepto los situados en los extremos del árbol, están conectados a controladores de bus hijos izquierdo y derecho, siendo N un entero, siendo uno de dichos controladores de bus un controlador de bus raíz (BC1) para conectar a dicho ordenador anfitrión dichos controladores de bus conectados al árbol binario;

10

N elementos de procesado (23, 25, 27), uno unido a cada uno de dichos controladores de bus;

N + 1 elementos de procesado (29, 31, 33, 35) conectados, dos cada uno, como hijos derecho e izquierdo, a los controladores de bus en los extremos de dicho árbol binario;

15

30

35

incluyendo cada uno de dichos elementos de procesado un microprocesador (39) y una memoria (41);

incluyendo cada uno de dichos controladores de bus, para cada elemento de procesado conectado al mismo, una interfaz con memoria intermedia (PIO) que conecta dicho elemento de procesado a dicho controlador de bus para transmitir instrucciones y datos entre el controlador de bus y el elemento de procesado conectado, y unos medios para escribir información en la memoria del elemento de procesado conectado sin involucrar al microprocesador de dicho elemento de procesado conectado.

- Ordenador de árbol binario según la reivindicación 1, en el que cada uno de dichos controladores de bus incluye

unos medios para leer información desde dicha memoria del elemento de procesado conectado sin involucrar al microprocesador de dicho elemento de procesado conectado.

- 3. Sistema de ordenador de árbol binario según la reivindicación 1, en el que cada uno de dichos controladores de bus incluye además unos medios para interpretar las instrucciones recibidas desde el ordenador anfitrión y para ejecutar dichas instrucciones dirigidas al mismo y para trasladar instrucciones a controladores de bus en sentido descendente por el bus del árbol si dicha instrucción va dirigida a uno o más de dichos controladores de bus.

- 4. Sistema de ordenador según la reivindicación 1, en el que cada uno de dichos controladores de bus incluye además unos medios para generar una señal cuando no está preparado para enviar información en sentido ascendente o descendente por el árbol con el fin de provocar que todos los controladores de bus en el camino de la información entren en pausa hasta que el controlador de bus que genera dicha señal deje de hacerlo.

- 5. Sistema de ordenador según la reivindicación 1, que presenta M controladores de bus, siendo M un entero impar mayor que 1, que incluye además una pluralidad de placas de circuito impreso, y en el que uno de dichos controladores de bus está dispuesto en una de dichas placas de circuito impreso y los restantes controladores de bus están dispuestos, dos cada uno, en unas placas adicionales de dichas placas de circuito impreso.

- 6. Sistema de ordenador según la reivindicación 5, en el que los elementos de procesado conectados a los controladores de bus en los extremos de dicho árbol binario están dispuestos todos ellos a lo largo de un borde de dichas placas de circuito impreso.