OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

① Número de publicación: 2 364 099

(51) Int. Cl.:

G01S 19/32 (2006.01) G01S 19/37 (2006.01)

|          | `  | ,                               |

|----------|----|---------------------------------|

| (12      | 2) | TRADUCCIÓN DE PATENTE EUROPEA   |

| <u> </u> | _  | THE DOCUMENT OF THE PORT OF THE |

Т3

- 96 Número de solicitud europea: 07872189 .1

- 96 Fecha de presentación : 19.10.2007

- 97 Número de publicación de la solicitud: 2082257 97 Fecha de publicación de la solicitud: 29.07.2009

- 54 Título: Receptor L1/L2 GPS con lógica programable.

- (30) Prioridad: **19.10.2006 US 852642 P**

- (73) Titular/es: DATAGRID. Inc. 1022 NW 2nd Street Gainesville, Florida 32601, US

- (45) Fecha de publicación de la mención BOPI: 24.08.2011

- (2) Inventor/es: Fridman, Alexander

- (45) Fecha de la publicación del folleto de la patente: 24.08.2011

- 74 Agente: Ponti Sales, Adelaida

ES 2 364 099 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### DESCRIPCIÓN

Receptor L1/L2 GPS con lógica programable.

#### 5 Antecedentes

Esta descripción se refiere en general a receptores vía satélite de un sistema de posicionamiento global (GPS) y, más particularmente, a una misma estructura general del mismo y a secciones específicas de procesamiento de señal digital dentro de dichos receptores.

Los satélites GPS transmiten señales de espectro extendido en bandas de frecuencia L1 y L2 a 154fo y 120fo respectivamente, donde fo = 10,23 MHz. Cada una de las señales L1 está modulada por código C/A y código P, que son únicos para cada satélite. Ambos códigos se conocen públicamente. Cada una de las señales L2 es modulada por el código P solamente. Aunque las secuencias de código C/A y código P son conocidas, cada satélite GPS está provisto de la capacidad de modular su código P con una señal secreta generalmente conocida como código W. Este "anti-spoofing" (A/S) permite que el sistema GPS sea utilizado para aplicaciones militares mediante la prevención de señales de interferencia sobre la base de códigos P conocidos que sean interpretados como señales GPS reales. La combinación del código P y del código W se suele denominar como el código Y.

Hay ventajas importantes para obtener acceso a las señales L1 y L2. En primer lugar, la refracción ionosférica puede ser medida y eliminada mediante el coprocesamiento de la pseudodistancia L1 y L2, lo que permite lograr una mayor precisión en aplicaciones independientes. En segundo lugar, para las aplicaciones de encuesta, hay una ventaja significativa con el uso de mediciones de fase portadora de las señales L1 y L2 en los sistemas de diferencia de fase. Las mediciones de la fase portadora L2 complementarias con las de L1 redoblan el número total de observables, y hacen que sea posible organizar los observables llamados de "vía amplia" que mejoran notablemente el rendimiento de la resolución de ambigüedad de fase.

Sin embargo, los sistemas y procedimientos existentes para el manejo de la señal L1 y L2 tienen desventajas. En particular, por ejemplo, las técnicas actuales de recuperación de la fase portadora L2 del código Y se están volviendo obsoletas porque los sistemas GPS evolucionan. Por ejemplo, las estructuras receptoras conocidas no son capaces de explotar las posibilidades del nuevo código L2c más robusto, que estará disponible para usuarios civiles. Las estructuras receptoras conocidas suelen ser difíciles o imposibles de adaptar a nuevas aplicaciones, ya que son implementadas mediante circuitos integrados de aplicaciones específicas (ASICs). Además, estos ASICs pueden ser costosos.

Además, las estructuras receptoras conocidas normalmente consumen energía y otros recursos de alto nivel con el fin de procesar las señales L1 y L2 de una manera aceptable. Ganguly, "Real-time dual frequency software receiver", simposio de posición, localización y navegación, 2004, describe un receptor de navegación en tiempo real basado en software. La patente US 5663733 describe un receptor de sistema de posicionamiento por satélite. La patente 5576715 describe un procedimiento y un aparato para procesamiento digital en un receptor de sistema de posicionamiento global. La patente 6125135 describe un sistema y un procedimiento de demodulación de señales GPS. La patente 5134407 describe un receptor de sistema de posicionamiento global.

El documento EP 0924532 describe la especificación funcional para el diseño de un receptor avanzado GPS y/o GLONASS (AGGR). El AGGR está preferentemente fabricado incluyendo al menos un subsistema implementado como un circuito integrado de aplicación específica (ASIC). La implementación ASIC del AGGR se conoce como el AGGA. La interfaz de extremo frontal del AGGA acepta señales de entrada de frecuencia intermedia (IF) digitalizada.

El documento EP 0924532 también describe un aparato para el procesamiento de señales de amplio espectro L1 y L2 recibidas de al menos un satélite de un sistema de posicionamiento global, donde cada una de las señales de amplio espectro incluye un soporte de frecuencia única con un código P pseudoaleatorio conocido y un código desconocido modulado en el mismo, que comprende: un generador de réplicas del código P conocido, un primer demodulador conectado al generador desmodular una de las señales recibidas L1 y L2 con una réplica del código P, un segundo demodulador para desmodular la otra de la señales recibidas L1 y L2 con una réplica del código P, un primer integrador para integrar de manera repetitiva y separada, la desmodulada de las señales L1 y L2 durante períodos de tiempo relacionados con el código desconocido, un segundo integrador para integrar de forma repetitiva y separada la otra desmodulada de las señales L1 y L2 durante períodos de tiempo relacionados con el código desconocido, un correlacionador para correlacionar un resultado de la etapa de integración de cada uno de las dos trayectorias de la señal L1 y L2 con la señal integrada de las otras trayectorias de la señal L1 y L2, y un ajustador de fase para el ajuste de las fases de las réplicas de código P generadas localmente en relación con las señales de entrada L1 y L2 con el fin de maximizar la potencia de correlación de las señales L1 y L2, en el que el correlacionador incluye: un comparador para comparar el valor absoluto de las señales L1 y L2 integradas desmoduladas, un combinador para combinar de forma individual los valores de las señales integradas desmoduladas L1 y L2 con un valor unitario que tiene el signo de las señales L1 y L2 desmoduladas integradas que tienen el mayor valor de salida mediante el comparador, y un primer acumulador para acumular individualmente y por separado las salidas del combinador de las señales L1 y L2 desmoduladas, y un segundo acumulador para acumular individualmente y por separado las salidas del combinador para la otro desmodulada de las señales L1 y L2. El combinador puede ser un multiplicador.

En consecuencia, hay una necesidad de un procedimiento de procesamiento y un sistema que mantenga una alta calidad al reducir la complejidad del hardware.

#### Descripción

La presente invención proporciona un procedimiento según la reivindicación 1. Realizaciones de la presente invención se dirigen a aspectos antes mencionados. Aquí se describe un receptor para el procesamiento de señales L1 y L2, donde el receptor es fácilmente configurable para procesar otros tipos de señales, tales como la señal L2c más robusta. Con este fin, el receptor puede comprender la lógica programable capaz de ser configurada y/o reconfigurada mediante, por ejemplo, un archivo de configuración en forma de datos electrónicos, tales como software o firmware. La lógica programable puede recibir el archivo de configuración de la memoria bajo el control de una unidad de procesamiento central (CPU), por ejemplo durante el encendido del receptor. Como que el receptor es fácilmente reconfigurable a través de los datos electrónicos del archivo de configuración, se evita la rigidez y el coste del ASIC.

15 Los receptores descritos en este documento pueden implementar un procedimiento eficiente de la presente invención que conserva una alta calidad al tiempo que permite que la complejidad del hardware se reduzca significativamente.

#### Breve descripción de los dibujos

20

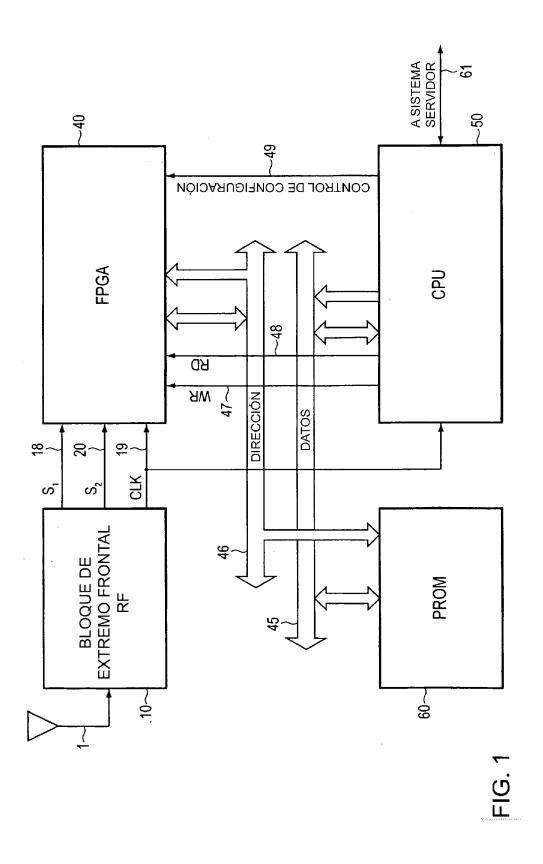

La figura 1 muestra un sistema de un receptor GPS de doble frecuencia;

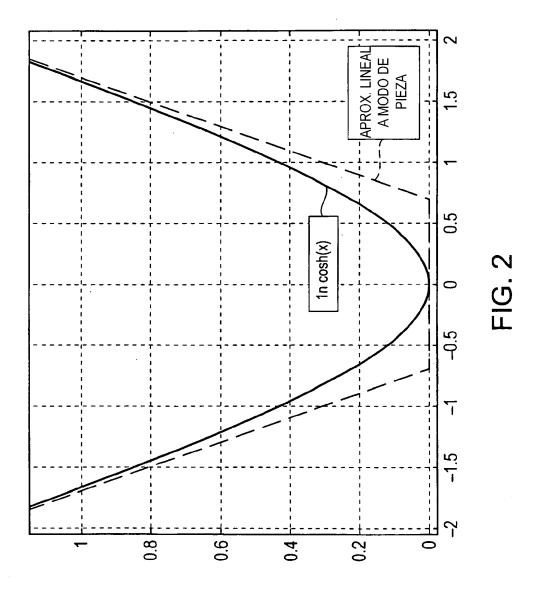

La figura 2 muestra una aproximación a modo de pieza de la función Ln cosh() de acuerdo con realizaciones de la presente invención;

25

30

45

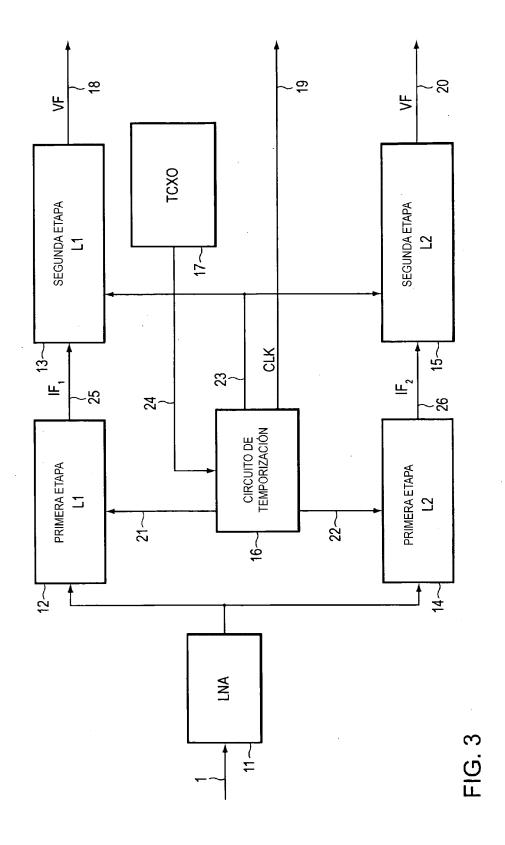

La figura 3 muestra una realización de una configuración de circuito del bloque de extremo frontal RF del sistema de la figura 1;

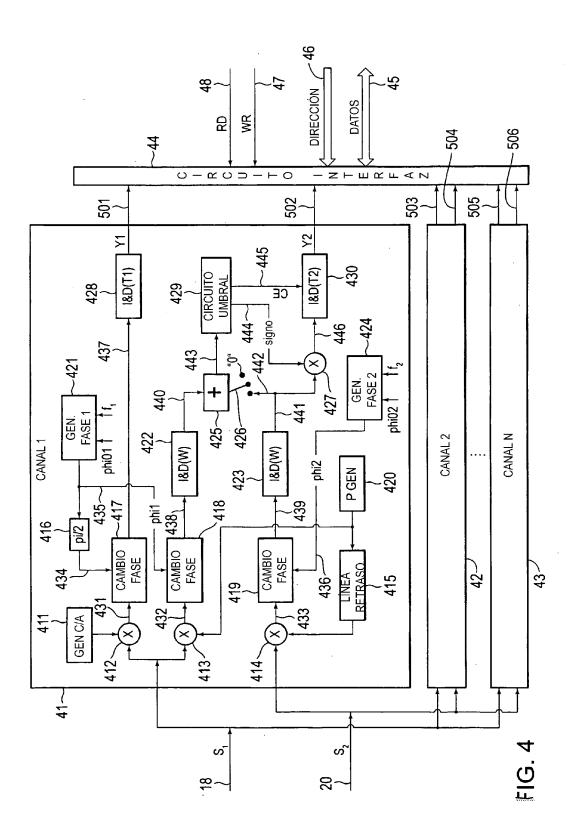

La figura 4 es un diagrama de bloques de una realización esquemática implementada en el sistema de la figura 1;

La figura 5 muestra detalles de una realización de circuitos de cambio de fase de la figura 4;

La figura 6 muestra detalles de una realización de un circuito de suma ponderada de la figura 4, y

La figura 7 ilustra etapas del proceso controladas mediante una unidad central de procesamiento (CPU) de acuerdo con realizaciones de la presente invención.

#### Descripción detallada de realizaciones

Tal como se mencionó anteriormente, ya que los sistemas GPS se están desarrollando, las nuevas señales están surgiendo en el rango de frecuencia L2, y nuevas señales están previstas para L1. Los consumidores se beneficiarían de un receptor versátil capaz de procesar señales de varias estructuras.

Se describe en este documento un receptor GPS que se puede utilizar la lógica programable, tal como una matriz de puerta de programable de campo (FPGA), para realizar funciones tales como procesamiento digital de múltiples canales de señales de navegación, en contraste con el anterior enfoque de desarrollo de circuito integrado de aplicaciones específicas (ASIC) para estas funciones. La lógica programable se puede conectar a una unidad de procesamiento programable central (CPU) a través de buses convencionales y señales de control, y ser capaz de recibir un archivo de configuración de funcionamiento de la CPU en cada inicio de encendido y ser capaz de volver a configurarse en cualquier momento. El archivo de configuración se puede almacenar en una memoria programable de sólo lectura (PROM). La CPU puede conectarse a la PROM mediante buses convencionales y señales de control. La CPU puede leer el fichero de configuración de la PROM y escribirlo en lógica programable en el inicio.

El receptor también puede comprender un bloque de extremo frontal de frecuencia de radio para amplificar, filtrar, convertir hacia abajo y digitalizar las señales de navegación L1/L2 recibidas, una PROM, y CPU que realiza el procesamiento adicional de los datos, soluciones de navegación y comunicación a un sistema de servidor externo.

Las ventajas de esta arquitectura de receptor incluyen la capacidad de adaptarse a la señal L2 codificada Y existente, así como a la nueva señal L2c y otras señales L1 o L2 futuras, sin ninguna modificación de hardware, que es difícil o imposible con los receptores tradicionales basados en ASIC. Un archivo de configuración simplemente se puede crear para una nueva señal. El archivo de configuración puede ser enviado a un usuario final. El usuario puede comunicar fácilmente el archivo de configuración de la CPU del receptor que, a su vez, puede actualizar el contenido de la PROM de manera correspondiente.

Otra de las ventajas de una arquitectura de receptor tal como se ha descrito en este documento es que puede haber varios archivos de configuración en la PROM del receptor que se vuelven a cargar de manera intercambiable y dinámica en la lógica programable (por ejemplo, FPGA) con el fin de adaptarse a diferentes situaciones durante el funcionamiento del receptor.

Otra ventaja de esta arquitectura de receptor es que elimina el alto coste del desarrollo ASIC.

Un receptor GPS tal como se describe aquí se puede utilizar, por ejemplo, en aplicaciones de navegación de estudio y de alta precisión (cinemáticas) en las que el acceso a las señales del portador L1 y L2 es necesario. La medición de la fase de pseudodistancia y pseudo-Doppler de ambas señales hace posible compensar la refracción ionosférica de las señales GPS, y asegura una rápida resolución de ambigüedad de fase en las aplicaciones de estudio (cinemáticas).

Tal como se indicó anteriormente, la presente invención implementa un procedimiento eficaz que conserva una alta calidad, al tiempo que permite que la complejidad del hardware se reduzca significativamente. El procedimiento puede llevar a cabo operaciones relacionadas con, por ejemplo, una aproximación de una función de probabilidad tal como se describe a continuación.

Las señales de entrada L1 y L2 complejas pueden representarse en tiempo continuo como:

15

$$S_1(t) = a_1 P(t) W(t) e^{j(\omega_1 t + \varphi_1)} + \xi_1(t)$$

señal compleja L1

$$S_2(t) = a_2 P(t) W(t) e^{j(\omega_2 t + \varphi_2)} + \xi_2(t)$$

señal compleja L2

donde:

25

30

35

a<sub>1</sub>, a<sub>2</sub>, son amplitudes reales de de la señal L1 y L2 de manera correspondiente, P(t) es un código P conocido,

W(t) es un código W desconocido,

$\omega_1$ ,  $\omega_2$  son frecuencias pseudo-Doppler en L1 y L2 de manera correspondiente,  $\omega_2 = 60/77 \ \omega_1$ ,

$\varphi_1, \varphi_2$  son las fases iniciales en L1 y L2 que cambian lentamente debido a los efectos de la ionosfera, y

$\zeta_1, \zeta_2$  son ruidos complejo de Gauss de media cero.

Las señales de entrada se multiplican por las réplicas correspondientes, y se integran en el intervalo de bit W. Las señales de réplica complejas son:

$$r_{1}(t) = P(t)e^{-j(\omega_{1}t+\varphi_{1})}$$

réplica compleja L1

$$r_{2}(t) = P(t)e^{-j(\omega_{1}t+\Psi)}$$

réplica compleja L2

En (2) se supone que el seguimiento en el código L1 C/A y la fase permite la alineación del código P de réplica con la de la señal de entrada, para establecer frecuencias de réplica iguales a las frecuencias de la señal, y para ajustar la fase L1 de la réplica igual a la fase de la señal  $\varphi_1$ . Esta última condición no se puede aplicar para L2, que es la razón por la qué la fase de réplica  $\psi$  se diferencia de  $\varphi_2$ . Las salidas del integrador complejo bit W pueden expresarse a partir de (1) y (2) como:

$$X_{1i} = \int_{t_i}^{t_i + T_w} S_1(t) r_1(t) dt = a_1 T_w w_i + \zeta_1$$

$$X_{2i} = \int_{t_i}^{t_i + T_w} S_2(t) r_2(t) dt = a_2 T_w w_i e^{j\theta} + \zeta_2$$

(3)

donde:

60

65

$\zeta_1, \zeta_2$  son variables complejas de Gauss de promedio cero,

$\theta = \varphi_2 - \psi$  es una diferencia de fase desconocida que se estimará,

T<sub>w</sub> es una duración de un intervalo de bit W, y

$w_i = \pm 1$  es un valor bit W desconocido en el intervalo de integración.

Indicando:

10

30

35

40

45

50

55

$$\begin{array}{ll}

x_i = \text{Re } X_{ti} \\

y_i = \text{Re } X_{2i} \\

z_i = \text{Im } X_{2h}

\end{array} \tag{4}$$

la función de densidad de probabilidad conjunta con la condición de  $\theta$ ,  $a_2$ , y  $w_i$  es:

15

$$p(x_i, y_i, z_i / \theta, a_1, w_i) = C \exp\left\{-\frac{a_1^2}{2\sigma^2} + \frac{w_i}{\sigma^2}(a_i x_i + a_2 y_i \cos \theta + a_1 z_i \sin \theta)\right\}$$

(5)

Suponiendo que el código W es estadísticamente independiente bit a bit, y las probabilidades de +1 y -1 son de 0,5 cada uno, dando la función de densidad de probabilidad incondicionada siguiente (por w<sub>1</sub>):

$$p(x_i, y_i, z_i/\theta, a_i) = C_1 \cosh(\frac{a_1 x_i + a_2 y_i \cos \theta + a_1 z_i \sin \theta}{\sigma^2}) \cdot \exp\{-\frac{a_1^2}{2\sigma^2}\}$$

(6)

A partir de (6), un logaritmo de una función de probabilidad para el intervalo de bit W i-ésimo sigue como:

$$L_i(\theta, \alpha_2) = \ln p(x_i, y_i, z_i / \theta, \alpha_2) = \ln C_i + \ln \cosh(\frac{\alpha_1 x_1 + \alpha_2 y_2 \cos \theta + \alpha_2 z_1 \sin \theta}{\sigma^2}) - \frac{\alpha_2^2}{2\sigma^2}, \tag{7}$$

y durante un período de estimación general que incluye m intervalos bit W:

$$L(\theta, a_2) = \sum_{i=1}^{m} L_i(\theta, a_2) = m \ln C_1 + \sum_{i=1}^{m} \ln \cosh(\frac{a_1 x_i + a_2 y_i \cos \theta + a_2 z_i \sin \theta}{\sigma^2}) - m \frac{a_1^2}{2\sigma^2},$$

(8)

En una operación ausente de las técnicas conocidas, el procedimiento de aproximación utiliza una aproximación lineal a tramos de la función Ln cosh(). Volviendo a la figura 2, se muestra la función Ln cosh() y su aproximación, representada como:

En

$$\cosh(u) \approx \begin{cases} u - 0.69 & \text{si } u > 0.69 \\ 0 & \text{si } |u| \le 0.69 \\ -u - 0.69 & \text{si } u < -0.69 \end{cases}$$

(9)

60 Se deduce de (8), (9):

$$L(\theta, a_2) \approx m \ln C_1 - 0.69 m_1 + \sum_{i=1}^{q} \frac{a_i \overline{x}_i}{\sigma^2} + \sum_{i=1}^{q} \frac{a_2 \overline{y}_i \cos \theta + a_2 \overline{z}_i \sin \theta}{\sigma^2} - m \frac{a_2^2}{2\sigma^2}, \tag{10}$$

donde:

40

50

55

5

$$\vec{z}_i = x_i, \vec{y}_i = y_i, \vec{z}_i = z_i$$

, si  $\frac{a_1 x_i + a_2 y_i \cos \theta + a_1 z_i \sin \theta}{\sigma^2} > 0.69$

$\vec{z}_i = 0, \vec{y}_i = 0, \vec{z}_i = 0$ , si  $\frac{|a_1 x_i + a_2 y_i \cos \theta + a_2 z_i \sin \theta|}{\sigma^2} \le 0.69$ ,

$\vec{z}_i = -x_i, \vec{y}_i = -y_i, \vec{z}_i = -z_i$ , si  $\frac{a_1 x_i + a_2 y_i \cos \theta + a_2 z_i \sin \theta}{\sigma^2} < 0.69$

y  $m_1$  es el número de artículos con  $x_i$  no cero.

La estimación de máxima probabilidad de  $\theta$  a partir de (10):

20

$$\theta_{ML} = \arctan(\frac{\sum_{i=1}^{m} \bar{z}_{i}}{\sum_{i=1}^{m} \bar{y}_{i}})$$

25

$$a_{2ML} = \frac{1}{m} \sqrt{(\sum_{i=1}^{m} \bar{y}_{i})^{2} + (\sum_{i=1}^{m} \bar{z}_{i})^{2}}$$

30

En un modo de seguimiento de estado estable, el valor de  $\theta$  se aproxima a cero, por lo que (11) se convierte en:

$$\bar{x}_{i} = x_{i}, \, \bar{y}_{i} = y_{i}, \, \bar{z}_{i} = z_{i}, \quad \text{si} \quad a_{1}x_{i} + a_{2}y_{i} > 0.69\sigma^{2}

\bar{x}_{i} = 0, \, \bar{y}_{i} = 0, \, \bar{z}_{i} = 0, \quad \text{si} \quad |a_{1}x_{i} + a_{2}y_{i}| \leq 0.69\sigma^{2}

\bar{x}_{i} = -x_{i}, \, \bar{y}_{i} = -y_{i}, \, \bar{z}_{i} = -z_{i}, \quad \text{si} \quad a_{1}x_{i} + a_{2}y_{i} < 0.69\sigma^{2}$$

(13)

Por otro lado, en el modo de inicialización del valor de  $\theta$  es totalmente desconocido, así que mejores resultados se logran si no hay datos de L2 incluidos en la ecuación (11), es decir:

45

$$\begin{aligned} \overline{x}_i &= x_i, \overline{y}_i = y_i, \overline{z}_i = z_i, & \text{si} \quad a_1 x_i > 0.69\sigma^2 \\ \overline{x}_i &= 0, \overline{y}_i = 0, \overline{z}_i = 0, & \text{si} \quad |a_1 x_i| \le 0.69\sigma^2 \\ \overline{x}_i &= -x_i, \overline{y}_i = -y_i, \overline{z}_i = -z_i, & \text{si} \quad a_1 x_i < 0.69\sigma^2 \end{aligned}$$

Una de las ventajas de la expresión (12), que puede ser caracterizada como un "estimador", es que es un estimador directo, y no requiere un gradiente o un sistema de bucle cerrado para su implementación.

Otra de las ventajas del estimador (12) es que no incluye ninguna operación de multiplicación en la acumulación de sumas en el numerador y el denominador de (12).

Con referencia a la figura 1, se ilustra una realización de un sistema que se puede incluir en un receptor tal como se describe aquí. En el sistema, una señal recibida de una antena se aplica inicialmente a través de una línea de transmisión, tal como un cable RF 1, a un bloque de extremo frontal de radiofrecuencia (RF) 10. El bloque de extremo frontal 10 puede amplificar, convertir hacia abajo, filtrar y digitalizar la señal L1 y L2 en la señal recibida. El bloque de extremo frontal RF 10 puede, por ejemplo, colocarse de modo que sus señales de salida en las líneas 18 y 20 son de frecuencia de vídeo (VF) con el fin de aliviar aún más el procesamiento digital. La frecuencia real de las señales en las líneas 18 y 20 puede ser una frecuencia pseudo-Doppler. Las señales de salida del bloque de extremo frontal RF S<sub>1</sub> y S<sub>2</sub> pueden ser complejas para evitar pérdidas de datos importantes, por lo que cada una de las líneas 18 y 20 puede comprender dos sub-líneas de componentes de la señal real e imaginaria.

El procesamiento de señal digital puede implementarse en lógica programable, tal como una matriz de puerta programable de campo (FPGA) 40, que recibe señales L1 y L2 complejas mediante las líneas 18 y 20, realiza el procesamiento de correlación de múltiples canales, y proporciona datos de correlación a una unidad central de procesamiento (CPU) 50. La CPU 50 puede leer los datos de correlación con el uso de un bus de datos 45 antes de establecer el bus de direcciones 46 a una dirección de un canal y un elemento de interés, y establecer una señal de control de lectura en la línea 48 en un estado de habilitación.

La CPU 50 puede realizar después un procesamiento de correlación posterior de los datos leídos del FPGA 40. El procesamiento puede incluir operaciones de bucle bloqueado de fase (PLL) y bucle bloqueado de retardo (DLL), así como la generación de datos de control a los canales de correlación del FPGA como el retraso de código, fase pseudo-Doppler y frecuencia, tal como se explicará más adelante con mayor detalle. Para enviar los datos de control, la CPU 50 puede poner los datos en el bus de datos 45, estableciendo el bus de direcciones 46 a la dirección de un canal y punto de interés, y estableciendo la señal de control de escritura en la línea 47 en el estado de habilitación. La CPU 50 puede comunicarse con un sistema de servidor externo a través de la línea de comunicación 61, enviando la posición medida, la velocidad y datos de tiempo al servidor, y recibiendo varios datos de control desde el mismo para la adaptación de los parámetros del receptor a las peticiones del usuario.

Una memoria programable de sólo lectura (PROM) 60 puede contener un código ejecutable para la CPU 50. En la alimentación del receptor, la CPU 50 puede buscar instrucciones de arranque de la PROM 60, y ejecutarlas con el fin de cargar el código ejecutable en la memoria interna de acceso aleatorio (RAM) de la CPU mediante el bus de datos 45 y el bus de direcciones 46. Después de la carga, la CPU 60 puede comenzar a ejecutar las instrucciones de su memoria RAM interna.

Las operaciones después de la alimentación del receptor pueden incluir cargar un archivo de configuración al FPGA 40. El archivo de configuración del FPGA puede definir la funcionalidad de cada uno de los bloques lógicos configurables (CLBs) del FPGA, y las interconexiones entre los mismos, obteniendo de esa manera la funcionalidad de procesamiento deseada de la totalidad de los esquemas de la FPGA. El archivo de configuración de la FPGA se puede almacenar en la PROM 60 junto con el código ejecutable de la CPU. La CPU 50 puede leer el archivo de configuración de la FPGA de la PROM 60 con el uso del bus de datos 45 y el bus de direcciones 46, y los escribe en la FPGA 40 mediante de los mismos buses 45 y 46. Las señales complementarias se pueden aplicar a la FPGA 40 mediante la línea 49 para controlar el proceso de carga del archivo de configuración.

La PROM 60 puede ser capaz de almacenar varios archivos de configuración adaptados a diferentes condiciones de funcionamiento del receptor. La CPU 50 puede elegir uno de los mismos para la carga de alimentación del receptor de acuerdo a una preferencia del usuario, que también puede ser almacenado en la PROM 60. Además, el usuario puede ejecutar un comando a través de la línea de comunicación 61 para cambiar a una configuración de la FPGA diferente durante el funcionamiento normal del receptor. En tal caso, la CPU 50 puede leer un archivo de configuración deseado en la PROM 60, y lo carga en la FPGA 40 de la misma manera tal como se ha descrito anteriormente para el modo de arranque. De esta manera, se logra un alto grado y rapidez de adaptabilidad.

Cuando la nueva señal L2c está disponible y un diseño esquemático está listo para su procesamiento, el archivo de configuración correspondiente se puede cargar desde el sistema del servidor a través de la línea de comunicación 61 a la CPU 50, que se escribirá en la PROM 60. A continuación, la CPU puede cargar un nuevo archivo de configuración en cada alimentación del receptor de la misma manera tal como se describió anteriormente. En realizaciones, una parte de los canales de correlación en la lógica programable (por ejemplo, FPGA) se pueden configurar para procesar las señales L2c, mientras que otra parte se puede configurar para procesar las señales antiguas L2. En consecuencia, una arquitectura de receptor tal como se describe aquí está lista para la señal L2c nueva, y también se actualizarán fácilmente de vez en cuando con capacidad L2c cuando más satélites GPS con capacidad L2c se lancen en órbita.

50

Volviendo ahora a la figura 3, el bloque de extremo frontal RF 10 se muestra con más detalle. Las señales recibidas mediante la antena pueden aplicarse mediante el cable 1, que puede ser una línea de transmisión de alta frecuencia, a un amplificador de bajo ruido 11, cuya salida se aplica a las entradas de los canales L1 y L2. El canal L1 puede incluir una primera etapa 12 y una segunda etapa 13, mientras que el canal L2 puede incluir una primera etapa 14 y una segunda etapa 15. En la primera etapa L1 12, la señal puede ser filtrada, amplificada, y convertida en una señal de frecuencia intermedia IF<sub>1</sub> 25. De modo similar, en la primera etapa L2 14 la señal puede ser filtrada, amplificada, y convertida en una señal de frecuencia intermedia IF<sub>2</sub> 26. La señal IF<sub>1</sub> 25 puede ser también filtrada, amplificada, y convertida en frecuencia de vídeo en fase y componentes de fase en cuadratura, y digitalizarse en el bloque de la segunda etapa 13. La salida 18 del bloque 13 puede incluir dos líneas: una primera línea de una señal digital en fase LI, y una segunda línea de una señal digital L1 en cuadratura de fase. De modo similar, la señal IF<sub>2</sub> 26 puede ser filtrada, amplificada y convertida en frecuencia de vídeo en fase y componentes de fase en cuadratura, y digitalizarse en el bloque de la segunda etapa 15, con una salida 20, que puede incluir dos líneas: una primera línea de una señal digital en fase L2, y una segunda línea de una señal digital de cuadratura en fase L2. Los circuitos de los bloques 12-15 comprende amplificadores, mezcladores, filtros y convertidores analógico a digital que funcionan de una manera convencional para realizar las transformaciones de la señal antes mencionadas. En una realización de ejemplo, cada una de dos líneas de salida 18 es una línea de un bit, y cada una de dos líneas de salida 20 es también una línea de un bit, de manera que los convertidores analógico a digital de las segundas etapas 18 y 20 pueden ser simples comparadores con umbral cero.

Un oscilador de cristal de temperatura compensada (TXCO) 17 suministra una frecuencia de referencia en la línea 24, que se utiliza en el circuitos de tiempo 16 para generar señales de oscilador locales en las líneas 21, 22 y 23, así como una señal de reloj en la línea 19. Con este fin, el circuito de tiempo 16 comprende sintetizadores convencionales de frecuencia. La señal de salida 19 se usa para controlar el tiempo de todos los otros bloques del receptor.

Volviendo a la figura 4, se muestran el esquema de la FPGA 40. Señales complejas de entrada S1 y S2 se pueden suministrar a una pluralidad de canales de procesamiento de banda base idénticos 41 a 43, cada uno de los cuales se puede asociar con un satélite separado del que se recibe una señal. El número de canales de banda previsto puede ser suficiente para asegurar que un canal de banda está disponible para cada señal del satélite recibida. En una realización de ejemplo, las señales de cuatro o más satélites se utilizan para hacer una determinación del parámetro deseado (por ejemplo, posición, velocidad y tiempo). Cada uno de los canales de banda 41 a 43 puede ser capaz de reconocer las salidas digitalizadas del bloque de extremo frontal RF 10 en las líneas 18, 20 que corresponden a un satélite particular, mediante la descorrelación las señales S1 y S2 usando réplicas de origen local de los códigos C/A y s P únicos de un satélite determinado.

15

Tal como se ilustra en la figura 4, cada canal de banda 41 a 43 puede comunicar datos  $Y_1$  y  $Y_2$  derivados de las señales digitales  $S_1$  y  $S_2$  para la CPU 50 a través de los circuitos de la interfaz 44, que se pueden conectar a una de las líneas 501 a 506 al bus de datos 45 de acuerdo con un canal deseado y su elemento de datos  $Y_1$  o  $Y_2$  tal como se define mediante la CPU 50 mediante el establecimiento de una dirección correspondiente en el bus de direcciones 46. Los circuitos de interfaz 44 también se pueden utilizar para datos de control desde la CPU 50 a los canales de la banda ed base 41 a 43. La CPU 50 puede controlar el número de identificación del satélite, fase de código C/A, la fase de código P, frecuencias pseudo-Doppler  $f_1$  y  $f_2$ , y fases iniciales pseudo-Doppler phi01, phi02 para coincidir las réplicas generadas L1 y L2 con la señal recibida del satélite. Con este fin, la CPU 50 puede configurar el bus de direcciones 46 de acuerdo con un canal de destino y un punto de control, y poner los datos de control en el bus de datos 45. Mediante las líneas de control 47, 48, la CPU puede indicar el modo de lectura (RD) cuando recibe datos del canal  $Y_1$  o  $Y_2$ , o puede indicar un modo de escritura (WR) cuando transfiere datos de control a un canal.

Tal como se ilustra en la figura 4, la señal compleja S1 se puede mezclar en el mezclador 413 con una réplica de código P generada mediante el generador de código P 420, proporcionando así una salida desmodulada 432. La estructura y la organización del generador de código P 420 puede estar en conformidad con el "Documento de Control de Interfaz ICD-GPS-200C", de Arinc Research Corporation (1993), Figs. 3.3 ... 3.7, por ejemplo. De modo similar, la señal compleja S2 se puede mezclar en el mezclador 414 con la misma de réplica código P pero retrasada en una línea de retardo controlable 415, proporcionando así una salida desmodulada 433. Los mezcladores 413, 414 pueden invertir los signos de ambos componentes en fase y en fase en cuadratura de S<sub>1</sub> y S<sub>2</sub>, en consecuencia, si el código P actual o el valor de código P retrasado es 1, y los deja pasar sin cambios de otra manera.

Cada una de las señales parcialmente desmodulada 432 y 433 se pueden aplicar entonces a los cambiadores de fase respectivos 418 y 419, que compensan las fases pseudo-Doppler. Con este fin, un generador de fase L1 421 puede generar un valor de fase phi1 en la línea 435 de acuerdo con la fase inicial phi01 y la frecuencia  $f_1$ , y un generador de fase L2 424 genera un valor de fase phi2 en la línea 436, de acuerdo con la fase inicial phi02 y la frecuencia  $f_2$ . La CPU 50, a través del circuito de interfaz 44, puede establecer los valores de phi01 phi02, fi f2 antes del inicio del periodo de acumulación actual T2. Los cambiadores de fase 418 y 419 pueden girar virtualmente vectores representados mediante señales complejas  $S_1$  y  $S_2$  y mediante el ángulo phi 1 en la línea 435, y phi2 en la línea 436, según corresponda.

Un componente en fase de la señal desmodulada y Doppler-compensada L1 en la línea 438 se puede aplicar a acumulador 422 que integra la señal en un período de tiempo correspondiente a la duración del bit W. Simultáneamente, los dos componentes en fase y en cuadratura de fase de la señal L2 desmodulada y Doppler-compensada en la línea 439 se pueden aplicar a los acumuladores 423 que integran las señales a través del período de tiempo correspondiente en la misma duración del bit W. El componente en fase L1 acumulado de puede ser trabado en el circuito o una línea representada mediante 440, mientras que los componentes en fase y en cuadratura de fase L2 pueden ser trabados en un circuito o una línea representada mediante 441.

El componente en fase L2 acumulado entonces puede separarse del circuito 441 al circuito 442, y se aplica a una estación de suma ponderada 425 a través de un interruptor controlable 426. Simultáneamente, un componente en fase L1 acumulado en el circuito 440 se puede aplicar a otra entrada de la estación de suma ponderada 425. La CPU 50 puede cerrar o abrir el interruptor 426 antes del inicio del periodo de acumulación actual T2 mediante un comando que se envía mediante el circuito de interfaz 44 y el interruptor 426. La señal de salida de la estación de suma ponderada en el circuito o una línea representada mediante 443 se puede aplicar a un circuito de umbral 429, que extrae el signo de la señal 443 en la línea 444, y compara la magnitud de la señal en un circuito o una línea 443 a un umbral. La CPU 50, a través del circuito de interfaz 44, puede establecer un valor umbral antes del inicio del periodo de acumulación actual T2. Si la magnitud de la señal supera el umbral, el circuito 429 puede establecer su salida 445 a 1, de lo contrario, puede ponerlo a 0. De esta manera, las condiciones indicadas en la ecuación (13) se pueden comprobar cuando el interruptor 426 se cierra, y las condiciones indicadas en la ecuación (14) se pueden comprobar cuando el interruptor 426 está abierto.

La señal compleja acumulada L2 en el circuito o una línea representada mediante 441 también se puede mezclar en un mezclador 427 con la señal entregada mediante la línea 444. El mezclador 427 puede simplemente invertir los signos de los componentes en fase y en cuadratura de fase de la señal compleja en el circuito 441 si el valor de signo

actual es 1, y se deja pasar sin cambios de otra manera. La salida del mezclador en el circuito 446 se puede aplicar al acumulador 430, que integra la señal 446 en un período de tiempo (T<sub>2</sub>). Luego, la señal en la línea 445 se puede utilizar como una señal de habilitación de reloj (CE) de manera que el acumulador 430 añade su entrada en el circuito 446 a un valor previamente acumulado, sólo si la señal CE en la línea 445 es 1. De esta manera, una señal Y2 compleja deseada L2 se puede desarrollar en la línea 502, de acuerdo con la ecuación (12).

Tal como también se indica en la figura 4, la señal compleja S1 se puede mezclar en el mezclador 412 con una réplica de código C/A generada mediante el generador de código C/A 411, proporcionando así una salida desmodulada en el circuito 431. La estructura y la organización del generador de código C/A 411 pueden estar en conformidad con el "Documento de Control de Interfaz ICD-GPS-200C". El mezclador 412 simplemente invierte los signos de los componentes en fase y en cuadratura de fase de S1 si el valor de código C/A actual es 1, y se dejan pasar sin cambios de otra manera.

La señal desmodulada C/A 431entonces se puede aplicar a un cambiador de fase 417, que compensa la fase pseudo-Doppler. Para esta operación, el valor de la fase phi1 en la línea 435 generada por el generador de fase L1 421 de acuerdo con la fase inicial phi01 y la frecuencia  $f_1$  se puede cambiar en  $\pi/2$  en el cambiador de fase 416. La CPU 50, a través del circuito de interfaz 44, puede establecer los valores de phi01 y  $f_1$  antes del inicio de un período de acumulación actual  $T_1$ . El cambiador de fase 417 puede girar virtualmente el vector representado mediante la señal complejo  $S_1$  mediante el ángulo phi  $1 = \pi/2$  en la línea 434. La salida del cambiador de fase en el circuito 437 se puede aplicar al acumulador 428, que integra la señal compleja 437 durante un período de tiempo ( $T_1$ ). De esta manera, la señal Y1 compleja deseada L1 puede desarrollarse en la línea 501.

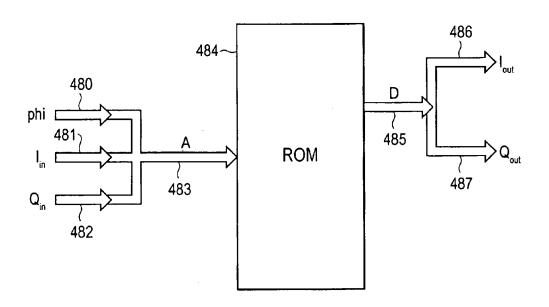

La figura 5 muestra cómo los cambiadores de fase 417 a 419 se pueden organizar para rotar su vector de entrada representado el componente en fase  $I_{\rm in}$  en un circuito o una línea representada mediante 481 y el componente en cuadratura de fase  $Q_{\rm in}$  en el circuito 482 mediante el ángulo phi en el circuito o un línea representada mediante 480. Los circuitos 480 a 482 se pueden fusionar en un solo circuito combinado 483 que se aplica como un bus de direcciones a una memoria de sólo lectura (ROM) 484. La ROM 484 puede almacenar valores predefinidos de la señal compleja cambiada que aparece en el bus de datos 485 en respuesta a la dirección A. El contenido de la ROM 484 puede calcularse previamente de tal manera que una parte del bus de datos 485 ofrece el componente en fase  $I_{\rm out}$  de la señal desplazada de fase en el circuito 486, mientras que otra parte suministra su componente en cuadratura de fase  $Q_{\rm out}$  en el circuito 487. De esta manera, una salida compleja deseada ( $I_{\rm out}$ ,  $Q_{\rm out}$ ) se puede generar para la combinación de todas y cada una de las señales de entrada ( $I_{\rm in}$ ,  $Q_{\rm in}$ ) y phi.

Para simplificar el bloque de suma ponderada 425, las ecuaciones (13), (14) se pueden aproximar en correspondencia:

$$\vec{x}_{i} = x_{i}, \vec{y}_{i} = y_{i}, \vec{x}_{i} = z_{i}, \quad \text{si} \quad 4x_{i} + 3y_{i} > \frac{0.69\sigma^{2}}{a_{i}}$$

$$\vec{x}_{i} = 0, \vec{y}_{i} = 0, \vec{z}_{i} = 0, \quad \text{si} \quad |4x_{i} + 3y_{i}| \leq \frac{0.69\sigma^{2}}{a_{i}}$$

$$\vec{x}_{i} = -x_{i}, \vec{y}_{i} = -y_{i}, \vec{z}_{i} = -z_{i}, \quad \text{si} \quad 4x_{i} + 3y_{i} < \frac{0.69\sigma^{2}}{a_{i}}$$

50 y

15

25

35

55

$$\vec{x}_i = x_i, \vec{y}_i = y_i, \vec{z}_i = z_i, \quad \text{si} \quad 4x_i > \frac{0.69\sigma^2}{a_1}$$

$$\vec{x}_i = 0, \vec{y}_i = 0, \vec{z}_i = 0, \quad \text{si} \quad |4x_i| \le \frac{0.69\sigma^3}{a_1}$$

$$\vec{x}_i = -x_i, \vec{y}_i = -y_i, \vec{z}_i = -z_i, \quad \text{si} \quad 4x_i < \frac{0.69\sigma^2}{a_1}$$

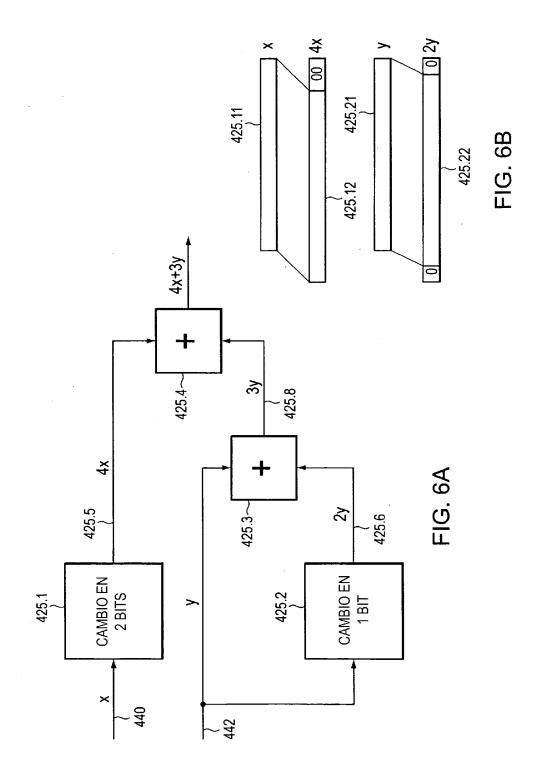

Las ecuaciones (15), (16) se basan en una relación de amplitud  $a_2/a_1 = 1/\text{sqrt}$  (2)  $\approx 0,707$ , de acuerdo con el "Documento de Control de Interfaz ICD-GPS-200C", y la relación de la amplitud  $a_2/a_1$  se aproxima en ¾ con precisión de aproximadamente el 6%. La figura 6 ilustra una realización del bloque de suma ponderada 425. El valor de entrada de múltiples bits x 425,11 en el circuito 440 puede cambiarse en 2 bits a la izquierda con reducción a cero de los bits liberados LSB tal como se indica en la figura 6(b). De esta manera, el valor cuadruplicado 4x 425,12 puede ser

entregado al circuito 425,7. De modo similar, el valor y de entrada de múltiples bits 425,21 en el circuito 442 puede ser cambiado en 1 bit a la izquierda con reducción a cero del bit liberado LSB y el bit MSB vacío como también se indica en la figura 6(b). De esta manera, el valor doble 2x 425.22 puede ser entregada al circuito 425,6. A continuación, los valores y y 2a se pueden añadir en una estación de suma 425,3, dando la señal 3y en el circuito 425,8, que también se puede añadir al valor 4x en otra estación de suma 425,4, produciendo una señal deseada 4x + 3y en el circuito o la línea 443. De esta manera, una suma ponderada deseada puede obtenerse sin complicadas operaciones de multiplicación.

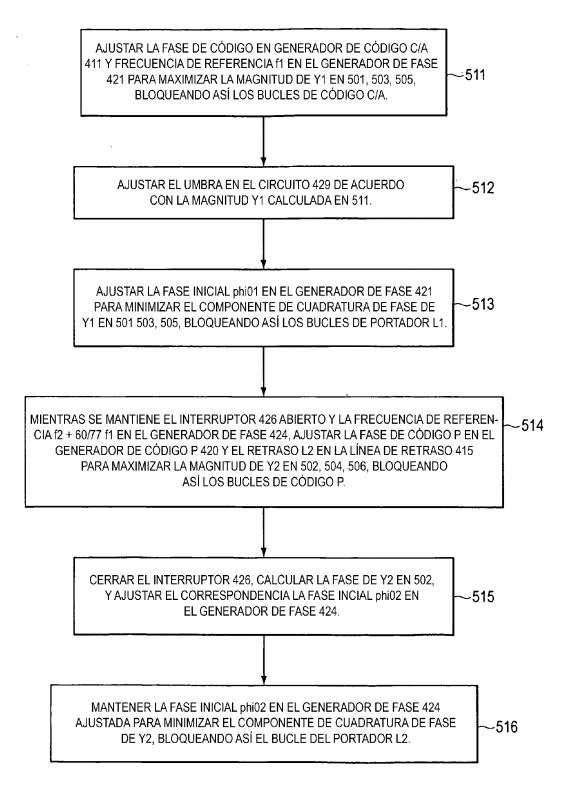

Con referencia a la figura 7, una técnica preferida se muestra para el ajuste y el bloqueo del portador y los generadores de código en fase con el portador y el código de las señales del satélite que se están procesando. En una primera etapa 511, la CPU 50 puede ajustar la fase de código C/A en el generador C/A 411 y la frecuencia de la réplica en el generador de fase 421 en cada uno de los canales de procesamiento 41 a 43 para maximizar la magnitud del vector Y1 en el circuito o líneas representadas mediante 501-505. Como todos los canales de procesamiento pueden ser de idéntica estructura, una descripción más detallada de la figura 7 se proporcionará sólo para un canal 41.

Cuando la magnitud Y1 alcanza el máximo, el código C/A nominal a la salida del generador C/A 411 está en fase con la señal L1 que se procesa, y la CPU 50 calcula la amplitud de la señal L1 como  $a_1 = [Y1]$ . A continuación, en una etapa 512, la CPU 50 puede establecer el umbral en el circuito 429 a 0,69  $\sigma^2/a_1$ ) de acuerdo con las ecuaciones (15), (16).

Una siguiente etapa 513 es para que la CPU 50 ajuste el phi1 de fase inicial en el circuito 435 y, en consecuencia, el circuito en fase 434 con el fin de minimizar el valor absoluto de la componente en cuadratura de fase de Y1 en el circuito o la línea 501. Cuando esto ocurre, la fase L1 nominal en el circuito 434 se sabe entonces que están en fase con la de la señal L1 que se está procesando. Esto proporciona una referencia inequívoca para el portador C/A L1, y por lo tanto también para el portador de código P L1 que se cambia en noventa grados respecto al mismo. A continuación, una diferencia de tiempo phi1 proporciona una estimación precisa de la frecuencia pseudo-Doppler f<sub>1</sub> que se utiliza en las siguientes etapas.

En una etapa 514, la CPU 50 puede comenzar a estimar los parámetros de la señal L2 mediante el ajuste de una frecuencia de referencia f<sub>2</sub> = 60/77 f<sub>1</sub> en el generador de fase L2 424, ajustando la fase de código P en el generador de código P 420, y ajustando el retraso L2 en la línea de retraso controlable 415 con el fin de maximizar la magnitud de Y2 en el circuito 502. Cuando esto ocurre, la fase de código P en la salida del generador de código P 420 es conocida por estar en fase con la señal L I que se procesa, y la fase de código P en la salida de la línea de retraso 415 se sabe que está en fase con la señal L2 que se está procesando. En este momento, la fase del vector Y2 contiene información sobre la fase pseudo-Doppler L2.

En una etapa 515, la CPU 50 puede calcular la fase pseudo-Doppler L2 mediante (12), y ajustar en consecuencia la fase inicial phi02 en el generador de fase 424. Esto proporciona el valor phi2 en el circuito 436 que garantiza la compensación de la fase pseudo-Doppler de la señal L2 en el cambiador 419. A su vez, esta compensación asegura de que el ángulo  $\theta$  en (11) es casi cero, por lo que es conveniente usar (15) en lugar de (16) en el proceso de generación del valor Y2. Por lo tanto, la CPU 50 puede cerrar el interruptor 426 para aplicar el componente en fase de la señal L2 en el circuito 442 a la entrada de la estación de suma ponderada 425.

En una etapa 516, la CPU 50 ajusta la fase inicial phi02 en el generador de fase 424 con el fin de minimizar el valor absoluto de la componente en cuadratura de fase de Y2 en el circuito 502. El valor phi02 es en realidad la fases pseudo-Doppler L2 deseada.

Cabe señalar que a las realizaciones de la presente invención se pueden aplicar las nuevas señales L3-L5. Además, las realizaciones se pueden utilizar en GPS, GNSS, o cualquier otro sistema similar o compatible.

De acuerdo con realizaciones de la presente invención, un archivo de configuración puede crearse simplemente para una nueva señal. El archivo de configuración puede ser enviado a un usuario final. El usuario puede comunicar el archivo de configuración a la CPU del receptor que, a su vez, puede actualizar el contenido de la PROM correspondiente.

Una arquitectura de receptor tal como se describe en este documento puede tener varios archivos de configuración de la PROM del receptor o estos archivos que se recargan de forma intercambiable y dinámica en la lógica programable (por ejemplo, FPGA) con el fin de adaptarse a diferentes situaciones durante el funcionamiento del receptor, podrían ser generados o modificados según sea necesario.

Se apreciará que varias de las características y funciones anteriormente descritas y otras, o alternativas de las mismas, pueden combinarse de manera deseable en muchos otros sistemas o aplicaciones diferentes. Además, varias alternativas, modificaciones, variaciones o mejoras no previstas en la actualidad o no anticipadas pueden ser realizadas posteriormente por los expertos en la materia, que también pretender estar incluidas mediante las siguientes reivindicaciones.

65

#### REIVINDICACIONES

- 1. Procedimiento para la derivación de una amplitud y una fase pseudo-Doppler de una señal L2 a partir de las señales L1 y L2 recibidas en un sistema de posicionamiento global, incluyendo cada una de dichas señales L1 y L2 una frecuencia portadora modulada separada modulada mediante un código P conocido y un código W desconocido, comprendiendo el procedimiento las etapas de:

- amplificar y filtrar las señales L1 y L2 recibidas desde una antena, y convertirlas hacia abajo a señales L1 y L2 de frecuencia de vídeo complejo;

convertir dichas señales L1 y L2 de frecuencia de vídeo complejo a un formato digital;

desmodular las señales L1 y L2 de frecuencia de vídeo digital complejo con una réplica de código P generada localmente para generar señales L1 y L2 complejas desmoduladas;

cambiar una fase pseudo-Doppler de dicha señal compleja desmodulada L1 por una fase digital generada localmente que cambia desde un primer valor de fase inicial de forma lineal de acuerdo con un primer valor de frecuencia para generar una señal L1 con compensación Doppler desmodulada;

- cambiar la fase pseudo-Doppler de dicha señal compleja desmodulada L2 por una fase digital generada localmente que cambia desde un segundo valor inicial linealmente de acuerdo con un segundo valor de frecuencia para generar una señal L2 con compensación Doppler desmodulada;

- integrar dichas señales L1 y L2 con compensación Doppler desmoduladas en un primer período de tiempo predefinido para generar las señales L1 y L2 preintegradas;

ponderar un componente en fase de dicha señal L1 preintegrada con un primer factor de ponderación para generar una señal L1 ponderada en fase;

- ponderar un componente en fase de dicha señal L2 preintegrada con un segundo factor de ponderación para generar una señal L2 ponderada en fase;

- añadir dicha señal L1 en fase ponderada a dicha señal L2 en fase ponderada para generar una señal en fase ponderada total;

- comparar una magnitud de dicha señal en fase ponderada total con un umbral predefinido para generar un indicador de exceso;

- invertir dicha señal L2 preintegrada mediante un signo de dicha señal en fase ponderada total para generar una señal L2 desencriptada; y

integrar dicha señal L2 desencriptada durante un segundo período de tiempo predefinido con la condición de dicho indicador de exceso para producir una señal L2 compleja integrada cuya magnitud es proporcional a la amplitud de salida deseada de la señal L2, y cuya fase, que se añade a dicha segunda fase inicial, es igual a una fase pseudo-Doppler de salida deseada de la señal L2.

- 2. Procedimiento según la reivindicación 1, que también comprende controlar dicho segundo factor de ponderación de manera que se ajuste a cero durante períodos de tiempo cuando no está disponible una estimación *a priori* de la fase pseudo-Doppler de la señal L2.

- 3. Procedimiento según la reivindicación 2, que también comprende:

45

desmodular la señal L1 de frecuencia de vídeo compleja digital con un réplica de código C/A para generar una segunda señal L1 desmodulada compleja;

cambiar dicha primera fase inicial en 90 grados para generar una tercera fase inicial;

- cambiar una fase pseudo-Doppler de dicha segunda señal L1 compleja desmodulada mediante una fase digital generada localmente que cambia desde dicho tercer valor de fase inicial de forma lineal de acuerdo con dicho primer valor de frecuencia para generar una segunda señal L1 con compensación Doppler desmodulada;

- integrar dicha segunda señal L1 de compensación Doppler desmodulada durante un tercer período de tiempo predefinido para producir una señal L1 integrada;

proporcionar dicha señal L1 integrada a un filtro de bucle de retroalimentación para generar una estimación de la fase pseudo-Doppler L1 y la frecuencia pseudo-Doppler; y

ajustar dicha primera fase inicial, de acuerdo con dichas estimaciones de fase pseudo-Doppler L1 y frecuencia pseudo-Doppler.

4. Procedimiento según la reivindicación 3, que también comprende: 5

10

15

20

25

30

35

40

45

50

55

60

65

restar dicha estimación de fase pseudo-Doppler L1 multiplicada por un factor de 60/77 a partir de una suma de dicha fase pseudo-Doppler de salida de la señal L2 y dicha segunda fase inicial para generar una diferencia de fase L1/L2;

suavizar dicha diferencia de fase L1/L2 para generar una diferencia de fase L1/L2 suavizada; y

ajustar dicha segunda fase inicial para ser igual a una suma de dicha estimación de la fase pseudo-Doppler L1 multiplicada por un factor de 60/77 y dicha diferencia de fase L1/L2 suavizada.

5. Procedimiento según la reivindicación 1, en el que la etapa de demodulación se realiza simultáneamente con la etapa de conversión.

FIG. 5

FIG. 7