OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

① Número de publicación: 2 367 835

(51) Int. Cl.:

**H03K 17/0812** (2006.01)

|          | `  | ,                               |

|----------|----|---------------------------------|

| (12      | 2) | TRADUCCIÓN DE PATENTE EUROPEA   |

| <u> </u> | _  | THE DOCUMENT OF THE PORT OF THE |

Т3

- 96 Número de solicitud europea: 06100448 .7

- 96 Fecha de presentación : **17.01.2006**

- Número de publicación de la solicitud: 1696565 97 Fecha de publicación de la solicitud: 30.08.2006

- (54) Título: Aparato inversor con control de puerta mejorado para mosfet de potencia.

- (30) Prioridad: 25.02.2005 JP 2005-51267

- 73 Titular/es: MITSUBISHI HEAVY INDUSTRIES, Ltd. 16-5, Konan 2-chome Minato-ku, Tokyo 108-8215, JP

- Fecha de publicación de la mención BOPI: 08.11.2011

- (72) Inventor/es: Okazaki, Yoshimi; Mori, Kiyoshi y Yamazaki, Hiroyuki

- (45) Fecha de la publicación del folleto de la patente: 08.11.2011

- (74) Agente: Carpintero López, Mario

ES 2 367 835 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## **DESCRIPCIÓN**

Aparato inversor con control de puerta mejorado para mosfet de potencia

#### Antecedentes de la invención

## 1. Campo de la invención

15

20

30

35

40

La presente invención se refiere a un aparato inversor, y en particular, se refiere a una técnica para controlar óptimamente puertas de los MOSFET de potencia (Transistores de Efecto de Campo de Metal Óxido Semiconductor) dentro de un aparato inversor.

#### 2. Descripción de la técnica relacionada

Un circuito de control de puerta que controla las puertas de los MOSFET de potencia dentro de un aparato inversor normalmente incluye un circuito de carga y un circuito de descarga. El circuito de carga se usa para cargar y polarizar a nivel alto las puertas de los MOSFET de potencia, y el circuito de descarga se usa para descargar y polarizar a nivel bajo las puertas.

En una configuración de inversor típica, se conectan un elemento de resistencia y un diodo en serie a lo largo de un camino de carga/descarga entre un circuito de carga/descarga y una puerta de un MOSFET de potencia. El elemento de resistencia se usa para ajustar la constante de tiempo del funcionamiento de carga/descarga, a la vez que se prevé el diodo para evitar que la intensidad de carga/descarga fluya en sentido inverso. El control de la constante de tiempo del funcionamiento de carga/descarga es importante para proporcionar un tiempo de conexión y un tiempo de desconexión deseados para el MOSFET de potencia y para de ese modo ajustar óptimamente un tiempo muerto. Por ejemplo, la solicitud de patente japonesa abierta a consulta por el público nº JP–A–Heisei 10–313242 da a conocer un aparato inversor que tiene un elemento de resistencia y un diodo conectado en serie a lo largo de un camino usado para cargar una puerta de un MOSFET de potencia, y que también tiene un elemento de resistencia a lo largo de un camino usado para descargar la puerta. Además, la solicitud de patente japonesa abierta a consulta por el público JP–P2002–223157A da a conocer un aparato inversor que tiene una bobina de inductancia de resonancia y un diodo en serie conectado a lo largo de un camino a través del que se descarga una puerta.

25 La patente de Estados Unidos US-3947727 da a conocer un inversor de la técnica anterior.

Un requisito impuesto al aparato inversor es el control de EMI (interferencia electromagnética, *electromagnetic interference*). Una causa de la EMI es la resonancia entre una capacidad drenador–fuente del MOSFET de potencia y una inductancia de interconexión, que puede producirse al llevar a estado de desconexión el MOSFET de potencia. Tal resonancia desarrolla de forma no deseable una intensidad de resonancia de una alta frecuencia, generando una EMI significativa. Posteriormente se da una descripción acerca de una resonancia entre la capacidad drenador–fuente y la inductancia de interconexión.

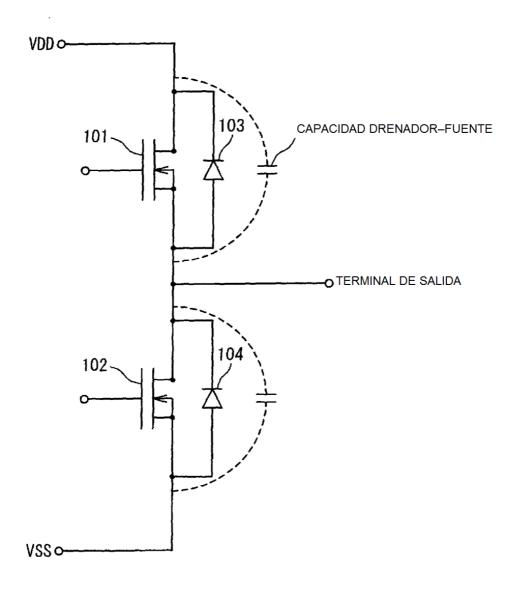

Con referencia a la figura 1, que muestra una configuración típica de una etapa de salida de un aparato inversor, la resonancia entre la capacidad drenador—fuente y la inductancia de interconexión está relacionada con las intensidades de recuperación de diodos 103 y 104 parásitos, que están incorporados en los MOSFET 101 y 102 de potencia. Por ejemplo, se considera un caso en el que el MOSFET 101 de potencia se conmuta del estado de conducción al estado de corte, y el MOSFET 102 de potencia se conmuta del estado de corte al estado de conducción posteriormente. Cuando el MOSFET 102 de potencia se conmuta al estado de conducción después de que el MOSFET 101 de potencia se conmute al estado de corte, el diodo 103 parásito manifiesta una recuperación inversa, y una intensidad de recuperación fluye a través del diodo 103 parásito. La intensidad de recuperación provoca la resonancia entre la capacidad drenador—fuente del MOSFET 101 de potencia y la inductancia de una interconexión conectada al MOSFET 101 de potencia, conduciendo al flujo de la intensidad de resonancia de una alta frecuencia.

Existe una necesidad de una técnica que reduzca la EMI provocada por la resonancia entre la capacidad drenador—fuente del MOSFET de potencia y la inductancia de interconexión.

## 45 Sumario de la invención

Por tanto, es un objeto de la presente invención proporcionar un aparato inversor que reduzca de forma eficaz la EMI provocada por la resonancia entre una capacidad drenador-fuente de un MOSFET de potencia y una inductancia de una interconexión conectada al MOSFET de potencia.

En un aspecto de la presente invención, un aparato inversor se compone de un MOSFET de potencia que tiene una fuente/drenador conectada a un terminal de salida; y un circuito de control de puerta que controla una puerta del MOSFET de potencia. El circuito de control de puerta incluye un camino de descarga conectado a la puerta del MOSFET de potencia. El camino de descarga incluye un conjunto de diodos conectados en serie que están conectados en sentido directo en el sentido de una intensidad de descarga desde la puerta del MOSFET de potencia.

Preferentemente, los diodos conectados en serie son diodos de silicio.

En otro aspecto de la presente invención, un aparato inversor se compone de: un primer MOSFET de potencia que tiene una fuente/drenador conectada a un terminal de salida; un segundo MOSFET de potencia que tiene una fuente/drenador conectada al terminal de salida; un primer circuito de control de puerta que controla una puerta del primer MOSFET de potencia; y un segundo circuito de control de puerta que controla una puerta del segundo MOSFET de potencia. Durante una polarización a nivel bajo de la puerta del primer MOSFET de potencia seguida de una polarización a nivel alto de la puerta del segundo MOSFET de potencia, el primer circuito de control de puerta controla la puerta del primer MOSFET de potencia de modo que una tensión puerta—fuente del primer MOSFET de potencia varía entre un 30% y un 70% de una tensión umbral del primer MOSFET de potencia con un sincronismo en el que el segundo circuito de control de puerta conduce una tensión puerta—fuente del segundo MOSFET de potencia a una tensión umbral del segundo MOSFET de potencia.

Preferentemente, la tensión puerta-fuente del primer MOSFET de potencia varía entre un 40% y un 60% de la tensión umbral del primer MOSFET de potencia con el sincronismo en el que el segundo circuito de control de puerta controla la tensión puerta-fuente del segundo MOSFET de potencia a la tensión umbral del segundo MOSFET de potencia.

En otro aspecto más de la presente invención, se prevé un procedimiento de funcionamiento para un aparato inversor que incluye unos MOSFET de potencia primero y segundo, teniendo el primer MOSFET de potencia una primera fuente/drenador conectada a un primer terminal de potencia y una segunda fuente/drenador conectada a un terminal de salida, y teniendo el segundo MOSFET de potencia una primera fuente/drenador conectada a un segundo terminal de potencia, y una segunda fuente/drenador conectada al terminal de salida. El método de funcionamiento incluye:

polarizar a nivel bajo una puerta del primer MOSFET de potencia para llevar al estado de corte al primer MOSFET de potencia; y

polarizar a nivel alto una puerta del segundo MOSFET de potencia para llevar al estado de conducción lineal el segundo MOSFET de potencia.

La tensión puerta-fuente del primer MOSFET de potencia varía entre un 30% y un 70% de una tensión umbral del primer MOSFET de potencia con un sincronismo en el que una tensión puerta-fuente del segundo MOSFET de potencia se conduce a una tensión umbral del segundo MOSFET de potencia durante la polarización a nivel alto de la puerta del segundo MOSFET de potencia.

## Breve descripción de los dibujos

5

10

15

20

25

30

35

40

45

50

55

La figura 1 es un esquema de circuito eléctrico que muestra una configuración típica de una etapa de salida dentro de un inversor trifásico;

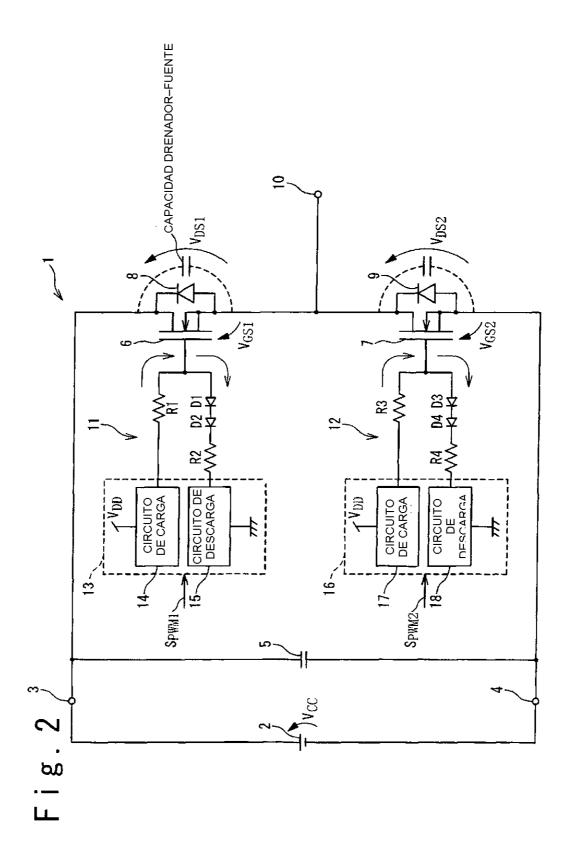

la figura 2 es un esquema de circuito eléctrico que muestra una configuración de un inversor trifásico en una realización de la presente invención;

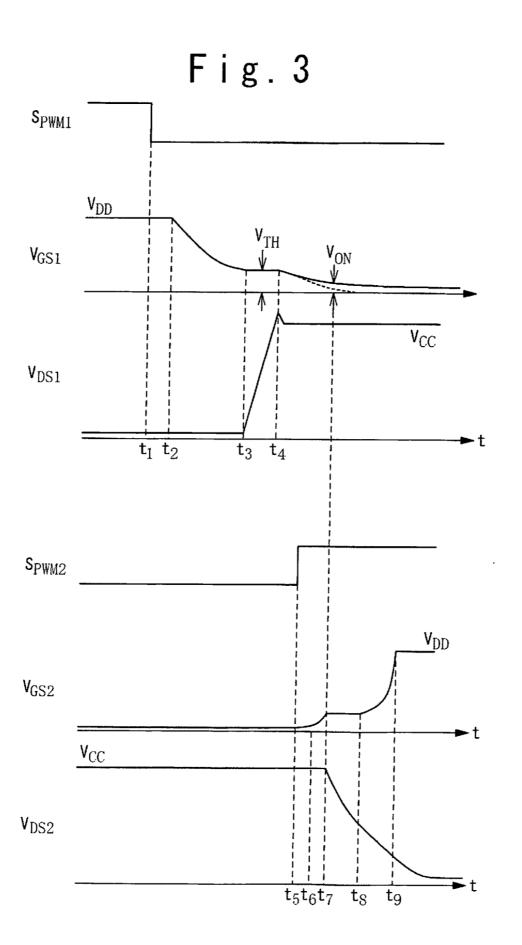

la figura 3 es un cronograma que muestra un funcionamiento de un inversor trifásico mostrado en la figura 2;

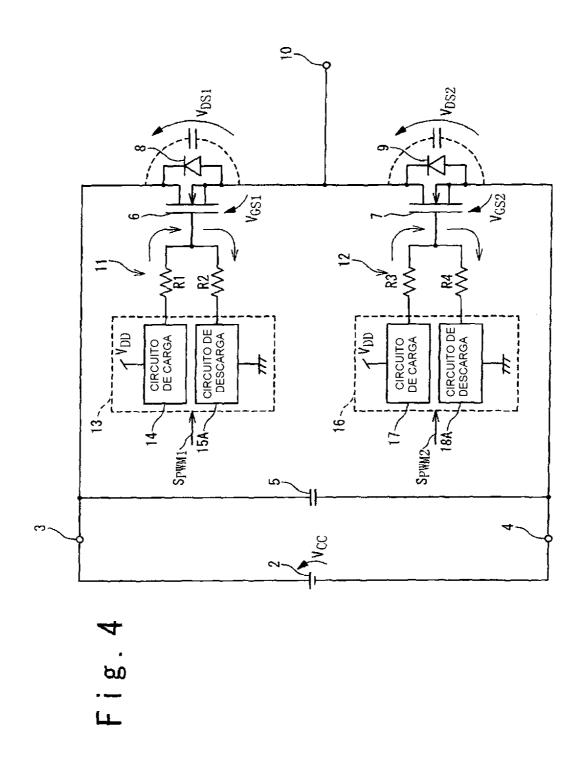

la figura 4 es un esquema de circuito eléctrico que muestra una configuración de un inversor trifásico en otra realización de la presente invención; y

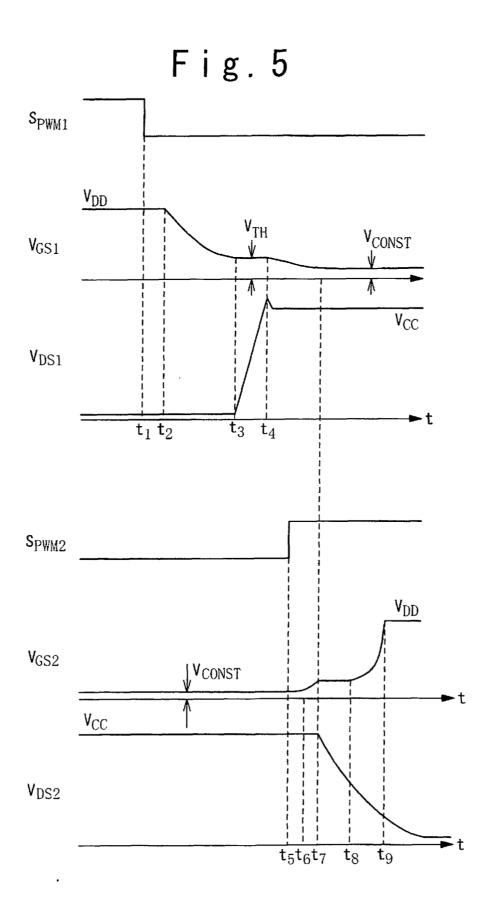

la figura 5 es un cronograma que muestra un funcionamiento de un inversor trifásico mostrado en la figura 4

# Descripción de las realizaciones preferidas

La figura 2 es un esquema de circuito eléctrico que muestra una configuración de un inversor trifásico 1 en una realización de la presente invención. Debe observarse que la figura 2 muestra sólo una parte correspondiente a la fase R en una etapa de salida que produce como salida una intensidad alterna trifásica; las partes correspondientes a otras fases (fase S y fase T), que no se muestran en la figura 2, tienen también la misma configuración.

Se dota al inversor 1 trifásico de un terminal 3 de electrodo positivo conectado a un cátodo de una batería 2 eléctrica; un terminal 4 de electrodo negativo conectado a un ánodo de la batería 2 eléctrica; un condensador 5 de filtrado conectado entre el terminal 3 de electrodo positivo y el terminal 4 de electrodo negativo; y unos MOSFET 6 y 7 de potencia de canal N. En una realización, una tensión  $V_{cc}$  de fuente de alimentación generada por la batería 2 eléctrica es de aproximadamente 48 V. El MOSFET 6 de potencia se usa para polarizar a nivel alto un terminal 10 de salida a través del que se produce como salida una tensión de fase R, a la vez que el MOSFET 7 de potencia se usa para polarizar a nivel bajo el terminal 10 de salida. Más concretamente, el MOSFET 6 de potencia tiene un drenador conectado al terminal 3 de electrodo positivo, y una fuente conectada al terminal 10 de salida. Por otro lado, el MOSFET 7 de potencia tiene un drenador conectado al terminal 10 de salida, y una fuente conectada al terminal 4 de electrodo negativo. Los MOSFET 6 y 7 de potencia incorporan diodos 8 y 9 parásitos, respectivamente.

Se dota al inversor 1 trifásico adicionalmente de los circuitos 11 y 12 de control de puerta para controlar las puertas

de los MOSFET 6 y 7 de potencia, respectivamente.

10

15

20

25

30

35

40

50

55

Se dota al circuito 11 de control de puerta de un circuito 13 de control, unos elementos R1 y R2 de resistencia; y unos diodos D1 y D2. El circuito 13 de control es sensible a la señal S<sub>PWM1</sub> de PWM recibida desde un dispositivo de control para realizar un control de PWM; el circuito 13 de control conmuta a estado de conducción y a estado de corte el MOSFET 6 de potencia. El circuito 13 de control incluye un circuito 14 de carga y un circuito 15 de descarga. El circuito 14 de carga carga la puerta del MOSFET 6 de potencia hasta un nivel V<sub>DD</sub> de fuente de alimentación a través del elemento R1 de resistencia, y lleva de ese modo al estado de conducción al MOSFET 6 de potencia. Por otro lado, el circuito 15 de descarga descarga la puerta del MOSFET 6 de potencia hasta un nivel V<sub>SS</sub> de tierra a través del elemento de resistencia R2 y los diodos D1 y D2, y lleva de ese modo al estado de corte al MOSFET 6 de potencia. Los diodos D1 y D2 se conectan en serie en un sentido directo con respecto a una intensidad de descarga que fluye de la puerta del MOSFET 6 de potencia a un terminal de tierra.

El circuito 12 de control de puerta, que controla la puerta del MOSFET 7 de potencia, tiene la misma configuración que el circuito 11 de control de puerta. El circuito 12 de control de puerta se dota de un circuito 16 de control, unos elementos R3 y R4 de resistencia; y unos diodos D3 y D4. El circuito 16 de control conmuta a estado de conducción y a estado de corte el MOSFET 7 de potencia en respuesta a una señal S<sub>WPM2</sub> de PWM. El circuito 16 de control tiene un circuito 17 de carga y un circuito 18 de descarga. El circuito 17 de carga carga la puerta del MOSFET 7 de potencia hasta el nivel V<sub>DD</sub> de fuente de alimentación a través del elemento R3 de resistencia, y lleva de ese modo al estado de conducción al MOSFET 7 de potencia. Por otro lado, el circuito 18 de descarga descarga la puerta del MOSFET 7 de potencia hasta el nivel V<sub>SS</sub> de tierra a través del elemento R4 de resistencia, los diodos D3 y D4, y lleva de ese modo al estado de corte al MOSFET 7 de potencia. Los diodos D3 y D4 se conectan en serie en un sentido directo con respecto a una intensidad de descarga que fluye de la puerta del MOSFET 7 de potencia al terminal de tierra.

Una característica importante del inversor 1 trifásico mostrado en la figura 2 es que se proporciona una pluralidad de diodos a lo largo de los caminos a través de los que se descargan las puertas de los MOSFET 6 y 7 de potencia. Los diodos D1 y D2 se conectan en serie en un sentido directo a lo largo del camino a través del que se descarga la puerta del MOSFET 6 de potencia. De forma correspondiente, los diodos D3 y D4 se conectan en serie en un sentido directo a lo largo del camino a través del que se descarga la puerta del MOSFET 7 de potencia.

Estos diodos proporcionan una función de mantenimiento de las tensiones puerta—fuente de los MOSFET 6 y 7 de potencia a unas tensiones ligeramente superiores a 0 V, durante un determinado periodo de tiempo después de que los MOSFET 6 y 7 de potencia se lleven a estado de corte. Por ejemplo, una tensión V<sub>GS1</sub> puerta—fuente del MOSFET 6 de potencia es superior a la suma de las tensiones directas V<sub>F</sub> de los diodos D1 y D2 durante tanto tiempo como la intensidad de descarga fluya a través de los mismos para descargar la puerta del MOSFET 6 de potencia. Más concretamente, cuando ambos diodos D1 y D2 son diodos de silicio, la tensión V<sub>GS1</sub> puerta—fuente del MOSFET 6 de potencia se mantiene a 0,9 V o superior durante tanto tiempo como la intensidad de descarga fluya a través de los mismos. Lo mismo se aplica a una tensión puerta—fuente V<sub>GS2</sub> del MOSFET 7 de potencia.

Es eficaz mantener las tensiones puerta-fuente a unas tensiones ligeramente superiores a 0 V después de la puesta en estado de corte de los MOSFET 6 y 7 de potencia para reducir la EMI provocada por la resonancia entre la capacidad drenador-fuente y la inductancia de interconexión. El mantenimiento de las tensiones puerta-fuente a las tensiones ligeramente superiores a 0 V reduce de forma eficaz las capacidades drenador-fuente de los MOSFET 6 y 7 de potencia cuando los MOSFET 6 y 7 de potencia se llevan a estado de corte. La reducción de la capacidad drenador-fuente disminuye las intensidades de alta frecuencia no deseadas a través de los MOSFET 6 y 7 de potencia, y reduce de forma eficaz la EMI provocada por la resonancia entre la capacidad drenador-fuente y la inductancia de interconexión.

Con referencia a la figura 3 se hace una descripción detallada de un funcionamiento del inversor 1 trifásico, en particular, del efecto de la pluralidad de diodos proporcionada a lo largo de los caminos a través de los que se descargan las puertas de los MOSFET 6 y 7 de potencia durante los funcionamientos del inversor 1 trifásico.

La figura 3 es un cronograma que muestra el funcionamiento del inversor 1 trifásico, en el que el MOSFET 6 de potencia se lleva a estado de corte, y el MOSFET 7 de potencia se lleva posteriormente a estado de conexión. Inicialmente, el MOSFET 6 de potencia tiene una tensión  $V_{\text{GS}1}$  puerta—fuente de  $V_{\text{DD}} - V_{\text{SS}}$  (aproximadamente igual a  $V_{\text{DD}}$ ), y el MOSFET 6 de potencia se lleva a estado de conexión. En este estado, la tensión  $V_{\text{DS}1}$  drenador—fuente del MOSFET 6 de potencia es el producto de la intensidad de drenador a través del MOSFET 6 de potencia multiplicada por una resistencia de conexión del mismo.

Por otro lado, la tensión puerta–fuente  $V_{GS2}$  del MOSFET 7 de potencia está aproximadamente cerca de una suma de las tensiones directas  $V_F$  de los diodos D3 y D4, y el MOSFET 7 de potencia se lleva a estado de corte. En este estado, la tensión  $V_{DS2}$  drenador–fuente del MOSFET 6 de potencia es substancialmente idéntica a la tensión  $V_{CC}$  de fuente de alimentación suministrada desde la batería 2 eléctrica al inversor 1 trifásico.

En respuesta a la polarización a nivel bajo de la señal  $S_{PWM1}$  de PWM al nivel "bajo" en un instante  $t_1$  de tiempo, el circuito 15 de descarga del circuito 11 de control de puerta inicia la descarga de la puerta del MOSFET 6 de potencia

en un instante  $t_2$  de tiempo. Como resultado, la tensión  $V_{GS1}$  puerta–fuente del MOSFET 6 de potencia se polariza a nivel bajo a una tensión umbral  $V_{TH}$  del MOSFET 6 de potencia en un instante  $t_3$  de tiempo. Cuando la tensión  $V_{GS1}$  puerta–fuente del MOSFET 6 de potencia alcanza la tensión umbral  $V_{TH}$ ' el MOSFET 6 de potencia se lleva a estado de corte, y la tensión  $V_{DS1}$  drenador–fuente comienza a aumentar. Después de que el MOSFET 6 de potencia se lleve a estado de corte, la tensión  $V_{GS1}$  puerta–fuente se mantiene a la tensión umbral  $V_{TH}$  durante un determinado periodo de tiempo. En la figura 3, la tensión  $V_{GS1}$  puerta–fuente se mantiene constante entre los instantes  $t_3$  y  $t_4$  de tiempo.

Posteriormente, la tensión  $V_{GS1}$  puerta-fuente se polariza a nivel bajo a partir de la tensión umbral  $V_{TH}$  a 0 V en el instante  $t_4$  de tiempo. Debe observarse que la tensión  $V_{GS1}$  puerta-fuente se reduce progresivamente, como resultado de la pluralidad de diodos D1 y D2 proporcionada a lo largo del camino a través del que se descarga la puerta del MOSFET 6 de potencia. En la figura 3, una línea continua indica un cambio en la tensión  $V_{GS1}$  puerta-fuente en el inversor 1 trifásico de la realización, a la vez que una línea discontinua indica un cambio en la tensión  $V_{GS1}$  puerta-fuente en el caso en el que sólo se prevé un único diodo a lo largo del camino usado para descargar la puerta del MOSFET 6 de potencia. La tensión  $V_{GS1}$  puerta-fuente se mantiene al doble o superior de la tensión  $V_F$  directa de los diodos D1 y D2 durante tanto tiempo como la intensidad de descarga continúe fluyendo.

10

15

20

25

30

45

El MOSFET 7 de potencia se lleva a estado de conexión después de que el MOSFET 6 de potencia se lleve a estado de corte. En detalle, en respuesta a la polarización a nivel alto de la señal  $S_{PWM2}$  de PWM al nivel "alto" en un instante  $t_5$  de tiempo, el circuito 17 de carga del circuito 12 de control de puerta inicia la carga de la puerta del MOSFET 7 de potencia en un instante  $t_6$  de tiempo. Como resultado, se aumenta la tensión puerta–fuente  $V_{GS2}$  del MOSFET 7 de potencia hasta la tensión umbral  $V_{TH}$  del MOSFET 7 de potencia, y el MOSFET 7 de potencia se lleva a estado de conexión en un instante  $t_7$  de tiempo. En respuesta a la puesta en estado de conducción del MOSFET 7 de potencia, la tensión drenador—fuente  $V_{DS2}$  del mismo se lleva hasta el producto de la intensidad de drenador a través del MOSFET 7 de potencia multiplicada por la resistencia de conexión del mismo. La tensión  $V_{GS2}$  puerta–fuente del MOSFET 7 de potencia se lleva hasta la tensión  $V_{DD} - V_{ss}$ , después de haberse mantenido a la tensión  $V_{TH}$  umbral durante un determinado periodo de tiempo. En la figura 3, la tensión  $V_{GS2}$  puerta–fuente se mantiene a la tensión  $V_{TH}$  umbral entre los instantes  $t_7$  y  $t_8$  de tiempo.

Es importante que la tensión  $V_{GS1}$  puerta-fuente de estado de corte del MOSFET 6 de potencia se mantenga lo suficientemente superior a 0 V cuando el MOSFET 7 de potencia se lleva a estado de conexión (concretamente, en el instante  $t_7$  de tiempo en el que la tensión puerta-fuente  $V_{GS2}$  del MOSFET 7 de potencia alcanza la tensión umbral  $V_{TH}$ ). En el instante  $t_7$  de tiempo en el que el MOSFET 7 de potencia se lleva a estado de conexión, una intensidad de recuperación que provoca la resonancia comienza a fluir a través del diodo parásito 8 del MOSFET 6 de potencia. Por tanto, la reducción de la capacidad drenador-fuente del MOSFET 6 de potencia en el instante  $t_7$  de tiempo es importante para reducir la EMI. Por consiguiente, es eficaz mantener la tensión  $V_{GS1}$  puerta-fuente del MOSFET 6 de potencia en el instante  $t_7$  de tiempo, a un valor suficientemente superior a 0 V.

Preferentemente, la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo es de aproximadamente la mitad de la tensión V<sub>TH</sub> umbral del MOSFET 6 de potencia, más concretamente en un intervalo de un 30% y un 70% de la tensión umbral V<sub>TH</sub>. Más preferentemente, la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo está en un intervalo de un 40% y un 60% de la tensión umbral V<sub>TH</sub> del MOSFET 6 de potencia. Si la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo es excesivamente baja, la capacidad drenador–fuente no se reduce suficientemente. Por otro lado, si la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo es excesivamente alta, el MOSFET 6 de potencia no se lleva suficientemente a estado de corte.

La tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo puede ajustarse con el número y/o tipos de los diodos proporcionados a lo largo de los caminos a través de los que se descargan las puertas de los MOSFET 6 y 7 de potencia. Es preferible que los diodos D1 a D4 sean diodos de silicio con el fin de aumentar suficientemente la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo con un número reducido de diodos. El diodo de silicio tiene esencialmente una tensión directa alta, y el uso de los diodos de silicio permite por tanto aumentar suficientemente la tensión V<sub>GS1</sub> puerta–fuente del MOSFET 6 de potencia en el instante t<sub>7</sub> de tiempo, con un número reducido de diodos.

A pesar de que la figura 3 sólo muestra el funcionamiento en el que el MOSFET 7 de potencia se lleva a estado de conexión después de que el MOSFET 6 de potencia se lleve a estado de corte, es evidente para los expertos en la técnica que un funcionamiento para llevar a estado de conexión el MOSFET 6 de potencia después de la puesta en estado de corte del MOSFET 7 de potencia se realiza también de la misma forma.

La figura 4 es un diagrama de bloques que muestra una configuración de un inversor 1A trifásico en otra realización. En la realización, los circuitos 15A y 18A de descarga están diseñados para mantener unas tensiones puerta—fuente de los MOSFET 6 y 7 de potencia a unas tensiones determinadas después de la puesta en estado de corte de los MOSFET 6 y 7 de potencia, en lugar de proporcionar una pluralidad de diodos a los caminos en los se descargan que las puertas de los MOSFET 6 y 7 de potencia.

Los circuitos 15A y 18A de descarga están configurados para mantener las tensiones puerta-fuente de los MOSFET

6 y 7 de potencia a aproximadamente la mitad de una tensión umbral V<sub>TH</sub> después de las puestas en estado de corte de los MOSFET 6 y 7 de potencia. Más concretamente, los circuitos 15A y 18A de descarga están configurados para mantener las tensiones puerta–fuente de los MOSFET 6 y 7 de potencia a unas tensiones en un intervalo de un 30% y un 70% de la tensión umbral V<sub>TH</sub> después de las puestas en estado de corte de los MOSFET 6 y 7 de potencia. En una realización preferida, los circuitos 15A y 18A de descarga están configurados para mantener las tensiones puerta–fuente de los MOSFET 6 y 7 de potencia a unas tensiones en un intervalo de un 40% y un 60% de la tensión umbral V<sub>TH</sub>.

5

10

15

20

La figura 5 es un cronograma que muestra un funcionamiento ejemplar del inversor 1A trifásico mostrado en la figura 4, en el que el MOSFET 7 de potencia se lleva a estado de conexión después de que el MOSFET 6 de potencia se lleve a estado de corte. La diferencia respecto del funcionamiento mostrado en la figura 3 es que el circuito 15A de descarga polariza a nivel bajo la puerta del MOSFET 6 de potencia a un nivel V<sub>A</sub> de potencial positivo determinado después de que el MOSFET 6 de potencia se lleve a estado de corte; la puerta del MOSFET 6 de potencia no se polariza hasta el nivel V<sub>SS</sub> de tierra. Por consiguiente, el circuito 15A de descarga mantiene una tensión V<sub>GS1</sub> puertafuente a una tensión V<sub>CONST</sub> (= V<sub>A</sub> – V<sub>SS</sub>) o superior, en todo momento. El nivel V<sub>A</sub> de potencial se selecciona de modo que la tensión V<sub>CONST</sub> se ajusta a aproximadamente la mitad de la tensión umbral V<sub>TH</sub>, y más concretamente, a un nivel en un intervalo de un 30% y un 70% de la tensión umbral V<sub>TH</sub>. En otras palabras, la tensión V<sub>GS1</sub> puertafuente de corte del MOSFET 6 de potencia se mantiene en un intervalo de un 30% y un 70% de la tensión umbral V<sub>TH</sub>, y por consiguiente se reduce la capacidad drenador–fuente. Como se indicó anteriormente, la reducción de la capacidad drenador–fuente es eficaz para reducir la EMI. En una realización más preferida, la tensión V<sub>CONST</sub> se ajusta para estar en un intervalo de un 40% y un 60% de la tensión V<sub>TH</sub> umbral.

A pesar de que la figura 5 sólo muestra un funcionamiento en el que el MOSFET 7 de potencia se lleva a estado de conexión después de que el MOSFET 6 de potencia se lleve a estado de corte, es evidente para los expertos en la técnica que un funcionamiento en el que el MOSFET 6 de potencia se lleva a estado de conexión después de la puesta en estado de corte del MOSFET 7 de potencia se realiza también de la misma forma.

Según se explicó anteriormente, el inversor trifásico en las realizaciones se diseña de modo que la tensión puertafuente del MOSFET de potencia se disminuye progresivamente después de la puesta en estado de corte del mismo,

o se mantiene a una tensión de aproximadamente la mitad de la tensión umbral V<sub>TH</sub>. Por consiguiente, la capacidad

drenador-fuente de estado de corte del MOSFET de potencia se reduce de forma eficaz. La reducción de la

capacidad drenador-fuente del MOSFET de potencia es eficaz para reducir la EMI provocada por la resonancia

entre la capacidad drenador-fuente y la inductancia de interconexión.

#### REIVINDICACIONES

1. 1. Un aparato inversor que comprende:

un primer MOSFET (6) de potencia que tiene una fuente/drenador conectada a un terminal (10) de salida; un primer circuito (11) de control de puerta que controla una puerta de dicho primer MOSFET (6) de potencia y que incluye un camino de descarga conectado a dicha puerta de dicho primer MOSFET (6) de potencia para controlar una puerta de dicho primer MOSFET (6) de potencia.

un segundo MOSFET (7) de potencia que tiene una fuente/drenador conectada a dicho terminal (10) de salida:

un segundo circuito (12) de control de puerta que controla una puerta de dicho segundo MOSFET (7) de potencia y que incluye un camino de descarga conectado a dicha puerta de dicho segundo MOSFET (7) de potencia para controlar una puerta de dicho segundo MOSFET (7) de potencia; y,

comprendiendo dichos caminos de descarga unos conjuntos respectivos de diodos (D1, D2; D3, D4) conectados en serie que están conectados en sentido directo en el sentido de una corriente de descarga desde dicha puerta de dicho MOSFET (6, 7) de potencia primero o segundo;

caracterizado porque

dichos MOSFET (6, 7) de potencia primero y segundo son MOSFET de tipo N; y

dichos circuitos de control de puerta primero y segundo están adaptados para, durante una polarización a nivel bajo de dicha puerta de dicho primer MOSFET (6) de potencia seguida de una polarización a nivel alto de dicha puerta de dicho segundo MOSFET (7) de potencia, controlar dicha puerta de dicho primer MOSFET (6) de potencia de modo que una tensión puerta—fuente de dicho primer MOSFET (6) de potencia varía entre un 30% y un 70% de una tensión umbral de dicho primer MOSFET (6) de potencia con un sincronismo en el que dicho segundo circuito (12) de control de puerta conduce una tensión puerta—fuente de dicho segundo MOSFET (7) de potencia a una tensión umbral de dicho segundo MOSFET (7) de potencia.

- 25 2. El aparato inversor de acuerdo con la reivindicación 1, c**aracterizado porque** dichos diodos (D1, D2) conectados en serie son diodos de silicio.

- 3. El aparato inversor de acuerdo con la reivindicación 1, **caracterizado porque** dichos circuitos de control de puerta primero y segundo están adaptados de modo que dicha tensión puerta—fuente de dicho primer MOSFET (6) de potencia varía entre un 40% y un 60% de dicha tensión umbral de dicho primer MOSFET (6) de potencia con dicho sincronismo en el que dicho segundo circuito (12) de control de puerta controla dicha tensión puerta—fuente de dicho segundo MOSFET (7) de potencia a dicha tensión umbral de dicho segundo MOSFET (7) de potencia.

- 4. Un procedimiento de funcionamiento de un aparato inversor que incluye:

un primer MOSFET (6) de potencia que tiene una primera fuente/drenador conectada a un primer terminal (3) de potencia, y una segunda fuente/drenador conectada a un terminal (10) de salida; y un segundo MOSFET (7) de potencia que tiene una primera fuente/drenador conectada a un segundo terminal (4) de potencia, y una segunda fuente/drenador conectada a dicho terminal (10) de salida, comprendiendo dicho procedimiento:

polarizar a nivel bajo una puerta de dicho primer MOSFET (6) de potencia para llevar al estado de corte dicho primer MOSFET (6) de potencia; y

polarizar a nivel alto una puerta de dicho segundo MOSFET (7) de potencia para llevar al estado de conducción lineal dicho segundo MOSFET (7) de potencia,

en el que la etapa de polarización a nivel bajo y la etapa de polarización a nivel alto se realizan con un sincronismo tal que una tensión puerta—fuente de dicho primer MOSFET (6) de potencia varía entre un 30% y un 70% de una tensión umbral de dicho primer MOSFET (6) de potencia con un sincronismo en el que una tensión puerta—fuente de dicho segundo MOSFET (7) de potencia se conduce a una tensión umbral de dicho segundo MOSFET (7) de potencia durante dicha polarización a nivel alto de dicha puerta de dicho segundo MOSFET (7) de potencia.

45

40

5

10

15

20

30

35

# Fig. 1 TÉCNICA ANTERIOR