OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

$\bigcirc$  Número de publicación:  $2\ 368\ 207$

(51) Int. Cl.:

H04W 28/06 (2006.01) H04L 25/49 (2006.01) H04L 5/06 (2006.01)

Т3

- 96 Número de solicitud europea: 04014610 .2

- 96 Fecha de presentación : **04.11.1997**

- 97 Número de publicación de la solicitud: 1458104 97) Fecha de publicación de la solicitud: **15.09.2004**

- 54 Título: Método y aparato para comprimir y transmitir datos a alta velocidad.

- (30) Prioridad: **07.11.1996 US 743749**

(73) Titular/es:

INTERDIGITAL TECHNOLOGY CORPORATION 3411 Silverside Road Concord Plaza Suite 105 Hagley Building Wilmington, Delaware 19810, US

- (45) Fecha de publicación de la mención BOPI: 15.11.2011

- (72) Inventor/es: Kurtz, Scott David

- (45) Fecha de la publicación del folleto de la patente: 15.11.2011

- (74) Agente: Blanco Jiménez, Araceli

ES 2 368 207 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### DESCRIPCIÓN

Método y aparato para comprimir y transmitir datos a alta velocidad.

#### **Campo de la invención**

Esta invención se refiere a un sistema de comunicación y, más particularmente, a las técnicas de procesamiento de señales para la compresión de señales de comunicación de datos de alta velocidad para un aprovechamiento mejorado de la transmisión y una mayor capacidad de comunicación del sistema.

#### Antecedentes de la invención

Los sistemas de telecomunicaciones son bien conocidos en la técnica, y los sistemas telefónicos actuales emplean varias técnicas de multiplexación para transmitir señales telefónicas de muchos usuarios por una línea de transmisión única, tal como un hilo o cable de fibra óptica. La mayoría de estos sistemas con "cableado directo" emplean una forma de multiplexación por división de tiempo (TDM) en el que se transmiten múltiples canales de forma secuencial a velocidades superiores a la velocidad de información del canal.

La multiplexación telefónica típica requiere un muestreo de la señal telefónica y la transmisión de las muestras con una frecuencia mucho más alta que la frecuencia de la señal telefónica. Con este fin, los sistemas digitales actuales muestrean y codifican la señal telefónica, multiplexan y transmiten la señal, y luego reciben, demultiplexan y decodifican la señal. Uno de estos sistemas de muestreo y codificación es la modulación de códigos por pulsos (PCM) en la que las señales analógicas en banda vocal se muestrean a una velocidad de 8 miles de muestras por segundo en cada muestra representada por 8 bits. En consecuencia, la señal en banda vocal se convierte en una señal digital de 64 kilobits por segundo (kb/s).

Otro tipo de sistema de telecomunicaciones es el sistema telefónico por radio. Los sistemas telefónicos por radio utilizan un grupo de radiofrecuencias (RF) seleccionadas para llevar las señales de comunicación telefónica entre dos o más lugares, y por lo general utilizan una forma de acceso múltiple por división de frecuencia (FDMA). Estos sistemas de radio, denominados sistemas de comunicación inalámbricos, se utilizan, por ejemplo, en zonas rurales para proporcionar servicios de telefonía local o en unidades móviles para prestar servicios de comunicación móvil.

Una de las categorías de los sistemas de comunicación por RF emplea la TDM para permitir el acceso de los usuarios a múltiples segmentos de tiempo de la información modulada en la portadora de RF. Si muchos usuarios compiten por un pequeño grupo de segmentos de tiempo de la información, el sistema se denomina acceso múltiple por división de tiempo (TDMA). Para permitir el TDMA de los canales de comunicación por RF de FDMA, se ha empleado un método, llamado FDMA/TDMA que se describe en la patente US 4.675.863, para aumentar la capacidad de los sistemas de comunicación por RF siguen teniendo su capacidad frecuentemente limitada en comparación con los sistemas de comunicación con cableado directo de hilo o fibra óptica.

En consecuencia, para aumentar la capacidad aún más, se han usado técnicas de compresión de señales para reducir el ancho de banda necesario para la transmisión de una señal telefónica en un canal de RF. Las técnicas normales utilizadas para las señales de voz son las de codificación subbanda, modulación de códigos por pulsos diferencial adaptativa (ADPCM) y codificación predictiva lineal (RELP). La RELP o los algoritmos de compresión de voz similares permiten transmitir una señal de voz cuantificada y muestreada de 64 kilobits por segundo (kb/s) por el canal de RF, como una señal con una velocidad de bits reducida (por ejemplo, 14,6 kb/s o menos). El receptor reconstruye la señal de voz de 64 kb/s de la señal con la velocidad de bits reducida, y el oyente percibe poca o ninguna pérdida de calidad de la señal.

El método subyacente de compresión de voz, incluyendo la RELP, es un algoritmo de codificación y decodificación que aprovecha las características conocidas de las señales de voz. Un tipo de método de RELP asume ciertas características de los armónicos de la voz humana. Hoy, sin embargo, una gran parte de las señales de comunicación, en una red telefónica, son señales de comunicaciones de datos que no son de voz, tales como datos de módem en banda vocal o de facsímil (fax). Desafortunadamente, los algoritmos de compresión de voz no son especialmente compatibles con estas señales de comunicaciones de datos porque las señales de datos no tienen las características de las señales de voz.

En consecuencia, algunos sistemas de comunicación por RF monitorizan la señal telefónica para detectar la presencia de una señal de comunicación de datos. Normalmente, se han detectado señales de datos que representaban señales de datos de módem en banda vocal o fax de hasta 2,4 kb/s (datos de baja velocidad) y se les ha proporcionado un algoritmo de compresión especializada. El receptor reconstruye la señal de datos, sin reducir la velocidad de transmisión de datos. Este sistema y método se describe, por ejemplo, en la patente US 4.974.099. Las señales telefónicas de datos actuales, sin embargo, son más bien de 9,6 kb/s (datos de alta velocidad) o superiores (datos de velocidad ultrarrápida, tales como de 14,4 kb/s o 28,8 kb/s, u otras, superiores o inferiores), y las técnicas de compresión actuales no comprimen estas velocidades más altas de datos satisfactoriamente. La compresión de estas velocidades de datos más altas, y sobre todo las codificaciones múltiples de estas velocidades de datos más altas, provocan una

degradación de la calidad de la señal del módem o fax, y la máquina del módem o fax reducirán con frecuencia la velocidad de transmisión de datos cuando las señales sean pasadas a través de un sistema de comunicación por RF.

WO 93/14492 describe un aparato para codificar un elemento de señal seleccionado de una señal que está definida por elementos de señal que están diferenciados por lo menos en una dimensión, el aparato comprendiendo: medios para dividir la señal en una pluralidad de bandas, al menos una banda teniendo una pluralidad de elementos de señal adyacentes, una de dichas bandas incluyendo el elemento de señal seleccionado, medios para identificar, en cada banda, un elemento de señal que tenga la mayor magnitud de cualquier elemento de señal en dicha banda, y designando dicho elemento de señal como un elemento de señal "patrón" de dicha banda; medios para cuantificar la magnitud de cada elemento de señal patrón para un primer grado de precisión; medios para asignar al elemento de señal seleccionado una asignación de bit del elemento de señal que está en función de las magnitudes cuantificadas de los elementos de señal patrones, seleccionándose la asignación de bit del elemento de señal de tal manera que la cuantificación del elemento de señal seleccionado que utiliza dicha asignación de bit del elemento de señal sea para un segundo grado de precisión, que es menor que el primer grado de precisión.

Además, este documento describe un aparato para decodificar una palabra código que representa un elemento de señal seleccionado de una señal de que ha sido codificada por un aparato como el mencionado anteriormente, el aparato de decodificación comprendiendo: medios para traducir la palabra código en base a una función de las magnitudes cuantificadas de los elementos de señal patrones que está debidamente relacionada inversamente con la función de las magnitudes cuantificadas utilizadas para asignar bits del elemento de señal seleccionado.

#### Sumario de la invención

La presente invención proporciona un aparato para codificar datos de alta velocidad según la reivindicación independiente 1, un aparato de decodificación de datos de alta velocidad según la reivindicación independiente 10 y un sistema de transmisión de compresión de datos de alta velocidad según la reivindicación independiente 15. Las formas de realización preferidas de la invención se reflejan en las reivindicaciones dependientes.

La invención reivindicada puede comprenderse mejor teniendo en cuenta las disposiciones descritas a continuación. En general, las disposiciones descritas describen las disposiciones preferidas de la invención. El lector atento observará, sin embargo, que algunos aspectos de las disposiciones descritas se extienden más allá del alcance de las reivindicaciones. Si las disposiciones descritas se extendieran verdaderamente más allá del alcance de las reivindicaciones, las disposiciones descritas deben ser consideradas información general complementaria y no constituyen definiciones de la invención *per se*. Lo mismo ocurre para las siguientes secciones "Breve descripción de los dibujos", así como "Introducción" y "Descripción detallada de la divulgación".

Un sistema de telecomunicaciones recibe un grupo de señales telefónicas, incluyendo señales de datos, cada una teniendo una forma de codificación, y transmite las señales telefónicas en al menos una portadora de radiofrecuencia (RF). Cada portadora de RF tiene un grupo de segmentos de información, y a cada señal telefónica se le asigna al menos un segmento de información de manera que la señal telefónica es modulada en la portadora de RF. El sistema incluye un proceso para monitorizar e identificar las señales de datos y para comprimir cada señal de datos para reducir el ancho de banda de transmisión necesario de la señal de datos.

## 45 Descripción breve de los dibujos

La divulgación se entiende mejor de la lectura de la siguiente descripción detallada en relación con los dibujos adjuntos, en los que:

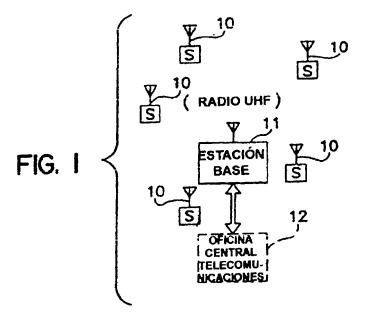

La figura 1 es un diagrama de bloques de un sistema de comunicación inalámbrico.

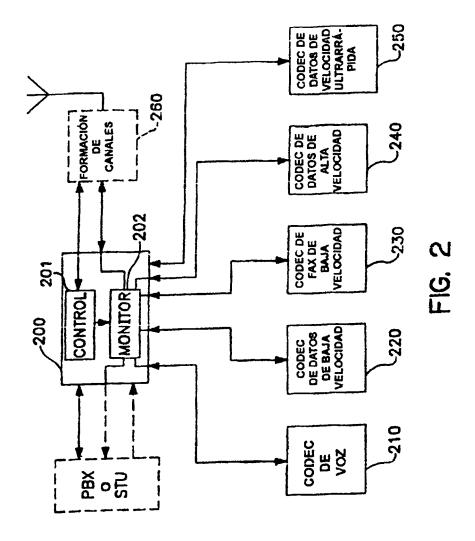

La figura 2 es un diagrama de bloques de alto nivel de la aplicación del sistema de compresión de la presente divulgación, incluida la función de asignación dinámica de ancho de banda y los códecs de datos de alta velocidad y de velocidad ultrarrápida.

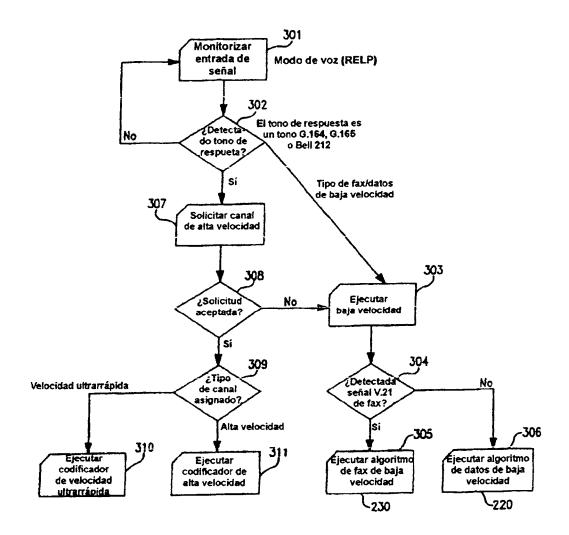

La figura 3A es un diagrama de flujo de alto nivel que ilustra la detección y selección de tipos de codificación de datos de alta velocidad y la determinación y asignación de segmentos de canales de radio, según una disposición ilustrativa de la presente divulgación.

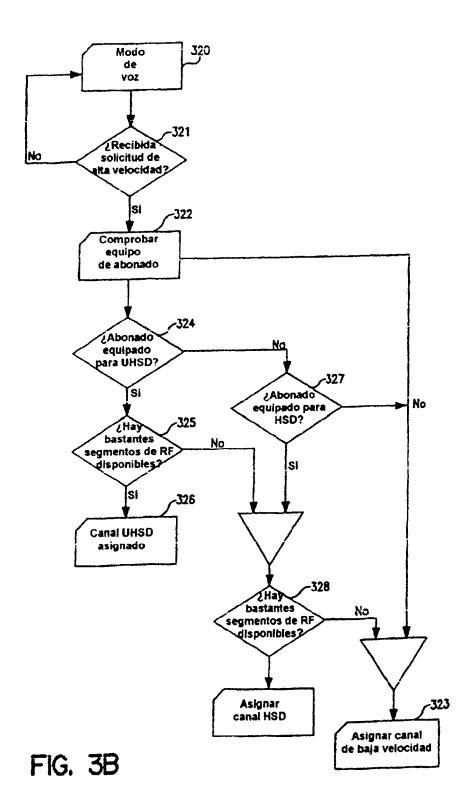

La figura 3B es un diagrama de flujo de alto nivel que muestra el proceso de asignación de canal realizado por el procesador de formación de canales tras la petición de un canal de datos de alta velocidad, según una disposición de la presente divulgación.

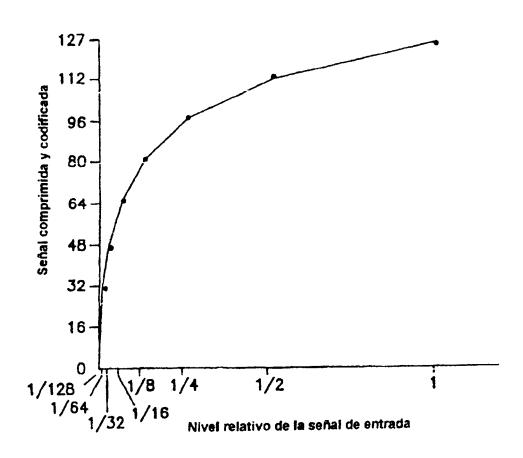

La figura 4A es un gráfico que muestra las características del cuantificador de ley A.

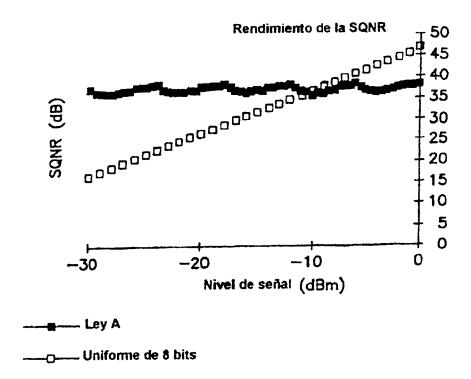

La figura 4B es un gráfico que muestra la señal para la ejecución de la cuantificación de ruido de la PCM frente a la cuantificación uniforme.

3

50

30

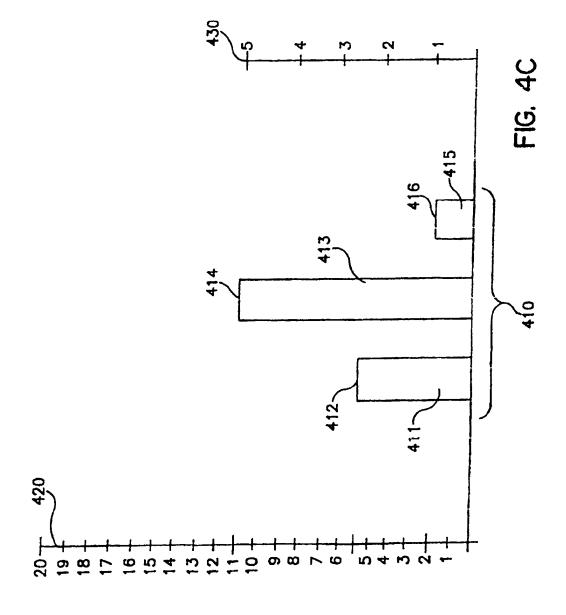

La figura 4C ilustra el método de compresión mediante el mapeo de muestras de señal de una cuantificación a otra cuantificación.

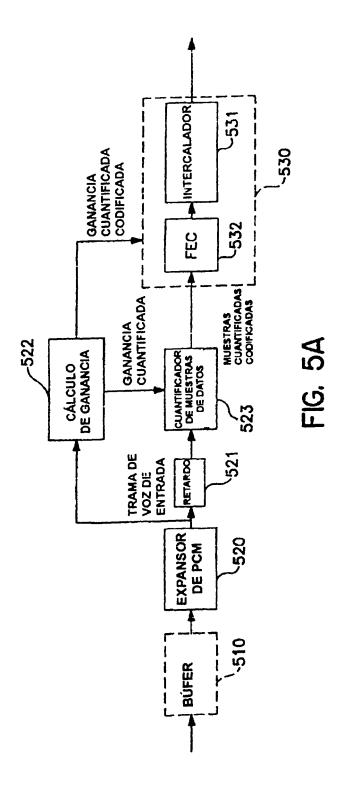

La figura 5A es un diagrama de bloques de alto nivel del codificador de datos de alta velocidad, según una disposición de la forma de realización ilustrativa de la presente divulgación.

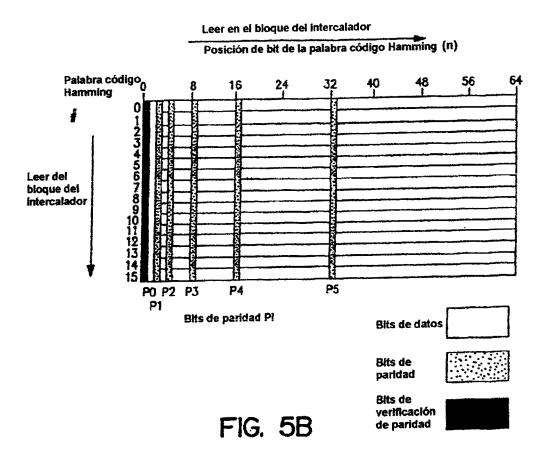

La figura 5B ilustra un proceso de codificación para la transmisión con un codificador de datos de alta velocidad, según una disposición ilustrativa de la presente divulgación.

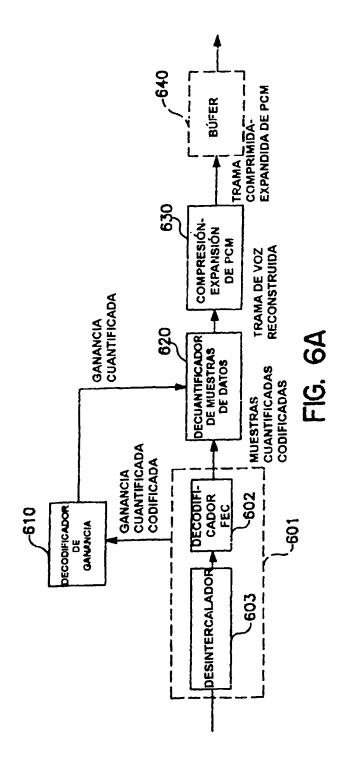

La figura 6A es un diagrama de bloques de alto nivel del decodificador de datos de alta velocidad, según una disposición ilustrativa de la presente divulgación.

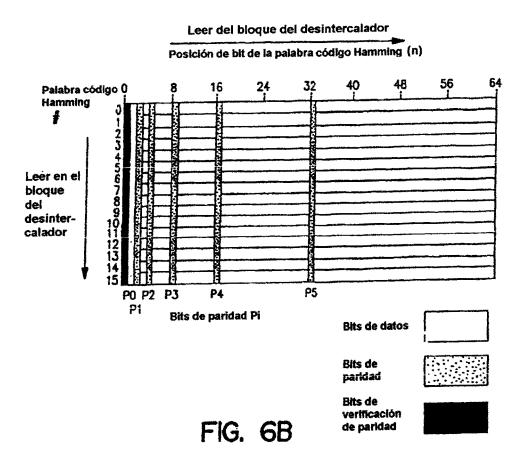

La figura 6B ilustra un proceso de decodificación para la transmisión con un decodificador de datos de alta velocidad, según una disposición ilustrativa de la presente divulgación.

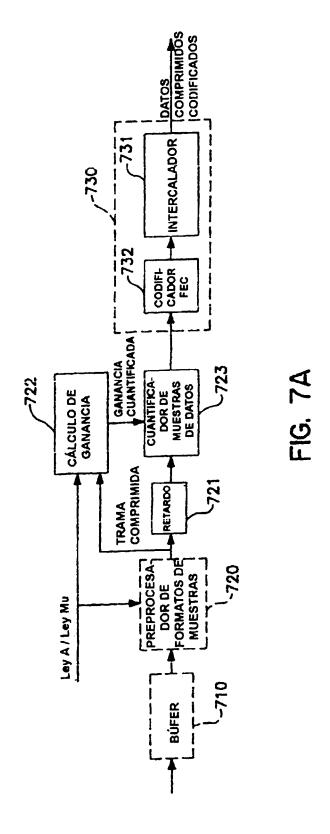

La figura 7A es un diagrama de bloques de alto nivel del codificador de datos de velocidad ultrarrápida, según una disposición ilustrativa de la presente divulgación.

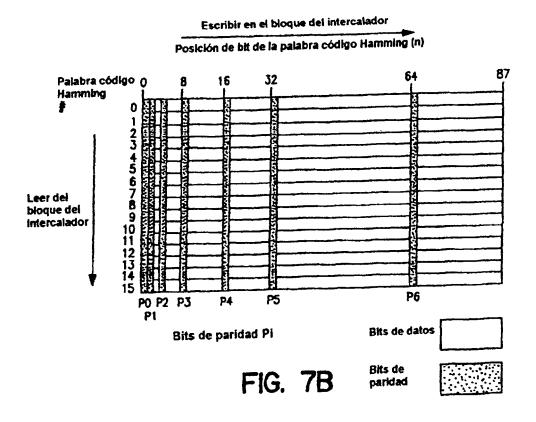

La figura 7B ilustra un proceso de codificación para la transmisión con un codificador de datos de velocidad ultrarrápida, según una disposición ilustrativa de la presente divulgación.

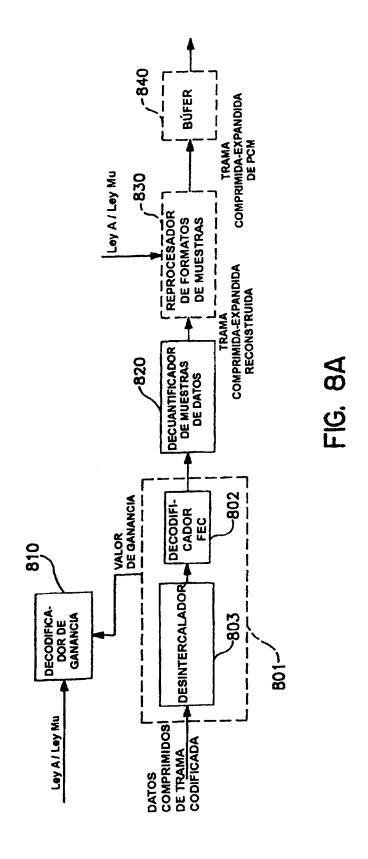

La figura 8A es un diagrama de bloques de alto nivel del decodificador de datos de velocidad ultrarrápida, según una disposición ilustrativa de la presente divulgación.

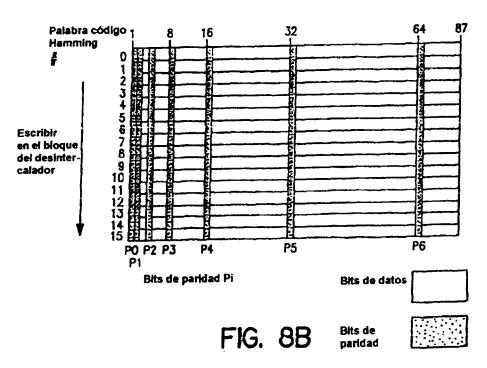

La figura 8B ilustra un proceso de decodificación para la transmisión con un decodificador de datos de velocidad ultrarrápida, según una disposición ilustrativa de la presente divulgación.

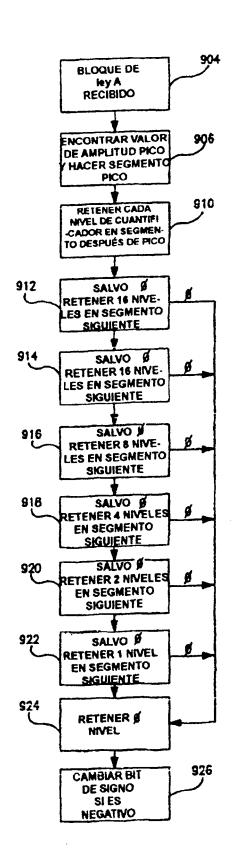

La figura 9 es un diagrama de flujo de alto nivel que ilustra un algoritmo de cuantificación de velocidad ultrarrápida utilizado para mapear las muestras cuantificadas de PCM en muestras cuantificadas comprimidas según una disposición ilustrativa de la presente divulgación.

### Introducción

15

2.5

Un aparato y método de telecomunicaciones recibe las señales telefónicas y modula cada una de las señales telefónicas en una portadora de radiofrecuencia (RF) de transmisión correspondiente. Cada portadora de RF de transmisión tiene un número predeterminado de segmentos de información, y a cada señal telefónica se le asigna al menos un segmento de información de manera que la señal telefónica sea modulada en la portadora de RF. El aparato y método de telecomunicaciones incluye un detector para recibir y monitorizar cada una de las señales telefónicas para detectar una señal de datos contenida en una de las señales telefónicas; y un codificador para codificar la señal de datos en una señal codificada comprimida. El aparato y el método también incluyen un controlador, que controla un estado de asignación de cada segmento de información cuando se detecta la señal de datos y localiza un número predeterminado de segmentos de información secuenciales no asignados (aunque no necesariamente contiguos) para un ancho de banda predeterminado necesario para transmitir la señal codificada comprimida. El estado de asignación indica si cada segmento de información no se ha asignado o se ha asignado a las señales de otro teléfono. El aparato y el método también incluyen un proceso para formar un canal de telecomunicaciones desde los segmentos de información secuenciales no asignados localizados y un proceso para modular la señal codificada en el canal de telecomunicaciones.

Según un aspecto de la presente divulgación, un sistema de transmisión de compresión de datos de alta velocidad transmite una señal de datos de alta velocidad a través de un canal de telecomunicaciones como una señal codificada comprimida. La señal de datos de alta velocidad es recibida como al menos un bloque de señales de datos de muestras, y el sistema incluye un codificador de datos de alta velocidad y un decodificador de datos de alta velocidad. El codificador de datos de alta velocidad incluye: 1) un receptor para los bloques de señales de datos que contienen cada uno al menos una muestra de la señal de datos que representa una amplitud pico, 2) una calculadora para calcular un valor de ganancia del bloque de señales de datos, que es proporcional al valor de la amplitud pico; y 3) un selector de cuantificadores que selecciona un cuantificador correspondiente al valor de ganancia.

El cuantificador tiene una pluralidad de valores de nivel del cuantificador con una separación determinada (por ejemplo, uniforme), que se determina a partir del valor de ganancia, y el cuantificador seleccionado cuantifica cada muestra de datos del bloque de señales de datos en una muestra de datos comprimida. El valor de ganancia y la pluralidad de muestras de datos comprimidas constituyen la señal comprimida codificada. El sistema de transmisión de compresión de datos de alta velocidad incluye un transmisor, para transmitir la señal comprimida codificada, a través del canal de telecomunicaciones, y un receptor para recibir la señal del canal de telecomunicaciones

El descodificador de datos de alta velocidad del sistema de transmisión de compresión de datos de alta velocidad incluye: 1) un receptor para las muestras de datos comprimidas y el valor de ganancia correspondiente, y 2) un selec-

tor de cuantificadores inverso para seleccionar, en base al valor de ganancia, un cuantificador inverso uniforme que tiene una pluralidad de valores de salida separados uniformemente que se determina a partir del valor de ganancia. El cuantificador inverso procesa cada una de las muestras de datos comprimidas en base al valor de ganancia para proporcionar un bloque de muestras de la señal de datos reconstruida.

Según otro aspecto de la presente divulgación, un sistema de transmisión de compresión de datos de velocidad ultrarrápida transmite una señal de datos de velocidad ultrarrápida a través de un canal de telecomunicaciones. La señal de datos de velocidad ultrarrápida es recibida como al menos un bloque de señales de datos de muestras que tiene una primera cuantificación, y el sistema incluye un codificador de datos de velocidad ultrarrápida y un decodificador de datos de velocidad ultrarrápida incluye: 1) un receptor para el bloque de señales de datos que contiene al menos una muestra de la señal de datos que tiene una amplitud pico, 2) una calculadora para calcular un valor de ganancia del bloque de señales de datos que es proporcional a la amplitud pico, y 3) un selector de cuantificadores para seleccionar un nuevo conjunto de niveles de cuantificación correspondiente al valor de ganancia del bloque de muestras, y cada uno del nuevo conjunto de niveles de cuantificación son niveles seleccionados de la primera cuantificación, y 4) un procesador de mapeo de niveles de cuantificación que mapea el valor de la muestra de la señal para un valor del nivel comprimido para cada valor de la muestra de la señal en base a una relación entre el conjunto de niveles de la primera cuantificación y el nuevo conjunto de niveles del cuantificador.

El valor de ganancia y las muestras de datos comprimidas constituyen una señal codificada. El sistema también incluye un transmisor para transmitir la señal codificada a través del canal de telecomunicaciones, y un receptor para recibir la señal codificada del canal de telecomunicaciones. A continuación se describe la disposición ilustrativa con referencia a un canal de telecomunicaciones de un sistema de comunicación inalámbrica. Sin embargo, la presente divulgación no se limita a los tipos de comunicación inalámbrica u otras con portadora de RF. Más bien, la presente divulgación también se puede utilizar con los canales de telecomunicaciones de los sistemas de comunicación por cable para aumentar la capacidad.

El decodificador de datos de velocidad ultrarrápida del sistema de transmisión de compresión de velocidad ultrarrápida incluye 1) un receptor para las muestras de datos comprimidas y el valor de ganancia correspondiente, 2) un selector de cuantificadores inversos para seleccionar, en base al valor de ganancia correspondiente, un cuantificador inverso que tenga valores de salida que se determinan a partir del valor de ganancia con el correspondiente nuevo conjunto de niveles del cuantificador. El cuantificador inverso procesa cada una de las muestras de datos comprimidas en base al valor de ganancia para proporcionar un bloque de muestras de señales de datos reconstruidas.

Según otro aspecto de la presente divulgación, un método para cuantificar datos de velocidad ultrarrápida mapea, a partir de una primera pluralidad de muestras de señal cuantificadas, cada muestra de señal teniendo su correspondiente valor cuantificado de amplitud y al menos una muestra de señal teniendo un valor de amplitud cuantificada pico, a una segunda pluralidad de muestras comprimidas cuantificadas y un valor de ganancia. El método incluye: 1) examinar cada amplitud para determinar un valor de amplitud pico, y establecer el valor de ganancia correspondiente al valor de amplitud pico, y definir para la primera pluralidad de muestras de la señal cuantificada un número predeterminado de segmentos sucesivos, cada segmento teniendo un número de valores del nivel cuantificado. Los valores del nivel cuantificado para cada segmento sucesivo se relaciona con el valor de ganancia, y un primer segmento del número predeterminado de segmentos sucesivos corresponde a la amplitud pico de la pluralidad de muestras de la señal.

El método de cuantificación incluye, además, el mapeo de cada una de las muestras de señal cuantificadas en muestras cuantificadas comprimidas mediante 1) la retención, para cada uno de los valores de la señal cuantificada, de aquellos seleccionados del número de valores del nivel cuantificado para cada segmento hasta que se encuentre un nivel de valor cero y 2) el establecimiento de un valor de signo a un valor negativo para indicar una amplitud valorada negativamente.

## Descripción detallada de la divulgación

55 El sistema de compresión de datos

35

45

La figura 1 es un diagrama de un sistema de telecomunicación inalámbrica en el que se pueden aplicar las características de la compresión de datos de alta velocidad de la presente divulgación. Como se ve, el sistema de radiotelecomunicaciones incluye una estación base 11 y un grupo de unidades de abonado 10. La estación base 11 se comunica simultáneamente con las unidades de abonado 10 mediante la difusión y recepción de canales de comunicación definidos en un rango de frecuencias de radio preseleccionadas. La estación base 11 también puede interconectar con el equipo de telefonía local en la oficina central de la empresa de telecomunicaciones 12.

Un sistema típico de radiotelecomunicaciones (por ejemplo, el SLS-104, fabricado por InterDigrtal Communications Corporation, King of Prussia, Pennsylvania) utiliza 24 canales predeterminados directos (de la estación base a la unidad de abonados) y 24 canales predeterminados inversos (de la unidad de abonado a la estación base) en la región espectral de 300-500 Megahercios (MHz). La comunicación de la estación base a la unidad de abonado se proporciona a través de pares de canales de comunicación (directos e inversos) modulados en frecuencias dentro de esta región

espectral. En un sistema típico, la estación base 11 comunica simultáneamente a través de estos 24 pares de canales. Los 24 canales pueden ocupar, por ejemplo, bandas de frecuencia de 2 MHz. La banda de frecuencia de 2 MHz puede soportar más canales, por ejemplo, 80 canales, empleando una separación de canales de 25 kHz. En una disposición del sistema, la estación base 11 puede transmitir a un abonado en la menor frecuencia de un par, y la unidad de abonado 10 puede transmitir a la estación base en el par de frecuencia más alta. Tal sistema se describe en la patente US 4.675.863, concedida el 23 de junio de 1987, titulada "Sistema telefónico de abonado por RF para proporcionar señales múltiples de voz y/o datos simultáneamente en uno o una pluralidad de canales de RF", a nombre de Paneth et al.

Con el fin de aumentar la capacidad de comunicación, se utilizan las técnicas de acceso múltiple por división de tiempo en cada frecuencia portadora. En un sistema ilustrativo, cada frecuencia del par de canales se divide en cuatro segmentos de tiempo de tal manera que la estación base 11 comunica simultáneamente con hasta cuatro unidades de abonado 10 en una frecuencia portadora. En consecuencia, la estación base, que utiliza 24 pares de canales, puede permitir que las señales telefónicas sean moduladas en 95 canales, y usar un canal para el control y otras funciones generales:

Uno de los aspectos de aumentar la capacidad de esta forma es comprimir los canales de telecomunicaciones que se transmiten por el canal de comunicación por RF (o el canal por cable). Para la voz, como se describió anteriormente, se pueden utilizar las técnicas de codificación de voz, tales como RELP. Además, se pueden utilizar las técnicas de compresión de datos de baja velocidad y datos de fax de baja velocidad, como se describe en la patente US 4.974.099 titulada "Sistema y método de compresión de señales de comunicación", a nombre de Lin *et al*.

En el sistema descrito anteriormente, tres codificadores en banda vocal, RELP, datos de baja velocidad y fax de baja velocidad, comprimen señales de PCM a 64 kb/seg en una señal a 14,5 kb/s. A 14,5 kb/s, estos tres codificadores pueden operar dentro de un solo segmento de RF de 16 fases o una ranura de RF de 4 fases de doble ancho. El codificador RELP se usa para la voz, el codificador de datos de velocidad baja se utiliza para pasar un número de transmisiones de módem en banda vocal a velocidades de hasta 2400 bps, y el codificador de fax de velocidad baja se utiliza para pasar transmisiones de fax de Grupo 3 a 2400 bps. Cada codificador de transmisión tiene un decodificador correspondiente dentro de un receptor, que puede, por ejemplo, ser asignado a través del canal de control del sistema.

Para permitir que el sistema de telecomunicaciones se adapte a los módems y máquinas de fax en banda vocal de alta velocidad, se emplean las dos técnicas de compresión en banda vocal relacionadas de la presente divulgación. Los codificadores y decodificadores (códecs), llamados códec de alta velocidad y códec de velocidad ultrarrápida, consiguen un aprovechamiento de la transmisión de datos comprimidos mejor que los codificadores de datos de baja velocidad y de fax, empleando menos compresión y por lo tanto proporcionando más ancho de banda a la señal de datos

El códec de alta velocidad permite que el sistema de telecomunicaciones pase transmisiones de fax y módem en banda vocal a velocidades de hasta 9,6 kb/s. El códec de velocidad ultrarrápida soporta transmisiones de fax y módem en banda vocal de hasta 14,4 kb/s, y superiores. El códec de alta velocidad funciona utilizando tres segmentos de RF de 16 fases o cuatro segmentos de RF de 8 fases. El códec de velocidad ultrarrápida funciona utilizando cuatro segmentos de RF de 16 fases. Preferiblemente, los algoritmos de compresión de datos de alta velocidad y de velocidad ultrarrápida pasan una representación de una forma de onda en banda vocal analógica a través de un canal digital con velocidades de datos limitadas mientras minimiza una distorsión perjudicial.

Debido a que estos códecs utilizan varios segmentos de RF, es necesaria la reasignación dinámica de los segmentos en los canales de comunicación por RF. La característica de asignación dinámica de segmento de tiempo/ancho de banda de la presente divulgación detecta y monitoriza la transmisión de datos y forma un canal de datos a partir del número necesario de segmentos, pero si el número necesario de segmentos no estuviera disponible, se asigna el codificador de datos de baja velocidad o datos de fax de baja velocidad a la llamada. Estos métodos de asignación se describen, por ejemplo, en la Patente US 4.785.450, concedida el 15 de noviembre de 1988, titulada "Aparato y método para obtener agilidad de frecuencia en sistemas de comunicación digital", a nombre de DR Bolgiano *et al.*

La figura 2 es un diagrama de bloques de alto nivel de la aplicación del sistema de compresión de la presente divulgación, incluida la función de asignación dinámica de segmentos de tiempo/ancho de banda, y los códecs de datos de alta velocidad y de velocidad ultrarrápida, para la compresión de datos de alta velocidad de la disposición ilustrativa de un sistema de telecomunicaciones inalámbricas. El sistema incluye: un procesador selector de compresión (CSP) 200, que incluye una unidad de control 201 y una sección monitora 202, un procesador de formación de canales 260, y los codificadores/decodificadores (códecs) de compresión RELP 210, datos de baja velocidad 220, fax de baja velocidad 230, datos de alta velocidad 240 y datos de velocidad ultrarrápida 250.

El CSP 200 recibe la señal telefónica desde el teléfono de la centralita local 270 y es un procesador digital diseñado para efectuar la monitorización de la señal telefónica para identificar los tipos específicos de las señales de datos con sus respectivos tonos de respuesta del módem e iniciar el establecimiento del canal de comunicación. En otra disposición ilustrativa que utiliza comunicaciones de abonado a abonado, el CSP 200 puede recibir la señal telefónica de otras fuentes locales. La sección monitora 202 del CSP 200 informa a la unidad de control 201 de la

presencia de la señal de datos. La unidad de control 201 es responsable de aplicar la formación externa de un canal de comunicación de RF, así como la asignación de un tipo de CODEC de compresión 210, 220, 230, 240 y 250.

El procesador de formación de canales 260 recibe una solicitud de canal de transmisión del CSP 200 y asigna un segmento de comunicación por RF disponible a una señal telefónica. El procesador de formación de canales 260 mantiene la información de asignación del canal actual del sistema en una memoria (que no se muestra) para determinar qué segmentos de tiempo no se utilizan actualmente para otras señales telefónicas. Como es conocido en los sistemas TDMA, cada segmento de tiempo del canal está formado con un tiempo de guardia, que es un período corto de señal utilizado para inicializar un receptor antes de enviar los datos. Si hay señales de datos que requieren más de un segmento de tiempo de RF, el procesador de formación de canales 260 forma el canal a partir de un número predeterminado de segmentos de tiempo es contiguo, sólo se utiliza un tiempo de guardia.

El procesador de formación de canales 260 de una disposición ilustrativa de la divulgación puede ser una unidad procesadora de radio (RPU) de una estación base de la red. La RPU puede ser la encargada de almacenar las asignaciones de intervalos de tiempo de canal y adjudicar los segmentos de tiempo de canal para todo el sistema de la figura 1.

El CODEC RELP 210 aplica los algoritmos de codificación (y decodificación) de compresión para las señales de voz. El CODEC de datos de baja velocidad 220 y el CODEC de fax de baja velocidad 230, el CODEC de datos de alta velocidad 240 y el CODEC de datos de velocidad ultrarrápida 250 aplican los respectivos algoritmos de compresión de datos para los datos en banda vocal del tipo identificado.

En general, el CSP 200 y los CODEC 210, 220, 230, 240 y 250 pueden integrarse en un procesador de señal digital para realizar la monitorización de la señal de datos, el procesamiento de las señales y las operaciones de codificación y decodificación de la compresión de señales. Un procesador de este tipo se elige, por ejemplo, de la familia de procesadores de señales digitales TMS 320C5X de Texas Instruments.

A continuación se describe el funcionamiento del sistema de compresión. Haciendo referencia aún a la figura 2, cuando la llamada de voz se establece por primera vez, el códec RELP de voz 210 se asigna inicialmente a la señal telefónica. El CSP 200 monitoriza la señal telefónica a través de la sección monitora 202, y la unidad de control 201 determina el tipo de señal en banda vocal basado en la detección de la señal de respuesta del módem. Cada tipo de datos en banda vocal tiene una señal de respuesta del módem particular e identificable. La Tabla 1 resuma algunas de las distintas características típicas del origen y respuesta del módem que son bien conocidas en la técnica.

La Tabla 1 sirve a efectos ilustrativos y no pretende, sin embargo, describir todas las características posibles del módem.

(Tabla pasa a página siguiente)

20

25

40

45

50

55

60

| 5 |  |

|---|--|

| J |  |

| Respuesta (o canal de retorno) | e retorno)    |        |      |        |       |       | Origen  |               |        |         |          |         |

|--------------------------------|---------------|--------|------|--------|-------|-------|---------|---------------|--------|---------|----------|---------|

| V.77/BPS                       | Desactivar EC | Dúplex | 9    | poæ    | £     | marca | espacio | fo            | pow    | fs      | marca    | espacio |

| V.16                           | ON            | В      | 480  | FSK    | 200   | 570   | 390     | 930 1400 2100 | FM     |         |          |         |

| V.16 digital                   | ON            | æ      | 480  | FSK    | 200   | 570   | 390     | 1400          | FSK    | 100     | 1480     | 1320    |

| V.19                           | NO            |        | 420  | AM     | 5     |       |         |               | DTMF   |         |          |         |

| V.19 a111                      | NO            | 13     | 1750 | FSK    | <=300 | 1830  | 1650    |               | DTMF   |         |          |         |

| V.19alL2                       | NO            | В      | 420  | FSK    | <=75  | 390   | 450     |               | DTMF   |         |          |         |

| V.20                           | ON            | 13     | 420  | AM     | 5     |       |         |               | MTFSK  |         | 920-1960 |         |

| V.20 alt                       | ON            | В      | 460  | FSK    | <=75  | 420   | 480     |               | MTFSK  |         | 920-1960 |         |

| V.21                           | 2100          | L      | 1730 | FSK    | <=300 | 1830  | 1650    | 1080          | FSK    | <=300   | 1180     | 980     |

| V.22 1200                      | 2100          | ш      | 2400 | 4 DPSK | 009   |       |         | 1200          | 4 DPSK | 009     |          |         |

| V.22 bis 2400                  | 2100          | ıL     | 2400 | 16QAM  | 000   |       |         | 1200          | 16QAM  | 009     |          |         |

| 5.2.1200                       | 2100          | B      | 420  | FSK    | <=75  | 390   | 450     | 1700          | FSK    | <= 1200 | 1300     | 2100    |

| V.23 600                       | 2100          | В      | 420  | FSK    | <=75  | 390   | 450     | 1500          | FSK    | 009=>   | 1300     | 1700    |

| V.26 ter                       | 2100          | F/H    | 1800 | 4DPSK  | <=75  |       |         | 1800          | 4 DPSK | 1200    |          |         |

| V.27 ter 4800                  | 2100          | =      | 1800 | 8 DPSK | 1100  |       |         | 1800          | 8 DPSK | 1200    |          |         |

| V.27 ter 2400                  | 2100          | II (B) | 1800 | 4 DPSK | 1200  |       |         | 1800          | 4 DPSK | 1200    |          |         |

| V.29 9600                      | 2100          | =      | 1700 | 16 QAM | 2400  |       |         | 1700          | 16 QAM | 2400    |          |         |

| V.29 7200                      | 2100          | =      | 1700 | 8 QAM  | 2400  |       |         | 1700          | 8 QAM  | 2400    |          |         |

| V.294800                       | 2100          | =      | 1700 | 4 PSK  | 2400  |       |         | 1700          | 4 QAM  | 2400    |          |         |

| V.J2 9600                      | 2100          | u_     | 1800 | 16 QAM | 2400  |       |         | 1800          | 16 QAM | 2400    |          |         |

| V.32 4800                      | 2100          | u.     | 1800 | 4 PSK  | 2400  |       |         | 1800          | 4 PSK  | 2400    |          |         |

| FAX canal a 300 bps            |               | æ      | 1900 | FSK    |       |       |         |               |        |         |          |         |

Características del módem en banda vocal

Volviendo a la Figura 2, una vez que se determina el tipo de datos en banda vocal, si se requiere la compresión de datos de alta velocidad o datos de velocidad ultrarrápida, el CSP 200 inicia la reasignación del canal de voz, y abajo se describe el método utilizado de asignación dinámica de segmentos de tiempo. La unidad de control 201 indica al procesador de formación de canales 260 que forme un canal de comunicación por RF con un número predeterminado de segmentos de tiempo. En una disposición de la presente divulgación, se asigna un segmento de tiempo automáticamente a la llamada, pero esto no es necesario. El procesador de formación de canales 260 examina la memoria para determinar el número y la ubicación de la portadora de RF de los segmentos de tiempo de RF disponibles. Si el procesador de formación de canales localiza el número de segmentos predeterminados, el canal de comunicación por RF es formado a partir del número predeterminado de segmentos de tiempo de RF y se avisa a la unidad de control 201. La unidad de control 201 asigna entonces un códec de datos de alta velocidad o un códec de datos de velocidad ultrarrápida correspondiente a la señal de datos, y la señal de datos comprimida es asignada a y modulada en el canal de comunicación por RF de múltiples segmentos formado.

15

Si no hay suficientes segmentos de tiempo disponibles, se informa a la unidad de control 201 y se forma un canal de comunicación por RF a partir de un solo segmento de tiempo de RF, y la unidad de control 201 asigna entonces el CODEC de datos de baja velocidad o el CODEC de fax de baja velocidad a la señal de datos. Como se indicó anteriormente, una disposición de la presente divulgación asigna automáticamente un segmento de tiempo cuando se recibe la señal telefónica antes de formar un canal de comunicación de múltiples segmentos de tiempo, y por lo tanto ya se le ha asignado a la señal telefónica un segmento en este momento.

La asignación dinámica de segmentos de tiempo/ancho de banda

La Tabla 2 resume los requisitos de los segmentos de tiempo para los tipos de compresión de señales:

#### TABLA 2

30

25

35

40

45

| # segmentos de 4 | # segmentos de 8 | # segmentos de 16 |

|------------------|------------------|-------------------|

| fases            | fases            | fases             |

| 2                | N/A              | 1                 |

| 2                | N/A              | 1                 |

| 2                | N/A              | 1                 |

| N/A              | 4                | 3                 |

| N/A              | N/A              | 4                 |

|                  | 2 2 2 N/A        | fases             |

Puesto que el codificador de alta velocidad modula los datos en canales de tres segmentos de 16 fases y cuatro segmentos de 8 fases, sus datos comprimidos encajan deseablemente en uno de los dos canales que tiene menos ancho de banda. En la Tabla 3 se muestra la disponibilidad de bits de los diversos tipos de canales de la disposición para el sistema de radiotelecomunicaciones descrito en la Figura 1.

55

50

60

#### TABLA 3

Mod, Modo ceros de Preám-CW bloque bloque ceros de Bits de 5 Nivel. inicio bulo B finalizadatos/ A Bloque Segmención tos 16-PSK, 1 80 328 voz / Ō 5 3 84 8 10 prueba de canal 16-PSK, 3 voz (HSD) 0 5 3 262 262 8 1048 15 16-PSK, 4 0 352 1408 voz 5 3 352 8 (UHSD) 20 prueba de 8-PSK, 1 0 14 4 0 8 462 154 canal 8-PSK. 4 voz (HSP) 0 14 4 347 347 8 1041 25 4-PSK, 2 voz/ 0 13 6 160 173 8 328 prueba de canal BPSK, 1 8 **RCC** 8 44 112 0 8 112 30 (UW) 8 HPSK, 1 Refinación 0 52 112 0 8 112 (UW)

35

En la tabla 3, los "ceros" indica que no hay ninguna modulación, el preámbulo es un patrón de sincronización de bits, y "cw" significa palabra código, que incluye el control de llamadas, el procesamiento de llamadas y la información de señalización. El bloque A y el bloque B, representan un primer y un segundo bloque de 22,5 mseg de muestras de datos en banda vocal comprimidas.

Como se observa en la Tabla 3, el canal de cuatro segmentos de 8 fases lleva menos bits que el canal de tres segmentos de 16 fases. El bloque de salida comprimido del codificador de alta velocidad de una disposición de la presente divulgación, por lo tanto, puede ocupar 1041 bits o menos. La Tabla 4A muestra la asignación de bits del bloque de salida comprimido del codificador de datos de alta velocidad.

TABLA 4A

| 55 |  |

|----|--|

|    |  |

| 60 |  |

| Datos               | Bits por Instancia | Cantidad | Protegido | Número de bits |

|---------------------|--------------------|----------|-----------|----------------|

| Muestra codificada  | 5                  | 180      | sí        | 900            |

| Ganancia codificada | 6                  | 1        | sí        | 6              |

| Reserva protegida   | 1                  | 6        | sí        | 6              |

| Paridad Hamming     | 7                  | 16       | N/A       | 112            |

| Reserva             | 1                  | 24       | no        | 24             |

| Total por bloque    |                    | ·        |           | 1048           |

En la Tabla 4A "protegido" indica que la corrección hacia delante de errores (FEC) se aplica al flujo de bits. El flujo de bits del codificador de velocidad ultrarrápida modula un canal de cuatro segmentos de 16 fases, de los cuales 1.408 bits están disponibles para los datos del codificador en cada período de tiempo de 22,5 mseg.

La Tabla 4B muestra la asignación de bits del bloque de salida comprimido del codificador de datos de velocidad ultrarrápida.

5 TABLA 4B

| Datos                | Bits por Instancia | Cantidad | Protegido | Número de bits |

|----------------------|--------------------|----------|-----------|----------------|

| Muestra codificada   | 7                  | 180      | sí        | 1260           |

| Ganancia codificada  | 7                  | 1        | sí        | 7              |

| Reserva protegida    | 13                 | 1        | sí        | 13             |

| Paridad de Hamming   | 7                  | 16       | N/A       | 112            |

| Reserva desprotegida | 16                 | 1        | no        | 16             |

| Total por bloque     |                    |          |           | 1408           |

20

10

15

Las técnicas de compresión de datos de alta velocidad y datos de velocidad ultrarrápida que se describen a continuación son disposiciones de la presente divulgación que pueden requerir múltiples segmentos de tiempo para un canal de comunicación, aunque se pueden desarrollar otras técnicas de compresión del mismo espíritu que aquí se describe para otros tipos específicos de señales de datos que no siguen necesariamente las características del módem en banda vocal descritas anteriormente. Estas otras disposiciones también pueden emplear el método de asignación dinámica de segmentos de tiempo/ancho de banda que se utiliza en la presente divulgación.

30

A continuación se describe el método general de asignación dinámica de segmentos de tiempo/ancho de banda. La Figura 3 ilustra el proceso de asignación dinámica de segmentos de tiempo/ancho de banda tal como se aplica en, por ejemplo, el CSP 200 de la figura 2. Haciendo referencia a la figura 3A, cuando la llamada de voz se establece por primera vez, la etapa de monitorización de voz 301, monitoriza el teléfono para detectar una señal de datos. En la etapa 301, el códec RELP 210 se asigna inicialmente a la señal telefónica. Sin embargo, cuando hay una señal de datos, la etapa de decisión 302 determina el tipo de señal en banda vocal basada en la detección de la señal de respuesta del módem.

35

Si los datos son datos de baja velocidad o fax de baja velocidad, la etapa 303 asigna el proceso de asignación de baja velocidad al que, por ejemplo, se ha asignado un solo segmento de portadora RF. A continuación, la etapa 304 determina si la señal de datos es fax o datos de baja velocidad, y asigna las respectivas etapas de algoritmo 305 y 306 del códec de fax de baja velocidad 230 o del códec de datos de baja velocidad 220.

40

Si la señal es de un tipo de datos de alta velocidad en la etapa 302, entonces, la siguiente etapa 307 solicita un canal de datos de alta velocidad del proceso de formación de canales 260. En una disposición de la presente divulgación, el proceso de formación de canales 260 requerirá que el usuario/abonado proporcione información para solicitar el tipo de canal. Otra disposición de la presente disposición puede además determinar a partir de las señales de módem si la señal de datos requiere el método de compresión de datos de alta velocidad o datos de velocidad ultrarrápida con el fin de solicitar el tipo correcto de canal.

La Figura 3B muestra el proceso de asignación de canal realizado por el procesador de formación de canales 260 tras la solicitud de un canal de datos de alta velocidad desde la etapa 307 de la figura 3A. El procesador de formación de canales puede ser una unidad procesadora de radio (RPU) de la estación base del sistema del estado de la técnica ilustrativo que se ha descrito anteriormente, y la RPU puede asignar segmentos de tiempo de la portadora de RF a las comunicaciones de abonados a través de un canal de comunicación.

55

Empezando en la etapa 320 de la figura 3B, el procesador normalmente asigna un canal de voz para una llamada telefónica; sin embargo, se puede elegir cualquier proceso inicial de asignación, como se describe en la patente US 4.675.863. A continuación, la etapa 321 comprueba si hay una solicitud de un canal de datos de alta velocidad a partir de la etapa 307 de la figura 3A. Si no hay ninguna petición, la asignación se mantiene en el modo por defecto, que es de voz para esta disposición ilustrativa. Si hay una petición, la etapa 322 comprueba el equipamiento del abonado para determinar si el abonado está equipado para aceptar un canal de datos de alta velocidad. Si el abonado no está equipado para aceptar un canal de datos de alta velocidad en la etapa 323 utilizando un número predeterminado de segmentos.

60

Si el abonado está equipado para un canal de datos de alta velocidad, la etapa 324 determina si el abonado está equipado para aceptar un canal de datos de alta velocidad del tipo de velocidad ultrarrápida ("Canal UHSD") (o si se ha solicitado). Si es así, la etapa 325 comprueba si hay un número predeterminado de segmentos de portadora de RF disponible, y si es así, la etapa 326 crea el canal UHSD. La etapa 325 puede ser realizada por un procesador que controla una memoria que contiene las asignaciones actuales de los canales del sistema para saber

si hay disponible un número requerido de segmentos de tiempo de RF de dieciséis fases (cuatro para la disposición ilustrativa). Si el número requerido de segmentos no está disponible, entonces intenta averiguar si se puede crear el canal como uno de tipo de datos de alta velocidad ("Canal HSD") como se describe posteriormente en la etapa 328.

c

Si la disponibilidad del abonado (o la solicitud) indica que el canal de datos de alta velocidad no debería formarse como un canal de velocidad ultrarrápida de tipo canal UHSD en la etapa 324, la etapa 327 comprueba si la solicitud o disponibilidad del abonado indica que el canal de datos de alta velocidad debería formarse como un canal de tipo HSD de alta velocidad. En caso contrario, se forma el canal de datos de baja velocidad en la etapa 323, como se ha descrito anteriormente, pero si se solicita o provee el Canal HSD, entonces la etapa 328 verifica si el número predeterminado de segmentos de tiempo de la portadora de RF está disponible para el canal de HSD.

La etapa 328 puede ser realizada por un procesador que comprueba si una memoria contiene las asignaciones actuales de los canales del sistema para encontrar si hay un primer número necesario de segmentos de tiempo disponible (segmentos de tiempo de RF de dieciséis fases) (tres para la disposición ilustrativa), y si no es así, si hay un segundo número necesario de segmentos de tiempo disponible (segmentos de RF de ocho fases) (cuatro para la disposición ilustrativa). Si el número necesario de segmentos de tiempo está disponible, se asignan los segmentos de tiempo y se forma el canal de HSD en la etapa 329. Si la etapa de disponibilidad de canal de alta velocidad no puede encontrar el número necesario de canales, entonces la etapa 323, simplemente asigna el canal de baja velocidad.

20

Volviendo a la figura 3A, en la etapa 308, el proceso comprueba la respuesta a la solicitud del canal de datos de alta velocidad. Si en la etapa 308 se deniega la solicitud y no se ha formado ningún canal de datos de alta velocidad, entonces se ejecutan la etapa 303 y la secuencia para asignar los algoritmos de baja velocidad. Si la solicitud de canal de datos de alta velocidad es aceptada, la etapa de disponibilidad de canal de alta velocidad 309 determina qué tipo de canal ha sido asignado. Si el canal de datos de alta velocidad se corresponde con los datos de velocidad ultrarrápida, se ejecutan los algoritmos de codificación del CODEC de datos de velocidad ultrarrápida 250 en la etapa 310, y si el canal de datos de alta velocidad se corresponde con los datos de alta velocidad, se ejecutan los algoritmos de codificación en el CODEC de datos de alta velocidad 240 en la etapa 311.

### 10 Los CODEC de alta velocidad y de velocidad ultrarrápida

El códec de alta velocidad 240 y el códec de velocidad ultrarrápida 250 proporcionan la compresión de un canal de datos bidireccional con señales telefónicas muestreadas (Modulación de códigos por pulsos (PCM)), siendo las señales telefónicas, en la disposición ilustrativa, la señal de entrada y la señal de salida. Las señales telefónicas proporcionadas al proceso de compresión suelen ser de PCM de ley A o ley Mu de 64 kb/s, aunque se pueden utilizar muestras enteras de 16 bits a 128 kb/s, o de otro tipo, empleando un proceso de conversión. El proceso de compresión comprime el flujo de bits de la muestra de 64 kb/s (o 128 kbs) a una velocidad de datos inferior. Los datos de velocidad inferior son enviados por el canal de RF para el proceso de expansión, que expande de nuevo los datos de velocidad inferior en un flujo de bits de la muestra reconstruida de 64 kb/s (o 128 kb/s). El objetivo del codificador es que las muestras sintetizadas o reconstituidas sean una representación aproximada de la señal muestreada original.

En los sistemas de PCM, las señales analógicas en banda vocal se convierten en una secuencia de muestras digitales a una velocidad de muestreo de 8 miles de muestras/segundo. Las muestras tienen un ancho de 8 bits, lo que permite 256 niveles de cuantificación posibles. Cuando las señales analógicas se muestrean, un importante factor de mérito es la relación de señal a ruido de cuantificación (SQNR). Para un cuantificador uniformemente separado, la SQNR es 6B-1.24 dB, donde B es el número de bits por muestra cuantificada.

Un cuantificador uniforme de 8 bits por lo tanto tiene una SQNR de 46,76 dB, que es excelente para las señales de voz. Esta SQNR sólo se consigue si la señal analógica original tiene una amplitud que ocupa todo el rango dinámico de la cuantificación. Si el rango dinámico de la señal original supera aquel del cuantificador, se produce una limitación. Este es un tipo muy indeseable de distorsión para ambas señales tanto de voz como de módem en banda vocal. Si la señal original tiene un rango dinámico menor que el del cuantificador, la SQNR resultante es menor que el óptimo de 46,76 dB. Por cada dB que el rango dinámico de la señal sea menor que el rango dinámico del cuantificador, se produce una pérdida de 1 dB de la SQNR.

Dado que las señales en banda vocal utilizadas en telefonía tienen un amplio rango dinámico, un cuantificador uniforme puede no ser la opción óptima. Por lo tanto, no se emplean cuantificadores no uniformes. Hay dos estándares para los cuantificadores no uniformes para la PCM: La ley Mu y la ley A, y estos estándares son muy conocidos en la técnica y han sido descritos en el capítulo 8 de Sistemas de comunicación, por Simón Haykin. Ambas técnicas utilizan niveles de cuantificadores separados logarítmicamente con el fin de aumentar el rango dinámico de los cuantificadores. La figura 4A muestra las características del cuantificador de ley A.

La separación entre los niveles del cuantificadores a niveles de señal altos es mayor que la separación a niveles bajos. El resultado es una SQNR más uniforme en una muestra para el muestreo. Aunque la mejor SQNR para estos cuantificadores es menor que la del cuantificador uniforme de 8 bits, estos cuantificadores pueden proporcionar una buena SQNR en un rango más amplio de niveles de señal.

La figura 4B compara el resultado de la SQNR con el nivel de señal de una ley A y un cuantificador uniforme de 8 bits. Aunque el cuantificador uniforme muestra un rendimiento superior a niveles altos de señal, el cuantificador de ley A conserva una buena SQNR en un rango dinámico más amplio.

Los módems en banda vocal funcionan bien en una red de telefonía que utilice cualquiera de las leyes Mu o A de PCM a 64 kb/s debido al amplio rango dinámico. El nivel de salida de transmisión de estos módems es alto con el fin de utilizar los canales a su máxima capacidad, pero los canales telefónicos tienen diversas pérdidas de nivel de señal. Como resultado, a pesar de que el nivel de salida del módem esté fijado en un nivel alto, el nivel en otro punto de la red puede ser significativamente inferior. El rango dinámico de la PCM compensa esta situación.

La compresión de la PCM de 64 kb/s a una velocidad de datos inferior disminuye el número de bits por muestra y por lo general produce una disminución significativa en la SQNR. La distorsión producida por la compresión se minimiza diseñando dinámicamente un cuantificador para ajustar el rango dinámico de la señal de entrada. Una vez que los dos rangos dinámicos se corresponden, las muestras se cuantifican usando un cuantificador con la separación de niveles que se acaba de definir.

La figura 4C ilustra un ejemplo simple del método de compresión mediante la asignación de las muestras de señal de una cuantificación a otra cuantificación. Un bloque de muestras de señal 410 se compone de tres muestras 411, 413 y 415. Un primer conjunto de niveles de cuantificación 420 indica el valor aproximado de las amplitudes de muestras 412, 414 y 416. Sin embargo, los niveles de cuantificación requieren que un cierto número de bits de información, cinco bits para los 20 niveles que se muestran de la primera cuantificación, se transmitan a un receptor para representar a uno de los niveles de la primera cuantificación. Para enviar tres valores de muestra correspondientes a las tres muestras 411, 413 y 415, quince bits son deseables.

El método ilustrativo de la presente divulgación define un nuevo conjunto de niveles para cada bloque de muestras de señal basado en la amplitud pico. Como se muestra en la figura 4C, el bloque de muestras 410 tiene una muestra 413 que tiene un valor de amplitud pico 414. El método define un nuevo conjunto de niveles de cuantificación mediante la definición de la amplitud pico 414 como el valor más alto de nivel, y determina un número predeterminado de valores de nivel por debajo de esta amplitud. Como se muestra en la figura 4C, esto corresponde a 5 valores de nivel. Para esta nueva cuantificación, sólo tres bits son necesarios para definir un valor de nivel, pero el valor de la amplitud pico debe ser enviada también como un factor de graduación para indicar la relación entre los valores nuevos de los niveles del cuantificador y los valores originales de los niveles del cuantificador. En consecuencia, o se transmiten cinco bits correspondientes al valor original de la amplitud pico y nueve bits (tres por muestra) para el bloque de muestras 410, o se necesitan catorce bits. El ejemplo muestra que se envía un bit menos, sin embargo, si hay diez muestras en el bloque, el método de cuantificación original requiere el envío de cincuenta bits, pero el nuevo cuantificador sólo requiere el envío de treinta y cinco bits.

A continuación se describen las disposiciones diseñadas para los estándares de la ley Mu y la ley A. Sin embargo, las técnicas descritas se extienden fácilmente a cualquier sistema de recepción de muestras cuantificadas con un cuantificador de compresión y expansión no uniforme.

#### El CODEC de datos de alta velocidad

25

50

La figura 5A es un diagrama de bloques de un codificador de alta velocidad. El codificador de la disposición ilustrativa transforma los datos entre la PCM de 64 kb/s y el flujo de datos comprimidos codificados con corrección de errores hacia adelante (FEC) de 46,58 kb/s. La velocidad de datos comprimidos es de 40,267 kb/s, y el resto del flujo de bits transmitido se utiliza para la corrección de errores.

Como se muestra en la figura 5, el codificador de datos de alta velocidad de la presente invención incluye un búfer opcional 510, un expansor de PCM 520, un proceso de cálculo de ganancia 522, un retardo 521, un cuantificador de muestras de datos 523, y un proceso de codificación de transmisión 530 opcional. El proceso de codificación de transmisión 530 incluye además un codificador FEC 532 y un intercalador 531.

El búfer opcional 510 tiene un número predeterminado de muestras para crear un bloque de muestras para el proceso de compresión de datos de alta velocidad. Alternativamente, las muestras pueden ser recibidas en un formato de bloque. El expansor de PCM 510 convierte las muestras de la PCM de ley A o ley Mu en muestras lineales. El proceso de cálculo de ganancia 522 calcula el valor de ganancia cuantificada para el bloque de muestras, y el cuantificador de muestras de datos utiliza el valor de ganancia cuantificada para crear un cuantificador separado uniformemente con los valores del nivel de cuantificación graduado por el valor de ganancia cuantificada. El retardo muestra que el valor de ganancia cuantificada se determina antes de que el proceso de compresión cree las muestras cuantificadas codificadas y el proceso de codificación de transmisión 530 se utiliza para proporcionar la codificación con corrección de errores para la transmisión de la ganancia cuantificada codificada y las muestras cuantificadas codificadas.

A continuación se describe el funcionamiento del codificador de compresión de datos de alta velocidad. Como se muestra en la figura 5A, las muestras de PCM de 64 kb/s (ley A o ley Mu) son recibidas por un búfer 510. El búfer 510 proporciona las muestras de PCM como bloques de muestras de 22,5 milisegundos. A la velocidad de 8 miles de muestras/segundo de la PCM, cada bloque contiene 180 muestras. La trama de la PCM recibida se introduce en el

expansor de PCM 520, que convierte las muestras de ley Mu o ley A en muestras lineales de 16 bits (muestras enteras de 16 bits).

El bloque resultante de muestras lineales, que son muestras enteras de 16 bits en la disposición ilustrativa, se introduce en el proceso de cálculo de ganancia 522, que encuentra la muestra en el bloque con el valor de amplitud más grande (valor absoluto). La amplitud de esta muestra determina el valor de ganancia cuantificada para el bloque. El valor de ganancia cuantificada puede ser el valor de amplitud, la diferencia entre el valor máximo de la muestra y la amplitud del bloque más grande, o un valor multiplicador. El valor de ganancia cuantificada es cuantificado utilizando un cuantificador separado logarítmicamente de 64 niveles. El proceso de cálculo de ganancia 522 proporciona tanto el valor de ganancia cuantificada codificado. El valor de ganancia cuantificada codificado es un número de 6 bits que representa uno de los 64 niveles en el cuantificador de ganancia separado logarítmicamente.

El valor de ganancia cuantificada del cálculo de ganancia 522 y el bloque de muestras del proceso de expansión de PCM son proporcionados al cuantificador de muestras de datos 523. El retardo 521 se muestra para indicar que el proceso de cálculo de ganancia 522 debe completar la tarea en el bloque antes de que las muestras sean comprimidas por el cuantificador de muestras de datos 523. El cuantificador de muestras de datos 523 cuantifica las 180 muestras en el bloque utilizando un cuantificador separado uniformemente de 32 niveles. Los niveles del cuantificador se ajustan dinámicamente bloque por bloque utilizando el valor de ganancia cuantificada. Por lo tanto, los niveles del cuantificador separado uniformemente varía de + valor de ganancia cuantificada a - valor de ganancia cuantificada para el conjunto actual de 180 muestras. El cuantificador de muestras emite solo la representación codificada de 5 bits de las 180 muestras, pues la compresión no requiere los valores cuantificados reales.

La ganancia cuantificada codificada y las muestras cuantificadas codificadas se introducen opcionalmente en el proceso de codificación de transmisión 530, que incluye el intercalador 531 y el codificador FEC 532. El codificador FEC 532 es un codificador Hamming extendido (64, 57) y el código Hamming es capaz de corregir un error de un bit y detectar un error de dos bits en cada bloque de 64 bits. El codificador FEC 532 recibe la ganancia cuantificada codificada y las muestras cuantificadas codificadas y las proporciona al intercalador 531, y el intercalador 531 emite los datos comprimidos codificados. El intercalador de una disposición ilustrativa de la presente divulgación es un intercalador de bloques de 16 \* 64 bits.

La figura 5B muestra una disposición ilustrativa del proceso de codificación de transmisión 530 incluyendo el intercalador 531 y el codificador Hamming FEC 532. Se muestra un bloque de 64 por 16 bits. Cada una de las 16 filas representa una sola palabra código Hamming extendida de 64 bits. En el codificador, se leen los datos en el bloque del intercalador de izquierda a derecha a través de las filas empezando por la palabra código 0 bit 0 y terminando con la palabra código 15 bit 63. Las posiciones de los bits (columnas) 0, 1, 2, 4, 8, 16 y 32 se omiten y se completan con cero. Después de completar el intercalador 531, la codificación Hamming se realiza mediante el codificador FEC 532 en los 57 bits de datos en cada fila. Los bits de paridad Hamming se introducen en las posiciones de bits 1, 2, 4, 8, 16 y 32, como se muestra en el diagrama. El bit de verificación de la paridad se introduce en la posición bit 0. Los bits de paridad y los bits de verificación de la paridad para los 16 códigos se pueden calcular a la vez utilizando una función O-Exclusiva amplia de 16 bits. Los bits de paridad Pi se calculan como sigue:

## Pi = XOR Palabra código Bit[k] i = 0..6

45

50

55

25

(k-1) &  $2^i \neq 0$ , donde "&" es una función binaria AND bit a bit.

Después de introducir los bits de paridad en sus posiciones de bit, los bits de verificación de la paridad PC (un bit por cada código) se calculan de la siguiente manera:

63

PC = XOR Palabra código Bit[k]

k=1

Una vez que los bits de paridad se han calculado e introducido, se leen los datos del intercalador de arriba a abajo por las columnas empezando con la palabra código 0, bit 0 y terminando con la palabra código 15, bit 63.

La figura 6A es un diagrama de bloques de alto nivel del decodificador de datos de alta velocidad según una disposición ilustrativa de la presente divulgación. El decodificador de datos de alta velocidad implementa la inversa del proceso de compresión del codificador de datos de alta velocidad, y el decodificador incluye un proceso de decodificación de transmisión 601 opcional, un decodificador de ganancia de trama 610, un decuantificador de muestras de datos 620, un compresor-expansor 630 y un búfer 640. El proceso de decodificación de transmisión 801 incluye un desintercalador 603 y un decodificador FEC 602.

A continuación se describe el funcionamiento del decodificador de datos de alta velocidad con referencia a la figura 6A. Los datos comprimidos recibidos se introducen opcionalmente en el desintercalador 603, que es un proceso de desintercalación de bloques de 16 \* 64 bits. La salida del desintercalador 603 se introduce en el decodificador FEC 602, que es un decodificador Hamming extendido (64, 57). El decodificador Hamming puede corregir errores de 1 bit y detectar errores de 2 bits por bloque. La Figura 6B muestra el proceso de descodificación Hamming y del desintercalador de una disposición de la presente divulgación. Los datos se leen en el desintercalador 603 de arriba a abajo empezando por la palabra código 0 bit 1 y terminando con la palabra código 15 bit 63. El síndrome se calcula como sigue:

Cálculo de los bits de paridad:

10

20

25

50

#### Pi = XOR Palabra código Bit[k] i = 0..5

15 (k-1) &  $2^i \neq 0$ , donde "&" es una función binaria AND bit a bit.

Síndrome = concatenación P5 | P4 | P3 | P1 | P0.

Los bits de verificación de la paridad (un bit por cada código) se calculan de la siguiente manera:

k=1

La representación numérica del síndrome indica la posición del bit (si existe), en la que se ha producido un error de bit. Cuando se produce un error de bit, el bit se invierte (corrige) si se ha establecido el bit de verificación de la paridad para ese código. De lo contrario, se asume que hay dos (o más) errores de bits en el código y el síndrome es incorrecto. Si el síndrome es cero, no se ha producido error de bit. Como en el caso del codificador, los bits de paridad y los bits de verificación de la paridad para las 16 palabras código se pueden calcular al mismo tiempo utilizando una operación O-Exclusiva amplia de 16 bits.

Volviendo a la figura 6A, los datos decodificados del decodificador FEC 602 consta de las muestras cuantificadas codificadas y de la ganancia cuantificada codificada. La ganancia cuantificada codificada se proporciona al decodificador de ganancia 610 que lee el valor de ganancia cuantificada de una tabla utilizando la ganancia cuantificada codificada como el índice en la tabla. Como se mencionó anteriormente, la ganancia cuantificada codificada representa un valor de nivel de un cuantificador separado logarítmicamente de 64 niveles.

El valor de ganancia cuantificada se proporciona al decuantificador de muestras de datos 620, donde se utiliza para graduar los valores de una tabla de niveles del cuantificador uniforme de 32 niveles. La tabla graduada del cuantificador decodifica las muestras cuantificadas codificadas en un bloque de muestras cuantificadas lineales.

El bloque de muestras cuantificadas lineales es convertido en un bloque de muestras de PCM (ley A o ley Mu) por 45 el proceso de compresión y expansión de PCM 630. El bloque de muestras de PCM, se proporciona opcionalmente al búfer 640 que proporciona las muestras de PCM como una señal de 64 kb/s de salida.

El CODEC de velocidad ultrarrápida

La figura 7A es un diagrama de bloques de alto nivel del codificador de velocidad ultrarrápida. El codificador de velocidad ultrarrápida realiza la compresión de datos y la expansión de las señales de módem en banda vocal de velocidad ultrarrápida. El codificador transforma los datos entre la PCM de 64 kb/s y un flujo de datos comprimidos codificados (FEC) de 62,58 kb/s. La velocidad real de datos comprimidos es de 56,311 kb/s, y el resto del flujo de bits se utiliza para los datos de corrección de errores. El códec de velocidad ultrarrápida es similar al códec de alta velocidad.

Como se muestra en la figura 7A, el codificador de datos de velocidad ultrarrápida incluye un búfer 710 opcional, un preprocesador de formato de muestra 720 opcional, un proceso de cálculo de ganancia 722, un retardo 721, un cuantificador de muestras de datos 723, y un proceso de codificación de transmisión 730 opcional. El proceso de codificación de transmisión 730 incluye además un codificador FEC 732 y un intercalador 731.

El búfer 710 opcional tiene un número predeterminado de muestras para crear un bloque de muestras para el proceso de compresión de datos de velocidad ultrarrápida. El preprocesador de formato de muestra 710 elimina la ley A, o cualquier otro formato de transmisión estándar de las muestras de PCM y también convierte los valores de la muestra en un formato numérico predeterminado, tal como sus equivalentes decimales, para mayor comodidad en el procesamiento posterior. El proceso de cálculo de ganancia 722 calcula el valor de ganancia cuantificada para el bloque de muestras, y el cuantificador de muestras de datos utiliza el valor de ganancia cuantificada para crear un conjunto de

niveles del cuantificador con una separación predeterminada y con los valores de nivel de cuantificación graduados por el valor de ganancia cuantificada. El retardo muestra que el valor de ganancia cuantificada se determina antes de que el proceso de compresión cree las muestras cuantificadas codificadas y el proceso de codificación de transmisión 730 se utiliza para proporcionar la codificación con corrección de errores para la transmisión de la ganancia cuantificada codificada y las muestras cuantificadas codificadas.

A continuación se describe el funcionamiento del codificador de compresión de datos de velocidad ultrarrápida. Las muestras de PCM de 64 kb/s (ley A o ley Mu) son proporcionadas al búfer 710. El búfer 710 proporciona las muestras de PCM como bloques de muestras de 22,5 milisegundos. A la velocidad de 8 miles de muestras/segundo de la PCM, cada bloque contiene 180 muestras.

A diferencia del códec de alta velocidad, el códec de velocidad ultrarrápida no convierte las muestras PCM en muestras lineales. En lugar de ello, los datos de PCM de 8 bits se convierten en un tipo predeterminado de formato para la representación de la muestra. En la disposición ilustrativa, para la ley Mu, no se requiere ninguna operación para convertir al formato, pero para la ley A, el preprocesador de formato de muestra 720 convierte las muestras en un formato de valor de nivel predeterminado antes del siguiente procesamiento del cuantificador. Como es evidente para un experto en la materia, las muestras de ley Mu podrían convertirse en una representación de ley A, o en otra disposición ilustrativa, ambos formatos podrían convertirse en un tercer formato predeterminado.

En el códec de velocidad ultrarrápida, es deseable que el tipo de compresión de PCM sea el mismo en ambos extremos de transmisión y recepción del enlace. De lo contrario, sin más procesamiento, las diferencias entre las características de la ley Mu y la ley A pueden producir una no linealidad en las características de extremo a extremo de la codificación de compresión.

El bloque de muestras recibido en el formato de muestra predeterminado se proporciona al proceso de cálculo de ganancia 722, que encuentra la muestra en el bloque con el valor de amplitud más grande (valor absoluto). La amplitud de esta muestra determina la ganancia cuantificada para el bloque. La ganancia cuantificada requiere 7 bits, pues no se usa el bit de signo de la amplitud.

La tabla 5 muestra cómo se representan los números en los estándares de ley A y ley Mu. Se determina el valor absoluto de la muestra correspondiente para esas representaciones respectivas y se calcula la amplitud máxima.

TABLA 5

40

45

50

| Número Dec | Equiv Ley A | Hex Ley A | Equiv Ley u | Hex Ley u |

|------------|-------------|-----------|-------------|-----------|

| 127        | 255         | FF        | 128         | 80        |

| 112        | 240         | F0        | 143         | 8F        |

| 96         | 224         | E0        | 159         | 9F        |

| 16         | 144         | 90        | 239         | EF        |

| 2          | 130         | 82        | 253         | FD        |

| 1          | 129         | 81        | 254         | FE        |

| 0          | 128         | 80        | 255         | FF        |

| -1         | 1           | 01        | 126         | 7E        |

| -2         | 2           | 02        | 125         | 7D        |

| -16        | 16          | 10        | 111         | 6F        |

| -96        | 96          | 60        | 31          | 1F        |

| -112       | 112         | 70        | 15          | OF        |

| -127       | 127         | 7F        | 0           | 00        |

55

La ganancia cuantificada del proceso de cálculo de ganancia 722 y el 2º bloque complementario, se proporcionan al cuantificador de muestras de datos 723 después de que el valor de ganancia cuantificada haya sido calculado, como lo demuestra la presencia del retardo 721.

60

El cuantificador de muestras de datos 723 crea un cuantificador nuevo con un conjunto de niveles del cuantificador a partir del bloque de muestras de ley A o ley Mu. La siguiente explicación describe cómo se determina el nuevo cuantificador para un bloque de muestras. El cuantificador de ley A divide el rango de amplitudes de entrada en 7 segmentos, y el cuantificador de ley Mu divide el rango de amplitudes de entrada en 8 segmentos. Para mayor comodidad, la explicación siguiente describe el proceso de ley A de 7 segmentos, pero es evidente para un experto en la materia extender la explicación de la ley A a la compresión de muestras de ley Mu.

Cada segmento (excepto el primero) tiene un rango de amplitudes que es la mitad del siguiente, y cada segmento (excepto el primero) tiene 16 valores de nivel de cuantificación. Como resultado, el tamaño del paso de cuantificación en cada segmento es el doble que el anterior. La Tabla 6 enumera los segmentos del cuantificador de ley A, junto con sus rangos de amplitud y tamaño de los pasos de una disposición ilustrativa.

TABLA 6

| Número de | Rango de amplitud | Rango de amplitud | Tamaño de paso | Código de |

|-----------|-------------------|-------------------|----------------|-----------|

| segmento  | de entrada        | normalizado       | normalizado    | ley A     |

| 1         | 031               | 01/64             | 1/2048         | 031       |

| 2         | 3263              | 1/641/32          | 1/1024         | 3247      |

| 3         | 64127             | 1/321/16          | 1/512          | 4863      |

| 4         | 128255            | 1/161/8           | 1/256          | 6479      |

| 5         | 256511            | 1/81/4            | 1/128          | 8095      |

| 6         | 5121023           | 1/41/2            | 1/64           | 96111     |

| 7         | 10232047          | 1/21              | 1/32           | 112127    |

25

50

10

15

20

Las muestras que representan la señal de datos de entrada pueden abarcar todo el rango dinámico del cuantificador de ley A, y el cuantificador de ley A se convierte en un cuantificador nuevo eliminando los niveles seleccionados de los niveles del cuantificador de ley A. A continuación se ilustra el proceso si el cuantificador nuevo resultante tiene una separación de valores de nivel uniforme y todos los segmentos se utilizan para representar un bloque de muestras. El tamaño de paso del último segmento, 1/32, es el mayor tamaño de paso en el cuantificador, por lo tanto, todos los valores de nivel del cuantificador en el último segmento se mantienen. El sexto segmento tiene un tamaño de paso de valor de nivel del cuantificador de 1/64. Un tamaño de paso de 1/32 en el séptimo segmento determina que cualquier otro nivel del cuantificador en el sexto segmento es eliminado, lo que da como resultado un tamaño de paso de 1/32. Del mismo modo, este proceso se repite para el quinto al tercer segmento. El primer y segundo segmento combinados sólo abarcan un rango de 1/32, y por lo tanto, ninguno de los niveles del cuantificador se mantiene. Esto se traduce en 31 niveles positivos y 31 niveles negativos, y se mantiene un nivel cero para separar el primer segmento positivo y el primer segmento negativo, dando un cuantificador uniforme de 63 niveles.

A continuación, el proceso calcula la amplitud máxima de un bloque de muestras y determina qué segmento de ley A contiene esa amplitud. Para ese bloque de datos se ignoran todos los segmentos superiores a ese "segmento pico". El tamaño del paso del segmento pico define el tamaño del paso del cuantificador. Por lo tanto, en el cuantificador uniforme resultante para el bloque, todos los niveles del cuantificador en el segmento pico se mantienen, la mitad de los niveles en el segmento inmediatamente inferior se mantienen, y los valores de nivel del cuantificador se asignan hasta que o bien se alcanza el último segmento o bien ya no quedan disponibles otros valores de nivel del cuantificador.

En la figura 9 se muestra el método de funcionamiento del cuantificador de velocidad ultrarrápida, un cuantificador de 128 niveles, de una disposición ilustrativa de la presente divulgación.

En la etapa 904, el método recibe un bloque de muestras comprimido y expandido (tal como por compresión y expansión de ley A o ley Mu).

En la etapa 906, se determina la muestra de la amplitud pico en el bloque y el segmento correspondiente, y el valor de la amplitud pico es el segmento pico.

En la etapa 910, se mantienen todos los valores de nivel del cuantificador del segmento pico.

En la etapa 912, a menos que se haya alcanzado el nivel cero, se mantienen los 16 niveles del segmento siguien-60 te.

En la etapa 914, a menos que se alcance el nivel cero, se mantienen los 16 niveles del segmento siguiente.

En la etapa 916, a menos que se alcance el nivel cero, se mantiene cualquier otro nivel (valores de 8 niveles) del segmento siguiente.

En la etapa 918, a menos que se alcance el nivel cero, se mantienen cuatro niveles del segmento siguiente más bajo.

En la etapa 920, a menos que se alcance el nivel cero, se mantienen 2 niveles del segmento siguiente más bajo.

En la etapa 922, a menos que se encuentre el nivel cero, se mantiene 1 nivel del segmento siguiente más bajo.

En la etapa 924, se mantiene el nivel cero.

5

10

15

40

45

50

55

60