11) Número de publicación: 2 368 417

51 Int. Cl.: H04B 1/713 H04L 27/26

(2011.01) (2006.01)

| 12            | TRADUCCIÓN DE PATENTE EUROPEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{}$ | TITAL DOCUMENT OF TAXABLE PORT |

T3

- 96 Número de solicitud europea: 06827089 .1

- 96 Fecha de presentación: 27.10.2006

- Número de publicación de la solicitud: 1949551

Fecha de publicación de la solicitud: 30.07.2008

- (54) Título: MÉTODO Y APARATO PARA GENERAR UNA PERMUTACIÓN PARA SALTO DE ENLACE DE AVANCE EN UN SISTEMA DE COMUNICACIÓN INALÁMBRICO.

- 30 Prioridad: 27.10.2005 US 731128 P

(73) Titular/es:

QUALCOMM INCORPORATED 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121, US

- 45 Fecha de publicación de la mención BOPI: 17.11.2011

- 72 Inventor/es:

PALANKI, Ravi y KHANDEKAR, Aamod

- 45 Fecha de la publicación del folleto de la patente: 17.11.2011

- (74) Agente: Isern Jara, Jorge

ES 2 368 417 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

Método y aparato para generar una permutación para salto de enlace de avance en un sistema de comunicación inalámbrico

#### ANTECEDENTES DE LA INVENCIÓN

#### Campo de la invención

10 La presente invención se refiere, de manera general, a comunicación inalámbrica, y más particularmente, a métodos y aparatos para generar una permutación para salto de enlace en avance.

#### **Antecedentes**

Los sistemas de comunicación inalámbricos han pasado a ser un medio prevalente, mediante el cual la mayoría de personas, a escala mundial, han pasado a comunicarse. Los dispositivos de comunicación inalámbricos han pasado a ser pequeños y más potentes, a efectos de cumplir con las necesidades de los consumidores y para mejorar la portabilidad y comodidad. El incremento en la potencia de proceso en dispositivos móviles, tales como teléfonos celulares, ha conducido a un incremento en la demanda de sistemas de transmisión de red inalámbrica.

De manera típica, estos sistemas no son actualizados tan fácilmente como los dispositivos celulares que comunican a través de ellos. Al aumentar las capacidades de los dispositivos móviles, puede ser difícil mantener un sistema de red inalámbrica antiguo, de manera que facilite la explotación completa de las nuevas capacidades de los dispositivos sin cables, perfeccionados.

Los sistemas de comunicación sin cables utilizan, en general, diferentes enfoques para generar recursos de transmisión en forma de canales. Estos sistemas pueden ser sistemas de multiplexado por división de código (CDM), sistemas de multiplexado por división de frecuencia (FDM), y sistemas de multiplexado por división de tiempo (TDM). Una variante utilizada de FDM es el multiplexado por división de frecuencia ortogonal (OFDM) que divide de manera efectiva la banda ancha del sistema global en múltiples subportadoras ortogonales. Estas subportadoras reciben también la denominación de tonos, bandejas, y canales de frecuencia. Cada subportadora puede ser modulada con datos. Con técnicas basadas en la división de tiempo, cada subportadora puede comprender una parte de segmentos de tiempo secuenciales o ranuras ("slots") de tiempo. Cada usuario puede estar dotado de una o varias ranuras de tiempo y combinaciones de subportadoras para transmitir y recibir información en un determinado periodo de emisión o trama. Los sistemas de salto pueden ser en general un sistema de salto de velocidad de símbolos o esquema de salto de bloque.

Las técnicas basadas en división de código transmiten, típicamente, datos sobre una serie de frecuencias, disponibles en cualquier momento dentro de un rango. En general, los datos son digitalizados y extendidos sobre el ancho de banda disponible, mientras que los múltiples usuarios pueden ser superpuestos sobre el canal, y los respectivos usuarios pueden recibir la asignación de un único código de secuencia. Los usuarios pueden transmitir en el mismo segmento del espectro de banda ancha, de manera que cada señal de usuario es extendida sobre la totalidad del ancho por su respectivo código 1 de extensión. Esta técnica puede proporcionar el concepto de compartir, en el que uno o varios usuarios puede transmitir y recibir simultáneamente. Esta acción de compartir se puede conseguir mediante la modulación digital del espectro extendido, en el que una corriente de bits de usuario es codificada y extendida sobre un canal muy ancho de forma seudoazar. El receptor está diseñado para reconocer el código de secuencia único asociado y deshacer la puesta al azar a efectos de recoger los bits para un usuario específico de manera coherente.

Una red de comunicación inalámbrica típica (por ejemplo, utilizando técnicas de división de frecuencia, tiempo, y/o código) incluye una o varias estaciones de base que proporcionan un área de cobertura y una o varias terminales móviles (por ejemplo, sin cables) que pueden transmitir y recibir datos dentro del área de cobertura. Una estación de base típica puede transmitir simultáneamente corrientes de datos para emitir ("broadcast"), emisión múltiple ("multicast"), y/o servicios ("unicast"), de manera que una corriente de datos es una corriente de datos que puede ser de interés para la recepción independiente de un terminal móvil. El terminal móvil, dentro del área de cobertura de dicha estación de base, puede estar interesado en recibir una, más de una, o la totalidad de corrientes de datos transmitidas desde la estación de base. De manera similar, un terminal móvil puede transmitir datos a la estación de base o a otro terminal móvil. En estos sistemas, la banda ancha y otros recursos del sistema son asignados utilizando un programador.

Las señales, formatos de señales, intercambio de señales, métodos, procesos, y técnicas que se dan a conocer en esta descripción proporcionan varias ventajas con respecto a los sistemas conocidos. Estos incluyen, por ejemplo, reducción de la carga de señalización, mejora de la producción del sistema, mayor flexibilidad de señalización, proceso con información reducida, ancho de banda de transmisión reducida, proceso reducido de bits, robustez incrementada, eficacia mejorada, y potencia de transmisión reducida.

40

45

50

El documento WO 2005/041515 A1 da a conocer técnicas para multiplexar múltiples corrientes de datos utilizando un sistema de multiplexado por división de frecuencia (FDM) en un sistema OFDM. Se forman M "entrelazamientos" separados con sub-bandas utilizables U. Cada entrelazamiento es un conjunto diferente de sub-bandas S, en el que las sub-bandas para cada entrelazamiento están entrelazadas con las sub-bandas para cada uno de los otros entrelazamientos. Se pueden definir ranuras M de tiempo ("slots") para cada periodo de símbolo, y se pueden asignar índices de ranura 1 a M. Los índices de ranura pueden ser mapeados para entrelazamientos, de manera tal que (1) se consigue diversidad de frecuencia para cada índice de ranura, y (2) los entrelazamientos utilizados para transmisión piloto tienen distancias variables a los entrelazamientos utilizados para cada índice de ranura, lo que mejora el rendimiento en la estimación de canales. Cada corriente de datos puede ser procesada como paquetes de datos de dimensiones fijas, y diferentes números de ranuras pueden ser utilizados para cada paquete de datos dependiendo del código y esquema de modulación utilizados para el paquete de datos.

#### **RESUMEN**

10

30

35

65

A continuación, se presenta un resumen simplificado de uno o varios aspectos, a efectos de proporcionar una comprensión básica de dichos aspectos. Este resumen no es una revisión extensa de todos los aspectos contemplados, y no está destinado a identificar elementos clave o críticos de todos los aspectos ni a delimitar el ámbito de cualquiera o de todos los aspectos. Su único objetivo consiste en presentar algunos conceptos de uno o varios aspectos de forma simplificada como preludio de la descripción más detallada, que se presenta más adelante.

De acuerdo con una realización, se da a conocer un método para generar una permutación de salto para salto de enlace en avance, tal como se define en la reivindicación 1.

De acuerdo con otra realización, se describe un soporte legible por ordenador que tiene instrucciones, tal como se indica en la reivindicación 2.

De acuerdo con otra realización, un aparato que puede funcionar en un sistema de comunicación inalámbrico es descrito tal como se define en la reivindicación 3.

Para conseguir los objetivos anteriores, y otros relacionados, el aspecto o aspectos de la invención comprenden las características que se describen a continuación de manera completa y, especialmente, reunidas en las reivindicaciones. La siguiente descripción y los dibujos adjuntos indican de manera detallada algunos aspectos ilustrativos de uno o varios aspectos. Estos aspectos de la invención son, no obstante, indicativos de algunas de las diferentes formas en las que los principios de varios aspectos pueden ser utilizados, y los aspectos descritos están destinados a incluir la totalidad de dichos aspectos y sus equivalentes.

# **BREVE DESCRIPCIÓN DE LOS DIBUJOS**

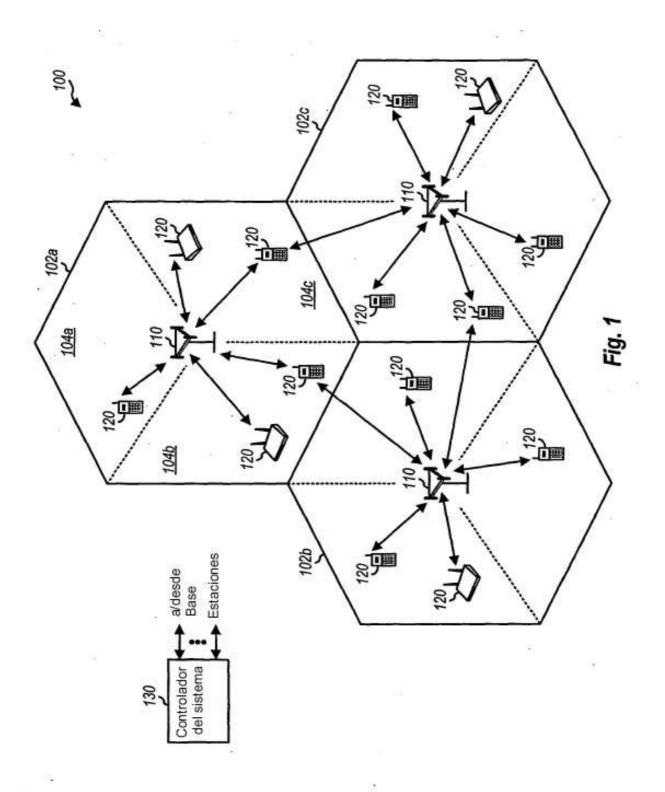

40 La figura 1 muestra aspectos de un sistema de comunicación inalámbrico con acceso múltiple,

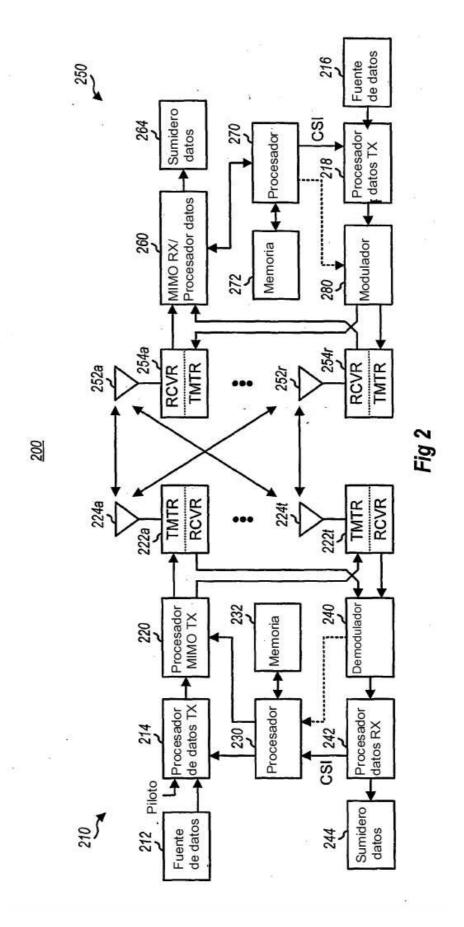

La figura 2 muestra aspectos de un transmisor y receptor en un sistema de comunicación inalámbrico de acceso múltiple,

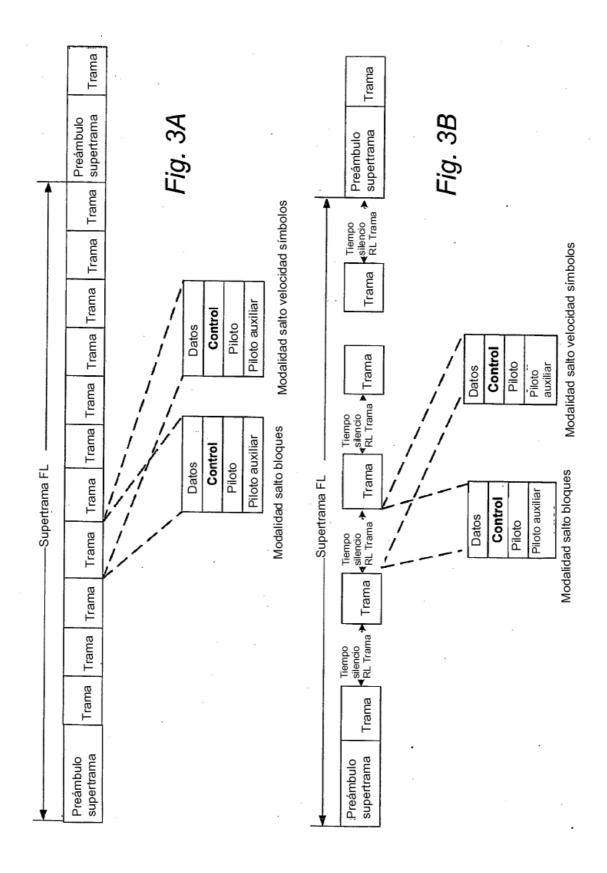

45 Las figuras 3A y 3B muestran aspectos de estructuras supertrama para un sistema de comunicación inalámbrico de acceso múltiple,

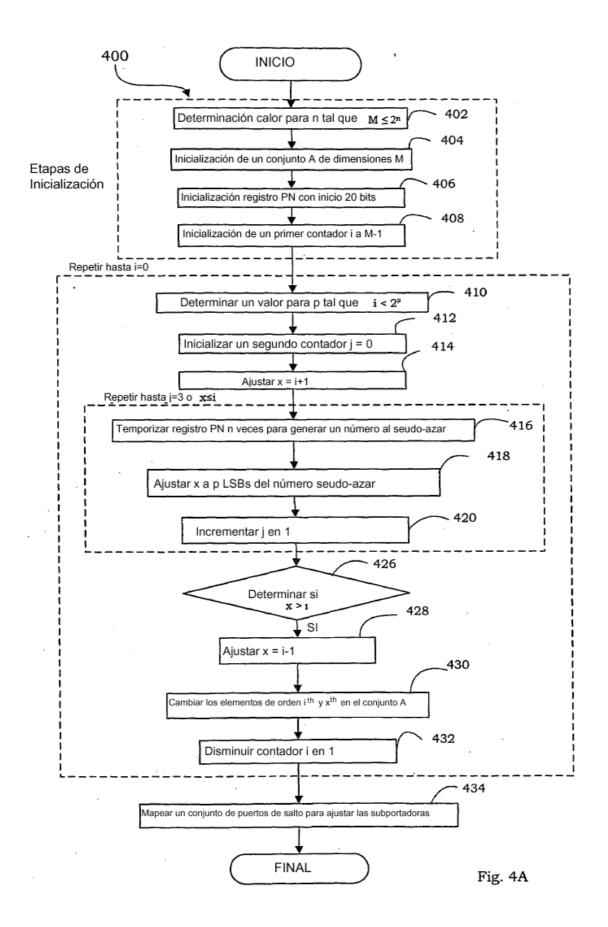

La figura 4A muestra un diagrama de flujo de un proceso utilizado por una red de acceso y,

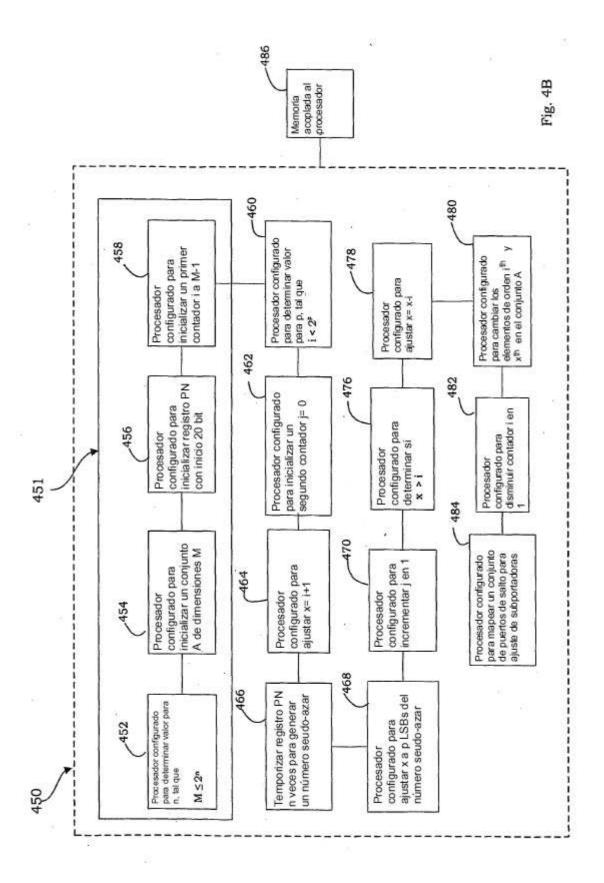

50 La figura 4B muestra uno o varios procesadores configurados para generar una permutación para salto de enlace en avance.

#### **DESCRIPCIÓN DETALLADA**

Varios aspectos se describirán a continuación con referencia a los dibujos, en los que los numerales de referencia iguales se utilizan para hacer referencia a elementos iguales en toda la descripción. En la siguiente descripción, a efectos explicativos, se indicarán numerosos detalles específicos para proporcionar una comprensión completa de uno o más aspectos. Puede ser evidente, no obstante, que dichos aspectos puedan ser practicados sin estos detalles específicos. En otros casos, se han mostrado estructuras y dispositivos bien conocidos en forma de diagrama de bloques para facilitar la descripción de uno o varios aspectos.

Haciendo referencia a la figura 1, se ha mostrado un sistema de comunicación inalámbrico con acceso múltiple según un aspecto de la invención. Un sistema de comunicación inalámbrico con acceso múltiple 100 comprende celdas múltiples, por ejemplo, las células 102, 104, y 106. En el aspecto de la figura 1, cada una de las células 102, 104, y 106 puede incluir un punto de acceso 150 que incluye múltiples sectores. Los múltiples sectores están

formados por grupos de antenas, cada una de las cuales es responsable de comunicación con terminales de acceso en una parte de la célula.

En la célula 102, cada uno de los grupos de antenas 112, 114 y 116 corresponde a un sector distinto. En la célula 104, los grupos de antenas 118, 120 y 122 corresponden cada uno de ellos a un sector distinto. En la célula 106, los grupos de antenas 124, 126 y 128 corresponden cada una de ellas a un sector diferente.

Cada una de las células incluye varios terminales de acceso que están en comunicación con uno o varios sectores de un punto de acceso. Por ejemplo, los terminales de acceso 130 y 132 que está en comunicación con la base 142, los terminales de acceso 134 y 136 están en comunicación con el punto de acceso 144 y los terminales de acceso 138 y 140 están en comunicación con el punto de acceso 146.

10

15

20

25

30

35

40

45

El controlador 130 está acoplado a cada una de las células 102, 104 y 106. El controlador 130 puede contener una o varias conexiones a múltiples redes, por ejemplo, Internet, otras redes basadas en paquetes o redes de voz conmutadas a circuito que proporcionan información hacia y desde los terminales de acceso en comunicación con las células del sistema de comunicación inalámbrico de acceso múltiple 100. El controlador 130 incluye un programador o está acoplado con el mismo, cuyo programador programa la transmisión desde y hacia los terminales de acceso. En otros aspectos, el programador puede residir en cada una de las células individuales, cada sector de una célula o una combinación de las mismas.

Tal como se utiliza en esta descripción, un punto de acceso puede ser una estación fija utilizada para comunicar con los terminales y también se puede referir a la funcionalidad de una estación base o incluir una parte o la totalidad de la misma, a un Nodo B o alguna otra terminología. Un terminal de acceso puede ser destinado también, incluyendo también una parte o la totalidad de la funcionalidad, un equipo de usuario (UE), un dispositivo de comunicación inalámbrica, un terminal, una estación móvil o alguna otra terminología.

Se debe observar que si bien la figura 1 muestra sectores físicos, es decir, que tienen diferentes grupos de antenas para diferentes sectores, se pueden utilizar otros sistemas. Por ejemplo, utilizando "haces" fijos, múltiples cada uno de los cuales cubre diferentes áreas de la célula en el espacio de frecuencia se puede utilizar en lugar de sectores físicos o en combinación con los mismos. Este sistema está mostrado y dado a conocer en la solicitud de patente pendiente con la actual US número de serie 11/260.895, titulada "Adaptive Sectorization in Cellular System" (Sectorización Adaptativa en un Sistema Celular).

Haciendo referencia a la figura 2, se ha mostrado un diagrama de bloques de un aspecto de un sistema transmisor 210 y un sistema receptor 250 en un sistema MIMO 200. En el sistema transmisor 210, se facilitan datos de tráfico para una serie de flujos de datos desde una fuente de datos 212 al procesador de datos de transmisión (TX) 214. En un aspecto, cada corriente de datos es transmitida sobre una antena de transmisión correspondiente. El procesador de datos TX 214 formatea, codifica e interpone los datos de tráfico para cada corriente de datos basándose en un esquema de codificación específico seleccionado para dicha corriente de datos para proporcionar datos codificados.

Los datos codificados para cada corriente de datos se puede multiplexar con datos piloto utilizado OFDM u otra técnica de ortogonalización o no ortogonalización. Los datos piloto son típicamente un modelo de datos conocidos que es procesado de manera conocida y que se puede utilizar en el sistema receptor para estimar la respuesta del canal. Los datos piloto multiplexados y codificados para cada flujo de datos son modulados (es decir, símbolo mapeado) basándose en uno o varios esquemas particulares de modulación (por ejemplo, BPSK, QSPK, M-PSK o M-QAM) seleccionados para dicho flujo de datos para proporcionar símbolos de modulación. La velocidad de datos, codificación y modulación para cada flujo de datos se pueden determinar por instrucciones llevadas a cabo o proporcionadas por el procesador 230.

Los símbolos de modulación para todas las corrientes de datos son proporcionadas a continuación a un procesador TX 220, que puede procesar además símbolos de modulación (por ejemplo, OFDM). El procesador TX 220 proporciona a continuación corrientes de símbolos de modulación N<sub>T</sub> a transmisores N<sub>T</sub> (TMTR) 222a a 222t. Cada transmisor 222 recibe y procesa una corriente de símbolos respectiva para proporcionar una o varias señales analógicas y otras condiciones (por ejemplo, amplifica, filtra y convierte de modo creciente) las señales analógicas para proporcionar una señal modulada adecuada para la transmisión por el canal MIMO. Las señales moduladas N<sub>T</sub> procedentes de los transmisores 222a a 222t son transmitidas a continuación desde antenas N<sub>T</sub> 224a a 224t, respectivamente.

En el sistema receptor 250, las señales moduladas transmitidas son recibidas por N<sub>R</sub> antenas 252a hasta 252r y la señal recibida de cada antena 252 es facilitada a un receptor respectivo (RCVR) 254. Cada receptor 254 acondiciona (por ejemplo filtra, amplifica y convierte de forma descendente) una señal respectiva recibida, digitaliza la señal acondicionada para proporcionar muestras y a continuación procesa las muestras para proporcionar una corriente de símbolos correspondiente "recibida".

65 Un procesador 260 de datos RX recibe a continuación y procesa las N<sub>R</sub> corrientes de símbolos recibidas desde N<sub>R</sub>

receptores 254 basándose en una técnica de proceso receptor específico para proporcionar  $N_T$  corrientes de símbolos "detectadas". El procesador 260 de datos RX se describe de manera más detallada más adelante. Cada corriente de símbolos detectada incluye símbolos que son estimaciones de los símbolos de modulación transmitidos para la corriente de datos correspondiente. El procesador 260 de datos RX que demodula, desintercala y decodifica cada corriente de símbolos detectados para recuperar los datos de tráfico para la corriente de datos. El proceso por el procesador de datos RX 218 es complementario con respecto al llevado a cabo por el procesador TX 220 y el procesador de datos TX 214 en el sistema transmisor 210.

El procesador 260 de datos RX puede estar limitado en cuanto a número de subportadoras que puede demodular simultáneamente, por ejemplo, 512 subportadoras de 5 MHz y este receptor debe ser programado en una portadora única. Esta limitación puede ser una función de su rango FFT, por ejemplo, velocidades de muestra en las que el procesador 260 puede funcionar, la memoria disponible para FFT u otras funciones disponibles para demodulación. Además, cuanto mayor es el número de subportadoras utilizadas, mayor es la degradación del terminal de acceso.

La estimación de respuesta del canal generada por el procesador 260 RX se puede utilizar para llevar a cabo proceso de espacio, espacio/tiempo en el receptor, ajustar niveles de potencia, cambiar velocidades o esquemas de modulación u otras acciones. El procesador RX 260 puede estimar además las proporciones de señal a señal y de interferencia (SNR) de las corrientes de símbolos detectadas y posiblemente otras características del canal y proporciona estas cantidades a un procesador 270. El procesador de datos RX 260 o procesador 270 puede deducir además una estimación del SNR "operativo" para el sistema.

A continuación, el procesador 270 proporciona información de estado de canal (CSI) que puede comprender varios tipos de información respecto al enlace de comunicación y/o la corriente de datos recibidos. Por ejemplo, el CSI puede comprender solamente el SNR operativo. En otros aspectos, el CSI puede comprender un indicador de calidad del canal (CQI) que puede ser un valor numérico indicativo de uno o varios estados del canal. El CSI es procesado a continuación por un procesador de datos TX 278 modulado por un modulador 280, acondicionado por transmisores 254a a 254r y transmitido nuevamente al sistema transmisor 210.

En el sistema transmisor 210, las señales moduladas del sistema receptor 250 son recibidas por antenas 224, acondicionadas por receptores 222, demoduladas por un demodulador 240 y procesadas por un procesador de datos RX 242 para recuperar el CSI indicado por el sistema receptor. El CSI indicado es facilitado a continuación al procesador 230 y utilizado para (1) determinar las velocidades de datos y esquemas de codificación y demodulación a utilizar para las corrientes de datos y (2) generar diferentes controles para el procesador de datos TX 214 y el procesador TX 220. De manera alternativa, el CSI puede ser utilizado por el procesador 270 para determinar esquemas de modulación y/o velocidades de decodificación para transmisión junto con otras informaciones. Esto puede ser facilitado, a continuación, al transmisor que utiliza esta información que se puede cuantificar para proporcionar transmisiones posteriores al receptor.

Los procesadores 230 y 270 dirigen el funcionamiento en los sistemas transmisor y receptor, respectivamente. Las memorias 232 y 272 proporcionan almacenamiento para los códigos de programa y datos utilizados por los procesadores 230 y 270, respectivamente.

En el receptor, varias técnicas de proceso pueden ser utilizadas para procesar las  $N_R$  señales recibidas para detectar las  $N_T$  corrientes de símbolos transmitidos. Estas técnicas de proceso del receptor pueden ser agrupadas en dos categorías principales (i) técnicas de proceso del receptor espaciales y de espacio-tiempo (a las que también se hace referencia como técnicas de ecualización; y (iii) "sucesiva cancelación de anulación/ecualización e interferencia" según una técnica de proceso del receptor (a la que se hace referencia también como "cancelación de interferencias sucesivas o técnica de proceso de receptor de "cancelación sucesiva").

Si bien la figura 2 explica un sistema MIMO, el mismo sistema puede ser aplicado a un sistema de multientradas y salida única en el que múltiples antenas de transmisión, por ejemplo las de una estación de base, transmiten una o varias corrientes de símbolos a un único dispositivo de antena, por ejemplo, una estación móvil. Asimismo se puede utilizar un sistema de antena de salida única a entrada única de la misma manera que se ha descrito con respecto a la figura 2.

Las técnicas de trasmisión descritas en esta descripción se pueden implementar de varias maneras. Por ejemplo, estas técnicas pueden ser implementadas en hardware, firmware, software o una combinación de los mismos. Para una implementación de hardware, las unidades de proceso de un transmisor pueden ser implementadas dentro de uno o varios circuitos integrados específicos de aplicación (ASIC), procesadores de señales digitales (DSP), dispositivos procesadores de señales digitales (DSPD), dispositivos lógicos programables (PLD), dispositivos de puerta programables en campo (FPGA), procesadores, controladores, microcontroladores, microprocesadores, dispositivos electrónicos, otras unidades electrónicas diseñadas para llevar a cabo las funciones descritas o una combinación de los mismos. Las unidades de proceso en un receptor pueden ser implementadas también dentro de uno o varios procesadores ASIC, DSP y así sucesivamente.

25

30

35

40

Para la implementación de un software, las técnicas de transmisión pueden ser implementadas por módulos (por ejemplo, procedimientos, funciones y otros) que llevan a cabo las funciones que se describen. Los códigos de software pueden ser alimentados en una memoria, (por ejemplo, memoria 230, 272x o 272y en la figura 2) y ejecutados por un procesador (por ejemplo, procesador 232, 270x o 270y). La memoria se puede complementar dentro del procesador o externamente al mismo.

Se debe observar que el concepto de canales se refiere en este caso a tipos de transmisión o de información que se puede transmitir por el punto de acceso o terminal de acceso. No requiere ni utiliza bloques fijos o predeterminados o subportadoras, periodos de tiempo u otros recursos dedicados a dichas transmisiones.

10

15

20

25

30

35

40

Haciendo referencia a las figuras 3A y 3B, se han mostrado aspectos de estructuras de supertrama para un sistema de comunicación inalámbrico de acceso múltiple. La figura 3A muestra aspectos de una estructura supertrama para un sistema de comunicación inalámbrico de acceso múltiple con división duplexada de frecuencia (FDD), mientras que la figura 3B muestra aspectos de estructuras supertrama para un sistema de comunicación sin cables de acceso múltiple duplexado por división de tiempo (TDD). El preámbulo de la supertrama puede ser transmitido separadamente para cada portadora o puede abarcar la totalidad de las portadoras del sector.

Tanto en las figura 3A como 3B, la transmisión de enlace en avance está dividida en unidades de supertramas. Una supertrama puede consistir de un preámbulo de supertrama seguido por series de tramas. En un sistema FDD, la transmisión por enlace inverso y por enlace directo o de avance pueden ocupar diferentes anchuras de banda de frecuencia, de manera que las transmisiones en los enlaces no se solapan o no lo hacen en su mayor parte en cualesquiera subportadoras de frecuencia. En un sistema TDD, N tramas de enlace en avance y M tramas de enlace inversas definen el número de tramas de enlace en avance secuenciales y de enlace inverso que pueden ser transmitidas continuamente antes de permitir la transmisión del tipo opuesto de trama. Se debe observar que el número de N y M puede variar dentro de una supertrama o entre supertramas.

En ambos sistemas FDD y TDD, cada supertrama puede comprender un preámbulo de supertrama. En ciertos aspectos, el preámbulo de supertrama comprende un canal piloto que incluye pilotos que pueden ser utilizados para la estimación de un canal por terminales de acceso, un terminal de emisión que comprende información de configuración que el terminal de acceso puede utilizar para demodular la información contenida en la trama de enlace en avance. Otra información de captación, tal como temporización y otras informaciones suficientes para que un terminal de acceso comunique en una de las portadoras y control de potencia básico o información de desplazamiento pueden ser incluidas también en el preámbulo de la supertrama. En otros casos, solamente algunas de las informaciones anteriores y/o otras informaciones pueden ser incluidas en este preámbulo de la supertrama.

Tal como se ha mostrado en las figuras 3A y 3B, el preámbulo de la supertrama está seguido de una secuencia de tramas. Cada trama puede consistir del mismo o distinto número de símbolos OFDM que puede constituir un número de subportadoras que puede ser simultáneamente utilizado para transmisión durante un periodo definido. Además, cada trama puede funcionar de acuerdo con una modalidad de salto de velocidad de símbolos, en la que uno o varios símbolos OFDM no contiguos están asignados a un usuario en un enlace en avance o en un enlace inverso o en una modalidad de salto de bloques, en la que los usuarios efectúan el salto dentro de un bloque de símbolos OFDM. Los bloques reales o símbolos OFDM pueden saltar o no entre las tramas.

Un terminal de acceso y una red de acceso comunican entre sí utilizando un enlace de comunicación. Basándose 45 en la temporización predeterminada, condiciones del sistema, u otros criterios de decisión, el terminal de acceso y la red de acceso se comunican entre sí. El enlace de comunicación puede ser implementado utilizando protocolos/normas de comunicación, tales como World Interoperability de Micro wave Access (WiMAX), (interoperabilidad mundial para acceso por microondas), protocolos de infrarrojos tales como Infrared Data 50 Association (IrDA), protocolos/tecnologías inalámbricos de alcance reducido, tecnología Bluetooth®, protocolo Zig-Bee®, protocolo de banda ultra ancha (UWB), frecuencia de radio doméstica (HomeRF), protocolo de acceso inalámbrico compartido (SWAP), tecnología de banda ancha tal como alianza de compatibilidad Ethernet inalámbrica (WECA), alianza de fidelidad inalámbrica (Wi-Fi Alliance), tecnología de red 802.11, tecnología de red telefónica conmutada pública, tecnología de red de comunicaciones heterogéneas públicas tales como Internet, 55 red de comunicaciones inalámbricas privadas, red de radio móvil terrestre, acceso múltiple por división de código (CDMA), acceso múltiple por división de código en banda ancha (WCDMA), sistema de telecomunicaciones móviles universal (UMTS), servicio telefónico móvil avanzado (AMPS), acceso múltiple por división de tiempo (TDMA), acceso múltiple por división de frecuencia (FDMA), múltiple de división de frecuencia ortogonal (OFDM), acceso múltiple de división de frecuencia ortogonal OFDMA), múltiple de división de frecuencia ortogonal FLASH (OFDM-FLASH), sistema global para comunicaciones móviles (GSM), tecnología de transmisión por radio de 60 portadora única (1X), tecnología de evolución de datos solamente (EV-DO), servicio de radio general por paquetes (GPRS), entorno GSM de datos amplificados (EDGE), acceso por paquetes de datos de enlace descendente de alta velocidad (HSPDA), sistemas por satélite analógicos y digitales, y cualesquiera otras tecnologías/protocolos que se puedan utilizar, como mínimo, en uno de una red de comunicaciones inalámbrica y una red de 65 comunicaciones de datos.

La permutación de salto es utilizada para mapear el conjunto de puertos de salto a un conjunto de subportadoras. Todas las permutaciones utilizadas para salto de enlace en avance (FL) se pueden generar utilizando un algoritmo de generación de permutación común, que es el que se describe más adelante. El algoritmo de permutación puede adoptar una base o simiente de 20 bit y una dimensión de permutación M al dar entrada y emitir a una permutación del conjunto {0,1,...,M-1}. El algoritmo utiliza un registro de desplazamiento de realimentación lineal para generar números seudoazar, que a su vez son utilizados para generar permutaciones seudoazar.

El algoritmo de generación de permutación común puede generar una permutación M. las etapas de inicialización del algoritmo incluyen asumir un entero n, de manera que  $M \le 2^n$ . A continuación, un conjunto A de dimensión M es inicializado con los números 0, 1, 2....M-1. Un registro PN es inicializado además con un inicio o simiente de 20 bits y un contador i se inicializa a M-1. El algoritmo comprende además etapas de repetición para encontrar un p más reducido, tal que i  $< 2^p$ , inicializando un contador j a 0, disponiendo x a i+1, temporizando el registro PN n veces para generar un número seudoazar, ajustando a x a p LSBs de dicho número, incrementar j por 1, repetir las etapas de temporización del registro PN e incrementar el valor de j hasta j= 3 o x  $\le$  i, disponiendo x= x-i si x>i, cambiando los elementos de orden i<sup>th</sup> y los elementos de orden x<sup>th</sup> en el conjunto A y disminuyendo el contador i en 1 hasta i= 0. El conjunto resultante A es la permutación de salida P.

10

15

30

35

40

45

50

55

60

65

Se define la permutación de salto FL para las modalidades multiportadora On y multiportadora Off (MultiCarrierOn and MultiCarrierOff. En la modalidad MultiCarrierOff, la permutación de salto depende de varios parámetros que se obtienen del Protocolo de Mensaje Superior (Overhead Message Protocol). En la modalidad MulticarrierOn, la permutación de salto en la portadora c, en la que c se encuentra en {0, 1,...., N<sub>CARRIERS</sub>-1} depende de varios parámetros obtenidos a partir del Protocolo de Mensaje Superior para la portadora c. Estos parámetros pueden variar de una portadora a otra. Un parámetro que varía de una portadora a otra puede ser indexado por el índice de portadora c.

La figura 4A muestra un diagrama de flujo del proceso 400, de acuerdo con una realización. En 402, se determina un valor para el entero n, tal que M $\leq$ 2". En 404, se inicializa un conjunto A de tamaño M. En 406, se inicializa un registro de seudo-ruido (PN) con un inicio o simiente de 20 bitss. En 408, un primer contador i es inicializado a M-1. En 410, se determina un valor para un entero p de manera tal que i<2 $^p$ . En 412, se inicializa un segundo contador j a '0'. En 414, se ajusta un entero x a valor j+1. En 416, el registro PN es temporizado n veces para generar un número seudoazar. En 418, x es ajustado a p LSBs del número seudoazar. En 420, el valor de j es incrementado en 1. El proceso en 416, 418, y 420 es repetido hasta que no se determina que j=3, o x $\leq$  i. Además, en 426 se determina si x>i. En 428, el valor de x se dispone en x-i, si x es mayor de i. En 430, los elementos de orden i<sup>th</sup> y x<sup>th</sup> del conjunto A son cambiados. En 432, el contador i es disminuido en 1. El proceso en 410, 412, 414, 416, 418, 420, 426, 428, 430 y 432 es repetido hasta que no se determina i = '0'. En 434, un conjunto de puertos de salto es mapeado en un conjunto de subportadoras basado en la permutación de salto generada.

La figura 4B muestra un procesador 450 para generar una permutación para salto de enlace en avance. El procesador al que se hace referencia puede ser un dispositivo electrónico y puede comprende uno o varios procesadores configurados para generar la permutación de acuerdo con la realización. Un procesador 451 es configurado para inicializar constantes de permutación. El procesador 451 puede comprender un procesador 452 para determinar un valor para un entero n, tal que M≤ 2<sup>n</sup>, un procesador 454 para inicializar un conjunto A de dimensiones M, un procesador 456 para inicializar un registro de seudo-ruido PN con un inicio o simiente de 20 bits y un procesador 458 para inicializar un primer contador i a M-1. El procesador 460 se ha configurado para determinar un valor para el entero p, tal que i < 2º. El procesador 462 está configurado para inicializar un segundo contador j a '0'. El procesador 464 está configurado para ajustar x a un valor i+1. El procesador 466 está configurado para temporizar el registro PN n veces para generar el número seudoazar. El procesador 468 está configurado para ajustar x a p LSBs del número seudoazar. El procesador 470 está configurado para incrementar el valor de j en 1. Un procesador está configurado para repetir la temporización del registro PN n veces para generar el número seudoazar, ajustando x al p LSBs del número seudoazar, e incrementar j en 1 hasta que no se determine que j=3 o x ≤ i. Además, el procesador 476 está configurado para determinar si x > i. El procesador 478 está configurado para ajustar el valor de x a x-i, si x es superior a i. El procesador 480 está configurado para cambiar el elemento de orden i y de orden x en el conjunto A. El procesador 482 está configurado para disminuir el contador i en 1. Además, un procesador está configurado para repetir la determinación del valor para p, de manera tal que  $i<2^p$  inicializando el segundo contador j=0, ajustando x a i+1, temporizando el registro PN n veces para generar el número seudoazar, ajustando x al p LSBs del número seudoazar, incrementando j en 1, determinando si x>i, disponiendo x a x-i, si x es superior a i, cambiando los elementos de orden i<sup>th</sup> y x<sup>th</sup> en el conjunto A, y disminuyendo el contado i en 1, hasta que no se determina que i = '0'. Un procesador 484 está configurado para mapear un conjunto de puertos de salto a un conjunto de subportadoras basándose en la permutación de salto generada. La funcionalidad de los procesadores discretos 452 a 484 mostrado en la figura, se puede combinar en un procesador único 450. Una memoria 486 está acoplada también al procesador 450.

En una realización, se describe un aparato que comprende medios para inicializar las constantes de permutación. Los medios de inicialización pueden comprender además medios para determinar un valor para un entero n, tal que

M≤ 2<sup>n</sup>, un medio para inicializar un conjunto A de tamaño M, un medio para inicializar un registro de seudo-ruido (PN) con un inicio o simiente de 20 bits, y un medio para inicializar un primer contador i a M-1. El aparato comprende además, un medio para determinar un valor para el entero p, tal que i< 2<sup>p</sup> medios para inicializar un segundo contador j a '0', medios para ajustar x a un valor i+1, medios para temporizar el registro PN n veces para generar el número seudoazar, medios para ajustar x a p LSBs del número seudoazar, y medios para incrementar el valor de j en 1. Se dispone un medio para repetir la temporización del registro PN n veces para generar un número seudoazar, ajustando x al p LSBs del número seudoazar, e incrementando j en 1 hasta que no se determina que j=3 o x≤ i. Además, se prevé un medio para determinar si x> i y medios para ajustar el valor de x a x-i, si x es superior a i. El aparto comprende además, un medio para cambiar los elementos de orden i<sup>th</sup> y de orden x<sup>th</sup> en el conjunto A, un medio para disminuir el contador i en 1, medios para repetir la determinación del valor para p, tal que i< 2<sup>p</sup> inicializando el segundo contador j=0, ajustando x a i+1, temporizando el registro PN n veces para generar el número seudoazar, ajustando al p LSBs del número seudoazar, e incrementando j en 1, determinando si x>i disponiendo x a x-i, si x es superior a i, cambiando los elementos de orden i<sup>th</sup> y x<sup>th</sup> en el conjunto A, y disminuyendo el contador i en 1, hasta que no se determinar que j='0'. También se dispone un medio para mapear un conjunto de puertos de salto a un conjunto de subportadoras basado en la permutación de salto generada. Los medios descritos pueden comprender uno o varios procesadores.

Además, se pueden implementar realizaciones por hardware, software, firmware, middleware, microcódigo o cualquier combinación de los mismos. Cuando se implementa en software, firmware, middleware, o microcódigo, el código de programa o segmentos de código para llevar a cabo las tareas necesarias se pueden almacenar en un soporte legible a máquina, tal como un almacenamiento o almacenamientos separados que no se han mostrado. Un procesador puede llevar a cabo las tareas necesarias. Un segmento de código puede representar un procedimiento, una función, un subprograma, un programa, una rutina, una subrutina, un módulo, un paquete de software, una clase, o cualquier combinación de instrucciones, estructura de datos, o afirmaciones de programa. Un segmento de código puede ser acoplado a otro segmento de código o a un circuito de hardware pasando y/o recibiendo información, datos, argumentos, parámetros, o contenidos de memoria, información, argumentos, parámetros, datos etc. se pueden pasar, enviar o transmitir mediante medios adecuados incluyendo memorias compartidas, paso de mensajes, paso de fichas, transmisión de red, etc.

### **REIVINDICACIONES**

- 1. Método para la generación de una permutación de salto de dimensión M para salto de enlace en avance en un sistema de comunicaciones inalámbrico, caracterizado por las siguientes etapas:

- a) inicializar constantes de permutación, comprendiendo:

- b) determinar (402) un entero n, tal que M es menor o igual a 2<sup>n</sup>;

- c) inicializar (404) un conjunto A de dimensiones M;

- d) inicializar (406) un registro de seudo-ruido PN con un inicio o simiente y;

- e) inicializar (408) un primer contador i a M-1; 10

- f) repetir las etapas siguientes q) a q), hasta que el primer contador i es igual a 0, comprendiendo las etapas:

- g) determinación (410) del valor para un entero p, de manera tal que i es menor de 2<sup>p</sup>;

- h) inicializar (412) un segundo contador i a '0':

- i) ajustar (414) un entero x a i+1, de manera que x es un índice de elementos del conjunto A;

- j) repetir las siguientes etapas k) hasta m) hasta que el segundo contador j es igual a 3 o el entero x es menor o igual a i, comprendiendo las etapas:

- k) temporización (416) del registro PN n veces para generar un número seudoazar;

- I) ajustar (418) x a p Bits Menos Significativos del número seudoazar;

- 20 m) incrementar (420) j en 1;

5

15

30

35

50

- n) determinar (426) si x es superior a i;

- o) ajustar (428) x a x-1 si x es superior a i; p) cambiar (430) los elementos de orden i<sup>th</sup> y x<sup>th</sup> en el conjunto A y;

- g) disminuir (432) el contador i en 1 y;

- 25 r) mapear (434) un conjunto de puertos de salto a un conjunto de subportadoras basándose en el conjunto A, la permutación de salto generada.

- 2. Soporte legible por ordenador que incluye instrucciones para generar una permutación de tamaño M almacenada en el mismo, caracterizado por:

- un primer conjunto de instrucciones para inicializar constantes de permutación, comprendiendo el primer conjunto de instrucciones:

- un primer subconjunto de instrucciones para determinar un entero n, tal que M es menor o igual a 2<sup>n</sup>; un segundo subconjunto de instrucciones para inicializar un conjunto A de dimensiones M;

- un tercer subconjunto de instrucciones para inicializar un registro de seudo-ruido PN con un elemento inicial o simiente; y

- un cuarto subconjunto de instrucciones para inicializar un primer contador i a M-1;

- 40 un segundo conjunto de instrucciones para repetir los subconjuntos guinto a duodécimo de instrucciones, hasta que el contador i es igual a 0, comprendiendo el segundo conjunto de instrucciones:

- un quinto subconjunto de instrucciones para determinar un valor para p, tal que i es menor que 2<sup>p</sup>; un sexto subconjunto de instrucciones para inicializar un segundo contador j a '0';

- un séptimo subconjunto de instrucciones para ajustar x a i+1, en el que x es un índice de elementos del 45 conjunto A;

- un octavo subconjunto de instrucciones para repetir los subconjuntos primero a tercero de instrucciones, hasta que el segundo contador j es igual a 3 o el entero x es menor o igual a i, comprendiendo el octavo subconiunto de instrucciones:

- un primer subconjunto de instrucciones para temporizar el registro PN n veces para generar un número seudoazar:

- un segundo subconjunto de instrucciones para ajustar x a p Bits Menos Significativos LSB del número seudoazar;

- 55 un tercer subconiunto de instrucciones para aumentar i en 1:

- un noveno subconjunto de instrucciones para determinar si x es superior a i;

- un décimo subconjunto de instrucciones para determinar x igual a x-i, si x es superior a i;

- un undécimo conjunto de instrucciones para cambiar los elementos de orden i<sup>th</sup> y x<sup>th</sup> en el conjunto A;

- un duodécimo subconjunto de instrucciones para disminuir el contador i en 1 y; 60

un tercer conjunto de instrucciones para mapear un conjunto de puertos de salto a un conjunto de subportadoras basado en el conjunto A, la permutación de salto generada.

3. Aparato accionable en un sistema de comunicaciones inalámbricas para generar una permutación de tamaño M, caracterizado porque:

medios (452, 454, 456, 548) para inicializar constantes de permutación, comprendiendo las constantes de permutación:

un entero n, tal que M es menor o igual que 2<sup>n</sup>; un conjunto A de dimensiones M; un registro seudo-ruido (PN) con un elemento inicial o simiente y; un primer contador i a M-1;

medios (460, 462, 464, 468, 470, 476, 478, 480,482) para repetir las siguientes etapas a) hasta k), hasta que el primer contado i es igual a 0, comprendiendo las etapas:

- a) determinar un valor para p, tal que i es menor de 2°;

- b) inicializar un segundo contador j a 0;

- c) disponer el entero x a i+1, en el que x es un índice de elementos del conjunto A:

- d) repetir las siguientes etapas e) a g), hasta que el segundo contador j es igual a 3 o que el entero x es menor o igual a i, comprendiendo dichas etapas:

- e) temporización del registro PN n veces para generar un número seudoazar;

- f) ajustar x a p Bits Menos Significativos LSB del número seudoazar;

- g) incrementar j en 1;

- h) determinar si x es superior a i;

- i) disponer x igual a x-i, si x es superior a i;

- 25 j) cambiar los elementos de orden i<sup>th</sup> y x<sup>th</sup> en el conjunto A;

- k) disminuir el contador i en 1 y;

medios (484) para mapear un conjunto de puertos de salto a un conjunto de subportadoras basado en el conjunto A, la permutación de salto generada.

30

5

10