11 Número de publicación: 2 370 828

51 Int. Cl.: H03K 19/096

(2006.01)

| 12                        | TRADUCCIÓN DE PATENTE EUROPEA                                                                                                                                                                                                         | T3 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                           | <ul> <li>96 Número de solicitud europea: 05257036 .3</li> <li>96 Fecha de presentación: 15.11.2005</li> <li>97 Número de publicación de la solicitud: 1732227</li> <li>97 Fecha de publicación de la solicitud: 13.12.2006</li> </ul> |    |

| (54) Título: <b>CIR</b> ( | CUITO DE ENGANCHE DE SALIDA DOMINÓ N.                                                                                                                                                                                                 |    |

(30) Prioridad: 14.10.2005 US 251517 27.12.2004 US 23145

(73) Titular/es: VIA TECHNOLOGIES, INC.

8F, NO.533, CHUNG-CHENG RD, HSIN-TIEN TAIPEI 231, TAIWAN, TW

- (45) Fecha de publicación de la mención BOPI: 23.12.2011

- (72) Inventor/es:

Lundberg, James R. y Bertram, Raymond A.

- (45) Fecha de la publicación del folleto de la patente: 23.12.2011

- (74) Agente: de Elzaburu Márquez, Alberto

ES 2 370 828 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

Circuito de enganche de salida dominó N.

#### CAMPO DEL INVENTO

5

10

25

30

35

40

45

El presente invento se refiere a funciones dinámicas de lógica y de registro, y más particularmente a un circuito de enganche de salida dominó que enfoca el problema de retener las salidas de circuitos de lógica compleja cuando la velocidad y el tamaño son factores importantes.

#### DESCRIPCIÓN DE LA TÉCNICA RELACIONADA

Los circuitos integrados usan un número notable de registros, particularmente los que tienen una arquitectura segmentada síncrona. El registro lógico es empleado para retener las salidas de dispositivos y circuitos durante un periodo de tiempo de manera que estas salidas puedan ser recibidas por otros dispositivos y circuitos. En un sistema temporizado, tal como un microprocesador segmentado, los registros son utilizados para enganchar y retener las salidas de una etapa segmentada dada durante un periodo de un ciclo de reloj de manera que los circuitos de entrada en una etapa subsiguiente puedan recibir las salidas durante ese período mientras la etapa segmentada dada está generando al mismo tiempo nuevas salidas.

En el pasado, ha sido la práctica común preceder y hacer seguir circuitos de evaluación lógica complejos, tales como multiplexadores de múltiples entradas (multiplexadores), codificadores multibits, etc., con registros para retener las entradas a los circuitos de evaluación y las salidas desde los mismos. Generalmente, estos registros tienen requisitos de configuración y tiempo de retención asociados, los cuales restringen los circuitos de evaluación en la etapa precedente. Además, los registros tienen características de tiempo de datos para salida correspondientes, que restringen los circuitos de evaluación en la etapa subsiguiente. La "velocidad" de un registro es juzgada típicamente en términos de su tiempo de datos para salida, es decir, la suma de su tiempo de configuración y tiempo de reloj para salida.

Preceder y seguir un circuito de evaluación lógica con circuitos de registro tradicionales introduce retrasos en un sistema segmentado cuyo efecto acumulativo da como resultado velocidades de funcionamiento significativamente más lentas. Más específicamente, una fuente notable de estos retrasos son los requisitos de tiempo de datos para salida que deben ser satisfechos por circuitos de evaluación lógica con el fin de asegurar salidas registradas estables. Se desea reducir estos retrasos para proporcionar tiempo adicional en cada etapa y aumentar por ello la velocidad total del sistema segmentado.

Una descripción anterior y relacionada, titulada "Registro Dominó No inversor" con número de expediente CNTR.2200 está dirigida a los problemas antes descritos. En la exposición anterior, se ha descrito un registro dominó no inversor que combinaba funciones de evaluación lógica con sus registros correspondientes para conseguir un tiempo de reloj para salida más rápido que las aproximaciones convencionales sin comprometer la estabilidad de su salida. Las transiciones de la señal de registro dominó no inversor expuestas en él fueron mostradas como muy rápidas en respuesta a transiciones de la señal de reloj en contraste con respuestas de transición más lentas de registros dominó de inversión convencional. El registro dominó no inversor anterior, sin embargo, no fue particularmente flexible con respecto a la lógica de evaluación, que tuvo que ser proporcionada como lógica de canal N. También, el registro dominó no inversor anterior podría experimentar potencialmente efectos de fuga cuando es realizado en un proceso de fuga elevada o de ruido elevado, tal como, por ejemplo, aislador sobre silicio (SOI) de 90 nanómetros (nm).

Consiguientemente, se desea proporcionar registros dominó N y dominó P mejorados con trayectos acelerados que proporcionan todos los beneficios de los registros dominó no inversor anteriores, y que son además flexibles con respecto a la etapa dominó, y que son además óptimos para utilizar en un entorno de fuga elevada o de ruido elevado.

Se ha deseado proporcionar un registro dominó mejorado que proporcione todos los beneficios del registro dominó no inversor anterior, y que sea además flexible con respecto a la etapa dominó y que sea óptimo para usar en un entorno de fuga elevada o de ruido elevado.

Se ha deseado además proporcionar una retención de salida dominó N mejorada que proporcione todos los beneficios del registro dominó no inversor anterior cuando es usado como un enganche, y que sea además flexible con respecto a la etapa dominó y que sea óptimo para usar en un entorno de fuga elevada o de ruido elevado.

Se ha deseado además proporcionar un circuito dominó P mejorado que, cuando es empleado como un enganche, proporcione todos los beneficios del registro dominó no inversor, y que sea optimizado para usar en un entorno de fuga elevada o de ruido elevado.

Adicionalmente se ha deseado proporcionar un circuito dominó P mejorado que, cuando es empleado como un enganche, proporcione todos los beneficios del registro no inversor anterior, y que sea optimizado para usar en un entorno de fuga elevada o de ruido elevado.

#### COMPENDIO DEL INVENTO

10

15

20

45

50

De acuerdo con un primer aspecto del invento se ha proporcionado un enganche dominó N, que comprende: una etapa dominó, acoplada a una señal de reloj aproximadamente simétrica, y para evaluar una función lógica de acuerdo con los estados de al menos una señal de datos y dicha señal de reloj aproximadamente simétrica, en el que dicha etapa dominó carga previamente un nodo precargado cuando dicha señal de reloj aproximadamente simétrica es baja, y descarga dicho nodo precargado a un estado bajo si dicha función lógica evalúa cuando dicha señal de reloj aproximadamente simétrica es alta, y mantiene dicho nodo precargado alto si dicha función lógica falla al evaluar cuando dicha señal de reloj aproximadamente simétrica es alta, en el que un estado de enganche de al menos dicha señal de datos es proporcionado a dicha etapa dominó cuando dicha señal de reloj aproximadamente simétrica es alta, en el que dicha etapa dominó comprende: un dispositivo de canal P que tiene una puerta acoplada a dicha señal de reloj aproximadamente simétrica, y una salida y una fuente acopladas entre una fuente de tensión y dicho nodo precargado; un dispositivo de canal N que tiene una puerta acoplada a dicha señal de reloj aproximadamente simétrica, una salida acoplada a dicho nodo precargado y una fuente; y lógica de evaluación acoplada entre masa y dicha fuente de dicho dispositivo de canal N; una etapa de escritura, acoplada a dicha etapa dominó y que responde a dicha señal de reloj aproximadamente simétrica, que emite un primer nodo de salida preliminar si dicho nodo precargado baja y que emite de dicho primer nodo de salida preliminar bajo si dicho nodo precargado permanece alto; un inversor que tiene una entrada acoplada a dicho primer nodo de salida preliminar y una salida acoplada a un segundo nodo de salida preliminar; un trayecto mantenedor elevado que mantiene dicho primer nodo de salida preliminar alto cuando está habilitado, en el que dicho trayecto mantenedor más elevado es habilitado cuando dicha señal de reloj aproximadamente simétrica y dicho segundo nodo de salida preliminar son ambos bajos y que es inhabilitado de otra manera; un trayecto mantenedor bajo que mantiene dicho primer nodo de salida preliminar cuando está habilitado, en el que dicho trayecto mantenedor bajo está habilitado cuando dicho segundo nodo de salida preliminar y dicho nodo precargado son ambos altos y que es de otra manera inhabilitado; y una etapa de salida que proporcionar una señal de salida basada en estados de dicho nodo precargado y de dicho segundo nodo de salida preliminar.

25 De acuerdo con un segundo aspecto del invento se ha proporcionado un método de enganchar una o más señales de datos de entrada, que comprende: cargar previamente un primer nodo alto mientras una señal de reloj aproximadamente simétrica es baja; cuando la señal de reloj aproximadamente simétrica es alta, evaluar una función lógica basada en una o más señales de datos de entrada para controlar el estado del primer nodo, comprendiendo dicha evaluación: en primer lugar acoplar una puerta de un dispositivo de canal P a la señal de reloj aproximadamente simétrica, y en segundo lugar 30 acoplar una salida y fuente del dispositivo de canal P entre la fuente de tensión y el primer nodo; en tercer lugar acoplar una entrada de un dispositivo N a la señal de reloj aproximadamente simétrica, y en cuarto lugar acoplar una salida del dispositivo de canal N al primer nodo; y en quinto lugar acoplar lógica de evaluación entre masa y una fuente del dispositivo de canal N; controlar el estado de un segundo nodo con el estado del primer nodo cuando la señal de reloj aproximadamente simétrica es alta; definir el estado de un tercer nodo como el estado invertido del segundo nodo; 35 habilitar un trayecto mantenedor de estado bajo para mantener el estado del segundo nodo bajo cuando el primer y tercer nodo son ambos altos e inhabilitar de otra manera el trayecto mantenedor de estado bajo; habilitar un trayecto mantenedor de estado alto para mantener el estado del segundo nodo alto cuando la señal de reloj aproximadamente simétrica y el tercer nodo son ambos bajos e inhabilitar de otra manera el trayecto mantenedor de estado alto; y cuando la señal de reloj aproximadamente simétrica es baja, enganchar el estado de un nodo de salida basándose en los estados del primer y 40 tercer nodos.

Los documentos US2004/257115 y US2005/046446 son ejemplos de un registro de enganche de salida dominó N y de lógica dinámica de la técnica anterior, respectivamente.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

Los beneficios, características y ventajas del presente invento resultarán mejor comprendidos con relación a la siguiente descripción, y a los dibujos adjuntos en los que:

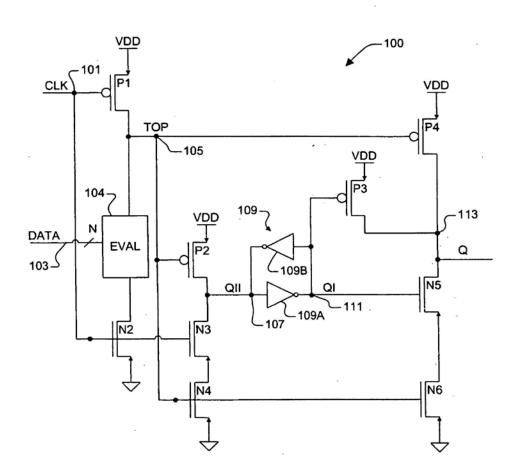

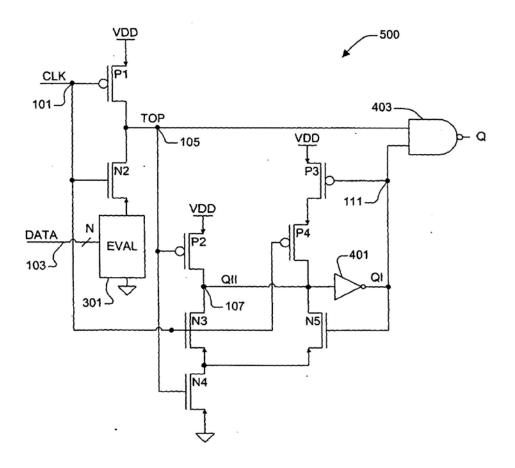

La fig. 1 es un diagrama esquemático de un registro dominó no inversor puesto en práctica de acuerdo con una exposición anterior que está incorporada como referencia;

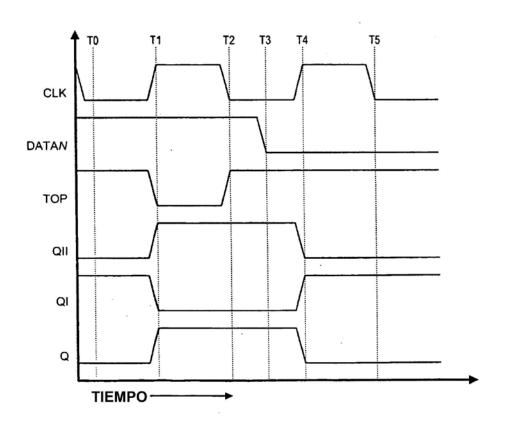

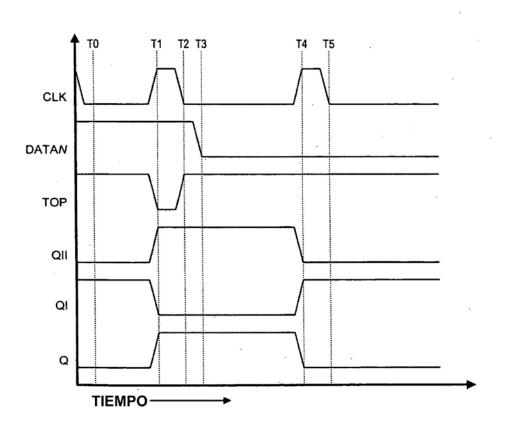

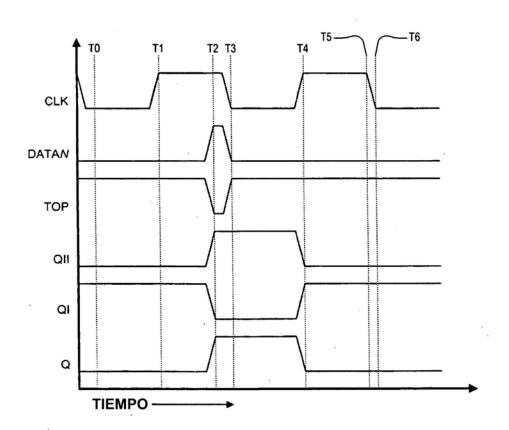

La fig. 2 es un diagrama de tiempo que ilustra el funcionamiento del registro dominó no inversor de las figs. 1, 3-4, y 5:

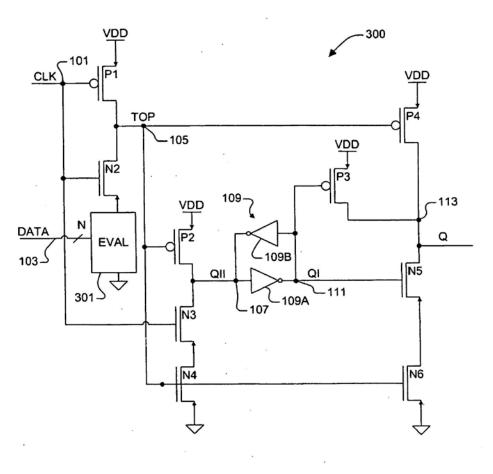

La fig. 3 es un diagrama esquemático de un registro dominó no inversor "sin pies" puesto en práctica de acuerdo con una realización ejemplar del presente invento;

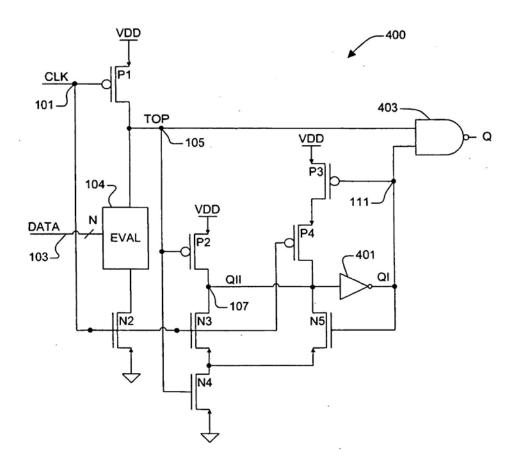

La fig. 4 es un diagrama esquemático de otro registro dominó no inversor puesto en práctica de acuerdo con una realización ejemplar del presente invento que emplea una etapa de almacenamiento mejorado;

La fig. 5 es un diagrama esquemático de otro registro dominó no inversor "sin pies" que emplea la etapa de

almacenamiento mejorado de la fig. 4 y puesto en práctica de acuerdo con una realización ejemplar del presente invento;

La fig. 6 es un diagrama de tiempo que ilustra el funcionamiento de los registros dominó no inversor de la figs. 1, 3-4, y 5 de acuerdo con una realización de reloj pulsatorio que es preferida para minimizar el tiempo de retención;

La fig. 7 es un diagrama de tiempo que ilustra el funcionamiento de una realización de enganche dominó N no inversor que emplea los circuitos de las figs. 1, 3-4, y 5;

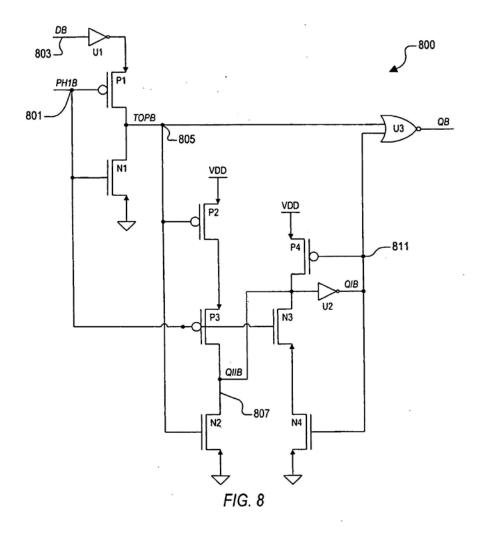

La fig. 8 es un diagrama esquemático de un circuito dominó P de acuerdo con otra realización ejemplar del presente invento;

La fig. 9 es un diagrama de tiempo que ilustra el funcionamiento del circuito dominó P de la fig. 8 cuando es empleado como una realización de registro dominó P del presente invento;

La fig. 10 es un diagrama de tiempo que ilustra el funcionamiento del circuito dominó P de la fig. 8 cuando es empleado como una realización de enganche dominó P del presente invento.

#### DESCRIPCIÓN DETALLADA

5

10

15

35

40

45

50

La siguiente descripción es presentada para permitir que un experto en la técnica haga y use el presente invento como está previsto dentro del contexto de una aplicación particular y de sus requisitos. Sin embargo, serán evidentes distintas modificaciones a la realización preferida para un experto en la técnica, y los principios generales aquí definidos pueden ser aplicados a otras realizaciones. Por ello, el presente invento no está destinado a estar limitado a las realizaciones particulares mostradas y descritas aquí, sino que ha de acordarse el marco más amplio en consonancia con los principios y nuevas características aquí descritos.

El inventor de la presente solicitud ha reconocido la necesidad de proporcionar salidas enganchadas y/o registradas para circuitos lógicos en las cuales la velocidad, el tamaño y la estabilidad son factores críticos, lo cual es flexible con respecto a la lógica de evaluación, y que pueden ser utilizadas en entornos de fuga elevada o de ruido elevado. Ha desarrollado por ello un registro dominó N no inversor y enganches de dominó N y dominó P que tienen un tiempo de datos para salida más rápido sin comprometer la estabilidad de la salida, que es flexible con relación a la puesta en práctica de la lógica de evaluación, y que puede ser usados en un entorno de fuga elevada o de ruido elevado, como será descrito adicionalmente a continuación con respecto a las figs. 1-5. Cuando es empleado en una arquitectura segmentada que se basa fuertemente en registros y lógica dominó para transferir datos de etapa a etapa, un registro dominó no inversor o enganche dominó de acuerdo con realizaciones del presente invento permite que la velocidad operativa del dispositivo completo sea aumentada significativamente. El dispositivo completo puede ser puesto en práctica usando dispositivos más rápidos y más pequeños en un proceso de fuga elevada o de ruido elevado sin comprometer la velocidad y sin requerir grandes dispositivos para superar a los dispositivos mantenedores.

La fig. 1 es un diagrama esquemático de un registro 100 dominó N no inversor puesto en práctica de acuerdo a la exposición anterior CNTR.2200. El registro 100 dominó no inversor incluye una etapa de entrada de evaluación lógica, o etapa dominó, que consiste de dispositivos P1 y N2 apilados de canal P y canal N y la lógica de evaluación 104. Los dispositivos P1 y N2 son un par complementario de dispositivos de evaluación acoplados a cada lado de la lógica de evaluación 104 en el apilamiento. La lógica de evaluación 104 puede ser tan simple como un único dispositivo de canal N o puede ser significativamente más compleja para la evaluación de cualquier función lógica deseada. La fuente de P1 está acoplada a una fuente de tensión VDD y su salida está acoplado al nodo 105 proporcionando una señal TOP. La lógica de evaluación 104 está acoplada entre el nodo 105 y la salida de N2, que tiene su fuente acoplada a masa. Una señal de reloj CLK de entrada es proporcionada a través del nodo 101 a las puertas de P1 y N2. Un conjunto 103 de N nodos proporciona N señales DATA de datos de entrada a la lógica de evaluación 104, en que N es cualquier entero positivo.

La etapa dominó del registro 100 dominó N no inversor va seguida por una etapa de almacenamiento que incluye dispositivos P2, N3, y N4 y un circuito de mantenimiento débil 109. Los dispositivos P2, N3 y N4 pueden ser considerados como una "etapa de escritura" y el circuito de mantenimiento 109 como una etapa conservadora dentro de la etapa de almacenamiento. El nodo 101 está acoplado a la puerta de N3 y el nodo 105 está acoplado a las puertas de P2 y N4. La fuente P2 está acoplada a VDD y su salida está acoplada a un primer nodo 107 de salida intermedia que proporciona una primera señal de salida intermedia QH. El nodo 107 está acoplado a la salida de N3, a la entrada de un inversor 109A y a la salida de otro inversor 109B. La salida del inversor 109A está acoplada a un segundo nodo 111 de salida intermedia que proporciona una segunda señal de salida intermedia Q1, que está acoplada a la entrada del inversor 109B. Los inversores 109A y 109B están acoplados cruzados entre los nodos 107 y 111 y forman colectivamente el circuito de mantenimiento débil 109. La fuente de N3 está acoplada a la salida de N4, que tiene su fuente acoplada a masa.

La etapa de almacenamiento del registro dominó no inversor 100 va seguida por una etapa de salida adicional, que incluye los dispositivos P3 y P4 de canal P y los dispositivos N5 y N6 de canal N. El nodo 105 está acoplado a las puertas de P4 y N6, y el nodo 111 está acoplado a las puertas de P3 y N5. Las fuentes de P3 y P4 están acopladas a VDD y sus salidas

están acoplados juntos en un nodo de salida 113 que proporciona una señal de salida Q. El nodo de salida 113 está acoplado a la salida de N5, que tiene su fuente acoplada a la salida de N6, que tiene su fuente acoplada a masa. Los dispositivos de canal P funcionan generalmente como dispositivos para llevar a un valor alto o elevar y los dispositivos de canal N funcionan generalmente como dispositivos para llevar a un valor bajo o descender.

- La fig. 2 es un diagrama de tiempos que ilustra el funcionamiento del registro 100 dominó N no inversor, en que las señales CLK, DATAN, TOP, QII, QI Y Q están trazadas en función del tiempo. Los tiempos de transición relativos son estimados y los retrasos son ignorados. La señal DATAN es mostrada como una señal única que representa el conjunto colectivo de N señales DATA. La señal DATAN está mostrada confirmada alta para el caso en que el estado colectivo de las señales de datos hace que la lógica de evaluación 104 evalúe, llevando por ello la señal TOP a un valor bajo, y está 10 mostrada confirmada baja para el caso en que la lógica de evaluación 104 falle al evaluar, lo que conserva la señal TOP alta. Así, cuando la lógica de evaluación 104 "evalúa", hace que la señal TOP transite desde su estado precargado alto a un estado bajo. Cuando la lógica de evaluación "falla al evaluar", TOP permanece en su estado precargado alto. En el instante T0, cuando la señal CLK es inicialmente baja, N2 está desactivado y P1 está activado, de manera que la etapa dominó precarga la señal TOP alta. La señal TOP es cargada previamente alta en preparación para la evaluación de la 15 señal DATAN por la lógica de evaluación 104 sobre el borde ascendente de CLK, donde la señal DATAN es inicialmente alta. La señal TOP cargada previamente activa N4 y N6. La señal QII permanece en su estado anterior (mostrada inicialmente en un estado lógico bajo) y es retenida allí por el circuito de mantenimiento 109. La señal QI es inicialmente alta activando N5, de manera que la señal de salida Q es inicialmente llevada a un valor bajo mediante los dispositivos N5

- En el instante T1 la señal CLK adopta un valor alto, lo que provoca que la señal TOP se descargue a un nivel bajo ya que la señal DATAN está alta. En particular, N2 es activado y la lógica de evaluación 104 lleva la TOP a un valor bajo mediante N2 a masa. La señal QII es llevada a un valor alto mediante P2 y la señal de salida Q es llevada a un valor alto mediante P4. Las señales QII y Q son ambas llevadas a un valor alto en el mismo instante T1, y la señal QI es llevada a un valor bajo por el inversor 109A. El estado invertido de la señal QI en la salida del circuito de mantenimiento 109 activa los dispositivos P3 y N5. Cuando QI es alta, P3 está desactivado y N5 está activado; y cuando QI es baja, P3 está activado y N5 desactivado. En el instante subsiguiente T2 cuando la siguiente señal CLK a continuación adopta un valor bajo, la señal TOP es otra vez cargada previamente alta. P2 y N3 son desactivados de manera que el nodo 107 no es activado a ningún estado. Los estados respectivos de las señales QII y QI permanecen sin cambios, sin embargo, mediante la operación del circuito de mantenimiento 109, de manera que las señales QI y QII permanecen altas y la señal QI permanece baja a lo largo de todo el resto del semiciclo de CLK.

- La señal DATAN está mostrada adoptando un valor bajo en el instante T3 mientras la señal CLK es aún baja, y la señal CLK es a continuación confirmada alta en el instante T4 mientras la señal DATAN es baja. La lógica de evaluación 104 falla al evaluar, de manera que TOP permanece alta mientras DATAN es baja y CLK es alta. Las señales CLK y TOP activan los dispositivos N3 y N4, respectivamente, de manera que la señal QII es confirmada baja aproximadamente en el instante T4, y la señal QI es llevada consecuentemente a un valor alto por el inversor 109A. Al ser alta la señal TOP conserva N6 activado. La señal QI activa N5 y desactiva P3, de manera que la señal Q es llevada a un valor bajo a través de N5 y N6. La señal CLK adopta un valor bajo a continuación en el instante T5 llevando TOP a un valor alto de nuevo. Los estados respectivos de las señales QII y QI permanecen sin cambios a través del funcionamiento del circuito de mantenimiento 109. La señal Q permanece baja a lo largo de todo el resto del ciclo de CLK ya que QI mantiene N5 activado y TOP mantiene N6 activado.

35

40

45

50

- La señal Q transita desde baja a alta de un modo relativamente rápido en respuesta a un borde ascendente de la señal CLK cuando la lógica de evaluación 104 evalúa la descarga de la señal TOP a un nivel bajo. Hay un retraso despreciable a través de los dispositivos N2 y P4 provocando la transición de la salida. La señal de salida Q transita desde alta a baja después de un retraso despreciable a través de los dispositivos N3, N5 y el inversor 109A en respuesta un borde ascendente de la señal CLK cuando la lógica de evaluación 104 falla al evaluar, dejando la señal TOP alta. El retraso a través del inversor 109A es minimizado al ser puesto en práctica como un dispositivo relativamente pequeño (con capacitancia mínima) ya que no necesita tener el tamaño ni realizar la función de una memoria tampón. En otra realización, el retraso puede ser minimizado empleando lógica proporcionada (es decir, el dispositivo P grande y el dispositivo N pequeño) para el inversor 109A. Es apreciado por los expertos en la técnica que las transiciones de la señal de salida Q del registro 100 dominó no inversor sean muy rápidas en respuesta a transiciones de la señal CLK. Si es necesaria una salida no inversora o deseada de otro modo, el registro 100 dominó no inversor proporciona una velocidad de datos para salida superior comparada con diseños convencionales entre otros beneficios y ventajas. El registro 100 dominó no inversor puede ser convertido a un registro dominó inversor simplemente añadiendo un inversor/tampón de salida (no mostrado).

- Como el funcionamiento del circuito 100 de la fig. 1 ha sido descrito, un experto en la técnica apreciará que como la función de la lógica de evaluación 104 es hacer transitar rápidamente la señal TOP desde su nivel alto previamente cargado a un nivel bajo, una realización del presente invento emplea dispositivos P y N proporcionados para configurar la lógica de evaluación 104. En esta realización, son empleados dispositivos N fuertes y dispositivos P débiles, dando como

resultado un funcionamiento más rápido.

10

15

20

25

30

35

40

45

50

La exposición anterior CNTR.2200 ha ilustrado la lógica AND y la lógica OR ejemplares (no mostradas aquí), que pueden ser usadas como la lógica de evaluación 104. Se ha descrito que cualquier combinación adecuada de los circuitos lógicos AND y OR es contemplada, y que cualquier otro circuito de evaluación lógica compleja es contemplado, incluyendo, por ejemplo, multiplexadores de entradas múltiples (multiplexadores), codificadores multi bits, etc. Cualquier lógica de evaluación deseada de simple a compleja puede ser sustituida por la lógica de evaluación 104 sin impactar de manera adversa en las tensiones de velocidad o de potencia asociadas del registro 100 dominó no inversor. Los circuitos lógicos AND y OR fueron solamente ejemplares y fueron previstos para ilustrar que la lógica de evaluación 104 puede ser cualquier circuito de evaluación lógica compleja como es apreciado por los expertos en la técnica. Una limitación posible del registro 100 dominó inversor, sin embargo, es que no es particularmente flexible con respecto a la lógica de evaluación 104, que típicamente tenía que ser puesta en práctica como lógica de canal N. La lógica de canal N no proporciona los niveles óptimos de margen de ruido de entrada.

La fig. 3 es un diagrama esquemático de otro registro 300 dominó no inversor puesto en práctica de acuerdo con una realización ejemplar del presente invento. El registro 300 dominó no inversor es sustancialmente similar al registro 100 dominó no inversor de la fig. 1, excepto en que la etapa de entrada de evaluación lógica, o etapa dominó, que comprende los dispositivos P1 y N2 apilados de canal P y canal N y la lógica de evaluación 104, es reordenada en una configuración "sin pies" y la lógica de evaluación 104 es reemplazada con la lógica de evaluación 301. Los dispositivos P1 y N2 son un par complementario de dispositivos de evaluación acoplados juntos en el nodo 105 que proporciona la señal TOP. En este caso, la salida de N2 está acoplada al nodo 105 y su fuente está acoplada al extremo superior de la lógica de evaluación 301. El extremo inferior de la lógica de evaluación 301 está acoplado a masa. De esta manera, la lógica de evaluación 301 está acoplada al pié del apilamiento de P1/N2 en oposición a estar acoplada entre P1 y N2. El funcionamiento es sustancialmente similar y el diagrama de tiempos de la fig. 2 permanece igualmente válido para el registro 300 dominó no inversor.

La lógica de evaluación 301 podría estar configurada de la misma manera sustancialmente que la lógica de evaluación 104. Como es comprendido por los expertos en la técnica, sin embargo, la lógica de evaluación 301 puede alternativamente ser realizada usando una lógica de semiconductor de óxido metálico (CMOS) complementaria en vez de la lógica de canal N, donde de nuevo, el diagrama de tiempos de la fig. 2 sigue siendo válido. La lógica CMOS proporciona un margen de ruido de nivel de entrada significativamente mejor sobre la lógica de canal N, de modo que el registro 300 dominó no inversor proporciona un margen de ruido de nivel de entrada significativamente mejor sobre el registro 100 dominó no inversor cuando se utiliza la lógica CMOS en la etapa dominó.

Los registros 100 y 300 dominó N no inversor experimentan ambos efectos de fuga cuando son realizados en un proceso de fuga elevada o de ruido elevado, tal como SOI de 90 nm y similar. Reducir los circuitos a 90 nm introduce cuestiones relacionadas con la fuga. Los procesos reducidos de tamaño exhiben fugas mayores ya que las longitudes de canal son más cortas. Por consiguiente, con el fin de escribir un nuevo estado en el nodo 107 de la etapa de almacenamiento para cualquiera de los registros 100 y 300, un dispositivo débil debe ser superado dentro del inversor de realimentación (por ejemplo, dentro del inversor 109B, un dispositivo de canal P débil para cambiar a un estado bajo y un dispositivo de canal N débil para cambiar a un estado alto). El coste de superar un dispositivo es velocidad y corriente. Además, en los procesos en que hay o bien una fuga elevada o bien un ruido elevado, los dispositivos N y P débiles dentro del inversor de realimentación 109B deben ser hechos más grandes con el fin de mantener el estado del nodo de salida en presencia de fuga o ruido.

Obsérvese, por ejemplo, que el nodo de almacenamiento 107 (señal QII) está aislado de la etapa de entrada cuando CLK es baja. No hay ninguna activación de la señal QII excepto el inversor de realimentación de mantenimiento 109B, que incluye dispositivos N y P débiles internos (no mostrados). Aún, debido a la fuga aumentada asociada con un proceso de modificación de tamaño, una mayor cantidad de corriente de fuga circula a través de los dispositivos P2 y N3. Así, los dispositivos N y P en el inversor 109B han de ser lo suficientemente grandes para superar esa fuga. Por ejemplo, si la señal QII es alta, la fuga ocurre a masa a través de los dispositivos N3 y N4, de manera que el dispositivo P dentro del inversor 109B ha de ser lo bastante grande para alimentar bastante corriente para superar esa fuga para mantener la señal QII alta. En los procesos en que hay una fuga elevada o corrientes elevadas y los dispositivos están desactivados, son necesarios dispositivos cada vez más amplios para retener el estado. Y el uso de dispositivos más amplios reduce sustancialmente el rendimiento porque cuando un nuevo estado es escrito, el dispositivo más amplio que está manteniendo el estado debe ser superado. Para compensar la reducción en velocidad, los dispositivos P2, N3 y N4 de etapa de almacenamiento son hechos mayores para activar el nuevo estado para superar el retenido por los dispositivos grandes en el inversor de realimentación de mantenimiento 109B. Los dispositivos más grandes consumen espacio valioso en un circuito integrado (IC).

La fig. 4 es un diagrama esquemático de otro registro 400 dominó no inversor puesto en práctica de acuerdo con una realización ejemplar del presente invento que emplea un circuito de mantenimiento perfeccionado. El registro 400 dominó no inversor incluye una etapa dominó de entrada seguida por una etapa de almacenamiento y una etapa de salida. La

etapa dominó y la parte inicial de la etapa de almacenamiento del registro 400 son similares a las del registro 100. El circuito de mantenimiento del registro 400, sin embargo, está modificado para mejorar el rendimiento eliminando la necesidad de superar dispositivos y reducir coste en términos de velocidad y corriente. La etapa dominó incluye dispositivos P1 y N2 apilados de canal P y canal N y lógica de evaluación 104. Como antes, los dispositivos P1 Y N2 son un par complementario de dispositivos de evaluación acoplados en cada lado de la lógica de evaluación 104 entre la fuente de tensión VDD y masa. La fuente de P1 está acoplada a VDD y su salida está acoplada al nodo 105 que proporciona la señal TOP. La lógica de evaluación 104 está acoplada entre el nodo 105 y la salida de N2 y la fuente de N2 está acoplada a masa. La señal de reloj de entrada CLK es proporcionada a través del nodo 101 a las puertas de P1, N2 y N3. Un conjunto de N nodos 103 proporciona N señales de datos de entrada DATA a la lógica de evaluación 104. Como antes, el nodo 105 que proporciona la señal TOP está acoplado a las puertas de los dispositivos P2 y N4. La parte inicial de la etapa de almacenamiento es sustancialmente la misma etapa de escritura que incluye los dispositivos apilados P2, N3 y N4. La fuente de P2 está acoplada a VDD y su salida está acoplada al nodo 107 desarrollando la primera señal de salida intermedia QII. La salida de N3 está acoplada al nodo 107 y su fuente está acoplada a la salida de N4, que tiene su fuente acoplada a masa.

10

- La etapa de almacenamiento del registro 400 dominó no inversor incluye la etapa de escritura que incluye los dispositivos P3, P4, y N5 y una etapa de mantenimiento que incluye los dispositivos P3, P4, N3 y un inversor 401. La etapa de almacenamiento va seguida por una etapa de salida, que comprende una puerta 403 NAND de dos entradas en la realización ilustrada. En este caso, la fuente de P3 está acoplada a VDD y su salida está acoplada a la fuente de P4, que tiene su salida acoplada a la salida de N5 en el nodo 107. La fuente de N5 está acoplada a la salida de N4 acoplado además a la fuente de N3. El nodo 101, que proporciona la señal CLK, está acoplado a la puerta de P4. El nodo 107, que desarrolla la señal QII, está acoplado a la entrada del inversor 401 que tiene su salida acoplada al nodo 111 que desarrolla la segunda señal de salida intermedia QI. El nodo 111 está acoplado a las puertas de P3 y N5 y está acoplado a una entrada de la puerta 403 NAND. El nodo 105, que proporciona la señal TOP, está acoplado a la otra entrada de la puerta 403 NAND, y la salida de la puerta 403 NAND proporciona la señal Q de salida.

- El diagrama de tiempos de la fig. 2 es aplicable para el registro 400 dominó no inversor para esta situación con sólo menores diferencias en tiempo, donde tales diferencias de tiempo y pequeños retrasos son ignorados (por ejemplo, retrasos a través del inversor 401 y la puerta 403 NAND son ignorados). De nuevo, supóngase que la señal QII es inicialmente baja y ha de ser confirmada alta. Con referencia a la fig. 2, en el instante T0, las señales CLK, Q y QII son inicialmente bajas y la señal QI es alta. Como CLK es baja, P1 es activado y TOP es cargada previamente alta activando N4. Como QI y TOP son ambas altas, la señal Q en la salida de la puerta 403 NAND es inicialmente baja. Mientras CLK es baja y QI es alta, N5 está activado, P3 está desactivado y P4 está activado. En este caso, por lo tanto, N5 y N4 están ambos activados proporcionando un trayecto de mantenimiento de estado "bajo" para el nodo 107 a masa que mantiene la señal QII baja. El trayecto de mantenimiento bajo es habilitado siempre que el segundo nodo de salida preliminar 111 y el nodo 105 cargado previamente sean ambos altos, y de otro modo es inhabilitado.

- Cuando la señal CLK adopta un valor alto en el instante T1, N2 es activado iniciando la evaluación de los operandos de DATA por la lógica de evaluación 104. Como antes, la señal DATAN, que representa los operandos de DATA de entrada, es mostrada inicialmente alta lo que hace que la lógica de evaluación 104 acople el nodo 105 a la salida de N2. Esto hace que la señal TOP sea llevada a un nivel bajo a través de N2. Al adoptar TOP un valor bajo hace que la puerta 403 NAND confirme Q alta aproximadamente en el instante T1 (después de un corto retraso a través de la puerta 403 NAND).

También, al adoptar TOP un nivel bajo desactiva N4, inhabilitando por ello el trayecto de mantenimiento bajo desde N5 a través de N4 hacia abajo a masa. Y al adoptar TOP un valor bajo activa P2 de manera que la señal QII es llevada a un valor alto aproximadamente en el instante T1. Cuando la señal QII adopta un valor alto en el instante T1, el inversor 301 lleva la señal QI a un valor bajo, lo que activa P3 y desactiva N5. La señal de salida Q permanece baja mientras la señal QI es baja.

- En este ejemplo, el trayecto de mantenimiento bajo a través de N5 es inhabilitado debido a que N4 es desactivado cuando la señal TOP adopta un valor bajo. Y como N4 es desactivado, P2 no tiene que superar N5 para llevar la señal QII a un valor alto. Siempre que la señal QII es baja y ha de ser llevada a un valor alto en respuesta a la evaluación (llevar TOP a un valor bajo), el trayecto de mantenimiento bajo está siempre inhabilitado (porque N4 está desactivado) de manera que la etapa de escritura de la etapa de almacenamiento no tiene que superar un dispositivo de mantenimiento.

- En el momento T2 cuando CLK adopta un valor bajo a continuación, TOP es otra vez cargada previamente alta. También en el instante T2, P4 es activado proporcionando un trayecto de mantenimiento de etapa "alto" desde el nodo 107 A VDD mediante P4 y P3, manteniendo por ello la señal QII alta. El trayecto de mantenimiento alto es habilitado siempre que el nodo 105 cargado previamente y el segundo nodo de salida preliminar 111 están ambos bajos, y de lo contrario es inhabilitado. Así, la señal QII es conservada alta, lo que a su vez mantiene QI baja para mantener el estado de la señal de salida Q mientras TOP adopta un valor alto en el instante T2. Al adoptar la señal TOP un valor alto activa N4 de nuevo aproximadamente en el instante T2, pero como la señal QI es baja, N5 es desactivado manteniendo por ello el trayecto conservador bajo desactivado o inhabilitado para el resto del ciclo.

La señal DATA*N* adopta un valor bajo en el instante T3 y la siguiente señal CLK adopta un valor alto a continuación en el instante T4 mientras la señal DATA*N* es aún baja de manera que la lógica de evaluación 104 no evalúa. Consiguientemente, TOP permanece alta en el instante T4 de manera que N4 permanece activado. Al adoptar la señal CLK un valor alto, desactiva P4 y activa N3. El trayecto de mantenimiento alto desde el nodo 107 a VDD es inhabilitado ya que P4 está desactivado, y N3 y N4 están ambos activados haciendo descender la señal QII. Como P4 está desactivado, N3 y N4 no tienen que superar ningún dispositivo, incluyendo dispositivos de mantenimiento débiles, para llevar a QII a un valor bajo. Siempre que la señal QII es alta y ha de ser llevada a un valor bajo en respuesta al fallo de evaluación (en que TOP permanece alta), el trayecto de mantenimiento alto está siempre inhabilitado (porque P4 está desactivado) de manera que la etapa de escritura de la etapa de almacenamiento no tiene que superar un dispositivo de mantenimiento. El inversor 401 lleva QI a un valor alto en el instante T4 en respuesta a que QI adopta un valor bajo. Como QI y TOP son ambas altas, la puerta NAND 403 lleva Q a un valor bajo en el instante T4. También, al adoptar QI un valor alto activa N5 y desactiva P3, de manera que el trayecto de mantenimiento alto es inhabilitado y el trayecto de mantenimiento bajo a través de N5 y N4 es rehabilitado. Cuando la CLK adopta un valor bajo a continuación en el instante T5, N3 es desactivados, pero QII es conservada baja a través del trayecto de mantenimiento bajo mientras N5 y N4 son mantenidos activados. Tanto TOP como QI permanecen altas, de manera que Q permanece baja durante el resto del ciclo de CLK.

10

15

20

40

45

50

55

El registro 400 dominó no inversor de la fig. 4 emplea una técnica mejorada para inhabilitar los dispositivos de realimentación de mantenimiento débiles, de manera que cuando se está escribiendo un nuevo estado, un dispositivo fuerte interno a un dispositivo de mantenimiento no tiene que ser superado. Por consiguiente, los dispositivos P3 y N5 son hechos más amplios para superar la fuga con el fin de mantener el estado, pero sin afectar a la velocidad debido a que los mismos dispositivos P3 y N5 son inhabilitados cuando se escribe un nuevo estado para el nodo de almacenamiento 107 (la señal QII). Cuando se escribe un nuevo estado de la señal QII, un circuito de mantenimiento de realimentación no tiene que ser superado, de manera que los dispositivos P2 y N3 pueden ser dispositivos de tamaño normal. El "mantenedor" del registro 400 dominó no inversor es solamente habilitado para almacenar el estado. En particular, los dispositivos de realimentación son habilitados para mantener el estado e inhabilitados cuando se está escribiendo un nuevo estado.

La fig. 5 es un diagrama esquemático de otro registro 500 dominó no inversor sin pies que emplea la etapa de mantenimiento mejorada del registro 400 y puesta en práctica de acuerdo a una realización alternativa. El registro 500 dominó no inversor es sustancialmente similar al registro 400 dominó no inversor, excepto en que la etapa de entrada de evaluación lógica, o etapa dominó, que comprende los dispositivos P1 y N2 apilados de canal P y canal N y la lógica de evaluación 104 es reemplazada con la lógica de evaluación 104 es reemplazada con la lógica de evaluación 301. El cambio al registro 500 desde el registro 400 es análogo al cambio desde el registro 300 al 100. De esta manera, la lógica de evaluación 301 del registro 500 dominó no inversor puede ser puesta en práctica con lógica CMOS en vez de con lógica de canal N, donde de nuevo, el diagrama de tiempos de la fig. 2 permanece aplicable. Como se ha descrito previamente, la lógica CMOS proporciona un margen de ruido de nivel de entrada significativamente mejor sobre la lógica de canal N de manera que el registro 500 dominó no inversor proporciona un margen de ruido de nivel de entrada algo mejor sobre el registro 400 dominó no inversor cuando se usa la lógica CMOS en la etapa dominó.

Un registro dominó no inversor implantado de acuerdo a las realizaciones así descritas tiene un tiempo de reloj para salida más rápido que las aproximaciones convencionales sin comprometer la estabilidad de su salida, Q. Además, la etapa de almacenamiento pueda ser mejorada adicionalmente para permitir que dispositivos más pequeños, más rápidos sean empleados en un entorno de fuga elevado que los que de otro modo serían requeridos para superar dispositivos de mantenimiento fuertes. Esto permite que el registro dominó no inversor sea llevado a la práctica en un proceso de fuga elevada o de ruido elevado, tal como SOI de 90 nm y similar, sin provocar degradación del rendimiento provocada por los factores de fuga. Así, los beneficios de un proceso a escala, incluyendo tamaño reducido, tensión, consumo de potencia, etc., pueden ser alcanzados sin provocar la degradación del rendimiento asociada con tales procesos de escalado.

Se ha observado que el funcionamiento de las distintas realizaciones del presente invento como se ha descrito antes con referencia a las figs. 2-5 tienen todos requisitos de tiempo de retención de datos que son una función del ciclo de trabajo de la señal de reloj CLK mostrada en el nodo 101. Más específicamente, las señales de datos DATAN en el nodo 103 deben ser retenidas al nivel deseado durante el período de tiempo en el que la señal de reloj CLK es alta. Si DATAN cambia el estado o estados durante el intervalo en el que CLK es alta, entonces el cambio de estado se propagará a través de la salida Q. Los presentes inventores han observado también que es deseable en algunas aplicaciones de registro proporcionar realizaciones del presente invento que minimizan los requisitos del tiempo de retención para DATAN. Por consiguiente, una realización de reloj pulsatorio será ahora descrita con referencia a la fig. 6, en que la realización está configurada para minimizar el tiempo de retención de datos.

Volviendo a la fig. 6, se ha presentado un diagrama de tiempos 600 que ilustra el funcionamiento del registro dominó no inversor de las figs. 1, 3, 4 y 5 de acuerdo con una realización de reloj pulsatorio que es preferida para minimizar el tiempo de retención. Como se ha descrito antes con referencia a la fig. 2, las señales CLK, DATAN, TOP, QII, QI y Q están trazadas en función del tiempo. Los tiempos de transiciones relativas son estimados y los retrasos son ignorados. La señal DATAN está mostrada como una única señal que representa el conjunto colectivo de N señales DATA. La señal DATAN está mostrada confirmada alta para cuando el estado colectivo de las señales de datos hace que la lógica de evaluación

104 evalúe llevando por ello la señal TOP a un valor bajo, y está mostrada confirmada baja para cuando la lógica de evaluación 104 falla al evaluar, lo que conserva la señal TOP alta. En el instante T0 cuando la señal CLK es inicialmente baja, N2 es desactivado y P1 es activado, de manera que la etapa dominó carga previamente la señal TOP alta. La señal TOP es cargada previamente alta en preparación para la evaluación de la señal DATAN por la lógica de evaluación 104 sobre el borde ascendente de CLK, en que la señal DATAN es inicialmente alta. La señal TOP cargada previamente activa N4 y N6. La señal QII permanece en su estado anterior (mostrada inicialmente en un estado lógico bajo) y es confirmada allí por el circuito de mantenimiento 109. La señal QI es inicialmente alta activando N5, de manera que la señal de salida Q es inicialmente llevada a un valor bajo mediante los dispositivos N5 y N6.

En el instante T1 la señal CLK adopta un valor alto, lo que hace que la señal TOP se descargue a un nivel bajo ya que la señal DATAN es alta. En particular, N2 es activado y la lógica de evaluación 104 evalúa llevando TOP a un valor bajo a través de N2 a masa. La señal QII es llevada a un valor alto a través de P2 y la señal de salida Q es llevada a un valor alto a través de P4. Las señales QII y Q son ambas llevadas a un valor alto en el mismo instante T1, y la señal QI es llevada a un valor bajo por el inversor 109A. El estado invertido de la señal QI en la salida del circuito de mantenimiento 109 activa los dispositivos P3 y N5. Cuando QI es alta, P3 es desactivado y N5 es activado; y cuando QI es baja, P3 es activado y N5 es desactivado. En el instante T2 subsiguiente cuando la siguiente señal CLK adopta un valor bajo, la señal TOP es una vez más cargada previamente alta. P2 y N3 son desactivados de manera que el nodo 107 no es activado a ningún estado. Los estados respectivos de las señales QII y QI permanecen sin cambios, sin embargo, mediante el funcionamiento del circuito de mantenimiento 109, de manera que las señales Q y QII permanecen altas y la señal QI permanece baja durante todo el resto del semiciclo de CLK.

La DATA*N* está mostrada adoptando un valor bajo en el instante T3 mientras la señal CLK es aún baja, y la señal CLK es a continuación confirmada alta en el instante T4 mientras la señal DATA*N* es baja. La lógica de evaluación 104 falla al evaluar, de manera que TOP permanece alta mientras CLK está alta. Las señales CLK y TOP activan los dispositivos N3 y N4, respectivamente, de manera que la señal QII es confirmada baja aproximadamente en el instante T4, y la señal QI es consiguientemente llevada a un valor alto por el inversor 109A. Al estar alta la señal TOP mantiene N6 activado. La señal QI activa N5 y desactiva P3, de manera que la señal Q es llevada a un valor bajo mediante N5 y N6. La señal CLK adopta un valor bajo a continuación en el instante T5 llevando TOP a un valor alto de nuevo. Los estados respectivos de las señales QII y QI permanecen sin cambios mediante el funcionamiento del circuito de mantenimiento 109. La señal Q permanece a lo largo de todo el resto del ciclo de CLK ya que QI mantiene N5 activado y TOP mantiene N6 activado.

30

35

40

45

50

55

La señal Q transita de baja a alta de modo relativamente rápido en respuesta a un borde ascendente de la señal CLK cuando la lógica de evaluación 104 evalúa descargar la señal TOP baja. Hay un retraso despreciable a través de los dispositivos N2 y P4 que provoca la transición de salida. La señal Q transita de alta a baja después de un retraso despreciable a través de los dispositivos N3, N5, y el inversor 109A en respuesta a un borde ascendente de la señal CLK cuando la lógica de evaluación 104 falla al evaluar dejando la señal TOP alta. El retraso a través del inversor 109A es minimizado siendo puesto en práctica como un dispositivo relativamente pequeño (con capacitancia mínima) ya que no necesita tener el tamaño ni realizar la función de un tampón. Es apreciado por los expertos en la técnica que las transiciones de la señal Q de salida del registro 100 dominó no inversor, son muy rápidas en respuesta a transiciones de la señal CLK. Si una salida no inversora es necesaria o deseada de otro modo, el registro 100 dominó no inversor proporciona una velocidad de datos para salida superior comparada con diseños convencionales entre otros beneficios y ventajas. El registro 100 dominó no inversor puede ser convertido a un registro dominó inversor simplemente añadiendo un inversor/tampón de salida (no mostrado).

Se ha observado que solamente la diferencia entre el diagrama de tiempos de la fig. 2 y el diagrama de tiempos de la fig. 6 es que el nodo 103 de los registros dominó no inversor de las figs. 1, 3, 4 y 5 están cada uno acoplado a una señal de reloj pulsatoria CLK en vez de estar acoplado a una señal de reloj CLK aproximadamente simétrica. Por consiguiente, el requisito del tiempo de retención para la señal de datos DATAN es reducido significativamente sobre las realizaciones descritas con referencia a la fig. 2. En una realización, el ciclo de trabajo de la señal de reloj pulsatoria CLK es menor o igual al 10%. Comparando las realizaciones de las figs. 2 y 6, se ha observado que el tiempo desde T1 (cuando CLK sube) a T3 (cuando el estado de DATAN es permitido que cambie) es notablemente menor que el periodo comparable de la fig. 2. Tal realización del presente invento es preferida para minimizar el tiempo de retención.

Se ha observado adicionalmente que como el estado de DATA*N* es permitido que se propague a través de la salida Q cuando CLK es alta, las configuraciones descritas con referencia a las figs. 1, 3, 4 y 5 pueden también ser realizadas como realizaciones de un enganche dominó N cuando el nodo 101 está acoplado a un reloj CLK de enganche aproximadamente simétrico y en que el nodo 103 recibe los datos de enganche DATA*N*. Los datos de enganche DATA*N* pueden ser proporcionados por un circuito dominó precedente para el que se desea una función de enganche. Los circuitos de las figs. 1, 3, 4 y 5 son ventajosos cuando son usados como realizaciones de enganche dominó N debido a un trayecto de descarga acelerado a través del nodo 105 a la señal de salida Q, permitiendo así que más circuitos dominó en serie precedan al nodo 103 que los que han sido previstos hasta ahora. Las realizaciones de enganche dominó N serán ahora descritas con referencia a la fig. 7.

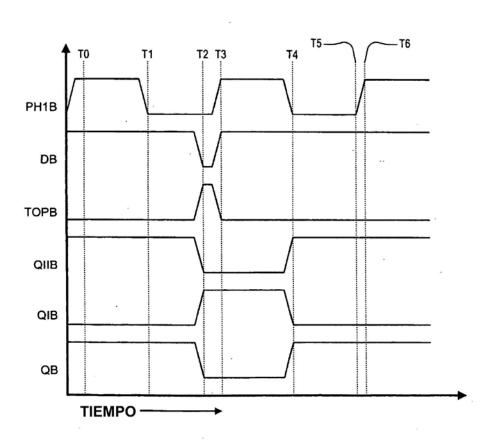

Volviendo a la fig. 7, se ha presentado un diagrama de tiempos 700 que ilustra las realizaciones de enganche dominó N del presente invento. Para emplear los circuitos de las figs. 1, 3, 4, y 5 como realizaciones de enganche dominó N, es deseable acoplar el nodo 101 a una señal CLK de reloj de enganche aproximadamente simétrica. En una realización, la señal CLK de reloj de enganche exhibe desde un 40 por ciento a un 60 por ciento de ciclo de trabajo. A modo de perspectiva general, se ha observado que durante el período en el que CLK es alta, una ventana de evaluación es abierta donde se permite que DATAN cambie y la salida Q siga a DATAN. Pero cuando CLK adopta un valor bajo, el estado de DATAN es retenido hasta que CLK vuelve de nuevo a ser alta. Por tanto, en el instante T0, CLK es baja y TOP está cargada previamente. El estado previo (es decir, el estado anterior a aquel en el que CLK adopta un valor bajo) de DATAN es retenido a través de las señales QII, QI, y a través de la salida Q. En el instante T1, CLK vuelve de nuevo a adoptar un valor alto, abriendo una ventana en la que se permite que el estado de DATAN se propague a través de la salida Q. Como DATAN es baja, la salida Q permanece baja. En el instante T2, DATAN adopta un valor alto haciendo que la señal TOP se descargue, activando así P2 y haciendo que la salida Q adopte un valor alto. Pero en el instante T3, CLK vuelve de nuevo a adoptar un valor bajo, cerrando la ventana de evaluación y reteniendo el estado de DATAN, manteniendo Q así alta durante este período. DATAN vuelve también de nuevo a adoptar un valor bajo en T3, reflejando el estado de una etapa dominó precedente cuya salida está acoplada al nodo 803. TOP se carga previamente en el instante T3, configurando la siguiente ventana de evaluación cuando CLK adopta un valor alto en el instante T4. Como DATAN es baja en el instante T4, TOP no se descarga. Así en el instante T4, N3 y N4 son activados, activando QII baja y QI alta. Debido a que tanto QI como TOP son altas en T4, Q es activada baja. En el instante T5, debido a que DATAN está aún baja (es decir, la etapa dominó precedente no ha evaluado), TOP permanece alta y el estado bajo permanece en la salida Q. En el instante T6, CLK vuelve a adoptar un valor bajo, reteniendo en el estado de DATAN en la salida Q durante el período en el que CLK es

10

15

20

35

40

45

50

55

Un experto en la técnica apreciará también que debido a que DATAN generalmente vuelve a un valor bajo cuando CLK adopta un valor bajo, el dispositivo N2 puede ser eliminado del circuito en una realización de enganche dominó N, que aumenta la velocidad del circuito.

Con referencia ahora a la fig. 8, se ha presentado un diagrama esquemático de un circuito 800 dominó P de acuerdo con el presente invento. El circuito 800 dominó P puede ser empleado bien como un enganche o bien como un registro, exhibiendo ventajas sobre la técnica anterior como se describirá en detalle con referencia al diagrama de tiempo de las figs. 9 y 10. El presente invento también ha reconocido la necesidad de resolver el problema de tiempos lentos de salida para reloj en enganches y registros de salida de dominó P. Se ha desarrollado por ello un circuito 800 de salida de dominó P que puede ser empleado bien como un enganche o bien como un registro, basado en el tipo de señal de reloj y entrada de datos a los que está acoplado el circuito 800 de dominó P.

La configuración y funcionamiento del circuito 800 dominó P es similar al funcionamiento de las realizaciones del circuito de dominó N descritas antes con referencia a las figs. 1-7, excepto en que muchas de las señales y estados de señal son invertidos como se ha descrito a continuación. El circuito 800 dominó P incluye tres etapas, incluyendo una etapa de evaluación, una etapa de retención, y una etapa de salida. La etapa de evaluación está formada por un dispositivo P1 de canal P, un dispositivo N1 de canal N y un inversor U1. La etapa de retención está formada por los dispositivos P2 y P3 de canal P, y un dispositivo N2 de canal N, acoplado en una configuración apilada. La etapa de salida está formada por un dispositivo P4 de canal P, dispositivos N3 y N4 de canal N, un inversor U2, y una puerta NOR U3 de dos entradas. Una señal de reloj o de fase PH1B es proporcionada a través del nodo 801 a las puertas de P1, N1, P3, y N3. La fuente de N1 está acoplada a masa (relativa a una fuente de tensión VDD) y su salida está acoplada a un nodo 805 de carga previa que desarrolla una señal de carga previa denominada aquí como TOPB. La salida de P1 está acoplada al nodo 805 y su fuente está acoplada a la salida del inversor U1, que tiene su entrada acoplada a un nodo 803 que proporciona una señal de datos DB a la entrada del inversor U1.

Los dispositivos P1 y N1 forman un par complementario de dispositivos de evaluación con el inversor U1 formando lógica de evaluación para evaluación la señal de datos DB. Un experto en la técnica apreciará que el dispositivo de evaluación de entrada U1 puede ser reemplazado con lógica P más compleja configurada para llevar la fuente de P1 a un valor alto cuando una o más entradas de datos DB evalúan verdad (en cuyo caso el nodo 803 comprende un conjunto de nodos que proporcionan señales de datos correspondientes a una lógica de evaluación más compleja). Un única entrada de datos DB y una puerta U1 lógica de evaluación correspondiente están mostradas a todo lo largo de la presente exposición con propósitos de simplicidad de explicación. Además, como en las realizaciones de dominó N de las figs. 1 y 4, el inversor U1 (o lógica de evaluación CMOS complementaria más compleja puede ser intercambiada en posición de circuito en cascada con el dispositivo P1 para permitir configuraciones de lógica de evaluación complementaria más complejas). En tales configuraciones, la fuente de P1 estaría acoplada a la fuente de tensión VDD. Además un experto en la técnica apreciará que como la función U1 (o lógica de evaluación más compleja) es hacer transitar rápidamente la señal TOPB desde su nivel bajo cargado previamente a un nivel alto, una realización del presente invento emplea dispositivos P y N proporcionados (dispositivos P fuertes y dispositivos N débiles), dando como resultado una operación más rápida. Así, cuando U1 "evalúa", hace que la señal TOPB transite desde su estado bajo cargado previamente a un estado alto. Cuando U1 "falla al evaluar", TOPB permanece en su estado bajo precargado.

El nodo 805 que proporciona la señal TOPB está acoplado a las puertas de los dispositivos P2 y N2 y a una entrada de la puerta NOR U3. La fuente de P2 está acoplada a VDD y su salida está acoplada a la fuente de P3, teniendo su salida acoplada a un nodo 807 que desarrolla una primera señal de salida intermedia QIIB. La salida de N2 está acoplada al nodo 807 y su fuente está acoplada a masa. La fuente de P4 está acoplada a VDD y su salida está acoplada a la salida de N3, teniendo su fuente acoplada a la salida de N4 en el nodo 807. La fuente de N4 está acoplada a masa. El nodo 807 está acoplado al nodo formado por las salidas de P4 y N4 y a la entrada del inversor U2, donde la salida de U2 está acoplada al nodo 811 que desarrolla una segunda señal de salida intermedia QIB. La señal QIB es activada al estado lógico opuesto como la señal QIIB después del retraso de una puerta a través del inversor U2. El nodo 811 está acoplado a las puertas de P4 y N4 y a la otra entrada de la puerta NOR U3. La salida de la puerta NOR U3 proporciona la señal QB de salida.

5

10

15

30

35

40

45

50

55

Volviendo ahora a la fig. 9, se ha presentado un diagrama de tiempos que ilustra el funcionamiento del circuito 800 dominó P cuando es empleado como un registro dominó P en que las señales PH1B, DB, TOPB, QIIB, QIB Y QB están trazadas en función del tiempo. Se han hecho varias simplificaciones en los diagramas de tiempos. Los retrasos a través de cada dispositivo o componente (dispositivos de canal N, dispositivos de canal P, puertas lógicas, multiplexadores, etc.) están mostrados como si fueran iguales ya que son aproximadamente equivalentes entre sí, y los tiempos de subida y bajada están mostrados también como si fueran iguales, ya que estos tiempos son también aproximadamente equivalentes. El diagrama de tiempos ilustra dos ciclos de PH1B. Como se ha descrito antes, emplear el circuito 800 dominó P como un registro dominó P, es deseable para acoplar el nodo 801 a una señal de reloj pulsatoria PH1B. En una realización PH1B tiene un ciclo de trabajo menor o igual al 10 por ciento.

En un instante T0 inicial, la señal QIIB es inicialmente alta y ha de ser confirmada baja en respuesta a la señal PH1B que adopta un valor bajo ya que la señal DB es baja. Como PH1B es alta, N1 es activado, P1 es desactivado, y TOPB es baja "descargada previamente" de manera que P2 y N3 son ambos activados. Como QIB y TOPB son ambas bajas, la señal QB en la salida de la puerta NOR 813 es inicialmente alta. Mientras QH1B es alta y QIB es baja, N4 es desactivado, N3 es activado y P4 es activado. En este caso, por lo tanto, P4 y N3 son ambos activados proporcionando un trayecto de mantenimiento de estado "alto" para el nodo 807 a VDD, que mantiene la señal QIIB alta.

La señal DB, que representa uno o más operandos de datos de entrada, es mostrada inicialmente baja, lo que hace que el inversor U1 lleve la fuente de P1 a un nivel alto. Cuando la señal PH1B adopta un valor bajo en el instante T1 mientras DB es baja, P1 es activado. Cuando P1 es activado, la señal TOPB es llevada a un valor alto mediante P1. Al adoptar TOPB un valor alto hace que la puerta NOR U3 se confirme QB baja. También, al adoptar TOPB un valor alto en el instante T1 activa N2 de manera que la señal QIB sea llevada a un valor bajo. En respuesta a que la señal QIB adopte un valor bajo, el inversor U2 lleva la señal QIB a un valor alto. Al adoptar un valor alto QIB activa N4 y desactiva P4. Al ser la señal QIB alta engancha efectivamente la señal de salida QB baja para el resto del ciclo de PH1B.

En un instante T2, cuando la siguiente PH1B adopta un valor alto, TOPB es una vez más baja cargada previamente a través de N1. Al estar alta la señal QIB mantiene N4 activado que mantiene QIIB baja y QIB alta para mantener el estado de la señal de salida QB mientras TOPB adopta un valor bajo. Al adoptar la señal TOPB un valor bajo se activa otra vez P2, pero como la señal PH1B es alta, P3 es desactivado de manera que la señal QIIB no sea llevada a un valor alto.

La señal DB adopta un valor alto en el instante T3 para configurar el próximo borde de PH1B, de modo que el inversor U1 lleva la fuente de P1 a un valor bajo. La señal PH1B adopta un valor bajo a continuación en el instante T4, activando P1. Como DB es aún alta y la fuente de P1 es baja, TOPB permanece baja en el instante T4. Al adoptar un valor bajo la señal PH1B desactiva N3 y activa P3. Como N2 permanece desactivado y P2 y P3 están ambos activados, la señal QIIB es llevada a un valor alto. El inversor U2 lleva QIB a un valor bajo en respuesta a que QIIB adopte un valor alto. Como QIB y TOPB son ambas bajas ahora, la puerta NOR U3 lleva QB a un valor alto.

La realización del registro dominó P del circuito 800 de la fig. 8 es muy adecuada para trayectos de temporización críticos a "evaluar" condiciones debido a que sólo dos etapas (U1 y U3) de retraso de puerta son presentadas durante un periodo de evaluación (cuando PH1B es baja). Acoplando el nodo 801 a una fuente PH1B de reloj pulsatoria como se ha descrito aquí, los requisitos de tiempo de retención para la señal DB acoplada al nodo 803 son minimizados. Por ejemplo, en el diagrama de tiempos de la fig. 9, DB puede cambiar de estado en cualquier instante siguiente T2 (o instante T5) debido a que el estado de DB es registrado en QB hasta el intervalo de evaluación de PH1.

Como se permite que el estado de DB se propague a través de la salida QB cuando PH1B es bajo, el circuito 800 dominó P también puede estar realizado como un enganche dominó P acoplando el nodo 801 a una señal PH1B de reloj de enganche aproximadamente simétrica y acoplando el nodo 803 a los datos de enganche DB. Los datos de enganche DB pueden ser proporcionados por un circuito dominó precedente para el que se desea una función de retención. El circuito 800 de la fig. 8 es ventajoso cuando es usado como una realización de enganche dominó P debido a un trayecto de "descarga" acelerada a través del nodo 805 a la señal de salida QB, permitiendo así que más circuitos dominó en serie precedan al nodo 803 de lo que se había previsto hasta ahora. La realización de enganche dominó P será descrita a continuación con referencia a la fig. 10.

Volviendo a la fig. 10, se ha presentado un diagrama de tiempos que ilustra una realización de enganche dominó P del presente invento. Para emplear el circuito 800 de la fig. 8 como un enganche dominó P, es deseable acoplar el nodo 801 a una señal PH1B de reloj de enganche aproximadamente simétrica. En una realización, la señal PH1B de reloj de enganche exhibe un ciclo de trabajo desde un 40 por ciento a un 60 por ciento. A modo de perspectiva general, se ha resaltado que durante el período en el que PH1B es baja, se ha abierto una ventana de evaluación en la que a DB se le permite cambiar y la salida de QB sique a DB. Pero cuando PH1B adopta un valor alto, el estado de DB es retenido hasta que PH1B vuelve de nuevo a ser baja. Por tanto, en el instante T0, PH1B es alta y TOPB es baja precargada. El estado previo (es decir, el estado anterior a que PH1B sea baja) de DB es retenido a través de las señales QIIB, QIB, y a la salida QB. En el instante TI, PH1B vuelve de nuevo a ser baja, abriendo una ventana en la que el estado de DB es permitido que se propaque a través a la QB emitida. Como DB es alto durante esta ventana, la QB emitida permanece alta. En el instante T2, DB adopta un valor bajo haciendo que la señal TOPB se "descarque" a un nivel alto, activando así N2 y haciendo que la QB emitida adopte un valor bajo. Pero en el instante T3, PH1B de nuevo vuelve a ser alta, cerrando la ventana de evaluación y reteniendo el estado de DB, manteniendo así QB baja durante este semiciclo de PH1B. DB también adopta de nuevo un valor alto en T3, refleiando el estado de una etapa dominó precedente cuya salida está acoplada al nodo 803. TOPB se precarga baja en el instante T3, configurándose para la siguiente ventana de evaluación cuando PH1B adopta un valor baio en el instante T4. Como DB está alta en el instante T4. TOP no se descarga. Así en el instante T4, P2 y P3 están activados, produciendo QIIB alta y QIB baja. Debido a que tanto QIB como TOPB son bajas en T4, QB es producida alta. En el instante T5, debido a que DB está aun alta (es decir, la etapa dominó precedente no ha evaluado de tal forma que DB adoptó un valor bajo), TOPB permanece baja y el estado alto permanece en la QB emitida. En el instante T6, PH1B adopta de nuevo un valor alto, reteniendo en el estado de DB en la QB emitida durante el período en el que PH1B es baja.

10

15

20

Un experto en la técnica también apreciará que debido a que DB generalmente adopta un valor alto cuando PH1B adopta un valor alto, el dispositivo P1 puede ser eliminado del circuito 800 en una realización de enganche dominó P, que aumenta la velocidad del circuito 800.

Aunque el presente invento ha sido descrito en considerable detalle con referencia a algunas versiones preferidas del mismo, son posibles y se han contemplado otras versiones y variaciones. Además, aunque la presente exposición contempla una puesta en práctica usando dispositivos de tipo MOS, incluyendo dispositivos CMOS y similares, tales como, por ejemplo, transistores NMOS y PMOS, también puede aplicarse de una forma similar a tipos diferentes o análogos de tecnologías y topologías, tales como dispositivos bipolares o similares. Finalmente, los expertos en la técnica deberían apreciar que pueden usar fácilmente la concepción y realizaciones específicas descritas como una base para diseñar y modificar otras estructuras para proporcionar los mismos propósitos del presente invento definido por las reivindicaciones adjuntas.

#### **REIVINDICACIONES**

1. Un circuito de enganche (500) dominó N que comprende:

una etapa dominó (P1, N2, 301) acoplada a una señal (CLK) de reloj aproximadamente simétrica, y para evaluar una función lógica (301) de acuerdo con los estados de al menos una señal de datos y dicha señal de reloj aproximadamente simétrica, en el que dicha etapa dominó carga previamente un nodo (TOP) precargado cuando dicha señal de reloj aproximadamente simétrica es baja, y descarga dicho nodo precargado a un estado bajo si dicha función lógica realiza la evaluación cuando dicha señal de reloj aproximadamente simétrica es alta, y mantiene dicho nodo precargado alto si dicha función lógica falla la evaluación cuando dicha señal de reloj aproximadamente simétrica es alta, en el que un estado de enganche de al menos dicha señal de datos es proporcionado a dicha etapa dominó cuando dicha señal de reloj aproximadamente simétrica es alta, en el que dicha etapa dominó comprende:

un dispositivo (P1) de canal P que tiene una puerta acoplada a dicha señal de reloj aproximadamente simétrica, y una salida y una fuente acopladas entre una tensión fuente y dicho nodo precargado;

un dispositivo (N2) de canal N que tiene una puerta acoplada a dicha señal de reloj aproximadamente simétrica, una SALIDA acoplada a dicho nodo precargado y una fuente; y

una lógica de evaluación (301) acoplada entre masa y dicha fuente de dicho dispositivo de canal N;

una etapa de escritura (P2, N3, N4), acoplada a dicha etapa dominó y que responde a dicha señal de reloj aproximadamente simétrica, que lleva un primer nodo (QII) de salida preliminar a un valor alto si dicho nodo (TOP) precargado adopta un valor bajo y que lleva dicho primer nodo de salida preliminar a un valor bajo si dicho nodo precargado permanece alto;

un inversor (401) que tiene una entrada acoplada a dicho primer nodo de salida preliminar y una salida acoplada a un segundo nodo (QI) de salida preliminar;

un trayecto de mantenimiento alto (401, P3, P4) que mantiene dicho primer nodo (QI) de salida preliminar alto cuando está habilitado, en el que dicho trayecto de mantenimiento alto es habilitado cuando dicha señal de reloj aproximadamente simétrica y dicho segundo nodo de salida preliminar están ambos bajos y que, de otra manera, es inhabilitado;

un trayecto de mantenimiento bajo (401, N5) que mantiene dicho primer nodo (QI) de salida preliminar bajo cuando está habilitado, en el que dicho trayecto de mantenimiento bajo es habilitado cuando dicho segundo nodo de salida preliminar y dicho nodo precargado están ambos altos y que, de otro modo es inhabilitado; y

una etapa de salida (403) que proporciona una señal de salida (Q) basada en estados de dicho nodo precargado y de dicho segundo nodo de salida preliminar.

- 2. El circuito de enganche dominó N según la reivindicación 1, en el que dicha lógica de evaluación comprende una lógica de semiconductor de óxido metálico complementaria.

- 3. El circuito de enganche dominó N según la reivindicación 1, en el que dicha etapa de escritura comprende:

un primer dispositivo (P2) de canal P que tiene una puerta acoplada a dicho nodo precargado, y una salida y fuente acoplados entre una tensión de fuente y dicho primer nodo de salida preliminar:

un primer dispositivo (N3) de canal N que tiene una puerta que recibe dicha señal de reloj aproximadamente simétrica, una salida acoplada a dicho primer nodo de salida preliminar y una fuente; y

un segundo dispositivo (N4) de canal N que tiene una puerta acoplada a dicho nodo precargado, una salida acoplada a dicha fuente de dicho primer dispositivo de canal N y una fuente acoplada a masa.

- 4. El circuito de enganche dominó N según la reivindicación 3, en el que dicho trayecto de mantenimiento alto comprende:

- un segundo dispositivo (P3) de canal P que tiene una puerta acoplada a dicho segundo nodo (QI) de salida preliminar, una fuente acoplada a dicha tensión de fuente y una salida; y

- un tercer dispositivo (P4) de canal P que tiene una puerta que recibe dicha señal de reloj aproximadamente simétrica, y una salida y una fuente acopladas entre dicha salida de dicho segundo dispositivo (P3) de canal P y dicho primer nodo de salida preliminar.

- 5. El circuito de enganche dominó N según la reivindicación 4, en el que dicho trayecto de mantenimiento bajo comprende

13

5

10

15

20

25

30

35

40

45

dicho segundo dispositivo (N5) de canal N y un tercer dispositivo (N4) de canal N que tiene una puerta acoplada a dicho segundo nodo (QI) de salida preliminar, y una salida y una fuente acopladas entre dicho primer nodo de salida preliminar y dicha salida de dicho segundo dispositivo de canal N.

- 6. El circuito de enganche dominó N según la reivindicación 1, en el que dicha etapa de salida comprende una puerta NAND (403).

- 7. El circuito de enganche dominó N según la reivindicación 1, en el que dicha etapa dominó, dicha etapa de escritura, dicho inversor (401), dichos trayectos de mantenimiento alto y bajo y dicha lógica de salida están integrados usando un proceso de aislador sobre silicio de 90 nanómetros escalado.

- 8. Un método de enganchar una o más señales de datos de entrada (DATA), que comprende:

5

10

15

20

25

30

35

40

precargar un primer nodo (TOP) con un valor alto mientras una señal (CLK) de reloj aproximadamente simétrica sea baja;

cuando la señal de reloj aproximadamente simétrica sea alta, evaluar una función lógica (301) basada en una o más señales de datos de entrada para controlar el estado del primer nodo, comprendiendo dicha evaluación:

en primer lugar, acoplar una puerta de un dispositivo (P1) de canal P a la señal de reloj aproximadamente simétrica y, en segundo lugar, acoplar una salida y una fuente del dispositivo de canal P entre una tensión de fuente y el primer nodo;

en tercer lugar, acoplar una puerta de un dispositivo (N2) de canal N a la señal de reloj aproximadamente simétrica y, en cuarto lugar, acoplar una salida del dispositivo de canal N al primer nodo; y

en quinto lugar acoplar la lógica de evaluación (301) entre masa y una fuente del dispositivo de canal N;

controlar el estado de un segundo nodo (QII) con el estado del primer nodo (TOP) cuando la señal de reloj aproximadamente simétrica sea alta;

definir el estado de un tercer nodo (QI) como el estado invertido del segundo nodo;

habilitar un trayecto de mantenimiento de estado bajo para mantener el estado del segundo nodo bajo cuando los nodos primero y tercero tengan, ambos valor alto y, de otro modo, inhabilitar el trayecto de mantenimiento bajo;

habilitar un trayecto de mantenimiento de estado alto para mantener el estado del segundo nodo alto cuando la señal de reloj aproximadamente simétrica y el tercer nodo sean, ambos, bajos y, de otro modo, inhabilitar el trayecto de mantenimiento de estado alto; y

cuando la señal de reloj aproximadamente simétrica sea baja, retener el estado de un nodo de salida (Q) basado en los estados de los nodos primero (TOP) y tercero (QI).

- 9. El método de la reivindicación 8, en el que dicha evaluación de una función lógica para controlar el estado del primer nodo comprende llevar el primer nodo a un valor bajo cuando la función lógica (301) realiza la evaluación y mantener el primer nodo alto cuando la función lógica falla la evaluación.

- 10. El método de la reivindicación 9, en el que dicho control del estado de un segundo nodo con el estado del primer nodo comprende llevar el segundo nodo a un valor alto si el primer nodo ha adoptado un valor bajo y llevar el segundo nodo a un valor bajo si el primer nodo permanece alto cuando la señal de reloj aproximadamente simétrica adopta un valor alto.

- 11. El método de la reivindicación 8, en el que dicha habilitación de un trayecto de mantenimiento de estado bajo y de otro modo la inhabilitación del trayecto de mantenimiento de estado bajo comprende controlar los dispositivos primero y segundo (N4, N5) llevados a un valor bajo acoplados en serie con los nodos primero y tercero, respectivamente.

- 12. El método de la reivindicación 8, en el que dicha habilitación de un trayecto de mantenimiento de estado alto y de otro modo la inhabilitación del trayecto de mantenimiento de estado alto comprende controlar los dispositivos primero y segundo (P3, P4) llevados a un valor alto acoplados en serie con la señal de reloj aproximadamente simétrica y el tercer nodo, respectivamente.

- 45 13. El método de la reivindicación 8, en el que dicha determinación del estado de un nodo de salida (Q) comprende combinar lógicamente los estados de los nodos primero y tercero con una función NAND (403).

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 9

FIG. 10