OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 375 104

51 Int. CI.:

**G11B 20/18** (2006.01) **H03M 13/29** (2006.01) **H03M 13/15** (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- 96 Número de solicitud europea: 02746108 .6

- 96 Fecha de presentación: 16.07.2002

- Número de publicación de la solicitud: 1410390

Fecha de publicación de la solicitud: 21.04.2004

- 64) Título: MÉTODO DE GRABACIÓN DE DATOS Y MEDIO DE GRABACIÓN.

- (30) Prioridad: 19.07.2001 JP 2001220510

73) Titular/es:

PANASONIC CORPORATION 1006, OAZA KADOMA, KADOMA-SHI OSAKA 571-8501, JP

Fecha de publicación de la mención BOPI: 24.02.2012

72 Inventor/es:

TAKAGI, Yuji; USUI, Makoto y YABUNO, Hiroyuki

Fecha de la publicación del folleto de la patente: 24.02.2012

(74) Agente: Curell Aguilá, Mireia

ES 2 375 104 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

Método de grabación de datos y medio de grabación.

#### Campo técnico

5

La presente invención se refiere a un método de grabación de datos que se utiliza cuando se graban datos, tales como datos AV y datos informáticos, en un medio de grabación, tal como un DVD; el medio de grabación que almacena los datos; y a un aparato para reproducir los datos a partir del medio de grabación.

#### 10 Antecedentes de la técnica

Convencionalmente, se ha utilizado un código corrector de errores, tal como un código Reed-Solomon, para corregir errores en un medio de grabación, tal como un DVD, causados por defectos del medio o por polvo o arañazos en la superficie del disco.

15

Recientemente, en el campo de la grabación de vídeo digital, se han llevado a cabo investigaciones con el objetivo de producir los DVD de próxima generación, dotados de una densidad más elevada y una mayor capacidad que los DVD convencionales. En dichas investigaciones, cuando se incrementa la densidad del medio de grabación, surge la necesidad de reducir la influencia de los errores de ráfaga debidos al polvo o los arañazos.

20

Para satisfacer dicha necesidad, se ha propuesto un método de grabación en, por ejemplo, el documento de Kouhei Yamamoto *et al.*, "Error Modeling and Performance Analysis of Error-Correcting Codes for the Digital Video Recording System" (parte del simposio internacional conjunto sobre memoria óptica y almacenamiento óptico de datos, 1999 - Koloa, Hawaii - julio de 1999, vol. SPIE 3864, pp. 339-341). En este método, se entrelazan dos códigos correctores de errores para aumentar de ese modo la capacidad de corrección de los errores de ráfaga.

25

En la publicación japonesa abierta al público nº 2000-40307, se da a conocer en detalle otro método de grabación de datos, en el que se entrelazan dos o más códigos correctores de errores.

30

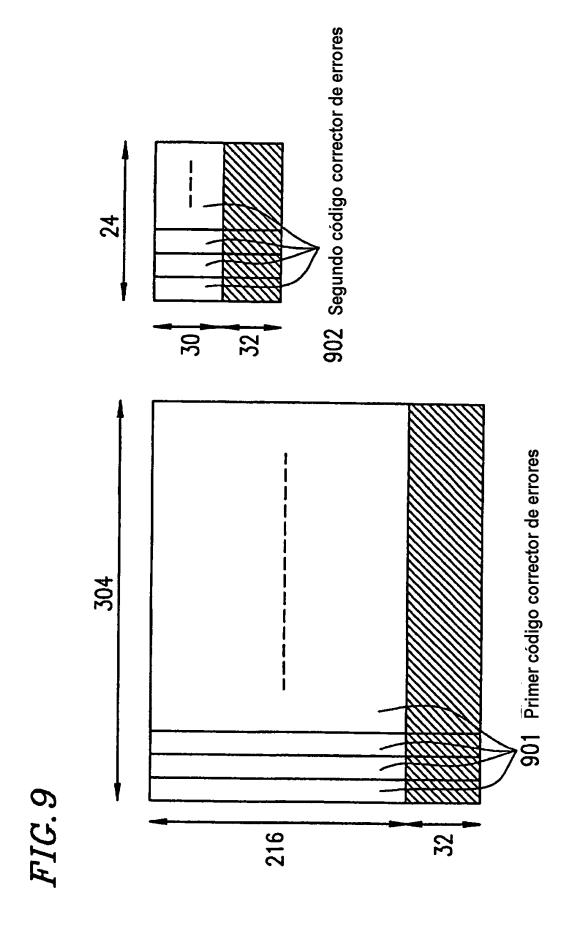

La figura 9 es un diagrama esquemático que representa una estructura convencional de los códigos correctores de errores del documento de Yamamoto et al.

35

Como se representa en la figura 9, se dividen aproximadamente 64 Kbytes de datos de usuario en 304 columnas, denominadas "partes de información", de 216 bytes cada una. Se añaden 32 bytes de paridad a cada parte de información para generar un primer código corrector de errores 901. El primer código corrector de errores 901 se codifica utilizando códigos Reed-Solomon en el campo finito GF (256). Un símbolo de componente es el elemento mínimo que constituye un código y tiene una longitud de 1 byte.

40

La capacidad de corrección del primer código corrector de errores 901 se evalúa de la forma indicada a continuación.

En general, se establece la siguiente condición:

$d \ge 2 \times t + 1$

45

en la que d representa la distancia mínima entre cada código y t representa el posible número de correcciones.

50

Cada primer código corrector de errores 901 contiene 32 bytes de paridad. La distancia mínima entre dos primeros códigos correctores de errores es de 33. Por lo tanto, según la relación descrita anteriormente, el primer código corrector de errores 901 tiene capacidad para corregir cualquier error (byte) hasta un máximo de 16 en la longitud de código de 248 (bytes).

55

Si en el proceso de corrección se conoce la posición del error, la información de la posición conocida del error puede utilizarse para realizar una corrección mediante supresión. La corrección por supresión es un método en el que cuando se somete un determinado código a una operación de corrección y se conoce de antemano el símbolo de componente (unidad mínima de un código) erróneo, se supone que el símbolo de componente se ha suprimido y el símbolo de componente suprimido se calcula a partir de los símbolos de componente restantes. Cuando se conocen las posiciones de error, la corrección por supresión puede aumentar la capacidad de corrección en un factor de hasta 2.

60

Esto puede expresarse mediante la relación siguiente:

$d \ge 2 \times t + e + 1$

en la que d representa la distancia mínima entre cada código y t representa el número de correcciones y e

representa el número de correcciones por supresión.

5

10

25

30

35

40

45

60

65

Si en el caso del primer código corrector de errores 901, en el que la distancia mínima d = 33, todas las correcciones se realizan mediante corrección por supresión (es decir, t = 0), se podrán corregir hasta 32 símbolos de componente (bytes) (e = 32).

Como se representa en la figura 9, se divide una cantidad de datos de control de 720 bytes en 24 columnas de 30 bytes cada una, denominadas "partes de información". Se añaden 32 bytes de paridad a cada parte de información para generar un segundo código corrector de errores 902. El segundo código corrector de errores 902 se codifica utilizando códigos Reed-Solomon en el campo finito GF (256). Un símbolo de componente es el elemento mínimo que constituye un código y tiene una longitud de 1 byte. Debe observarse que los datos de control de 720 bytes contienen información de dirección y de otro tipo que se utiliza cuando los datos de usuario se graban finalmente en un disco óptico.

Cada segundo código corrector de errores 902 contiene también 32 bytes de paridad. La distancia mínima entre dos segundos códigos correctores de errores 902 es de 33, como en el primer código corrector de errores 901. Por consiguiente, el segundo código corrector de errores 902 tiene la capacidad de corregir cualquier error (byte) de un máximo de 16 en la longitud de código de 62 (bytes). El número de correcciones del segundo código corrector de errores 902 es igual al del primer código corrector de errores 901 (16 (bytes)). Sin embargo, puesto que el segundo código corrector de errores 902, la capacidad de corrección del segundo código corrector de errores 902 es superior a la del primer código corrector de errores 901.

De esta manera, se forman los primeros códigos correctores de errores 901 y los segundos códigos correctores de errores 902, y a continuación se entrelazan con una señal de sincronización 903 para generar flujos de datos que a su vez se graban en un medio de grabación.

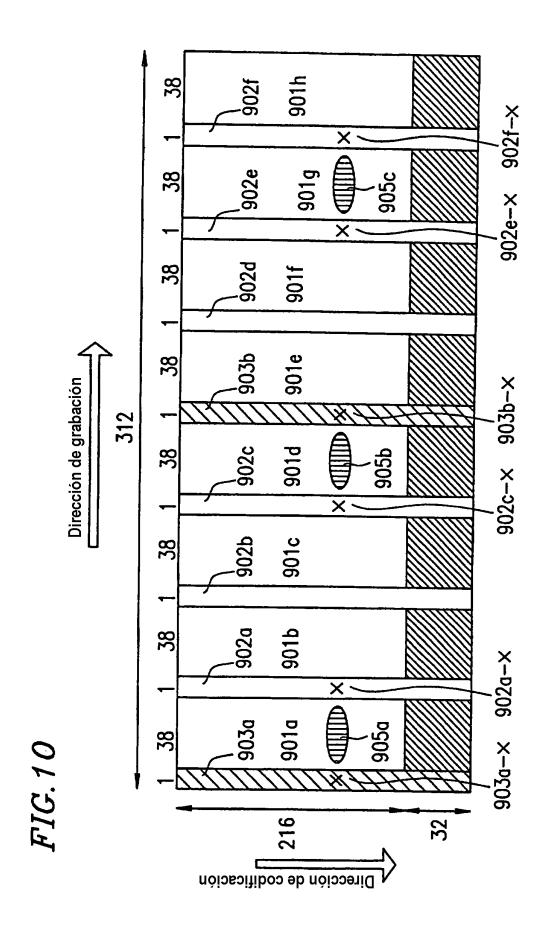

La figura 10 representa una estructura de flujo de datos en la que los primeros códigos correctores de errores 901 y los segundos códigos correctores de errores 902 convencionales representados en la figura 9 se entrelazan con una señal de sincronización conforme a una regla de entrelazado predeterminada.

En la figura 10, las referencias 901a a 901h indican unos primeros códigos correctores de errores, las referencias 902a a 902f indican segundos códigos correctores de errores y las referencias 903a y 903b son señales de sincronización. Los símbolos de componente que constituyen los códigos y las señales de sincronización se graban de tal forma que quedan dispuestos en una matriz de 312 columnas x 248 filas y entrelazados en la dirección de las filas. Cada código se codifica en la dirección de las columnas (dirección vertical) y debe grabarse en la dirección de las filas (dirección horizontal), con lo cual se obtiene una estructura resistente a los errores de ráfaga. En el ejemplo convencional, se añade una señal de sincronización de 1 byte por cada 155 bytes (=38+1+38+1+38+1+38 bytes). Los 156 bytes constituyen una trama. El flujo de datos presenta la denominada estructura de tramas. La señal de sincronización se utiliza para sincronizar de byte en byte los datos de una trama e indicar la posición de la trama en la totalidad del flujo de datos (el bloque de datos). La señal de sincronización se utiliza también para realizar la sincronización al principio de la reproducción o la resincronización cuando se produce una pérdida de bits por deriva de reloi o una causa similar. Con esta finalidad, la señal de sincronización presenta un patrón, que no puede generarse mediante demodulación en el momento en que finalmente se graba el flujo de datos en un disco óptico, y una señal de patrón predeterminada que comprende un número de trama e información similar. El aparato de reproducción determina si el patrón reproducido por el aparato de reproducción es idéntico o no a un correspondiente patrón predeterminado que debería haberse grabado, causando de ese modo la activación de la señal de sincronización.

Como se observa en la estructura de datos de la figura 10, se interponen 38 bytes de símbolos de componente en cada primer código corrector de errores, entre una señal de sincronización de 1 byte y un símbolo de componente de 1 byte de un segundo código corrector de errores o entre los símbolos de componente de 1 byte de dos segundos códigos correctores de errores. La razón entre el número de columnas que presentan una señal de sincronización y el número de columnas que presentan símbolos de componente de un segundo código corrector de errores es 1:3.

Es posible generar marcas de supresión que facilitan información de posición de error para la corrección por supresión, dependiendo de si se detecta o no un error en una señal de sincronización o los símbolos de componente de un segundo código corrector de errores, basándose en el resultado de la detección de una señal de sincronización o el resultado de corrección de errores mediante un segundo código corrector de errores que presenta una capacidad de corrección superior a la del primer código corrector de errores.

Por ejemplo, se supone que al someter un segundo código corrector de errores a corrección de errores se detecta un error en los símbolos de componente de dos segundos códigos correctores de errores consecutivos 902e y 902f (902e-x y 902f-x en la figura 10) y que se efectúa una corrección de errores. En este caso, la posibilidad de que se produzca un error en los símbolos de componente de 38 bytes del primer código corrector de errores 901g interpuestos entre los símbolos de componente de los segundos códigos correctores de errores 902e-x y 902f-x se considera que es alta (es decir, se supone que se produce un error de ráfaga). En este caso, se genera una marca

de supresión 905c para el símbolo de componente del primer código corrector de errores 901g.

Análogamente, por ejemplo, para los símbolos de componente de 38 bytes del primer código corrector de errores 901a interpuestos entre la señal de sincronización 903a y los símbolos de componente del segundo código corrector de errores 902a, y los símbolos de componente de 38 bytes del primer código corrector de errores 901d interpuestos entre los símbolos de componente del segundo código corrector de errores 902c y la señal de sincronización 903b, se detecta un error en el resultado de la corrección de errores del segundo código corrector de errores o el resultado de la detección de sincronización para detectar o no una señal de sincronización y, mediante el resultado, se generan marcas de supresión para los símbolos de componente de los primeros códigos correctores de errores 901a y 901d. En la figura 10, se representa la generación de una marca de supresión 905a como consecuencia de la detección de errores en 903a-x y 902a-x, y la generación de una marca de supresión 905b como consecuencia de la detección de errores en 902c-x y 903b-x.

Como se ha descrito anteriormente, las marcas de supresión pueden utilizarse para realizar la corrección por supresión, con lo cual es posible mejorar la capacidad de corrección (el número de correcciones) en un factor de hasta 2. Por lo tanto, puede alcanzarse un excelente nivel de resistencia a los errores de ráfaga debidos a arañazos o polvo.

En el ejemplo convencional descrito anteriormente, el resultado de la corrección de errores de los segundos códigos correctores de errores o el resultado de la detección de la señal de sincronización se utiliza para generar una correspondiente marca de supresión.

La detección de errores mediante un segundo código corrector de errores es diferente de la detección de errores mediante la señal de sincronización desde el punto de vista de la capacidad de detección de errores, debido a la diferencia entre los métodos de detección. La detección de errores mediante una señal de sincronización presenta una capacidad de detección mucho más elevada que la detección de errores mediante un segundo código corrector de errores

En el ejemplo convencional, el segundo código corrector de errores presenta una capacidad de corrección más elevada que la del primer código corrector de errores, aunque la capacidad de corrección es solo de 16 (bytes) de 62 (bytes). Por consiguiente, cuando se produce una cantidad de errores (en bytes) igual a 17 o más en 62 (bytes), no es posible corregir los errores. En este caso, no es posible utilizar una marca de supresión para indicar la posición del error.

- La detección de errores mediante una señal de sincronización puede realizarse mediante una simple comparación bit a bit entre la señal de sincronización reproducida y la señal de sincronización antes de ser reproducida. Aunque se produzca una cantidad de errores (en bytes) igual a 17 o más (por ejemplo, en 62 bytes) en una señal de sincronización, es posible detectar todos los errores.

- 40 Por consiguiente, en el ejemplo convencional, los mismos primeros códigos correctores de errores presentan diferentes fiabilidades de corrección de errores, dependiendo de la posición del primer código corrector de errores en el flujo de datos, es decir, de cómo está entrelazado el primer código corrector de errores con uno o más segundos códigos correctores de errores y/o una o más señales de sincronización. En particular, un primer código corrector de errores interpuesto entre los símbolos de componente de dos segundos códigos correctores de errores que presentan una capacidad de detección más baja es menos fiable que otro primer código corrector de errores interpuesto entre una señal de sincronización y un segundo código corrector de errores, debido a la capacidad de detección de errores.

- Cuando coexisten fiabilidades altas y bajas, la fiabilidad del conjunto se ve limitada por la fiabilidad más baja. En el ejemplo convencional, es muy probable que se alcance un estado de error, tal como el de incapacidad de reproducción de los datos, en un primer código corrector de errores interpuesto entre los símbolos de componente de dos segundos códigos correctores de errores que tienen una fiabilidad inferior y una capacidad de detección de errores inferior.

- La presente invención está destinada a resolver los problemas descritos anteriormente. El objetivo de la presente invención es proporcionar un método de grabación de datos, un medio de grabación y un aparato de reproducción, cuya capacidad de corrección general se incrementa eliminando la diferencia en la fiabilidad de detección de errores dependiente de la posición del primer código corrector de errores en el flujo de datos, es decir, de cómo los primeros códigos correctores de errores se entrelazan con los segundos códigos correctores de errores y las señales de sincronización, y por medio de los cuales puede llevarse a cabo una reproducción sumamente fiable.

### Exposición de la invención

5

10

25

65

La presente invención proporciona un método de grabación de datos que comprende las etapas de codificación de los datos de usuario en primeros códigos correctores de errores que presentan una primera capacidad de corrección, codificación de información de control en segundos códigos correctores de errores que presentan una

segunda capacidad de corrección superior a la primera capacidad de corrección, generación de un flujo de datos que contiene el primer código corrector de errores, el segundo código corrector de errores y las señales de sincronización, en el que los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los primeros códigos correctores de errores, y grabación del flujo de datos. Por lo tanto, el objetivo descrito anteriormente puede alcanzarse.

La presente invención también proporciona un medio de grabación, que almacena un flujo de datos que contiene unos primeros códigos correctores de errores obtenidos codificando los datos de usuario, unos segundos códigos correctores de errores obtenidos codificando información de control y unas señales de sincronización, en los que los primeros códigos correctores de errores presentan una primera capacidad de corrección, los segundos códigos correctores de errores presentan una segunda capacidad de corrección superior a la primera capacidad de corrección y, en el flujo de datos, los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los primeros códigos correctores de errores. Por lo tanto, el objetivo descrito anteriormente puede alcanzarse.

15

20

10

5

La presente invención proporciona también un aparato de reproducción para reproducir el flujo de datos grabado en el medio de grabación, comprendiendo el aparato una sección de reproducción para generar datos binarios a partir del flujo de datos, una sección de demodulación para demodular los datos binarios en los primeros códigos correctores de errores y los segundos códigos correctores de errores, en el que la sección de demodulación comprende una sección de detección de señales de sincronización, y una sección de corrección de errores para detectar un error en los primeros códigos correctores de errores y los segundos códigos correctores de errores obtenidos en la sección de demodulación y corregir el error, en el que la sección de corrección de errores comprende una sección de generación de marcas de supresión para el primer código corrector de errores para realizar la corrección por supresión basándose en el resultado de la corrección de errores del segundo código corrector de errores y el resultado de la detección de señales de sincronización, y una sección de corrección por supresión para utilizar la marca de supresión para realizar la corrección por supresión. Por lo tanto, el objetivo descrito anteriormente puede alcanzarse.

25

30

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta las señales de sincronización en un tiempo diferente del tiempo previsto, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores en una posición del flujo de datos anterior a la señal de sincronización.

35

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta la señal de sincronización en un tiempo diferente del tiempo previsto, y se detecta un error en un símbolo de componente del segundo código corrector de errores en la posición anterior más cercana a la señal de sincronización en el flujo de datos, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores en una posición del flujo de datos anterior a la señal de sincronización.

40

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta la señal de sincronización en un tiempo diferente del tiempo previsto, y no se detecta ningún error en un símbolo de componente del segundo código corrector de errores en la posición anterior más cercana a la señal de sincronización en el flujo de datos, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores entre el segundo código corrector de errores y la señal de sincronización.

45

50

En una forma de realización de la presente invención, la sección de detección de señales de sincronización cuenta el número de ciclos de reloj y bits reproducidos desde el tiempo de detección de la señal de sincronización y, basándose en el resultado del recuento, predice el tiempo de detección de la siguiente señal de sincronización.

55

La presente invención provee también un circuito corrector de errores para utilizar en el aparato de reproducción, que comprende una sección de generación de marcas de supresión para el primer código corrector de errores, que genera una marca de supresión para la corrección por supresión basándose en el resultado de la corrección de errores del segundo código corrector de errores y el resultado de detección de la señal de sincronización, y una sección de corrección por supresión para utilizar la marca de supresión en la corrección por supresión. Por lo tanto, el objetivo descrito anteriormente puede alcanzarse.

60

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta la señal de sincronización en un tiempo diferente del tiempo previsto, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores en una posición del flujo de datos anterior a la señal de sincronización.

65

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta la señal de sincronización en un tiempo diferente del tiempo previsto y se detecta un error en un símbolo de componente del segundo código corrector de errores en la posición anterior más cercana a la señal de

sincronización en el flujo de datos, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores en una posición del flujo de datos anterior a la señal de sincronización.

En una forma de realización de la presente invención, cuando la sección de detección de señales de sincronización detecta la señal de sincronización en un tiempo diferente del tiempo previsto y no se detecta ningún error en un símbolo de componente del segundo código corrector de errores en la posición anterior y más cercana a la señal de sincronización en el flujo de datos, la sección de generación de marcas de supresión coloca una marca de supresión en un símbolo de componente del primer código corrector de errores entre el segundo código corrector de errores y la señal de sincronización.

En una forma de realización de la presente invención, la sección de detección de señales de sincronización cuenta el número de ciclos de reloj y bits reproducidos desde el tiempo de detección de la señal de sincronización y, basándose en el resultado del recuento, predice el tiempo de detección de la siguiente señal de sincronización.

#### Breve descripción de los dibujos

15

20

35

40

65

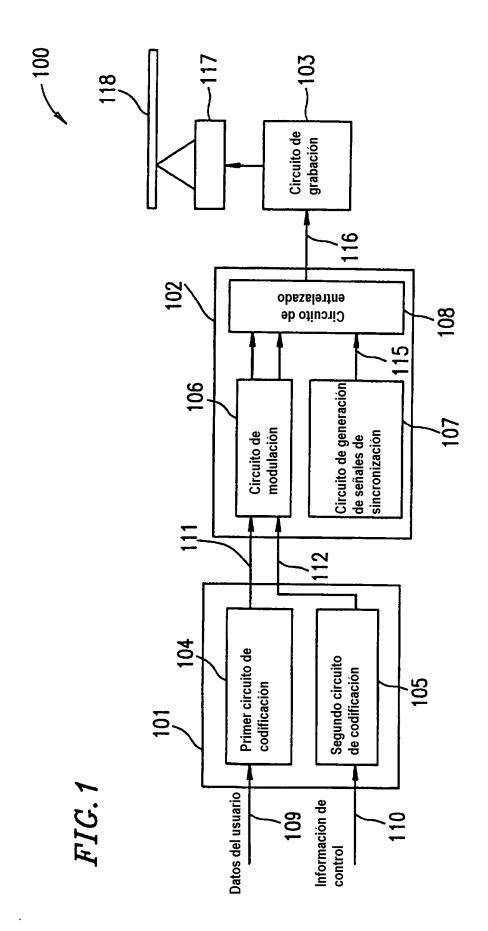

La figura 1 es un diagrama esquemático que representa la estructura de un aparato de grabación para grabar datos en un medio de grabación según la presente invención.

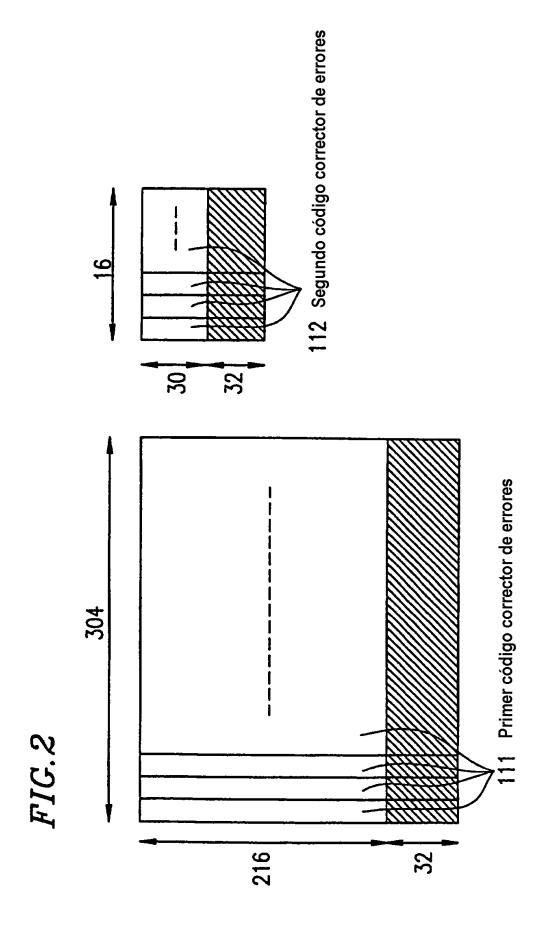

La figura 2 es un diagrama esquemático que presenta unos primeros códigos correctores de errores y unos segundos códigos correctores de errores antes de ser entrelazados mediante un método según la presente invención.

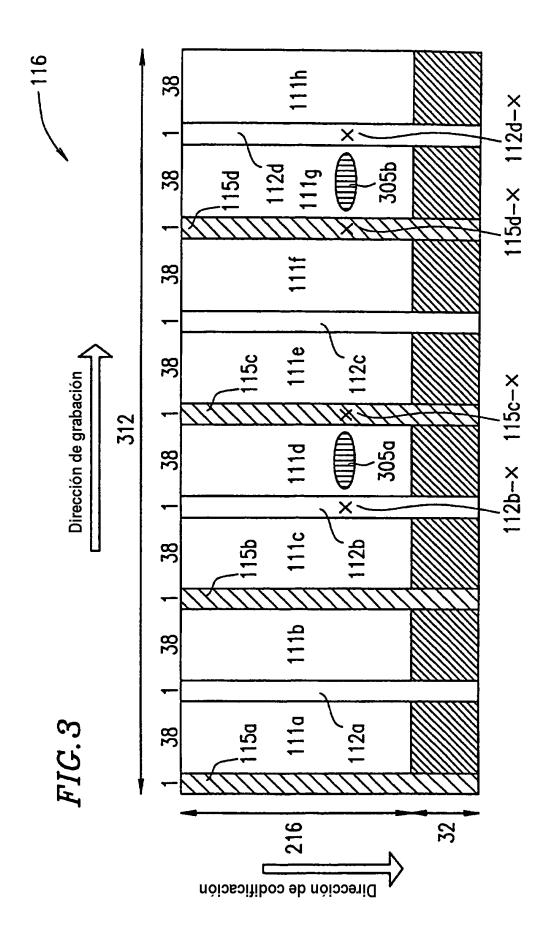

- La figura 3 es un diagrama que representa una estructura de datos de un flujo de datos, en el que los primeros códigos correctores de errores y los segundos códigos correctores de errores representados en la figura 2 se entrelazan con señales de sincronización según una norma de entrelazado predeterminada.

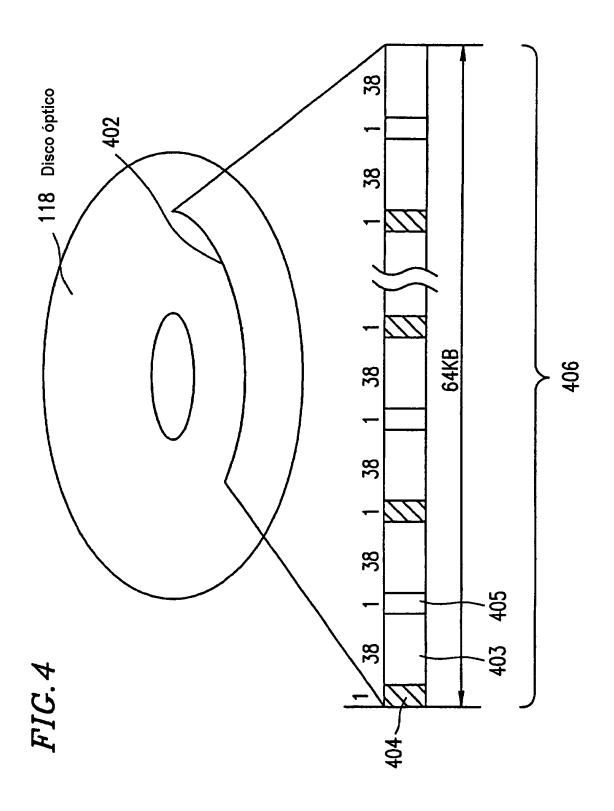

- La figura 4 es un diagrama que representa una estructura de datos grabada en una pista en espiral o concéntrica de 30 un disco óptico según la presente invención.

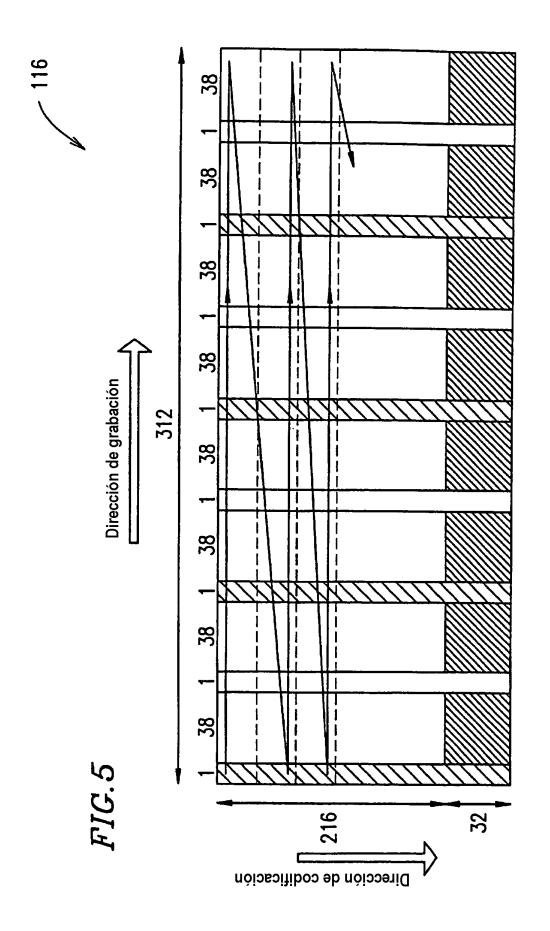

- La figura 5 es un diagrama que representa el orden de grabación de un flujo de datos según la presente invención.

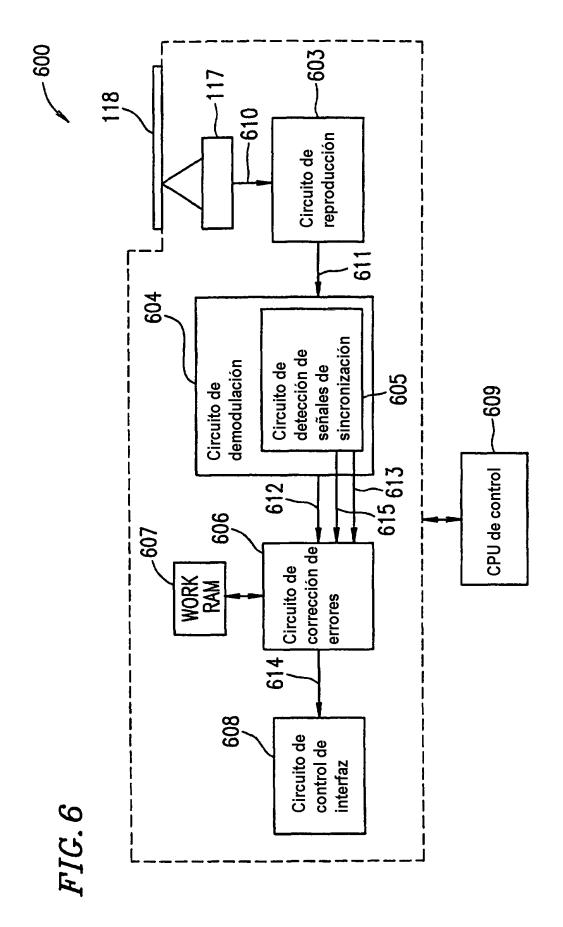

- La figura 6 es un diagrama esquemático que representa un aparato de reproducción según la presente invención.

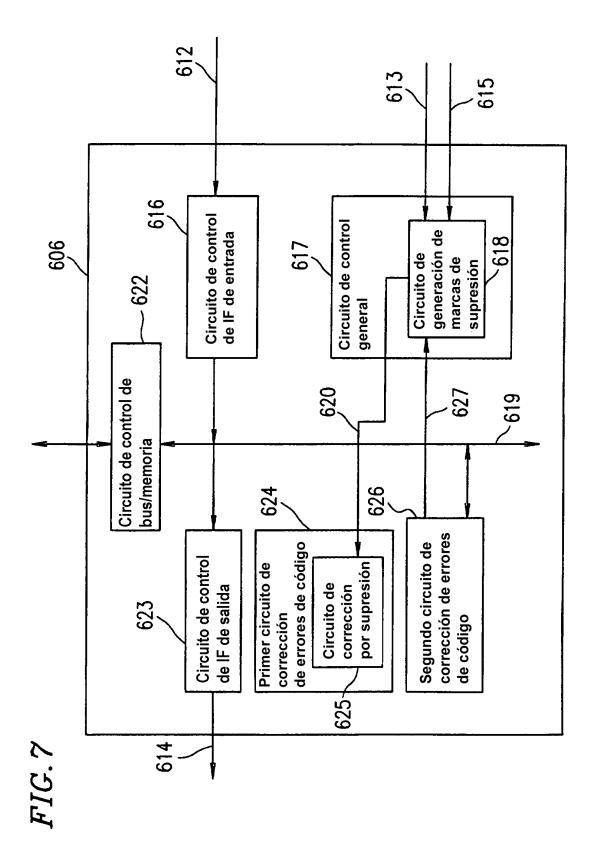

- La figura 7 es un diagrama que representa en detalle el circuito de corrección de errores representado en la figura 6.

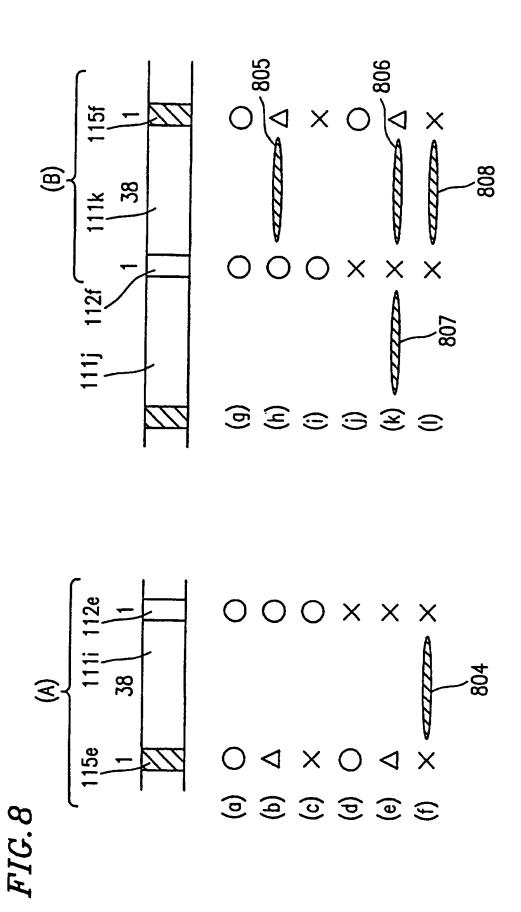

- La figura 8 es un diagrama que representa un algoritmo que describe una regla para generar una marca de supresión.

- La figura 9 es un diagrama esquemático que representa una estructura de un código corrector de errores convencional.

- La figura 10 es un diagrama que representa una estructura de datos de un flujo de datos convencional, en la que los primeros códigos correctores de errores y los segundos códigos correctores de errores representados en la figura 9 se entrelazan con señales de sincronización según una regla de entrelazado predeterminada.

### Mejor modo de poner en práctica la invención

- 50 En lo sucesivo, la presente invención se describirá por medio de ejemplos ilustrativos con referencia a los dibujos adjuntos.

- La figura 1 es un diagrama esquemático que representa la estructura de un aparato de grabación 100 para grabar datos en un medio de grabación. Los ejemplos de medio de grabación comprenden discos ópticos, discos magnéticos y discos magneto-ópticos, aunque no se limitan a estos. La presente invención puede aplicarse a cualquier medio de grabación. En los ejemplos siguientes se emplea un disco óptico.

- El aparato de la grabación 100 comprende un codificador 101, un modulador 102 y un circuito de grabación 103. El codificador 101 puede comprender un primer circuito de codificación 104 y un segundo circuito de codificación 105.

El modulador 102 comprende un circuito de modulación 106, un circuito de generación de señales de sincronización 107 y un circuito de entrelazado 108.

- Los datos del usuario 109 se introducen en el primer circuito de codificación 104. La información de control 110 se introduce en el segundo circuito de codificación 105. Los datos del usuario 109 son datos binarios. Los ejemplos de datos de usuario 109 comprenden datos AV, datos de texto y datos de programa de aplicación. La información de control 110 es información utilizada para controlar los datos de usuario 109. Los ejemplos de información de control

110 comprenden información de dirección e información de administración de derechos de autor (información de permiso de copia, información de clave de encriptación, etc.).

El primer circuito de codificación 104 genera unos primeros códigos correctores de errores 111 a partir de los datos de usuario 109 y los envía al circuito de modulación 106 del modulador 102. Análogamente, el segundo circuito de codificación 105 genera unos segundos códigos correctores de errores 112 a partir de la información de control 110 y los envía al circuito de modulación 106 del modulador 102. Se supone que el primer código corrector de errores 111 presenta una primera capacidad de corrección y que el segundo código corrector de errores 105 presenta una segunda capacidad de corrección superior a la primera capacidad de corrección. El circuito de modulación 106 modula opcionalmente el primer código corrector de errores 111 y el segundo código corrector de errores 112, y envía los códigos resultantes al circuito de entrelazado 108. El circuito de generación de señales de sincronización 107 genera una señal de sincronización 115 para corregir las pérdidas de bits por deriva del reloj o problemas similares, y envía la señal de sincronización 115 al circuito de entrelazado 108. El circuito de entrelazado 108 genera un flujo de datos 116 que contiene los primeros códigos correctores de errores 111, los segundos códigos correctores de errores 112 y las señales de sincronización 115, en el que los primeros códigos correctores de errores 111 están entrelazados alternadamente con los segundos códigos correctores de errores 112 y las señales de sincronización 115, y envía el flujo de datos 116 al circuito de grabación 103. El circuito de la grabación 103 recibe el flujo de datos 116 desde el circuito de entrelazado 108 y lo graba en un disco óptico 118 mediante un cabezal óptico 117.

20

25

5

10

15

Como se ha descrito, el aparato de grabación 100 de la presente invención genera un flujo de datos 116 que contiene los primeros códigos correctores de errores 111, los segundos códigos correctores de errores 112 y las señales de sincronización 115, en el que los primeros códigos correctores de errores 111 están entrelazados alternadamente con los segundos códigos correctores de errores 112 y las señales de sincronización 115, y graba el flujo de datos 116 en el disco óptico 118.

A continuación, se describirá una estructura de datos generada en el transcurso de la grabación de los datos de usuario 109 y la información de control 110 por el aparato de grabación 100 de la presente invención en el disco óptico 108, con referencia a figuras 2 a 4.

30

La figura 2 es un diagrama esquemático que representa los primeros códigos correctores de errores 111 y los segundos códigos correctores de errores 112 antes de ser entrelazados.

35

Se dividen aproximadamente 64 Kbytes de datos de usuario en 304 columnas de 216 bytes cada una, denominadas "partes de información". Se añaden 32 bytes de paridad a cada parte de información para generar un primer código corrector de errores 111. El primer código corrector de errores 111 se codifica utilizando códigos Reed-Solomon en el campo finito GF (256). Un símbolo de componente es el elemento mínimo que constituye un código y tiene una longitud de 1 byte. La dirección de codificación del primer código corrector de errores 111 es la dirección de las columnas (dirección vertical).

40

La capacidad de corrección del primer código corrector de errores 111 se evalúa de la forma indicada a continuación.

En general, se establece la siguiente condición:

45

50

$d \ge 2 \times t + 1$

en la que d representa la distancia mínima entre cada código y t representa el número de correcciones posibles. Cada primer código corrector de errores 111 contiene 32 bytes de paridad. La distancia mínima entre dos primeros códigos correctores de errores es de 33. Por lo tanto, según la relación descrita anteriormente, el primer código corrector de errores 111 tiene capacidad para corregir cualquier error (byte) hasta un máximo de 16 en la longitud de código de 248 (bytes).

Si en el proceso de corrección se conoce la posición del error, la información de la posición conocida del error puede utilizarse para realizar la corrección mediante supresión. La corrección por supresión es un método en el que, cuando se somete un determinado código a una operación de corrección y se conoce de antemano un símbolo de componente (unidad mínima de un código) erróneo, se supone que el símbolo de componente se suprime y el símbolo de componente suprimido se calcula a partir de los símbolos de componente restantes. Cuando se conocen las posiciones de error, la corrección por supresión puede aumentar la capacidad de corrección en un factor de hasta 2.

Esto puede expresarse mediante la relación siguiente:

$d \ge 2 \times t + e + 1$ ,

65

en la que d representa la distancia mínima entre cada código, t representa el número de correcciones y e representa

el número de correcciones por supresión.

5

10

25

30

35

40

45

50

55

60

65

Si en el caso del primer código corrector de errores 111, en el que la distancia mínima d = 33, todas las correcciones se realizan mediante corrección por supresión (es decir, t = 0), se podrán corregir hasta 32 símbolos de componente (bytes) (e = 32).

Como se representa en la figura 2, se divide una cantidad de datos de control de 480 bytes en 16 columnas de 30 bytes cada una, denominadas "partes de información". Se añaden 32 bytes de paridad a cada parte de información para generar un segundo código corrector de errores 112. El segundo código corrector de errores 112 se codifica utilizando códigos Reed-Solomon en el campo finito GF (256). Un símbolo de componente es el elemento mínimo que constituye un código y tiene una longitud de 1 byte. Debe observarse que los datos de control de 480 bytes contienen información de dirección y de otro tipo que se utiliza cuando los datos de usuario se graban finalmente en un disco óptico.

Cada segundo código corrector de errores 112 contiene también 32 bytes de paridad. La distancia mínima entre dos segundos códigos correctores de errores 112 es de 33, como en el primer código corrector de errores 111. Por consiguiente, el segundo código corrector de errores 112 presenta la capacidad de corregir cualquier error (byte) de un máximo de 16 en la longitud de código de 62 (bytes). El número de correcciones del segundo código corrector de errores 112 es igual al del primer código corrector de errores 111 (16 (bytes)). Sin embargo, puesto que el segundo código corrector de errores 112 tiene una longitud de código más corta que la del primer código corrector de errores 111, la capacidad de corrección del segundo código corrector de errores 112 es superior a la del primer código corrector de errores 111.

Los primeros códigos correctores de errores 111 y los segundos códigos correctores de errores 112 se construyen de esta manera. En la presente invención, el aparato de grabación 100 entrelaza alternadamente los primeros códigos correctores de errores 111 con los segundos códigos correctores de errores 112 y la señal de sincronización 115 para generar el flujo de datos 116 que, a su vez, se graba en el disco óptico 118.

La figura 3 representa una estructura del flujo de datos entrelazados 116.

En la figura 3, las referencias 111a a 111h indican los primeros códigos correctores de errores, las referencias 112a a 112d indican los segundos códigos correctores de errores y las referencias 115a a 115d indican las señales de sincronización. Los símbolos de componente que constituyen los códigos y las señales de sincronización se graban de tal forma que se distribuyen en una matriz de 312 columnas x 248 filas y se entrelazan en la dirección de las filas. Cada código se codifica en la dirección de las columnas (dirección vertical) y debe grabarse en la dirección de las filas (dirección horizontal), para obtener de ese modo una estructura resistente a los errores de ráfaga. En este ejemplo, se añade una señal de sincronización de 1 byte por cada 77 bytes (=38+1+38+bytes). Los 78 bytes constituyen una trama. El flujo de datos presenta la denominada estructura de tramas. La señal de sincronización se utiliza para sincronizar de byte en byte los datos de una trama e indicar la posición de una trama en el conjunto del flujo de datos (bloque de datos). La señal de sincronización se utiliza también para realizar la sincronización al principio de la reproducción o la resincronización cuando se produce una pérdida de bits por deriva de reloj o una causa similar. Con esta finalidad, la señal de sincronización presenta un patrón, que no puede generarse mediante demodulación en el momento de grabar finalmente el flujo de datos en un disco óptico, y una señal de patrón predeterminado que comprende un número de trama e información similar. El aparato de reproducción determina si el patrón reproducido por el aparato de reproducción es idéntico o no a un correspondiente patrón predeterminado que debería haberse grabado, causando de ese modo la activación de la señal de sincronización. Debe observarse que, aunque la longitud de la señal de sincronización es de un byte en este ejemplo, la longitud de la señal de sincronización no se limita necesariamente a un byte, sino que puede ser de cualquier valor dependiendo del método de modulación u otras consideraciones.

Como se observa en la estructura de datos de la figura 3, siempre se interponen símbolos de componente de 38 bytes en cada primer código corrector de errores entre una señal de sincronización de 1 byte y un símbolo de componente de 1 byte de un segundo código corrector de errores. La razón entre el número de columnas que presentan una señal de sincronización y el número de columnas que presentan símbolos de componente de un segundo código corrector de errores es 1:1. Es posible generar marcas de supresión que facilitan información de posición de error para la corrección por supresión, dependiendo de si se detecta o no un error en una señal de sincronización o los símbolos de componente de un segundo código corrector de errores, basándose en el resultado de la detección de sincronización de una señal de sincronización o el resultado de la corrección de errores mediante un segundo código corrector de errores que presenta una capacidad de corrección superior a la de los primeros códigos correctores de errores.

Por ejemplo, se supone que no se detecta un elemento 115d-x de la señal de sincronización 115d y que se detecta un error en un símbolo de componente 112d-x del segundo código corrector de errores 112d durante la corrección de errores del segundo código corrector de errores 112d. En este caso, la posibilidad de que se produzca un error en los símbolos de componente de 38 bytes del primer código corrector de errores 111g interpuestos entre el elemento 115d-x y el símbolo de componente 112d-x se considera que es alta (es decir, se supone que se produce

un error de ráfaga). En este caso, se genera una marca de supresión 305b para el símbolo de componente del primer código corrector de errores 111g.

Asimismo, por ejemplo, se supone que se detecta un error en un símbolo de componente 112b-x del segundo código corrector de errores 112b durante la corrección de errores del segundo código corrector de errores 112b, y que no se detecta un elemento 115c-x de la señal de sincronización115c. En este caso, la posibilidad de que se produzca un error en los símbolos de componente de 38 bytes del primer código corrector de errores 111d interpuestos entre el símbolo de componente112b-x y el elemento 115c-x se considera que es alta (es decir, se supone que se produce un error de ráfaga). En este caso, se genera una marca de supresión 305a para el símbolo de componente del primer código corrector de errores 111d.

5

10

15

20

25

30

35

40

45

55

60

65

Como se ha descrito anteriormente, en la presente invención, siempre se interpone en un flujo de datos un primer código corrector de errores entre una señal de sincronización de 1 byte y un símbolo de componente de 1 byte de un segundo código corrector de errores. Por consiguiente, todos los primeros códigos correctores de errores pueden someterse a la misma detección de errores. Entonces, la presente invención permite soslayar el problema convencional descrito anteriormente, en el que la precisión de la detección de errores varía dependiendo de la posición del primer código corrector de errores en un flujo de datos, es decir, de cómo se entrelaza el primer código corrector de errores con el segundo código corrector de errores y la señal de sincronización en el flujo de datos, y como consecuencia del cual la fiabilidad global del flujo de datos fluctúa.

Como se ha descrito anteriormente, las marcas de supresión pueden utilizarse para realizar la corrección por supresión, con lo cual es posible mejorar la capacidad de corrección (el número de correcciones) en un factor de hasta 2. Por lo tanto, puede obtenerse un excelente nivel de resistencia a los errores de ráfaga debidos a arañazos o polvo en la superficie del medio de grabación.

Cuando se genera una marca de supresión a partir de una señal de sincronización, se puede utilizar una función de resincronización si se produce una pérdida de bits por deriva de reloj (una función intrínseca de la señal de sincronización) para generar una marca de supresión con mayor precisión. Por ejemplo, si durante la reproducción se detecta una señal de sincronización y ésta se reproduce en una posición que presenta un desplazamiento de varios ciclos de reloj respecto de la posición normal, se añaden marcas de supresión solo a los símbolos de componente de un primer código corrector de errores grabado en una posición del flujo de datos anterior a la señal de sincronización, en lugar de realizar la resincronización. Esto es debido al hecho de que es probable que los datos situados en una posición del flujo de datos anterior a una señal de sincronización reproducida sean erróneos como consecuencia de una pérdida de sincronización, y que los datos que ocupan una posición posterior a la señal de sincronización no sean erróneos.

Las expresiones "añadir una marca de supresión" o "generar una marca de supresión" hacen referencia a la acción de adjuntar, al símbolo de componente, una marca que indica que es posible suprimir un símbolo de componente (es decir, se puede producir un error en el símbolo de componente). La adición de una marca de supresión se realiza, por ejemplo, de la forma indicada a continuación. Se prepara un mapa de bits de 248 x 304 bits en el que se asigna un bit a cada símbolo de la totalidad de los primeros códigos correctores de errores de un bloque de datos (que comprende símbolos de componentes de 248 x 304 bits). Se representa la adición de una marca de supresión mediante la asignación del valor 1 a un correspondiente bit. Cuando no se añade ninguna marca de supresión, se asigna el valor 0 a un correspondiente bit.

Aunque en este caso la longitud de la señal de sincronización es de 1 byte, dicha longitud puede variar dependiendo del formato de modulación u otras características similares.

Tanto el primer código corrector de errores como el segundo código corrector de errores pueden contener cualquier número de símbolos de componente.

La capacidad de detección de errores mediante una señal de sincronización es más alta que la detección de errores en la que se determina si se ha producido o no un error en cada byte. Se coloca una señal de sincronización que presenta una alta capacidad de detección en una posición adyacente, ya sea anterior o posterior, a cada uno de los primeros códigos correctores de errores que presentan una longitud unitaria de 38 bytes. Por consiguiente, puede obtenerse un método de grabación de datos sumamente fiable.

Como se ha descrito anteriormente, en el método de grabación de datos de la presente invención, el aparato de grabación genera un flujo de datos que contiene unos primeros códigos correctores de errores, unos segundos códigos correctores de errores y unas señales de sincronización, en el que los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los primeros códigos correctores de errores, y el flujo de datos se graba en un medio de grabación. De esta forma, pues, se puede aplicar la misma detección de errores a todos los primeros códigos correctores de errores. Por consiguiente, la precisión de la detección de errores no varía en función de la posición del primer código corrector de errores en el flujo de datos entrelazado con el segundo código corrector de errores y las señales de sincronización, y de ese modo los primeros códigos correctores de errores pueden presentar una alta fiabilidad en todo el flujo de datos.

La figura 4 representa cómo se graban los datos 406 en una pista en espiral o concéntrica 402 del disco óptico 118. Los datos 406 contienen una parte 403 del primer código corrector de errores, una parte 405 del segundo código corrector de errores y una parte 404 de la señal de sincronización. Los datos 406 se obtienen dividiendo el flujo de datos 116 (figura 3) en 248 filas en la dirección de las filas (dirección horizontal) e interconectando las filas por contigüidad. Este sistema se describirá más adelante con referencia a la figura 5.

5

10

15

25

30

35

40

45

50

55

60

La figura 5 es un diagrama que representa el orden de grabación del flujo de datos 116. El flujo de datos 116 dividido en 248 filas en la dirección de las filas se graba en el disco óptico 118 en el orden indicado mediante las flechas representadas en la figura 5. Debe observarse que el orden de grabación del flujo de datos dividido 116 no se limita al del sistema representado en la figura 5, sino que el flujo de datos dividido 116 puede grabarse en el disco óptico 118 en cualquier orden.

La grabación del disco óptico 118 en sí se realiza con cavidades convexas y cóncavas, puntos de densidad variable de un material de cambio de fase o elementos similares. Durante la grabación, habitualmente se someten los datos codificados a modulación digital mediante códigos de modulación, tales como códigos de modulación 8/16 o RLL (1,7), antes de grabarlos en la pista de un disco. Debe tenerse en cuenta que en la figura 4 se omite la descripción de la modulación mediante códigos de modulación para simplificar, y que los datos codificados se graban tal cual.

En el disco óptico 118, los datos 406 se graban en el orden siguiente: una parte 404 de la señal de sincronización (1 byte), una parte 403 del primer código corrector de errores (38 bytes), una parte 405 del segundo código corrector de errores (1 byte), una parte 403 del primer código corrector de errores (1 byte), ..., y así sucesivamente. Es decir, las partes 405 del segundo código corrector de errores y las partes 404 de las señales de sincronización se entrelazan alternadamente con las partes 403 de los primeros códigos correctores de errores.

Por lo tanto, en el caso del disco óptico de la presente invención, los datos se disponen de tal forma que los símbolos de componente de los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los símbolos de componente de los primeros códigos correctores de errores, y los datos se graban en el disco óptico. Por esta razón, cuando dicho disco óptico se reproduce, es posible aplicar la misma detección de errores a todos los símbolos de componente de los primeros códigos correctores de errores. Por consiguiente, la precisión de la detección de errores no varía en función de la posición del primer código corrector de errores en el flujo de datos entrelazado con el segundo código corrector de errores y las señales de sincronización, y de ese modo los primeros códigos correctores de errores pueden presentar una alta fiabilidad en todo el flujo de datos.

Debe tenerse en cuenta que el disco óptico de la presente invención no se limita a un disco óptico grabado mediante el método de la presente invención (es decir, el método en el que se utiliza el aparato de grabación 100 representado en la figura 1), sino que puede ser un disco grabado mediante cualquier método, siempre y cuando los datos grabados en el disco óptico presenten la estructura de datos descrita anteriormente.

La figura 6 es un diagrama esquemático que representa una estructura de un aparato de reproducción 600 según la presente invención. El aparato de reproducción 600 reproduce los datos grabados en el disco óptico 118 de la presente invención. Se supone en este caso que los datos grabados en el disco óptico 118 presentan la estructura de datos 406 representada en la figura 4.

El aparato de reproducción 600 comprende un circuito de reproducción (sección de reproducción) 603 para reproducir los datos grabados en el disco óptico 118 y generar datos binarios 611, un circuito de demodulación (sección de demodulación) 604 para demodular los datos binarios 611 en primeros códigos correctores de errores y segundos códigos correctores de errores y un circuito de corrección de errores (sección de corrección de errores) 606 para detectar y corregir un error en los primeros códigos correctores de errores y los segundos códigos correctores de errores generados por el circuito de demodulación 604.

El circuito de demodulación 604 comprende un circuito de detección de señales de sincronización (sección de detección de señales de sincronización) 605 para generar un resultado de detección de señal de sincronización.

El circuito de corrección de errores 606 comprende un circuito de generación de marcas de supresión (sección de generación de marcas de supresión) para generar una marca de supresión, que se utiliza en la corrección por supresión, para el primer código corrector de errores, basándose en un resultado de la corrección de errores del segundo código corrector de errores o un resultado de la detección de la señal de sincronización, y un circuito de corrección por supresión (sección de corrección por supresión) para utilizar la marca de supresión y realizar la corrección por supresión. Estos circuitos se describen a continuación. El circuito de corrección de errores 606 detecta y corrige errores en el medio de grabación, debidos a arañazos, polvo o causas similares, y genera datos corregidos 614, de los cuales se han eliminado los errores.

65 El aparato de reproducción 600 puede comprender además un cabezal óptico 117 para leer los datos del disco óptico 118, una WORK RAM 607 para utilizar durante el funcionamiento del circuito de corrección de errores 606, un

circuito de control de interfaz 608 para controlar un protocolo, tal como el protocolo SCSI o ATAPI, y una CPU de control 609. El cabezal óptico 117 puede comprender un láser de semiconductores y un elemento óptico. El circuito de control de interfaz 608 lleva a cabo el control de la interfaz para transmitir datos de usuario reproducidos a un ordenador personal o un dispositivo similar. La CPU de control 609 controla todo el aparato de reproducción 600.

5

10

15

20

25

45

50

55

60

65

En el aparato de reproducción de la presente invención con la estructura descrita, los datos del disco óptico 118 se reproducen mediante el método indicado a continuación.

Inicialmente, se emite un rayo láser de un láser de semiconductores, a través del cabezal óptico 117, para irradiar el disco óptico 118. El haz de láser se refleja en el disco óptico 118, y la señal de luz reflejada 610 se somete, en el circuito de reproducción 603, a conversión en señal analógica, amplificación y conversión en valores binarios, y se transmite como datos binarios 611 al circuito de demodulación 604. El circuito de demodulación 604 demodula digitalmente una señal modulada en la grabación (señal de modulación digital, por ejemplo, modulación 8/16 o RLL (1.7)). Los datos demodulados digitalmente 612 se transmiten al circuito de corrección de errores 606, en el que se detectan y corrigen errores debidos a arañazos, polvo o causas similares en el medio con ayuda de la WORK RAM 607. En este caso, los datos demodulados 612 contienen unos primeros códigos correctores de errores y unos segundos códigos correctores de errores. En el circuito de demodulación 604, el circuito de detección de señales de sincronización 605 detecta una señal de sincronización, analizando de bit en bit la señal de sincronización de los datos binarios 611, y realiza la resincronización en caso de que los datos pierdan la sincronización con los ciclos de reloj debido a una pérdida de bits por deriva de reloj o una causa similar. El circuito de detección de señales de sincronización 605 predice el tiempo de detección de la siguiente señal de sincronización contando el número de ciclos de reloj o el número de bytes desde la señal de sincronización actual, hallándose dicha señal de sincronización actual en una posición en el flujo de datos anterior a la siguiente señal de sincronización. Cuando se detecta una señal de sincronización en un tiempo diferente del tiempo previsto y esta se somete a corrección de sincronización, se transmite una señal de corrección de sincronización 613 al circuito de corrección de errores 606. Cuando no se detecta ninguna señal de sincronización alrededor del tiempo previsto, se transmite una señal de sincronización no detectada 615 al circuito de corrección de errores 606.

El circuito de corrección de errores 606 decodifica los primeros códigos correctores de errores y los segundos códigos correctores de errores. Cuando se aplica la corrección de errores al primer código corrector de errores, se utiliza el resultado de la corrección de errores del segundo código corrector de errores, la señal de corrección de sincronización 613 y la señal de sincronización no detectada 615 para generar una marca de supresión que facilita información de posición de los errores. La marca de supresión se utiliza en la corrección por supresión.

En el método de corrección, se emplean códigos Reed-Solomon conocidos, por ejemplo. Los datos sometidos a corrección de errores 614 se transmiten a través del circuito de control de interfaz 608 a un ordenador principal o dispositivo similar (no representado). La CPU de control 609 controla el conjunto de operaciones para la reproducción.

40 La figura 7 es un diagrama que representa en particular la estructura del circuito de corrección de errores 606 representado en la figura 6.

En la figura 7, el circuito de corrección de errores 606 comprende un circuito de generación de marcas de supresión (sección de generación de marcas de supresión) 618 para generar una marca de supresión para la corrección por supresión del primer código corrector de errores, basándose en el resultado de la corrección de errores del segundo código corrector de errores y el resultado de la detección de la señal de sincronización, y un circuito de corrección por supresión (sección de corrección por supresión) 625 para realizar la corrección de errores mediante la marca de supresión.

El circuito de corrección de errores 606 puede comprender además un circuito de control de bus/memoria 622 para controlar la grabación y la reproducción de la WORK RAM 607, y un bus interno 619, un circuito de control de IF de salida 623 para generar los datos de usuario 614 después de la corrección de errores, un primer circuito de corrección de errores de código 624 para decodificar el primer código corrector de errores que codifica los datos de usuario, y un segundo circuito de corrección de errores de código 626 para decodificar el segundo código corrector de errores que contiene información de control codificada. El circuito de control de IF de salida 623 realiza la negociación de establecimiento de comunicación con el circuito de control de interfaz 608. El primer circuito de corrección de errores de código 624 realiza la corrección de errores en cada una de las columnas del primer código corrector de errores, que contiene 216 bytes de datos y 32 bits de paridad adicionales. En la corrección de errores, la marca de supresión 620 que indica la posición de un error puede utilizarse para realizar la corrección de errores de hasta 32 bytes para un solo código. El circuito de corrección por supresión 625 realiza la corrección por supresión. El segundo circuito de corrección de errores de código 626 corrige el segundo código corrector de errores que contiene 30 bytes de datos y 32 bytes de paridad adicionales, pudiéndose realizar la corrección de errores en un máximo de 16 bytes para un solo código. El primer circuito de corrección de errores de código 624, el segundo circuito de corrección de errores de código 626 y el circuito de corrección por supresión 625 descritos anteriormente pueden estar provistos de un circuito de corrección de errores, en el que se emplean códigos Reed-Solomon conocidos o similares.

El circuito de corrección de errores 606 puede comprender además un circuito de control de IF de entrada 616 para realizar el control de la IF con el circuito de demodulación 604, y un circuito de control general 617 para controlar todo el circuito de corrección de errores 606, que comprende un microcontrolador o un dispositivo similar. Los datos demodulados 612 introducidos en el circuito de control de IF de entrada 616 se almacenan, por medio del circuito de control del bus/memoria 622, en la WORK RAM 607. El circuito de control general 617 genera la marca de supresión 620 basándose en la posición de error 627 del segundo código corrector de errores del segundo circuito de corrección de errores de código 626, la señal de corrección de sincronización 613 y la señal de sincronización no detectada 615, y la transmite al circuito de corrección por supresión 625.

10

A continuación, se describirá una operación del circuito de corrección de errores 606 con la estructura mencionada anteriormente.

15

Los datos demodulados 612 reproducidos y demodulados desde el medio de grabación se almacenan en la WORK RAM 607 por medio del circuito de control de IF de entrada 616 y el circuito de control de bus/memoria 622. Se decodifica el primer código corrector de errores y el segundo código corrector de errores de los datos almacenados.

20

Para la decodificación, el segundo circuito de corrección de errores de código 626 decodifica en primer lugar el segundo código corrector de errores. El segundo circuito de corrección de errores de código 626 obtiene la posición del error 627 mediante la decodificación y la transmite al circuito de generación de marcas de supresión 618.

25

El circuito de generación de marcas de supresión 618 genera la marca de supresión 620 basándose en la señal de corrección de sincronización 613 y la señal de sincronización no detectada 615, introducidas al mismo tiempo en que se facilitan de antemano los datos demodulados 612 del circuito de demodulación 604 al circuito de control de IF de entrada 616 conforme a una regla predeterminada descrita a continuación, y transmite la marca de supresión 620 al circuito de corrección por supresión 625 del primer circuito de corrección de errores de código 624.

El primer circuito de corrección de errores de código 624 y el circuito de corrección por supresión 625 aplican la corrección por supresión al primer código corrector de errores basándose en la marca de supresión 620.

30

Una vez terminada la corrección de errores, los datos de usuario 614 de los cuales se han suprimido los errores se transmiten al circuito de control de interfaz 608, por medio del circuito de control de IF de salida 623.

35

El circuito de control general 617 y el circuito de generación de marcas de supresión 618 que comprenden un microcontrolador o un dispositivo similar pueden ejecutar el control descrito anteriormente de la totalidad del circuito de corrección de errores 606 o la generación de marcas de supresión 620. La ejecución puede también ser llevada a cabo mediante software o un simple circuito lógico.

40

La figura 8 es un diagrama que representa un algoritmo que describe una regla para generar una marca de supresión. Conforme a la regla de generación representada en la figura 8, se genera una marca de supresión 420 mediante software o un simple circuito lógico.

45

En la figura 8, se clasifica una secuencia de datos reproducidos según el resultado de la detección de una señal de sincronización o la presencia o ausencia de un error en los símbolos de componente de un segundo código corrector de errores. En la figura 8, O indica la detección normal de la señal de sincronización o la ausencia de un error en los símbolos de componente del segundo código corrector de errores durante la corrección de errores, X indica la no detección de la señal de sincronización o la presencia de un error en los símbolos de componente del segundo código corrector de errores durante la corrección de errores. Δ indica que se ha detectado una señal de sincronización en un tiempo desplazado respecto del tiempo previsto desde la señal de sincronización previa situada en una posición anterior en el flujo de datos, γ se realiza una corrección de la sincronización.

50

En la figura 8, 115e y 115f indican señales de sincronización, 111i, 111j y 111k indican símbolos de componente de primeros códigos correctores de errores y 112e y 112f indican símbolos de componente de segundos códigos correctores de errores. (A) a la izquierda de la figura 8 representa una regla para generar una marca de supresión para el símbolo de componente 111i del primer código corrector de errores, cuando la señal de sincronización 115e, el símbolo de componente 111i del primer código corrector de errores y el símbolo de componente 112e del segundo código corrector de errores se disponen en este orden. (B) a la derecha de la figura 8 representa una regla para generar una marca de supresión para los símbolos de componente 111j y 111k del primer código corrector de errores, cuando el símbolo de componente 112f del segundo código corrector de errores, el símbolo de componente 111k del primer código corrector de errores y la señal de sincronización 115f se disponen en este orden.

60

55

#### [Caso (A) a la izquierda de la figura 8]

65

(a) Cuando se detecta la señal de sincronización 115e de la forma habitual y no se detecta ningún error en el símbolo de componente 112e del segundo código corrector de errores, no se añade ninguna marca de supresión al símbolo de componente 111i del primer código corrector de errores.

- (b) Cuando se detecta la señal de sincronización 115e en un tiempo desplazado respecto del tiempo previsto desde la señal de sincronización previa situada en una posición anterior del flujo de datos y no se detecta ningún error en el símbolo de componente 112e del segundo código corrector de errores, no se añade ninguna marca de supresión al símbolo de componente 111i del primer código corrector de errores.

- (c) Cuando no se detecta la señal de sincronización 115e y no se detecta ningún error en el símbolo de componente 112e del segundo código corrector de errores, no se añade ninguna marca de supresión al símbolo de componente 111i del primer código corrector de errores.

- (d) Cuando se detecta la señal de sincronización 115e de la forma habitual y se detecta un error en el símbolo de componente 112e del segundo código corrector de errores, no se añade ninguna marca de supresión al símbolo de componente 111i del primer código corrector de errores.

- (e) Cuando se detecta la señal de sincronización 115e en un tiempo desplazado respecto del tiempo previsto desde la señal de sincronización previa situada en una posición anterior del flujo de datos y se detecta un error en el símbolo de componente 112e del segundo código corrector de errores, no se añade ninguna marca de supresión al símbolo de componente 111i del primer código corrector de errores.

- 20 (f) Cuando no se detecta la señal de sincronización 115e y se detecta un error en el símbolo de componente 112e del segundo código corrector de errores, se supone que se produce un error de ráfaga y se añade una marca de supresión 804 al símbolo de componente 111i del primer código corrector de errores.

### [Caso (B) a la derecha de la figura 8]

5

10

25

35

- (g) Cuando no se detecta ningún error en el símbolo de componente 112f del segundo código corrector de errores y se detecta la señal de sincronización 115f de la forma habitual, no se añade ninguna marca de supresión al símbolo de componente 111k del primer código corrector de errores.

- (h) Cuando no se detecta ningún error en el símbolo de componente 112f del segundo código corrector de errores y se detecta la señal de sincronización 115f en un tiempo desplazado respecto del tiempo previsto desde la señal de sincronización previa situada en una posición anterior del flujo de datos, se supone que se produce un error de ráfaga debido a una pérdida de bits por deriva de reloj y se añade una marca de supresión 805 al símbolo de componente 111k del primer código corrector de errores.

- (i) Cuando no se detecta ningún error en el símbolo de componente 112f del segundo código corrector de errores y no se detecta la señal de sincronización 115f, no se añade ninguna marca de supresión al símbolo de componente 111k del primer código corrector de errores.

- 40 (j) Cuando se detecta un error en el símbolo de componente 112f del segundo código corrector de errores y se detecta la señal de sincronización 115f de la forma habitual, no se añade ninguna marca de supresión al símbolo de componente 111k del primer código corrector de errores.

- (k) Cuando se detecta un error en el símbolo de componente 112f del segundo código corrector de errores y se detecta la señal de sincronización 115f en un tiempo desplazado respecto del tiempo previsto desde la señal de sincronización previa situada en una posición anterior del flujo de datos, se supone que se produce un error de ráfaga debido a una pérdida de bits por deriva de reloj y se añaden unas marcas de supresión 806 y 807 a los símbolos de componente 111k y 111j del primer código corrector de errores.

- (I) Cuando se detecta un error en el símbolo de componente 112f del segundo código corrector de errores y no se detecta la señal de sincronización 115f, se supone que se produce un error de ráfaga y se añade una marca de supresión 808 al símbolo de componente 111k del primer código corrector de errores.

- Conforme a las reglas descritas en los casos (A) y (B), se generan las marcas de supresión. Las marcas de supresión generadas se utilizan para someter el primer código corrector de errores a corrección por supresión, permitiendo aumentar la capacidad de corrección en un factor de hasta 2. Para todos los primeros códigos correctores de errores, se generan marcas de supresión independientemente de la posición del primer código corrector de errores en el flujo de datos, es decir, de cómo los primeros códigos correctores de errores se entrelazan con los segundos códigos correctores de errores y las señales de sincronización, pero sólo en función del resultado de la detección de la señal de sincronización y el resultado de la detección de errores de los símbolos de componente del segundo código corrector de errores.

- Como se ha descrito anteriormente, en el aparato de reproducción de la presente invención, pueden generarse de igual manera marcas de supresión para todos los primeros códigos correctores de errores, mediante la detección de errores de la señal de sincronización y los símbolos de componente de los segundos códigos correctores de errores. Por consiguiente, la precisión de la detección de errores no varía en función de la posición del primer código

corrector de errores en el flujo de datos, entrelazado con el segundo código corrector de errores y las señales de sincronización, y de ese modo los primeros códigos correctores de errores pueden presentar una alta fiabilidad en todo el flujo de datos.

#### 5 Aplicabilidad industrial

10

15

Como se ha descrito anteriormente, en el método de grabación de datos, el medio de grabación y el aparato de grabación de la presente invención, se genera un flujo de datos que contiene unos primeros códigos correctores de errores, unos segundos códigos correctores de errores y unas señales de sincronización, en el que los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los primeros códigos correctores de errores, y el aparato de grabación graba el flujo de datos en el medio de grabación. De esta forma, pues, puede aplicarse la misma detección de errores de ráfaga a todos los primeros códigos correctores de errores. Por consiguiente, la fiabilidad no varía según el sistema de entrelazado, y de ese modo puede garantizarse una alta fiabilidad de corrección de errores en todo el flujo de datos. Por lo tanto, con la presente invención, el método de grabación de datos, el disco óptico y el aparato de reproducción presentan cada uno de ellos un alto grado de fiabilidad.

#### **REIVINDICACIONES**

- 1. Método de grabación de datos, que comprende las etapas siguientes:

- codificar los datos de usuario (109) en unos primeros códigos correctores de errores (111) que presentan una primera capacidad de corrección;

- codificar la información de control (110) en unos segundos códigos correctores de errores (112) que presentan una segunda capacidad de corrección superior a la primera capacidad de corrección;

- generar un flujo de datos (116) que contiene el primer código corrector de errores (111), el segundo código corrector de errores (112) y unas señales de sincronización (115), en el que los segundos códigos correctores de errores y las señales de sincronización se entrelazan alternadamente con los primeros códigos correctores de errores; y

- grabar el flujo de datos (116).

5

15

- Medio de grabación (118) que almacena un flujo de datos (116) que contiene unos primeros códigos correctores de errores (111) obtenidos mediante la codificación de los datos de usuario, unos segundos códigos correctores de errores (112) obtenidos mediante la codificación de la información de control y unas señales de sincronización, en el que:

- los primeros códigos correctores de errores (111) presentan una primera capacidad de corrección;

- los segundos códigos correctores de errores (112) presentan una segunda capacidad de corrección superior a la primera capacidad de corrección; y

- en el flujo de datos (116), los segundos códigos correctores de errores (112) y las señales de sincronización (115) se entrelazan alternadamente con los primeros códigos correctores de errores (111).