(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 375 424**

(51) Int. Cl.:

**G11C 11/16** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Número de solicitud europea: **08745261 .1**

(96) Fecha de presentación: **07.04.2008**

(97) Número de publicación de la solicitud: **2137734**

(97) Fecha de publicación de la solicitud: **30.12.2009**

(54) Título: **MEMORIA MAGNETORRESISTIVA POR PAR DE TRANSFERENCIA DE ESPÍN DE ACCESO ALEATORIO Y PROCEDIMIENTOS DE DISEÑO.**

(30) Prioridad:

05.04.2007 US 910255 P

11.01.2008 US 972674

(73) Titular/es:

QUALCOMM INCORPORATED

ATTN: INTERNATIONAL IP ADMINISTRATION

5775 MOREHOUSE DRIVE

SAN DIEGO, CALIFORNIA 92121, US

(45) Fecha de publicación de la mención BOPI:

**29.02.2012**

(72) Inventor/es:

JUNG, Seong-ook;

SANI, Mehdi, Hamidi;

KANG, Seung H. y

YOON, Sei Seung

(45) Fecha de la publicación del folleto de la patente:

**29.02.2012**

(74) Agente: **Carpintero López, Mario**

**ES 2 375 424 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio y procedimientos de diseño

### Reivindicación de prioridad a tenor de 35 U.S.C. §119

5 La presente solicitud de patente reivindica prioridad con respecto a la solicitud provisional nº 60/910.255, titulada "SPIN TRANSFER TORQUE MAGNETORESISTIVE RANDOM ACCESS MEMORY WITH REDUCED READ VOLTAGE", presentada el 5 de abril de 2007.

### Campo de la revelación

10 Las realizaciones de la invención versan acerca de la memoria de acceso aleatorio (RAM). Más en particular, las realizaciones de la invención versan acerca de la memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM).

### Antecedentes

15 La memoria de acceso aleatorio (RAM) es un componente omnipresente de las arquitecturas digitales modernas. La RAM puede consistir en dispositivos dedicados o puede estar integrada o incorporada dentro de dispositivos que usan la RAM, como microprocesadores, microcontroladores, circuitos integrados para aplicaciones específicas (ASIC), dispositivos de integración de sistema en un chip (SoC) y otros dispositivos similares, como será apreciado por los expertos en la técnica. La RAM puede ser volátil o no volátil. La RAM volátil pierde su información almacenada cada vez que se quita la alimentación eléctrica. La RAM no volátil puede mantener su contenido de memoria aunque se quite la alimentación eléctrica de la memoria. Aunque la RAM no volátil tiene ventajas en la capacidad de mantener su contenido sin que se aplique energía eléctrica, la RAM no volátil convencional tiene tiempos de lectura / escritura más lentos que los de la RAM volátil.

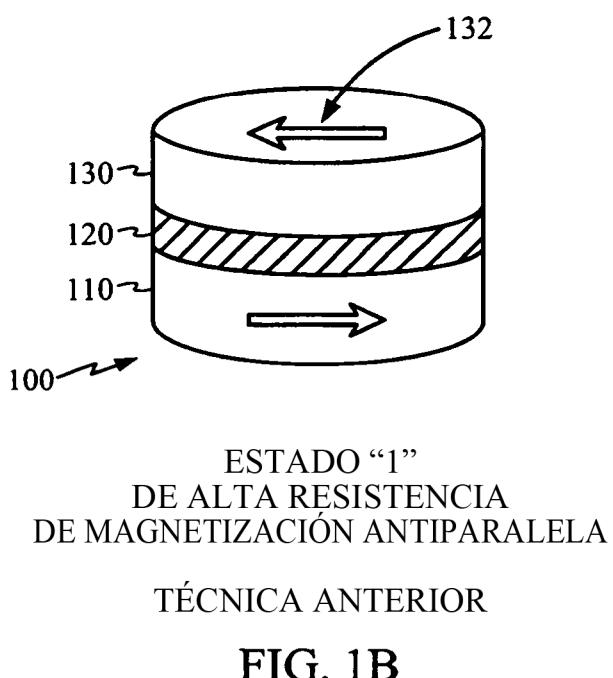

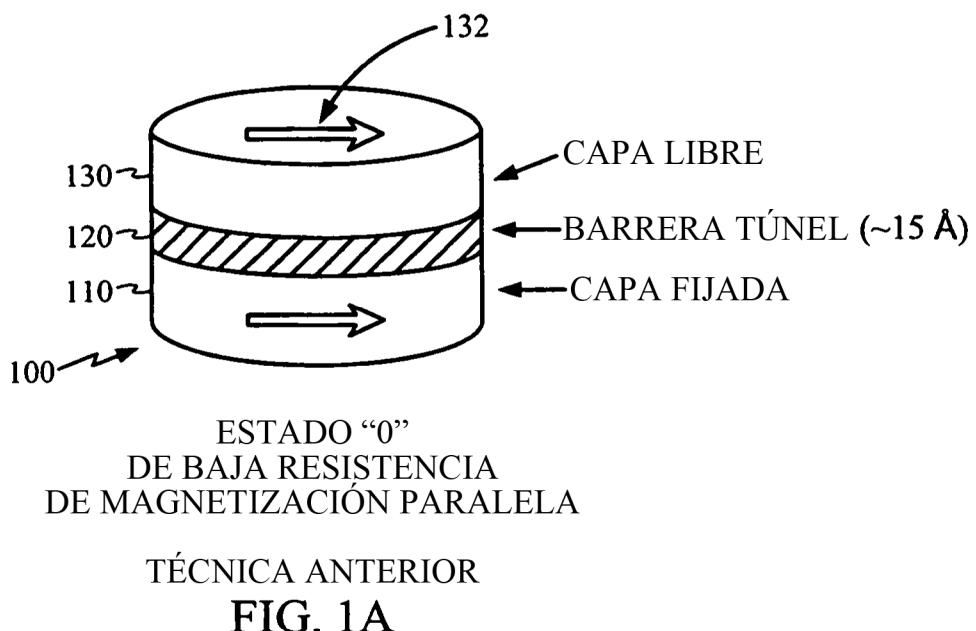

20 La memoria magnetoresistiva de acceso aleatorio (MRAM) es una tecnología de memoria no volátil que tiene tiempos de respuesta (lectura / escritura) comparables a los de la memoria volátil. A diferencia de las tecnologías de RAM convencional que almacenan datos como cargas eléctricas o flujos de corriente, la MRAM usa elementos magnéticos. Según se ilustra en las Figuras 1A y 1B, puede formarse un elemento 100 de almacenamiento de unión de túnel magnético (MTJ) a partir de dos capas magnéticas 110 y 130, cada una de las cuales puede mantener un campo magnético, separadas por una capa aislante 120 (barrera túnel). Una de las dos capas (por ejemplo, la capa fijada 110) está configurada con una polaridad particular. La polaridad 132 de la otra capa (por ejemplo, la capa libre 130) está libre de cambiar para igualar la de un campo externo que puede ser aplicado. Un cambio en la polaridad 132 de la capa libre 130 cambiará la resistencia del elemento 100 de almacenamiento de la MTJ. Por ejemplo, cuando se alinean las polaridades, Fig. 1A, existe un estado de baja resistencia. Cuando las polaridades no están alineadas, Fig. 1B, entonces existe un estado de alta resistencia. La ilustración de la MTJ 100 ha sido simplificada y los expertos en la técnica apreciarán que cada capa ilustrada puede comprender una o más capas de materiales, tal como se conoce en la técnica.

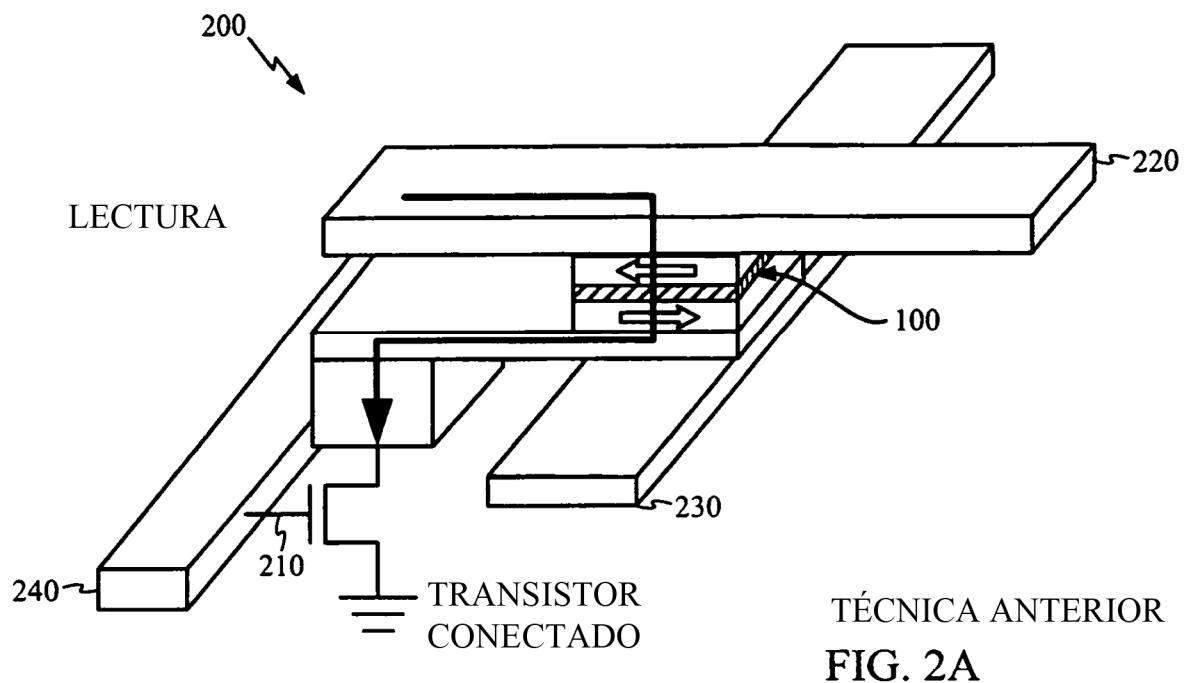

25 Con referencia a la Fig. 2A, se ilustra una celda 200 de memoria de una MRAM convencional para una operación de lectura. La celda 200 incluye un transistor 210, una línea 220 de bits, una línea 230 de dígitos y una línea 240 de palabras. La celda 200 puede ser leída midiendo la resistencia eléctrica de la MTJ 100. Por ejemplo, puede seleccionarse una MTJ 100 particular activando un transistor 210 asociado, que puede comutar la corriente de una línea 220 de bits a través de la MTJ 100. Debido al efecto túnel magnetoresistivo, la resistencia eléctrica de la MTJ 100 cambia en base a la orientación de las polaridades en las dos capas magnéticas (por ejemplo, 110, 130), tal como se expone más arriba. La resistencia dentro de cualquier MTJ 100 particular puede determinarse a partir de la corriente resultante de la polaridad de la capa libre. Convencionalmente, si la capa fijada 110 y la capa libre 130 tienen la misma polaridad, la resistencia es baja y se lee un "0". Si la capa fijada 110 y la capa libre 130 tienen polaridad opuesta, la resistencia es más alta y se lee un "1".

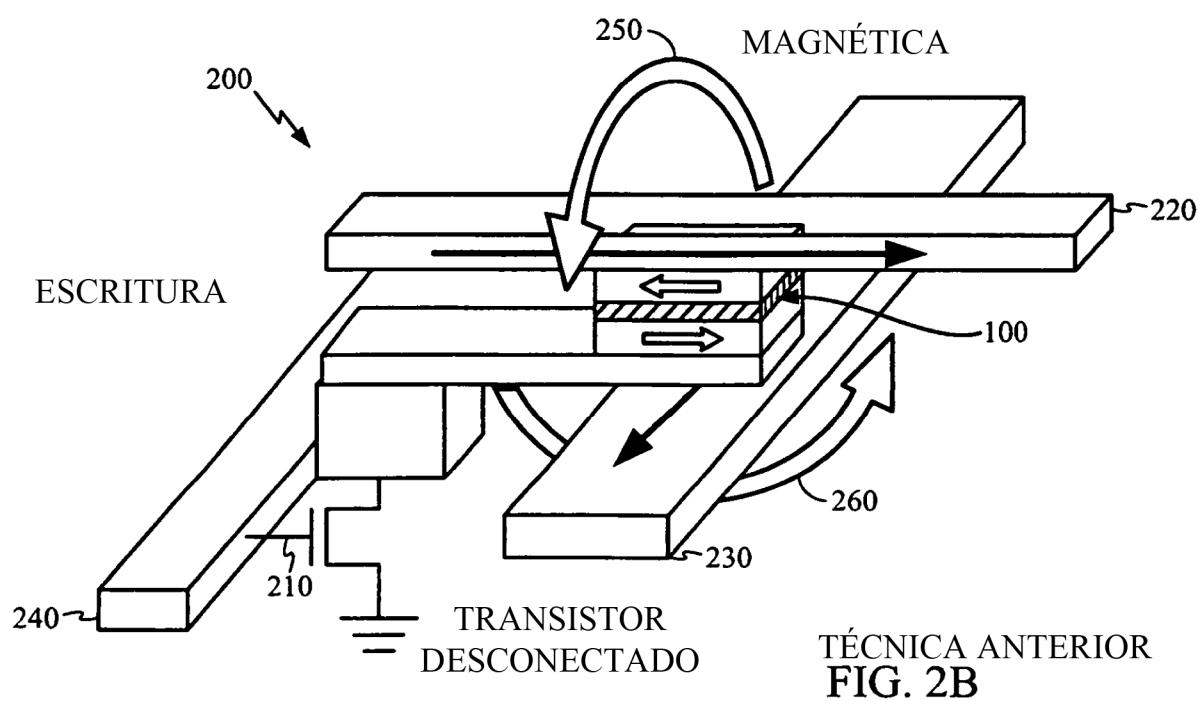

30 Con referencia a la Fig. 2B, la celda 200 de memoria de una MRAM convencional está ilustrada para una operación de escritura. La operación de escritura de la MRAM es una operación magnética. En consecuencia, el transistor 210 está desconectado durante la operación de escritura. La corriente se propaga a través de la línea 220 de bits y la línea 230 de dígitos para establecer campos magnéticos 250 y 260 que pueden afectar a la polaridad de la capa libre de la MTJ 100 y, en consecuencia, al estado lógico de la celda 200. En consecuencia, pueden escribirse y almacenarse datos en la MTJ 100.

35 La MRAM tiene varias características deseables que la hacen candidata para una memoria universal, como alta velocidad, densidad elevada (es decir, tamaño pequeño de la celda de bit), bajo consumo de energía y ninguna degradación con el tiempo. Sin embargo, la MRAM tiene problemas de escalabilidad. Específicamente, a medida que las celdas de bits se hacen menores, los campos magnéticos usados para comutar el estado de la memoria aumentan. En consecuencia, la densidad de la corriente y el consumo de energía aumentan para proporcionar los mayores campos magnéticos, limitando así la escalabilidad de la MRAM.

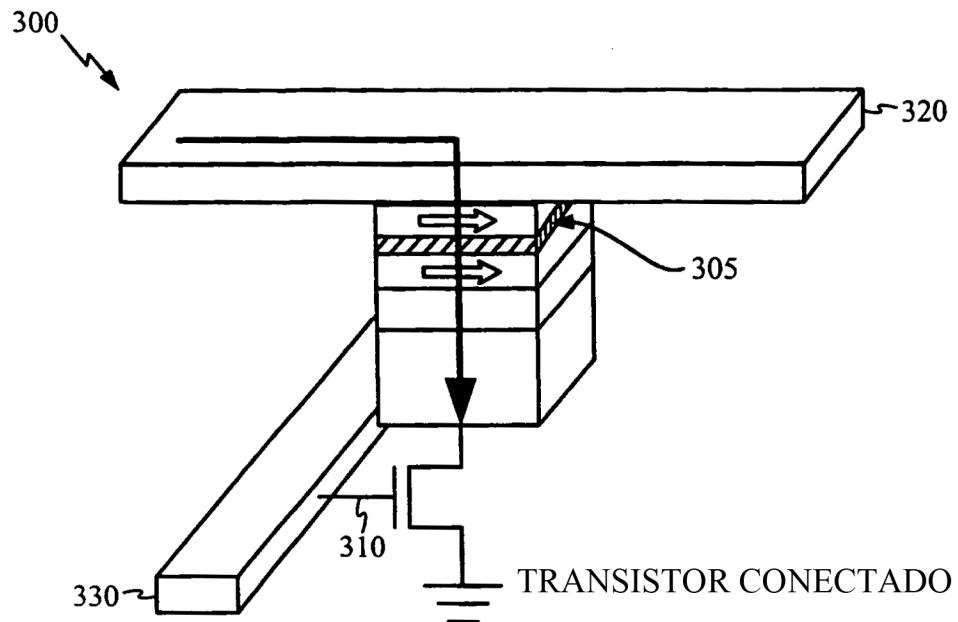

A diferencia de la MRAM convencional, la memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) usa electrones que se polarizan en su espín a medida que los electrones pasan a través de una película delgada (filtro de espín). La STT-MRAM también es denominada RAM por par de transferencia de espín (STT-RAM), RAM de conmutación de la magnetización por transferencia de torsión de espín (Spin-RAM) y transferencia del momento del espín (SMT-RAM). Durante la operación de escritura, los electrones polarizados por espín ejercen un par en la capa libre, que puede conmutar la polaridad de la capa libre. La operación de lectura es similar a la MRAM convencional, porque se usa una corriente para detectar el estado de resistencia / lógico del elemento de almacenamiento de la MTJ, tal como se ha expuesto en lo que antecede. Según se ilustra en la Fig. 3A, una celda 300 de bit de STT-MRAM incluye la MTJ305, el transistor 310, la línea 320 de bits y la línea 330 de palabras. El transistor 310 se conecta para las operaciones tanto de lectura como de escritura para permitir que la corriente fluya por la MTJ 305 para que el estado lógico pueda ser leído o escrito.

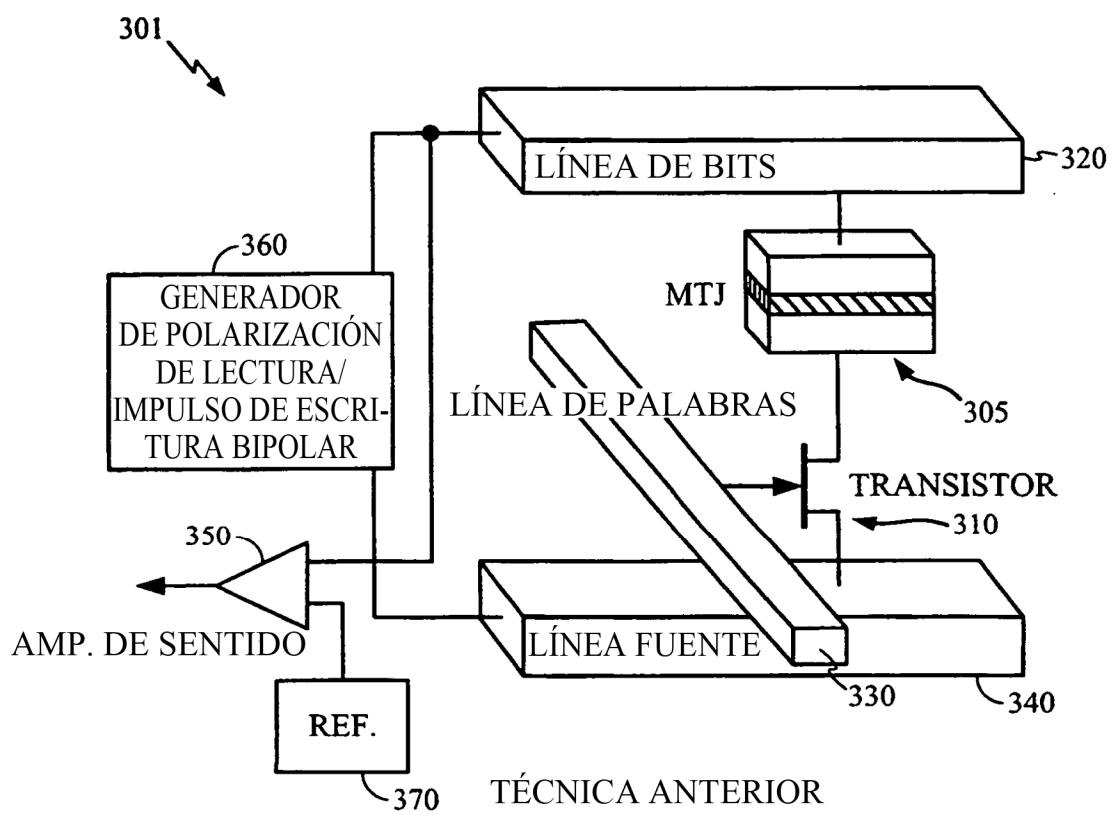

Con referencia a la Fig. 3B, se ilustra un diagrama más detallado de una celda 301 de STT-MRAM, para una presentación adicional de las operaciones de lectura / escritura. Además de elementos presentados previamente, como la MTJ 305, el transistor 310, la línea 320 de bits y la línea 330 de palabras, se ilustran una línea fuente 340 un amplificador 350 de sentido, la circuitería 360 de lectura / escritura y la referencia 370 de la línea de bits. Según se expone en lo que antecede, la operación de escritura en una STT-MRAM es eléctrica. La circuitería 360 de lectura / escritura genera una tensión de escritura entre la línea 320 de bits y la línea fuente 340. Dependiendo de la polaridad de la tensión entre la línea 320 de bits y la línea fuente 340, puede cambiar la polaridad de la capa libre de la MTJ 305 y, en consecuencia, puede escribirse el estado lógico a la celda 301. Así mismo, durante una operación de lectura, se genera una corriente de lectura, que fluye entre la línea 320 de bits y la línea fuente 340 a través de la MTJ 305. Cuando se permite que la corriente fluya a través del transistor 310, puede determinarse la resistencia (estado lógico) de la MTJ 305 en base al diferencial de tensión entre la línea 320 de bits y la línea fuente 340, que se compara con una referencia 370 y luego se amplifica con el amplificador 350 de sentido. Los expertos en la técnica apreciarán que la operación y la construcción de la celda 301 de memoria son conocidas en la técnica. Se proporcionan detalles adicionales, por ejemplo, en M. Hosomi, et al., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM, proceedings of IEDM conference (2005).

La operación de escritura eléctrica de la STT-MRAM elimina el problema de escalado debido a la operación de escritura magnética en la MRAM. Además, el diseño del circuito es menos complicado para la STT-MRAM. Sin embargo, dado que se llevan a cabo operaciones tanto de lectura como de escritura haciendo pasar corriente a través de la MTJ 305, existe un potencial de que las operaciones de lectura perturben los datos almacenados en la MTJ 305. Por ejemplo, si la corriente de lectura es similar o mayor en magnitud que el umbral de corriente de escritura, hay entonces una probabilidad sustancial de que la operación de lectura pueda perturbar el estado lógico de la MTJ 305 y degradar, así, la integridad de la memoria.

El documento US 2007/003074 describe un dispositivo de memoria magnética que utiliza la transferencia de espín en el que las celdas de memoria comprenden un transistor de acceso y una unión MTJ. El documento FR2829868 describe una memoria magnética con una escritura por corriente polarizada por espín. El documento US6269018 describe una memoria magnética de acceso aleatorio que tiene una primera capa ferromagnética libre, una segunda capa ferromagnética libre que se extiende en una dirección paralela a la primera capa ferromagnética y una capa altamente conductora formada entre la primera capa ferromagnética y la segunda capa ferromagnética.

#### 40 Resumen

Las realizaciones exemplares de la invención se dirigen a sistemas, circuitos y procedimientos para una tensión reducida de lectura en una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM).

En consecuencia, una realización de la invención puede incluir un procedimiento para el diseño de una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) que comprende: la obtención de una curva característica para un transistor de acceso; la determinación de una resistencia de estado0 y una resistencia de estado1 de un elemento de almacenamiento de unión de túnel magnético (MTJ), correspondientes a unos estados primero y segundo de la memoria; la determinación de una tensión de escritura tal que los puntos operativos tanto de las operaciones de escritura del primer estado como del segundo intercepten la curva característica en una región saturada; y la determinación de una tensión de lectura tal que los puntos operativos tanto de las operaciones de lectura del primer estado como del segundo intercepten la curva característica en una región lineal.

En la memoria de acceso (STT-MRAM) que tiene una pluralidad de celdas de bits, cada celda de bit comprende: un elemento de almacenamiento de unión de túnel magnético (MTJ), que tiene una resistencia de estado0 y una resistencia de estado1, correspondientes a unos estados primero y segundo de la memoria; un transistor de acceso acoplado en serie con la MTJ entre una línea de bits y una línea fuente, en el que una compuerta del transistor de acceso está acoplada a una línea de palabras; una tensión de suministro ( $V_{DD}$ ) acoplada a la línea de bits o la línea fuente durante las operaciones de escritura; una tensión de lectura ( $V_R$ ) acoplada a la línea de bits durante una operación de lectura, y en el que la tensión de lectura se selecciona de modo que el transistor de acceso opere en

una región lineal durante las operaciones de lectura y en el que el transistor de acceso opere en una región de saturación durante las operaciones de escritura.

Otra realización de la invención incluye un medio legible por ordenador que incluye código almacenado en el mismo para el diseño de una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) que comprende: código para hacer que un ordenador cargue una curva característica para un transistor de acceso; código para hacer que un ordenador determine una resistencia de estado0 y una resistencia de estado1 de un elemento de almacenamiento de unión de túnel magnético (MTJ), correspondientes a unos estados primero y segundo de la memoria; código para hacer que un ordenador determine una tensión de escritura de modo que los puntos operativos de las operaciones de escritura tanto del primer estado como del segundo estado interceptan la curva característica en una región saturada; y código para hacer que un ordenador determine una tensión de lectura de modo que los puntos operativos de las operaciones de lectura tanto del primer estado como del segundo estado interceptan la curva característica en una región lineal. La invención es definida en las reivindicaciones adjuntas.

#### **Breve descripción de los dibujos**

Los dibujos adjuntos se presentan para ayudar en la descripción de las realizaciones de la invención y se proporcionan únicamente para la ilustración de las realizaciones y no para una limitación de la misma.

Las Figuras 1A y 1B son ilustraciones de un elemento de almacenamiento de unión de túnel magnético (MTJ).

Las Figuras 2A y 2B son ilustraciones de una celda de memoria magnetoresistiva de acceso aleatorio (MRAM) durante operaciones de lectura y de escritura, respectivamente.

Las Figuras 3A y 3B son ilustraciones de celdas de memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM).

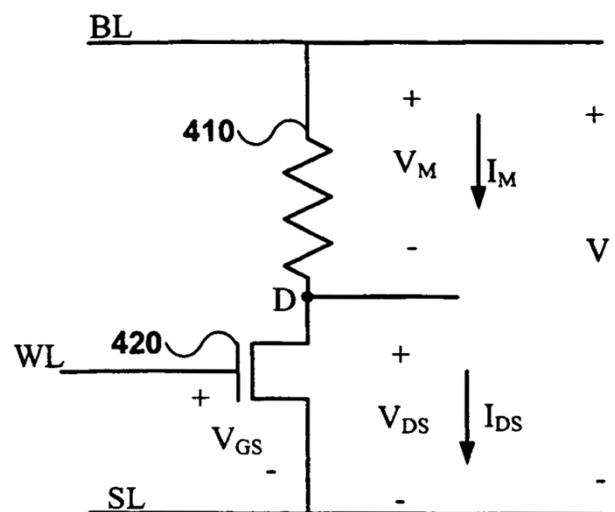

La Fig. 4A es una representación esquemática simplificada de una celda de STT-MRAM.

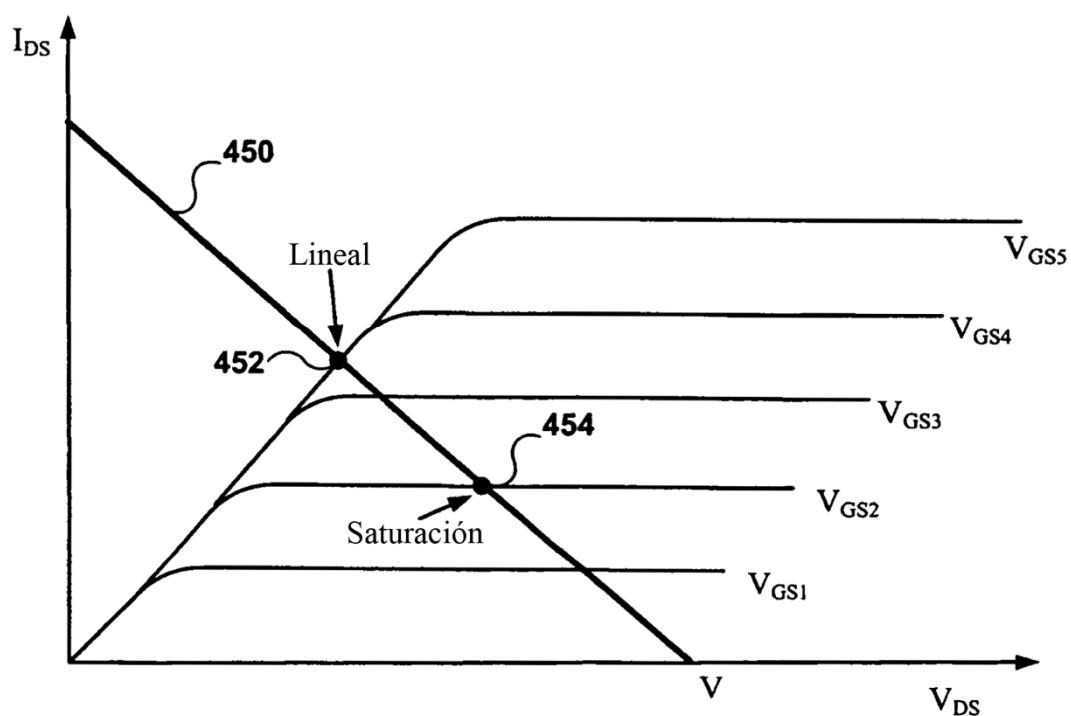

La Fig. 4B es un gráfico que ilustra curvas características de un transistor de línea de palabras y una línea de carga que indican diversos puntos operativos.

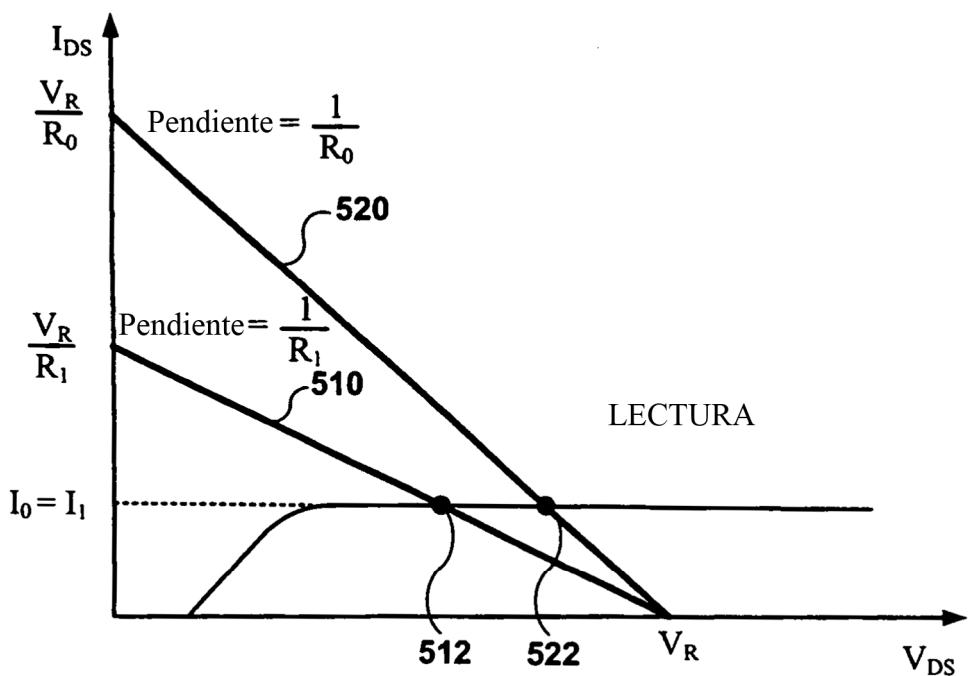

La Fig. 5A es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de lectura en la región saturada.

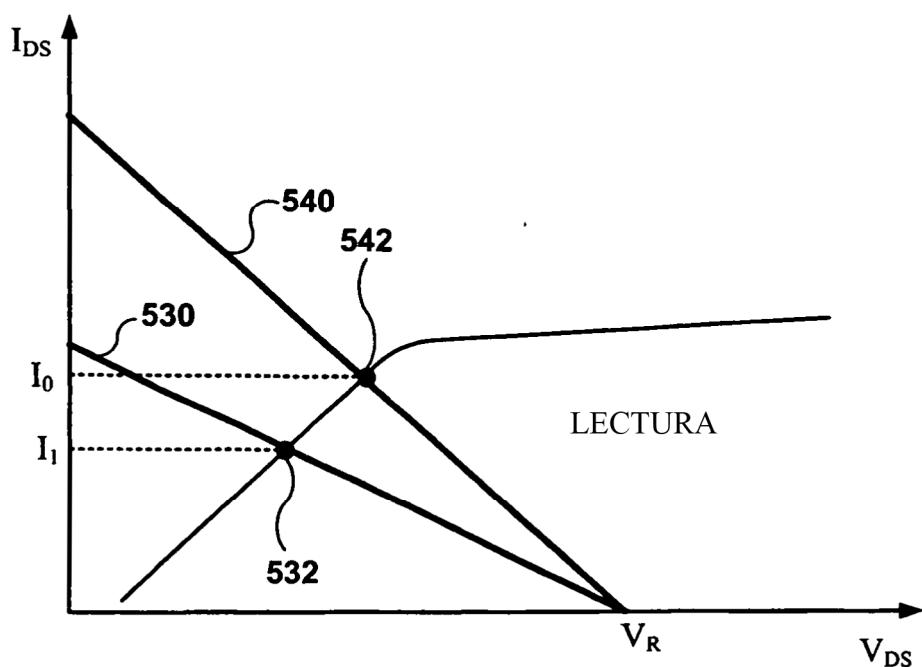

La Fig. 5B es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de lectura en la región lineal.

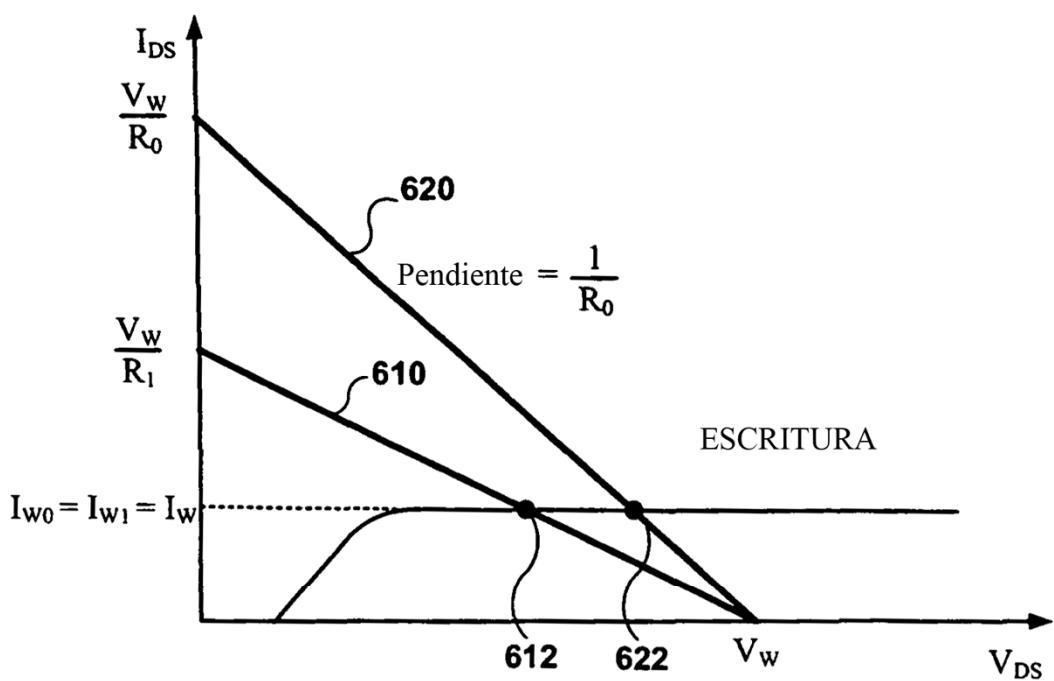

La Fig. 6A es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de escritura en la región saturada.

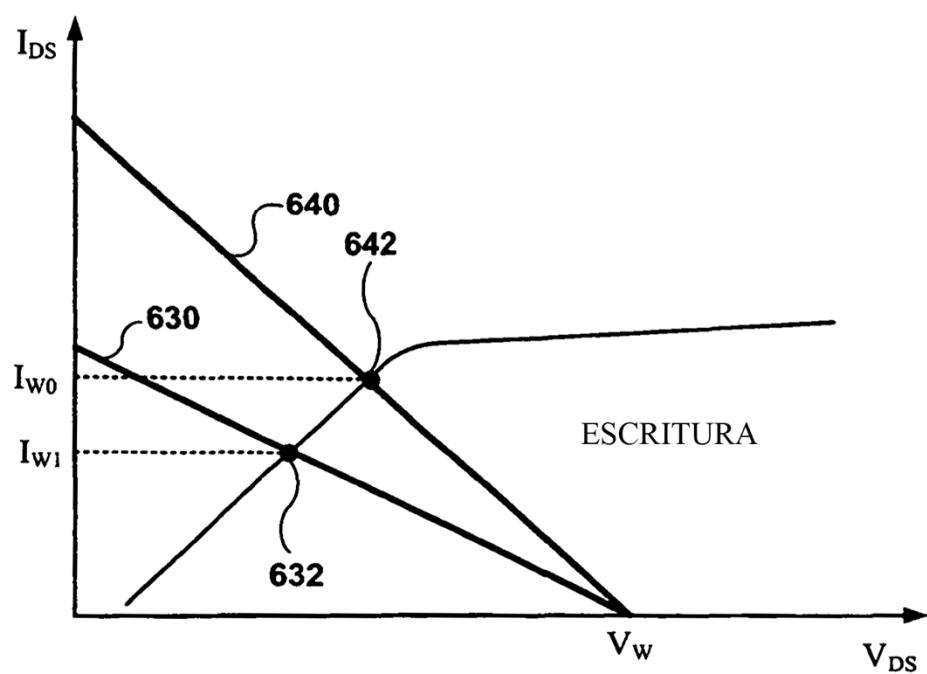

La Fig. 6B es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de escritura en la región lineal.

La Fig. 7 es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de lectura y escritura.

La Fig. 8 es un gráfico que ilustra una curva característica para un transistor de línea de palabras y líneas de carga que indican diversos puntos operativos de lectura y escritura.

La Fig. 9 es un diagrama de flujo que ilustra un procedimiento de diseño para determinar diversos puntos operativos de una celda de bit de STT-MRAM.

#### **Descripción detallada**

En la siguiente descripción y en los dibujos relacionados dirigidos a realizaciones específicas de la invención se dan a conocer aspectos de realizaciones de la invención. Pueden idearse realizaciones alternativas sin apartarse del alcance de la invención. Además, los elementos bien conocidos de la invención no serán descritos en detalle o serán omitidos para no oscurecer los detalles relevantes de las realizaciones de la invención.

La terminología usada en el presente documento tiene el propósito exclusivo de describir realizaciones particulares y no se pretende que sea limitante de las realizaciones de la invención. Según se usan en el presente documento, se pretende que las formas singulares "un", "una", "el" y "la" incluyan también las formas plurales, a no ser que el contexto indique claramente lo contrario. Se entenderá, además, que los términos "comprende", "que comprende", "incluye" y/o "que incluye", cuando se usan en el presente documento, especifican la presencia de características, enteros, etapas, operaciones, elementos y/o componentes especificados, pero no excluyen la presencia o la adición de uno o más características, enteros, etapas, operaciones, elementos, componentes adicionales y/o grupos de los mismos.

La palabra “ejemplar” se usa en el presente documento con el significado de “servir de ejemplo, caso o ilustración”. No debe interpretarse necesariamente que ninguna realización descrita en el presente documento como “ejemplar” se prefiera o sea ventajosa con respecto a otras realizaciones. De forma similar, la expresión “realizaciones de la invención” no requiere que todas las realizaciones de la invención incluyan la característica, la ventaja o el modo de operación presentados.

Tal como se expone en los antecedentes, la STT-MRAM usa una corriente reducida de escritura para cada celda, lo que es una ventaja de este tipo de memoria con respecto a la MRAM. Sin embargo, en diseños convencionales la corriente de lectura de celdas puede aproximarse o superar el umbral de corriente de escritura y provocar así que ocurra un operación de escritura inválida / lectura destructiva.

- 10 Con referencia a la Fig. 4A, se ilustra un esquema simplificado de una celda de STT-MRAM. La MTJ está representada por la resistencia ( $R$ ) 410 está en serie con el transistor 420 de acceso entre la línea de bits (BL) y la línea fuente (SL). Puede considerarse que la operación de la celda tiene tres modos: Ruptura, Lectura y Escritura. Se desea una gran corriente en la celda entre el estado0 y el estado1 para la debida operación de captación. En el modo de Escritura, la operación de escritura es una operación bidireccional para escribir el estado0 y el estado1, según se ha expuesto anteriormente. Se usa una corriente reducida de escritura para una operación de poca energía. Algunos de los retos de diseño para esta celda de memoria incluyen que las operaciones de lectura y escritura usen la misma ruta y sean eléctricas. En consecuencia, ocurrirá una lectura destructiva si la corriente de lectura es mayor que la corriente mínima de escritura. Además, puede ocurrir el modo de Ruptura si la tensión entre los extremos de la MTJ (por ejemplo,  $V_M$ ) durante una operación de escritura es mayor que  $V_{ruptura}$ . La tensión ( $V$ ) es la suma de la tensión entre los extremos de la MTJ ( $V_M$ ) y la tensión drenaje-fuente ( $V_{DS}$ ). La tensión entre los extremos de la MTJ puede determinarse como:

- 15

- 20

$$I_M = \frac{V_M}{R} = \frac{V - V_{DS}}{R},$$

y la corriente drenaje-fuente ( $I_{DS}$ ) puede determinarse como función de la tensión compuerta-fuente ( $V_{GS}$ ), de la tensión drenaje-fuente ( $V_{DS}$ ), de la tensión umbral del transistor ( $V_t$ ) y la proporción entre la anchura de canal y la longitud de canal ( $W/L$ ), que puede darse como:

$$I_{DS} = f(V_{GS}, V_{DS}, V_t, W/L).$$

- 25 La tensión compuerta-fuente ( $V_{GS}$ ) puede determinarse como:

$$V_{GS} = V_{WL} - V_{SL},$$

siendo  $V_{WL}$  la tensión en la línea de palabras y siendo  $V_{SL}$  la tensión en la línea fuente. La tensión drenaje-fuente ( $V_{DS}$ ) puede determinarse como:

$$V_{DS} = V_D - V_{SL},$$

siendo  $V_D$  la tensión en el nodo D entre la MTJ 410 y el transistor 420 de acceso. La tensión ( $V$ ) también puede determinarse como:

$$V = V_{BL} - V_{SL},$$

- 30 siendo  $V_{BL}$  la tensión en la línea de bits. Además, las condiciones para la región lineal y la región de saturación del transistor de acceso pueden definirse como:

$$\text{Región lineal: } V_{GS} - V_T > V_{DS}$$

$$\text{Región de saturación: } V_{GS} - V_T \leq V_{DS}$$

Además del esquema simplificado, en la Fig. 4B se proporcionan curvas características para el transistor 420 de acceso (o línea de palabras). Las curvas características son una familia de curvas, cada una de las cuales es un gráfico de la corriente drenaje-fuente ( $I_{DS}$ ) en función de la tensión drenaje-fuente ( $V_{DS}$ ) para una tensión compuerta-fuente ( $V_{GS}$ ) particular. Además de las curvas características se traza una línea 450 de carga. La línea 450 de carga cruza la región lineal de las curvas características en el punto 452 y una región de saturación en el punto 454, como puede verse en la Fig. 4B.

La Fig. 5A ilustra una línea de carga para la operación de lectura de un estado0, 520, y una línea de carga para la operación de lectura de un estado1, 510, para una tensión dada de lectura  $V_R$ . La línea 520 de carga tiene una

pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 510 de carga tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Ambas líneas cruzan la línea de tensión drenaje-fuente ( $V_{DS}$ ) en el punto  $V_R$  y cruzan la porción saturada de la curva del transistor de acceso en los puntos 512 y 522, respectivamente. Dado que ambos estados operan en la porción saturada, la corriente de lectura para el estado0 es sustancialmente igual a la corriente de lectura para el estado1 (es decir,  $I_0 = I_1$ ). En consecuencia, si la operación de lectura ocurre en la región saturada, será difícil detectar el estado de la MTJ, ya que las corrientes de lectura para ambos estados serán similares.

La operación del modo de lectura puede estar diseñada para que tenga una diferencia significativa de corriente entre estado0 y estado1 si está diseñada para operar en la región lineal. La Fig. 5B ilustra una línea de carga para la operación de lectura de un estado0 540 y una línea de carga para la operación de lectura de un estado1 530 para una tensión dada de lectura  $V_R$  y una tensión compuerta-fuente ( $V_{GS}$ ) dada. La línea 540 de carga tiene una pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 530 de carga también tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Ambas líneas cruzan la línea de tensión drenaje-fuente en el punto  $V_R$ . Sin embargo, en esta configuración, las líneas de carga cruzan la porción lineal de la curva del transistor de acceso en los puntos 532 y 542 para  $R_1$  y  $R_0$ , respectivamente. Operando en la porción lineal durante la operación de lectura, la corriente de lectura para el estado0 puede ser mayor que la corriente de lectura para el estado1 (es decir,  $I_0 > I_1$ ), como puede verse en la Fig. 5B. Puede lograrse el objetivo de diseño de tener una diferencia significativa de corriente entre el estado0 y el estado1. En consecuencia, el estado de la MTJ será más fácil de detectar en base a las diferentes corrientes y pueden reducirse los errores de lectura. Otros factores también pueden aumentar la diferencia de la corriente, como una menor resistencia del estado activado  $R_{activado}$  del transistor de la línea de palabras (o de acceso). Además, la diferencia entre la tierra  $R_1$  también tenderá a aumentar la diferencia de las corrientes entre la operación de lectura.

A diferencia de la operación de lectura, la operación de escritura puede tener una magnitud similar de corriente para cada estado y, preferentemente, tiene una baja corriente de escritura como sea posible para reducir el consumo de energía. En las Figuras 6A y 6B se ilustran líneas de carga para la operación de escritura. En la Fig. 6A se ilustra una línea de carga para la operación de escritura de un estado0 620 y una línea de carga para la operación de escritura de un estado1 610 para una tensión dada de escritura  $V_w$ . La línea 620 de carga tiene una pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 610 de carga tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Ambas líneas cruzan la línea de tensión drenaje-fuente en el punto  $V_w$  y cruzan la porción saturada del transistor de la línea de palabras en los puntos 612 y 622, respectivamente. Dado que ambos estados operan en la porción saturada, la magnitud de la corriente de escritura para el estado0 puede ser sustancialmente igual a la magnitud de la corriente de escritura para el estado1 (es decir,  $I_{w0} = I_{w1} = I_w$ ).

Alternativamente, la Fig. 6B ilustra una línea de carga que cruza la región lineal para la operación de escritura de un estado0 640 y una línea de carga para la operación de escritura de un estado1 630 para una tensión dada de escritura  $V_w$ . La línea 640 de carga también tiene una pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 630 de carga tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Ambas líneas cruzan la línea de tensión drenaje-fuente ( $V_{DS}$ ) en el punto  $V_w$ . Sin embargo, las líneas de carga cruzan la porción lineal de la curva del transistor de la línea de palabras en los puntos 632 y 642 para  $R_1$  y  $R_0$ , respectivamente. Operando en la porción lineal durante la operación de lectura, la magnitud de la corriente de escritura para el estado0 es mayor que la magnitud de la corriente de escritura para el estado1 (es decir,  $I_{w0} > I_{w1}$ ), como puede verse en la Fig. 6B. La gran diferencia de corriente no se precisa en la operación de escritura, de modo que un objetivo de diseño es hacer que la operación de escritura ocurra en la región de saturación del transistor de acceso.

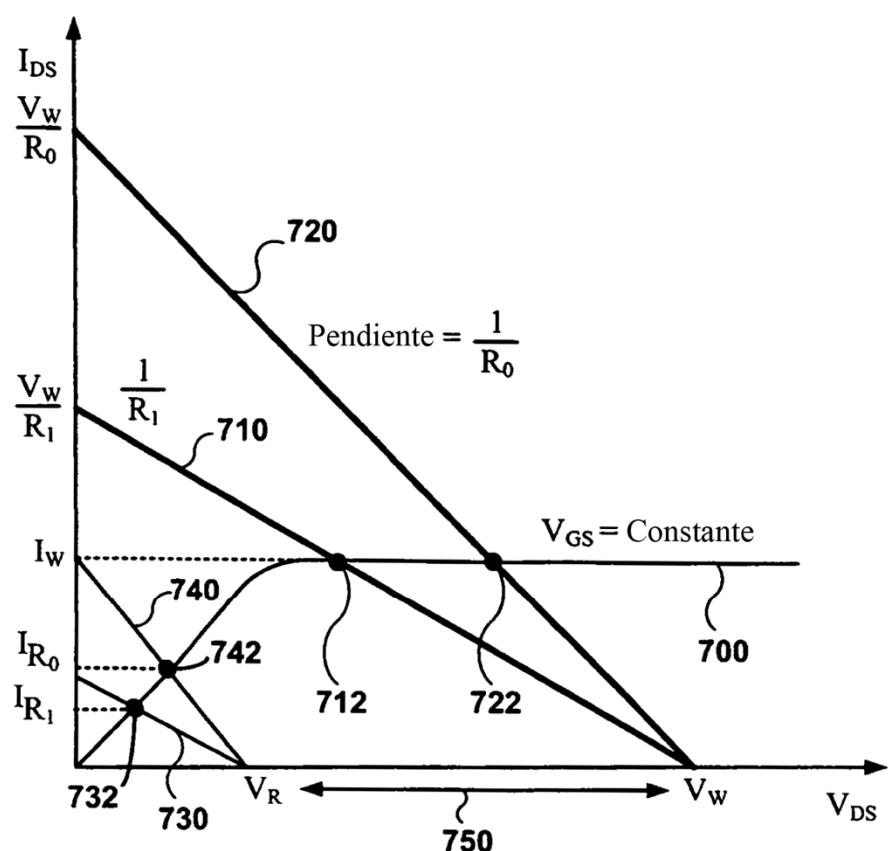

La Fig. 7 ilustra un ejemplo de puntos operativos combinados de lectura y escritura y líneas de carga relacionadas en un diseño ejemplar. En el ejemplo ilustrado, se considera que la tensión compuerta-fuente ( $V_{GS}$ ) en el transistor de acceso es constante, de modo que solo se traza una curva 700 para  $V_{GS}$ . En este diseño, se ilustran una línea de carga para la operación de escritura de un estado0 720 y una línea de carga para la operación de escritura de un estado1 710 para una tensión dada de escritura  $V_w$ . Una vez más, la línea 720 de carga tiene una pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 710 de carga tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Ambas líneas cruzan la línea de tensión drenaje-fuente ( $V_{DS}$ ) en el punto  $V_w$  y pueden estar diseñadas para cruzar la región saturada en los puntos 712 y 722 para  $R_1$  y  $R_0$  respectivamente. En consecuencia, puede obtenerse una magnitud coherente de la corriente de escritura  $I_w$ .

En la operación de lectura, se desea que haya un diferencial de corriente para los diferentes estados de lectura. En consecuencia, se trazan una línea de carga para la operación de lectura de un estado0 740 y una línea de carga para la operación de lectura de un estado1 730 para una tensión dada de lectura  $V_R$ . La línea 740 de carga también tiene una pendiente de  $1/R_0$ , siendo  $R_0$  la resistencia de estado0 de la MTJ. De forma similar, la línea 730 de carga tiene una pendiente de  $1/R_1$ , siendo  $R_1$  la resistencia de estado1 de la MTJ. Se apreciará que estas pendientes corresponden generalmente a las mismas pendientes para la operación de escritura. Ambas líneas cruzan la línea de tensión de drenaje en una tensión de lectura  $V_R$ . Seleccionando una tensión apropiada de lectura  $V_R$ , las líneas

de carga pueden cruzar la porción lineal de la curva 700 del transistor de acceso en los puntos 732 y 742 para  $R_1$  y  $R_0$  respectivamente. Operando en la porción lineal durante la operación de lectura, puede establecerse una diferencia detectable entre la corriente de lectura para el estado0 y la corriente de lectura para el estado1 (es decir,  $I_{R0} > I_{R1}$ ), como puede verse en la Fig. 7.

5 El ejemplo ilustrado en la Fig. 7 logra al menos los siguientes objetivos de diseño.

- Punto operativo de lectura: Región lineal del transistor de acceso

- Punto operativo de escritura: Región de saturación del transistor de acceso

- La corriente de lectura es menor que la corriente de escritura para prevenir lecturas destructivas

10 Según se ha hecho notar en lo que antecede, la operación de lectura ocurre en la región lineal, de modo que la corriente de lectura para el estado0 va a ser mayor que la corriente de lectura para el estado1 (es decir,  $I_0 > I_1$ ). En consecuencia, una diferencia significativa en la corriente entre el estado0 y el estado1 facilita la detección del estado de la MTJ y pueden reducirse los errores de lectura. Cuanto mayor sea la diferencia entre los estados de lectura, más resiliente será el diseño a las variaciones de proceso, tensión y temperatura (PVT) experimentadas por todos los circuitos. De modo similar, diseñar que las operaciones de escritura ocurran en la región de saturación con una corriente más elevada que cualquiera de las dos corrientes de lectura (es decir,  $I_w >> I_0 > I_1$ ) puede mejorar la tolerancia a las variaciones de PVT con respecto al problema de lectura destructiva presentado en lo que antecede. Según se ilustra, esto puede lograrse haciendo que la tensión de escritura ( $V_w$ ) sea mayor que la tensión de lectura ( $V_R$ ). La diferencia 750 entre la tensión de escritura y la tensión de lectura es un parámetro de diseño que puede ser determinado en base a las variaciones esperadas de PVT y las curvas características del transistor de acceso para un diseño dado.

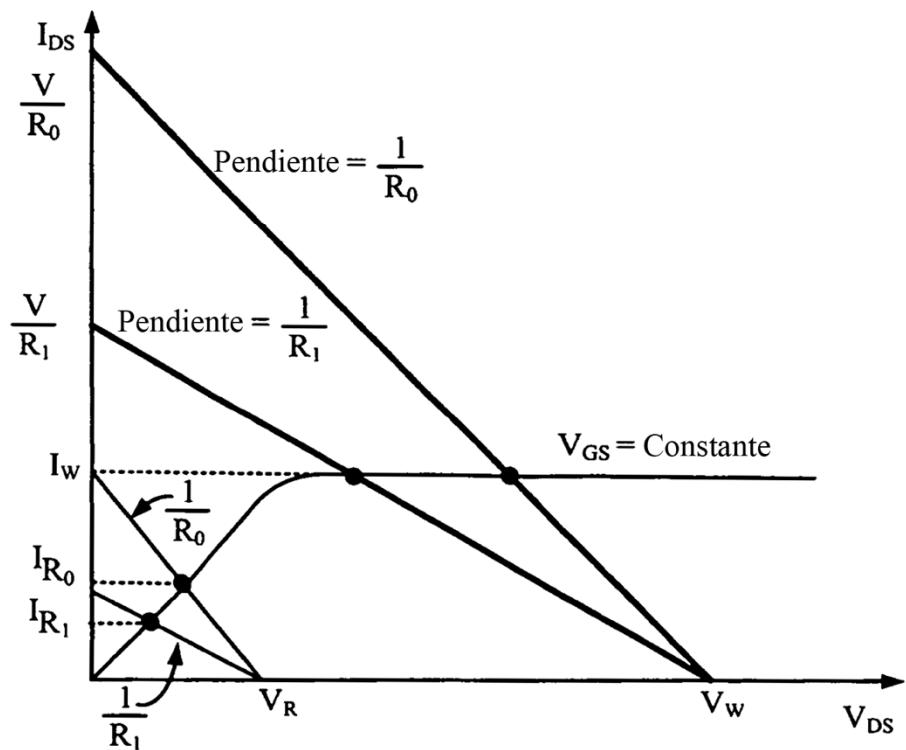

20 La Fig. 8 es un gráfico generalizado que ilustra diversos puntos operativos de lectura y escritura según realizaciones de la invención. Los elementos del gráfico pueden ser obtenidos a partir de diversos parámetros del diseño de celda de la STT-MRAM. Estos parámetros incluyen las resistencias del estado0 ( $R_0$ ) y el estado1 ( $R_1$ ) de la MTJ y una curva característica para el transistor de acceso para una tensión dada ( $V_{GS}$ ), por ejemplo. La tensión de escritura ( $V_w$ ) puede entonces ser seleccionada para interceptar la región de saturación y la tensión de lectura ( $V_R$ ) puede ser configurada para interceptar la región lineal en base a las líneas de carga de escritura y lectura. Además, las tensiones de lectura y escritura pueden estar configuradas para garantizar que la corriente máxima de lectura (por ejemplo,  $I_{R0}$ ) es menor que la corriente de escritura ( $I_w$ ) y que una corriente mínima de escritura para satisfacer los objetivos de diseño expuestos en lo que antecede. La corriente mínima de escritura ( $I_{w\min}$ ) puede determinarse considerando la corriente de la celda, las variaciones en la resistencia de la MTJ, el tamaño de la celda y  $V_t$ . Puede establecerse la corriente mínima de escritura para que sea mayor que la corriente mínima de escritura calculada.

25 Puede lograrse un diseño simple de circuito usando solo una fuente de alimentación (por ejemplo, la tensión de suministro ( $V_{DD}$ ) y la tierra) y generando una tensión intermedia para la tensión de lectura ( $V_R$ ). Una configuración exemplar puede tener la siguiente configuración:

- 35

- $V_{DD}$ , 0 y  $V_R$  como niveles de tensión

- $V_{WL} = V_{DD}$  tanto para lectura como para escritura

- $V_{BL} = V_{DD}$  (0) y  $V_{SL} = 0$  ( $V_{DD}$ ) para escritura

- $V_{BL} = V_R$  y  $V_{SL} = 0$  para lectura

40 En lo precedente,  $V_{DD}$  es una tensión de suministro,  $V_R$  es la tensión de lectura,  $V_{WL}$  es la tensión de la línea de palabras,  $V_{BL}$  es la tensión de la línea de bits y  $V_{SL}$  es la tensión de la línea fuente. Los anteriores parámetros usan solo un generador de tensión de CC para  $V_R$ . Según se ha hecho notar más arriba, la tensión tanto de la línea de bits como de la línea fuente está acoplada a tierra (0) o a  $V_{DD}$  durante las operaciones de escritura, dependiendo del estado que se está escribiendo. La tensión de la línea fuente está fijada a tierra (0) durante la lectura y la línea de bits está fijada a  $V_R$ . La tensión de la línea de palabras está acoplada a  $V_{DD}$  tanto para la lectura como para la escritura, cuando está habilitada. En consecuencia, pueden lograrse todos los estados operativos con solo  $V_{DD}$ ,  $V_R$  y tierra (0) como niveles de tensión. La apropiada selección de  $V_{DD}$  y  $V_R$  en combinación de las curvas características del transistor de acceso puede permitir que se logren los objetivos de diseño expuestos más arriba (es decir, un punto operativo de lectura en la región lineal del transistor de acceso; un punto operativo de escritura en la región de saturación del transistor de acceso; y siendo la corriente de lectura menor que la corriente de escritura) con un número mínimo de tensiones de CC.

45 En consecuencia, una realización de la invención puede incluir una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) que tiene una pluralidad de celdas de bits. Cada celda puede incluir un elemento de almacenamiento de unión de túnel magnético (MTJ) que tiene una resistencia de

5 estado0 y resistencias de estado1 y un transistor de acceso, tal como se ilustra en la Fig. 4A. El transistor de acceso puede acoplarse en serie con la MTJ entre una línea de bits y una línea fuente. Una compuerta del transistor de acceso puede estar acoplada a una línea de palabras (WL). Puede aplicarse una tensión de suministro ( $V_{DD}$ ) a la línea de bits o a la línea fuente durante operaciones de escritura. La otra línea (línea de bits o línea fuente) no acoplada a  $V_{DD}$  puede acoplarse a tierra para permitir las operaciones de escritura para ambos estados, tal como se expone en lo que antecede. Puede aplicarse una tensión de lectura ( $V_R$ ) a la línea de bits durante una operación de lectura y la línea fuente puede fijarse a tierra o 0 voltios. Además, la WL puede ser acoplada a  $V_{DD}$  durante las operaciones tanto de lectura como de escritura. Tal como se ha expuesto en lo que antecede, la tensión de lectura puede seleccionarse de tal modo que el transistor de acceso opere en una región lineal durante las operaciones de lectura y la tensión de escritura ( $V_{DD}$ ) puede seleccionarse para que el transistor de acceso opere en una región de saturación durante las operaciones de lectura.

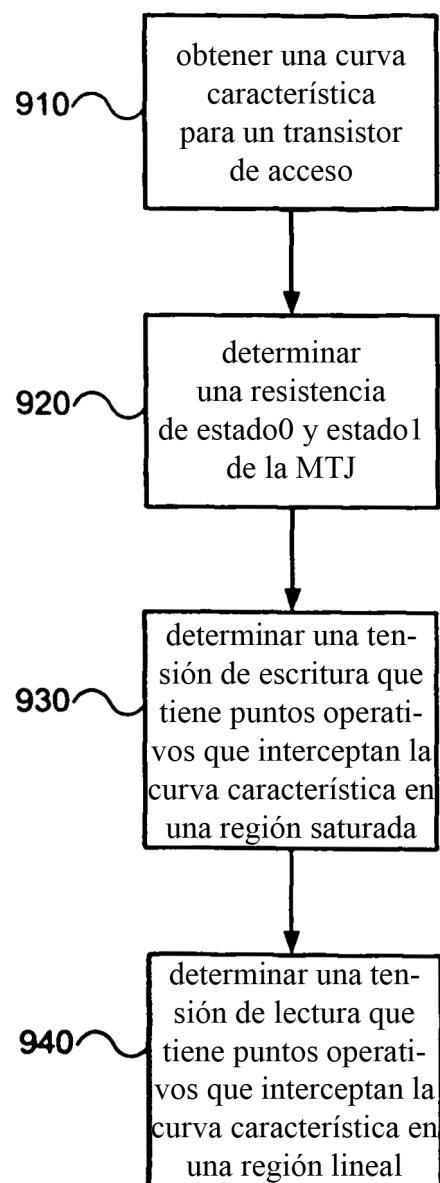

10 En vista de lo anterior, se apreciará que los procedimientos para llevar a cabo las diversas secuencias de acciones, etapas, funciones y/o algoritmos están incluidos en realizaciones de la invención. En consecuencia, con referencia a la Fig. 9, una realización de la invención puede incluir un procedimiento para diseñar una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) que comprende: la obtención, 910, de una curva 15 característica para un transistor de acceso. Puede determinarse, 920, la resistencia del estado0 y la resistencia del estado1 de un elemento de almacenamiento de unión de túnel magnético (MTJ), correspondientes a unos estados primero y segundo de la memoria. Puede determinarse, 930, una tensión de escritura tal que los puntos operativos tanto de las operaciones de escritura del primer estado como del segundo intercepten la curva característica en una 20 región saturada. Luego, puede determinarse, 940, una tensión de lectura tal que los puntos operativos tanto de las operaciones de lectura del primer estado como del segundo intercepten la curva característica en una región lineal. Además, se establece una corriente máxima de lectura para que sea menor que una corriente mínima de escritura.

25 Además, puede determinarse el efecto de las variaciones de proceso, tensión y temperatura (PVT) en una pluralidad de celdas de bits en una matriz de memoria. Cada celda de bit tiene la MTJ, un transistor de acceso y tensiones de escritura y tensiones de lecturas similares. En consecuencia, puede evaluarse el impacto de las variaciones de PVT y puede evaluarse el diseño para garantizar que operará con éxito en el intervalo esperado de variación, que puede 30 ser determinado a partir de información fácilmente disponible a los ingenieros de diseño (por ejemplo, curvas características para diversos diseños del transistor de acceso) y por límites impuestos por los ingenieros de diseño (por ejemplo, tensión y temperatura operativos mínimos y máximos). Si se determina que el diseño original no es aceptable, puede ajustarse al menos uno de la resistencia del estado0, la resistencia del estado1, la tensión de escritura o la tensión de lectura en base al impacto determinado de las variaciones de PVT y puede repetirse, por ejemplo, el procedimiento de la Fig. 9. Además, puede considerarse un diseño diferente de transistor de acceso con 35 curvas características diferentes. En consecuencia, puede determinarse un diseño de memoria tal que cada una de la pluralidad de celdas de bits tenga operaciones de escritura que intercepten la curva característica en la región saturada y cada una de las operaciones de lectura intercepte la curva característica en una región lineal.

40 Los procedimientos, las secuencias y/o los algoritmos descritos en conexión con las realizaciones dadas a conocer en el presente documento pueden implementarse directamente en soporte físico, en un módulo de soporte lógico ejecutado por un procesador o en una combinación de los dos. Un módulo de soporte lógico puede residir en memoria RAM, memoria flash, memoria ROM, memoria EPROM, memoria EEPROM, registros, un disco duro, un disco extraíble, un CD-ROM o cualquier otra forma de medio de almacenamiento conocida en la técnica. Un medio de almacenamiento ejemplar está acoplado al procesador, de modo que el procesador pueda leer información del medio de almacenamiento y escribir información en el mismo. De forma alternativa, el medio de almacenamiento puede ser integral al procesador. El procesador y el medio de almacenamiento pueden residir en un ASIC. El ASIC 45 puede residir en un terminal de usuario. De forma alternativa, el procesador y el medio de almacenamiento pueden residir como componentes diferenciados en un terminal de usuario. En consecuencia, una realización de la invención puede incluir un terminal de usuario configurado para llevar a cabo los procedimientos de diseño descritos en lo que antecede.

50 En una o más realizaciones exemplares, las funciones descritas pueden ser implementadas en soporte físico, soporte lógico, soporte lógico inalterable o cualquier combinación de los mismos. Si se implementan en soporte lógico, las funciones pueden ser almacenadas o transmitidas como una o más instrucciones o código en un medio legible por ordenador. Los medios legibles por ordenador incluyen tanto medios de almacenamiento de ordenador y medios de comunicaciones que incluyen cualquier medio que facilite la transferencia de un programa de ordenador de un lugar a otro. Un medio de almacenamiento puede ser cualquier medio disponible que pueda ser objeto de acceso por parte de un ordenador. A título de ejemplo, y no de limitación, tales medios legibles por ordenador 55 pueden comprender RAM, ROM, EEPROM, CD-ROM u otro almacenamiento en disco óptico, almacenamiento en disco magnético u otros dispositivos de almacenamiento magnético, o cualquier otro medio que pueda ser usado para portar o almacenar el código de programa deseado en forma de instrucciones o estructuras de datos y que pueda ser objeto de acceso por parte de un ordenador. Además, cualquier conexión se denominada con propiedad medio legible por ordenador. Por ejemplo, si el soporte lógico es transmitido desde un sitio web, un servidor u otra fuente remota usando un cable coaxial, un cable de fibra óptica, un par trenzado, una línea digital de abonado (DSL) 60 o tecnologías inalámbricas como la infrarroja, la radio y las microondas, entonces en la definición de medio están

- 5 incluidos un cable coaxial, un cable de fibra óptica, un par trenzado, una línea digital de abonado (DSL) o tecnologías inalámbricas como la infrarroja, la radio y las microondas. Según se usa aquí, disco (*disk* o *disc* en inglés) incluye disco compacto (CD), disco láser, disco óptico, disco versátil digital (DVD), disco flexible y disco Blu-ray, reproduciendo normalmente los discos llamados *disks* en inglés los datos de forma magnética, mientras que los discos llamados *discs* en inglés reproducen los datos ópticamente con láseres. También debieran incluirse combinaciones de lo anterior dentro del alcance de los medios legibles por ordenador.

- 10 En consecuencia, una realización de la invención puede incluir un medio legible por ordenador que incluye código almacenado en el mismo para el diseño de una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio (STT-MRAM) que comprende: código para hacer que un ordenador cargue una curva característica para un transistor de acceso; código para hacer que un ordenador determine una resistencia de estado0 y una resistencia de estado1 de un elemento de almacenamiento de unión de túnel magnético (MTJ), correspondientes a unos estados primero y segundo de la memoria; código para hacer que un ordenador determine una tensión de escritura de modo que los puntos operativos de las operaciones de escritura tanto del primer estado como del segundo estado interceptan la curva característica en una región saturada; y código para hacer que un ordenador 15 determine una tensión de lectura de modo que los puntos operativos de las operaciones de lectura tanto del primer estado como del segundo estado interceptan la curva característica en una región lineal. Además, cualquiera de las funciones descritas en el presente documento puede ser incluida como código adicional en realizaciones adicionales de la invención.

- 20 Aunque la revelación precedente muestra realizaciones ilustrativas de la invención, debería hacerse notar que podrían efectuarse diversos cambios y modificaciones en el presente documento sin apartarse del alcance de las realizaciones de la invención según está definida por las reivindicaciones adjuntas. no es preciso que las funciones, las etapas y/o las funciones de los procedimientos según las realizaciones de la invención descritas en el presente documento se lleven a cabo en ningún orden particular. Además, aunque elementos de la invención pueden ser descritos o reivindicados en singular, se contempla el plural, a no ser que se afirme explícitamente la limitación al singular.

- 25

**REIVINDICACIONES**

1. Un procedimiento de diseño de una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio, STT-MRAM, que comprende:

- la obtención (910) de una curva característica para un transistor (420) de acceso;

- 5 la determinación (920) de una resistencia de estado0 y una resistencia de estado1 de un elemento de almacenamiento de unión de túnel magnético, MTJ, correspondientes a unos estados primero y segundo de la memoria;

- 10 la determinación (930) de una tensión de escritura tal que los puntos operativos (612, 622) tanto de las operaciones de escritura del primer estado como del segundo intercepten la curva característica en una región saturada; y

- la determinación (940) de una tensión de lectura tal que los puntos operativos (532, 542) tanto de las operaciones de lectura del primer estado como del segundo intercepten la curva característica en una región lineal.

2. El procedimiento de la reivindicación 1 que, además, comprende:

- 15 establecer que una corriente máxima de lectura sea menor que una corriente máxima de escritura.

3. El procedimiento de la reivindicación 2 en el que la corriente máxima de lectura se determina en base a parámetros de variación de proceso, tensión y temperatura, PVT, de al menos una de la resistencia de estado0 de la MTJ, la resistencia de estado1 de la MTJ, la curva característica del transistor (420) de acceso o la tensión de lectura.

- 20 4. El procedimiento de la reivindicación 3 en el que la variación de PVT se modela en una pluralidad de celdas de bits en una matriz de memoria.

5. El procedimiento de la reivindicación 2 en el que la corriente mínima de escritura se determina en base a parámetros de variación de proceso, tensión y temperatura, PVT, de al menos una de la resistencia de estado0 de la MTJ, la resistencia de estado1 de la MTJ, la curva característica del transistor (420) de acceso o la tensión de escritura.

- 25 6. El procedimiento de la reivindicación 5 en el que la variación de PVT se modela en una pluralidad de celdas de bits en una matriz de memoria.

7. El procedimiento de la reivindicación 5 en el que la tensión de lectura es sustancialmente menor que la tensión de escritura.

- 30 8. El procedimiento de la reivindicación 1 en el que está determinado que la tensión de escritura sea una tensión de suministro.

9. El procedimiento de la reivindicación 1 que, además, comprende:

- 35 la determinación del efecto de las variaciones de proceso, tensión y temperatura, PVT, en una pluralidad de celdas de bits en una matriz de memoria, teniendo cada celda de bit una MTJ con resistencias de estado0 y estado1, un transistor (420) de acceso, una tensión de escritura y una tensión de lectura.

10. El procedimiento de la reivindicación 9 que, además, comprende:

- 40 el ajuste de al menos una de la resistencia de estado0, la resistencia de estado1, la tensión de escritura o la tensión de lectura en base al efecto determinado de las variaciones de PVT de manera que cada una de la pluralidad de celdas de bits tenga operaciones de escritura que intercepten la curva característica en la región saturada y operaciones de lectura que intercepten la curva característica en una región lineal.

11. Una memoria magnetoresistiva por par de transferencia de espín de acceso aleatorio, STT-MRAM, que tiene una pluralidad de celdas de bits en la que cada celda de bit comprende:

- 45 un elemento de almacenamiento de unión de túnel magnético, MTJ, que tiene una resistencia de estado0 y una resistencia de estado1, correspondientes a unos estados primero y segundo de la memoria;

- un transistor (420) de acceso acoplado en serie con la MTJ entre una línea de bits (BL) y una línea fuente (SL), en el que una compuerta del transistor (420) de acceso está acoplada a una línea de palabras (WL);

- una tensión de suministro ( $V_{DD}$ ) acoplada a la línea de bits (BL) o la línea de palabras (SL) durante las operaciones de escritura;

una tensión de lectura ( $V_R$ ) acoplada a la línea de bits (BL) durante una operación de lectura; la STT-MRAM comprende:

un medio para seleccionar una tensión de escritura tal que el transistor (420) de acceso opere en una región de saturación durante las operaciones de escritura;

5 un medio para aplicar una tensión a la compuerta; y **está caracterizada porque**, además, comprende:

un medio para seleccionar la tensión de lectura tal que el transistor (420) de acceso opere en una región lineal durante las operaciones de lectura.

12. La STT-MRAM de la reivindicación 11 en la que la línea fuente (SL) está acoplada a un potencial de tierra durante la operación de lectura.

10 13. La STT-MRAM de la reivindicación 11 en la que la tensión compuerta-fuente ( $V_{GS}$ ) del transistor (420) de acceso tiene sustancialmente el mismo valor durante las operaciones de lectura y escritura.

14. La STT-MRAM de la reivindicación 13 en la que la tensión de suministro ( $V_{DD}$ ) está acoplada a la línea de palabras (WL) tanto en las operaciones de lectura como de escritura.

15 15. Un medio legible por ordenador que incluye código almacenado en el mismo que, cuando es ejecutado por un ordenador, da como resultado la realización de las etapas del procedimiento de cualquiera de las reivindicaciones 1 a 10.

LECTURA Y ESCRITURA

TÉCNICA ANTERIOR

**FIG. 3A**

TÉCNICA ANTERIOR

**FIG. 3B**

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7

FIG. 8

FIG. 9