11 Número de publicación: 2 375 818

51 Int. Cl.: H05K 7/14

(2006.01)

| $\overline{}$ |                          |                |

|---------------|--------------------------|----------------|

| ้ 1 2         | 2) TD A DLICCIÓNI DE DAT | ENITE ELIDADEA |

| 12            | 2) TRADUCCIÓN DE PAT     | ENTE EURUPEA   |

T3

96 Número de solicitud europea: 09158551 .3

96 Fecha de presentación: 23.04.2009

Número de publicación de la solicitud: 2244544

Fecha de publicación de la solicitud: 27.10.2010

- (54) Título: MÓDULO DE HARDWARE Y PANEL TRASERO PARA UN DISPOSITIVO INTELIGENTE IED.

- Fecha de publicación de la mención BOPI: **06.03.2012**

73) Titular/es:

ABB Technology AG Affoltern strasse 44 8050 Zürich

- Fecha de la publicación del folleto de la patente: **06.03.2012**

- 72 Inventor/es:

Gloor, Mathias y Borner, Christian

74 Agente: Ungría López, Javier

# **DESCRIPCIÓN**

Módulo de hardware y panel trasero para un dispositivo inteligente IED.

#### Campo de la invención

5

10

15

35

40

45

50

55

La invención se refiere al campo de la comunicación interna de dispositivos en Dispositivos Electrónicos Inteligentes para la automatización de subestaciones. Parte de un módulo de hardware o tarjeta, como se describe en el preámbulo de la reivindicación 1.

#### Antecedentes de la invención

Las subestaciones en las redes de potencia eléctrica de alta tensión y de media tensión incluyen dispositivos primarios, tales como cables eléctricos, líneas, barras colectoras, dispositivos de conmutación y transformadores de potencia. Estos dispositivos primarios son accionados de una manera automática a través de un sistema de Automatización de Subestaciones (SA). El sistema SA comprende dispositivos secundarios, entre los cuales los Dispositivos Electrónicos Inteligentes (IED) son responsables de la protección, control y supervisión de los dispositivos primarios. Los IEDs controlan controladores de dispositivos primarios asignados sobre la base de señales que proceden de sensores asignados para la posición de conmutación de toma de conmutadores o transformadores, temperatura, tensión, corriente, etc., señales de otros IEDs y señales desde un sistema de supervisión. A la inversa, un IED comunica un estado o comportamiento de sus dispositivos primarios asignados, es decir, lecturas de sensores seleccionados, a otros IEDs o al sistema de supervisión. En función de su localización específica en la subestación y, en particular, de la proximidad a los dispositivos primarios, los IEDs tienen que cumplir ciertos requerimientos de resistencia al medio ambiente y de Compatibilidad Electromagnética (EMC).

En IEDs modulares, una pluralidad de módulos o tarjetas, cada uno de los cuales comprende un Cuadro de Circuito Impreso (PCB) y componentes electrónicos montados encima, están conectados a través de conectores del panel trasero a un bus de panel trasero de interconexión. Este último puede operar, por ejemplo, de acuerdo con una topología de bus de punto-a-punto, que implica un controlador exclusivo y una pareja de receptores por canal. Un número limitado de transiciones desde un medio al siguiente (es decir, una transición desde un cuadro de circuito impreso hasta un cable a través de un conector) implican que el canal tendrá muy probablemente impedancia bien controlada, lo que a su vez permite talas de señalización muy altas. En particular, la Señalización Diferencial de Baja Tensión (LVDS), la Lógica de Modo de Corriente (CML) y la Lógica Acoplada de Emisor Positiva de Baja Tensión (LVPECL) son tecnologías de señalización diferencial diseñadas para transmisión de señales punto-a-punto, con señales de salida del controlador que comprenden bordes rápidos que permiten la transmisión de multi-gigabits. Por ejemplo, la oscilación típica de las señales de 350 mV de LVDS permite tasas de datos de hasta 3 Gbps, mientras que solamente consumen una cantidad pequeña de potencia.

De acuerdo con ello, LVDS se considera una tecnología muy eficiente, a pesar del hecho de que los bordes rápidos de las señales son muy sensibles a cualquier discontinuidad de la impedancia y exigen diseños de interconexión cuidadosos. La llamada interconexión, o trayectoria de señal física, consta típicamente de dos trazas de conductores impresas sobre un panel trasero. La impedancia controlada de la interconexión, la carga adecuada de controlador, y la terminación de la interconexión son puntos clave de consideración cuando se diseñan para transmisión de señales de baja inestabilidad. Una ventaja económica particular reside en el hecho de que un controlador LVDS interno de Matriz de Puerta Programable en el Campo (FPGA) puede proporcionar una calidad suficiente de la señal y una potencia de transmisión suficiente para comunicación punto-a-punto. Por otra parte, las topologías de puntos múltiples y, en particular las topologías 'multi-drop' con un controlador individual y receptores múltiples por canal, requieren amplificación adicional de la señal transmitida.

El cuadro de panel trasero, además de alojar el bus de panel trasero, está adaptado generalmente para distribuir señales adicionales, tales como por ejemplo señales de reloj, sí como para proporcionar tensión de alimentación de potencia a los módulos. En algunos IEDs, la anchura de los módulos, es decir, su extensión máxima en una dirección perpendicular al PCB como se define esencialmente por componentes más altos montados encima puede no ser uniforme. Éste es el caso, por ejemplo, de los módulos I/O, que comprenden una pluralidad de abrazaderas para cableado a cables de Cu a varios Transformadores de Instrumentos u otras fuentes de señales analógicas / binarias, o que comprenden componentes voluminosos, tales como transformadores de corriente / tensión montados sobre el PCB. Si el número de tales módulos sobredimensionados y su disposición con relación a otros módulos de tamaño estándar no tienen que estar predefinidos de antemano, el cuadro de panel trasero puede estar equipado con ranuras espaciadas de una manera uniforme para alojar los módulos, con un espaciamiento lateral uniforme de acuerdo con la anchura máxima del módulo. Sin embargo, esto representa un derroche de espacio no deseado. Como una alternativa menos ventajosa en cuanto al coste con un bus de panel trasero algo separado del cuadro de panel trasero, se puede utilizar un cableado de cinta plana para conexión flexible y economizadora de espacio de punto-a-punto entre los módulos.

# ES 2 375 818 T3

Un módulo de hardware de este tipo se conoce, por ejemplo, a partir del documento US-B1-6 650 844.

### Descripción de la invención

10

15

30

35

Por lo tanto, un objetivo de la invención es permitir una disposición flexible y economizadora de espacio de módulos en un Dispositivo Electrónico Inteligente (IED). Este objetivo se consigue por medio de un módulo de hardware y un cuadro de panel trasero de acuerdo con las reivindicaciones 1 y 5, respectivamente. Otras formas de realización preferidas son evidentes a partir de las reivindicaciones dependientes de la patente.

De acuerdo con la invención, un módulo de hardware para un IED está adaptado para acoplarse con una ranura o casquillo de un panel trasero del IED con el fin de comunicarse, en un modo de punto-a-punto sobre un sistema de bus de panel trasero en serie que comprende dicha ranura, con dos módulos adyacentes en el IED. El módulo comprende un selector de fuente para seleccionar, en el modo de recepción, entre recepción de señales transmitidas a través de una ranura adyacente más próxima, que es preferida, o a través de una ranura más próxima siguiente. En este contexto, "cerca" y "más próxima siguiente" se refieren a la disposición espacial y, en particular, lineal de las ranuras sobre el panel trasero del IED con respecto a la ranura acoplada por el propio módulo de hardware. Además, se entiende que la ranura más próxima siguiente es, a su vez, una ranura más próxima a la ranura más próxima original. El selector de fuentes evalúa las señales digeridas hacia un lado trasero de un cuatro de circuito del módulo, estando el lado trasero sustancialmente desprovisto de componentes electrónicos. Esta dirección de la comunicación se designa como dirección "descendente" a continuación.

En una variante preferida de la invención, el propio módulo está adaptado para transmitir una señal en la dirección "descendente" en paralelo tanto a una ranura más próxima como también a una ranura más próxima siguiente.

20 En otra variante preferida de la invención, el módulo está configurado permanentemente para recibir exclusivamente en una dirección "ascendente" opuesta a la dirección "descendente", señales desde un módulo adyacente que está acoplado con una ranura más próxima, si el módulo tiene una anchura estándar, o desde un módulo adyacente que está acoplado a una ranura más próxima siguiente, si la anchura del módulo excede una anchura estándar.

En general, los controladores LVDS internos de Matriz de Puerta Programable en el Campo (FPGA) son suficientemente potentes para un bus de panel trasero que utiliza Señalización Diferencial de Baja Tensión en una topología de comunicación bidireccional (full dúplex).

En una forma de realización ventajosa de la invención, un cuadro de panel trasero comprende un número de ranuras distribuidas de una manera uniforme para el alojamiento de módulos, en el que una distancia lateral entre las ranuras está correlacionada con la anchura del módulo estándar, y en el que los módulos de acoplamiento forman una disposición de cuadros de extensión orientados geométricamente en paralelo. Dos trayectorias o canales de señales, impresos o soportados de otra manera por el cuadro de panel trasero, terminan en cada ranura y conectan este último a una fuente en una ranura más próxima o una ranura más próxima siguiente.

Cada una de las dos trayectorias de señales puede ser una trayectoria completamente individual o aislada que interconecta dos ranuras. De manera alternativa, ambas trayectorias de señales pueden comprende una bifurcación o unión, desde la que se deriva otra trayectoria de la señal. Las dos derivaciones que tienen un origen común una ranura fuente particular terminan en una ranura más próxima o en una ranura adyacente más próxima siguiente, respectivamente. Esta topología requiere un controlador individual de señales por módulo fuente y dirección de comunicación, y se emplea de manera ventajosa en dirección "ascendente", donde la resistencia de terminación y el receptor están conectados a una sola de las dos derivaciones.

Un IED que comprende un panel trasero y un módulo de hardware, como se ha descrito anteriormente, es particularmente adecuado para un uso en la automatización de subestaciones, ya que reduce al mínimo los requerimientos de espacio y presenta una topología de conexión de bus de panel trasero que da lugar solamente a un número limitado de líneas de transmisión relativamente cortas no utilizadas y, por lo tanto, da lugar a una alta integridad de las señales y a buena Compatibilidad Electromagnética (EMC) y resistencia a la Descarga Electrostática (ESD).

# Breve descripción de los dibujos

El asunto objeto de la invención se explicará con más detalle en el texto siguiente con referencia a formas de realización ejemplares preferidas, que se ilustran en los dibujos adjuntos, en los que:

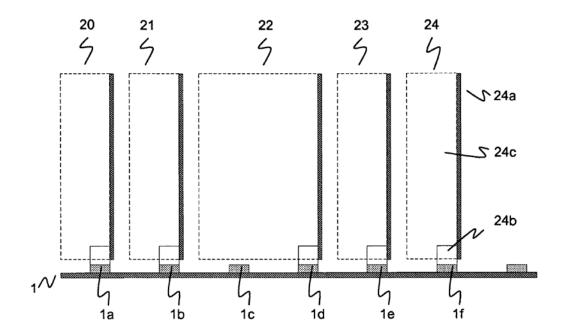

La figura 1 ilustra de forma esquemática una vista de la sección transversal de un IED con cinco módulos.

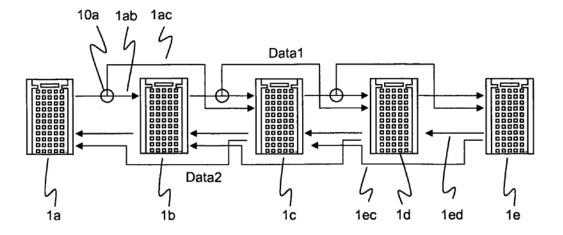

La figura 2 ilustra una vista superior de un panel trasero con cinco ranuras.

La figura 3 es una tabla que resume el flujo de señales entre cuatro ranuras adyacentes, y

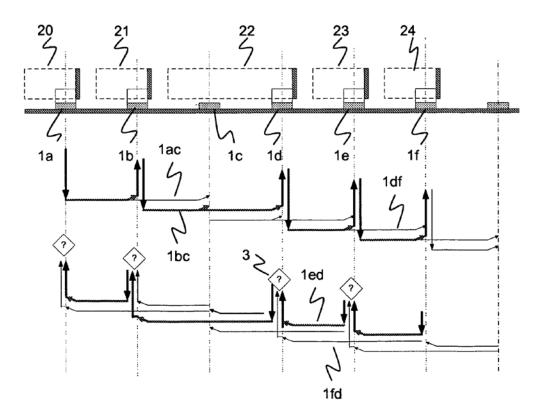

La figura 4 muestra algunas trayectorias de rutas entre-módulos, líneas no utilizadas y líneas de comunicaciones no

#### utilizadas.

10

25

30

35

40

45

50

55

Los símbolos de referencia utilizados en los dibujos y sus significados se indican en forma de resumen en la lista de designaciones. En principio, las partes idénticas están provistas con los mismos símbolos de referencia en las figuras.

### 5 Descripción detallada de formas de realización preferidas

Los IEDs de módem en Automatización de Subestaciones utilizan con frecuencia una señalización en serie de alta velocidad con topología de punto-a-punto con el fin de intercambiar paquetes de datos entre un módulo base o módulo maestro y módulos de extensión que comprenden funcionalidad múltiple para fines de protección, control y supervisión en sistemas de potencia eléctrica. Todas las conexiones relacionadas con el intercambio de datos entre módulos se realizan a través de un Cuadro de Circuito Impreso (PCB) de panel trasero pasivo. Los paquetes de datos son transmitidos de módulo a módulo hasta que se alcanza el módulo de destino. Con el fin de alojar módulos con una anchura que excede la distancia entre dos ranuras físicas del cuadro de panel trasero, se necesita algún tipo de mecanismo de selección o de conmutación para asegurar la comunicación o bien con la ranura siguiente o con la ranura siguiente excepto un a.

La figura 1 ilustra de forma esquemática una vista interna del IED en la sección transversal a lo largo de la intersección de un cuadro de panel trasero 1. Cada uno de los módulos comprende un PCB 24a y un conector de panel trasero 24b para conectar eléctricamente el módulo al panel trasero. A la izquierda de cada PCB se indica un espacio 24c para los componentes eléctricos con líneas discontinuas, donde el módulo central 22 tiene claramente una anchura que está en algún lugar entre la anchura individual y el doble de la anchura estándar de los otros módulos. Sobre el cuadro de panel trasero, se disponen ranuras 1a a 1f espaciadas iguales, donde la distancia entre dos ranuras adyacentes corresponde a la anchura del módulo estándar.

La figura 2 ilustra de forma esquemática una vista superior del plano trasero con cinco ranuras 1a a 1e, cada una de las cuales está en forma de una matriz rectangular de 55 conectores de pines individuales, es decir, conectores del tipo macho o hembra para acoplarse con conectores de contra parte correspondientes de un conector de panel trasero. Las conexiones eléctricas entre las ranuras se ilustran como líneas continuas, donde cada conexión o línea corresponde a dos trazas de conductores (positiva y negativa) impresas sobre el cuatro de panel trasero y que terminan en una pareja de dos de los conectores de pines anteriores. Una señal Data1 es propagada desde la ranura más izquierda 1a, que aloja un módulo básico o módulo maestro, en una dirección "ascendente" hacia las otras ranuras 1b a 1e que, a su vez, aloja módulos de extensión (no se muestran los módulos en la figura 2). Todas las conexiones "ascendentes" entre módulos advacentes comprenden una bifurcación o unión-"Y" 10a. desde la que se transmite la señal Data1 en paralelo sobre dos líneas de derivación 1ab, 1ac hasta la ranura más próxima 1b y hasta la ranura más próxima siguiente 1c. Por lo tanto, cualquier señal "ascendente" cuando es emitida por un módulo fuente a través de una pareja sencilla de pines es destinada inherentemente a dos anuras advacentes. Por otra parte, las señales Data2 que son propagadas en una dirección "descendente" desde la derecha hacia la izquierda pueden actuar de esta manera a través de dos trayectorias 1ed, 1ec totalmente distintas, teniendo su origen ambas en pares distintos de conectores de pines en la ranura fuente 1e y que terminan en la ranura más próxima 1d y en la ranura adyacente más próxima siguiente, respectivamente.

La figura 3 es una tabla que resume el flujo de señales anteriores entre cuatro ranuras adyacentes. La señal Data1 "ascendente" es generada como dout1 y es recibida como din1a en la ranura adyacente y como din1b en la ranura alejada. Las señales Data2 "descendentes" son preparadas como dout2a y dout2b y son recibidas como din2a y din2b en la ranura adyacente y en la ranura alejada, respectivamente.

En la figura 4, los módulos de la figura 1 se ilustran en parte, junto con trayectorias de rutas intra-módulos como se indica por flechas verticales debajo de cada módulo, así como travectorias de ruta inter-módulos como se indica por flechas horizontales. La comunicación inter-módulos comprende, en una dirección "ascendente" desde la izquierda hacia la derecha, emitir por el primer módulo 20 y colocado más a la izquierda, un mensaje hacia el segundo módulo 21 (flecha en negrilla). En virtud de la bifurcación 10a mencionada anteriormente en o cerca de la ranura 1b, la misma señal es emitida también a la ranura 1c no utilizada a lo largo de una derivación o línea de comunicación 1ac no utilizada. El segundo módulo 21 emite, a su vez, señales a lo largo de una traza exclusiva en el cuadro del panel trasero hasta la ranura 1c y, además, hasta la ranura 1d que aloja un módulo 22 sobredimensionado. El módulo 22 transmite, además, las señales "ascendentes" hacia módulos 23 y 24 adyacentes. No obstante, con el módulo 24 que conoce su anchura estándar y, por lo tanto, el hecho de que debe existir un módulo 23 próximo adyacente, la señal desde el módulo 22 es ignorada por el módulo 24 que, a su vez, convierte a la derivación 1df en una línea de comunicación no utilizada. Esto se puede conseguir de manera más fácil omitiendo o interrumpiendo, en el PCB del módulo 24, la traza de conductor que conduce hacia los conectores de contra parte de la derivación 1df. Las consideraciones de la calidad de las señales de Data1 "ascendente" en las formas de realización anteriores no requieren una resistencia de terminación para las derivaciones no utilizadas, ni en el cuadro de panel trasero ni en el propio módulo.

# ES 2 375 818 T3

En la mitad inferior de la figura 4, cada módulo de transmisión emite las señales Data2 en dirección opuesta o "descendente" (desde la derecha hacia la izquierda) sobre trayectorias distintas tanto a la ranura más próxima como también a la ranura adyacente más próxima siguiente. Puesto que el módulo de recepción 22 ejemplar tiene una resistencia de terminación de 100 ohmios tanto para la trayectoria 12d desde el módulo adyacente más próximo 23 como para la trayectoria 1fd desde el módulo adyacente siguiente al más próximo 24, está en una posición para determinar si la tensión diferencial está próxima a 0 voltios, o si existe un controlador LV en el otro extremo de cada trayectoria de la señal. El módulo de recepción puede determinar de esta manera si existe o no la señal desde el módulo adyacente más próximo (data2a) y/o la señal desde el módulo siguiente más próximo (data2b). En el caso de que se reciban ambas señales, se selecciona la que procede desde el módulo adyacente próximo 23 para procesamiento posterior, haciendo que toda la trayectoria 1fd desde el módulo adyacente alejado 24 se convierta en una línea no utilizada con terminación adecuada. Por otra parte, si durante una cantidad específica de tiempo de típicamente 100 ns después de la conexión de la potencia o después de un reseteado no se detecta ninguna señal desde el módulo localizado próximo, un selector de fuente 3 en el receptor selecciona de forma automática la señal desde el módulo localizado alejado. Durante el funcionamiento normal hasta que se inicie la siguiente conexión de la potencia o proceso de reseteado, la selección anterior permanece, en general, inalterada.

# Lista de signos de referencia

5

10

15

| 20 | 1<br>1a – 1f<br>1ab, 1ac, 1df<br>1ed, 1ec, 1fd<br>10a<br>20 – 24 | Cuadro de panel trasero<br>Ranura<br>Derivación "ascendente"<br>Trayectoria "descendente"<br>Bifurcación<br>Módulo |

|----|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|    | 20 24<br>20a                                                     | PCB                                                                                                                |

|    | 20b                                                              | Conector de panel trasero                                                                                          |

| 25 | 20c                                                              | Espacio para componentes electrónicos                                                                              |

|    | 3                                                                | Selector de fuente                                                                                                 |

### **REIVINDICACIONES**

1.- Un módulo de hardware (20 – 24) para un Dispositivo Electrónico Inteligente IED, que comprende un cuadro de circuito (24a), componentes electrónicos montados sobre el cuadro de circuito, y un conector de panel trasero (24b) para acoplamiento en una ranura (1a-1f) de un panel trasero (1) del IED, estando adaptado el módulo (20 – 24) para recibir, sobre un bus en serie de panel trasero, y para procesar una señal desde un módulo fuente (22; 23) del IED, caracterizado porque el módulo (20-24) comprende un selector de fuente (3) que está adaptado para determinar si un módulo adyacente se acopla con la ranura más próxima (1c; 1e) del panel trasero y, en caso afirmativo, para seleccionar este módulo (23) como el módulo fuente, así como, en caso negativo, para seleccionar un módulo (22) adyacente que se acopla con la ranura (1d) más próxima siguiente del panel trasero como el módulo fuente.

5

20

25

- 2.- El módulo de acuerdo con la reivindicación 1, **caracterizado porque** está adaptado para transmitir, como un módulo fuente (23), una señal a una ranura más próxima (1d) así como a una ranura (1c) más próxima siguiente.

- 3.- El módulo de acuerdo con la reivindicación 1, **caracterizado porque** está configurado para recibir, de acuerdo con una anchura del módulo (20-24) señales desde una ranura más próxima (1a) o una ranura más próxima siguiente (1b).

- 4.- El módulo de acuerdo con la reivindicación 1, caracterizado porque comprende una Matriz de Puerta Programable en el Campo FPGA con un controlador incrustado para Señalización Diferencial de Baja Tensión LVDS.

- 5.- Un cuadro de panel trasero (1) para un IED, que comprende ranuras (1a-1f) espaciadas regularmente y adaptadas para alojar e interconectar en comunicación, a través de un bus de panel trasero en serie, un número de módulos de hardware (20-24) de acuerdo con una de las reivindicación es anteriores, **caracterizado porque** el cuadro de panel trasero comprende dos trayectorias de señales (1bc, 1ac; 1ed, 1fd) que conduce hacia una ranura (1c; 2d) y que procede desde una ranura más próxima (1b; 1e) y una ranura más próxima siguiente (1a; 1f).

- 6.- El cuadro de panel trasero de acuerdo con la reivindicación 5, **caracterizado porque** la trayectoria de la señal desde la ranura más próxima siguiente (1a) comprende una bifurcación (10a), desde la que otra trayectoria de la señal (1ab) conduce hasta la ranura más próxima (1b).

- 7.- Uso de un cuadro de panel rasero de acuerdo con la reivindicación 5 ó 6 y de módulos de hardware de acuerdo con las reivindicaciones 1 a 4 en un IED para Automatización de Subestaciones.

Fig. 1

Fig. 2

| slot n | slot n+1 | slot n+2 | slot n+3 |

|--------|----------|----------|----------|

| dout1⇒ | ⇔din1a   | ⇒din1b   |          |

|        | dout1⇒   | ⇔din1a   | ⇒din1b   |

|        |          |          | -        |

|        |          | din2a⇔   | ⇔ dout2a |

|        | din2b⇔   |          | ⇔ dout2b |

|        | din2a⇔   | ⇔ dout2a |          |

| din2b⇔ |          | ⇔ dout2b |          |

Fig. 3

Fig. 4