OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 380 750

51 Int. Cl.: **G06K 19/07**

7 (2006.01)

| $\sim$ | `                           |                            |

|--------|-----------------------------|----------------------------|

| (12)   | TRADUCCIÓN DE PATENTE EUROI | D = V                      |

|        | INADUCCION DE FATENTE EURO  | $\Gamma$ $\square$ $\land$ |

**T**3

- 96 Número de solicitud europea: 08290289 .1

- 96 Fecha de presentación: 27.03.2008

- Número de publicación de la solicitud: 1975855

(97) Fecha de publicación de la solicitud: 01.10.2008

- 54 Título: Tarjeta de microprocesador

- 30 Prioridad: 30.03.2007 FR 0754193

73 Titular/es:

OBERTHUR TECHNOLOGIES

50, Quai Michelet

92300 Levallois-Perret , FR

45 Fecha de publicación de la mención BOPI: 18.05.2012

(72) Inventor/es:

Stranges, Lorenzo y Chamley, Olivier

Fecha de la publicación del folleto de la patente: 18.05.2012

74 Agente/Representante:

Linage González, Rafael

ES 2 380 750 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

Tarjeta de microprocesador

#### 5 Descripción

La presente invención se refiere a una tarjeta de microprocesador. Más en particular, se refiere a tarjetas de microprocesador conformes a la norma ISO 7816 y a tarjetas de microprocesador conformes a la norma MMC (*MultiMedia Card*, tarjeta multimedia).

10

Algunas tarjetas de microprocesador pueden contener múltiples aplicaciones almacenadas en una memoria no volátil, por ejemplo una ROM o una EEPROM, es decir, su microprocesador contiene en memoria códigos ejecutables (o interpretables) de múltiples aplicaciones de procesamiento de datos y está adaptado para ejecutarlos. En algunos casos, las tarjetas de microprocesador pueden incluir al mismo tiempo una aplicación con un alto requisito de seguridad y una aplicación con requisito de seguridad moderado.

15

Aplicaciones con un alto requisito de seguridad son normalmente aplicaciones de pago, por ejemplo, o aplicaciones que identifican al titular (pasaporte, carné de identidad). Los clientes exigen un alto nivel de seguridad en estas aplicaciones y esto necesita evaluaciones particularmente lentas y costosas, por ejemplo según criterios comunes, realizadas por una organización certificada independiente. Algunas evaluaciones de un diseño de una tarjeta con procesador pueden tardar más de un año y costar decenas de miles de euros. Si la aplicación evoluciona se requiere una evaluación adicional, posiblemente a menor escala.

20

Aplicaciones con un requisito de seguridad moderado incluyen, por ejemplo, aplicaciones de telefonía móvil (por ejemplo, identificación de abonado de red de telefonía móvil) y aplicaciones de transporte (por ejemplo, acceso a una red pública de transporte). Estas aplicaciones no necesitan generalmente una certificación o necesitan una certificación que es mucho menos lenta y costosa que las mencionadas anteriormente.

25

30

Si estos dos tipos de aplicación coexisten en el mismo microprocesador de tarjeta inteligente, las aplicaciones con requisitos de seguridad moderados deben evaluarse y certificarse según los mismos criterios que las aplicaciones con un alto requisito de seguridad, lo que da lugar a altos costes y largos retrasos.

35

Además, los lectores de tarjeta de microprocesador están adaptados generalmente para leer una tarjeta con microprocesador a través de contactos previstos para este fin en la superficie de la tarjeta con microprocesador, cuya función está generalmente predeterminada y no cambia durante la vida útil del lector. Para adaptarse a una nueva función de un contacto, generalmente es necesario modificar los componentes electrónicos del lector, lo que generalmente no es posible (a un coste razonable) por parte de los consumidores que utilizan estos lectores.

40

Además, el número de contactos según la norma ISO 7816 está limitada a ocho, cinco de los cuales se utilizan para el protocolo que se ajusta a la norma ISO 7816 (c1, c2, c3, c5, c7), dos pueden usarse para un protocolo USB de alta velocidad (por ejemplo, c4 y c8), o tres en el caso de un protocolo MMC, lo que limita la capacidad de evolución de las tarjeta de microprocesador.

45

La presente invención tiene como objetivo eliminar estos inconvenientes.

A partir de las publicaciones FR 2680262, EP 0779598 y NL 9301540 se conocen tarjetas con múltiples chips en las que se recibe una señal de selección para conmutar medios de conmutación de la tarjeta, de manera que el contacto de E/S de la tarjeta se conecta directamente al chip seleccionado.

50

En el documento DE 4406704, una unidad de conexión de un microcontrolador decide qué microcontrolador de una tarjeta con múltiples chips va a utilizarse.

Para este fin, un primer aspecto de la presente invención está dirigido a una tarjeta de microprocesador, como se define en la reivindicación 1.

55

Gracias a estas aportaciones, un lector de tarjeta de microprocesador puede enviar comandos a los dos microprocesadores sin ser necesaria la utilización de contactos adicionales en comparación con la situación en la que solo se controla a un microprocesador. Además, la seguridad del primer y del segundo microprocesador puede certificarse de manera independiente.

60

Según características particulares, el primer microprocesador está adaptado para ejecutar un primer software de aplicación que determina los comandos de microprocesador que van a transmitirse al segundo microprocesador.

Según características particulares, la tarjeta según la presente invención comprende contactos eléctricos externos destinados a transportar señales de control, estando conectados dichos contactos eléctricos externos solamente al primer microprocesador.

5 Según características particulares, el primer microprocesador comprende medios para controlar el segundo microprocesador mediante comandos conformes a la norma ISO 7816.

Gracias a estas aportaciones, un lector puede enviar comandos APDU (*Application Protocol Data Unit*, unidad de datos de protocolo de aplicación) a ambos microprocesadores.

Según características particulares, la tarjeta según la presente invención comprende al menos una línea de entrada/salida según la norma ISO 7816 que conecta los dos microprocesadores y se utiliza para intercambiar información entre los dos microprocesadores.

- Según características particulares, una conexión de reloj conecta los dos microprocesadores, suministrando el primer microprocesador al segundo microprocesador, en conformidad con la norma ISO 7816, una señal de reloj en función de una señal de reloj interna al primer microprocesador.

- Gracias a estas aportaciones, los dos microprocesadores pueden funcionar con diferentes relojes, por ejemplo sincronizados a diferentes frecuencias.

Según características particulares, el primer microprocesador comprende medios para inhibir dicha señal de reloj suministrada al segundo microprocesador.

- Gracias a estas aportaciones, si el segundo microprocesador comprende medios para seleccionar un modo en espera en ausencia de señales de reloj, en particular para economizar la corriente suministrada por el lector, lo que puede ser particularmente crítico cuando el lector está en un objeto portátil alimentado por batería, tal como un teléfono móvil, el primer microprocesador puede ordenar a todo o a parte del segundo microprocesador que pase a un modo en espera.

- Según características particulares, el primer microprocesador está adaptado para suministrar una señal de reinicio al segundo microprocesador en conformidad con la norma ISO 7816.

- La conexión de señal de reinicio corresponde al contacto c2 de la norma ISO 7816.

10

30

35

- Según características particulares, los dos microprocesadores están conectados en paralelo a dos contactos de alimentación enrasados.

- Según la norma ISO 7816, el contacto c1 "Vcc" y el contacto c5 "GND" suministran energía a una tarjeta de microprocesador.

- Gracias a estas aportaciones, es sencillo suministrar energía a ambos microprocesadores.

- Según características particulares, los dos microprocesadores son partes de dos microcircuitos diferentes.

- Gracias a estas aportaciones, al menos uno de los dos microprocesadores puede ser un microprocesador ya existente o un microprocesador utilizado de manera independiente, posiblemente solo, en otras tarjetas, lo que permite utilizar un microprocesador que ya esté certificado y/o de menor coste.

- 50 Según características particulares, el primer microprocesador utiliza un nivel de seguridad inferior al del segundo microprocesador.

- Gracias a estas aportaciones, un lector de tarjeta de microprocesador que implementa solamente el nivel de seguridad del primer microprocesador puede hacer funcionar al primer microprocesador. Además, el segundo microprocesador puede haber aumentado su seguridad porque sus comandos provienen exclusivamente del primer microprocesador.

- Los expertos en la materia conocen ampliamente los niveles de seguridad. En particular, los microprocesadores y aplicaciones bancarias se certifican generalmente mediante el procedimiento de criterios comunes (correspondiente a la norma ISO 15408) en un nivel igual o superior al EAL4 (Evaluation Assurance Level 4, nivel 4 de garantía de evaluación), normalmente en el nivel EAL4+. Por otro lado, los microprocesadores y las aplicaciones de telefonía móvil no se certifican generalmente según los criterios comunes. Esto se debe a que en el campo de la telefonía móvil hay requisitos más bajos en lo que respecta a la seguridad y requisitos más altos en lo que respecta al tiempo

de respuesta de la tarjeta, en comparación con el campo de los pagos.

Según características particulares, el primer microprocesador implementa una aplicación de identificación de abonado de red de telefonía móvil.

5

- Según características particulares, el segundo microprocesador implementa una aplicación de pago.

- Según características particulares, el segundo microprocesador se ajusta a la norma Europay Mastercard Visa (EMV).

10

Según características particulares, el primer microprocesador comprende medios para la comunicación con una interfaz de comunicaciones inalámbricas de un lector de tarjeta.

15

- Por consiguiente, por ejemplo en el caso de un teléfono móvil provisto de medios de comunicación según la norma NFC (*Near Field Communication,* comunicación de campo cercano), el pago puede llevarse a cabo utilizando un microprocesador de pago ya existente certificado según los criterios comunes.

- Según características particulares, dichos medios de comunicación utilizan un protocolo de cable único (SWP, *single wire protocol*) como el protocolo de comunicaciones.

20

- Según características particulares, el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta a través de contactos enrasados de la tarjeta.

- Según características particulares, el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta que incluyen una interfaz de comunicaciones inalámbricas.

- Según características particulares, el primer microprocesador comprende medios para identificar un comando destinado al primer microprocesador y para identificar un comando destinado al segundo microprocesador.

- 30 Según características particulares, los medios de identificación están adaptados para identificar, en cada comando destinado al segundo microprocesador, datos que indican que dicho comando está destinado al segundo microprocesador.

- Según características particulares, los medios de identificación están adaptados para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se transmiten por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no transmite al segundo microprocesador ningún comando procedente del lector.

40

Un segundo aspecto de la presente invención está dirigido a un procedimiento de comunicación, como se define en la reivindicación 23.

- 45 Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el primer microprocesador determina, según un primer software de aplicación, los comandos de microprocesador que van a transmitirse al segundo microprocesador.

- Según características particulares, durante la etapa de transmisión por parte del primer microprocesador al segundo microprocesador, el primer microprocesador controla al segundo microcontrolador mediante comandos conformes a la norma ISO 7816.

- Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el primer microprocesador suministra al segundo microprocesador, en conformidad con la norma ISO 7816, una señal de reloj en función de una señal de reloj interna al primer microprocesador.

- Según características particulares, el procedimiento según la presente invención comprende una etapa en la que se inhibe la señal de reloj suministrada al segundo microprocesador en función de los comandos recibidos desde el exterior de la tarjeta mediante el primer microprocesador.

60

55

Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el primer microprocesador suministra un señal de reinicio al segundo microprocesador según la norma ISO 7816.

Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el primer microprocesador procesa los comandos recibidos desde el exterior de la tarjeta y una etapa en la que el segundo microprocesador procesa los comandos recibidos desde el primer microprocesador, donde el procesamiento del primer microprocesador utiliza un nivel de seguridad inferior al del procesamiento del segundo microprocesador.

Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el primer microprocesador ejecuta una aplicación de identificación de abonado de red de telefonía móvil.

Según características particulares, el procedimiento según la presente invención comprende una etapa en la que el segundo microprocesador ejecuta una aplicación de pago.

Según características particulares, el primer microprocesador utiliza medios para la comunicación con una interfaz de comunicaciones inalámbricas de un lector de tarjeta.

Según características particulares, durante la etapa de transmisión al exterior de la tarjeta, el primer microprocesador utiliza un protocolo de cable único (SWP) como el protocolo de comunicaciones.

Según características particulares, durante al menos una etapa de transmisión, el primer microprocesador utiliza al menos un contacto enrasado de la tarjeta para comunicarse con un lector de tarjeta de microprocesador.

Según características particulares, durante al menos una etapa de transmisión, el primer microprocesador utiliza medios de comunicación que incluyen una interfaz de comunicaciones inalámbricas.

25 Según características particulares, el procedimiento según la presente invención comprende una etapa de identificación de un comando destinado al primer microprocesador y/o de un comando destinado al segundo microprocesador.

Según características particulares, durante la etapa de identificación se procesan los datos de cada comando destinado al segundo microprocesador y que indican que dicho comando está destinado al segundo microprocesador.

Según características particulares, durante la etapa de identificación, el modo de funcionamiento del primer microprocesador se conmuta entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

Un tercer aspecto de la presente invención está dirigido a un lector de tarjeta de microprocesador, como se define en la reivindicación 38.

Según características particulares, el lector de tarjeta según la presente invención comprende medios para controlar al segundo microprocesador a través del primer microprocesador mediante comandos conformes a la norma ISO 7816.

Según características particulares, el lector de tarjeta según la presente invención comprende medios para identificar un comando destinado al microprocesador y medios para identificar un comando destinado al segundo microprocesador.

Según características particulares, el lector de tarjeta según la presente invención comprende medios para introducir en cada comando destinado al segundo microprocesador datos que permiten que el primer microprocesador detecte que es un comando destinado al segundo microprocesador.

Según características particulares, el lector de tarjeta según la presente invención comprende medios para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

5

15

20

5

35

45

40

55

60

Según características particulares, el lector de tarjeta según la presente invención utiliza un nivel de seguridad con una aplicación del primer microprocesador inferior al utilizado con una aplicación del segundo microprocesador.

Según características particulares, el lector de tarjeta según la presente invención utiliza junto con el primer microprocesador una aplicación de identificación de abonado de red de telefonía móvil.

Según características particulares, el lector de tarjeta según la presente invención utiliza junto con el segundo microprocesador una aplicación de pago.

10 Según características particulares, el lector de tarjeta según la presente invención comprende medios de comunicaciones inalámbricas para la comunicación con el primer microprocesador.

Según características particulares, dichos medios de comunicación utilizan el protocolo de cable único (SWP) como el protocolo de comunicaciones.

Según características particulares, el lector de tarjeta según la presente invención comprende medios de comunicaciones inalámbricas para la comunicación con un lector externo.

Según características particulares, los medios de comunicaciones inalámbricas para la comunicación con un lector externo utilizan un protocolo de comunicación de campo cercano.

Un cuarto aspecto de la presente invención está dirigido a un teléfono móvil que comprende un lector de tarjeta como el explicado de manera concisa anteriormente.

Un quinto aspecto de la presente invención está dirigido a un procedimiento para proporcionar una tarjeta de microprocesador, como se define en la reivindicación 51.

Las ventajas, objetivos y características particulares de estos procedimientos, de este lector y de este teléfono son similares a los de la tarjeta que es el objeto de la presente invención, como se ha explicado antes brevemente, por lo que no vuelven a describirse.

Otras ventajas, objetivos y características particulares de la presente invención surgirán a partir de la siguiente descripción proporcionada a modo de ejemplo y de manera no limitativa con referencia a los dibujos adjuntos, en los que:

35

40

30

5

15

20

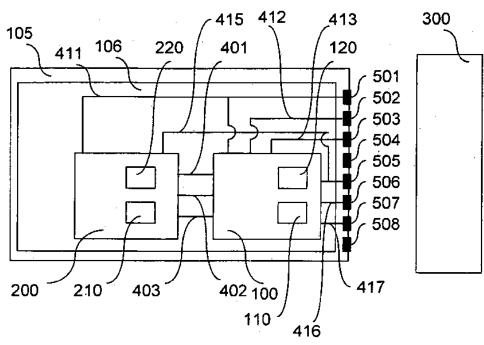

- la figura 1 representa esquemáticamente una primera realización particular de la tarjeta y del lector que son el objeto de la presente invención.

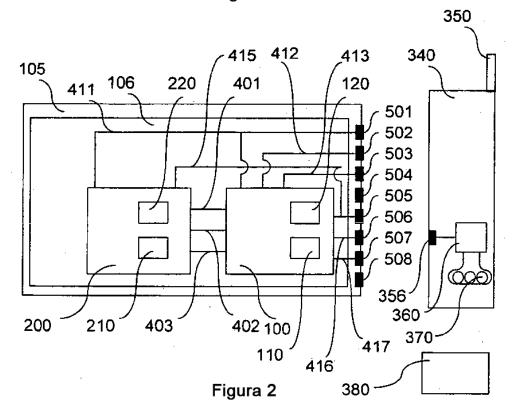

- la figura 2 representa esquemáticamente una segunda realización particular de la tarjeta y del lector que son el objeto de la presente invención,

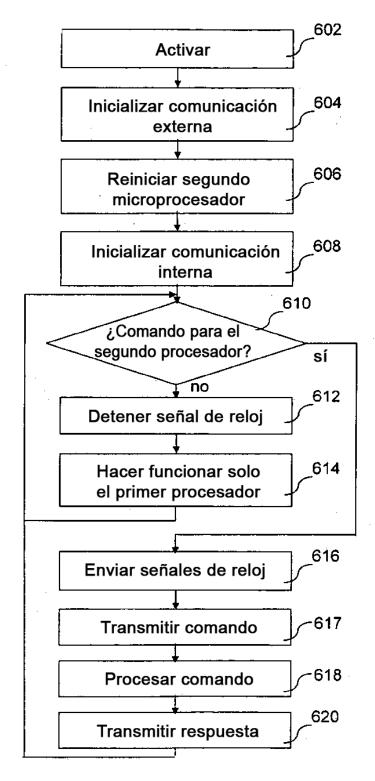

- la figura 3 representa en forma de diagrama de flujo las etapas de una realización particular del procedimiento que es el objeto de la presente invención,

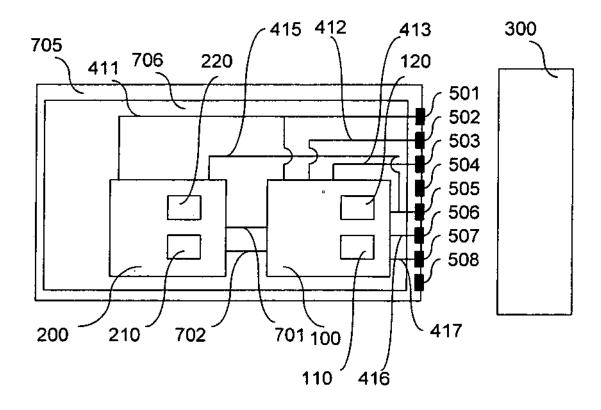

- la figura 4 representa esquemáticamente una tercera realización de la tarjeta y del lector que son el objeto de la presente invención, y

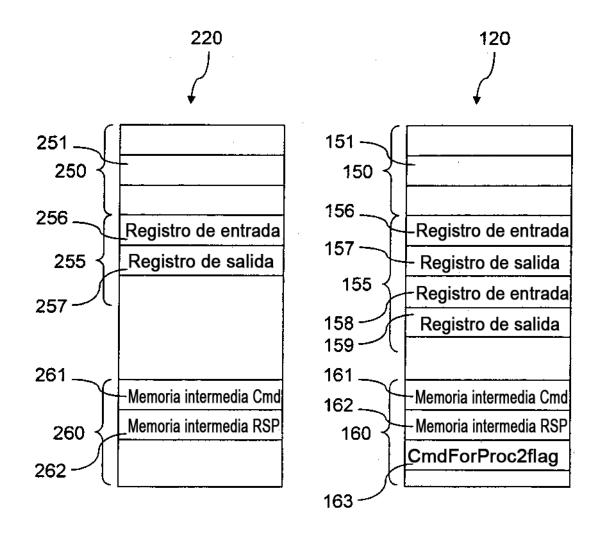

- la figura 5 representa el contenido de memorias asociadas con dos procesadores.

45

60

La figura 1 muestra una tarjeta 105 que incluye un módulo electrónico 106 que comprende un primer microcircuito 100, un segundo microcircuito 200, contactos enrasados 501 a 508 destinados a conectarse a un lector 300 de tarjeta, y conexiones eléctricas que conectan los microcircuitos 100 y 200 entre sí y a los contactos enrasados.

El primer microcircuito 100 comprende un primer microprocesador 110 asociado a una primera memoria 120 que contiene instrucciones de código ejecutable (o interpretable) de una primera aplicación, como se muestra en la figura 5. El segundo microcircuito 200 comprende un segundo microprocesador 210 asociado a una segunda memoria 220 que contiene instrucciones de código ejecutable (o interpretable) de una segunda aplicación, como se muestra en la figura 5. Cada uno de los microcircuitos 100 y 200 es un microcontrolador que incluye un microprocesador y una memoria, por ejemplo.

En la primera y en la segunda aplicación, el primer microprocesador 110 utiliza preferentemente un nivel de seguridad inferior al del segundo microprocesador 210. En lo sucesivo, "seguridad" significa la capacidad de resistir ataques, fallos o pérdidas de datos, pero no incluye la capacidad de continuar con el funcionamiento en condiciones ambientales adversas.

En realizaciones particulares, un "nivel de seguridad" se refiere más en particular a la capacidad de resistir ataques procedentes de partes no autorizadas.

En realizaciones particulares, un "nivel de seguridad" se refiere más en particular a procedimientos conocidos por el experto en la materia como "procedimientos de criterios comunes" (por ejemplo, correspondientes a la norma ISO 15408). En estos procedimientos de criterios comunes, un "nivel alto" puede considerarse igual o superior al EAL4 (nivel 4 de garantía de evaluación).

5

Por ejemplo, la primera aplicación es una aplicación para identificar abonados de una red de telefonía móvil, conocida como un módulo de identificación de abonado (SIM, subscriber identification module) y la segunda aplicación es una aplicación de pago a través de banco, por ejemplo en conformidad con la norma EMV (Europay Mastercard Visa). Como alternativa, el microprocesador 110 es más seguro que el microprocesador 210.

10

Los expertos en la materia conocen ampliamente los niveles de seguridad. En particular, los microprocesadores y las aplicaciones bancarias se certifican generalmente mediante el procedimiento de criterios comunes (correspondiente a la norma ISO 15408) en un nivel igual o superior al EAL 4 (nivel 4 de garantía de evaluación), normalmente en el nivel EAL4+. Por otro lado, los microprocesadores y las aplicaciones de telefonía móvil no se certifican generalmente según los criterios comunes. Esto se debe a que en el campo de la telefonía móvil hay requisitos más bajos en lo que respecta a la seguridad y requisitos más altos en lo que respecta al tiempo de respuesta de la tarjeta, en comparación con el campo de los pagos.

15

Si la primera aplicación es una aplicación de telefonía móvil, el lector 300 de tarjeta es un teléfono móvil.

20

Una conexión interna 401 de entrada/salida interconecta los dos microprocesadores 110 y 210 y permite que se intercambie información entre los mismos. Los intercambios de información a través de la conexión interna 401 se ajustan preferentemente a la norma ISO 7816. Una conexión interna 402 de reloj transmite una señal de reloj desde el primer microprocesador 110 al segundo microprocesador 210, permitiendo al primero sincronizar o inhibir el funcionamiento del segundo.

25

Más en particular, la señal de reloj suministrada por el primer microprocesador 110 al segundo microprocesador 210 puede estar basada en una señal de reloj que es interna al primer microprocesador 110. Por ejemplo, la señal de reloj suministrada al segundo microprocesador 210 puede tener una frecuencia que sea:

30

- en instantes particulares, la frecuencia de la señal de reloj interna al primer microprocesador 110 dividida por un número entero,

- en otros instantes cero. v

- en otros instantes, la misma que la frecuencia de la señal de reloj interna al primer microprocesador 110.

35

La conmutación entre estas frecuencias suministradas al segundo microprocesador 210 puede depender de comandos, del último comando recibido desde el lector de tarieta, o de un procesamiento interno realizado por el primer microprocesador 110.

40

Una conexión interna de reinicio 403 transmite una señal de reinicio desde el primer microprocesador 110 hasta el segundo microprocesador 210, permitiendo al primero ordenar al segundo que se reinicie.

En la realización representada en la figura 1, los contactos 501 a 508 se ajustan a la norma ISO 7816.

45

El primer contacto 501, denotado como "c1" en la norma ISO 7816, está conectado al primer microprocesador 110 y al segundo microprocesador 210 mediante una primera conexión externa 411. Este primer contacto 501 y esta primera conexión externa 411 transmiten un voltaje de alimentación de CC denotado generalmente como "Vcc" a los microprocesadores 110 y 210 desde el lector 300.

50

El segundo contacto 502, denotado como "c2" en la norma ISO 7816, está conectado al primer microprocesador 110 mediante una segunda conexión externa 412. Este segundo contacto 502 y esta segunda conexión externa 412 transmiten una señal de reinicio, denotada generalmente como "RST", para reiniciar el microprocesador 110.

55

El tercer contacto 503, denotado como "c3" en la norma ISO 7816, está conectado al primer microprocesador 110 mediante una tercera conexión externa 413 y transmite una señal de reloi, denotada generalmente como "CLK", de manera que el lector 300 pueda sincronizar el funcionamiento del primer microprocesador 110.

El cuarto contacto 504, denotado como "c4" en la norma ISO 7816, no está conectado a ninguno de los microprocesadores 110 ó 210.

60

El quinto contacto 505, denotado como "c5" en la norma ISO 7816, está conectado al primer microprocesador 110 y al segundo microprocesador 210 mediante una quinta conexión externa 415. Este quinto contacto 505 y esta quinta conexión externa 415 están conectados a tierra, denotada generalmente como "GND", para completar el circuito que suministra energía a los microprocesadores 110 y 210 desde el lector 300.

5

10

15

30

45

El sexto contacto 506, denotado como "c6" en la norma ISO 7816, está conectado al primer microprocesador 110 mediante una sexta conexión externa 416 y transmite una señal de datos, denotada aquí como "SWP", que implementa el protocolo de cable único (SWP) para las comunicaciones entre el primer microprocesador 110 y el lector 300. Por ejemplo, el lector 300 envía comandos a la tarjeta 100 utilizando este contacto 506.

El séptimo contacto 507, denotado como "c7" en la norma ISO 7816, está conectado al primer microprocesador 110 mediante una séptima conexión externa 417 y transmite datos, denotados generalmente como "E/S", de manera que el lector 300 y el primer microprocesador 110 pueden intercambiar datos. Por ejemplo, el lector 300 envía comandos a la tarjeta 100 utilizando este contacto 507.

El octavo contacto 508, denotado como "c8" en la norma ISO 7816, no está conectado a ninguno de los microprocesadores 110 ó 210.

En otras realizaciones, el primer microprocesador 110 comprende medios de recepción conformes a un protocolo para las comunicaciones con una interfaz de comunicaciones inalámbricas que se ajusta al protocolo de cable único (SWP).

- La figura 2 muestra la tarjeta 105 mostrada en la figura 1 y un lector que consiste en un teléfono móvil 340 que tiene una antena 350 y un circuito 360 de interfaz. El circuito 360 de interfaz es del tipo campo cercano, por ejemplo en conformidad con la norma NFC, tiene una antena 370 de interfaz y está conectado a un contacto 356 para las comunicaciones con el contacto 506 de la tarjeta 105.

- Un lector 380 provisto de una interfaz de comunicaciones de campo cercano, por ejemplo en conformidad con la norma NFC, se comunica con el teléfono móvil 340 a través de la interfaz 360.

- En este caso, "campo cercano" se refiere a una distancia inferior a 1 metro, preferentemente inferior a 50 cm, y normalmente inferior a 20 cm. Esto depende, por ejemplo, de que los medios de comunicación se ajusten a la norma de comunicación de campo cercano (NFC) o la norma 14443 de la Organización Internacional de Normalización (ISO, *International Standardization Organization*) relacionada con la identificación mediante radiofrecuencia (RFID, radio-frequency identification), no estando la invención limitada a estos protocolos.

- Una ventaja de la comunicación de campo cercano es que permite a un usuario llevar a cabo una comunicación inalámbrica de manera intencionada y voluntaria acercando un dispositivo portátil a un lector fijo, normalmente a pocos centímetros. En el caso de una tarjeta de pago con microcircuito sin contactos, por ejemplo, con dimensiones conformes a la norma ISO 7816, por ejemplo, esta distancia limita el riesgo de que se realice un cobro en la cuenta del titular de la tarjeta, sin que éste lo haya indicado expresamente, al acercarse su tarjeta a pocos centímetros de un lector apropiado, llevándose a cabo de ese modo una operación de pago entre el lector y su tarjeta.

En el caso de aplicaciones con altos requisitos de seguridad, por ejemplo aplicaciones de transacciones o de pago, el lector 380 envía comandos al segundo microprocesador 210 y recibe respuestas del mismo. Estos comandos están adaptados de manera que el primer microprocesador 110 puede reconocer que están destinados al segundo microprocesador 210, tal y como se ha explicado anteriormente. Para este fin, el teléfono móvil 340 o el lector 380 son los dispositivos que realizan la adaptación.

La figura 3 muestra una etapa 602 en la que el lector 300 activa la tarjeta 106. Después, durante una etapa 604, se inicializa la comunicación entre la tarjeta 106 y el lector 300 según la norma ISO 7816.

- Durante una etapa 606, el primer microprocesador 110 envía una señal de reinicio al segundo microprocesador 210, junto con una señal de reloj para sincronizar el funcionamiento del segundo microprocesador 210. En la realización descrita con referencia a la figura 1, el primer microprocesador 110 suministra una señal de reinicio al segundo microprocesador 210 según la norma ISO 7816, señal correspondiente al contacto c2 de la norma ISO 7816.

- Durante una etapa 608, los microprocesadores 110 y 210 inicializan una comunicación entre los mismos. En la realización descrita y mostrada, esta comunicación se lleva a cabo según el protocolo ISO 7816. En esta comunicación, el primer microprocesador 110 se comporta como un lector del segundo microprocesador 210, excepto en el suministro de energía eléctrica.

- Durante una etapa 610, el primer microprocesador 110 recibe un comando desde el lector 300. Este comando se recibe por la tarjeta 100 en el contacto 507 (c7), por ejemplo, y se ajusta a la norma ISO 7816 (es un comando APDU) o se recibe a través del contacto 506 (c6) y se ajusta al protocolo SWP. El primer microprocesador 110 determina después si ha recibido un comando del lector 300 destinado al segundo microprocesador 210 durante un

periodo de tiempo predeterminado, por ejemplo los cinco segundos anteriores.

Hay varias maneras para que el primer microprocesador 110 determine si un comando está destinado al segundo microprocesador 210.

5

En este caso, es el lector 300 ó 340 el que genera los comandos. En el caso de la segunda realización mostrada en la figura 2, es el lector externo 340 o el circuito de interfaz NFC 360 el dispositivo que adapta los comandos para que el primer microprocesador 110 reconozca comandos destinados al segundo microprocesador 210. Para este fin, en una primera realización, en cada comando destinado al segundo microprocesador 210 hay datos insertados que permiten al primer microprocesador 110 detectar si es un comando destinado al segundo microprocesador 210. De manera simétrica, cuando el segundo microprocesador 210 envía al primer microprocesador 110 una respuesta destinada al lector 300, inserta en esta respuesta datos que identifican al lector 300 como el destinatario previsto. En una segunda realización, el modo del primer microprocesador 110 conmuta entre:

15

10

- un primer modo de funcionamiento en el que todos los comandos del lector 300 se reenvían por el primer microprocesador 110 al segundo microprocesador 210, y en el que todas las respuestas procedentes del segundo microprocesador 210 se reenvían por el primer microprocesador 110 al lector 300, y

- un segundo modo de funcionamiento en el que el primer microprocesador 110 no reenvía al segundo microprocesador 210 ningún comando procedente del lector 300.

20

Para llevar a cabo la conmutación del modo de funcionamiento del primer microprocesador 110, el lector 300 utiliza, por ejemplo, un comando "select" de APDU (unidad de datos de protocolo de aplicación).

25

Si el primer microprocesador 110 no recibe ningún comando desde el lector 300 destinado al segundo microprocesador 210 durante el periodo de tiempo predeterminado, el primer microprocesador 110 interrumpe la señal de reloj destinada al segundo microprocesador 210, el cual pasa al modo en espera durante una etapa 612. Esta etapa 612 puede implementarse fácilmente por el primer microprocesador 110 utilizando un "temporizador" que realiza una cuenta atrás de la señales de reloj hasta que se alcance un valor predeterminado y después genera una interrupción que interrumpe la transmisión de la señal de reloj al segundo microprocesador 210.

30

35

Si el segundo microprocesador 210 comprende medios para pasar al modo en espera en ausencia de una señal de reloj, la inhibición de la señal de reloj transmitida por el primer microprocesador 110 al segundo microprocesador 210 ahorra la corriente suministrada por el lector, lo que puede ser particularmente crítico si el lector está en un objeto portátil alimentado por batería, tal como un teléfono móvil. En otras realizaciones, el primer microprocesador 110 puede ordenar que una parte del segundo microprocesador 210 pase al modo en espera. Después, el primer microprocesador 110 funciona de una manera conocida para el experto en la materia, por ejemplo como una tarieta SIM en el contexto de una aplicación de telefonía móvil, durante una etapa 614, y vuelve regularmente a la etapa 610. Durante la etapa 614, el primer microprocesador ejecuta cada comando destinado al mismo y envía una respuesta al lector 300.

40

Si en una etapa 610, el primer microprocesador determina que ha recibido un comando desde el lector 300 destinado al segundo microprocesador 210, el primer microprocesador 110 envía la señal de reloj al segundo microprocesador 210, que reanuda su funcionamiento durante una etapa 616. En algunos tipos de microprocesador y algunas maneras de pasar al modo en espera, durante la etapa 616, el primer microprocesador 110 ordena un reinicio del segundo microprocesador 210.

45

Durante una etapa 617, el primer microprocesador 110 reenvía al segundo microprocesador 210 cada comando destinado al segundo microprocesador 210.

50

Como alternativa, el primer microprocesador 110 genera comandos para el segundo microprocesador 210 en función de comandos recibidos desde el lector 300. Como alternativa, el primer microprocesador 110 genera comandos para el segundo microprocesador 210 en función de un comando recibido desde el lector 300 e información almacenada en la memoria asociada 120.

55

Después, el segundo procesador 210 procesa ese comando, que es de tipo APDU en conformidad con la norma ISO 7816, por ejemplo, y devuelve una respuesta al primer microprocesador 110, destinada al lector 300, durante una etapa 618.

Después, durante una etapa 620, el primer microprocesador 110 reenvía la respuesta recibida desde el segundo microprocesador 210 al lector 300 y vuelve a la etapa 610.

60

Aplicaciones de la presente invención incluyen tarjetas de microprocesador conformes a la norma ISO 7816 y tarjetas de microprocesador conformes a la norma MMC.

Aplicaciones con un alto requisito de seguridad, por ejemplo aplicaciones de pago o identificación (pasaporte, carné de identidad), están almacenadas preferentemente en la memoria 220 y se ejecutan por el segundo microprocesador 210. La memoria 220 es preferentemente una memoria no volátil, por ejemplo una memoria de solo lectura (ROM, *read-only memory*).

5

10

Por otro lado, aplicaciones con un requisito de seguridad moderado, por ejemplo aplicaciones de telefonía móvil (por ejemplo aplicaciones de identificación de abonado de red de telefonía móvil) o aplicaciones de transporte (por ejemplo una tarjeta que da acceso a una red pública de transporte) están guardadas en la memoria 120 y se ejecutan por el primer microprocesador 110. Estas aplicaciones no necesitan generalmente una certificación o pueden necesitar una certificación que es mucho menos lenta y costosa que la de las aplicaciones con un alto requisito de seguridad.

Por lo tanto, la presente invención permite que ambos tipos de aplicación coexistan en la misma tarjeta y facilita la actualización de aplicaciones con un requisito de seguridad moderado, sin tener que volver a certificar aplicaciones con un alto requisito de seguridad.

La figura 4 muestra una tarjeta 705 que incluye un módulo electrónico 706 que comprende el primer microcircuito 100, el segundo microcircuito 200, los contactos enrasados 501 a 508 destinados a conectarse al lector 300 de tarjeta, y conexiones eléctricas que conectan los microcircuitos 100 y 200 entre sí y a los contactos enrasados.

20

35

40

50

55

El primer microcircuito 100 y el segundo microcircuito 200 son idénticos a los descritos con referencia a la figura 1, excepto en que están adaptados para comunicarse entre sí utilizando el protocolo de bus serie universal (USB, universal serial bus).

Dos conexiones internas 701 y 702 interconectan los dos microprocesadores 110 y 210 y permiten el intercambio de información entre los mismos. Estas conexiones corresponden a las líneas "D+" y "D-" de la norma USB. A través de estas conexiones internas 701 y 702 se intercambia información según la norma USB.

La implementación del procedimiento que es el objeto de la presente invención que utiliza la tarjeta mostrada en la figura 4 es similar a la mostrada en la figura 3, excepto en las etapas 612 y 616, relacionadas con señales de reloj.

Tal y como se muestra en la Figura 5, en realizaciones particulares, la primera memoria 120 asociada con el primer microprocesador 110 comprende una parte 150 de solo lectura (o ROM), una parte 155 de registros y una parte 160 de acceso aleatorio (o RAM). La parte ROM 150 almacena en particular una aplicación 151 que controla las comunicaciones entre el primer microprocesador 110 y el segundo microprocesador 210.

La parte 155 de registros comprende cuatro registros: un registro 156 de entrada asociado con el lector 300, un registro 157 de salida asociado también con el lector 300, un registro 158 de entrada asociado con el segundo microprocesador y un registro 159 de salida asociado con el segundo microprocesador. La parte RAM 160 comprende una memoria intermedia de comandos "memoria intermedia Cmd" 161, una memoria intermedia de respuestas "memoria intermedia RSP" 162 y una bandera para comandos para el segundo procesador "CmdForProc2flag".

La segunda memoria 220 asociada con el segundo microprocesador 210 comprende una parte 250 de solo lectura (o ROM), una parte 255 de registros y una parte 260 de acceso aleatorio (o RAM). La parte ROM 250 almacena en particular una aplicación 251 que controla las comunicaciones entre el primer microprocesador 110 y el segundo microprocesador 210.

La parte 255 de registros comprende un registro 256 de entrada y un registro 257 de salida. La parte RAM 260 comprende una memoria intermedia de comandos "memoria intermedia Cmd" 261 y una memoria intermedia 262 de respuestas "memoria intermedia RSP".

El microprocesador 110 ejecuta la aplicación 151, que puede ser parte del sistema operativo. Por ejemplo, la aplicación 151 ejecuta las etapas 604, 606, 608, 610, 612, 614, 616, 617 y 620 descritas en relación con la figura 3. En particular, durante la etapa 610, el microprocesador 110 lee un comando del lector 300 de tarjeta en el registro 156 de entrada, copia el contenido del registro 156 de entrada a la memoria intermedia 161 de comandos. Después, si el valor de la bandera *CmdForProc2flag* está fijado a "1", lo que significa que cada comando debe transmitirse al procesador 210, el microprocesador 110 avanza hasta la etapa 616. En caso contrario, el microprocesador 110 avanza hasta la etapa 612.

60

En una realización alternativa, en lugar de decidir si transmitir un comando según el valor de una bandera, se utiliza una función. Los datos de entrada para la misma es el contenido de la memoria intermedia 161 de comandos. Esto permite que se utilicen algunas propiedades del propio comando para determinar si el comando va a transmitirse al

segundo microprocesador. Si esta función devuelve verdadero, el microprocesador 110 avanza hasta la etapa 612.

Durante la etapa 617, el microprocesador 110 copia el contenido de la memoria intermedia 161 de comandos en el registro 159 de salida y escribe el contenido del registro 159 de salida en la conexión interna 401.

El microprocesador 210 ejecuta la aplicación 251, que puede ser parte del sistema operativo. Por ejemplo, la aplicación 251 ejecuta la etapa 618 descrita en relación con la figura 3. Durante la etapa 618, el microprocesador 210 lee un comando de la conexión interna 401 en el registro 256 de entrada, copia el contenido del registro 256 de entrada en la memoria intermedia 261 de comandos, procesa el comando almacenado en la memoria intermedia 261 de comandos, escribe la respuesta en la memoria intermedia de respuestas 262, copia el contenido de la memoria intermedia de respuestas 262 en el registro 257 de salida y escribe el contenido del registro 257 de salida en la conexión interna 401. El microprocesador 110 copia la respuesta de 401 en el registro 158 de entrada, después la respuesta se copia desde el registro 158 al registro 157 y se proporciona al lector.

5

- 15 En otras realizaciones, no mostradas, los microprocesadores utilizan un protocolo de comunicaciones de tarjeta multimedia (MMC).

- Como una alternativa para cada una de las realizaciones de la tarjeta que es el objeto de la presente invención, el primer microprocesador comprende medios de comunicaciones que incluyen una interfaz de comunicaciones inalámbricas.

- Como una alternativa para cada una de las realizaciones, el primer microprocesador y el segundo microprocesador están diseñados para presentar diferentes capacidades para no interrumpir su funcionamiento en condiciones ambientales extremas (por ejemplo, temperaturas extremas, campos electromagnéticos, radiofrecuencias, voltajes de alimentación, vibraciones mecánicas u otras tensiones mecánicas).

#### **REIVINDICACIONES**

1. Tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110) para ejecutar primeras aplicaciones, caracterizada porque dicha tarjeta de microprocesador comprende además un segundo microprocesador (210) para ejecutar segundas aplicaciones, incluyendo dicho primer microprocesador medios para transmitir al segundo microprocesador comandos procedentes desde el exterior (300) de la tarjeta y para transmitir al exterior de la tarjeta respuestas a esos comandos procedentes del segundo microprocesador, estando adaptado el primer microprocesador para utilizar un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del segundo microprocesador.

5

10

25

30

45

- 2. Tarjeta (105, 705) según la reivindicación 1, en la que el primer microprocesador está adaptado para utilizar un nivel de capacidad para resistir ataques procedentes de partes no autorizadas inferior al del segundo microprocesador.

- 3. Tarjeta (105, 705) según cualquiera de las reivindicaciones 1 ó 2, en la que el segundo microprocesador proporciona al menos un nivel de seguridad EAL4 (nivel 4 de garantía de evaluación) definido por la norma ISO 15408.

- 4. Tarjeta (105, 705) según una de las reivindicaciones 1 a 3, caracterizada porque el primer microprocesador está adaptado para ejecutar un primer software (120) de aplicación que determina los comandos de microprocesador que van a transmitirse al segundo microprocesador.

- 5. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 4, caracterizada porque comprende contactos eléctricos externos (502, 503, 504, 506, 507, 508) destinados a transmitir señales de control, estando conectados dichos contactos eléctricos externos solamente al primer microprocesador.

- 6. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 5, caracterizada porque el primer microprocesador comprende medios para controlar el segundo microprocesador mediante comandos conformes a la norma ISO 7816.

- 7. Tarjeta (105, 705) según la reivindicación 6, caracterizada porque comprende al menos una línea (401) de entrada/salida según la norma ISO 7816 que conecta los dos microprocesadores y que se utiliza para intercambiar información entre los dos microprocesadores.

- 35 8. Tarjeta (105, 705) según cualquiera de las reivindicaciones 6 ó 7, caracterizada porque una conexión (402) de reloj conecta los dos microprocesadores, suministrando el primer microprocesador al segundo microprocesador, en conformidad con la norma ISO 7816, una señal de reloj en función de una señal de reloj interna al primer microprocesador.

- 40 9. Tarjeta (105, 705) según la reivindicación 8, caracterizada porque el primer microprocesador comprende medios para inhibir dicha señal de reloj suministrada al segundo microprocesador.

- 10. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 6 a 9, caracterizada porque el primer microprocesador está adaptado para suministrar una señal de reinicio (403) al segundo microprocesador en conformidad con la norma ISO 7816.

- 11. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 10, caracterizada porque los dos microprocesadores están conectados en paralelo a dos contactos de alimentación enrasados.

- 50 12. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 11, caracterizada porque los dos microprocesadores son partes de dos microcircuitos diferentes.

- 13. Tarjeta según una cualquiera de las reivindicaciones 1 a 12, caracterizada porque el primer microprocesador implementa una aplicación de identificación de abonado de red de telefonía móvil.

- 14. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 13, caracterizada porque el segundo microprocesador implementa una aplicación de pago.

- 15. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 14, caracterizada porque el segundo microprocesador se ajusta a la norma *Europay Mastercard Visa* (EMV).

- 16. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 15, caracterizada porque el primer microprocesador comprende medios para la comunicación con una interfaz de comunicaciones inalámbricas de un

lector (300) de tarjeta.

5

20

25

35

40

55

- 17. Tarjeta (105, 705) según la reivindicación 16, caracterizada porque dichos medios de comunicación utilizan un protocolo de cable único (SWP) como el protocolo de comunicaciones.

- 18. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 17, caracterizada porque el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta a través de contactos enrasados de la tarjeta.

- 10 19. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 18, caracterizada porque el primer microprocesador comprende medios para la comunicación con el exterior de la tarjeta que incluyen una interfaz de comunicaciones inalámbricas.

- 20. Tarjeta (105, 705) según una cualquiera de las reivindicaciones 1 a 19, caracterizada porque el primer microprocesador comprende medios para identificar un comando destinado al primer microprocesador y para identificar un comando destinado al segundo microprocesador.

- 21. Tarjeta (105, 705) según la reivindicación 20, caracterizada porque los medios de identificación están adaptados para identificar, en cada comando destinado al segundo microprocesador, datos que indican que dicho comando está destinado al segundo microprocesador.

- 22. Tarjeta (105, 705) según la reivindicación 20, caracterizada porque los medios de identificación están adaptados para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se transmiten por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no transmite al segundo microprocesador ningún comando procedente del lector.

- 23. Procedimiento de comunicación para una tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110), incluyendo el procedimiento una etapa de ejecución de una primera aplicación (120) por parte del primer microprocesador, caracterizado porque dicho procedimiento comprende además:

- una etapa (617) en la que el primer microprocesador reenvía a un segundo microprocesador (210) para la ejecución de segundas aplicaciones de la tarjeta un comando procedente del exterior (300) de la tarjeta

- una etapa (619) en la que el primer microprocesador envía al exterior de la tarjeta una respuesta a un comando procedente del segundo microprocesador,

- una etapa (614) en la que el primer microprocesador procesa comandos recibidos desde el exterior de la tarjeta y una etapa (618) en la que el segundo microprocesador procesa comandos recibidos desde el primer microprocesador, donde el procesamiento por parte del primer microprocesador utiliza un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del procesamiento por parte del segundo microprocesador.

- 45 24. Procedimiento según la reivindicación 23, caracterizado porque comprende además una etapa (610) en la que el primer microprocesador determina, según un primer software de aplicación, los comandos de microprocesador que van a transmitirse al segundo microprocesador.

- 25. Procedimiento según cualquiera de las reivindicaciones 23 ó 24, caracterizado porque, durante la etapa de transmisión por parte del primer microprocesador al segundo microprocesador, el primer microprocesador controla al segundo microprocesador mediante comandos conformes a la norma ISO 7816.

- 26. Procedimiento según cualquiera de las reivindicaciones 23 a 25, caracterizado porque comprende una etapa en la que el primer microprocesador suministra al segundo microprocesador, de acuerdo con la norma ISO 7816, una señal (402) de reloj en función de una señal de reloj interna al primer microprocesador.

- 27. Procedimiento según la reivindicación 26, caracterizado porque comprende una etapa de inhibición (612) de la señal de reloj suministrada al segundo microprocesador en función de comandos recibidos desde el exterior de la tarjeta por el primer microprocesador.

- 28. Procedimiento según una cualquiera de las reivindicaciones 23 a 27, caracterizado porque comprende una etapa (606) en la que el primer microprocesador suministra una señal de reinicio al segundo microprocesador según la norma ISO 7816.

- 29. Procedimiento según una cualquiera de las reivindicaciones 23 a 28, caracterizado porque comprende una etapa en la que el primer microprocesador ejecuta una aplicación de identificación de abonado de red de telefonía móvil.

- 30. Procedimiento según una cualquiera de las reivindicaciones 23 a 29, caracterizado porque comprende una etapa en la que el segundo microprocesador ejecuta una aplicación de pago.

5

10

20

25

35

40

45

- 31. Procedimiento según una cualquiera de las reivindicaciones 23 a 30, caracterizado porque, durante la etapa de transmisión al exterior de la tarjeta, el primer microprocesador utiliza medios para la comunicación con una interfaz de comunicaciones inalámbricas de un lector de tarjeta.

- 32. Procedimiento según la reivindicación 31, caracterizado porque, durante la etapa de transmisión al exterior de la tarjeta, el primer microprocesador utiliza un protocolo de cable único (SWP) como el protocolo de comunicaciones.

- 33. Procedimiento según una cualquiera de las reivindicaciones 23 a 32, caracterizado porque durante al menos una etapa de transmisión, el primer microprocesador utiliza al menos un contacto enrasado de la tarjeta para comunicarse con un lector de tarjeta de microprocesador.

- 34. Procedimiento según una cualquiera de las reivindicaciones 23 a 33, caracterizado porque, durante al menos una etapa de transmisión, el primer microprocesador utiliza medios de comunicación que incluyen una interfaz de comunicaciones inalámbricas.

- 35. Procedimiento según una cualquiera de las reivindicaciones 23 a 34, caracterizado porque comprende una etapa de identificación de un comando destinado al primer microprocesador y/o de un comando destinado al segundo microprocesador.

- 36. Procedimiento según la reivindicación 35, caracterizado porque, durante la etapa de identificación, se procesan datos en cada comando destinado al segundo microprocesador y que indican que dicho comando está destinado al segundo microprocesador.

- 30 37. Procedimiento según la reivindicación 35, caracterizado porque, durante la etapa de identificación, el modo de funcionamiento del primer microprocesador conmuta entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

- 38. Lector (300) de tarjeta de microprocesador que incluye medios para la comunicación con un primer microprocesador (110) de una tarjeta (105, 705), caracterizado porque dichos medios de comunicación están adaptados además para transmitir al primer microprocesador un comando procedente del exterior de la tarjeta y destinado a un segundo microprocesador y para recibir una respuesta a un comando desde el segundo microprocesador a través del primer microprocesador, utilizando dicho lector de tarjeta un nivel de capacidad para resistir ataques, fallos o pérdidas de datos, con una aplicación del primer microprocesador, inferior al utilizado con una aplicación del segundo microprocesador.

- 39. Lector (300) de tarjeta según la reivindicación 38, caracterizado porque utiliza un nivel de capacidad para resistir ataques procedentes de partes no autorizadas, con una aplicación del primer microprocesador, inferior al utilizado con una aplicación del segundo microprocesador.

- 40. Lector (300) de tarjeta según cualquiera de las reivindicaciones 38 ó 39, caracterizado porque comprende medios para controlar al segundo microprocesador a través del primer microprocesador mediante comandos conformes a la norma ISO 7816.

- 41. Lector (300) de tarjeta según cualquiera de las reivindicaciones 38 a 40, caracterizado porque comprende medios para identificar un comando destinado al microprocesador y medios para identificar un comando destinado al segundo microprocesador.

- 42. Lector (300) de tarjeta según la reivindicación 41, caracterizado porque comprende medios para introducir en cada comando destinado al segundo microprocesador datos que permiten al primer microprocesador detectar que es un comando destinado al segundo microprocesador.

- 43. Lector (300) de tarjeta según la reivindicación 41, caracterizado porque comprende medios para conmutar el modo de funcionamiento del primer microprocesador entre:

- un primer modo de funcionamiento en el que todos los comandos procedentes del lector se reenvían por el primer microprocesador al segundo microprocesador, y

- un segundo modo de funcionamiento en el que el primer microprocesador no reenvía al segundo microprocesador ningún comando procedente del lector.

- 44. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 43, caracterizado porque utiliza junto con el primer microprocesador una aplicación de identificación de abonado de red de telefonía móvil.

- 45. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 44, caracterizado porque utiliza junto con el segundo microprocesador una aplicación de pago.

5

20

- 46. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 45, caracterizado porque comprende medios de comunicaciones inalámbricas para la comunicación con el primer microprocesador.

- 47. Lector (300) de tarjeta según la reivindicación 46, caracterizado porque dichos medios de comunicación utilizan el protocolo de cable único (SWP) como el protocolo de comunicaciones.

- 48. Lector (300) de tarjeta según una cualquiera de las reivindicaciones 38 a 47, caracterizado porque comprende medios de comunicaciones inalámbricas para la comunicación con un lector externo.

- 49. Lector (300) de tarjeta según la reivindicación 48, caracterizado porque los medios de comunicaciones inalámbricas para la comunicación con un lector externo utilizan un protocolo de comunicación de campo cercano.

- 50. Teléfono móvil (340), caracterizado porque comprende un lector de tarjeta según una cualquiera de las reivindicaciones 38 a 49.

- 51. Procedimiento para proporcionar una tarjeta (105, 705) de microprocesador que incluye un primer microprocesador (110), caracterizado porque dicho procedimiento comprende una etapa de certificación de un segundo microprocesador (210) y una etapa de asociación del primer y del segundo microprocesador en una tarjeta, asociación en la que dicho primer microprocesador comprende medios para reenviar al segundo microprocesador comandos procedentes del exterior (300) de la tarjeta y para transmitir al exterior de la tarjeta respuestas a esos comandos procedentes del segundo microprocesador, en el que el primer microprocesador está adaptado para utilizar un nivel de capacidad para resistir ataques, fallos o pérdidas de datos inferior al del segundo microprocesador.

Figura 1

Figura 3

Figura 4

Figura 5