**ESPAÑA**

11 Número de publicación: 2 382 914

(2006.01) H04L 2//26 (2006.01) H04L 5/00 (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- 96 Número de solicitud europea: 08253372 .0

- 96 Fecha de presentación: 17.10.2008

- 97 Número de publicación de la solicitud: 2056469

97 Fecha de publicación de la solicitud: 06.05.2009

- 54 Título: Aparato y método de procesado de datos

- (30) Prioridad: 30.10.2007 GB 0721271 30.10.2007 GB 0721269 19.11.2007 GB 0722645 20.11.2007 GB 0722728

- (73) Titular/es: SONY CORPORATION 1-7-1 KONAN, MINATO-KU TOKYO, JP

- 45) Fecha de publicación de la mención BOPI: **14.06.2012**

- 72 Inventor/es:

Taylor, Matthew Paul Athol; Asanbeng Atungsiri, Samuel y Wilson, John Nicholas

- 45 Fecha de la publicación del folleto de la patente: 14.06.2012

- (74) Agente/Representante: Curell Aguilá, Mireia

ES 2 382 914 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## **DESCRIPCIÓN**

Aparato y método de procesado de datos.

#### Campo de la invención

La presente invención se refiere a aparatos de procesado de datos que se pueden hacer funcionar para establecer correspondencias de símbolos de entrada sobre señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM). La presente invención se refiere también a un generador de direcciones para su uso en la escritura de símbolos en/lectura de símbolos desde una memoria intercaladora.

Formas de realización de la presente invención pueden proporcionar un transmisor de OFDM.

#### Antecedentes de la invención

15

20

25

30

35

45

50

55

65

10

5

La normativa de Radiodifusión de Vídeo Digital Terrestre (DVB-T) utiliza el Multiplexado por División Ortogonal de Frecuencia (OFDM) para comunicar, a receptores, datos que representan imágenes de vídeo y sonido, a través de una señal de radiocomunicaciones de radiodifusión. Se sabe que existen dos modos para la normativa DVB-T, que son conocidos como el modo 2k y el 8k. El modo 2k proporciona 2.048 subportadoras, mientras que el modo 8k proporciona 8.192 subportadoras. De manera similar, se ha proporcionado un modo 4k para la normativa de Radiodifusión de Vídeo Digital para Portátiles (DVB-H), en el cual el número de subportadoras es 4.096.

Para mejorar la integridad de datos comunicados usando la DVB-T o la DVB-H, se proporciona un intercalador de símbolos para intercalar símbolos de datos de entrada cuando se establecen correspondencias de estos símbolos sobre las señales subportadoras de un símbolo OFDM. Dicho intercalador de símbolos comprende una memoria intercaladora en combinación con un generador de direcciones. El generador de direcciones genera una dirección para cada uno de los símbolos de entrada, indicando cada dirección una de las señales subportadoras del símbolo OFDM sobre la cual se va a establecer la correspondencia del símbolo de datos. En la normativa DVB-T se ha dado a conocer una disposición para el modo 2k y el modo 8k con el fin de generar las direcciones para el establecimiento de correspondencias. De modo similar, para el modo 4k de la normativa DVB-H se ha proporcionado una disposición para generar direcciones para el establecimiento de correspondencias, y en la solicitud de patente europea 04251667.4 se da a conocer un generador de direcciones para implementar este establecimiento de correspondencias. El generador de direcciones comprende un registro de desplazamiento con realimentación lineal que se puede hacer funcionar para generar una secuencia seudoaleatoria de bits, y un circuito de permutación. El circuito de permutación permuta el orden del contenido del registro de desplazamiento con realimentación lineal para generar una dirección. La dirección proporciona una indicación de una de las subportadoras OFDM para transportar un símbolo de datos de entrada almacenado en la memoria intercaladora, con el fin de establecer correspondencias de los símbolos de entrada sobre las señales subportadoras del símbolo OFDM.

40 De acuerdo con otra evolución de la normativa de Radiodifusión de Vídeo Digital Terrestre, conocida como DVB-T2, se ha propuesto que se proporcionen otros modos para comunicar datos.

El documento EP1463256 da a conocer un aparato de procesado de datos que está dispuesto para establecer correspondencias de símbolos de datos de entrada, que van a ser comunicados, sobre un número predeterminado de señales subportadoras de un símbolo OFDM. El aparato de procesado de datos incluye un intercalador que usa una memoria intercaladora y un generador de direcciones para intercalar los símbolos de datos de entrada sobre las subportadoras del símbolo OFDM. El generador de direcciones incluye un registro de desplazamiento con realimentación lineal y un circuito de permutación, los cuales están adaptados para generar direcciones que se pueden usar para intercalar los símbolos de datos de entrada sobre las subportadoras de los símbolos OFDM cuando el número de direcciones es aproximadamente 4k. Por lo tanto, el aparato de procesado de datos es adecuado para ser usado en un transmisor del modo 4k de la DVB-T2.

En la patente US nº 6.353.900 se da a conocer un intercalador para ser usado con la intercalación de símbolos de datos codificados para transmisión y para recepción. El intercalador incluye una memoria intercaladora y un generador de direcciones. El generador de direcciones incluye un registro de desplazamiento con realimentación lineal que genera una secuencia de Números Seudoaleatorios (PN) a partir de la cual se pueden generar las direcciones. Las tomas del registro de desplazamiento con realimentación lineal se seleccionan para producir una secuencia de PN de longitud óptima.

#### 60 Sumario de la invención

Según un aspecto de la presente invención, se proporciona un aparato de procesado de datos que se puede hacer funcionar para establecer correspondencias de símbolos de entrada, que van a ser comunicados, sobre un número predeterminado de señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM). El aparato de procesado de datos comprende un intercalador que se puede hacer funcionar para escribir en una memoria el número predeterminado de símbolos de datos para el establecimiento de correspondencias sobre

las señales subportadoras OFDM, y para leer de la memoria los símbolos de datos para las subportadoras OFDM con el fin de efectuar el establecimiento de correspondencias. La lectura se efectúa en un orden diferente a la escritura, determinándose el orden a partir de un conjunto de direcciones, con el resultado de que los símbolos de datos se intercalan en las señales subportadoras. El conjunto de direcciones está determinado por un generador de direcciones, generándose una dirección para cada uno de los símbolos de entrada con el fin de indicar una de las señales subportadoras sobre la cual se va a establecer una correspondencia del símbolo de datos.

5

10

40

45

50

55

60

El generador de direcciones comprende un registro de desplazamiento con realimentación lineal que incluye un número predeterminado de etapas de registro, y se puede hacer funcionar para generar una secuencia seudoaleatoria de bits de acuerdo con un polinomio generador, y un circuito de permutación y una unidad de control. El circuito de permutación se puede hacer funcionar para recibir el contenido de las etapas del registro de desplazamiento y permutar los bits presentes en las etapas del registro según un orden de permutación, con el fin de formar una dirección de una de las subportadoras OFDM.

La unidad de control se puede hacer funcionar en combinación con un circuito de comprobación de direcciones, para volver a generar una dirección cuando una dirección generada supera una dirección válida máxima predeterminada. El aparato de procesado de datos está caracterizado porque la dirección válida máxima predeterminada es aproximadamente dieciséis mil, el registro de desplazamiento con realimentación lineal tiene trece etapas de registro con un polinomio generador para el registro de desplazamiento con realimentación lineal de R'<sub>k</sub>[12] = R'<sub>k-1</sub>[0]⊕R'<sub>k-1</sub> [1]⊕R'<sub>k-1</sub>[1]⊕R'<sub>k-1</sub>[1]⊕R'<sub>k-1</sub>[1], y el orden de permutación forma, con un bit adicional, una dirección de catorce bits R<sub>k</sub>[n] para el símbolo de datos i-ésimo a partir del bit presente en la etapa de registro n-ésima R'<sub>k</sub>[n] de acuerdo con la tabla:

| Posiciones de bit de R'i | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|--------------------------|----|----|----|---|---|----|---|---|----|----|---|---|---|

| Posiciones de bit de Ri  | 8  | 4  | 3  | 2 | 0 | 11 | 1 | 5 | 12 | 10 | 6 | 7 | 9 |

Aunque, dentro de la normativa DVB-T, se conoce la provisión del modo 2k y el modo 8k, y la normativa DVB-H proporciona un modo 4k, se ha propuesto la provisión de un modo 16k para la DVB-T2. Mientras que el modo 8k proporciona una disposición para establecer una red de una sola frecuencia con suficientes periodos de guarda para adaptarse a retardos mayores de propagación entre transmisores DVB, se sabe que el modo 2k proporciona una ventaja en aplicaciones móviles. Esto es debido a que el periodo de símbolo 2k es solamente la cuarta parte del periodo de símbolo 8k, permitiendo que la estimación del canal se actualice con más frecuencia lo cual permite que el receptor realice con más precisión el seguimiento de la variación de tiempo del canal debida al efecto doppler y otros. Por lo tanto, el modo 2k es ventajoso para aplicaciones móviles.

Para proporcionar un despliegue todavía con mayor dispersión de transmisores DVB dentro de una red de una sola frecuencia, se ha propuesto proporcionar el modo 16k. Para implementar el modo 16k, se debe proporcionar un intercalador de símbolos para establecer correspondencias de los símbolos de datos de entrada sobre las señales subportadoras del símbolo OFDM.

Formas de realización de la presente invención pueden proporcionar un aparato de procesado de datos que se puede hacer funcionar como intercalador de símbolos para establecer correspondencias de símbolos de datos, que van a ser comunicados, sobre un símbolo OFDM, que tiene sustancialmente dieciséis mil señales subportadoras. En una forma de realización, el número de señales subportadoras puede ser un valor sustancialmente entre doce mil y dieciséis mil trescientos ochenta y cuatro. Además, el símbolo OFDM puede incluir subportadoras piloto, que están dispuestas para transportar símbolos conocidos, y la dirección válida máxima predeterminada depende de un número de los símbolos de las subportadoras piloto presentes en el símbolo OFDM. Como tal, el modo 16k se puede proporcionar, por ejemplo, para una normativa DVB, tal como la DVB-T2, la DVB-T o la DVB-H.

El establecimiento de correspondencias de símbolos de datos, que van a ser transmitidos, sobre las señales subportadoras de un símbolo OFDM, en donde el número de señales subportadoras es aproximadamente dieciséis mil, representa un problema técnico que requiere análisis y pruebas de simulación para establecer un polinomio generador apropiado para el registro de desplazamiento con realimentación lineal y el orden de permutación. Esto es debido a que el establecimiento de correspondencias requiere que los símbolos se intercalen sobre las señales subportadoras con el resultado de que símbolos sucesivos del flujo continuo de datos de entrada estén separados en frecuencia por una magnitud lo mayor posible, con el fin de optimizar el rendimiento de los esquemas de codificación de corrección de errores.

Los esquemas de codificación de corrección de errores, tales como la codificación LDPC/BCH, que se ha propuesto para la DVB-T2 presentan un mejor rendimiento cuando el ruido y el deterioro de los valores de símbolos resultantes de la comunicación no presentan ninguna correlación. Los canales de radiodifusión terrestres pueden adolecer de un desvanecimiento correlacionado en los dominios tanto del tiempo como de la frecuencia. Por ello, separando tanto como sea posible símbolos codificados sobre diferentes señales subportadoras del símbolo OFDM, se puede incrementar el rendimiento de esquemas de codificación de corrección de errores.

Tal como se explicará, a partir del análisis de rendimiento por simulación, se ha descubierto que el polinomio

generador para el registro de desplazamiento con realimentación lineal en combinación con el orden del circuito de permutación indicado anteriormente, proporciona un buen rendimiento. Además, proporcionando una disposición que pueda implementar una generación de direcciones para cada uno del modo 2k, el modo 4k y el modo 8k, cambiando las tomas del polinomio generador para el registro de desplazamiento con realimentación lineal y el orden de permutación, se puede proporcionar una implementación rentable del intercalador de símbolos para el modo 16k. Además, un transmisor y un receptor se pueden cambiar entre el modo 2k, el modo 4k, el modo 8k y el modo 16k, cambiando el polinomio generador y los órdenes de permutación. Esto se puede efectuar en software (o mediante la señalización incorporada) con lo cual se proporciona una implementación flexible.

El bit adicional, que se usa para formar la dirección a partir del contenido del registro de desplazamiento con realimentación lineal, se puede producir mediante un circuito de conmutación, que cambia de 1 a 0 para cada dirección, con el fin de reducir la probabilidad de que si una dirección supera la dirección válida máxima predeterminada, entonces la siguiente dirección sea una dirección válida. En un ejemplo, el bit adicional es el bit más significativo.

En un ejemplo, el código de permutación anterior se usa para generar las direcciones con el fin de realizar la intercalación para símbolos OFDM sucesivos. En otros ejemplos, el código de permutación anterior es uno de una pluralidad de códigos de permutación que se cambian para reducir una posibilidad de que se establezcan correspondencias, sobre la misma subportadora de un símbolo OFDM, de bits sucesivos o bits de datos que estén próximos en cuanto a su orden en un flujo continuo de datos de entrada. En un ejemplo, se usa un código de permutación diferente para ejecutar la intercalación entre símbolos OFDM sucesivos. El uso de códigos de permutación diferentes para símbolos OFDM sucesivos puede proporcionar una ventaja en la que el aparato de procesado de datos se puede hacer funcionar para intercalar los símbolos de datos de entrada sobre las señales subportadoras de cada uno de los símbolos OFDM únicamente escribiendo los símbolos de datos en la memoria en un orden secuencial y leyendo los símbolos de datos de la memoria de acuerdo con el conjunto de direcciones generadas por el generador de direcciones.

En las reivindicaciones adjuntas se definen varios aspectos y características de la presente invención. Otros aspectos de la presente invención incluyen un método de establecimiento de correspondencias de símbolos de entrada, que van a ser comunicados, sobre un número predeterminado de señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM), así como un transmisor.

#### Breve descripción de los dibujos

20

25

30

- A continuación se describirán formas de realización de la presente invención, solamente a título de ejemplo, en referencia a los dibujos adjuntos, en los que las partes iguales están provistas de números de referencia correspondientes, y en los cuales:

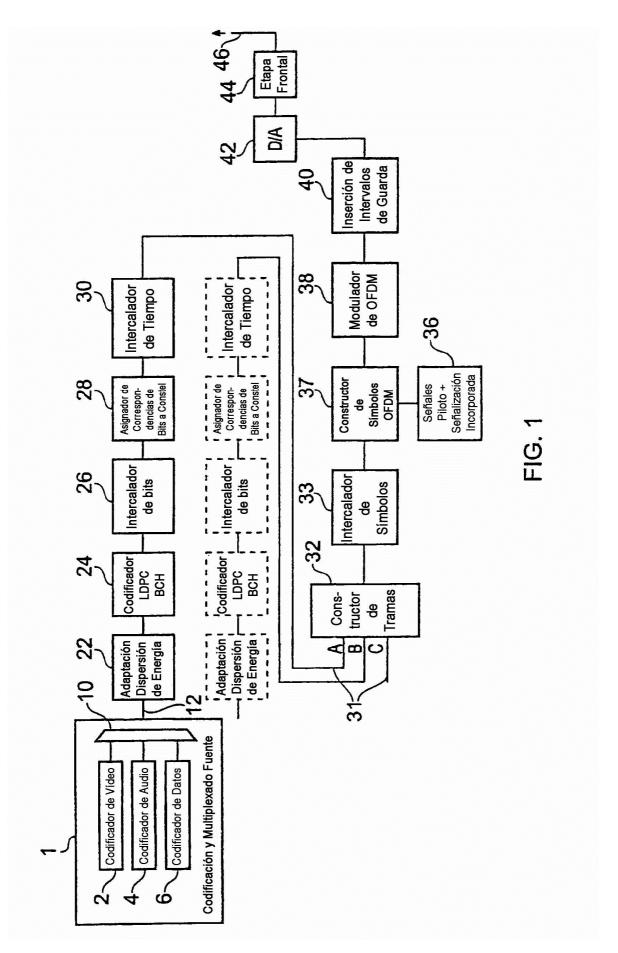

- la figura 1 es un diagrama de bloques esquemático de un transmisor de OFDM Codificado que se puede usar, por ejemplo, con la normativa DVB-T2;

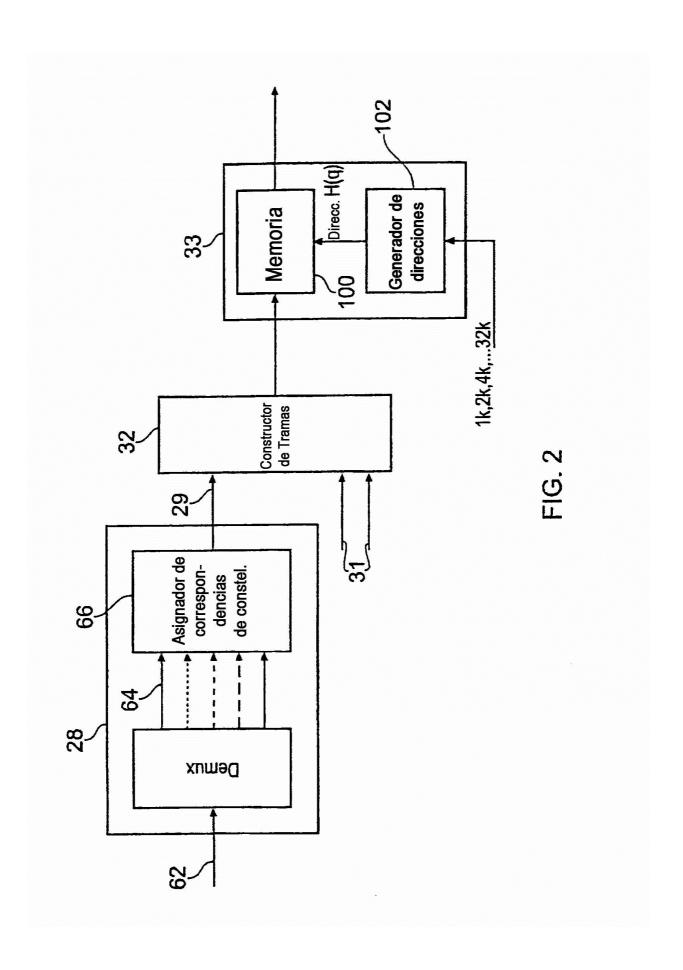

- la figura 2 es un diagrama de bloques esquemático de partes del transmisor mostrado en la figura 1 en el cual un asignador de correspondencias de símbolos y un constructor de tramas ilustran el funcionamiento de un intercalador;

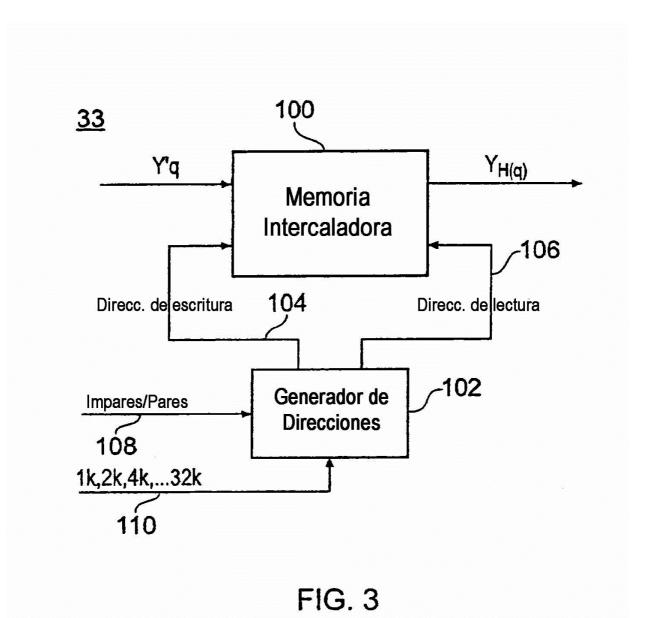

- 45 la figura 3 es un diagrama de bloques esquemático del intercalador de símbolos mostrado en la figura 2;

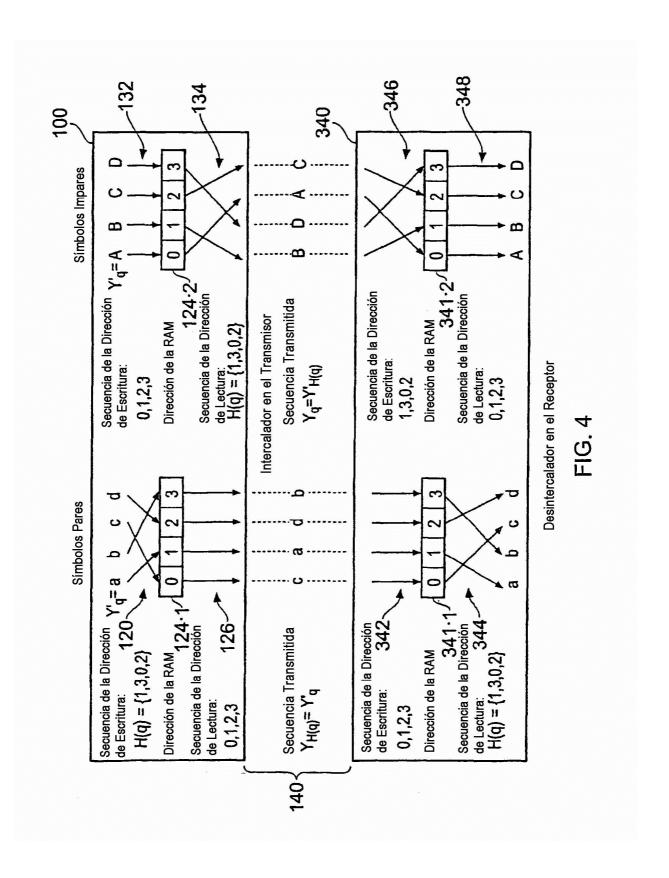

- la figura 4 es un diagrama de bloques esquemático de una memoria intercaladora mostrada en la figura 3, y el correspondiente desintercalador de símbolos del receptor;

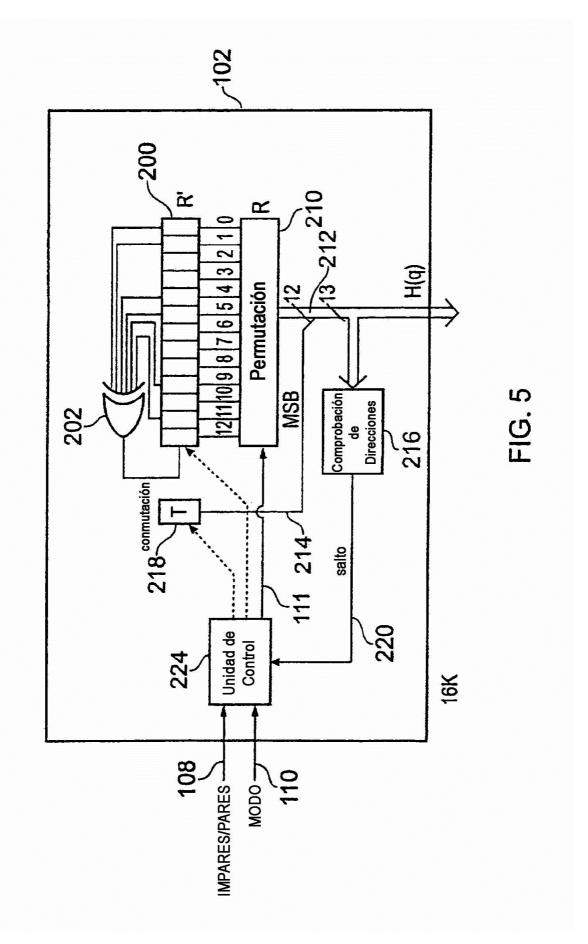

- la figura 5 es un diagrama de bloques esquemático de un generador de direcciones mostrado en la figura 3 para el modo 16k;

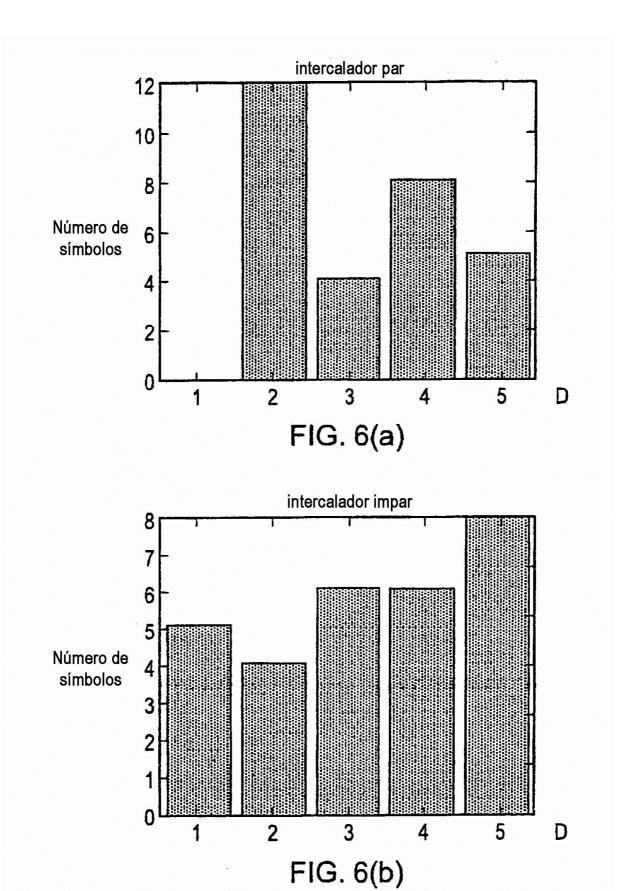

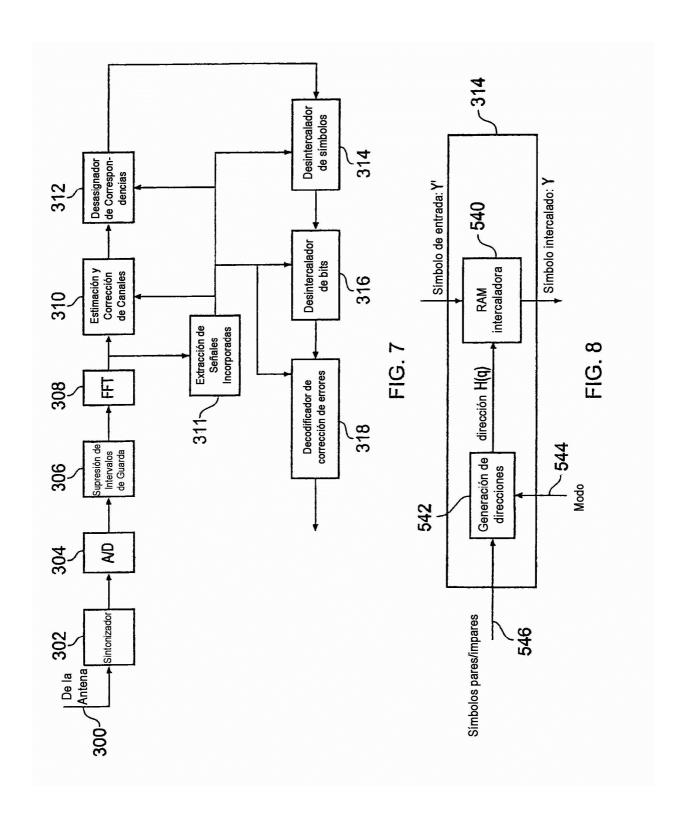

- la figura 6(a) es un diagrama que ilustra resultados correspondientes a un intercalador que usa el generador de direcciones mostrado en la figura 5 para símbolos pares, y la figura 6(b) es un diagrama que ilustra resultados de simulación de diseño para símbolos impares, mientras que la figura 6(c) es un diagrama que ilustra resultados comparativos para un generador de direcciones que usa un código de permutación diferente para símbolos pares y la figura 6(d) es un diagrama correspondiente para símbolos impares;

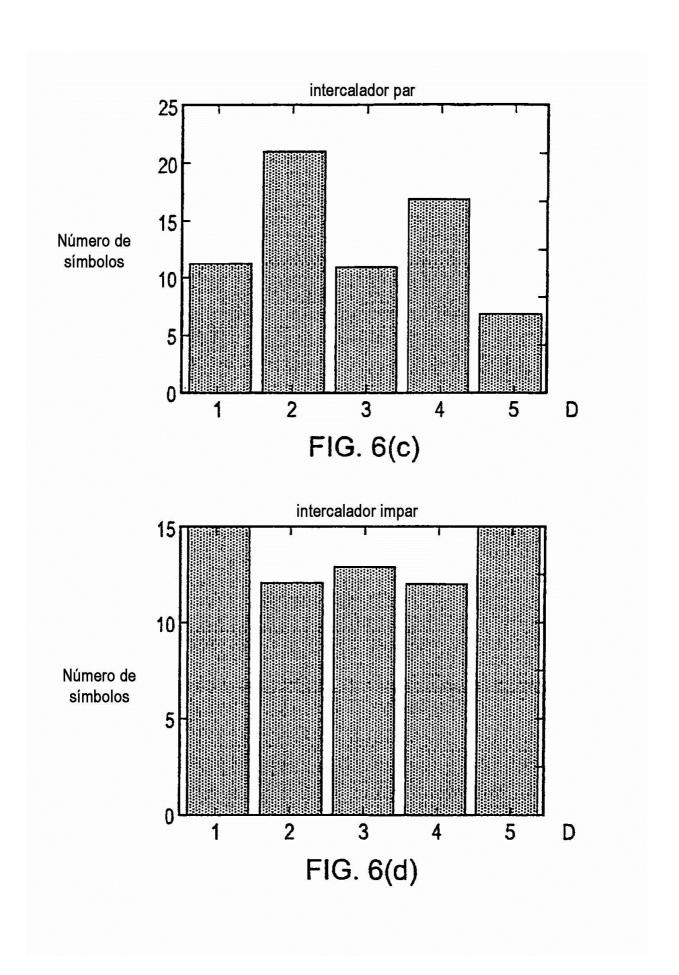

- la figura 7 es un diagrama de bloques esquemático de un receptor de OFDM Codificado que se puede usar, por ejemplo, con la normativa DVB-T2;

- la figura 8 es un diagrama de bloques esquemático de un desintercalador de símbolos que aparece en la figura 7;

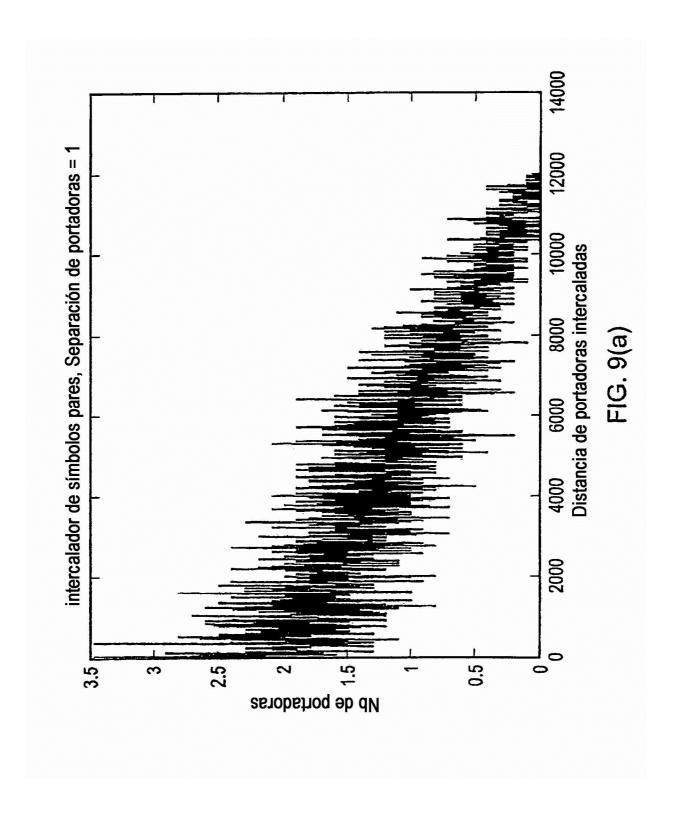

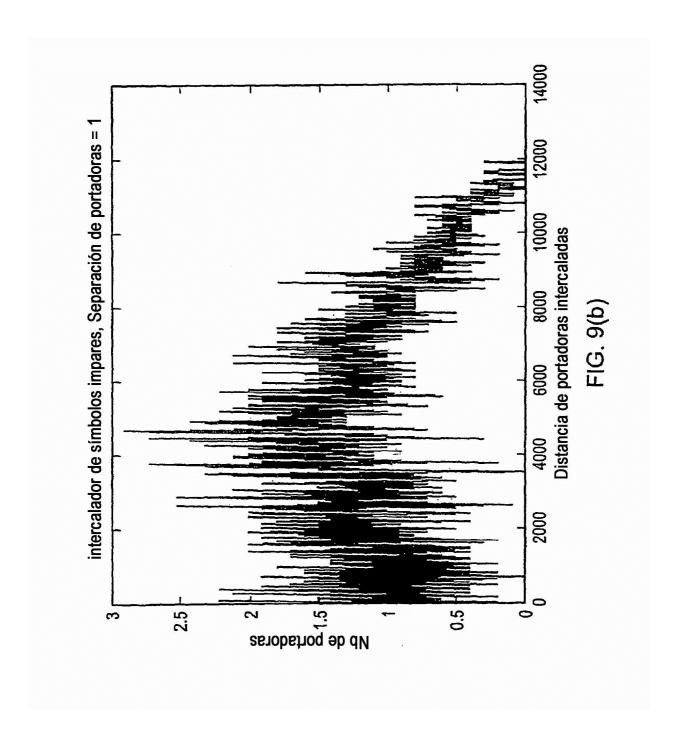

- la figura 9(a) es un diagrama que ilustra resultados para un intercalador que usa el generador de direcciones mostrado en la figura 5 para símbolos OFDM pares, y la figura 9(b) es un diagrama que ilustra resultados para símbolos OFDM impares. Las figuras 9(a) y 9(b) muestran representaciones gráficas de la distancia, en la salida del

intercalador, de subportadoras que eran adyacentes en la entrada del intercalador;

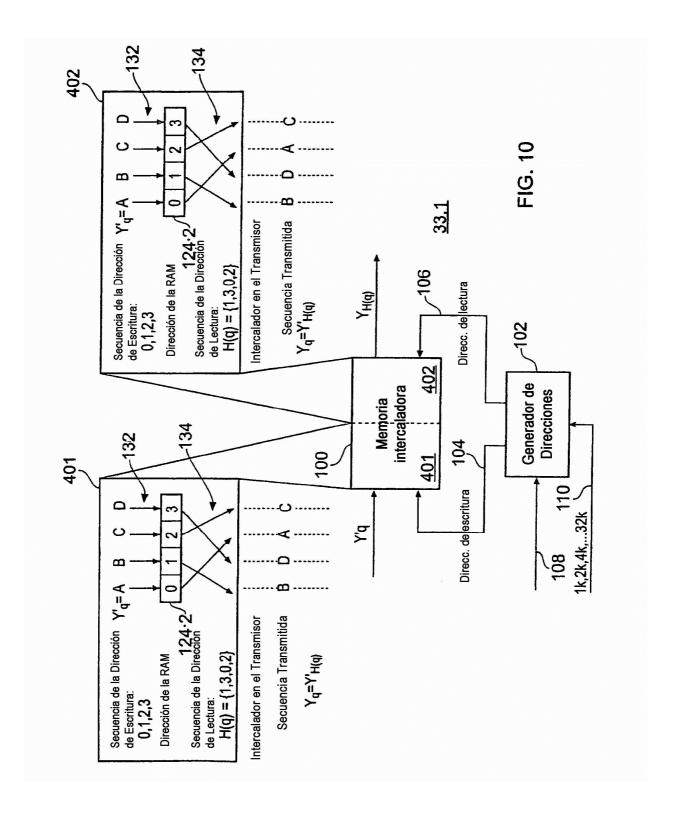

la figura 10 proporciona un diagrama de bloques esquemático del intercalador de símbolos mostrado en la figura 3, que ilustra un modo de funcionamiento en el cual la intercalación se realiza de acuerdo únicamente con un modo de intercalación impar; y

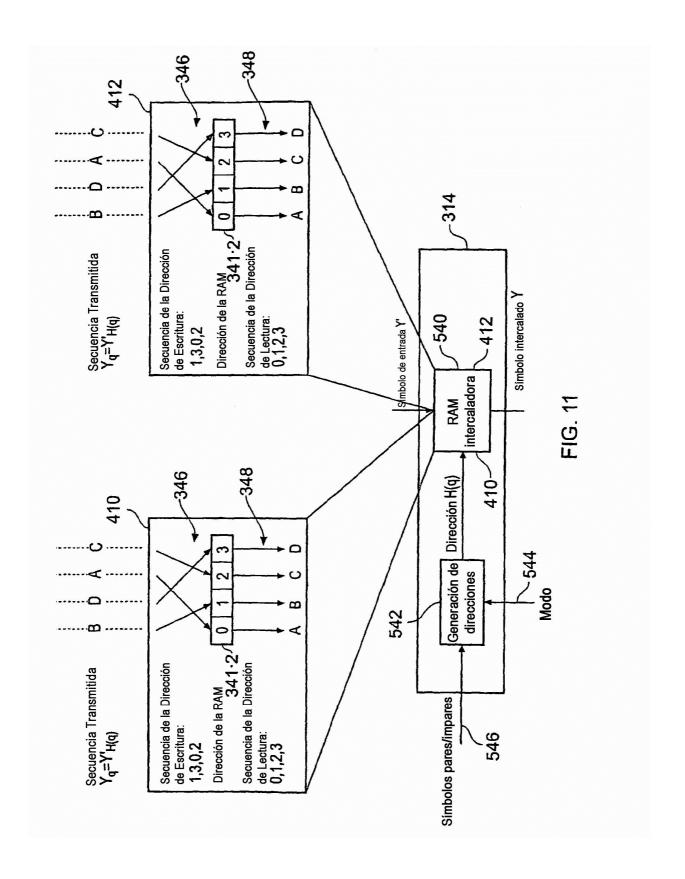

la figura 11 proporciona un diagrama de bloques esquemático del desintercalador de símbolos mostrado en la figura 8, que ilustra el modo de funcionamiento en el cual se realiza la intercalación de acuerdo únicamente con el modo de intercalación impar.

#### Descripción de formas de realización preferidas

Se ha propuesto que el número de modos que están disponibles en la normativa DVB-T2 se debería ampliar de manera que incluya un modo 1k, un modo 16k y un modo 32k. La siguiente descripción se proporciona para ilustrar el funcionamiento de un intercalador de símbolos de acuerdo con la presente técnica, aunque se apreciará que el intercalador de símbolos se puede usar con otros modos y otras normativas de DVB.

La figura 1 proporciona un diagrama de bloques ejemplificativo de un transmisor de OFDM Codificado que se puede usar, por ejemplo, para transmitir imágenes de vídeo y señales de audio de acuerdo con la normativa DVB-T2. En la figura 1, una fuente de programas genera datos que han de ser transmitidos por el transmisor de COFDM. Un codificador de vídeo 2, un codificador de audio 4 y un codificador de datos 6 generan vídeo, audio y otros datos a transmitir, los cuales son suministrados a un multiplexor de programas 10. La salida del multiplexor de programas 10 forma un flujo continuo multiplexado, con otra información necesaria para comunicar el vídeo, el audio y otros datos. El multiplexor 10 proporciona un flujo continuo sobre un canal de conexión 12. Puede haber muchos de estos flujos continuos multiplexados que son suministrados a diferentes ramas A, B, etcétera. Por motivos de simplicidad, solamente se describirá la rama A.

Tal como se muestra en la figura 1, un transmisor de COFDM 20 recibe el flujo continuo en un bloque de adaptación de multiplexado y dispersión de energía 22. El bloque de adaptación de multiplexado y dispersión de energía 22 aleatoriza los datos y suministra los datos apropiados a un codificador de corrección directa de errores 24 que efectúa una codificación de corrección de errores del flujo continuo. Se proporciona un intercalador de bits 26 para intercalar los bits de datos codificados que, para el ejemplo de la DVB-T2, son la salida del codificador de LDCP/BCH. La salida del intercalador de bits 26 se suministra a un asignador de correspondencias de bits a constelación 28, el cual establece correspondencias de grupos de bits sobre un punto de constelación, que se usará para transportar los bits de datos codificados. Las salidas del asignador de correspondencias de bits a constelación 28 son etiquetas de puntos de constelación que representan componentes reales e imaginarios. Las etiquetas de puntos de constelación representan símbolos de datos formados a partir de dos o más bits en función del esquema de modulación usado. A las mismas se les hará referencia como celdas de datos. Estas celdas de datos se hacen pasar a través de un intercalador de tiempo 30 cuyo efecto es intercalar celdas de datos resultantes de múltiples palabras de código LDPC.

Las celdas de datos son recibidas por un constructor de tramas 32, con celdas de datos producidas por la rama B, etcétera, de la figura 1, a través de otros canales 31. A continuación, el constructor de tramas 32 forma secuencias a partir de muchas celdas de datos, que se transportarán sobre símbolos COFDM, en donde un símbolo COFDM comprende varias celdas de datos, estableciéndose una correspondencia de cada celda de datos sobre una de las subportadoras. El número de subportadoras dependerá del modo de funcionamiento del sistema, el cual puede incluir uno de 1k, 2k, 4k, 8k, 16k ó 32k, cada uno de los cuales proporciona un número diferente de subportadoras de acuerdo, por ejemplo, con la siguiente tabla:

Número de subportadoras adaptadas de la DVB-T/H

| Modo | Subportadoras |

|------|---------------|

| 1K   | 756           |

| 2K   | 1.512         |

| 4K   | 3.024         |

| 8K   | 6.048         |

| 16K  | 12.096        |

| 32K  | 24.192        |

De este modo, en un ejemplo, el número de subportadoras para el modo 16k es doce mil noventa y seis. Para el sistema DVB-T2, el número de subportadoras por símbolo OFDM puede variar dependiendo del número de señales piloto y otras portadoras reservadas. Así, en el DVB-T2, a diferencia del DVB-T, el número de subportadoras para transportar datos no es fijo. Las entidades de radiodifusión pueden seleccionar uno de los modos de funcionamiento de entre 1k, 2k, 4k, 8k, 16k, 32k que proporcionan cada uno de ellos un intervalo de subportadoras para datos por símbolo OFDM, de manera que el máximo disponible para cada uno de estos modos es respectivamente 1.024,

5

50

55

45

5

10

15

20

25

30

35

2.048, 4.096, 8.192, 16.384, 32.768. En el DVB-T2, una trama de la capa física está compuesta por muchos símbolos OFDM. Típicamente, la trama comienza con uno o más preámbulos o símbolos OFDM P2, a los cuales les sigue a continuación una serie de símbolos OFDM portadores de carga útil. El final de la trama de la capa física viene marcado por un símbolo de cierre de trama. Para cada modo de funcionamiento, el número de subportadoras puede ser diferente para cada tipo de símbolo. Además, esto puede variar para cada uno según si se selecciona ampliación del ancho de banda, si se habilita la reserva de tono y según qué patrón de subportadoras piloto haya sido seleccionado. Como tal, resulta difícil plantear una generalización para un número específico de subportadoras por símbolo OFDM. No obstante, el intercalador de frecuencia para cada modo puede intercalar cualquier símbolo cuyo número de subportadoras sea menor que o igual al número disponible máximo de subportadoras para el modo dado. Por ejemplo, en el modo 1k, el intercalador funcionaría para símbolos con un número de subportadoras menor que o igual a 1.024 y para el modo 16k con un número de subportadoras menor que o igual a 16.384. La secuencia de celdas de datos a transportar en cada símbolo COFDM se traslada a continuación al intercalador de símbolos 33. Seguidamente, se genera el símbolo COFDM por medio de un bloque constructor de símbolos COFDM 37 que introduce señales piloto y de sincronización suministradas desde un formador de señales piloto y señales incorporadas 36. A continuación, un modulador de OFDM 38 forma el símbolo OFDM en el dominio del tiempo, el cual se suministra a un procesador de inserción de intervalos de guarda 40 para generar un intervalo de guarda entre símbolos, y a continuación a un conversor digital a analógico 42 y finalmente a un amplificador de RF en una etapa frontal de RF 44 para su radiodifusión final por parte del transmisor de COFDM desde una antena 46.

## 20 Provisión de un modo 16K

10

15

25

30

35

40

45

50

60

65

Para crear un nuevo modo 16K, deben definirse varios elementos, uno de los cuales es el intercalador de símbolos de 16K 33. En la figura 2 se muestran más detalladamente el asignador de correspondencias de bits a constelación 28, el intercalador de símbolos 33 y el constructor de tramas 32.

Tal como se ha explicado anteriormente, la presente invención proporciona un mecanismo para proporcionar un establecimiento casi óptimo de correspondencias de los símbolos de datos sobre las señales subportadoras de OFDM. Según la técnica de ejemplo, el intercalador de símbolos se proporciona para efectuar el establecimiento óptimo de correspondencias de símbolos de datos de entrada sobre señales subportadoras de COFDM de acuerdo con un código de permutación y un polinomio generador, que ha sido verificado mediante análisis de simulación.

Tal como se muestra en la figura 2, se proporciona una ilustración ejemplificativa más detallada del asignador de correspondencias de bits a constelación de símbolos 28 y el constructor de tramas 32, con el fin de ilustrar una forma de realización ejemplificativa de la presente técnica. Bits de datos recibidos desde el intercalador de bits 26 a través de un canal 62 se agrupan en conjuntos de bits de los cuales se establecerán correspondencias sobre una celda de datos, de acuerdo con un número de bits por símbolo proporcionado por el esquema de modulación. Los grupos de bits, que forman una palabra de datos, se suministran en paralelo, a través de canales de datos 64, a un procesador de correspondencias 66. A continuación, el procesador de correspondencias 66 selecciona uno de los símbolos de datos, de acuerdo con un establecimiento preasignado de correspondencias. El punto de constelación está representado por un componente real y uno imaginario, que se suministra al canal de salida 29 como uno de un conjunto de entradas para el constructor de tramas 32.

El constructor de tramas 32 recibe las celdas de datos del asignador de correspondencias de bits a constelación 28 a través del canal 29, junto con celdas de datos de los otros canales 31. Después de construir una trama de muchas secuencias de celdas COFDM, las celdas de cada símbolo COFDM se escriben a continuación en una memoria intercaladora 100 y se leen de la memoria intercaladora 100 de acuerdo con direcciones de escritura y direcciones de lectura generadas por un generador de direcciones 102. Según el orden de escritura y de lectura, se logra la intercalación de las celdas de datos, mediante la generación de direcciones apropiadas. El funcionamiento del generador de direcciones 102 y la memoria intercaladora 100 se describirá más detalladamente de forma breve en referencia a las figuras 3, 4 y 5. A continuación, las celdas de datos intercaladas se combinan con símbolos piloto y de sincronización recibidos desde el formador de señalización piloto e incorporada 36 hacia un constructor de símbolos OFDM 37, con el fin de formar el símbolo COFDM, el cual se suministra al modulador de OFDM 38 tal como se ha explicado anteriormente.

## 55 <u>Intercalador</u>

La figura 3 proporciona un ejemplo de partes del intercalador de símbolos 33, que ilustra la presente técnica para intercalar símbolos. En la figura 3, las celdas de datos de entrada del constructor de tramas 32 se escriben en la memoria intercaladora 100. Las celdas de datos se escriben en la memoria intercaladora 100 de acuerdo con una dirección de escritura suministrada desde el generador de direcciones 102 sobre el canal 104, y se leen de la memoria intercaladora 100 de acuerdo con una dirección de lectura suministrada desde el generador de direcciones 102 sobre un canal 106. El generador de direcciones 102 genera la dirección de escritura y la dirección de lectura tal como se explica posteriormente, en función de si el símbolo COFDM es impar o par, lo cual se identifica a partir de una señal suministrada desde un canal 108, y en función de un modo seleccionado, el cual se identifica a partir de una señal suministrada desde un canal 110. Tal como se ha explicado, el modo puede ser uno de entre un modo 1k, un modo 2k, un modo 4k, un modo 8k, un modo 16k o un modo 32k. Tal como se explica posteriormente, la

dirección de escritura y la dirección de lectura se generan de manera diferente para símbolos impares y pares según se explica en referencia a la figura 4, que proporciona una implementación ejemplificativa de la memoria intercaladora 100.

- En el ejemplo mostrado en la figura 4, la memoria intercaladora se muestra de manera que comprende una parte superior 100 que ilustra el funcionamiento de la memoria intercaladora en el transmisor, y una parte inferior 340, que ilustra el funcionamiento de la memoria desintercaladora en el receptor. El intercalador 100 y el desintercalador 340 se muestran juntos en la figura 4 para facilitar la comprensión de su funcionamiento. Tal como se muestra en la figura 4, una representación de la comunicación entre el intercalador 100 y el desintercalador 340, a través de otros dispositivos y a través de un canal de transmisión, se ha simplificado y representado como una sección 140 entre el intercalador 100 y el desintercalador 340. El funcionamiento del intercalador 100 se describe en los párrafos siguientes:

- Aunque la figura 4 proporciona una ilustración de solo cuatro celdas de datos de entrada en un ejemplo de cuatro señales subportadoras de un símbolo COFDM, se apreciará que la técnica ilustrada en la figura 4 se puede ampliar a un número mayor de subportadoras, tal como 756 para el modo 1k, 1.512 para el modo 2k, 3.024 para el modo 4k y 6.048 para el modo 8k, 12.096 para el modo 16k y 24.192 para el modo 32k.

- La asignación de direcciones de entrada y de salida de la memoria intercaladora 100 mostrada en la figura 4 se muestra para símbolos impares y pares. Para un símbolo COFDM par, las celdas de datos se toman del canal de entrada 77 y se escriben en la memoria intercaladora 124.1 de acuerdo con una secuencia de direcciones 120 generada para cada símbolo COFDM por el generador de direcciones 102. Las direcciones de escritura se aplican para el símbolo par de modo que, tal como se ilustra, la intercalación se efectúa mediante la redistribución de las direcciones de escritura. Por lo tanto, para cada símbolo intercalado y(h(q)) = y'(q).

- Para símbolos impares se usa la misma memoria intercaladora 124.2. Sin embargo, tal como se muestra en la figura 4, para el símbolo impar, el orden de escritura 132 se produce en la misma secuencia de direcciones usada para leer el símbolo par anterior 126. Esta característica permite que las implementaciones de los intercaladores de símbolos impares y pares usen solamente una memoria intercaladora 100, siempre que la operación de lectura para una dirección dada se efectúe antes que la operación de escritura. A continuación, las celdas de datos escritas en la memoria intercaladora 124 durante símbolos impares se leen en una secuencia 134 generada por el generador de direcciones 102 para el siguiente símbolo COFDM par, y así sucesivamente. De este modo, únicamente se genera una dirección por símbolo, realizándose simultáneamente la escritura y la lectura correspondientes al símbolo COFDM impar/par.

- En resumen, tal como se representa en la figura 4, una vez que se ha calculado el conjunto de direcciones H(q) para todas las subportadoras activas, se procesa el vector de entrada  $Y' = (y_0, y_1, y_2, ..., y_{Nmax-1})$  para producir el vector intercalado  $Y = (y_0, y_1, y_2, ..., y_{Nmax-1})$  definido por:

- 40  $y_{H(q)} = y'_q$  para símbolos pares, para  $q = 0, ..., N_{max}-1$

30

35

50

55

- $y_q = y'_{H(q)}$  para símbolos impares, para  $q = 0, ..., N_{max}-1$

- En otras palabras, para símbolos OFDM pares, las palabras de entrada se escriben de una manera permutada en una memoria, y se vuelven a leer de una manera secuencial, mientras que para símbolos impares, se escriben secuencialmente y se vuelven a leer permutadas. En el caso anterior, la permutación H(q) queda definida por la siguiente tabla:

Tabla 1: Permutación para un caso sencillo en donde Nmax = 4

| q    | 0 | 1 | 2 | 3 |

|------|---|---|---|---|

| H(q) | 1 | 3 | 0 | 2 |

Tal como se muestra en la figura 4, el desintercalador 340 funciona de manera que invierte la intercalación aplicada por el intercalador 100, aplicando el mismo conjunto de direcciones que el generado por un generador de direcciones equivalente, pero aplicando las direcciones de escritura y lectura a la inversa. Por tanto, para símbolos pares, las direcciones de escritura 342 están en orden secuencial, mientras que las direcciones de lectura 344 son proporcionadas por el generador de direcciones. De forma correspondiente, para los símbolos impares, el orden de escritura 346 se determina a partir del conjunto de direcciones generado por el generador de direcciones, mientras que la lectura 348 se efectúa en orden secuencial.

### 60 Generación de direcciones para el modo 16k

En la figura 5 se representa un diagrama de bloques esquemático del algoritmo usado para generar la función de permutación H(q) para el modo 16K.

En la figura 5 se muestra una implementación del generador de direcciones 102 para el modo 16k. En la figura 5, un registro de desplazamiento con realimentación lineal está formado por trece etapas de registro 200 y una puerta xor 202, que está conectada a las etapas del registro de desplazamiento 200 de acuerdo con un polinomio generador. Por lo tanto, según el contenido del registro de desplazamiento 200, se proporciona un bit sucesivo del registro de desplazamiento desde la salida de la puerta xor 202, efectuando una operación xor del contenido de los registros de desplazamiento R[0], R[1], R[4], R[5], R[9], R[11] de acuerdo con el polinomio generador:

$$R'_{i}[12] = R'_{i-1}[0] \oplus R'_{i-1}[1] \oplus R'_{i-1}[4] \oplus R'_{i-1}[5] \oplus R'_{i-1}[9] \oplus R'_{i-1}[11]$$

- 10 De acuerdo con el polinomio generador, se genera una secuencia seudoaleatoria de bits a partir del contenido del registro de desplazamiento 200. Sin embargo, para generar una dirección para el modo 16k tal como se ilustra, se proporciona un circuito de permutación 210 que permuta efectivamente el orden de los bits dentro del registro de desplazamiento 200.1, de un orden R'[n] a un orden R[n] en la salida del circuito de permutación 210. A continuación, trece bits de la salida del circuito de permutación 210 se suministran sobre un canal de conexión 212, 15 a los cuales se les añade un bit más significativo, a través de un canal 214, que es proporcionado por un circuito de conmutación 218. Por lo tanto, en el canal 212 se genera una dirección de catorce bits. Sin embargo, para garantizar la autenticidad de una dirección, un circuito de comprobación de direcciones 216 analiza la dirección generada para determinar si supera un valor máximo predeterminado. El valor máximo predeterminado se puede corresponder con el número máximo de señales subportadoras, que están disponibles para símbolos de datos en el símbolo COFDM, 20 disponible para el modo que se está usando. No obstante, el intercalador para el modo 16k también se puede usar para otros modos, de manera que el generador de direcciones 102 también se puede usar para el modo 2k, el modo 4k, el modo 8k, el modo 16k y el modo 32k, ajustando de manera correspondiente el número de la dirección válida máxima.

- Si la dirección generada supera el valor máximo predeterminado, entonces la unidad de comprobación de direcciones 216 genera una señal de control y la misma se suministra a una unidad de control 224 a través de un canal de conexión 220. Si la dirección generada supera el valor máximo predeterminado, entonces esta dirección es rechazada y se vuelve a generar una nueva dirección para el símbolo particular.

- Para el modo 16k se define una palabra  $R'_i$  de  $(N_r 1)$  bits, con  $N_r = log_2$   $M_{max}$ , en donde  $M_{max} = 16.384$  usando un LFSR (Registro de Desplazamiento con Realimentación Lineal).

Los polinomios usados para generar esta secuencia son:

Modo 16K:

$$R'_{i}[12] = R'_{i-1}[0] \oplus R'_{i-1}[1] \oplus R'_{i-1}[4] \oplus R'_{i-1}[5] \oplus R'_{i-1}[9] \oplus R'_{i-1}[11]$$

donde i varía de 0 a M<sub>max</sub> -1.

5

35

40

45

50

55

60

Una vez que se ha generado una palabra  $R'_i$ , la palabra  $R'_i$ , es sometida a una permutación para producir otra palabra de  $(N_r - 1)$  bits denominada  $R_i$ .  $R_i$  se obtiene a partir de  $R'_i$  mediante las permutaciones de bits proporcionadas a continuación:

| Posiciones de bit de R'i             | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|--------------------------------------|----|----|----|---|---|----|---|---|----|----|---|---|---|

| Posiciones de bit de R'i             | 8  | 4  | 3  | 2 | 0 | 11 | 1 | 5 | 12 | 10 | 6 | 7 | 9 |

| Permutación de bits para el modo 16K |    |    |    |   |   |    |   |   |    |    |   |   |   |

Como ejemplo, esto significa que para el modo 16K, el bit número 12 de R'i se envía a la posición de bit número 8 de Ri.

A continuación, se obtiene la dirección H(q) a partir de R<sub>i</sub> a través de la siguiente ecuación:

$$H(q) = (i \bmod 2) \cdot 2^{N_r - 1} + \sum_{i=0}^{N_r - 2} R_i(j) \cdot 2^j$$

La parte (i mod2)·2 <sup>Nr-1</sup> de la ecuación anterior está representada en la figura 5 por el bloque de conmutación T 218.

A continuación se efectúa una comprobación de dirección sobre H(q) para verificar que la dirección generada está dentro del intervalo de direcciones aceptables: si  $(H(q) < N_{max})$ , en donde  $N_{max} = 12.096$ , por ejemplo, en el modo 16K, entonces la dirección es válida. Si la dirección no es válida, se informa a la unidad de control y ésta intentará generar una nueva H(q) incrementando el índice i.

La función del bloque de conmutación es garantizar que no se genera una dirección que supere  $N_{max}$  dos veces seguidas. En efecto, si se generase un valor excesivo, esto significaría que el MSB (es decir, el bit de conmutación) de la dirección H(q) era uno. Por tanto, el siguiente valor generado tendrá un MSB fijado a cero, lo cual garantiza la

producción de una dirección válida.

5

10

15

20

Las siguientes ecuaciones resumen el comportamiento global y ayudan a comprender la estructura de bucle de este algoritmo:

q = 0; para (i = 0; i < M<sub>max</sub>; i = i +1) {  $H(q)=(i \mod 2) \cdot 2^{N_r-1} + \sum_{j=0}^{N_r-2} R_i(j) \cdot 2^j$ ; si  $(H(q) < N_{MAX})$  q = q+1; }

Tal como se explicará brevemente, en un ejemplo del generador de direcciones, el código de permutación antes mencionado se usa para generar direcciones para todos los símbolos OFDM. En otro ejemplo, los códigos de permutación se pueden cambiar entre símbolos, con el resultado de que se recorre un conjunto de códigos de permutación para símbolos OFMD sucesivos. Con este fin, las líneas de control 108, 110 que proporcionan una indicación sobre si el símbolo OFDM es impar o par y el modo actual se usan para seleccionar el código de permutación. Este modo de ejemplo en el que se recorre una pluralidad de códigos de permutación resulta particularmente apropiado para el ejemplo en el que únicamente se usa el intercalador de símbolos impares, lo cual se explicará posteriormente. A través de un canal de control 111 se proporciona una señal que indica que debería usarse un código de permutación diferente. En un ejemplo, los códigos de permutación posibles se almacenan previamente en el circuito de códigos de permutación 210. En otro ejemplo, la unidad de control 224 suministra el código de permutación nuevo a usar para un símbolo OFDM.

#### Análisis de apoyo para el generador de direcciones para el modo 16k

Se ha identificado la selección del generador de polinomios y del código de permutación explicado anteriormente para el generador de direcciones 102 para el modo 16k, siguiendo un análisis de simulación del rendimiento relativo del intercalador. El rendimiento relativo del intercalador se ha evaluado usando una capacidad relativa del intercalador para separar símbolos sucesivos o una "calidad de intercalación". Tal como se ha mencionado anteriormente, la intercalación debe funcionar efectivamente para símbolos tanto impares como pares, con el fin de usar una única memoria intercaladora. La medida relativa de la calidad del intercalador se determina definiendo una distancia D (en número de subportadoras). Se escoge un criterio C para identificar un número de subportadoras que están a una distancia ≤ D en la salida del intercalador y que estaban a la distancia ≤ D en la entrada del intercalador, ponderándose a continuación el número de subportadoras para cada distancia D con respecto a la distancia relativa. Se evalúa el criterio C para símbolos COFDM tanto impares como pares. La reducción al mínimo de C produce un intercalador de calidad superior.

$$C = \sum_{l}^{d=D} N_{par}(d)/d + \sum_{l}^{d=D} N_{impar}(d)/d$$

donde: N<sub>par</sub>(d) y N<sub>impar</sub>(d) son el número de subportadoras en un símbolo par e impar respectivamente en la salida del intercalador, que permanecen a menos de una separación de subportadoras d entre sí.

El análisis del intercalador antes identificado, para el modo 16k para un valor de D = 5 se muestra en la figura 6(a) para los símbolos COFDM pares y en la figura 6(b) para el símbolo COFDM impar. De acuerdo con el análisis anterior, el valor de C para el código de permutación identificado anteriormente para el modo 16k produjo un valor de C=22,43, de manera que el número ponderado de subportadoras con símbolos que están separados por cinco o menos en la salida según la anterior ecuación fue 22,43.

Se proporciona un análisis correspondiente para un código de permutación alternativo para símbolos COFDM pares en la figura 6(c) y para símbolos COFDM impares en la figura 6(d). Como puede observarse en comparación con los resultados ilustrados en las figuras 6(a) y 6(b), hay más componentes presentes que representan símbolos separados por distancias pequeñas tales como D=1, y D=2, cuando se realiza una comparación con los resultados mostrados en la figura 6(a) y 6(b), lo cual ilustra que el código de permutación identificado anteriormente para el intercalador de símbolos de modo 16k produce un intercalador de calidad superior.

#### Códigos de permutación alternativos

Se ha observado que los siguientes nueve posibles códigos alternativos (posiciones de bit de  $[n]R_i$ , donde n = 1 a 9) proporcionan un intercalador de símbolos con una buena calidad según se determina por medio del criterio C antes identificado.

60

45

50

| Posiciones de bit de R'i               | 12 | 11 | 10 | 9  | 8  | 7  | 6 | 5 | 4  | 3  | 2  | 1  | 0  |

|----------------------------------------|----|----|----|----|----|----|---|---|----|----|----|----|----|

| Posiciones de bit de [1]R <sub>i</sub> | 7  | 12 | 5  | 8  | 9  | 1  | 2 | 3 | 4  | 10 | 6  | 11 | 0  |

| Posiciones de bit de [2]R <sub>i</sub> | 8  | 5  | 4  | 9  | 2  | 3  | 0 | 1 | 6  | 11 | 7  | 12 | 10 |

| Posiciones de bit de [3]R <sub>i</sub> | 7  | 5  | 6  | 9  | 11 | 2  | 3 | 0 | 8  | 4  | 1  | 12 | 10 |

| Posiciones de bit de [4]R <sub>i</sub> | 11 | 5  | 10 | 4  | 2  | 1  | 0 | 7 | 12 | 8  | 9  | 6  | 3  |

| Posiciones de bit de [5]R <sub>i</sub> | 3  | 9  | 4  | 10 | 0  | 6  | 1 | 5 | 8  | 11 | 7  | 2  | 12 |

| Posiciones de bit de [6]R <sub>i</sub> | 4  | 6  | 3  | 2  | 0  | 7  | 1 | 5 | 8  | 10 | 12 | 9  | 11 |

| Posiciones de bit de [7]R <sub>i</sub> | 10 | 4  | 3  | 2  | 1  | 8  | 0 | 6 | 7  | 9  | 11 | 5  | 12 |

| Posiciones de bit de [8]R <sub>i</sub> | 10 | 4  | 11 | 3  | 7  | 1  | 5 | 0 | 2  | 12 | 8  | 6  | 9  |

| Posiciones de bit de [9]R <sub>i</sub> | 2  | 4  | 11 | 9  | 0  | 10 | 1 | 7 | 8  | 6  | 12 | 3  | 5  |

Permutación de bits para el modo 16K

#### Receptor

5

10

15

20

30

35

40

55

La figura 7 proporciona una ilustración ejemplificativa de un receptor que se puede usar con la presente técnica. Tal como se muestra en la figura 7, una antena 300 recibe una señal COFDM y la misma es detectada por un sintonizador 302 y convertida en un formato digital por un conversor analógico-a-digital 304. Un procesador de supresión de intervalos de guarda 306 suprime el intervalo de guarda de un símbolo COFDM recibido, antes de que los datos sean recuperados del símbolo COFDM, usando un procesador de Transformada Rápida de Fourier (FFT) 308 en combinación con un estimador y una corrección de canales 310, en cooperación con una unidad de decodificación de señalización incorporada 311, según técnicas conocidas. Los datos demodulados se recuperan a partir de un asignador de correspondencias 312 y se suministran a un desintercalador de símbolos 314, que funciona de manera que efectúa la inversión del establecimiento de la correspondencia del símbolo de datos recibido con el fin de volver a generar un flujo continuo de datos de salida con los datos desintercalados.

El desintercalador de símbolos 314 se forma a partir de un aparato de procesado de datos tal como se muestra en la figura 7, con una memoria intercaladora 540 y un generador de direcciones 542. La memoria intercaladora es como la mostrada en la figura 4, y funciona como ya se ha explicado anteriormente para efectuar la desintercalación utilizando conjuntos de direcciones generados por el generador de direcciones 542. El generador de direcciones 542 está formado tal como se muestra en la figura 8, y está dispuesto para generar direcciones correspondientes con el fin de establecer correspondencias de los símbolos de datos recuperados de cada una de las señales subportadoras COFDM hacia un flujo continuo de datos de salida.

Las partes restantes del receptor de COFDM mostrado en la figura 7 están dispuestas para efectuar una decodificación de corrección de errores 318 con el fin de corregir errores y recuperar una estimación de los datos fuente

Una ventaja proporcionada por la presente técnica, tanto para el receptor como para el transmisor, es que un intercalador de símbolos y un desintercalador de símbolos que funcionen en los receptores y transmisores, se pueden conmutar entre el modo 1k, 2k, 4k, 8k, 16k y 32k cambiando los polinomios generadores y el orden de permutación. Por lo tanto, el generador de direcciones 542 mostrado en la figura 8 incluye una entrada 544, que proporciona una indicación del modo, así como una entrada 546 que indica si hay símbolos COFDM impares/pares. Se proporciona así una implementación flexible puesto que un intercalador y un desintercalador de símbolos se pueden formar tal como se muestra en las figuras 3 y 8, con un generador de direcciones como el ilustrado en cualquiera de las figuras 5. Por lo tanto, el generador de direcciones se puede adaptar a los diferentes modos cambiando a los polinomios generadores y los órdenes de permutación indicados para cada uno de los modos. Por ejemplo, esto se puede efectuar usando un cambio de software. Alternativamente, en otras formas de realización, una señal incorporada que indica el modo de la transmisión DVB-T2, puede ser detectada en el receptor, en la unidad de procesado de señalización incorporada 311, y puede ser usada para configurar automáticamente el desintercalador de símbolos según el modo detectado.

#### Uso óptimo de intercaladores de símbolos impares

Tal como se muestra en la figura 4, dos procesos de intercalación de símbolos, uno para símbolos COFDM pares y otro para símbolos COFDM impares, permiten reducir la cantidad de memoria usada durante la intercalación. En el ejemplo mostrado en la figura 4, el orden de escritura para el símbolo impar es el mismo que el orden de lectura para el símbolo par por lo que, mientras se está leyendo un símbolo impar de la memoria, se puede escribir un símbolo par en la posición de la que se acaba de leer; posteriormente, cuando ese símbolo par se lee de la memoria, el siguiente símbolo impar se puede escribir en la posición de la que se acaba de leer.

Tal como se ha mencionado anteriormente, durante un análisis experimental del rendimiento de los intercaladores (usando el criterio C según se ha definido anteriormente) y, por ejemplo, mostrado en la figura 9(a) y la figura 9(b), se ha descubierto que los esquemas de intercalación diseñados para los intercaladores de símbolos de 2k y de 8k para la DVB-T y el intercalador de símbolos de 4k para la DVB-H funcionan mejor para símbolos impares que para

símbolos pares. De este modo, a partir de la evaluación del rendimiento, los resultados de los intercaladores, por ejemplo, según se ilustra mediante las figuras 9(a) y 9(b), han revelado que los intercaladores de símbolos impares funcionan mejor que los intercaladores de símbolos pares. Esto se puede observar comparando la figura 9(a), que muestra resultados correspondientes a un intercalador para símbolos pares, y la figura 6(b) que ilustra resultados para símbolos impares: puede observarse que la distancia media, en la salida del intercalador, de subportadoras que eran adyacentes en la entrada del intercalador, es mayor para un intercalador de símbolos impares que un intercalador de símbolos pares.

Tal como se entenderá, la cantidad de memoria intercaladora requerida para implementar un intercalador de símbolos depende del número de símbolos de datos de los que se van a establecer correspondencias sobre los símbolos de portadoras COFDM. De este modo, un intercalador de símbolos de modo 16k requiere la mitad de la memoria necesaria para implementar un intercalador de símbolos del modo 32k, y de manera similar, la cantidad de memoria necesaria para implementar un intercalador de símbolos de 8k es la mitad de la necesaria para implementar un intercalador de 16k. Por lo tanto, un transmisor o receptor que está dispuesto para implementar un intercalador de símbolos de un modo, el cual fija el número máximo de símbolos de datos que pueden ser transportados por cada símbolo OFDM, incluirá memoria suficiente para implementar dos procesos de intercalación impar para cualquier otro modo que proporcione la mitad o menos de la mitad del número de subportadoras por cada símbolo OFDM en ese modo máximo dado. Por ejemplo, un receptor o transmisor que incluya un intercalador de 32K tendrá memoria suficiente para dar acomodo a dos procesos de intercalación impar de 16K, cada uno de ellos con su propia memoria de 16K.

10

15

20

25

30

35

40

45

50

55

60

65

Por lo tanto, para aprovechar el mejor rendimiento de los procesos de intercalación impar, un intercalador de símbolos capaz de dar acomodo a múltiples modos de modulación se puede disponer de manera que solamente se use un proceso de intercalación de símbolos impares si el mismo se encuentra en un modo que comprende la mitad o menos de la mitad del número de subportadoras de un modo máximo, el cual representa el número máximo de subportadoras por cada símbolo OFDM. Por lo tanto, este modo máximo fija el tamaño de memoria máximo. Por ejemplo, en un transmisor/receptor con capacidad para el modo 32K, cuando se está funcionando en un modo con menos portadoras (es decir, 16K, 8K, 4K ó 1K), entonces, en lugar de utilizar procesos independientes de intercalación de símbolos impares y pares, se usarían dos intercaladores de símbolos impares.

En la figura 10 se muestra una ilustración de una adaptación del intercalador de símbolos 33 que se muestra en la figura 3 cuando se intercalan símbolos de datos de entrada sobre las subportadoras de símbolos OFDM en el modo solamente de intercalación impar. El intercalador de símbolos 33.1 se corresponde exactamente con el intercalador de símbolos 33 que se muestra en la figura 3, excepto que el generador de direcciones 102.1 está adaptado para realizar únicamente el proceso de intercalación impar. Para el ejemplo mostrado en la figura 10, el intercalador de símbolos 33.1 está funcionando en un modo en el que el número de símbolos de datos que se pueden transportar por cada símbolo OFDM es menos de la mitad del número máximo que puede transportar un símbolo OFDM en un modo de funcionamiento con el número más grande de subportadoras por símbolo OFDM. Por ello, el intercalador de símbolos 33.1 se ha dispuesto para dividir la memoria intercaladora 100. Para la presente ilustración mostrada en la figura 10, la memoria intercaladora 100 se divide por lo tanto en dos partes 401, 402. Como ilustración del intercalador de símbolos 33.1 que funciona en un modo en el que se establecen correspondencias de símbolos de datos sobre los símbolos OFDM usando el proceso de intercalación impar, la figura 10 proporciona una vista ampliada de cada mitad de la memoria intercaladora 401, 402. La vista ampliada proporciona una ilustración del modo de intercalación impar según se representa para el lado del transmisor para cuatro símbolos A, B, C, D reproducidos a partir de la figura 4. De este modo, tal como se muestra en la figura 10, para conjuntos sucesivos de primeros y segundos símbolos de datos, los símbolos de datos se escriben en la memoria intercaladora 401, 402 en un orden secuencial y se leen de acuerdo con direcciones generadas por el generador de direcciones 102 en un orden permutado según las direcciones generadas por el generador de direcciones tal como se ha explicado previamente. De este modo, tal como se ilustra en la figura 10, puesto que se está realizando un proceso de intercalación impar para conjuntos sucesivos de primeros y segundos conjuntos de símbolos de datos, la memoria intercaladora se debe dividir en dos partes. Símbolos de un primer conjunto de símbolos de datos se escriben en una primera mitad de la memoria intercaladora 401, y símbolos de un segundo conjunto de símbolos de datos se escriben en una segunda parte de la memoria intercaladora 402, puesto que el intercalador de símbolos ya no puede volver a utilizar las mismas partes de la memoria intercaladora de símbolos a las que se puede dar acomodo cuando se funciona en un modo impar y par de intercalación.

En la figura 11 se muestra un ejemplo correspondiente del intercalador en el receptor, el cual aparece en la figura 8 aunque adaptado para funcionar con un proceso de intercalación impar solamente. Tal como se muestra en la figura 11, la memoria intercaladora 540 está dividida en dos mitades 410, 412, y el generador de direcciones 542 está adaptado para escribir símbolos de datos en la memoria intercaladora y leer símbolos de datos de la memoria intercaladora hacia partes respectivas de la memoria 410, 402 para conjuntos sucesivos de símbolos de datos con el fin de implementar un proceso de intercalación impar solamente. Por lo tanto, en correspondencia con la representación mostrada en la figura 10, la figura 11 muestra el establecimiento de correspondencias del proceso de intercalación que se realiza en el receptor y se ilustra en la figura 4 como una vista ampliada que funciona tanto para la primera como para la segunda mitades de la memoria de intercalación 410, 412. De este modo, un primer conjunto de símbolos de datos se escribe en una primera parte de la memoria intercaladora 410 en un orden

permutado definido de acuerdo con las direcciones generadas por el generador de direcciones 542 según se ilustra mediante el orden de escritura en los símbolos de datos que proporciona una secuencia de escritura de 1, 3, 0, 2. A continuación, tal como se ilustra, los símbolos de datos se leen de la primera parte de la memoria intercaladora 410 en un orden secuencial, recuperando de este modo la secuencia original A, B, C, D.

5

De manera correspondiente, un segundo conjunto subsiguiente de símbolos de datos que se recuperan de un símbolo OFDM sucesivo se escribe en la segunda mitad de la memoria intercaladora 412 de acuerdo con las direcciones generadas por el generador de direcciones 542 en un orden permutado, y se leen hacia el flujo continuo de datos de salida en un orden secuencial.

10

15

En un ejemplo, las direcciones generadas para un primer conjunto de símbolos de datos a escribir en la primera mitad de la memoria intercaladora 410 se pueden reutilizar para escribir un segundo conjunto subsiguiente de símbolos de datos en la memoria intercaladora 412. De manera correspondiente, el transmisor también puede reutilizar direcciones generadas para una mitad del intercalador para un primer conjunto de símbolos de datos con el fin de leer un segundo conjunto de símbolos de datos que se han escrito en la segunda mitad de la memoria en orden secuencial.

#### Intercalador de símbolos impares con deriva

El rendimiento de un intercalador que usa dos intercaladores de símbolos impares se podría mejorar adicionalmente usando una secuencia de intercaladores solamente de símbolos impares en lugar de un único intercalador solamente de símbolos impares, de manera que cualquier bit de datos introducido en el intercalador no module siempre la misma portadora en el símbolo OFDM.

Una secuencia de intercaladores solamente de símbolos impares se podría lograr mediante cualquiera de las siguientes opciones:

- sumando una deriva a la dirección del intercalador módulo el número de portadoras de datos, o

- usando una secuencia de permutaciones en el intercalador

30

35

60

#### Suma de una deriva

La suma de una deriva a la dirección del intercalador módulo el número de portadoras de datos efectivamente desplaza y reinicia cíclicamente el símbolo OFDM de manera que cualquier bit de datos introducido en el intercalador no modula siempre la misma portadora en el símbolo OFDM. De este modo, el generador de direcciones podría incluir opcionalmente un generador de derivas, el cual genera una deriva en una dirección generada por el generador de direcciones sobre el canal de salida H(q).

La deriva cambiaría cada símbolo. Por ejemplo, esta deriva podría proporcionar una secuencia cíclica. Esta secuencia cíclica podría tener, por ejemplo, una longitud 4 y consistiría, por ejemplo, en números primos. Por ejemplo, dicha secuencia podría ser:

0,41,97,157

Además, la deriva puede ser una secuencia aleatoria, que puede ser generada por otro generador de direcciones desde un intercalador de símbolos OFDM similar o puede ser generada por algunos otros medios.

## Uso de una secuencia de permutaciones

Tal como se muestra en la figura 5, una línea de control 111 se prolonga desde la unidad de control del generador de direcciones al circuito de permutación. Como se ha mencionado anteriormente, en un ejemplo, el generador de direcciones puede aplicar un código de permutación diferente de entre un conjunto de códigos de permutación para símbolos OFDM sucesivos. El uso de una secuencia de permutaciones en el generador de direcciones del intercalador reduce la probabilidad de que cualquier bit de datos introducido en el intercalador no module siempre la misma subportadora en el símbolo OFDM.

Por ejemplo, esta podría ser una secuencia cíclica, de manera que un código de permutación diferente de un conjunto de códigos de permutación en una secuencia se usa para símbolos OFDM sucesivos y a continuación se repite. Esta secuencia cíclica podría tener, por ejemplo, una longitud de dos o cuatro. Para el ejemplo del intercalador de símbolos de 16K, una secuencia de dos códigos de permutación que son recorridos por cada símbolo OFDM podría ser, por ejemplo:

mientras que una secuencia de cuatro códigos de permutación podría ser:

8432011151210679 7953111402121086 6117523011081294 5129031024678111

La conmutación de un código de permutación a otro se podría efectuar en respuesta a un cambio de la señal Impar/Par indicada sobre el canal de control 108. Como respuesta, la unidad de control 224 cambia el código de permutación en el circuito de códigos de permutación 210 a través de la línea de control 111.

Para el ejemplo de un intercalador de símbolos de 1k, dos códigos de permutación podrían ser:

10

432105678 325014786

mientras que cuatro códigos de permutación podrían ser:

432105678 325014786 753826140 168253407

15

20

Pueden ser posibles otras combinaciones de secuencias para los modos de 2k, 4k y 8k portadoras o incluso el modo de 0,5k portadoras. Por ejemplo, los siguientes códigos de permutación para cada uno de 0,5k, 2k, 4k y 8k proporcionan una buena decorrelación de símbolos y se pueden usar cíclicamente para generar la deriva sobre la dirección generada por un generador de direcciones para cada uno de los modos respectivos:

Modo 2k:

0751826934\* 4832901567 8390215746 7048369152

25

Modo 4k:

710581249036\*\*

627108034195

954231010687

141039726508

30 Modo 8k:

51130108692417\*

10854291067311

11698472101053

83117915640210

Para los códigos de permutación indicados anteriormente, los dos primeros se podrían usar en un ciclo de dos secuencias, mientras que la totalidad de los cuatro se podría usar para un ciclo de cuatro secuencias. Adicionalmente, a continuación se proporcionan algunas otras secuencias de cuatro códigos de permutación, las cuales se recorren para proporcionar la deriva en un generador de direcciones con el fin de producir una buena decorrelación en los símbolos intercalados (algunas son comunes a las anteriores):

Modo 0,5k:

37461205 42573016 53604127 61052743

5

Modo 2k:

0751826934\*

3270158496

4832901567

7395210648

10 Modo 4k:

710581249036\*\*

627108034195

103412706859

089510463217

Modo 8k:

15

5 11 3 0 10 8 6 9 2 4 1 7 \* 8 10 7 6 0 5 2 1 3 9 4 11 11 3 6 9 2 7 4 10 5 1 0 8 10 8 1 7 5 6 0 11 4 2 9 3

20 \*\* estas son las permutaciones en la normativa DVB-H

En la solicitud de patente europea número 04251667.4 se dan a conocer ejemplos de generadores de direcciones, e intercaladores correspondientes, para los modos 2k, 4k y 8k. En nuestra solicitud de patente UK en tramitación con la presente, número 0722553.5, se da a conocer un generador de direcciones para el modo 0,5k. Sobre las formas de realización descritas anteriormente se pueden efectuar varias modificaciones sin desviarse con respecto al alcance de la presente invención. En particular, la representación ejemplificativa del polinomio generador y el orden de permutación que se han usado para representar aspectos de la invención no están destinados a ser limitativos y se extienden a formas equivalentes del polinomio generador y el orden de permutación dentro del alcance de las reivindicaciones adiuntas.

30

35

25

Tal como se apreciará, el transmisor y el receptor mostrados en las figuras 1 y 7, respectivamente, se aportan únicamente como ilustraciones, y no están destinados a ser limitativos. Por ejemplo, se apreciará que se puede cambiar la posición del intercalador de símbolos y del desintercalador, por ejemplo con respecto al intercalador de bits y al asignador de correspondencias. Tal como se apreciará, el efecto del intercalador y del desintercalador no cambia por su posición relativa, aunque el intercalador puede estar intercalando símbolos I/Q en lugar de vectores de v bits. En el receptor se puede efectuar un cambio correspondiente. Por consiguiente, el intercalador y el desintercalador pueden estar trabajando sobre diferentes tipos de datos, y pueden estar situados de manera diferente a la posición descrita en las formas de realización ejemplificativas.

Según una implementación de un receptor, se proporciona un aparato de procesado de datos para establecer correspondencias de símbolos recibidos desde un número predeterminado de señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM) hacia un flujo continuo de símbolos de salida. El aparato de procesado de datos comprende un desintercalador que se puede hacer funcionar para escribir en una memoria el número predeterminado de símbolos de datos desde las señales subportadoras OFDM, y para leer de la memoria los símbolos de datos hacia el flujo continuo de símbolos de salida con el fin de efectuar el establecimiento de correspondencias, produciéndose la lectura en un orden diferente al de la escritura, determinándose el orden a partir de un conjunto de direcciones, con el resultado de que los símbolos de datos se desintercalan de las señales subportadoras OFDM, un generador de direcciones que se puede hacer funcionar para generar el conjunto de

<sup>\*</sup> estas son las permutaciones en la normativa DVB-T

direcciones, generándose una dirección para cada uno de los símbolos de datos recibidos con el fin de indicar la señal subportadora OFDM desde la cual se va a establecer una correspondencia del símbolo de datos recibido hacia el flujo continuo de símbolos de salida, comprendiendo el generador

5 un registro de desplazamiento con realimentación lineal, que incluye un número predeterminado de etapas de registro y que se puede hacer funcionar para generar una secuencia seudoaleatoria de bits de acuerdo con un polinomio generador,

un circuito de permutación que se puede hacer funcionar para recibir el contenido de las etapas del registro de desplazamiento y para permutar los bits presentes en las etapas del registro de acuerdo con un orden de permutación con el fin de formar una dirección de una de las subportadoras OFDM, y

15

20

una unidad de control que se puede hacer funcionar en combinación con un circuito de comprobación de direcciones para volver a generar una dirección cuando una dirección generada supera una dirección válida máxima predeterminada, caracterizado porque

la dirección válida máxima predeterminada es aproximadamente dieciséis mil, el registro de desplazamiento con realimentación lineal tiene trece etapas de registro con un polinomio generador para el registro de desplazamiento con realimentación lineal de  $R'_{i,1}[2] = R'_{i,1}[0] \oplus R'_{i,1}[1] \oplus R'_{i,1}[4] \oplus R'_{i,1}[5] \oplus R'_{i,1}[9] \oplus R'_{i,1}[11]$ , y el orden de permutación forma, con un bit adicional, una dirección de catorce bits  $R_{i,1}[n]$  para el símbolo de datos i-ésimo a partir del bit presente en la etapa de registro n-ésima  $R'_{i,1}[n]$  de acuerdo con un código definido por la tabla:

| Posiciones de bit de R'i | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|--------------------------|----|----|----|---|---|----|---|---|----|----|---|---|---|

| Posiciones de bit de Ri  | 8  | 4  | 3  | 2 | 0 | 11 | 1 | 5 | 12 | 10 | 6 | 7 | 9 |

Tal como se ha explicado anteriormente, los códigos de permutación y el polinomio generador del intercalador, que se ha descrito en referencia a una implementación de un modo particular, se pueden aplicar también a otros modos, cambiando la dirección permitida máxima predeterminada, de acuerdo con el número de subportadoras para ese modo.

Tal como se ha mencionado anteriormente, formas de realización de la presente invención encuentran aplicación con normativas DVB, tales como DVB-T, DVB-T2 y DVB-H, que se incorporan a la presente a título de referencia. 30 Por ejemplo, se pueden usar formas de realización de la presente invención en un transmisor o receptor que funcionen de acuerdo con la normativa DVB-H, en terminales móviles portátiles. Los terminales móviles pueden estar integrados con teléfonos móviles (ya sean de la generación segunda, tercera o superior) o Asistentes Personales Digitales, o por ejemplo, PCs de tipo Tablet. Dichos terminales móviles pueden tener la capacidad de 35 recibir señales compatibles con DVB-H o DVB-T dentro de edificios o en movimiento, por ejemplo, en automóviles o trenes, incluso a velocidades elevadas. Los terminales móviles pueden alimentarse, por ejemplo, mediante baterías, la red eléctrica o una fuente de alimentación DC de bajo voltaje, o se pueden alimentar desde la batería de un automóvil. Los servicios que puede proporcionar la DVB-H pueden incluir voz, mensajería, navegación por internet, radio, imágenes de vídeo estáticas y/o en movimiento, servicios de televisión, servicios interactivos, vídeo o vídeo a la carta y otras opciones. Los servicios podrían funcionar en combinación mutua. En otros ejemplos, formas de 40 realización de la presente invención encuentran aplicación con la normativa DVB-T2 según se especifica de acuerdo con la norma ETSI EN 302 755. En otros ejemplos, formas de realización de la presente invención encuentran aplicación con la normativa de transmisión por cable conocida como DVB-C2. No obstante, se apreciará que la presente invención no se limita a la aplicación con la DVB, y se puede ampliar a otras normativas de transmisión o 45 recepción, tanto fijas como móviles.

#### **REIVINDICACIONES**

1. Aparato de procesado de datos que se puede hacer funcionar para establecer correspondencias de símbolos de entrada, que van a ser comunicados, sobre un número predeterminado de señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM), comprendiendo el aparato de procesado de datos

5

10

25

30

35

40

55

un intercalador (33) que se puede hacer funcionar para escribir en una memoria (100) el número predeterminado de símbolos de datos para el establecimiento de correspondencias sobre las señales subportadoras OFDM, y para leer de la memoria (100) los símbolos de datos para las subportadoras OFDM con el fin de efectuar el establecimiento de correspondencias, realizándose la lectura en un orden diferente al de la escritura, determinándose el orden a partir de un conjunto de direcciones, con el resultado de que los símbolos de datos se intercalan en las señales subportadoras,

un generador de direcciones (102) que se puede hacer funcionar para generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de entrada con el fin de indicar una de las señales subportadoras sobre la cual se va a establecer una correspondencia del símbolo de datos, comprendiendo el generador de direcciones (102)

un registro de desplazamiento con realimentación lineal (200) que incluye un número predeterminado de etapas de registro y que se puede hacer funcionar para generar una secuencia seudoaleatoria de bits de acuerdo con un polinomio generador,

un circuito de permutación (210) que se puede hacer funcionar para recibir el contenido de las etapas de registro de desplazamiento y para permutar los bits presentes en las etapas de registro de acuerdo con un orden de permutación con el fin de formar una dirección de una de las subportadoras OFDM, y

una unidad de control (224) que se puede hacer funcionar en combinación con un circuito de comprobación de direcciones para volver a generar una dirección cuando una dirección generada supera una dirección válida máxima predeterminada, caracterizado porque

la dirección válida máxima predeterminada es aproximadamente dieciséis mil, el registro de desplazamiento con realimentación lineal tiene trece etapas de registro con un polinomio generador para el registro de desplazamiento con realimentación lineal de  $R'_{i1}[12] = R'_{i1}[0] \oplus R'_{i1}[1] \oplus R'_{i1}[4] \oplus R'_{i1}[5] \oplus R'_{i1}[9] \oplus R'_{i1}[11]$ , y el orden de permutación forma, con un bit adicional, una dirección de catorce bits  $R_{i1}[n]$  para el símbolo de datos i-ésimo a partir del bit presente en la etapa de registro n-ésima  $R'_{i1}[n]$  de acuerdo con un código definido por la tabla:

| Posiciones de bit de R'i            | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------------------------------------|----|----|----|---|---|----|---|---|----|----|---|---|---|

| Posiciones de bit de R <sub>i</sub> | 8  | 4  | 3  | 2 | 0 | 11 | 1 | 5 | 12 | 10 | 6 | 7 | 9 |

- 2. Aparato de procesado de datos según la reivindicación 1, en el que la dirección válida máxima predeterminada es un valor sustancialmente comprendido entre doce mil y dieciséis mil trescientos ochenta y cuatro.

- 3. Aparato de procesado de datos según la reivindicación 1, en el que el símbolo OFDM incluye subportadoras piloto, que están dispuestas para transportar símbolos conocidos, y la dirección válida máxima predeterminada depende de un número de los símbolos de las subportadoras piloto presentes en el símbolo OFDM.

- 4. Aparato de procesado de datos según la reivindicación 1, en el que la memoria intercaladora (100) se puede hacer funcionar para efectuar el establecimiento de correspondencias de los símbolos de datos de entrada sobre las señales subportadoras para símbolos OFDM pares mediante la escritura de los símbolos de datos de acuerdo con el conjunto de direcciones generadas por el generador de direcciones (102) y la lectura en un orden secuencial, y para símbolos OFDM impares mediante la escritura de los símbolos en la memoria (100) en un orden secuencial y la lectura de los símbolos de datos de la memoria (100) de acuerdo con el conjunto de direcciones generadas por el generador de direcciones (102).

- 5. Aparato de procesado de datos según cualquiera de las reivindicaciones anteriores, en el que el circuito de permutación (210) se puede hacer funcionar para cambiar el código de permutación, el cual permuta el orden de los bits de las etapas de registro para formar las direcciones de un símbolo OFDM a otro.

- 6. Aparato de procesado de datos según la reivindicación 5, en el que el circuito de permutación (210) se puede hacer funcionar para recorrer una secuencia de diferentes códigos de permutación para símbolos OFDM sucesivos.

- 7. Aparato de procesado de datos según la reivindicación 6, en el que la secuencia de códigos de permutación comprende dos códigos de permutación, que son

| Posiciones de bit de R'i | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|--------------------------|----|----|----|---|---|----|---|---|----|----|---|---|---|

| Posiciones de bit de Ri  | 8  | 4  | 3  | 2 | 0 | 11 | 1 | 5 | 12 | 10 | 6 | 7 | 9 |

У

| Posiciones de bit de R'i            | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 4 | 3  | 2  | 1 | 0 |

|-------------------------------------|----|----|----|---|----|---|---|---|---|----|----|---|---|

| Posiciones de bit de R <sub>i</sub> | 7  | 9  | 5  | 3 | 11 | 1 | 4 | 0 | 2 | 12 | 10 | 8 | 6 |

- 8. Aparato de procesado de datos según la reivindicación 5, 6 ó 7, en el que tanto para símbolos OFDM impares como para símbolos OFDM pares, el intercalador se puede hacer funcionar para escribir en la memoria (100) el número predeterminado de símbolos de datos para el establecimiento de correspondencias sobre las señales subportadoras OFDM en un orden secuencial, y para leer de la memoria (100) los símbolos de datos para las subportadoras OFDM con el fin de efectuar el establecimiento de correspondencias de acuerdo con el conjunto de direcciones generadas por el generador de direcciones.

- 9. Transmisor para transmitir datos usando el Multiplexado por División Ortogonal de Frecuencia (OFDM), incluyendo el transmisor un aparato de procesado de datos (33) según cualquiera de las reivindicaciones anteriores.

- 10. Transmisor según la reivindicación 9, en el que el transmisor se puede hacer funcionar para transmitir datos de acuerdo con una normativa de Radiodifusión de Vídeo Digital tal como la Radiodifusión de Vídeo Digital Terrestre, la normativa de Radiodifusión de Vídeo Digital para Portátiles o la normativa de Radiodifusión de Vídeo Digital Terrestre.

- 20 11. Método de establecimiento de correspondencias de símbolos de entrada, que van a ser comunicados, sobre un número predeterminado de señales subportadoras de un símbolo Multiplexado por División Ortogonal de Frecuencia (OFDM), comprendiendo el método

- escribir en una memoria (100) el número predeterminado de símbolos de datos para el establecimiento de correspondencias sobre las señales subportadoras OFDM,

- leer de la memoria (100) los símbolos de datos para las subportadoras OFDM con el fin de efectuar el establecimiento de correspondencias, realizándose la lectura en un orden diferente al de la escritura, determinándose el orden a partir de un conjunto de direcciones, con el resultado de que los símbolos de datos se intercalan en las señales subportadoras,

- generar el conjunto de direcciones, generándose una dirección para cada uno de los símbolos de entrada, con el fin de indicar una de las señales subportadoras sobre la cual se va a establecer la correspondencia del símbolo de datos, comprendiendo la generación del conjunto de direcciones

- usar un registro de desplazamiento con realimentación lineal (200) que incluye un número predeterminado de etapas de registro para generar una secuencia seudoaleatoria de bits de acuerdo con un polinomio generador,

- usar un circuito de permutación (210) que se puede hacer funcionar para recibir el contenido de las etapas de registro de desplazamiento con el fin de permutar los bits presentes en las etapas de registro de acuerdo con un orden de permutación para formar una dirección, y

- volver a generar una dirección cuando una dirección generada supera una dirección válida máxima predeterminada, caracterizado porque