OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 383 120**

⑯ Int. Cl.:

**B41J 2/05** (2006.01)

**G06K 15/10** (2006.01)

⑫

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- ⑯ Número de solicitud europea: **05732007 .9**

⑯ Fecha de presentación: **06.04.2005**

⑯ Número de publicación de la solicitud: **1737667**

⑯ Fecha de publicación de la solicitud: **03.01.2007**

⑮

Título: **Dispositivo para la expulsión de fluido**

⑯ Prioridad:

**19.04.2004 US 827142**

⑯ Titular/es:

**HEWLETT-PACKARD DEVELOPMENT

COMPANY, L.P.

INTELLECTUAL PROPERTY ADMINISTRATION

20555 S.H. 249

HOUSTON TX 77070, US**

⑯ Fecha de publicación de la mención BOPI:

**18.06.2012**

⑯ Inventor/es:

**BENJAMIN, Trudy L.**

⑯ Fecha de la publicación del folleto de la patente:

**18.06.2012**

⑯ Agente/Representante:

**de Elzaburu Márquez, Alberto**

**ES 2 383 120 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Dispositivo para la expulsión de fluido

5 **Referencia a solicitudes relacionadas**

Esta solicitud se refiere a la Solicitud de Patente Número de Serie (no asignado todavía), referencia de su representante nº 200209168-1, titulada "dispositivo para la expulsión o eyección de fluido", Solicitud de Patente Número de Serie (todavía no asignado), referencia de su representante nº 200208780-1, titulada "dispositivo para la expulsión o eyección de fluido con generador de dirección", Solicitud de Patente Número de Serie (todavía no asignado), nº 200311485-1, titulada "dispositivo con puertas configurado en estructura en bucle", Solicitud de Patente Número de Serie (todavía no asignado), nº 200210152-1, titulada "dispositivo de expulsión o eyección de fluido" y la Solicitud de Patente Número de Serie (todavía no asignado), referencia de representante nº 200209237-1 titulada "dispositivo de expulsión o eyección de fluido con células de identificación", cada una de las cuales están cedidas al cesionario de esta solicitud y son solicitadas en la misma fecha, adjuntas.

15

Antecedentes

Un sistema de impresión por inyección de tinta, como una forma de realización de un sistema de expulsión o eyección de fluido, puede incluir un cabezal de impresión, un suministrador de tinta, que proporciona tinta líquida al cabezal de impresión, y un controlador electrónico, que controla el cabezal de impresión. El cabezal de impresión, como una forma de realización de un sistema de expulsión o eyección de fluido, inyecta gotas de tinta a través de una pluralidad de orificios o boquillas. La tinta es proyectada hacia el medio de impresión, como una hoja de papel, para imprimir una imagen sobre el medio de impresión. Las boquillas están, típicamente, dispuestas en una o más matrices, de forma que la expulsión o eyección adecuada de tinta desde las boquillas, cause la impresión de caracteres u otras imágenes sobre el medio de impresión, al moverse el cabezal de impresión y el medio de impresión, con referencia uno al otro.

En un sistema térmico típico de inyección de tinta, el cabezal de impresión inyecta gotas de tinta a través de las boquillas, mediante el calentamiento rápido de pequeños volúmenes de tinta localizados en cámaras de evaporación. La tinta es calentada con pequeños calentadores eléctricos, como resistencias de film finas, referidas aquí como resistencias de disparo. El calentamiento de la tinta causa la evaporación de la tinta y su expulsión o eyección a través de las boquillas.

Para inyectar una gota de tinta, el controlador eléctrico, que controla el cabezal de tinta, activa una corriente eléctrica, desde el suministrador de corriente exterior al cabezal de tinta. La corriente eléctrica pasa a través de una resistencia de disparo seleccionada, para calentar la tinta en una correspondiente cámara de evaporación seleccionada e inyecta la tinta a través de la correspondiente boquilla. Los generadores de gotas conocidos incluyen una resistencia de disparo, una cámara correspondiente de vaporización y una correspondiente boquilla.

Al ir evolucionando los cabezales de impresión por inyección de tinta, el número de generadores de gotas en un cabezal de impresión se ha incrementado para mejorar la velocidad y/o calidad de impresión. El incremento del número de generadores de gotas por cabezal de impresión, ha dado como resultado un correlativo incremento en el número de pads de entrada necesarios en la base de un cabezal de impresión, para energizar el número incrementado de resistencias de disparo. En un tipo de cabezal de impresión, cada resistencia de disparo es conectada con un correspondiente pad de entrada, para proporcionar electricidad que energice la resistencia de disparo. Al incrementarse el número de resistencias de disparo, un pad de entrada por resistencia de disparo resulta impráctico.

El número de generadores de gotas por pad de entrada es incrementado, significativamente, en otro tipo de cabezal de impresión que tiene unidades primitivas. Un único cable de energía proporciona electricidad a todas las resistencias de disparo de una unidad primitiva. Cada resistencia de disparo es conectada, en serie, con el cable de energía y la trayectoria de la fuente de drenaje de un correlativo transistor de efecto de campo (FET). La puerta de cada FET en una unidad primitiva, está conectada a un cable de dirección, energizable separadamente, que es compartido por múltiples unidades primitivas.

Los fabricantes continúan reduciendo el número de pads de entrada e incrementando el número de generadores de gotas, sobre la base de un cabezal de impresión. Un cabezal de impresión con menos pads de entrada, típicamente, cuesta menos, que un cabezal de impresión con más pads de entrada. También, un cabezal de impresión con más generadores de gotas, típicamente, imprime con mayor calidad y/o velocidad de impresión. Para mantener los costes y proporcionar una particular franja de altura de impresión, el tamaño de la base de un cabezal de impresión no puede cambiar significativamente, con un número incrementado de generadores de gotas. Al incrementarse la densidad de generadores de gotas y descender el numero de pads de entrada, puede resultar cada vez más complejo el diseño de las bases de los cabezales de tinta.

La Patente Europea con número de publicación 1128324 revela un cabezal de impresión, el cual puede acelerar la transferencia de datos de imagen y la conducción de los elementos de impresión, sin incrementar el número de

líneas de señales y terminales de conexión. Una señal de datos de imagen, separada por una señal de selección, suministrada al cabezal de impresión, tiene un formato de bus de 4-bits, que contiene datos de selección de bloque en su cabeza.

5 Por estas y otras razones, existe una necesidad para la presente invención.

Breve descripción de los dibujos

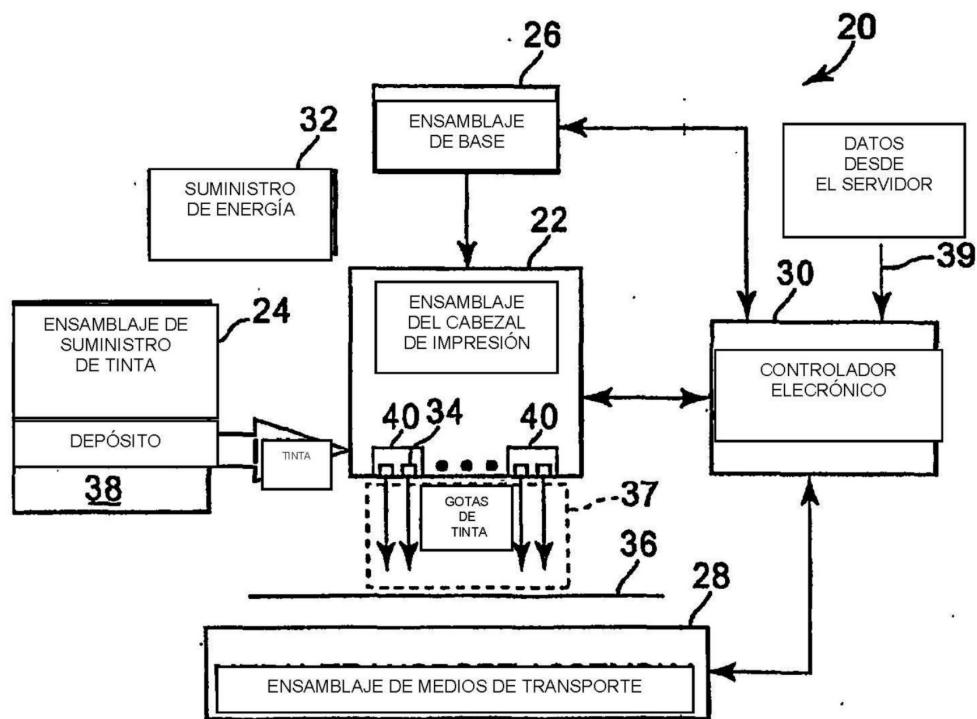

La Figura 1, ilustra una forma de realización de un sistema de impresión por inyección de tinta.

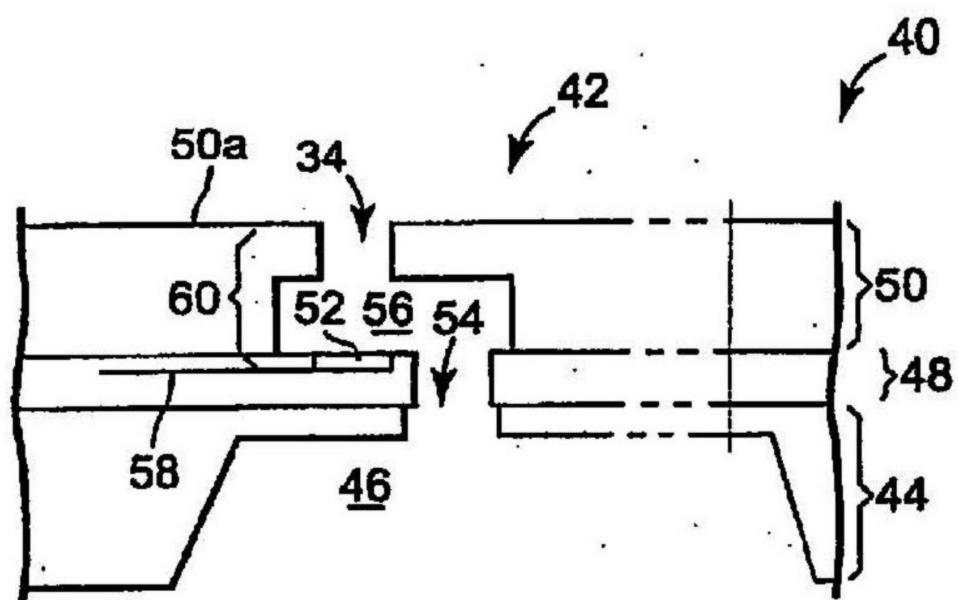

10 La Figura 2, es un diagrama que ilustra una parte de una forma de realización de la base de un cabezal de impresión.

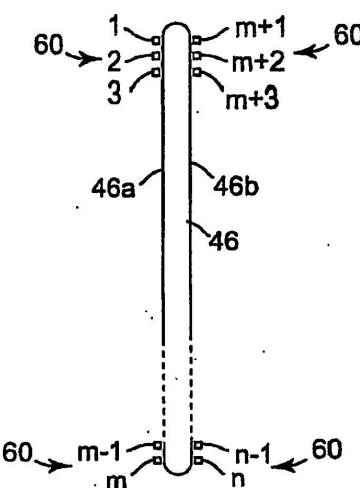

La Figura 3, es un diagrama que ilustra un diseño de generadores de gotas, situados a lo largo de una ranura de alimentación de tinta, en una forma de realización de la base de un cabezal de impresión.

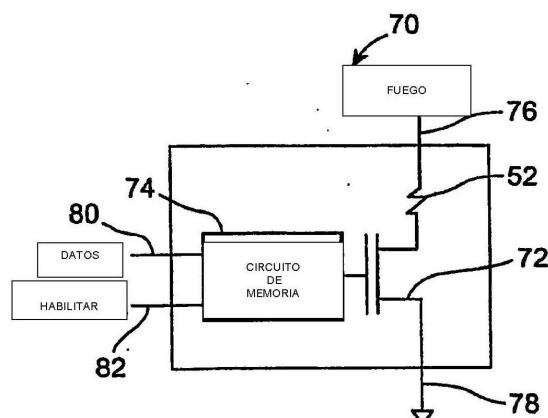

15 La Figura 4, es un diagrama que ilustra una forma de realización de una célula de disparo, empleada en una forma de realización de una base de un cabezal de impresión.

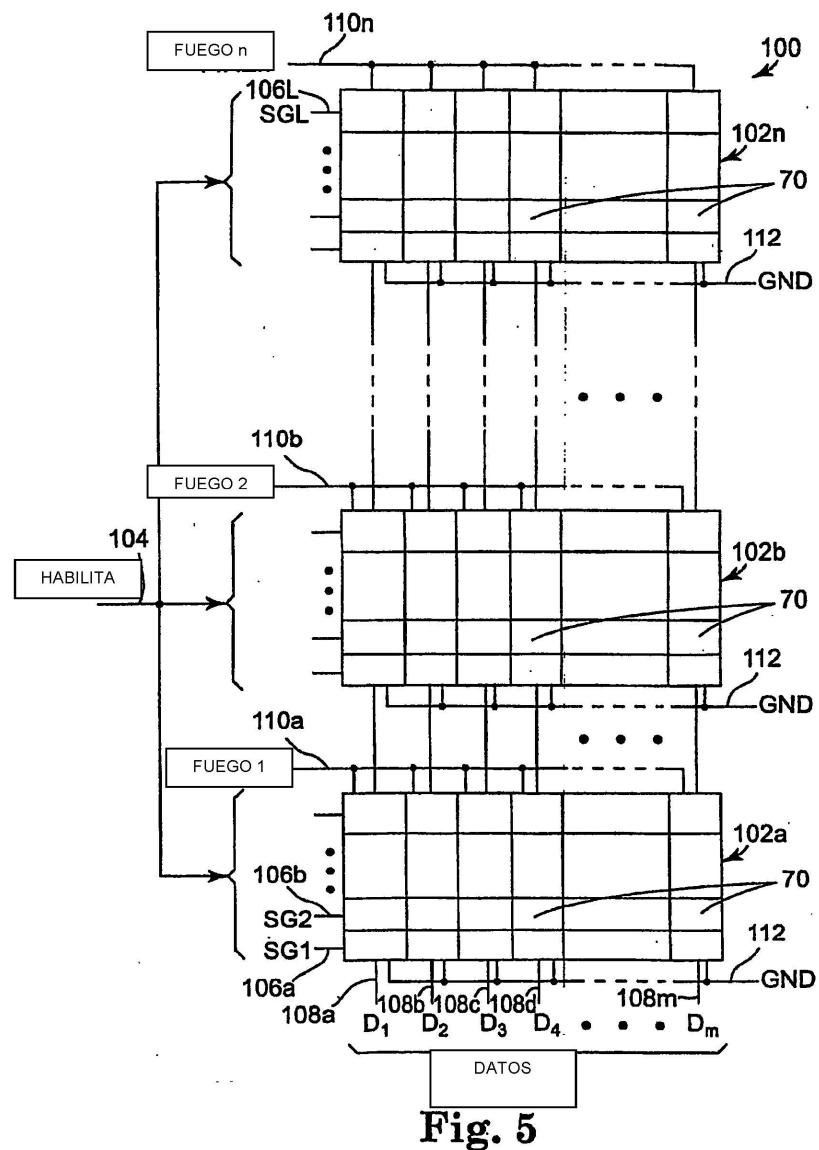

La Figura 5, es un diagrama esquemático que ilustra una forma de realización de una matriz de células de un cabezal de impresión por inyección de tinta.

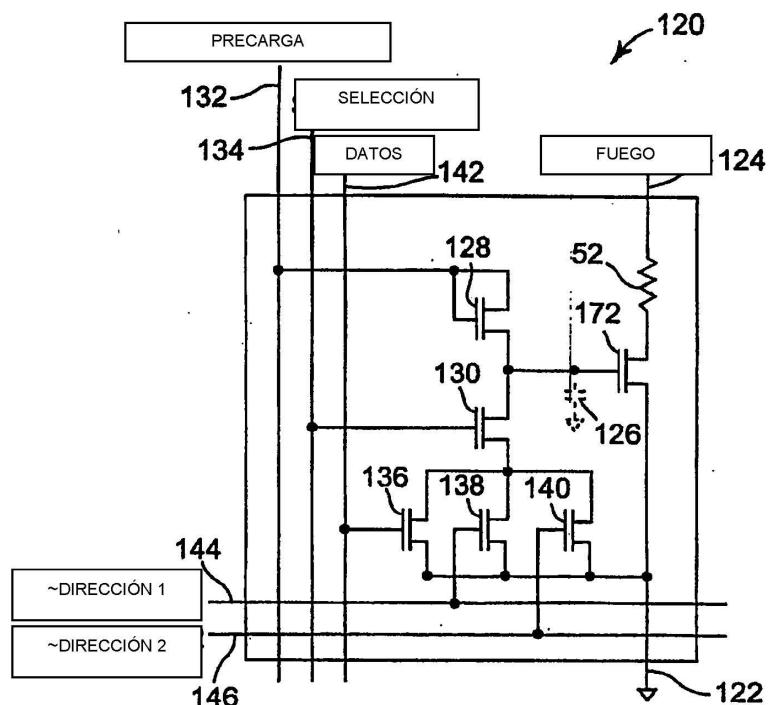

20 La Figura 6, es un diagrama esquemático que ilustra una forma de realización de una célula de disparo precargada.

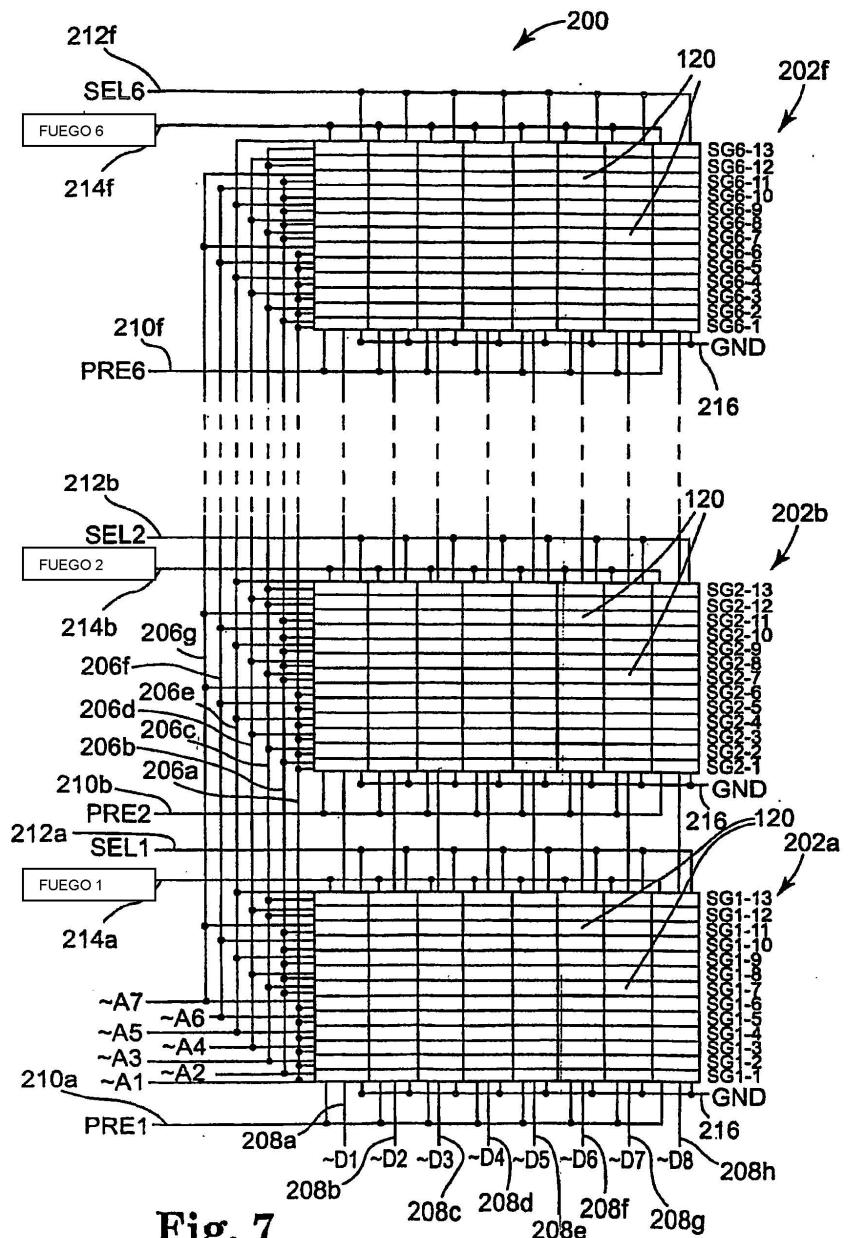

La Figura 7, es un diagrama esquemático que ilustra una forma de realización de una matriz de células de disparo de un cabezal de impresión por inyección de tinta.

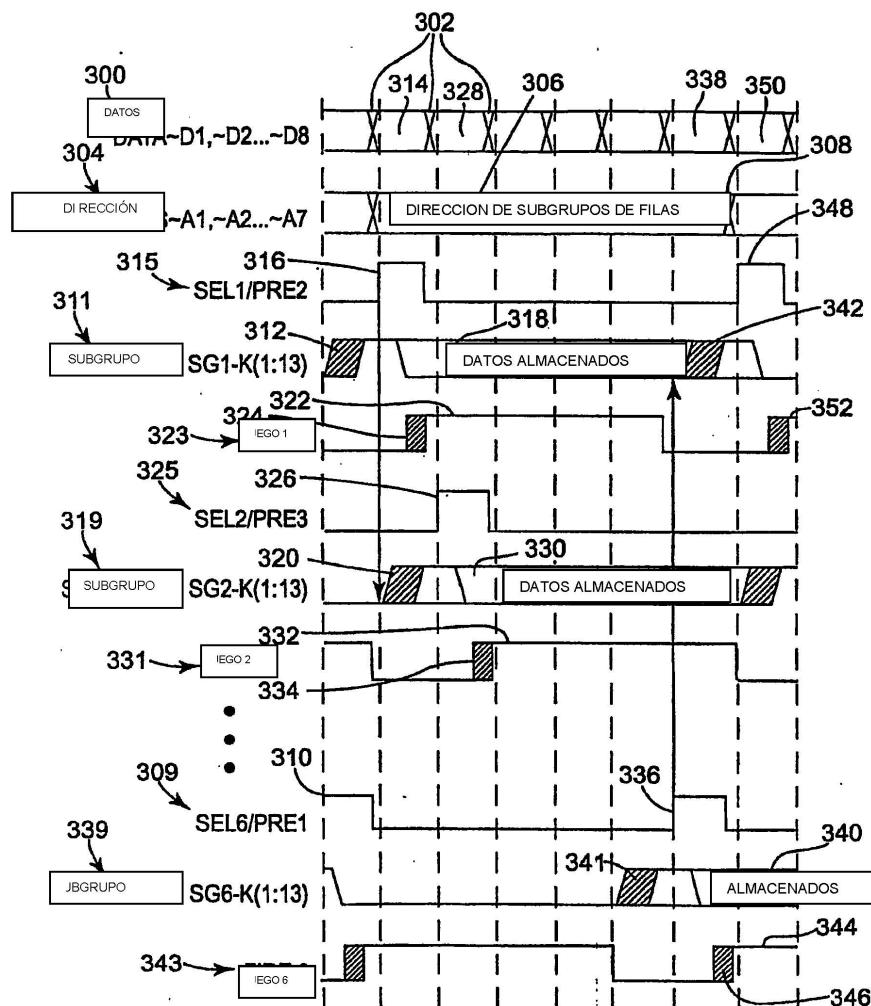

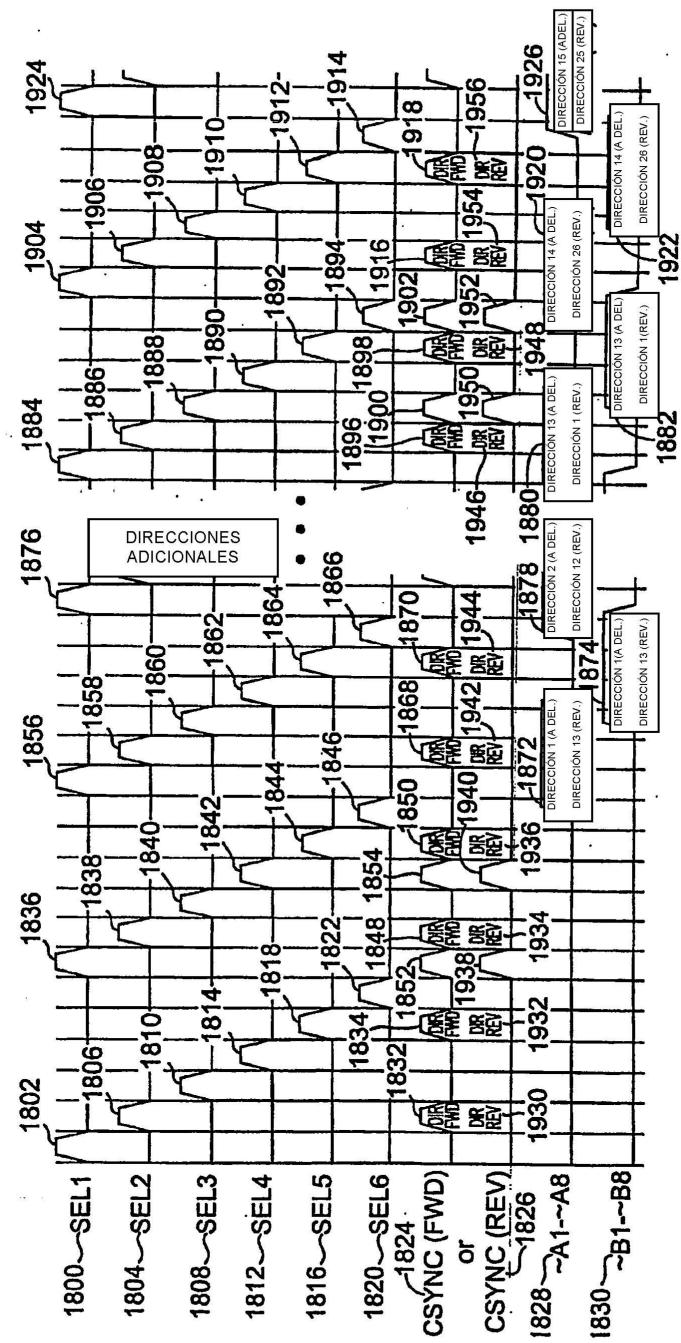

25 La Figura 8, es un diagrama de temporización que ilustra el funcionamiento de una forma de realización de una matriz de células de disparo.

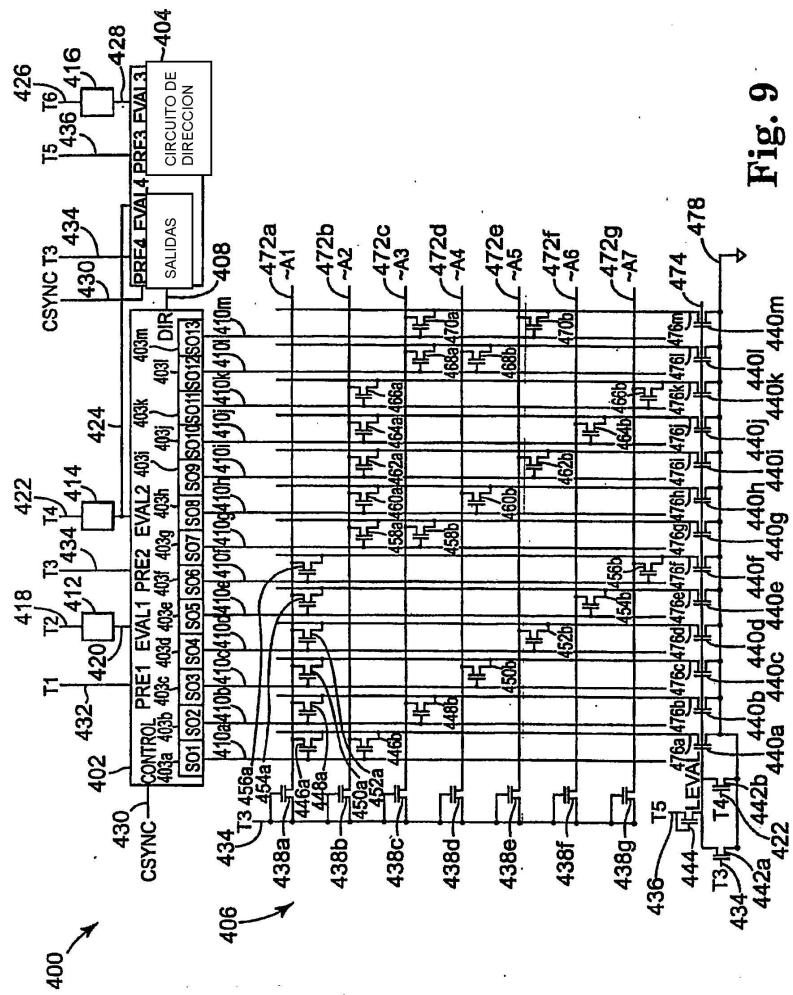

La Figura 9, es un diagrama que ilustra una forma de realización de un generador de dirección en la base de un cabezal de impresión.

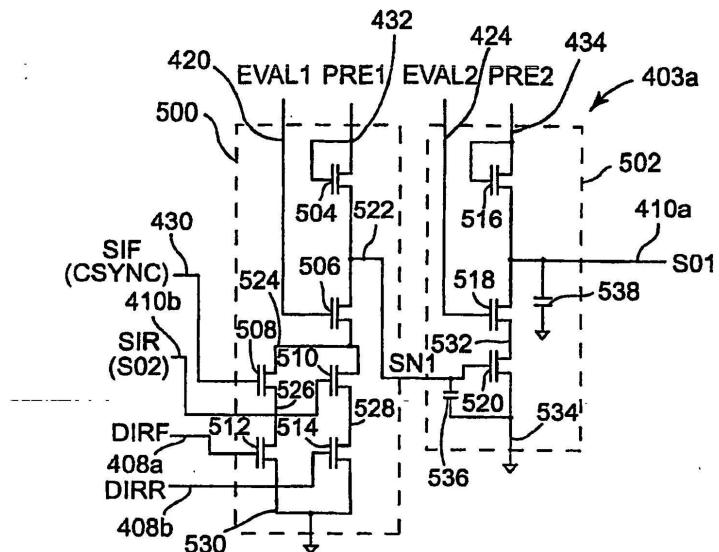

25 La Figura 10A, es un diagrama que ilustra una célula de registro de desplazamiento, en un registro de desplazamiento.

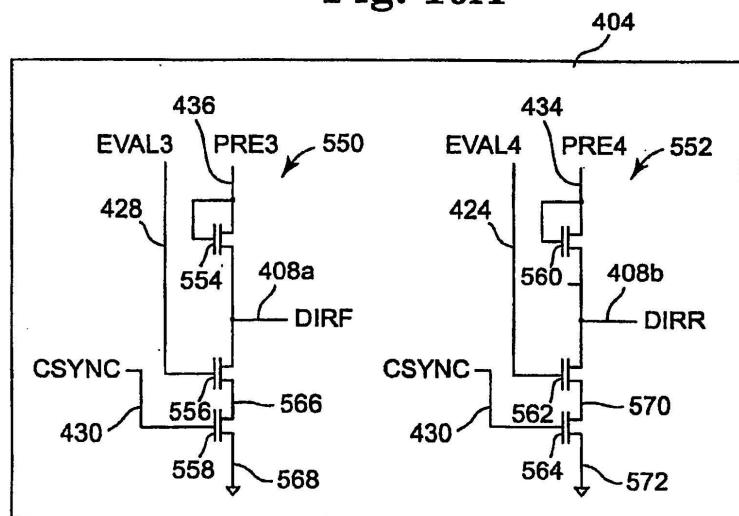

La Figura 10B, es un diagrama que ilustra un circuito de dirección.

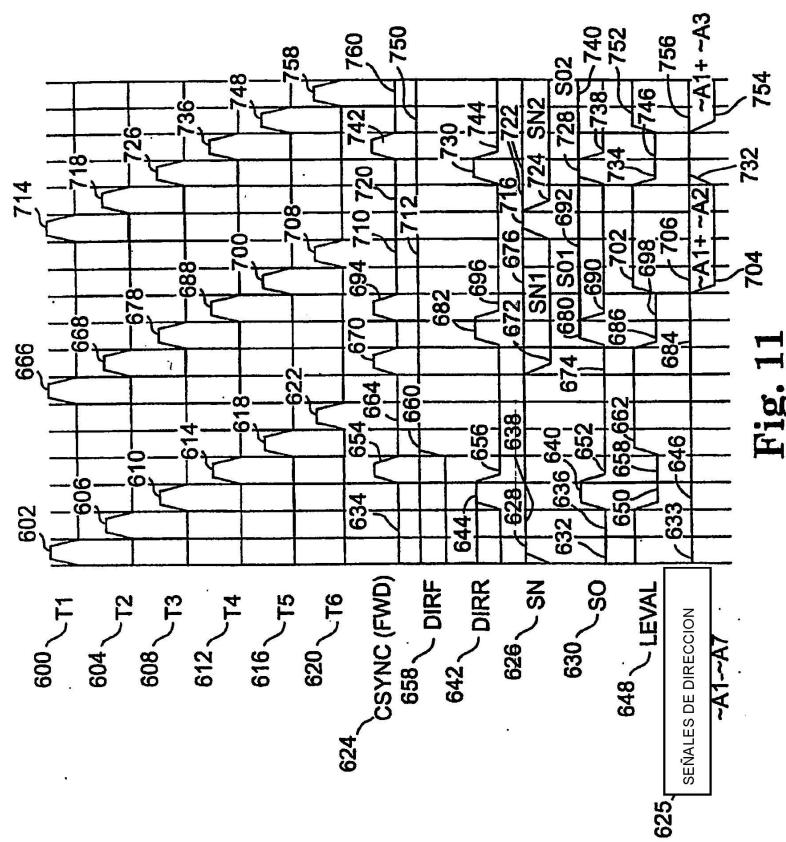

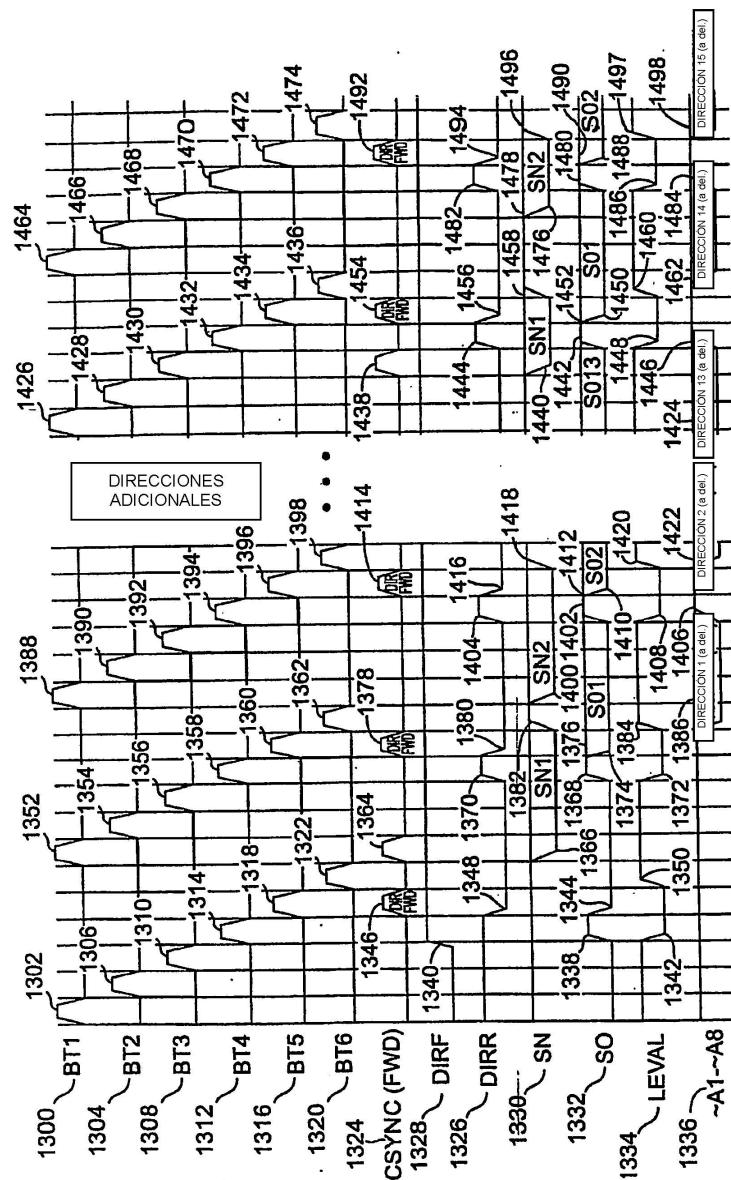

30 La Figura 11, es un diagrama de temporización que ilustra el funcionamiento de un generador de dirección en dirección hacia delante.

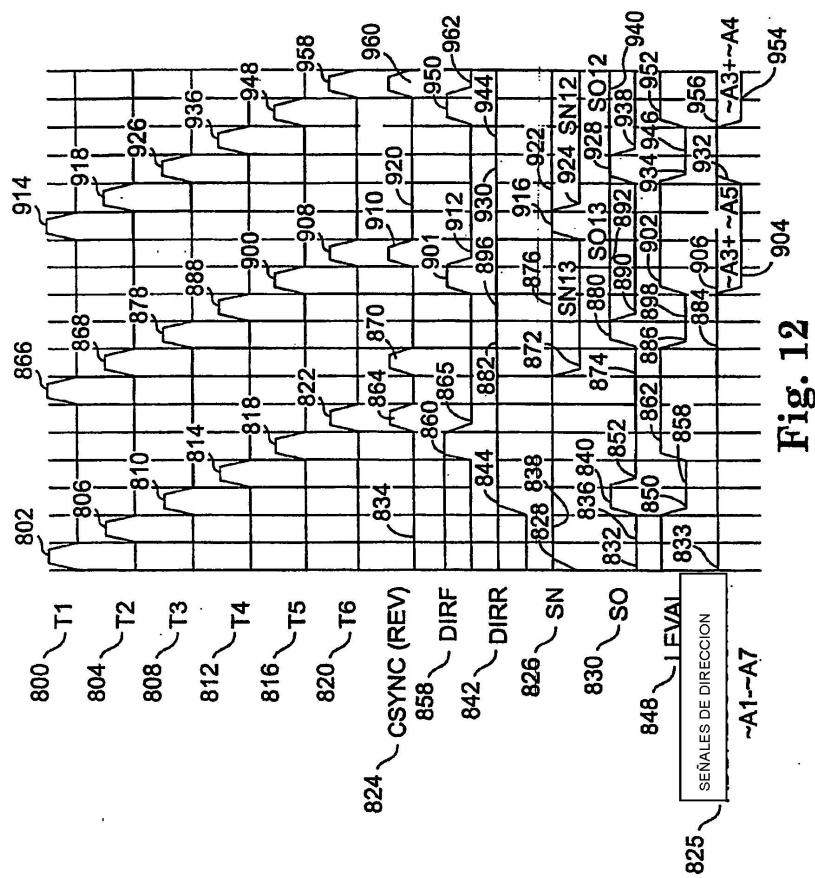

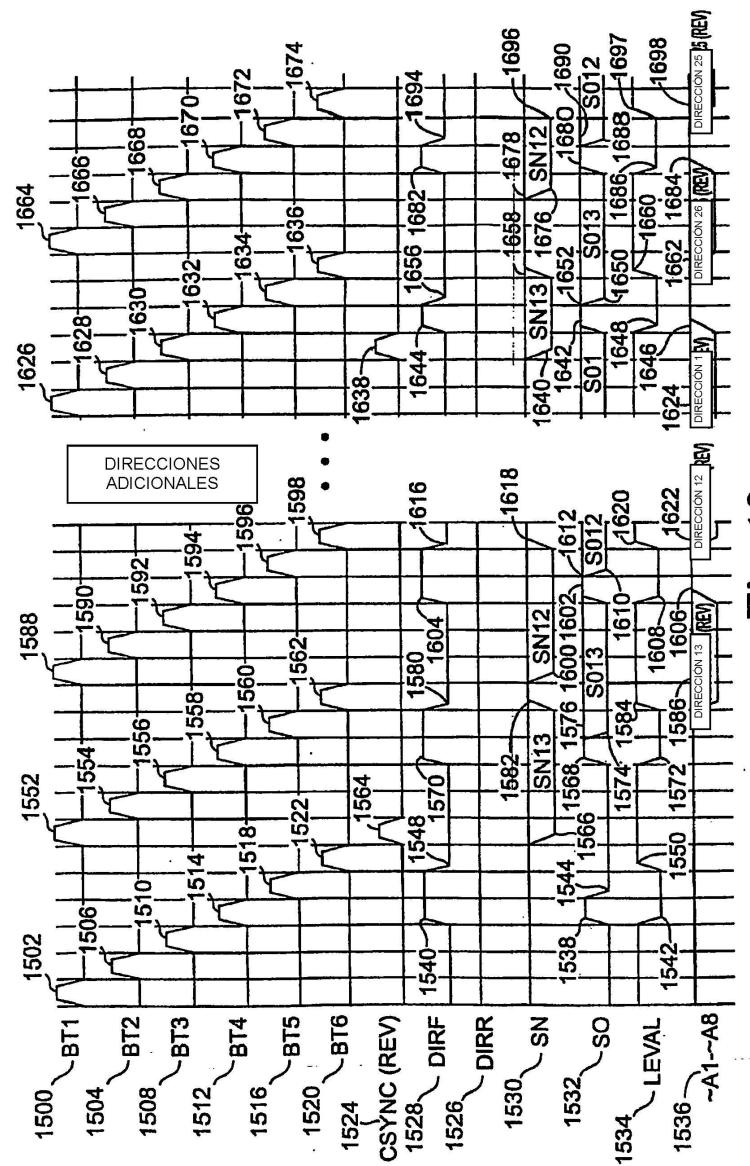

La Figura 12, es un diagrama de temporización que ilustra el funcionamiento de un generador de dirección en dirección reversa.

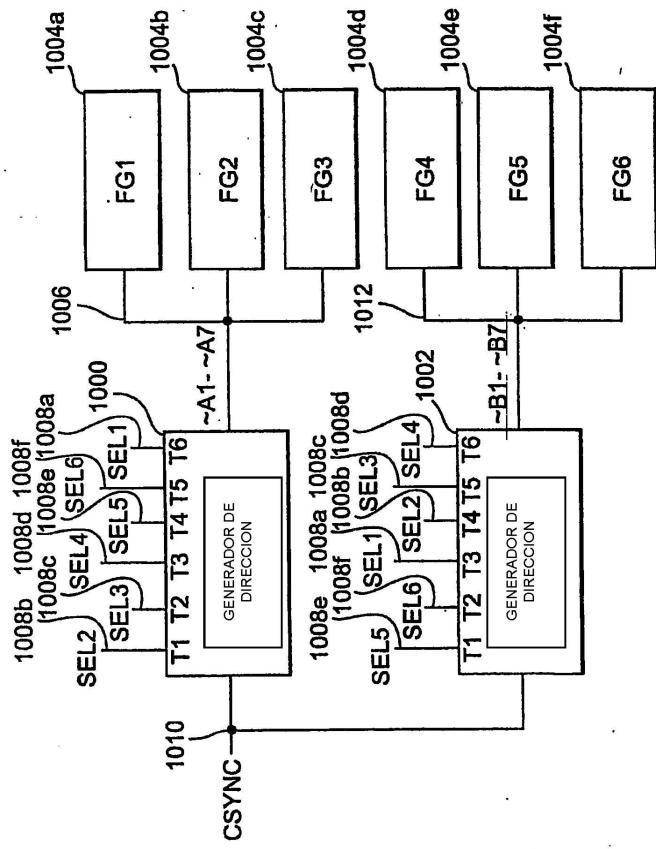

35 La Figura 13, es un diagrama de bloque que ilustra una forma de realización de dos generadores de dirección y seis grupos de disparo, en la base de un cabezal de impresión.

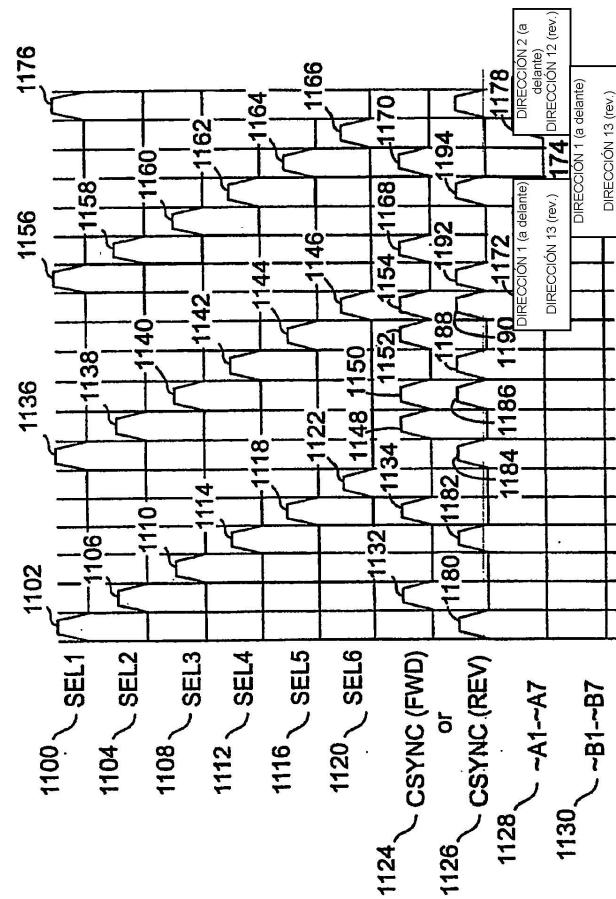

La Figura 14, es un diagrama de temporización que ilustra el funcionamiento hacia delante y hacia atrás de los generadores de dirección, en la base de un cabezal de impresión.

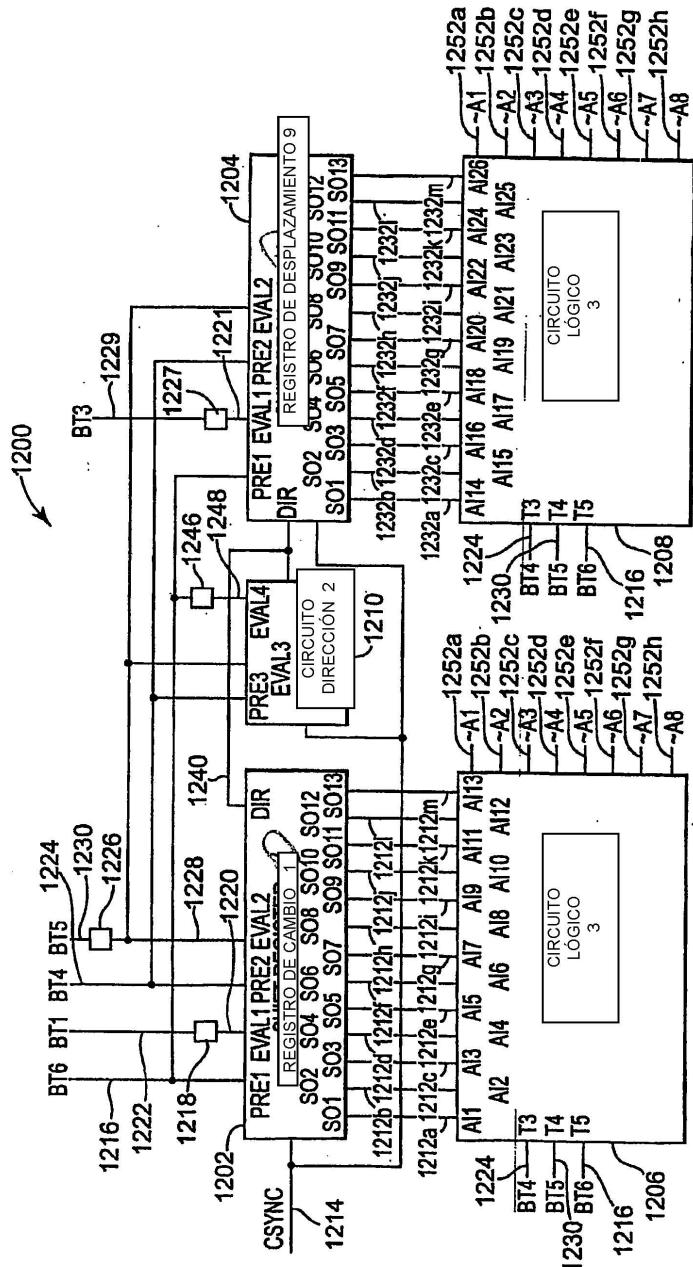

40 La Figura 15, es un diagrama de bloque que ilustra una forma de realización de un generador de dirección, un circuito de cierre y seis grupos de disparo, en la base de un cabezal de impresión.

La Figura 15, es un diagrama que ilustra una forma de realización de un generador de dirección de selección de banco, en la base de un cabezal de impresión.

45 La figura 16, es un diagrama que ilustra una forma de realización de un circuito de dirección.

La Figura 17, es un diagrama de temporización que ilustra el funcionamiento de una forma de realización de un generador de dirección de selección de banco en la dirección hacia delante.

La Figura 18, es un diagrama de temporización que ilustra el funcionamiento de una forma de realización de un generador de dirección de selección de banco en la dirección reversa.

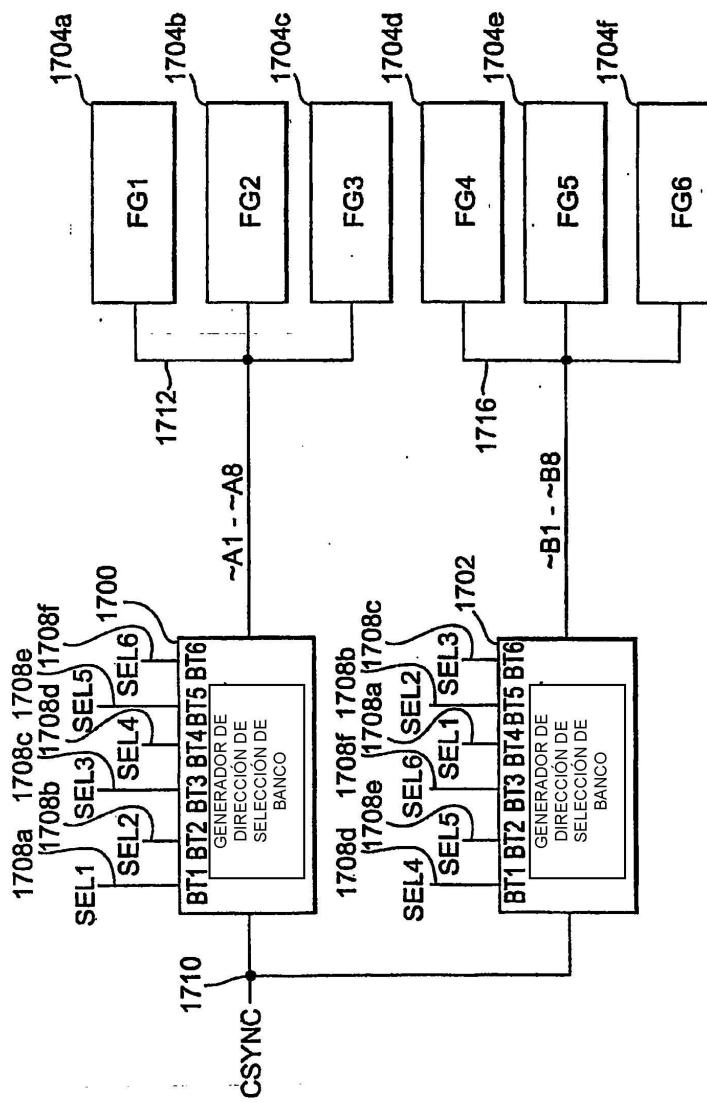

45 La Figura 19, es un diagrama que ilustra una forma de realización de dos generadores de selección de dirección de banco y seis grupos de disparo, en la base de un cabezal de impresión.

La Figura 20, es un diagrama de temporización que ilustra el funcionamiento hacia delante y reverso de una forma de realización de dos generadores de banco de selección de dirección, en la base de un cabezal de impresión.

50 Descripción detallada

En la siguiente descripción detallada, se hace referencia a los dibujos que se acompañan, los cuales forman parte de esta y en los cuales se muestra, a modo de ilustración, formas específicas de realización, en las cuales la invención puede ser llevada a la práctica. A este respecto, terminología direccional, tal como "parte superior", "parte inferior", "parte delantera", "parte trasera", "principal", "borde", etc., es utilizada con referencia a la orientación de las Figura(s) que se describen. Debido a que los componentes y formas de realización de la presente invención, pueden ser colocados en un número de orientaciones diferentes, la terminología direccional es utilizada con propósito de ilustración y no es, en ningún caso, limitativa. Debe ser entendido, que pueden ser utilizadas otras formas de realización y pueden ser realizados cambios estructurales o lógicos, sin que se aparten del ámbito de protección de la presente invención. Por tanto, la siguiente descripción detallada no debe ser tomada en sentido limitativo y el campo de protección de la presente invención se define por las reivindicaciones que se acompañan.

65 La Figura 1, ilustra una forma de realización de un sistema de impresión por inyección de tinta 20. El sistema de impresión por inyección de tinta 20, constituye una forma de realización de un sistema de expulsión o eyeción de fluido, que incluye un dispositivo de expulsión o eyeción de fluido, tal como un ensamblaje de cabezal de impresión

de tinta 22 y un ensamblaje de suministro de fluido, tal como un ensamblaje de suministro de tinta 24. El sistema de impresión por inyección de tinta 20, también incluye un ensamblaje de base 26, un ensamblaje de medios de transporte 28 y un controlador electrónico 30. Al menos un suministrador de energía 32, proporciona electricidad a los diferentes componentes eléctricos del sistema de impresión por inyección de tinta 20.

- 5 En una forma de realización, el ensamblaje de cabezal de impresión por inyección de tinta 22, incluye, al menos, un cabezal de impresión o una base de cabezal de impresión 40, que inyecta gotas de tinta a través de una pluralidad de orificios o boquillas 34, hacia un medio de impresión 36, de tal forma que imprime sobre el medio de impresión 36. El cabezal de impresión, es una forma de realización de un dispositivo de expulsión o eyeción de fluido. El medio de impresión 36, puede ser cualquier tipo de hoja de material adecuado, como papel, cartulina, transparencias, Mylar, tela y parecidos. Típicamente, las boquillas 34 están dispuestas en una o más columnas o matrices, de tal forma que la expulsión o eyeción secuenciada apropiada de tinta desde las boquillas 34, hace que caracteres, símbolos y/o otros gráficos o imágenes, sean impresos sobre el medio de impresión 36, al ser movidos, uno con relación al otro, el ensamblaje de cabezal de impresión por inyección de tinta 22 y el medio de impresión 36.

- 10 15 Mientras la siguiente descripción se refiere a la inyección de tinta desde el ensamblaje del cabezal de impresión 22, se entiende que otros líquidos, fluidos o materiales fluidificables, incluyendo fluido transparente, pueden ser inyectados desde el ensamblaje del cabezal de impresión 22.

- 20 El ensamblaje de suministro de tinta 24, como una forma de realización de un ensamblaje de suministro de fluido, proporciona tinta al ensamblaje del cabezal de impresión 22 e incluye un depósito 38 para el almacenaje de tinta. Como tal, la tinta fluye desde el depósito 38 al ensamblaje del cabezal de impresión por inyección de tinta 22. El ensamblaje de suministro de tinta 24 y el ensamblaje del cabezal de impresión por inyección de tinta 22, pueden formar, bien un sistema de suministro de tinta de un solo sentido o un sistema de suministro de tinta recirculante. En un sistema de suministro de tinta de un solo sentido, sustancialmente, toda la tinta proporcionada al ensamblaje del cabezal de impresión por inyección de tinta 22, es consumida durante la impresión. En un sistema de suministro de tinta recirculante, solo una porción de la tinta proporcionada al ensamblaje del cabezal de impresión por inyección de tinta 22, es consumida durante la impresión. Como tal, la tinta no consumida durante la impresión, es devuelta al ensamblaje de suministro de tinta 24.

- 25 30 35 40 45 50 55 60 65 En una forma de realización, el ensamblaje del cabezal de impresión por inyección de tinta 22 y el ensamblaje de suministro de tinta 24, están albergados juntos en un cartucho de inyección de tinta pluma. El cartucho de inyección de tinta o pluma, es una forma de realización de un dispositivo de expulsión o eyeción de fluido. En otras forma de realización, el ensamblaje de suministro de tinta 24, esta separado del ensamblaje del cabezal de impresión por inyección de tinta 22 y proporciona tinta al ensamblaje del cabezal de impresión por inyección de tinta 22, a través de una conexión interfaz, como un tubo de suministro (no mostrado). En cualquiera las dos formas de realización, el depósito 38 del ensamblaje de suministro de tinta 24, puede ser extraído, reemplazado y/o rellenado. En una forma de realización, en donde el ensamblaje del cabezal de impresión por inyección de tinta 22 y el ensamblaje de suministro de tinta 24, están albergados juntos en un cartucho de inyección de tinta, el depósito 38 incluye un depósito local, situado dentro del cartucho y puede también incluir un depósito más grande, situado separadamente del cartucho. Como tal, el depósito más grande separado, sirve para llenar el depósito local. Correlativamente, el depósito más grande separado y/o el depósito local, pueden ser extraídos, reemplazados y/o rellenados.

- El ensamblaje de base 26 sitúa el ensamblaje del cabezal de impresión por inyección de tinta 22, en relación al ensamblaje de medios de transporte 28 y el ensamblaje de medios de transporte 28 sitúa el medio de impresión 36, en relación al ensamblaje del cabezal de impresión por inyección de tinta 22. Así, es definida una zona de impresión 37, como adyacente a las boquillas 34, en un área entre el ensamblaje del cabezal de impresión por inyección de tinta 22 y el medio de impresión 36. En una forma de realización, el ensamblaje del cabezal de impresión por inyección de tinta 22, es un ensamblaje de cabezal de impresión de tipo escáner. Como tal, el ensamblaje de base 26 incluye un cartucho (no mostrado), para el movimiento del ensamblaje del cabezal de impresión por inyección de tinta 22 con relación al ensamblaje de medios de transporte 28, para escanear el medio de impresión 36. En otra forma de realización, el ensamblaje del cabezal de impresión por inyección de tinta 22, es un ensamblaje de cabezal de impresión de tipo no escáner. Como tal, el ensamblaje de base 26 fija el ensamblaje del cabezal de impresión por inyección de tinta 22 en una posición prescrita, relativa al ensamblaje de medios de transporte 28. Así, el ensamblaje de medios de transporte 28 coloca el medio de impresión 36, en relación al ensamblaje del cabezal de impresión por inyección de tinta 22.

- El controlador electrónico o el controlador de impresión 30, típicamente, incluye un procesador, firmware y otros electrónicos, o cualquier combinación de los mismos, para comunicar con y controlar el ensamblaje del cabezal de impresión por inyección de tinta 22, el ensamblaje de base 26 y el ensamblaje de medios de transporte 28. El controlador electrónico 30 recibe los datos 39 de un sistema de servidor, como un ordenador y, usualmente, incluye memoria para almacenar temporalmente los datos 39. Típicamente, los datos 39 son enviados al sistema de impresión por inyección de tinta 20, a lo largo de un sendero de transmisión de información electrónico, de infrarrojos, óptico u otros. Los datos 39 representan, por ejemplo, un documento y/o archivo a ser impreso. Como tal, los datos 39 forman un trabajo de impresión para el sistema de impresión por inyección de tinta 20 e incluyen uno o más comandos de trabajos de impresión y/o comandos de parámetros.

En una forma de realización, el controlador electrónico 30, controla el ensamblaje del cabezal de impresión por inyección de tinta 22, para la expulsión o eyección de gotas de tinta desde las boquillas 34. Como tal, el controlador electrónico 30 define un patrón de gotas de tinta expulsadas o eyectadas, que forman caracteres, símbolos y/u otros gráficos o imágenes, sobre el medio de impresión 36. El patrón de gotas de tinta expulsadas o eyectadas, está determinado por los comandos de los trabajos de impresión y/o los parámetros de los comandos.

En una forma de realización, el ensamblaje del cabezal de impresión por inyección de tinta 22, incluye un cabezal de impresión 40. En otra forma de realización, el ensamblaje del cabezal de impresión por inyección de tinta 22, es un ensamblaje de matriz amplia o de cabezal de impresión multicabezas. En una forma de realización de una matriz amplia, el ensamblaje del cabezal de impresión por inyección de tinta 22 incluye un carro transportador, que transporta las bases de los cabezales de impresión 40, proporciona comunicación eléctrica entre las bases de los cabezales de impresión 40 y el controlador electrónico 30 y proporciona comunicación de fluidos entre las bases de los cabezales de impresión 40 y el ensamblaje de suministro de tinta 24.

La Figura 2, es un diagrama que ilustra una porción de una forma de realización de una base de un cabezal de impresión 40. La base del cabezal de impresión 40 incluye una matriz de impresión o de elementos de expulsión o eyección de fluido 42. Los elementos de impresión 42 están formados sobre un sustrato 44, el cual tiene una ranura de alimentación de tinta 46, formada en el mismo. Como tal, la ranura de alimentación de tinta 46 proporciona un suministro de tinta líquida a los elementos de impresión 42. La ranura de alimentación de tinta, es una forma de realización de una fuente de alimentación de fluido. Otras formas de realización de fuentes de alimentación de fluido, incluyen pero no se limitan, a los correspondientes agujeros individuales de alimentación de tinta, que alimentan las correspondientes cámaras de vaporización y las zanjas múltiples de alimentación de tinta más cortas, que alimentan, cada una, los correspondientes grupos de elementos de expulsión o eyección de fluido. Una estructura de película delgada 48 tiene un canal de alimentación de tinta 54 formado en la misma, el cual se comunica con la ranura de alimentación de tinta 46, formada en el sustrato 44. Una capa de orificios 50 tiene una cara frontal 50a y una abertura de boquilla 34 formada en la cara frontal 50a. La capa de orificios 50 también tiene una cámara de boquilla o cámara de vaporización 56, formada en la misma, la cual se comunica con la abertura de boquilla 34 y el canal de alimentación de tinta 54 de la estructura de película delgada 48. Una resistencia de disparo 52 esta situada dentro de la cámara de vaporización 56 y lleva 58 la resistencia de disparo 52 conectada eléctricamente con los circuitos que controlan la aplicación de corriente eléctrica a través de las resistencias de disparo seleccionadas. Un generador de gotas 60, como se indica aquí, incluye la resistencia de disparo 52, la cámara de boquilla o cámara de vaporización 56 y la abertura de boquilla 34.

Durante la impresión, la tinta fluye desde la ranura de alimentación de tinta 46 a la cámara de vaporización 56, a través del canal de alimentación de tinta 54. La abertura de la boquilla 34, esta asociada operativamente con la resistencia de disparo 52, de forma que, las gotitas de tinta que están dentro de la cámara de vaporización 56, son expulsadas o eyectadas a través de la abertura de la boquilla 34 (por ejemplo, sustancialmente normal al plano de la resistencia de disparo 52) y hacia el medio de impresión 36, mediante la energización de la resistencia de disparo 52.

Formas de realización ejemplares de las bases de los cabezales de impresión 40, incluyen un cabezal de impresión térmico, un cabezal de impresión piezoelectrónico y un cabezal de impresión electroestático o cualquier otro tipo de dispositivo de expulsión o eyección de fluido, conocido en el estado de la técnica, que pueda ser integrado en una estructura multicapas. El sustrato 44 esta formado, por ejemplo, de silicona, cristal, cerámica o un polímero estable y la estructura de película delgada 48 esta formada para incluir uno o más sustratos de pasivación o aislamiento de dióxido de silicona, carburo de silicona, nitrógeno de silicona, tantalio, cristal polisilicio u otro material adecuado. La estructura de película delgada 48 también incluye, al menos, un sustrato conductor, el cual define la resistencia de disparo 52 y los cables 58. En una forma de realización, el sustrato conductor comprende, por ejemplo, aluminio, oro, tantalio, aluminio tantalio u otro metal o aleación de metal. En una forma de realización, el circuito de células de disparo, como se describe en detalle abajo, es implementado en capas de sustrato y de película delgada, como el sustrato 44 y la estructura de película delgada 48.

En una forma de realización, la capa de orificios 50 comprende una resina epoxi foto impresionable, por ejemplo, un epoxi referido como SU8 comercializado por Micro-Chem, Newton, MA. Técnicas ejemplares para la fabricación de la capa de orificios 50, con SU8 u otros polímeros, se describen en detalle en la Patente USA Número 6162589. En una forma de realización, la capa de orificios 50 esta formada por dos capas separadas, referidas como una capa de barrera (por ejemplo, una capa barrera de film seco foto resistente) y una capa metálica de orificios (por ejemplo una capa de níquel, cobre, aleaciones hierro/níquel, paladio, oro o rodio) formada sobre la capa de barrera. Sin embargo, para formar la capa de orificios 50 pueden ser empleados otros materiales adecuados.

La Figura 3, es un diagrama que ilustra los generadores de gotas 60, situados a lo largo de la ranura de alimentación de tinta 46, en una forma de realización de la base del cabezal de impresión 40. La ranura de alimentación de tinta 46 incluye lados opuestos de la ranura de alimentación de tinta 46a y 46b. Los generadores de gotas 60 están dispuestos a lo largo de cada uno de los lados opuestos de la ranura de alimentación de tinta 46a y 46b. Un total de

n generadores de gotas 60 están situados a lo largo de la ranura de alimentación de tinta 46, con m generadores de gotas 60 situados a lo largo del lado de la ranura de alimentación de tinta 46a y n – m generadores de gotas 60 situados a lo largo del lado de la ranura de alimentación de tinta 46b. En una forma de realización, n equivale a 200 generadores de gotas 60 situados a lo largo de la ranura de alimentación de tinta 46 y m equivale a 100 generadores de gotas 60 situados a lo largo de cada uno de los lados opuestos de la ranura de alimentación de tinta 46a y 46b. En otras formas de realización, cualquier número adecuado de generadores de gotas 60, puede ser dispuesto a lo largo de la ranura de alimentación de tinta 46.

5 La ranura de alimentación de tinta 46, proporciona tinta a cada uno de los n generadores de gotas 60 dispuestos a lo largo de la ranura de alimentación de tinta 46. Cada uno de los n generadores de gotas 60 incluye una resistencia de disparo 52, una cámara de vaporización 56 y una boquilla 34. Cada una de las n cámaras de vaporización 56 está conectada fluidamente con la ranura de alimentación de tinta 46, a través de, al menos, un canal de alimentación de tinta 54. Las resistencias de disparo 52 de los generadores de gotas 60, son energizadas en una secuencia controlada, para expulsar o eyectar fluido desde las cámaras de vaporización 56 y a través de las boquillas 34, para imprimir una imagen sobre el medio de impresión 36.

10 La Figura 4, es un diagrama que ilustra una forma de realización de una célula de disparo 70, empleada en una forma de realización de la base del cabezal de impresión 40. La célula de disparo 70 incluye una resistencia de disparo 52, un interruptor de accionamiento de resistencia 72 y un circuito de memoria 74. La resistencia de disparo 20 52 es parte del generador de gotas 60. El interruptor de accionamiento 72 y el circuito de memoria 74, son parte de los circuitos que controlan la aplicación de corriente eléctrica a través de la resistencia de disparo 52. La célula de disparo 70 esta formada en la estructura de película delgada 48 y sobre el sustrato 44.

15 En una forma de realización, la resistencia de disparo 52 es una resistencia de película delgada y el interruptor de accionamiento 72 es un transistor de efecto de campo (FET). La resistencia de disparo 52 esta conectada eléctricamente con la línea de disparo 76 y la trayectoria de la fuente de drenaje del interruptor de accionamiento 72. La trayectoria de la fuente de drenaje del interruptor de accionamiento 72 esta también conectada eléctricamente con la línea de referencia 78, que esta conectada con un voltaje de referencia, como tierra. La puerta del interruptor de accionamiento 72 está conectada eléctricamente con el circuito de memoria 74, que controla el estado del 25 interruptor de accionamiento 72.

20 El circuito de memoria 74 esta conectado eléctricamente con una línea de datos 80 y las líneas de activación 82. La línea de datos 80 recibe una señal de datos que representa parte de una imagen y las líneas de activación 82 reciben señales de activación para controlar el funcionamiento del circuito de memoria 74. El circuito de memoria 35 74 almacena un bote de datos, como sea habilitado por las señales de activación. El nivel lógico de los bites de datos almacenados, fija el estado (por ejemplo, encendido o apagado, conduciendo o no conduciendo) del interruptor de accionamiento 72. Las señales de habilitación pueden incluir una o más señales de selección y una o más señales de dirección.

30 40 La línea de disparo 76 recibe una señal de energía, que comprende pulsaciones de energía y proporciona una pulsación de energía a la resistencia de disparo 52. En una forma de realización, las pulsaciones de energía son proporcionadas por un controlador electrónico 30, para tener tiempos de encendido temporizados y duración temporizada, para proporcionar una cantidad apropiada de energía para calentar y vaporizar el fluido, en la cámara de vaporización 56 del generador de gotas 60. Si el interruptor de accionamiento 72 esta encendido (conduciendo), 45 la pulsación de energía calienta la resistencia de disparo 52 para calentar y expulsar o eyectar fluido desde el generador de gotas 60. Si el interruptor de accionamiento 72 esta apagado (no conduciendo), la pulsación de energía no calienta la resistencia de disparo 52 y el fluido permanece en el generador de gotas 60.

45 50 La Figura 5, es un diagrama esquemático que ilustra una forma de realización de una matriz de células de disparo de un cabezal de impresión por inyección de tinta, indicado como 100. La matriz de células de disparo 100 incluye una pluralidad de células de disparo 70, dispuestas en n grupos de disparo 102a-102n. En una forma de realización, las células de disparo 70 están dispuestas en seis grupos de disparo 102a-102n. En otras formas de realización, las células de disparo 70 pueden estar dispuestas en cualquier número adecuado de grupos de disparo 102a-102n, como cuatro o más grupos de disparo 102a-102n.

55 60 65 Las células de disparo 70 en la matriz 100, están dispuestas esquemáticamente en L filas y m columnas. Las L filas de células de disparo 70 están conectadas eléctricamente con las líneas de activación 104, que reciben las señales de habilitación. Cada fila de células de disparo 70, referidas aquí como un subgrupo de filas o subgrupo de células de disparo 70, esta conectada eléctricamente con un set de líneas de activación de subgrupo 106a-106L. Las líneas de activación de subgrupo 106a-106L reciben las señales de activación de subgrupo SG1, SG2, ... SGL, que habilitan el correspondiente subgrupo de células de disparo 70.

70 75 80 Las m columnas, están conectadas eléctricamente con las m líneas de datos 108a-108m, que reciben las señales de datos D1, D2 ... Dm, respectivamente. Cada una de las m columnas incluye las células de disparo 70, en cada uno de los n grupos de disparo 102a-102n y cada columna de células de disparo 70, referida aquí como un grupo de

línea de datos o grupo de datos, esta conectada eléctricamente con una de las líneas de datos 108a-108m. En otras palabras, cada una de las líneas de datos 108a-108m, esta conectada eléctricamente con cada una de las células de disparo 70 en una columna, incluyendo las células de disparo 70 en cada uno de los grupos de disparo 102a-102n. Por ejemplo, la línea de datos 108a esta conectada eléctricamente con cada una de las células de disparo 70, en la última columna de la izquierda, incluyendo las células de disparo 70 en cada uno de los grupos de disparo 102a-102n.

5 La línea de datos 108b esta conectada eléctricamente con cada una de las células de disparo 70, en la columna adyacente y, así sucesivamente, sobre e incluyendo la línea de datos 108m, que esta conectada eléctricamente con cada una de las células de disparo 70 de la ultima columna de la derecha, incluyendo las células de disparo 70 de cada uno de los grupos de disparo 102a-102n.

10 En una forma de realización, la matriz 100 esta dispuesta en seis grupos de disparo 102a-102n y cada uno de los seis grupos de disparo 102a-102n incluye 13 subgrupos y ocho grupos de línea de datos. En otras formas de realización, la matriz 100 puede estar dispuesta en cualquier número adecuado de grupos de disparo 102a-102n y en de cualquier número adecuado de subgrupos y grupos de línea de datos. En cualquier forma de realización, los

15 grupos de disparo 102a-102n no se encuentran limitados por tener el mismo número de subgrupos y de grupos de línea de datos. En cambio, cada uno de los grupos de disparo 102a-102n puede tener un número diferente de subgrupos y/o de grupos de línea de datos, en comparación con cualquier otro grupo de disparo 102a-102n. Además, cada subgrupo puede tener un número diferente de células de disparo 70, en comparación con cualquier otro subgrupo y cada grupo de línea de datos puede tener un número diferente de células de disparo 70, en

20 comparación con cualquier otro grupo de línea de datos.

Las células de disparo 70 en cada uno de los grupos de disparo 102a-102n, están conectadas eléctricamente con una de las líneas de disparo 110a-110n. En un grupo de disparo 102a, cada una de las células de disparo 70 esta conectada eléctricamente con la línea de disparo 110a, que recibe la señal de disparo o señal de energía FUEGO1.

25 En el grupo de disparo 102b, cada una de las células de disparo 70 esta conectada eléctricamente con la línea de disparo 110b, que recibe la señal de disparo o la señal de energía FUEGO2 y, así en sucesivamente, hasta e incluyendo el grupo de disparo 102n, en donde cada una de las células de disparo 70 esta conectada eléctricamente con la línea de disparo 110n, que recibe la señal de disparo o la señal de energía FUEGOOn. Además, cada una de las células de disparo 70, en cada uno de los grupos de disparo 102a-102n, esta conectada eléctricamente con una

30 línea de referencia común 112, que esta unida a tierra.

En funcionamiento, los subgrupos de señales de activación SG1, SG2, ... SGL son proporcionados sobre las líneas de activación de subgrupo 106a-106L, para habilitar un subgrupo de células de disparo 70. Las células de disparo habilitadas 70 almacenan las señales de datos D1, D2 ... Dm proporcionadas sobre las líneas de datos 108a-108m.

35 Las señales de datos D1, D2 ... Dm son almacenadas en los circuitos de memoria 74 de las células de disparo habilitadas 70. Cada una de las señales de datos almacenadas D1, D2 ... Dm, fija el estado del interruptor de accionamiento 72 en una de las células de disparo habilitadas 70. El interruptor de accionamiento 72 es fijado para conducir o no conducir, basado en el valor de señal de los datos almacenada.

40 Después de que los estados de los interruptores de accionamiento seleccionados 72 están fijados, es proporcionada una señal de energía FUEGO1-FUEGOOn, sobre la línea de disparo 110a-110n que se corresponde con el grupo de disparo 102a-102n, que incluye el subgrupo seleccionado de células de disparo 70. La señal de energía FUEGO1-FUEGOOn incluye una pulsación de energía. La pulsación de energía es proporcionada sobre la línea de disparo seleccionada 110a-110n, para energizar las resistencias de disparo 52, en las células de disparo 70 que tienen los interruptores de accionamiento 72 conductores. Las resistencias de disparo 52 energizadas, calientan y expulsan o eyectan tinta sobre el medio de impresión 36, para imprimir una imagen representada por las señales de datos D1, D2 ... Dm. El proceso de habilitar a un subgrupo de células de disparo 70, almacenar las señales de datos D1, D2 ... Dm en el subgrupo habilitado y proporcionar una señal de energía FUEGO1-FUEGOOn para energizar las resistencias de disparo 52 en el subgrupo habilitado, continua hasta que la impresión se detiene.

50 En una forma de realización, como se proporciona una señal de energía FUEGO1-FUEGOOn a un grupo de disparo seleccionado 102a-102n, los subgrupos de señales de activación SG1, SG2, ... SGL cambian, para seleccionar y habilitar otro subgrupo en un grupo de disparo diferente 102a-102n. El subgrupo nuevamente habilitado, almacena las señales de datos D1, D2 ... Dm proporcionadas sobre las líneas de datos 108a-108m y una señal de energía

55 FUEGO1-FUEGOOn es proporcionada sobre una de las líneas de disparo 110a-110n, para energizar las resistencias de disparo 52 en las células de disparo nuevamente habilitadas 70. En cada momento, solo un subgrupo de células de disparo 70 es habilitado, por el subgrupo de señales de activación SG1, SG2, ... SGL, para almacenar las señales de datos D1, D2 ... Dm proporcionadas en las líneas de datos 108a-108m. A este respecto, las señales de datos D1, D2 ... Dm sobre las líneas de datos 108a-108m, son señales de datos de división multiplicada temporizada. También, solo un subgrupo en un grupo de disparo seleccionado 102a-102n, incluye los interruptores de accionamiento 72, que están fijados para conducir mientras una señal de energía FUEGO1-FUEGOOn es proporcionada al grupo de disparo seleccionado 102a-102n. Sin embargo, las señales de energía FUEGO1-FUEGOOn proporcionadas a los diferentes grupos de disparo 102a-102n, pueden y de hecho se superponen.

La Figura 6, es un diagrama esquemático que ilustra una forma de realización de una célula de disparo precargada 120. La célula de disparo precargada 120 es una forma de realización de la célula de disparo 70. La célula de disparo precargada 120, incluye un interruptor de accionamiento 172 conectado eléctricamente con una resistencia de disparo 52. En una forma de realización, el interruptor de accionamiento 172 es un FET que incluye una trayectoria de fuente de drenaje, conectada eléctricamente, en un extremo, con un terminal de la resistencia de disparo 52 y, en el otro, con una línea de referencia 122. La línea de referencia 122 está unida a un voltaje de referencia, como tierra. El otro terminal de la resistencia de disparo 52 esta conectado eléctricamente con una línea de disparo 124, que recibe una señal de disparo o una señal de energía FUEGO que incluye pulsaciones de energía. Las pulsaciones de energía energizan la resistencia de disparo 52, si el interruptor de accionamiento 172 está encendido (conduciendo).

La puerta del interruptor de accionamiento 172 forma una capacidad de nodo de almacenaje 126, que funciona como un elemento de memoria para almacenar datos, debido a la activación secuencial de un transistor de precarga 128 y un transistor de selección 130. La trayectoria de la fuente de drenaje y la puerta del transistor de precarga 128, están conectadas eléctricamente con una línea de precarga 132 que recibe una señal de precarga. La puerta del interruptor de accionamiento 172 esta conectada eléctricamente con la trayectoria de la fuente de drenaje del transistor de precarga 128 y la trayectoria de la fuente de drenaje del transistor de selección 130. La puerta del transistor de selección 130 esta conectada eléctricamente con una línea de selección 134, que recibe una señal de selección. La capacidad del nodo de almacenaje 126 se muestra en líneas de guiones, ya que es parte del interruptor de accionamiento 172. Alternativamente, puede ser utilizado como un elemento de memoria, un condensador de capacidad separado del interruptor de accionamiento 172.

Un transistor de datos 136, un transistor de primera dirección 138 y un transistor de segunda dirección 140, incluyen trayectorias de fuentes de drenaje que están conectadas eléctricamente en paralelo. La combinación paralela del transistor de datos 136, el transistor de primera dirección 138 y el transistor de segunda dirección 140, está conectada eléctricamente, entre la trayectoria de la fuente de drenaje del transistor de selección 130 y la línea de referencia 122. El circuito en serie que incluye el transistor de selección 130, conectado a la combinación paralela del transistor de datos 136, el transistor de primera dirección 138 y el transistor de segunda dirección 140, esta conectado eléctricamente a través de la capacidad del nodo 126 del interruptor de accionamiento 172. La puerta del transistor de datos 136 esta conectada eléctricamente con la línea de datos 142, que recibe las señales de datos ~DATOS. La puerta del transistor de primera dirección 138 está conectada eléctricamente con una línea de dirección 144, que recibe las señales de dirección ~DIRECCION1 y la puerta del transistor de segunda dirección 140 esta conectada eléctricamente con una línea de segunda dirección 146, que recibe las señales de dirección ~DIRECCION2. Las señales de datos ~DATOS y las señales de dirección ~DIRECCION1 y ~DIRECCION2, están activas cuando son bajas, como se indica por la tilde (-) al principio del nombre de la señal. La capacidad del nodo 126, el transistor de precarga 128, el transistor de selección 130, el transistor de datos 136 y los transistores de dirección 138 y 140, forman una célula de memoria.

En funcionamiento, la capacidad del nodo 126 es precargada a través del transistor de precarga 128, mediante el suministro de una pulsación de voltaje de nivel alto sobre la línea de precarga 132. En una forma de realización, después de la pulsación de voltaje de nivel alto sobre la línea de precarga 132, es proporcionada una señal de datos ~DATOS sobre la línea de datos 142 para fijar el estado del transmisor de datos 136 y las señales de dirección ~DIRECCION1 y ~DIRECCION2 son proporcionadas sobre las líneas de dirección 144 y 146, para fijar los estados del transistor de primera dirección 138 y del transmisor de segunda dirección 140. Una pulsación de voltaje de suficiente magnitud es proporcionada sobre la línea de selección 134, para encender el transistor de selección 130 y la capacidad del nodo 126 descarga, si el transistor de datos 136, el transistor de primera dirección 138 y/o el transistor de segunda dirección 140, están encendidos. Alternativamente, la capacidad del nodo 126 permanece cargada si el transistor de datos 136, el transistor de primera dirección 138 y el transistor de segunda dirección 140, están todos apagados.

La célula de disparo precargada 120 es una célula de disparo dirigida, si ambas señales de dirección ~DIRECCION1 y ~DIRECCION2 están bajas y la capacidad del nodo 126 bien descarga, si la señal de datos ~DATOS es alta, o permanece cargada, si la señal de datos ~DATOS es baja. La célula de disparo precargada 120, no es una célula de disparo dirigida, si al menos una de las señales de dirección ~DIRECCION1 y ~DIRECCION2 es alta y la capacidad del nodo 126 descarga, independientemente del nivel de voltaje de la señal de datos ~DATOS. Los transistores de primera y segunda dirección 136 y 138 comprenden un decodificador de dirección y el transistor de datos 136 controla el nivel de voltaje sobre la capacidad del nodo 126, si la célula de disparo precargada 120 está dirigida.

La célula de disparo precargada 120 puede utilizar cualquier número de otras topologías o disposiciones, siempre que las relaciones operativas descritas arriba se mantengan. Por ejemplo, una puerta OR puede estar conectada con las líneas de dirección 144 y 146, estando la salida de la misma conectada con un único transistor.

La Figura 7, es un diagrama esquemático que ilustra una forma de realización de una matriz de una célula de disparo de cabezal de impresión por inyección de tinta 200. La matriz de la célula de disparo 200 incluye una pluralidad de células de disparo precargadas 120, dispuestas dentro de seis grupos de disparo 202a-202f. Las

células se disparo precargadas 120 en cada grupo de disparo 202a-202f, están dispuestas esquemáticamente en 13 filas y ocho columnas. Los grupos de disparo 202a-202f y las células de disparo precargadas 120 en la matriz 200, estas dispuestas esquemáticamente en 78 filas y ocho columnas, aunque el número de células de disparo precargadas y su distribución puede variar como se deseé.

- 5 Las ocho columnas de células de disparo precargadas 120 están conectadas eléctricamente con ocho líneas de datos 208a-208h, que reciben las señales de datos ~D1, ~D2 ... ~D8, respectivamente. Cada una de las ocho columnas, referidas aquí como un grupo de línea de datos o grupo de datos, incluye células de disparo precargadas 120 en cada uno de los seis grupos de disparo 202a-202f. Cada una de las células de disparo 120, en cada columna de células de disparo precargadas 120, está conectada eléctricamente con una de las líneas de datos 208a-208h. Todas las células de disparo precargadas 120 en un grupo de línea de datos, están conectadas eléctricamente con la misma línea de datos 208a-208h, que está conectada eléctricamente con las puertas de los transistores de datos 136 en las células de disparo precargadas 120 de la columna.

- 10 15 La línea de datos 208a esta conectada eléctricamente con cada una de las células de disparo precargadas 120 de la última columna de la izquierda, incluyendo las células de disparo precargadas en cada uno de los grupos de disparo 202a-202f. La línea de datos 208b esta conectada eléctricamente con cada una de las células de disparo precargadas 120 de la columna adyacente y, así sucesivamente, sobre e incluyendo la línea de datos 208h, que esta conectada eléctricamente con cada una de las células de disparo precargadas 120 de la última columna de la derecha, incluyendo las células de disparo precargadas 120 en cada uno de los grupos de disparo 202a-202f.

- 20 25 Las filas de las células de disparo precargadas 120, están conectadas eléctricamente con las líneas de dirección 206a-206g, que reciben las señales de dirección ~A1, ~A2 ... ~A7, respectivamente. Cada célula de disparo precargada 120, en una fila de células de disparo precargadas 120, referidas aquí como un subgrupo de filas o subgrupo de células de disparo precargadas 120, esta conectada eléctricamente con dos de las líneas de dirección 206a-206g. Todas las células de disparo precargadas 120 de un subgrupo de filas, están conectadas eléctricamente con las mismas dos líneas de dirección 206a-206g.

- 30 35 Los subgrupos de los grupos de disparo 202a-202f están identificados como los subgrupos SG1-1, a través de SG1-13 en el grupo de disparo uno (FG1) 202a, los subgrupos SG2-1 a través de SG2-13 en el grupo de disparo dos (FG2) 202b y, así sucesivamente, hasta e incluyendo los subgrupos SG6-1 a través de SG6-13 en el grupo de disparo seis (FG6) 202f. En otras formas de realización, cada grupo de disparo 202a-202f puede incluir cualquier número adecuado de subgrupos, como 14 o más subgrupos.

- 40 45 Cada subgrupo de células de disparo precargadas 120 esta conectado eléctricamente con dos líneas de dirección 206a-206g. Las dos líneas de dirección 206a-206g que se corresponden con un subgrupo, están conectadas eléctricamente con los transistores de dirección primera y segunda 138 y 140, en todas las células de disparo precargadas 120 del subgrupo. Una línea de dirección 206a-206g está conectada eléctricamente con la puerta de uno de los transistores de dirección primera y segunda 138 y 140 y otra línea de dirección 206a-206g esta conectada eléctricamente con la puerta del otro de los transistores de dirección primera y segunda 138 y 140. Las líneas de dirección 206a-206g reciben las señales de dirección ~A1, ~A2 ... ~A7 y están conectadas para proporcionar las señales de dirección ~A1, ~A2 ... ~A7 a los subgrupos de la matriz 200 como sigue:

| Señales de Dirección de Subaruno de filas | Subgrupos de Fila         |

|-------------------------------------------|---------------------------|

| ~A1, ~A2                                  | SG1-1, SG2-1 ... SG6-1    |

| ~A1, ~A3                                  | SG1-2, SG2-2 ... SG6-2    |

| ~A1, ~A4                                  | SG1-3, SG2-3 ... SG6-3    |

| ~A1, ~A5                                  | SG1-4, SG2-4 ... SG6-4    |

| ~A1, ~A6                                  | SG1-5, SG2-5 ... SG6-5    |

| ~A1, ~A7                                  | SG1-6, SG2-6 ... SG6-6    |

| ~A2, ~A3                                  | SG1-7, SG2-7 ... SG6-7    |

| ~A2, ~A4                                  | SG1-8, SG2-8 ... SG6-8    |

| ~A2, ~A5                                  | SG1-9, SG2-9 ... SG6-9    |

| ~A2, ~A6                                  | SG1-10, SG2-10 ... SG6-10 |

| ~A2, ~A7                                  | SG1-11, SG2-11 ... SG6-11 |

| ~A3, ~A4                                  | SG1-12, SG2-12 ... SG6-12 |

| ~A3, ~A5                                  | SG1-13, SG2-13 ... SG6-13 |

5

Los subgrupos de células de disparo precargadas 120 son dirigidos mediante el suministro de las señales de dirección ~A1, ~A2 ... ~A7 sobre las líneas de dirección 206a-206g. En una forma de realización, las líneas de dirección 206a-206g están conectadas eléctricamente con uno o más generadores de dirección, proporcionados sobre la base del cabezal de impresión 140.

- 10 Las líneas de precarga 210a-210f reciben las señales de precarga PRE1, PRE2 ... PRE6 y proporcionan las señales de precarga PRE1, PRE2 ... PRE6 a los correspondientes grupos de disparo 202a-202f. La línea de precarga 210a está conectada eléctricamente con todas las células de disparo precargadas 120 en FG1 202a. La línea de precarga 210b esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG2 202b y, así sucesivamente, hasta e incluyendo la línea precargada 210f, que está conectada eléctricamente con todas las células de disparo precargadas 120 en FG6 202f. Cada una de las líneas de precarga 210a-210f está conectada eléctricamente con la puerta y la trayectoria de la fuente de drenaje de todos los transistores de precarga 128 en el correspondiente grupo de disparo 202a-202f y todas las células de disparo precargadas 120 en un grupo de disparo 202a-202f, están conectadas eléctricamente con solo una línea de precarga 210a-210f. Así, las capacidades del nodo 126 de todas las células de disparo precargadas 120 en un grupo de disparo 202a-202f, son cargadas mediante el suministro de la correspondiente señal de precarga PRE1, PRE2 ... PRE6 a la correspondiente línea de precarga 210a-210f.

- 15 Las líneas de selección 212a-212f reciben las señales de selección SEL1, SEL2 ... SEL6 y proporcionan las señales de selección SEL1, SEL2 ... SEL6 a los correspondientes grupos de disparo 202a-202f. La línea de selección 212a esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG1 202a. La línea de selección 212b esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG2 202b y, así sucesivamente, hasta e incluyendo la línea de selección 212f que esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG6 202f. Cada una de las líneas de selección 212a-212f esta conectada eléctricamente con la puerta de todos los transistores de selección 130, en el grupo de disparo correspondiente 202a-202f y todas las células de disparo precargadas 120 en un grupo de disparo 202a-202f están conectadas eléctricamente con solo una línea de selección 212a-212f.

- 20 Las líneas de disparo 214a-214f reciben las señales de disparo o señales de energía FUEGO1, FUEGO2, ... FUEGO6 y proporcionan las señales de energía FUEGO1, FUEGO2, ... FUEGO6 a los correspondientes grupos de disparo 202a-202f. La línea de disparo 214a esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG1 202a. La línea de disparo 214b esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG2 202b y, así sucesivamente, hasta e incluyendo la línea de disparo 214f que esta conectada eléctricamente con todas las células de disparo precargadas 120 en FG6 202f. Cada una de las líneas de disparo 214a-214f está conectada eléctricamente con todas las resistencias de disparo 52 en el correspondiente grupo de disparo 202a- 202f y todas las células de disparo precargadas 120, en un grupo de disparo 202a- 202f, están conectadas eléctricamente con solo una línea de disparo 214a-214f. Las líneas de disparo 214a-214f están conectadas eléctricamente con un circuito externo de suministro, mediante los pads de interfaz apropiados (véase la

- 25

- 30

- 35

- 40

Figura 25). Todas las células de disparo precargadas 120, en la matriz 200, están conectadas eléctricamente con una línea de referencia 216 que esta unida a un voltaje de referencia, como tierra. Así, las células de disparo precargadas 120 en un subgrupo de filas de células de disparo precargadas 120, están conectadas eléctricamente con las mismas líneas de dirección 206a-206g, línea de precarga 210a-210f, línea de selección 212a-212f y línea de disparo 214a-214f.

En funcionamiento, en una forma de realización, los grupos de disparo 202a-202f son seleccionados para disparar en sucesión. FG1 202a es seleccionado antes que FG2 202b, el cual es seleccionado antes que FG3 y, así sucesivamente, hasta FG6 202f. Después de FG6 202f, el ciclo de grupo de disparo empieza de nuevo con FG1 202a. Sin embargo, pueden se utilizadas otras secuencias y selecciones no secuenciales.

Las señales de dirección ~A1, ~A2 ... ~A7 circulan hasta las direcciones de subgrupos de filas 13 antes de repetir una dirección del subgrupo de filas. Las señales de dirección ~A1, ~A2 ... ~A7 proporcionadas sobre las líneas de dirección 206a-206g, son fijadas a una dirección del subgrupo de filas durante cada ciclo, a través de los grupos de disparo 202a-202f. Las señales de dirección ~A1, ~A2 ... ~A7 seleccionan un subgrupo de filas en cada uno de los grupos de disparo 202a-202f para un ciclo, a través de los grupos de disparo 202a-202f. Para el siguiente ciclo, a través de los grupos de disparo 202a-202f, las señales de dirección ~A1, ~A2 ... ~A7 son cambiadas, para seleccionar otro subgrupo de filas en cada uno de los grupos de disparo 202a-202f. Esto continua hasta que las señales de dirección ~A1, ~A2 ... ~A7 seleccionan el último subgrupo de filas en los grupos de disparo 202a-202f.

Después del último subgrupo de filas, las señales de dirección ~A1, ~A2 ... ~A7 seleccionan el primer subgrupo de filas para empezar el ciclo de dirección otra vez.

En otro aspecto del funcionamiento, uno de los grupos de disparo 202a-202f es puesto en funcionamiento, mediante la aportación de una señal de precarga PRE1, PRE2 ... PRE6 sobre la línea de precarga 210a-210f de un grupo de disparo 202a-202f. La señal de precarga PRE1, PRE2 ... PRE6 define un intervalo de tiempo de precarga o periodo de tiempo durante el cual la capacidad del nodo 126 en cada interruptor de accionamiento 172 en el grupo de disparo uno 202a-202f, es cargada hasta un nivel de voltaje alto, para precargar el grupo de disparo uno 202a-202f.

Las señales de dirección ~A1, ~A2 ... ~A7 son proporcionadas sobre las líneas de dirección 206a-206g para dirigir el subgrupo de filas uno, en cada uno de los grupos de disparo 202a-202f, incluyendo el subgrupo de filas uno en el grupo de disparo precargado 202a-202f. Las señales de datos ~D1, ~D2 ... ~D8 son proporcionadas sobre las líneas de datos 208a-208h para proporcionar datos a todos los grupos de disparo 202a-202f, incluyendo la dirección del subgrupo de filas en el grupo de disparo precargado 202a-202f.

A continuación, una señal de selección SEL1, SEL2 ... SEL6 es proporcionada sobre la línea de selección 212a-212f del grupo de disparo precargado 202a-202f, para seleccionar el grupo de disparo precargado 202a-202f. La señal de selección SEL1, SEL2 ... SEL6 define un intervalo de tiempo de descarga, para descargar la capacidad del nodo 126 en cada uno de los interruptores de accionamiento 172 en una célula de disparo precargada 120, que, o bien no esta en el subgrupo de filas dirigido en el grupo de disparo seleccionado 202a-202f o esta dirigida en el grupo de disparo seleccionado 202a-202f y que recibe una señal de datos de nivel alto ~D2, ~D2 ... ~D8. La capacidad del nodo 126 no descarga en las células de disparo precargadas 120, que están dirigidas en el grupo de disparo seleccionado 202a-202f y que reciben una señal de datos de nivel bajo ~D1, ~D2 ... ~D8. Un nivel de voltaje alto en la capacidad del nodo 126 enciende el interruptor de accionamiento 172 (conduciendo).

Después de que los interruptores de accionamiento en el grupo de disparo seleccionado 202a-202f, son fijados para conducir o no conducir, se proporciona una pulsación de energía o pulsación de voltaje sobre la línea de disparo 214a-214f del grupo de disparo seleccionado 202a-202f. Las células de disparo precargadas 120, que tienen interruptores de accionamiento conductores 172, conducen la corriente a través de la resistencia de disparo 52, para calentar tinta y expulsar o eyectar tinta desde correspondiente generador de gotas 60.

Con los grupos de disparo 202a-202f funcionando en sucesión, la señal de selección SEL1, SEL2 ... SEL6 para un grupo de disparo 202a-202f, es utilizada como señal de precarga PRE1, PRE2 ... PRE6 para el siguiente grupo de disparo 202a-202f. La señal de precarga PRE1, PRE2 ... PRE6 para un grupo de disparo 202a-202f, precede a la señal de selección SEL1, SEL2 ... SEL6 y la señal de energía FUEGO1, FUEGO2 ... FUEGO6 para el grupo de disparo uno 202a-202f. Después de la señal de precarga PRE1, PRE2 ... PRE6, las señales de datos ~D1, ~D2 ... ~D8 se multiplican en el tiempo y se almacenan en el subgrupo de filas dirigido de uno de los grupos de disparo 202a- 202f, mediante la señal de selección SEL1, SEL2 ... SEL6. La señal de selección SEL1, SEL2 ... SEL6 para el grupo de disparo seleccionado 202a- 202f, es también la señal de precarga PRE1, PRE2 ... PRE6 para el siguiente grupo de disparo 202a-202f. Después de que la señal de selección SEL1, SEL2 ... SEL6 para el grupo de disparo seleccionado 202a- 202f es completa, se proporciona la señal de selección SEL1, SEL2 ... SEL6 para el siguiente grupo de disparo 202a- 202f. Las células de disparo precargadas 120 en el grupo de disparo seleccionado, disparan o calientan tinta basadas en la señal de datos almacenada ~D2, -D2 ... -D8, como las señales de energía FUEGO1, FUEGO2, ..., FUEGO6, incluyendo una pulsación de energía, que es proporcionada al grupo de disparo seleccionado 202a-202f.

- La Figura 8, es un diagrama de temporización que ilustra el funcionamiento de una forma de realización de la matriz de células de disparo 200. Los grupos de disparo 202a-202f son seleccionados en sucesión para energizar células de disparo precargadas 120, basados en las señales de datos ~D1, ~D2 ... ~D8, indicadas en 300. Las señales de datos ~D1, ~D2 ... ~D8 en 300, son cambiadas dependiendo de las boquillas que deben expulsar o eyectar fluido, indicadas en 302, para cada combinación de dirección del subgrupo de filas y grupo de disparo 202a-202f. Las señales de dirección ~A1, ~A2 ... ~A7 en 304, son proporcionadas a las líneas de dirección 206a-206g, para dirigir un subgrupo de filas de cada uno de los grupos de disparo 202a- 202f. Las señales de dirección ~A1, ~A2 ... ~A7 en 304, son fijadas en una dirección, indicada en 306, para un ciclo, a través de los grupos de disparo 202a- 202f. Despues de que el ciclo se haya completado, las señales de dirección ~A1, ~A2 ... ~A7 en 304, son cambiadas en 308, para dirigir un subgrupo de filas diferente de cada uno de los grupos de disparo 202a-202f. Las señales de dirección ~A1, ~A2 ... ~A7 en 304, se incrementan a través de los subgrupos de filas, para dirigir los subgrupos de filas en orden secuencial, desde uno hasta 13 y hacia atrás hasta uno. En otras formas de realización, las señales de dirección ~A1, ~A2 ... ~A7 en 304, pueden ser fijadas para dirigir los subgrupos de filas en cualquier orden adecuado.

- 15 Durante un ciclo, a través de los grupos de disparo 202a-202f, la línea de selección 212f conectada con FG6 202f y la línea de precarga 210a conectada con FG1 202a, reciben la señal SEL6/PRE1, 309, incluyendo la pulsación de señal SEL6/PRE1 310. En una forma de realización, la línea de selección 212f y la línea de precarga 210a están conectadas juntas eléctricamente, para recibir la misma señal. En otra forma de realización, la línea de selección 212f y la línea de precarga 210a no están conectadas juntas eléctricamente, pero reciben señales similares.

- 20 La pulsación de señal SEL6/PRE1 en 310, sobre la línea de precarga 210a, precarga todas las células de disparo 120 en FG1 202a. La capacidad del nodo 126 para cada una de las células de disparo precargadas 120 en FG1 202a, es cargada en un alto nivel de voltaje. La capacidad del nodo 126 para las células de disparo precargadas 120 en un subgrupo de filas SG1-K, indicado en 311, son precargadas a un nivel de voltaje alto en 312. La dirección del subgrupo de filas en 306, selecciona el subgrupo SG1-K y una señal de datos fijada en 314, es proporcionada a los transistores de datos 136, en todas las células de disparo precargadas 120 de todos los grupos de disparo 202a-202f, incluyendo la dirección seleccionada del subgrupo de filas SG1-K.

- 25 30 La línea de selección 212a para FG1 202a y la línea de precarga 210b para FG2 202b, reciben la señal SEL1/PRE2 315, incluyendo la pulsación de la señal SEL1/PRE2 316. La pulsación de la señal SEL1/PRE2 316, sobre la línea de selección 212a, enciende el transistor de selección 130 en cada una de las células de disparo precargadas 120 en FG1 202a. La capacidad del nodo 126 es descargada en todas las células de disparo precargadas 120 en FG1 202a, que no están en la dirección seleccionada del subgrupo de filas SG1-K. En la dirección seleccionada del subgrupo de filas SG1-K, los datos en 314 son almacenados, indicados en 318, en la capacidad del nodo 126 de los interruptores de accionamiento 172 en el subgrupo de filas SG1-K, para bien encender el interruptor de accionamiento (conduciendo) o apagarlo (no conduciendo).

- 35 40 La pulsación de señal SEL1/PRE2, en 316 sobre la línea de precarga 210b precarga todas las células de disparo 120 en FG2 202b. La capacidad del nodo 126 para cada una de las células de disparo precargadas 120 en FG2 202b, es cargada a un nivel de voltaje alto. Las capacidades de nodo 126 para las células de disparo precargadas 120 en un subgrupo de filas SG2-K, indicado en 319, son precargadas hasta un nivel de voltaje alto en 320. La dirección del subgrupo de filas en 306 selecciona el subgrupo SG2-K y una señal de datos fijada en 328 es proporcionada a los transistores de datos 136 en todas las células de disparo precargadas 120 de todos los grupos de disparo 202a-202f, incluyendo la dirección del subgrupo de filas seleccionado SG2-K.

- 45 50 La línea de disparo 214a recibe la señal de energía FUEGO1, indicada en 323, incluyendo una pulsación de energía en 322, para energizar las resistencias de disparo 52 de las células de disparo precargadas 120, que tienen interruptores de accionamiento conductores 172 en FG1 202a. La pulsación de energía FUEGO1 322 va alta, mientras la pulsación de señal SEL1/PRE2 316 es alta y mientras la capacidad del nodo 126 en los interruptores de accionamientos no conductores 172, han sido activamente arrastradas bajas, indicadas en la señal de energía FUEGO1 323 en 324. Desplazando la pulsación de energía 322 alta mientras las capacidades de nodo 126 están activamente arrastradas bajas, se evita que las capacidades de nodo 126 se carguen de forma inadvertida a través del interruptor de accionamiento 172, al ir alta la pulsación de energía 322. La señal SEL1/PRE2 315 va baja y la pulsación de energía 322 es proporcionada a FG1 202a por un tiempo predeterminado, para calentar tinta y expulsar o eyectar tinta a través de las boquillas 34 que se corresponden con las células de disparo precargadas conductoras 120.

- 55 60 La línea de selección 212b para FG2 202b y la línea de precarga 210c para FG3 202c, reciben la señal SEL2/PRE3 325, incluyendo la pulsación de señal SEL2/PRE3 326. Despues la pulsación de señal SEL1/PRE2 316 va baja y mientras la pulsación de energía 322 es alta, la pulsación de señal SEL2/PRE3 326, sobre la línea se selección 212b, enciende el transistor de selección 130 en cada una de las células de disparo precargadas 120 en FG2 202b. La capacidad del nodo 126 es descargada en todas las células de disparo precargadas 120 en FG2 202b, que no están en la dirección del subgrupo de filas seleccionado SG2-K. La señal de datos fijada 328 para el subgrupo SG2-K, es almacenada en las células de disparo precargadas 120 del subgrupo SG2-K, indicada en 330, para, o bien

encender los interruptores de accionamiento 172 (conduciendo) o apagarlos (no conduciendo). La pulsación de señal SEL2/PRE3 sobre la línea de precarga 210c, precarga todas las células de disparo precargadas 120 en FG3 202c.

- 5 La línea de disparo 214b recibe la señal de energía FUEGO2, indicada en 331, incluyendo la pulsación de energía 332, para energizar las resistencias de disparo 52 en las células de disparo precargadas 120 de FG2 202b, que tienen interruptores de accionamiento conductores 172. La pulsación de energía FUEGO2 332 va alta mientras la pulsación de señal SEL2/PRE3 326 es alta, indicada en 334. La pulsación de señal SEL2/PRE3 326 va baja y la pulsación de energía FUEGO2 332 permanece alta, para calentar y expulsar o eyectar tinta desde el correspondiente generador de gotas 60.

Después la pulsación de señal SEL2/PRE3 326 va baja y mientras la pulsación de energía 332 es alta, una señal SEL3/PRE4 es proporcionada para seleccionar FG3 202c y precargar FG4 202d. El proceso de precarga, selección y suministro de una señal de energía, que incluye una pulsación de energía, continua hasta e incluyendo FG6 202f.

- 15 La pulsación de señal SEL5/PRE6 sobre la línea de precarga 210f, precarga todas las células de disparo 120 en FG6 202f. La capacidad del nodo 126 de cada una de las células de disparo precargadas 120 en FG6 202f, es cargada a un alto nivel de voltaje. Las capacidades del nodo 126 para las células de disparo precargadas 120 en el subgrupo de filas uno SG6-K, indicado en 339, son precargadas a un nivel de voltaje alto en 341. La dirección del subgrupo de filas en 306 selecciona el subgrupo SG6-K y la señal de datos fijada 338 es proporcionada a los transistores de datos 136, en todas las células de disparo precargadas 120 de todos los grupos de disparo 202a-202f, incluyendo la dirección del subgrupo de filas seleccionado SG6-K.

- 20 La línea de selección 212f de FG6 202f y la línea de precarga 210a para FG1 202a, reciben una segunda pulsación de señal SEL6/PRE1 en 336. La segunda pulsación de señal SEL6/PRE1 sobre la línea de selección 212f, enciende el transistor de selección 130 en cada una de las células de disparo precargadas 120 en FG6 202f. La capacidad del nodo 126 es descargada, en todas las células de disparo precargadas 120 en FG6 202f, que no están en la dirección del subgrupo de filas seleccionado SG6-K. En la dirección del subgrupo de filas seleccionado SG6-K, los datos 338 son almacenados en 340, en la capacidad del nodo 126 de cada interruptor de accionamiento 172, para bien encender o apagar el interruptor de accionamiento.

- 25 La señal SEL6/PRE1 sobre la línea de precarga 210a, precarga las capacidades de nodo 126 en todas las células de disparo 120 en FG1 202a, incluyendo las células de disparo 120 en el subgrupo de filas SG1-K, indicado en 342, a un nivel de voltaje alto. Las células de disparo 120 en FG1 202a están precargadas mientras las señales de dirección ~A1, ~A2 ... ~A7 304 seleccionan los subgrupos de filas SG1-K, SG2- K y en adelante, hasta el subgrupo de filas SG6-K.

- 30 La línea de disparo 214f recibe la señal de energía FUEGO6, indicada en 343, incluyendo una pulsación de energía en 344 para energizar las resistencias de disparo 52 en las células de disparo precargadas 120, que tienen los interruptores de accionamiento conductores 172 en FG6 202f. La pulsación de energía 344 va alta mientras la pulsación de señal SEL6/PRE1 336 es alta y las capacidades de nodo 126 en los interruptores de accionamiento no conductores 172 han sido activamente arrastrados bajos, indicados en 346. Desplazando la pulsación de energía 344 alta, mientras las capacidades de nodo 126 son activamente arrastradas bajas, evita que las capacidades de nodo 126 sean inadvertidamente cargadas a través del interruptor de accionamiento 172 al ir alta la pulsación de energía 344. La pulsación de señal SEL6/PRE1, 336 va baja y la pulsación de energía 344 es mantenida alta por un tiempo predeterminado, para calendar tinta y expulsar o eyectar tinta a través de las boquillas 34 que se corresponden con las células de disparo precargadas conductoras 120.

- 35 Despues la pulsación de señal SEL6/PRE1 336 va baja y mientras la pulsación de energía 344 es alta, las señales de dirección ~A1, ~A2 ... ~A7 304 son cambiadas en 308 para seleccionar otro set de subgrupos SG1-K+1, SG2-K+1 y, así sucesivamente, hasta SG6-K+1. La línea de selección 212a para FG1 202a y la línea de precarga 210b para FG2 202b, reciben una pulsación de señal SEL1/PRE2, indicada en 348. La pulsación de señal SEL1/PRE2 348, sobre la línea de selección 212a, enciende el transistor de selección 130 en cada una de las células de disparo precargadas 120 en FG1 202a. La capacidad del nodo 126 es descargada en todas las células de disparo precargadas 120 en FG1 202a que no están en la dirección del subgrupo seleccionado SG1-K+1. La señal de datos fijada 350 para el subgrupo de filas SG1-K+1, es almacenada en las células de disparo precargadas 120 del subgrupo SG1-K+1, para bien encender o apagar los interruptores de accionamiento 172. La pulsación de señal SEL1/PRE2 348, sobre la línea de precarga 210b precarga todas las células de disparo 120 en FG2 202b.

- 40 La línea de disparo 214a recibe la pulsación de energía 352, para energizar las resistencias de disparo 52 y las células de disparo precargadas 120 de FG1 202a, que tienen interruptores de accionamiento conductores 172. La pulsación de energía 352 va alta mientras la pulsación de señal SEL1/PRE2 en 348 es alta. La pulsación de señal SEL1/PRE2 348 va baja y la pulsación de energía 352 permanece alta, para calentar y expulsar o eyectar tinta desde los correspondientes generadores de gotas 60. El proceso continua hasta que la impresión está completada.

La Figura 9, es un diagrama que ilustra una forma de realización de un generador de dirección 400 en la base de un cabezal de impresión 40. El generador de dirección 400 incluye un registro de desplazamiento 402, un circuito de dirección 404 y una matriz lógica 406. El registro de desplazamiento 402 está conectado eléctricamente con el circuito de dirección 404, a través de las líneas de control de dirección 408. También, el registro de transmisión 402 está conectado eléctricamente con la matriz lógica 406, a través de las líneas de salida del registro de desplazamiento 410a-410m.

En las formas de realización descritas abajo, el generador de dirección 400 proporciona señales de dirección a las células de disparo 120. En una forma de realización, el generador de dirección 400 recibe señales externas, véase la Figura 25, incluyendo una señal de control CSYNC y seis señales de temporización T1-T6 y, en respuesta, proporciona siete señales de dirección ~A1, ~A2, ... ~A7. Las señales de dirección ~A1, ~A2, ... ~A7 están activas cuando las mismas están en el nivel de voltaje bajo, como se indica por las tildes que preceden a cada nombre de señal. En una forma de realización, las señales de temporización T1-T6 son proporcionadas sobre las líneas de selección (por ejemplo, las líneas de selección 212a-212f mostradas en la Figura 7). El generador de dirección 400 es una forma de realización de un circuito de control configurado para responder a una señal de control (por ejemplo, CSYNC), para iniciar una secuencia (por ejemplo, una secuencia de direcciones ~A1, ~A2 ... ~A7, en orden hacia delante o reverso), para habilitar la activación de las células de disparo 120.

El generador de dirección 400 incluye redes de resistencia de segmentación 412, 414 y 416, que reciben las señales de temporización T2, T4 y T6. La red de resistencia de segmentación 412 recibe la señal de temporización T2 a través de la línea de señal de temporización 418 y divide el nivel de voltaje de la señal de temporización T2, para proporcionar una señal de temporización de nivel de voltaje reducido T2 sobre la línea de señal de primera evaluación 420. La red de resistencia de segmentación 414 recibe la señal de temporización T4, a través de la línea de señal de temporización 422 y divide el nivel de voltaje de la señal de temporización T4, para proporcionar una la señal de temporización de nivel de voltaje reducido T4, sobre la línea de señal de segunda evaluación 424. La red de resistencia de segmentación 416 recibe la señal de temporización T6, a través de la línea de señal de temporización 426 y divide el nivel de voltaje de la señal de temporización T6, para proporcionar una señal de temporización de nivel de voltaje reducido T6 sobre la línea de señal de tercera evaluación 428.

El registro de desplazamiento 402 recibe la señal de control CSYNC, a través de la línea de señal de control 430 y las señales de dirección, a través de las líneas de señal de dirección 408. También, el registro de desplazamiento 402 recibe la señal de temporización T1, a través de la línea de señal de temporización 432, como primera señal de precarga PRE1. La señal de temporización de nivel de voltaje reducido T2 es recibida a través de la línea de señal de primera evaluación 420, como primera señal de evaluación EVAL1. La señal de temporización T3 es recibida a través de la línea de señal de temporización 434, como segunda señal de precarga PRE2 y la señal de temporización de nivel reducido de voltaje T4 es recibida a través de la línea de señal de segunda evaluación EVAL2. El registro de desplazamiento 402 proporciona las señales de salida del registro de desplazamiento SO1-SO13 en las líneas de salida del registro de desplazamiento 410a-410m.

El registro de desplazamiento 402 incluye trece células del registro de desplazamiento 403a-403m que proporcionan las trece señales de salida del registro de desplazamiento SO1-SO13. Cada célula del registro de desplazamiento 403a-403m proporciona una de las señales de salida del registro de desplazamiento SO1-SO13. Las trece células del registro de desplazamiento 403a-403m están conectadas eléctricamente en serie, para proporcionar el desplazamiento en la dirección hacia delante y la dirección inversa. En las otras formas de realización, el registro de desplazamiento 402 puede incluir cualquier número adecuado de células del registro de desplazamiento 403, para proporcionar cualquier número adecuado de señales de salida del registro de desplazamiento, para proporcionar cualquier número deseado de señales de dirección.

La célula del registro de desplazamiento 403a proporciona la señal de salida del registro de desplazamiento SO1, sobre la línea de salida del registro de desplazamiento 410a. La célula del registro de desplazamiento 403b proporciona la señal de salida del registro de desplazamiento SO2 sobre la línea de salida del registro de desplazamiento 410b. La célula del registro de desplazamiento 403c proporciona la señal de salida del registro de desplazamiento SO3 sobre la línea de salida del registro de desplazamiento 410c. La célula del registro de desplazamiento 403d proporciona la señal de salida del registro de desplazamiento SO4 sobre la línea de salida del registro de desplazamiento 410d. La célula del registro de desplazamiento 403e proporciona la señal de salida del registro de desplazamiento SO5 sobre la línea de salida del registro de desplazamiento 410e. La célula del registro de desplazamiento 403f proporciona la señal de salida del registro de desplazamiento SO6 sobre la línea de salida del registro de desplazamiento 410f. La célula del registro de desplazamiento 403g proporciona la señal de salida del registro de desplazamiento SO7 sobre la línea de salida del registro de desplazamiento 410g. La célula del registro de desplazamiento 403h proporciona la señal de salida del registro de desplazamiento SO8 sobre la línea de salida del registro de desplazamiento 410h. La célula del registro de desplazamiento 403i proporciona la señal de salida del registro de desplazamiento SO9 sobre la línea de salida del registro de desplazamiento 410i. La célula del registro de desplazamiento 403j proporciona la señal de salida del registro de desplazamiento SO10 sobre la línea de salida del registro de desplazamiento 410j. La célula del registro de desplazamiento 403k proporciona la señal de salida del registro de desplazamiento SO11 sobre la línea de salida del registro de desplazamiento 410k. La célula

del registro de desplazamiento 403l proporciona la señal de salida del registro de desplazamiento SO12 sobre la línea de salida del registro de desplazamiento 410l. La célula del registro de desplazamiento 403m proporciona la señal de salida del registro de desplazamiento SO13 sobre la línea de salida del registro de desplazamiento 410m.

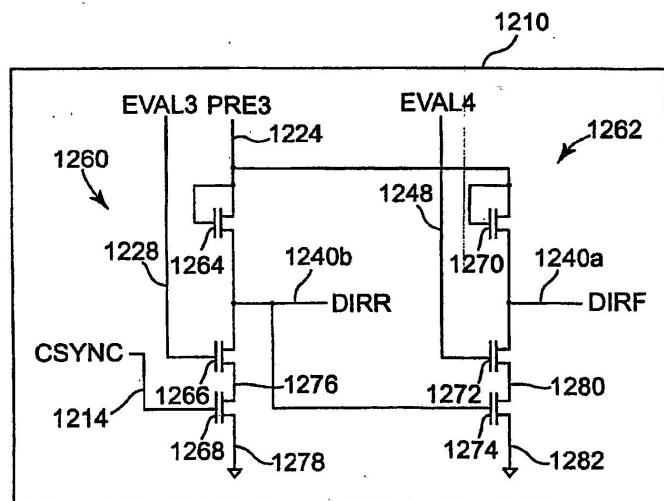

- 5 El circuito de dirección 404 recibe la señal de control CSYNC sobre la línea de señal de control 430. La señal de temporización T3 es recibida en la línea de señal de temporización 434, como cuarta señal de precarga PRE4. La señal de temporización de nivel de voltaje reducido T4 es recibida en la línea de señal de evaluación 424, como cuarta señal de evaluación EVAL4. La señal de temporización T5 es recibida en la línea de señal de temporización 436, como tercera señal de precarga PRE3 y la señal de temporización de nivel de voltaje reducido T6 es recibida en la línea de señal de evaluación 428, como tercera señal de evaluación EVAL3. El circuito de dirección 404 proporciona señales de dirección al registro de desplazamiento 402, a través de las líneas de señal de dirección 408.