OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

①Número de publicación: 2 383 614

51 Int. CI.:

H03K 17/0814 (2006.01) H03K 17/687 (2006.01) H03K 17/10 (2006.01) H03K 19/0175 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- 96 Número de solicitud europea: 07013423 .4

- 96 Fecha de presentación: **10.07.2007**

- 97 Número de publicación de la solicitud: 1887698

97 Fecha de publicación de la solicitud: 13.02.2008

- 54 Título: Desviador de nivel para un conmutador de accionamiento para componentes semiconductores de potencia

- 30 Prioridad: 10.08.2006 DE 102006037336

73 Titular/es:

SEMIKRON ELEKTRONIK GMBH & CO. KG PATENTABTEILUNG SIGMUNDSTRASSE 200 90431 Nürnberg , DE

- Fecha de publicación de la mención BOPI: 22.06.2012

- 72 Inventor/es:

Herzer, Reinhard; Rossberg, Matthias y Vogler, Bastian

- Fecha de la publicación del folleto de la patente: 22.06.2012

- (74) Agente/Representante:

Isern Jara, Jorge

ES 2 383 614 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

Desviador de nivel para un conmutador de accionamiento para componentes semiconductores de potencia

La invención describe un desviador de nivel, preferiblemente para un circuito de control el cual se requiere en sistemas electrónicos de potencia a fin de accionar conmutadores de semiconductor de potencia los cuales están instalados como conmutadores individuales o en un circuito en puente. Los circuitos en puente de este tipo son conocidos en la forma de circuito de una fase, circuitos en puente de dos o tres fases, en el que el circuito de una fase, un denominado medio puente representa un bloque de construcción básica de los circuitos electrónicos de potencia. En un circuito de medio puente, dos conmutadores de potencia, un primero denominado conmutador TOP y un segundo denominado conmutador BOT están conectados en serie.

Un medio puente de este tipo típicamente comprende una conexión a un circuito de vinculación de corriente continua intermedio. La salida, típicamente el terminal de tensión de corriente alterna del medio puente, generalmente está conectada a la carga. El circuito de control típicamente consiste en una pluralidad de subcircuitos o bloques funcionales. La señal de control es procesada en un primer subcircuito, la lógica de control, y alimentada a través de componentes adicionales a los circuitos excitadores y finalmente a la entrada de control del conmutador de potencia respectivo.

15

35

55

60

20 Tensiones del circuito intermedio más altas, por ejemplo superiores a 100 V, la lógica de control generalmente está aislada por potencial de los circuitos excitadores, puesto que los conmutadores de potencia asociados están a potenciales diferentes y por lo tanto es obligatorio el aislamiento a base de la tensión. Este aislamiento se aplica por lo menos al conmutador TOP, pero también se implanta a niveles de potencia más altos para el conmutador BOT, debido a una posible ruptura del potencial de tierra durante la conmutación. Un aislamiento se puede implantar por 25 ejemplo por medio de transformadores de impulso (separación galvánica), por medio de acopladores ópticos o fibras ópticas o bien utilizando tecnología de circuitos integrados en un circuito integrado de alta tensión (HVIC). La última variante, debido a diversas ventajas, tales como dimensiones pequeñas, bajo precio y una larga vida de servicio, se utiliza con una frecuencia creciente. Al mismo tiempo los HVIC ofrecen la posibilidad de incorporar un componente de alta tensión con una tensión de ruptura mayor o igual a la tensión del circuito intermedio, la cual puede ser 30 utilizada en circuitos para conversiones del nivel de señal, en los denominados desviadores de nivel. Típicamente para esto se utiliza un MOSFET (transistor de efecto de campo semiconductor de óxido de metal) de alta tensión lateral.

La sección del circuito presentada es parte del circuito de excitación y preferiblemente se implanta como una instalación de circuito integrado. Sirve para transmitir una señal desde una sección del circuito con un potencial de referencia bajo (lado bajo) a una sección del circuito la cual a veces tiene un potencial de referencia más alto (lado alto), o viceversa. Una instalación de este tipo se requiere para el accionamiento integrado y aislado de potencial de los semiconductores de potencia y es conocido como un desviador de nivel.

Dos tecnologías de aislamiento fundamentales son conocidas para utilizarlas en los HVIC. En primer lugar las tecnologías SOI (silicio en aislante) y en segundo lugar las tecnologías PN aisladas (aislamiento de unión). La tecnología SOI ofrece un aislamiento dieléctrico de los componentes y de grupos de componentes, pero únicamente está disponible actualmente hasta una resistencia a la ruptura de la tensión de 800 V. Las obleas de sustrato SOI son marcadamente más caras que los sustratos normales, sin embargo los costes se compensan por las simplificaciones en el procesamiento que resulta a partir del aislamiento dieléctrico. En el caso de tecnologías PN aisladas la tensión inversa es transportada por una unión PN de polarización inversa. Esta técnica está actualmente disponible hasta 1200 V. Es muy complicada de producir sin embargo y por lo tanto es muy cara. Existen también problemas técnicos, por ejemplo con las corrientes de pérdida y los efectos de cierre por ejemplo a temperaturas más altas, por ejemplo por encima de las temperaturas de funcionamiento de 125 °C y debido a la ruptura del potencial de tierra durante los procesos dinámicos rápidos.

Como se revela en el documento DE 10152930 A1, una señal también puede ser convertida de una manera paso a paso por medio de una pluralidad de n desviadores de nivel conocidos idénticos conectados en cascada, en donde en este caso y en lo que sigue, n es un número entero mayor o igual a dos. La tensión de ruptura de un componente de alta tensión individual como parte del desviador de nivel necesita por lo tanto sólo añadir la n-sima parte de la tensión total (tensión del circuito intermedio más la sobretensión dinámica máxima durante la conmutación), suponiendo que la tensión total se distribuye uniformemente sobre todos los n desviadores de nivel. Del mismo modo la gama de desviación del nivel que se puede utilizar se puede incrementar si se incrementa el número de pasos. Cada desviador de nivel individual puede tener un circuito de transmisión de señal conectado aguas abajo. Desde un circuito del divisor de tensión que funciona de forma de resistividad el cual está acoplado al potencial alterno en la salida del medio puente de potencia, los potenciales intermedios para los terminales negativos de la tensión de suministro son derivados para el circuito de transmisión de la señal primero hasta el (n-1)-simo.

Puesto que el potencial en la salida varía cíclicamente entre 0 V y una tensión previamente definida, por ejemplo 600 V, el intervalo entre cada dos potenciales intermedios cambia en una gama de casi 0 V hasta 600 V/n. Esta

generación uniforme de potenciales intermedios, vinculados a las fases de conmutación del medio puente de potencia, asegura que la tensión de ruptura del componente de alta tensión no puede ser excedido en cualquiera de los n desviadores de nivel.

La formación en cascada de los n desviadores de nivel revelada en el documento DE 10152930 A1, sin embargo, tiene la desventaja de que el número de trayectorias de corriente transversales, con una trayectoria de corriente transversal por desviador de nivel, se incrementa en n - veces comparado con un desviador de nivel individual. El consumo de corriente por lo tanto incrementa, y de ese modo también la pérdida de potencia de la instalación de desviador de nivel, por el factor n. Una corriente transversal estática adicional por lo tanto fluye a través de un circuito divisor de tensión el cual genera los n-1 potenciales intermedios para los desviadores de nivel, lo cual adicionalmente incrementa la pérdida de potencia.

El suministro de tensión para cada uno de los circuitos de transmisión de señal se efectúa a través de un suministro de tensión de arranque según la técnica anterior, lo cual significa que un condensador está conectado entre la tensión de funcionamiento y el terminal de tierra de cada circuito de transmisión de señal y es cargado cíclicamente, según la fase de conmutación del medio puente, por una fuente de corriente continua. Puesto que el circuito de transmisión de señal está suministrado separadamente, los requisitos de circuitos y espacio para el suministro incrementan en n- veces.

15

45

50

55

60

65

Además, a partir del documento DE 10152930A1 se conocen diferentes formas de realización para la conversión del nivel de la señal en múltiples etapas. Por lo tanto, por ejemplo, una señal la cual se obtiene a partir de un circuito de medición para la detección de un estado de funcionamiento del conmutador TOP en el lado alto, puede ser transmitida a través de una pluralidad de desviadores de nivel hasta un circuito de procesamiento de señal del lado bajo y suministrada a un micro control. Como componente de alta tensión para un desviador de nivel correspondiente, se puede utilizar un MOSFET de alta tensión de canal P. Por medio de esta señal de detección el micro control puede supervisar el estado de funcionamiento del conmutador TOP. Las desventajas descritas antes en este documento también se aplican a esta variante de la misma manera.

El artículo de M. Vander Kooi y otros "MOS se desplaza hacia aplicaciones de potencia más elevada" (ELECTRONICS, volumen 49, número 13, 24 de junio de 1976, páginas 98 - 103, XP 002531713) revela un MOSFET de potencia integrado dentro de un circuito divisor de tensión, que tiene un circuito en serie de transistores de alta tensión con condensadores conectados en paralelo con un punto nodo intermedio el cual está conectado a un transistor y el cual regula una tensión de salida entre los potenciales de referencia de +15 V y +100 V.

El artículo de B. Serneels y otros: "7.8 - Excitador de salida de alta tensión en una tecnología CMOS normal 2.5 0.25/spl mu/m" (15 de febrero de 2004, IEEE IN-TERNATIONAL SOLID-STATE CIRCUITS CONFE-RENCE 2004; DIGEST OF TECHNICAL PAPERS. IEEE, PISCATAWAY, NJ, USA, Páginas 146 - 155, XP010722195; ISBN: 978-0-7803-8267-1) revela un excitador de salida de alta tensión para tecnología CMOS, el cual también comprende un circuito en serie de transistores de alta tensión en paralelo con una cadena en serie de condensadores los cuales tienen un nodo que está conectado a la entrada de control de un transistor de alta tensión.

El problema al que se dirige la invención es extender un desviador de nivel, por ejemplo para circuitos de control de componentes de semiconductor de potencia, preferiblemente en forma de por lo menos un circuito integrado, de tal modo que el consumo de potencia y la complejidad del circuito se reduzcan comparado con la técnica anterior.

El problema se resuelve según la invención mediante las medidas de las características de la reivindicación 1. Formas de realización preferidas se describen en las reivindicaciones subordinadas.

La idea inventiva se basa en un circuito de control que tiene un desviador de nivel para la transmisión unidireccional de una señal desde una primera sección del circuito a un primer potencial hasta una segunda sección del circuito a un segundo potencial. Para este propósito el circuito de control comprende un desviador de nivel, realizado como un circuito en serie de una pluralidad de transistores, en el que la entrada del desviador de nivel está conectada a la entrada de control del primer transistor del circuito en serie. Este primer transistor es un transistor de conmutación o un transistor de alta tensión, mientras todos los otros transistores son transistores de alta tensión.

Además el desviador de nivel comprende un circuito divisor de tensión capacitiva conectado en paralelo con los transistores de alta tensión, en el que este divisor de tensión capacitiva está conectado entre un potencial de referencia del lado bajo y un potencial de referencia del lado alto. El desviador de nivel también comprende nodos entre los condensadores individuales, los cuales están conectados a los terminales de control de los transistores de alta tensión asociados.

Una ventaja de la topología según la invención es el hecho de que la utilización de n transistores de alta tensión permite que se obtenga n veces la capacidad de bloqueo de un transistor de alta tensión individual. Al mismo tiempo el circuito según la invención, comparado con el circuito descrito según la técnica anterior, tiene sólo una y no n trayectorias de corriente transversal. Además, el circuito según la invención no contiene circuitos de procesamiento de señal en potenciales intermedios, de modo que tampoco se requieren medios costosos para el suministro de

potencia a estos circuitos.

5

15

25

30

35

40

45

50

55

60

65

Por lo consiguiente, tanto el consumo de potencia como la complejidad del circuito se pueden reducir comparados con la técnica anterior. Esto resulta en requisitos de espacio menor y por lo tanto costes menores.

Diseños particularmente preferidos del desviador de nivel se indican en la deserción respectiva de las formas de realización ejemplares. La solución inventiva también se explica con detalle adicional sobre la base de estas formas de realización ejemplares de las figuras 1 a 5.

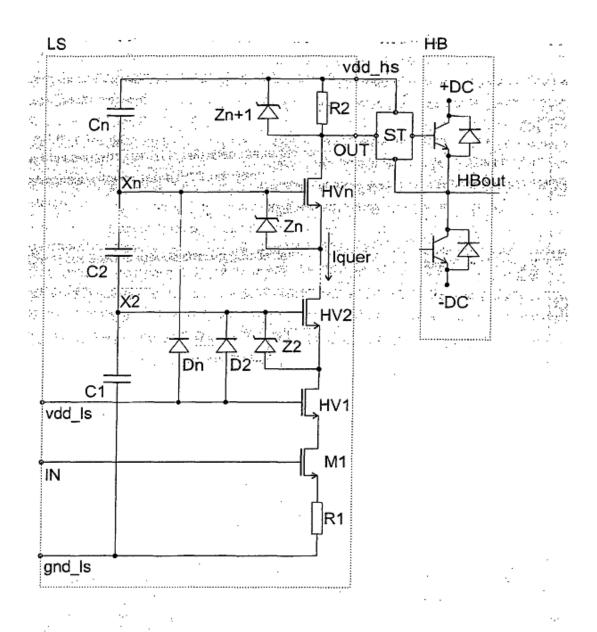

10 La figura 1 muestra un primer desviador de nivel según la invención en dos formas de realización.

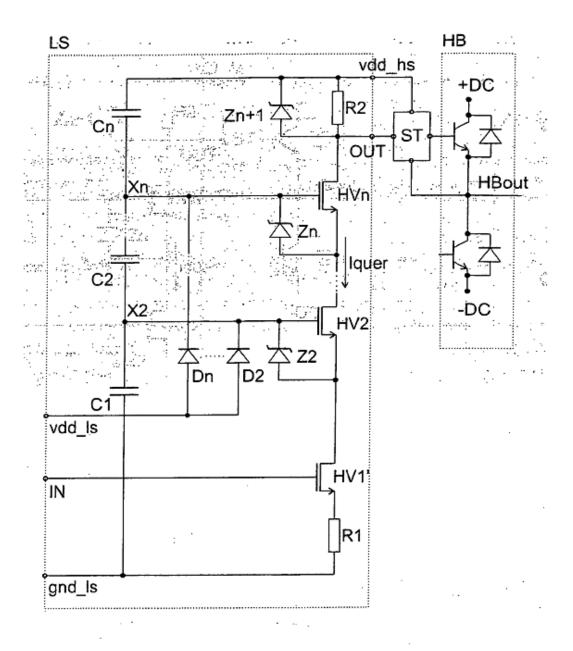

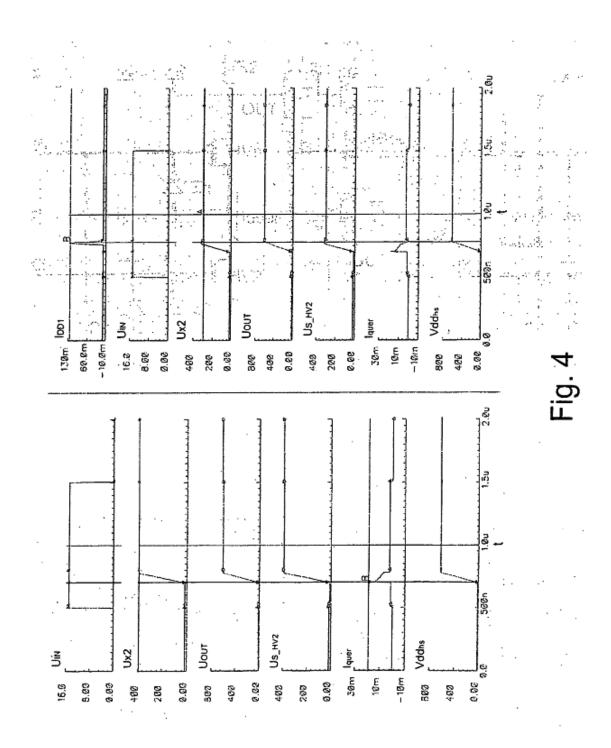

La figura 2 muestra los resultados de la simulación para un desviador de nivel según la figura 1a.

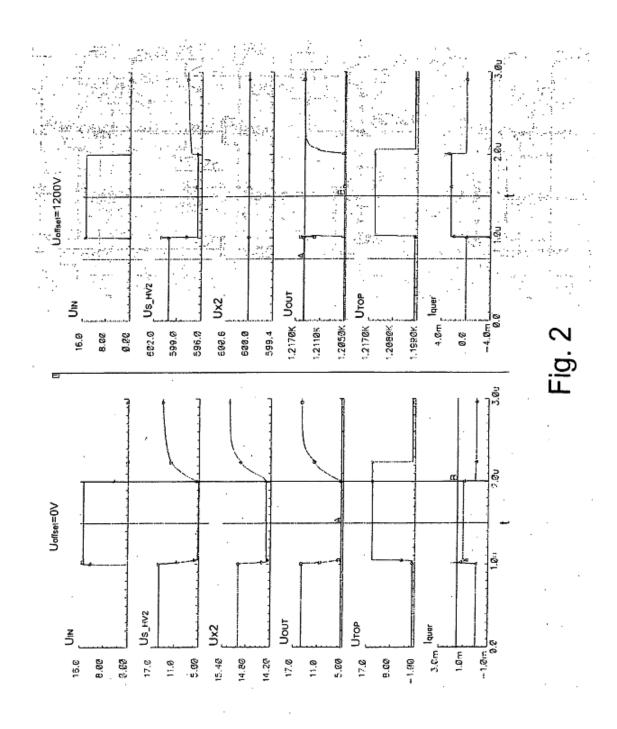

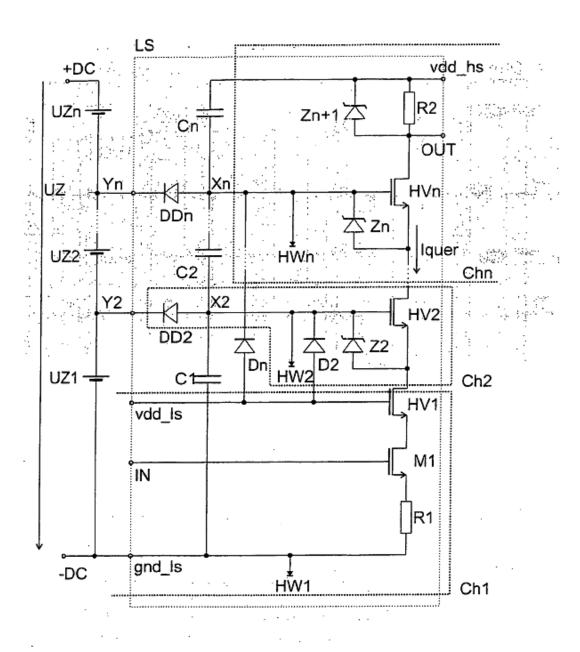

La figura 3 muestra una segunda configuración de un desviador de nivel según la invención.

La figura 4 muestra simulaciones comparativas de los desviadores de nivel según la figura 1a y la figura 3.3.

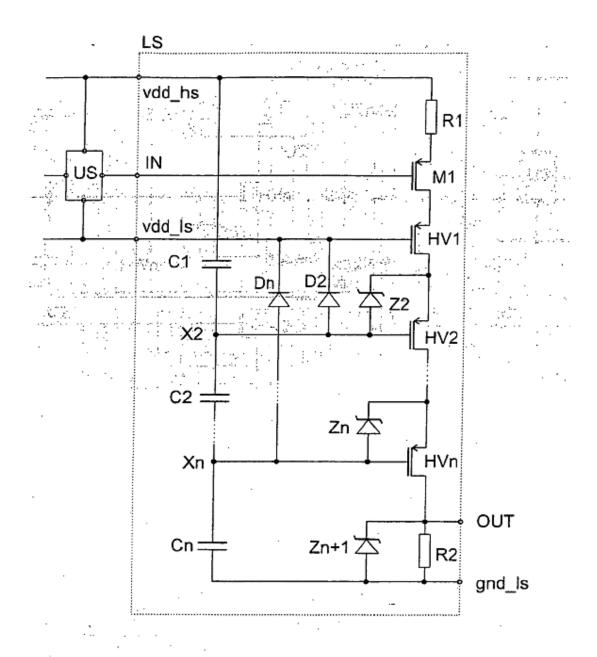

La figura 5 muestra un tercer diseño de un desviador de nivel según la invención.

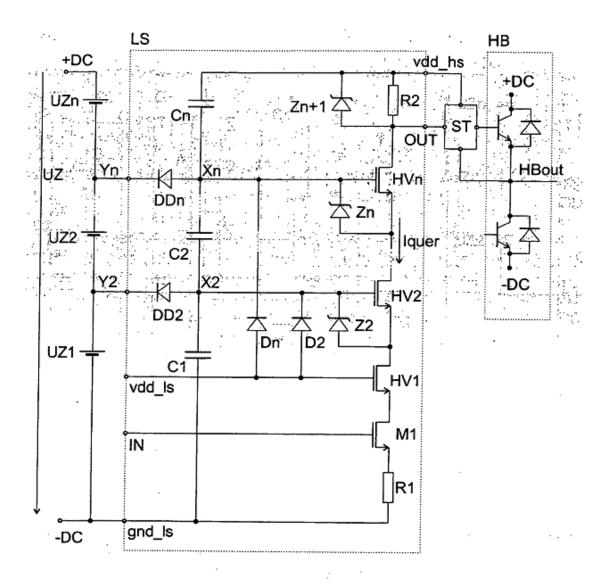

20 La figura 6 muestra un cuarto diseño de un desviador de nivel según la invención.

La figura 1a muestra una instalación que tiene un desviador de nivel (LS) según la invención, en la que un transistor de conmutación (M1) y un número n de transistores de alta tensión (HV1 hasta HVn) están conectados en serie. En el caso de una transmisión de señal desde el lado bajo al lado alto, todos los transistores son del tipo de canal N. Una primera resistencia (R1) está conectada a la fuente del transistor de conmutación (M1) y al carril de tierra (gnd\_ls) del lado bajo. Una segunda resistencia (R2) está conectada al drenaje del último transistor de alta tensión (HVn) y al terminal de la tensión de funcionamiento del lado alto (vdd\_hs). La entrada del desviador de nivel, al cual se pasa la señal que se va a transmitir, está directamente conectada a la puerta del transistor de conmutación (M1). El terminal de drenaje del último transistor de alta tensión (HVn) es la salida (OUT) del desviador de nivel (LS). Un circuito de análisis de la señal (ST) está conectado a éste, por ejemplo un disparador Schmitt. El carril de tierra del circuito de análisis de la señal (ST) está conectado al nodo del centro (HBout) de un medio puente de potencia (HB). El nodo del centro (HBout) del medio puente (HB) forma el potencial de referencia (gnd\_hs) del lado alto y dependiendo del estado de conmutación del semiconductor de potencia (TOP, BOT) está tanto cerca de la tensión del circuito intermedio (UZ) en el electrodo positivo (+DC) del circuito intermedio como cerca del potencial en el electrodo negativo (-DC) del circuito intermedio, el cual típicamente está conectado al carril de tierra (gnd\_ls).

El suministro de tensión de funcionamiento para los circuitos en el lado alto puede estar implantado con técnicas conocidas. Éstas incluyen el suministro de tensión de arranque o convertidores de corriente continua / corriente continua.

La puerta del primer transistor de alta tensión (HV1) está conectada directamente al carril de tensión de funcionamiento (vdd\_ls) del lado bajo y por lo tanto siempre recibe un potencial constante, por ejemplo 15 V, el cual es generado por una fuente de tensión de corriente continua. El cátodo de un primer diodo asociado (D2 hasta Dn) se conecta a cada uno de los terminales de la puerta de los otros transistores de alta tensión (HV2 hasta HVn), en donde estos diodos también pueden estar formados a partir de un circuito en serie de una pluralidad de diodos. Los ánodos de los primeros diodos (D2 hasta Dn) están conectados al potencial (vdd\_ls). En un estado de conmutación en el cual los potenciales de referencia del lado alto y el lado bajo son iguales, lo cual significa que el valor de (gnd\_hs) es igual al valor de (gnd\_ls), los primeros diodos (D2 hasta Dn) son desviados en el sentido directo y un potencial definido se aplica en los terminales de la puerta de los transistores de alta tensión asociados (HV2 hasta HVn), el cual casi corresponde a la tensión que es generada por la fuente de tensión de corriente continua, menos las tensiones directas del diodo.

La puerta en la entrada de control (IN) del transistor de conmutación (M1) tiene una señal de control periódicamente recurrente aplicada al mismo, por ejemplo un impulso rectangular, el cual está preparado por la lógica de control del excitador de la puerta. La señal de control causa una conmutación del transistor de conmutación (M1). Los transistores de alta tensión (HV1 hasta HVn) son conectados y desconectados de ese modo. Cuando están conectados, una corriente transversal (Iquer) fluye a través del desviador de nivel (LS). La señal de entrada digital es por lo tanto convertida en una señal de corriente y transmitida de ese modo a través del desviador de nivel (LS). La caída de tensión a través de la segunda resistencia (R2) es proporcional a la corriente transversal (Iquer).

El circuito de análisis de la señal (ST) conectado a la salida (OUT) del desviador de nivel (LS) convierte la señal transmitida de vuelta a una señal digital. A diferencia del diseño según la técnica anterior, el desviador de nivel según la invención no requiere circuitos adicionales de transmisión de la señal a n-1 potenciales intermedios.

A continuación la señal es sometida a un procesamiento de la señal lógica adicional o es enviada directamente al excitador para el conmutador TOP. Una señal transmitida al lado alto conduce a un proceso de conmutación del

conmutador TOP del medio puente de potencia (HB). Cuando ocurre un proceso de conmutación del medio puente de potencia (HB), en el cual el conmutador BOT es desconectado y el conmutador TOP es conectado simultáneamente o poco después, la tensión en la salida del medio puente (HBout) incrementa con un cambio rápido por unidad de tiempo (du/dt), por ejemplo 10 kV/µs. El potencial de referencia del lado alto incrementa a la misma velocidad al mismo tiempo. Después del proceso de conmutación, existe una tensión entre los potenciales (vdd\_hs y vdd\_ls, respectivamente entre gnd\_hs y gnd\_ls) de aproximadamente la tensión del circuito intermedio (UZ). La mayor parte de la tensión cae a través de los transistores de alta tensión (HV1 hasta HVn).

5

20

35

60

Un divisor de tensión capacitiva está conectado entre (vdd\_hs) y (gnd\_ls), que consiste en condensadores (C1 hasta Cn) conectados juntos en serie, los cuales cuando ocurre un cambio temporal en la tensión de salida del medio puente (HB) generan n-1 potenciales intermedios en los nodos (X2 hasta Xn), los cuales están conectados cada uno de ellos a las puertas de los transistores de alta tensión (HV2 hasta HVn). Proporcionando un dimensionado adecuado a los condensadores (C2 hasta Cn) la tensión que varía se divide uniformemente sobre los nodos (X2 hasta Xn), de modo que ocurre una caída de tensión a través de cada condensador que corresponde a la n-sima parte de la tensión actualmente aplicada entre (vdd hs) y (gnd ls).

La tensión máxima que puede caer a través de un condensador (C1 hasta Cn) aproximadamente corresponde a la n-sima parte de la tensión del circuito intermedio (UZ). La división de la tensión producida por los condensadores también se conserva después de que se haya disipado el cambio de la tensión temporal, puesto que los condensadores (C1 hasta Cn) mantienen la carga almacenada. Si el potencial de referencia del lado alto es más alto que el potencial de referencia del lado bajo, entonces los primeros diodos (D2 hasta Dn) son polarizados a la inversa. Estos diodos (D2 hasta Dn) requieren una tensión de ruptura la cual es por lo menos tan grande como la tensión máxima que ocurre entre los nodos (X2 hasta Xn) y (vdd\_ls).

Además, cada transistor de alta tensión (HV2 hasta HVn) está conectado a un diodo Zener (Z2 hasta Zn), en el que el cátodo está conectado a la puerta y el ánodo a la fuente del transistor de alta tensión asociado. La tensión de fuente de la puerta de cada transistor de alta tensión (HV2 hasta HVn) está sometida de ese modo a un límite superior con un valor por debajo de la tensión de ruptura de la trayectoria de la fuente de la puerta de un transistor de alta tensión y por lo tanto evita una ruptura del componente. La tensión Zener del diodo Zener, típicamente sólo unos pocos voltios, se puede despreciar con relación a la tensión de circuito intermedio cuando se considera el ajuste del potencial intermedio.

El potencial en la puerta del transistor de alta tensión está relacionado por lo tanto a la fuente del mismo transistor, o al drenaje del transistor por debajo del mismo. A través de la trayectoria de la fuente de drenaje de cada transistor de alta tensión (HV1 hasta HVn) por lo tanto, la máxima tensión que puede caer es la n-sima parte de la tensión del circuito intermedio (UZ). Una resistencia a la ruptura de la tensión del desviador de nivel completo (LS) se puede obtener por lo tanto, la cual corresponde aproximadamente a n veces la tensión de ruptura de la trayectoria de la fuente de drenaje de un transistor de alta tensión.

- Un diodo Zener adicional (Zn+1) se conecta en paralelo con la segunda resistencia (R2). El cátodo de (Zn+1) se conecta a (vdd\_hs), el ánodo a la salida del desviador de nivel (LS). Esto significa que la caída de tensión a través de (R2) la cual ocurre en el caso de una corriente transversal a través del desviador de nivel está limitada de tal manera que el potencial en la salida (OUT) del desviador de nivel no cae por debajo del potencial de tierra (gnd\_hs), del disparador Schmitt (ST) aguas abajo y al mismo tiempo garantiza una oscilación de la tensión en la salida la cual permite una diferenciación entre el nivel alto y el bajo trasmitido. Un valor preferido es el nivel de la tensión de funcionamiento en el lado alto, por ejemplo 15 V. Ajustando los potenciales intermedios en las puertas de los transistores de alta tensión (HV2 hasta HVn) por medio del divisor de tensión capacitiva, una transmisión de señal a través del desviador de nivel (LS) es posible durante todos los estados de funcionamiento del medio puente (HB).

- Una configuración simplificada adicional según la figura 1b del desviador de nivel prescinde del transistor de conmutación (M1) y conecta la entrada (IN) directamente a la puerta del primer transistor de alta tensión (HV1'). A diferencia de la configuración según la figura 1a los primeros diodos (D2 hasta Dn) no están conectados a la puerta del primer transistor de alta tensión (HV1). La otra configuración es idéntica a aquella según la figura 1a. La consecuencia de la eliminación del transistor de conmutación (M1, según la figura 1a) sin embargo, es que la velocidad de transmisión es inferior para la misma potencia de conmutación.

En la figura 2 la respuesta de transmisión transitoria del desviador de nivel según la figura 1a se ilustra en el contexto de una simulación. En este caso se ha escogido una forma de realización con dos transistores de alta tensión para la simulación. A partir de los diagramas es evidente que tanto a un potencial de referencia constante del lado alto y el lado bajo (Uoffset = 0 V) como a un potencial de referencia del lado alto próximo a la tensión del circuito intermedio (Uoffset = 600 V/1200 V), una señal de control (IN) es trasmitida desde el lado bajo al lado alto (OUT). El disparador Schmitt detecta correctamente la señal transmitida. Con C1 = C2 el potencial en el nodo X1 se ajusta él mismo, como se desea, hasta aproximadamente la mitad de la tensión del circuito intermedio de 600 V.

La figura 3 muestra una segunda forma de realización del desviador de nivel (LS) según la invención, extendido con relación a la figura 1a. Una tensión del circuito intermedio (UZ) se genera a partir de n fuentes idénticas de tensión

(UZ1 hasta UZn) las cuales están conectadas juntas en serie, en donde cada fuente de tensión puede generar la misma tensión parcial UZ/n. El potencial en el nodo adicional (Y2) por lo tanto corresponde al potencial máximo que se espera que ocurra en el nodo (X2). La misma afirmación se aplica de forma análoga a los nodos (Y3 y X3 hasta Yn y Xn). Esto se explicará adicionalmente utilizando un ejemplo simple. La tensión del circuito intermedio del sistema tiene el valor de 600 V en este ejemplo. La tensión de ruptura de los transistores de alta tensión disponibles es por lo menos 300 V pero inferior a 600 V. A fin de garantizar la resistencia a la ruptura de la tensión requerida del desviador de nivel por lo tanto, dos transistores de alta tensión se deben conectar en serie, esto es n = 2. El potencial en la puerta de (HV2) es establecido por el divisor de tensión capacitiva (C1, C2). Si el circuito intermedio está entonces compuesto por dos fuentes de tensión (UZ1 = UZ2) cada una con 300 V, entonces el potencial en el nodo central (Y2) del circuito intermedio corresponde exactamente al potencial (300 V) que debe estar presente en el nodo (X2) (puerta de HV2) a fin de garantizar una distribución de la tensión aproximadamente igual a través de los transistores de alta tensión (en cada caso 300 V).

10

15

20

25

60

65

Además de la instalación según la figura 1, la forma de realización según la figura 3 se extiende mediante los diodos adicionales (DD2 hasta DDn). Los ándos de estos diodos están conectados cada uno de ellos a los nodos (X2 hasta Xn) y los cátodos correspondientes a los ándos adicionales (Y2 hasta Yn). La transmisión de la señal a través del desviador de nivel (LS) tiene lugar del mismo modo que en la primera forma de realización. El ajuste de los potenciales en los nodos (X2 hasta Xn) durante un proceso de conmutación en el cual el conmutador BOT es conectado y el conmutador TOP desconectado, se obtiene adicionalmente por medio de los condensadores (C1 hasta Cn). El potencial máximo en los nodos (X2 hasta Xn) está de ese modo limitado a partir de lo anterior al potencial constante en los nodos adicionales correspondientes (Y2 hasta Yn). Si el potencial en un nodo (Xk) se hace mayor que el potencial en el nodo adicional (Yk) más la tensión directa del diodo adicional (DDk) (½ k ≤ n), entonces el diodo adicional se convierte en circuito abierto (DDk) y el potencial en el nodo (Xk) no puede incrementar adicionalmente. La limitación únicamente tiene efecto si la capacitancia de uno o más de los condensadores (C1 hasta Cn) se desvía del valor deseado, o están activas capacitancias parásitas (C1 hasta Cn). Una desviación en la capacitancia del condensador a partir del valor deseado puede ocurrir, por ejemplo, debido a la variabilidad de los parámetros durante la fabricación. La desviación de la capacitancia como resultado conduce a una división de la tensión asimétrica.

30 Debido a la limitación de los potenciales en los nodos (X2 hasta Xn) a un valor superior sin embargo, no se garantiza en todas las circunstancias que la tensión de ruptura del transistor de alta tensión (HV1 hasta HVn) no pueda ser excedida. Esto se explicará otra vez utilizando el ejemplo de n = 2. Si C1 y C2 son iguales en tamaño, entonces el potencial en la puerta de (HV2) es establecido por el divisor de tensión hasta aproximadamente UZ/2 = 300 V y la limitación no produce efecto. Si la capacitancia de (C2) es mayor que la de (C1) entonces el diodo adicional (DD2) 35 limita el potencial en la puerta de (HV2) (nodo X2) a 300 V. También, en ambos casos la tensión de la fuente de drenaje de (HV1 y HV2) no es superior a un máximo de 300 V, de modo que la tensión de ruptura de los transistores no se excede. Si la capacitancia de (C1) es mayor que la de (C2), entonces la mayor parte de la tensión actualmente aplicada entre (vdd hs) y (gnd ls) cae a través (C2). La tensión de la fuente de drenaje de (HV2) puede por lo tanto exceder la tensión de ruptura, es decir, la tensión de ruptura deseada del desviador de nivel (LS) posiblemente deja 40 de estar garantizada. En el caso en el que la capacitancia de (C2) sea mayor que aquella de (C1) por lo tanto representa la variante preferida, puesto que la limitación de la tensión en la puerta de (HV2) siempre tendrá efecto y la tensión de ruptura de (HV2) no puede ser excedida. A fin de obtener un comportamiento del circuito análogo para la forma de realización con n transistores de alta tensión conectados en serie, las capacitancias de (C1 hasta Cn) están dimensionadas de tal modo que las capacitancias de los condensadores respectivos (C1 hasta Cn) 45 incrementan con su número de secuencia (1 hasta n). Esta forma de realización ventajosa del desviador de nivel (LS) es por lo tanto adecuada para aplicaciones en las cuales los valores de los condensadores (C1 hasta Cn) sean altamente dispersas, o ciertas capacitancias parásitas de la instalación no se puedan calcular con precisión, o estén sometidas a variaciones debido a la aplicación.

La figura 4 muestra el comportamiento simulado de un desviador de nivel para n = 2 según la figura 1a (parte de la izquierda del dibujo) y según la figura 3 (parte de la derecha del dibujo) durante el proceso de conexión, en el que la capacitancia de (C1) es en cada caso mucho menor que aquella de (C2). Debido a la carga capacitiva no uniforme, el potencial intermedio en el nodo (X2) del desviador de nivel según la figura 1a incrementa con el rápido du/dt del potencial de referencia del lado alto (vdd\_hs) hasta un valor mayor que UZ/2 = 300 V (aproximadamente 395 V). En el desviador de nivel según la figura 3 el potencial intermedio en el nodo (X2) no se eleva por encima de UZ/2 puesto que no tiene efecto el proceso de limitación descrito debido al diodo adicional (DD2).

La figura 5 ilustra una forma de realización del desviador de nivel (LS) según la invención, con la cual es posible transmitir señales a través de una barrera de potencial que es mayor que la resistencia a la ruptura de la tensión entre el lado alto y el lado bajo en un circuito integrado. Esta resistencia a la ruptura de la tensión se determina en primer lugar mediante la tensión de ruptura del desviador de nivel integrado, la cual en el caso de topologías convencionales está determinada por la tensión de ruptura del transistor de alta tensión integrado y en segundo lugar por la resistencia a la ruptura de la tensión del aislamiento entre el lado alto y el lado bajo. La resistencia a la ruptura de la tensión del aislamiento se determina mediante la tecnología de semiconductores y no se puede incrementar con técnicas de la tecnología de circuitos. En tanto en cuanto a la tensión de ruptura del transistor de alta tensión que se puede integrar es por lo menos n veces inferior que la resistencia a la ruptura de la tensión del

aislamiento, la resistencia a la ruptura de la tensión del desviador de nivel, como ha sido descrito antes en este documento, puede ser incrementada mediante la utilización de n transistores de alta tensión en un HVIC hasta n veces el valor, esto es, como máximo hasta la resistencia a la ruptura de la tensión del aislamiento.

Puesto que en la mayoría de los casos la tensión de ruptura del aislamiento y del transistor de alta tensión son aproximadamente del mismo tamaño, la resistencia a la ruptura de la tensión del desviador de nivel entero únicamente se puede incrementar por un factor de n si cada uno de los n transistores de alta tensión está integrado en un sustrato separado. Por lo tanto, con procedimientos de aislamiento de 600 V según la técnica anterior, se pueden superar diferencias de potencial más altas. Si, por ejemplo, se utilizan dos pastillas, una instalación de circuito integrado también se puede implantar para la clase de tensión de 1200 V.

La forma de realización en la figura 5 difiere de aquella según la figura 3 en que el desviador de nivel está dividido entre n pastillas separadas (Ch1 hasta Chn); en donde uno de los n transistores de alta tensión (HV1 hasta HVn) ha sido integrado en cada pastilla. Se supone, por ejemplo, que se utilizó una tecnología SOI para fabricar las pastillas. El transistor de alta tensión (HV1), el transistor de computación (M1) y la primera resistencia (R1) están integrados en una pastilla (Ch1). Si es apropiado, circuitos adicionales, tales como un módulo lógico y un excitador para un conmutador BOT pueden estar integrados en una pastilla (Ch1).

15

30

35

40

60

65

Las pastillas (Ch2 hasta Chn-1) contienen cada una de ellas un transistor de alta tensión (HV2 hasta HVn-1) y los diodos. Zener asociados (Z2 hasta Zn-1), los cuales al igual que las formas de realización anteriores están conectados a los transistores de alta tensión (HV2 hasta HVn-1). Los diodos primero y segundo n - (D2 hasta Dn y DD2 hasta DDn) pueden estar integrados en la pastilla respectiva (Ch2 hasta Chn) si la tensión de bloqueo que puede ocurrir como máximo en el diodo es menor que la resistencia a la ruptura de la tensión del aislamiento de la pastilla. Si la tensión de bloqueo que ocurre como máximo en los diodos (D2 hasta Dn y DD2 hasta DDn) es mayor que la resistencia a la ruptura de la tensión del aislamiento de la pastilla, entonces los diodos correspondientes deben ser implantados como componentes exteriores.

La pastilla (Chn) contiene el transistor de alta tensión (HVn); los diodos Zener (Zn, Zn-1) y la resistencia (R2). Si es posible, todas las secciones adicionales del circuito del lado alto; por ejemplo el circuito de análisis de señales y el excitador para el conmutador TOPS pueden estar integrados en la pastilla (Chn). Los condensadores (C1 hasta Cn) pueden estar integrados en las pastillas asociadas (Ch1 hasta Chn). Debido a la alta área de pastilla requerida para los condensadores, la implantación con componentes discretos exteriores es una forma de realización preferida.

Por supuesto, es posible una forma de realización de este desviador de nivel sin los diodos de limitación de la tensión (DD2 hasta DDn), de forma análoga a las primeras formas de realización según las figuras 1a y 1b.

El electrodo en la parte posterior de cada pastilla (Ch1 hasta Chn), a fin de poder garantizar un funcionamiento correcto del circuito, debe transportar un potencial que sea próximo al potencial más bajo de la pastilla respectiva. Un cambio en el potencial en el contacto posterior de una pastilla cambia el comportamiento eléctrico de los componentes en la parte superior. Este efecto es conocido como el efecto "backgate" (puerta trasera). En las tecnologías PN aisladas según la técnica anterior, el contacto posterior debe transportar siempre el potencial más bajo que pueda ocurrir en la pastilla, puesto que de otro modo la unión PN la cual va a transportar la tensión entre el lado alto y el lado bajo es desviada directa y de ese modo no puede cumplir esta función.

Por el contrario, en una tecnología SOI el contacto posterior (HW) está aislado dieléctricamente de los componentes 45 en la parte superior de la oblea, de modo que incluso con un potencial bastante alto en el contacto posterior el aislamiento no se deteriora. Un efecto notable del potencial posterior incrementado en el comportamiento eléctrico de los componentes típicamente ocurre únicamente por encima de unos pocos 10 V. Esta ventaja de la tecnología SOI se utiliza en el circuito según la invención en esta tecnología. El contacto posterior de la pastilla 1 (HW1) está 50 conectado al carril de tierra de la pastilla (gnd ls). Los contactos posteriores (HW2 hasta HWn) de las pastillas (Ch2 hasta Chn) están conectados cada uno de ellos a los terminales de la puerta de los transistores de alta tensión correspondientes (HV2 hasta HVn), o a los nodos correspondientes (X2 hasta Xn). El potencial en el terminal de la fuente de un transistor de alta tensión es siempre el potencial más bajo que ocurre en la pastilla en la cual está integrado el transistor de alta tensión. Los diodos Zener (Z2 hasta Zn) limitan la tensión de la fuente de la puerta de 55 los transistores (HV2 hasta HVn) a unos pocos voltios, por ejemplo 15 V y de ese modo mantienen el potencial en la fuente del transistor de alta tensión integrado cerca del potencial del contacto posterior de la pastilla respectiva. Las pastillas (Ch1 hasta Chn) están aisladas unas de las otras, pero de forma ventajosa están instaladas en un paquete común. La conexión eléctrica entre las pastillas se puede obtener con procedimientos conocidos, por ejemplo un procedimiento de unión a masa.

La figura 6 muestra un desviador de nivel en una cuarta forma de realización. La variante presentada en este caso es un desviador de nivel el cual transmite una señal de tensión que ha sido generada en el lado alto hacia el lado bajo, a fin de ser analizada allí por un circuito lógico. Del mismo modo, la señal desde el lado bajo puede ser dirigida a un micro control. La señal de tensión puede ser, por ejemplo, una señal de estado de un circuito de supervisión (US), el cual detecta el estado de funcionamiento de ciertos subcircuitos del lado alto, por ejemplo una supervisión de la tensión de funcionamiento o la temperatura de un subcircuito. El micro control puede de ese modo supervisar

la señal de estado de un estado de funcionamiento en el lado alto.

5

El desviador de nivel (LS) está estructurado de una manera complementaria a la forma de realización según la figura 1a. Es decir, se utiliza la misma topología, siendo la diferencia que tanto los n transistores de alta tensión (HV1 hasta HVn) como el transistor de conmutación (M1) son del tipo de canal P. La primera resistencia (R1), los transistores (M1, HV1 hasta HVn) y la segunda resistencia (R2) están conectados otra vez en serie. Un terminal de la primera resistencia (R1) está conectado a la fuente del transistor de conmutación (M1), el otro terminal al carril de tensión de funcionamiento (vdd hs) del lado alto.

- La segunda resistencia (R2) está conectada al drenaje del transistor (HVn) y al carril de tierra (gnd\_ls) del lado bajo. El terminal de la puerta del transistor de conmutación (M1) es la entrada (IN) del desviador de nivel (LS), al cual se alimenta la señal que se va a transmitir. El terminal de drenaje del transistor de alta tensión (HVn) es la salida (OUT) del desviador de nivel. Un circuito de análisis de la señal (ST) está conectado a éste, por ejemplo un disparador Schmitt. La tierra del circuito de análisis de la señal está conectada al carril de tierra (gnd\_ls) del lado bajo.

- Cada uno de los terminales de la puerta de los transistores de alta tensión (HV2 hasta HVn) está conectado al ánodo de uno de los primeros diodos (D2 hasta Dn). Los cátodos de los diodos están conectados al potencial (gnd\_hs). En un estado de conmutación en el cual los potenciales de referencia del lado alto y el lado bajo son iguales, es decir (vdd\_hs = vdd\_ls o gnd\_hs = gnd\_ls), los diodos (D2 hasta Dn) son desviados directamente y un potencial definido está presente en los terminales de la puerta de los transistores de alta tensión (HV2 hasta HVn) el cual casi corresponde al potencial en (gnd\_hs). Un diodo Zener (Zn+1) está conectado en paralelo con la segunda resistencia (R2). El ánodo de (Zn+1) está conectado a (gnd\_ls), el cátodo de la salida (OUT) del desviador de nivel (LS). (Zn+1) limita la caída de tensión a través de (R2) como se ha descrito en la primera forma de realización de la figura 1.

- 25 El divisor de tensión capacitiva entre (vdd\_hs) y (gnd\_ls), que consiste en los condensadores (C1 hasta Cn) los cuales están conectados juntos en serie, está conectado como en la primera forma de realización y controla el ajuste del potencial en los electrodos de la puerta de los transistores de alta tensión (HV2 hasta HVn) cuando tiene lugar un cambio temporal en el potencial de referencia del lado alto de la manera descrita. Del mismo modo que en la primera forma de realización según la figura 1a, un diodo Zener (Z2 hasta Zn) está conectado a cada uno de los transistores 30 de alta tensión (HV2 hasta HVn), en donde el cátodo está conectado a la fuente y el ánodo a la puerta del transistor de alta tensión. La tensión de la fuente de la puerta de cada transistor de alta tensión (HV2 hasta HVn) se limita de ese modo y se evita por lo tanto la ruptura del componente. La transmisión de la señal de una señal de tensión desde el lado alto al lado bajo tiene lugar del mismo modo que la transmisión de la señal desde el lado bajo al lado alto en la primera forma de realización. La señal de control es pasada a la puerta del transistor de conmutación (M1) 35 y causa la conmutación del transistor de conmutación (M1). Esto causa que los transistores de alta tensión (HV1 hasta HVn) se conecten y se desconecten. Cuando están conectados, una corriente transversal (Iguer) fluye a través del desviador de nivel (LS). La señal de entrada digital es convertida en una señal de corriente y de ese modo es transmitida a través del desviador de nivel (LS). La caída de tensión a través de la segunda resistencia (R2) es proporcional a la corriente transversal. El circuito de análisis de las señales (ST) conectado a la salida (OUT) del 40 desviador de nivel (LS) convierte la señal transmitida en una señal digital.

#### REIVINDICACIONES

- 1. Desviador de nivel para la transmisión unidireccional de una señal desde una primera sección del circuito a un primer potencial hasta una segunda sección del circuito a un segundo potencial, provisto de un circuito en serie de una pluralidad de transistores en el que la entrada (IN) del desviador de nivel (LS) está conectada a la entrada de control del primer transistor del circuito en serie, este primer transistor es un transistor de conmutación (M1) o un transistor de alta tensión (HV1') y todos los otros transistores son transistores de alta tensión, y estando provisto de un circuito divisor de tensión capacitiva conectado en paralelo con los transistores de alta tensión (HV1 hasta HVn), en el que dicho circuito divisor de tensión capacitiva está conectado entre un potencial de referencia (gnd\_ls) del lado bajo y un potencial de referencia (vdd\_hs) del lado alto y están instalados nodos (X2 hasta Xn) entre los condensadores individuales (C1 hasta Cn) los cuales están conectados a los terminales de control de los transistores de alta tensión asociados (HV2 hasta HVn) y en el que primeros diodos (D2 hasta Dn) están conectados en cada caso entre un suministro de tensión del lado de la entrada (vdd\_ls) del desviador de nivel (LS) y las entradas de control de los transistores de alta tensión (HV2 hasta HVn).

- 15 2. El desviador de nivel según la reivindicación 1 en el que todos los condensadores (C1 hasta Cn) tienen la misma capacitancia.

- 3. El desviador de nivel según la reivindicación 1 en el que las capacitancias de los respectivos condensadores (C1 hasta Cn) incrementan con su número de secuencia (1 hasta n).

- 4. El desviador de nivel según la reivindicación 1 en el que en el caso de una transmisión de señal desde el lado bajo hasta el lado alto, el transistor de conmutación (M1) así como los transistores de alta tensión (HV1 hasta HVn) son del tipo de canal N, una primera resistencia (R1) está conectada en serie antes del primer transistor (M1 o HV1') y una segunda resistencia (R2) está conectada en serie después del último transistor de alta tensión (HVn).

- 5. El desviador de nivel según la reivindicación 1 en el que en el caso de una transmisión de señal desde el lado alto hasta el lado bajo, el transistor de conmutación (M1) así como los transistores de alta tensión (HV1 hasta HVn) son del tipo de canal P, una primera resistencia (R1) está conectada en serie antes del primer transistor (M1 o HV1') y una segunda resistencia (R2) está conectada en serie después del último transistor de alta tensión (HVn).

- 6. El desviador de nivel según la reivindicación 1 en el que para el propósito de la limitación de la tensión, diodos Zener (Z2 hasta Zn) están conectados entre la entrada de control y la fuente de los transistores de alta tensión asociados (HV2 hasta HVn).

- 7. El desviador de nivel según la reivindicación 1 en el que para el propósito de la limitación de la tensión un diodo Zener adicional (Zn+1) está conectado en paralelo con la resistencia (R2).

- 8. El desviador de nivel según la reivindicación 1 en el que los nodos (X2 hasta Xn) están conectados cada uno de ellos por medio de segundos diodos (DD2 hasta DDn) a terminales exteriores asociados del desviador de nivel (LS).

- 9. El desviador de nivel según la reivindicación 1 en el que el desviador de nivel (LS) está implantado como un circuito monolíticamente integrado en un sustrato o adecuadamente distribuido sobre una pluralidad de sustratos (S1 hasta Sn).

45

40

10

20

25

30

Fig. 1a

Fig. 1b

Fig. 3

Fig. 5

Fig. 6