OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 384 428

(2006.01)

51) Int. Cl.: H01L 21/331 H01L 21/265

**H01L 21/265** (2006.01) **H01L 21/268** (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Número de solicitud europea: 09178466 .0

- 96 Fecha de presentación: 09.12.2009

- Número de publicación de la solicitud: 2360717

Fecha de publicación de la solicitud: 24.08.2011

- (54) Título: Método para la producción de un dispositivo semiconductor que usa el recocido láser para activar selectivamente los adulterantes implantados

- Fecha de publicación de la mención BOPI: **04.07.2012**

73 Titular/es:

ABB Technology AG Affolternstrasse 44 8050 Zürich, CH

- Fecha de la publicación del folleto de la patente: **04.07.2012**

- 72 Inventor/es:

Vobecky, Jan y Rahimo, Munaf

(74) Agente/Representante: Ungría López, Javier

ES 2 384 428 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

Método para la producción de un dispositivo semiconductor que usa el recocido láser para activar selectivamente los adulterantes implantados

# Campo de la invención

5

10

25

30

35

40

50

65

La presente invención se refiere a un método para producir un dispositivo semiconductor con una superficie modelada que comprende al menos una zona adulterada con un adulterante de un primer tipo de conductividad y al menos una zona adulterada con un adulterante de un segundo tipo de conductividad en un mismo lateral de un sustrato semiconductor.

#### Antecedentes de la técnica

Hay dispositivos semiconductores en los que tanto las zonas tipo-n como las zonas tipo-p se generan en un mismo lateral de un sustrato semiconductor. Por ejemplo, la fabricación de una nueva generación de IGBT (Transistor Bipolar de Puerta Aislada - Insulated Gate Bipolar Transistors) puede requerir superficies laterales posteriores modeladas adecuadamente de una oblea semiconductora en la que la superficie lateral posterior comprende zonas de tipo-p que forman un ánodo del IGBT y el lateral posterior comprende también zonas de tipo-n que forman un cátodo de un diodo anti-paralelo. En esta, "el modelado" puede significar tanto, una geometría optimizada como un perfil de adulterante optimizado de las zonas de tipo-p y de tipo-n.

Convencionalmente, tales semiconductores modelados se han procesado con el uso de, por ejemplo, técnicas de enmascaramiento sofisticadas. Por ejemplo, un área completa de la superficie que se modela primero se adultera con un adulterante, por ejemplo, boro o aluminio para formar un adulterante de tipo-p. A continuación, las áreas que mantendrán el adulterante de tipo-p pueden protegerse con una capa de protección, tal como un dieléctrico cuya capa de protección puede modelarse con el uso de, por ejemplo, tecnología de enmascaramiento y de fotolitografía. A continuación, en un segundo proceso adulterante, otro adulterante, por ejemplo, fósforo o arsénico forman un adulterante de tipo-n, que puede adulterarse en las áreas no protegidas y compensar en exceso el adulterante para formar el adulterante de tipo-p en estas áreas.

En el documento US 2009/267200, se describe otro método de fabricación de un IGBT que usa enmascaramiento, en el que un adulterante-p como el boro, el fluoruro de boro o el aluminio se implanta profundamente a través de un enmascaramiento en una primera profundidad en la superficie posterior del dispositivo y después se realiza un primer recocido láser, por lo que al recocer la superficie se funde a la primera profundidad y el adulterante se activa completamente. Debido a la alta movilidad durante la fusión el adulterante se distribuye homogéneamente en la parte fundida. Después, un adulterante-n tal como el fósforo o el arsénico se implanta en una segunda profundidad, que es más pequeña que la primera profundidad con el fin de formar un tampón-n. Se realiza un segundo recocido láser, mediante el cual el sustrato se funde a la segunda profundidad de manera que otra vez el adulterante n se distribuye homogéneamente en la parte fundida.

Sin embargo, tal modelado de la zona de tipo-p y de tipo-n que usa técnicas de enmascaramiento puede requerir un trabajo y un coste sustanciales.

# 45 Divulgación de la invención

Puede ser un objetivo de la presente invención proporcionar un método para producir un dispositivo semiconductor con una superficie modelada que comprende zonas adulteradas con un adulterante de un primer tipo de conductividad y otras zonas adulteradas con un adulterante de un segundo tipo de conductividad en un mismo lateral de un sustrato semiconductor, método que permite reducir el trabajo y el coste.

Tal objetivo puede resolverse mediante el objeto de la reivindicación 1. Se proporcionan las realizaciones ventajosas en las reivindicaciones dependientes.

De acuerdo con un aspecto de la presente invención, se propone un método para producir un dispositivo semiconductor con una superficie modelada que comprende al menos una zona adulterada con un adulterante de un primer tipo de conductividad y al menos una zona adulterada con un adulterante de un segundo tipo de conductividad en el mismo lateral de un sustrato semiconductor. Preferentemente, el método comprende las siguientes etapas pero no necesariamente en el siguiente orden:

(a) implantar el adulterante del primer tipo de conductividad tal como, por ejemplo, boro o aluminio para formar el adulterante de tipo-p e implantar el adulterante del segundo tipo de conductividad tal como, por ejemplo, fósforo o arsénico para formar el adulterante de tipo-n en la superficie a modelar;

(b) activar localmente el adulterante del primer tipo de conductividad mediante el calentamiento a nivel local de las zonas parciales de la superficie para que se modele a una primera temperatura con el uso de un rayo láser; y

(c) activar el adulterante del segundo tipo de conductividad mediante el calentamiento del sustrato a una segunda temperatura que es menor que la primera temperatura.

La invención se basa en la idea de usar el siguiente efecto: en general se conoce que un material semiconductor puede adulterarse para tener un tipo de conductividad específica, es decir, para tener un tipo-n o un tipo-p, mediante la introducción de partículas tales como átomos, iones o moléculas en una red cristalina del material semiconductor. Sin embargo, se ha observado que las partículas que se han introducido en el material semiconductor mediante implantación iónica pueden necesitar que se "activen" antes de que actúe de manera eficaz como adulterante. Este efecto puede entenderse que es debido al hecho de que durante la implantación iónica las partículas implantadas no pueden localizarse en lugares dentro de la retícula del material semiconductor en los lugares que actuaría de manera eficaz como un adulterante. Además, la retícula del material semiconductor puede dañarse debido al proceso de implantación iónico. Por consiguiente, con el fin de activar las partículas implantadas puede necesitarse calentar la zona de implantación y de este modo sinterizar o incluso fundir esta zona. Tras tal calentamiento, las partículas implantadas pueden difundirse dentro de la retícula y finalmente pueden llegar a los lugares donde pueden actuar de manera eficaz como adulterantes.

Se ha observado que adulterantes diferentes pueden tener que activarse mediante procedimientos de calentamiento diferentes. Por ejemplo, un primer tipo de adulterante tal como, por ejemplo, el boro puede que necesite calentarse a temperaturas muy elevadas tal como, por ejemplo, más de 850 °C , preferentemente entre 900 y 1000 °C , con el fin de activarse en una concentración requerida para adulterantes. Otros tipos de un adulterante tal como, por ejemplo, el fósforo pueden activarse en una concentración requerida para adulterante ya en muchas menores temperaturas, por ejemplo, temperaturas por debajo de 650 °C, preferentemente temperaturas entre 400 y 600 °C, por ejemplo entre 500 y 550 °C.

15

20

35

40

50

60

Por consiguiente, ambos tipos de adulterantes, es decir, un primer tipo de adulterante para generar un primer tipo de conductividad y un segundo tipo de adulterante para generar un segundo tipo de conductividad, pueden implantarse en la superficie del sustrato semiconductor a modelar. Las áreas, en que se implanta el adulterante del primer tipo de conductividad y las áreas en que se implanta el adulterante del segundo tipo de conductividad pueden al menos solaparse parcialmente, tal que en las áreas de solapamiento, ambos adulterantes existen después de los procesos de implantación. También puede ser posible implantar el adulterante de cada tipo de conductividad en la superficie del sustrato completa para que se modele.

A continuación, para generar el tipo de conductividad que finalmente prevalecerá en una localización específica dentro de la superficie del sustrato modelada, el adulterante respectivo puede activarse selectivamente mediante el uso de un proceso de calentamiento adecuado.

Si, por ejemplo, sólo se calienta una localización a una baja temperatura de, por ejemplo 600 °C, sólo el tipo de adulterante que genera el segundo tipo de conductividad de los adulterantes que pueden activarse a tales bajas temperaturas se activará realmente, mientras que el otro tipo de adulterante que genera el primer tipo de conductividad, en el que el adulterante necesita una temperatura de activación mayor, permanece inactivo o activo a una concentración mucho más baja que el segundo tipo de conductividad. Por consiguiente, tal zona de la superficie del sustrato modelado finalmente tendrá el segundo tipo de conductividad.

En otra localización de la superficie del sustrato que se modela, puede usarse un proceso de calentamiento diferente con el fin de calentar a temperaturas mucho más altas, tales como, por ejemplo, más de 850 °C o incluso 900 °C a la cual también se activa la temperatura del adulterante del primer tipo de conductividad.

Entonces puede ser ventajoso para el implantar y activar el adulterante del primer tipo de conductividad a una mayor concentración de adulterante que el adulterante del segundo tipo de conductividad tal que el adulterante del primer tipo de conductividad pueda localmente compensar en exceso el adulterante del segundo tipo de conductividad. Por consiguiente, cuando una zona de la superficie del sustrato se calienta localmente a una temperatura muy elevada de, por ejemplo, entre 900 y 1000 °C , obtendrá finalmente el primer tipo de conductividad como, mientras ambos tipos de adulterantes se activan, el adulterante del primer tipo de conductividad está presente en una concentración superior que el adulterante del segundo tipo de conductividad de tal manera que este adulterante del primer tipo de conductividad determina el tipo de conductividad final en esta localización. Cuando una zona de la superficie del sustrato se calienta a una baja temperatura de, por ejemplo, menos de 650 °C solamente, el adulterante del segundo tipo de conductividad se activa, mientras que el del primer tipo de conductividad no se activa o no se activa completamente de tal manera que el adulterante del primer tipo de conductividad determina el tipo de conductividad final.

Con el fin de lograr las concentraciones de adulterante y los perfiles de adulterante adecuados, las energías y las dosis con que se implantan cada uno de los adulterantes del primer y segundo tipo de conductividad pueden tener que optimizarse el próximo proceso de activación de adulterante. Por ejemplo, se ha encontrado que el adulterante del primer tipo de conductividad puede implantarse adecuadamente con una dosis que va desde 1 x  $10^{13}$  cm<sup>-2</sup> hasta 1 x  $10^{16}$  cm<sup>-2</sup> y con una energía que va desde 5 keV hasta 200 keV, mientras que el adulterante del segundo tipo de conductividad puede implantarse adecuadamente con una dosis que va desde 1 x  $10^{12}$  cm<sup>-2</sup> hasta 1 x  $10^{16}$  cm<sup>-2</sup> y

con una energía que va desde 50 keV hasta 600 keV.

conductividad en la primera temperatura muy elevada.

25

30

35

45

Además, puede ser ventajoso implantar el adulterante del primer tipo de conductividad a una menor profundidad que el adulterante del segundo tipo de conductividad. Tal profundidad de implantación diferente puede usarse ventajosamente cuando las temperaturas muy altas necesarias pueden fácilmente generarse para activar el adulterante del primer tipo de conductividad sólo en una capa delgada cercana a la superficie del sustrato semiconductor, mientras que las temperaturas más bajas necesarias para activar el adulterante del segundo tipo de conductividad pueden también alcanzarse fácilmente para mayores profundidades.

Con el fin de activar localmente el adulterante del primer tipo de conductividad, las zonas respectivas pueden calentarse localmente mediante el uso de un rayo láser de energía y longitud de onda adecuadas. Por ejemplo, tal rayo láser puede proporcionarse mediante un aparato que se ha desarrollado por el bien conocido proceso de recocido láser. En esto, un rayo láser de alta energía y punto focal pequeño puede dirigirse a una zona para que se caliente a temperaturas muy elevadas. El rayo láser puede explorarse a lo largo de una zona que en el dispositivo semiconductor final deberá tener el primer tipo de conductividad. Una densidad de energía láser y una velocidad de exploración se pueden adaptar tal que una parte superficial del sustrato se calienta temporalmente a la muy elevada primera temperatura. En esto, la parte superficial puede tener una profundidad de menos de 1 µm, preferentemente menos de 300 nm. Por consiguiente, como el tiempo durante el cual la zona se ilumina con el rayo láser puede ser muy corto, la energía del rayo láser puede que no se disipe a una gran profundidad del sustrato tal que sólo la parte superficial se calienta a la primera temperatura alta y tal que solamente en esta parte superficial, se activa realmente el adulterante que forma el primer tipo de conductividad.

El método propuesto puede usarse dentro de una secuencia de procesamiento para producir diversos tipos de dispositivos semiconductores que tienen tanto, zonas de tipo-n, como zonas de tipo-p en un mismo lateral de un sustrato semiconductor. Por ejemplo, el método propuesto puede usarse en una secuencia de procesamiento para la preparación de un transistor bipolar de puerta aislada de conducción inversa (reverse conducting insulated gate bipolar transistor (RC-IGBT)) o un transistor bipolar de puerta aislada bimodal (bimode insulated gate bipolar transistor (BIGT)). En tales dispositivos semiconductores, el lateral que tiene la superficie modelada es el lateral posterior del dispositivo semiconductor.

En particular, cuando la preparación de este tipo de dispositivos semiconductores, tales como un RC-IGBT o un BIGT, las estructuras laterales anteriores del dispositivo semiconductor se pueden preparar primero antes de las etapas del proceso de implantación y activación del método como se ha descrito anteriormente que se realizan. En otras palabras, las estructuras laterales anteriores del dispositivo semiconductor que comprenden, por ejemplo, diversas áreas adulteradas, capas de pasivación y/o capas de metalización pueden estar antes completamente preparadas, en etapas posteriores, se generan las estructuras laterales posteriores que comprenden entre otras, la superficie modelada con sus zonas adulteradas con adulterantes del primer y segundo tipo de conductividad. En esto, el beneficio se puede tomar desde el hecho de que para la activación de los adulterantes del primer y segundo tipo de conductividad, no todo el dispositivo semiconductor se tiene que calentar a temperaturas muy elevadas. Por el contrario, la superficie modelada en el lateral posterior del dispositivo semiconductor puede prepararse sólo mediante el calentamiento de todo el dispositivo hasta la segunda baja temperatura de, por ejemplo, entre 500 y 650 °C. Tal baja temperatura puede activar el adulterante del segundo tipo de conductividad pero normalmente no perjudica o incluso no daña las estructuras previamente preparadas en el lateral anterior del sustrato del semiconductor que frecuentemente incluyen capas de aluminio que tienen un punto de fusión muy por encima de tales temperaturas. El adulterante del primer tipo de conductividad puede activarse localmente mediante el recocido láser que calienta localmente las zonas parciales respectivas de la superficie lateral posterior hasta temperaturas por encima de, por ejemplo, 900 °C. En esto, se puede tomar ventaja desde el hecho de que en la etapa de recocido láser la primera temperatura muy elevada sólo se alcanza en una zona muy delgada cercana a la superficie irradiada por el rayo láser pero, por ejemplo, debido a la corta duración de la pulsación usado por el recocido láser local, la energía térmica no se disipa a lo largo de todo el sustrato semiconductor. De esta manera, el lateral anterior que incluye las estructuras previamente preparadas sobre él mismo no se calienta a temperaturas muy elevadas y de

esta manera, no se ve afectado negativamente por la etapa de activación local del adulterante del primer tipo de

De acuerdo con una secuencia de procesamiento específica, la etapa de calentamiento del sustrato para la segunda, baja temperatura se realiza como una etapa de sinterización posterior a la etapa de calentamiento local de las zonas parciales del sustrato que se modela a la primera, alta temperatura usa un rayo láser. En otras palabras, primero, el adulterante del primer tipo de conductividad se activa localmente mediante el calentamiento de las zonas parciales respectivas que usan el rayo láser y, a continuación, en una etapa de calentamiento posterior, se activan los adulterantes del segundo tipo de conductividad. En esto, la segunda etapa de calentamiento puede ser una etapa de calentamiento que, en una secuencia de procesamiento del semiconductor típica, se realiza de todos modos a fin de que, por ejemplo, las capas de metalización de sinterización finalmente se apliquen al sustrato semiconductor para formar contactos eléctricos. Por consiguiente, para la generación de la superficie modelada después de la implantación de los adulterantes de ambos tipos de conductividad, sólo una etapa de procesamiento adicional, es decir, la etapa que localmente activa el adulterante del primer tipo de conductividad con el uso del rayo láser, puede ser necesaria, mientras que la etapa de activación del adulterante de la segunda conductividad puede

combinarse con una etapa de sinterización que se realiza típicamente cerca del final de una secuencia de procesamiento.

Tiene que tenerse en cuenta que los aspectos y las realizaciones de la presente invención se describen en el presente documento con referencia a distintos temas. En particular, algunas características se describen con referencia al método para la producción del dispositivo semiconductor, mientras que otras características se describen con referencia al propio dispositivo semiconductor. Sin embargo, un experto en la materia deducirá a partir de lo anterior y la siguiente descripción que, a menos que se notifique otra cosa, además de cualquier combinación o características que pertenezcan a un tipo de tema también se considera que se describe con esta solicitud cualquier combinación entre las características relativas a diferentes temas, en particular entre las características de los dispositivos semiconductores y las características del método para la producción de tal dispositivo.

### Breve descripción de los dibujos

20

25

30

45

50

55

60

65

15 Las realizaciones de la invención se explicarán con más detalle en el siguiente texto con referencia a los dibujos adjuntos en los que:

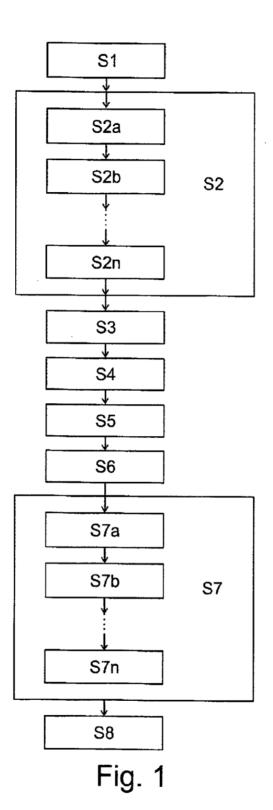

La figura 1 muestra un diagrama de flujo que describe un método para producir un dispositivo semiconductor de acuerdo con una realización de la presente invención.

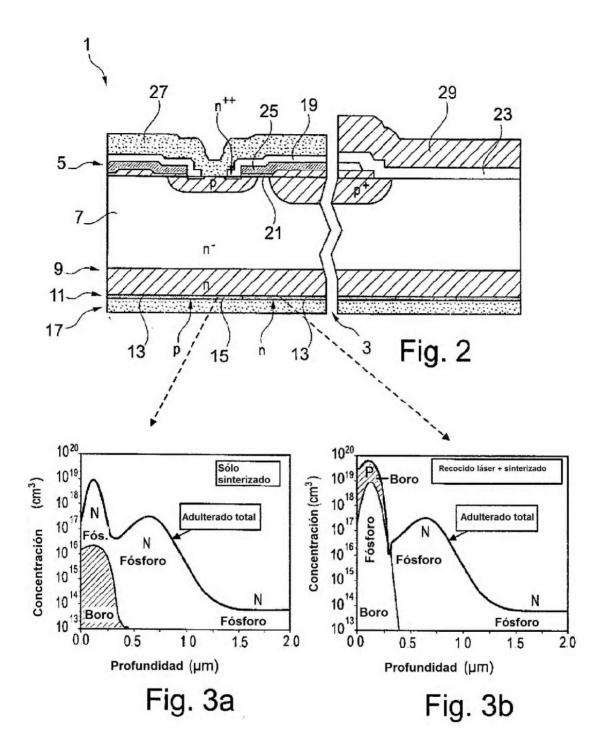

La figura 2 muestra un dispositivo semiconductor ejemplar que tiene una superficie posterior modelada que comprende las zonas de tipo-n y las zonas de tipo-p.

La figura 3a muestra un perfil de difusión típico en un lateral posterior del dispositivo semiconductor de la figura 2 que tiene un adulterante de tipo-n en una zona cercana a la superficie posterior generado con un método de acuerdo con una realización de la presente invención.

La figura 3b muestra un perfil de difusión típico en un lateral posterior del dispositivo semiconductor de la figura 2 que tiene un adulterante de tipo-p en una zona cercana a la superficie posterior generado con un método de acuerdo con una realización de la presente invención.

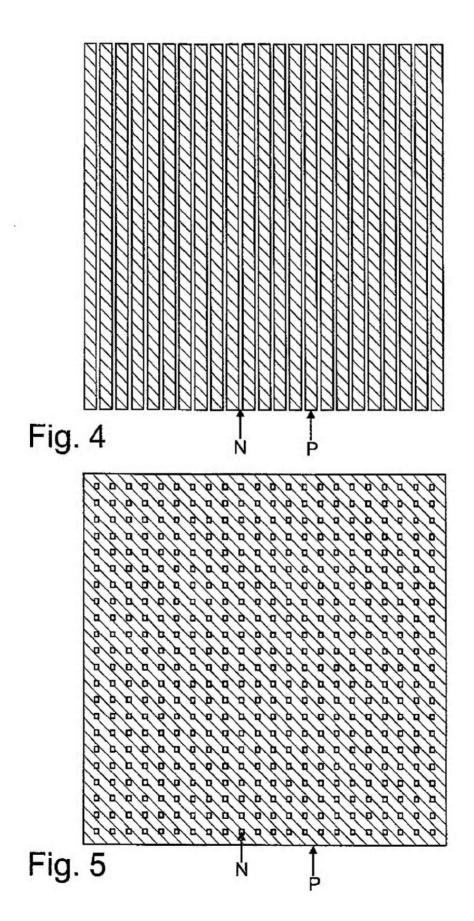

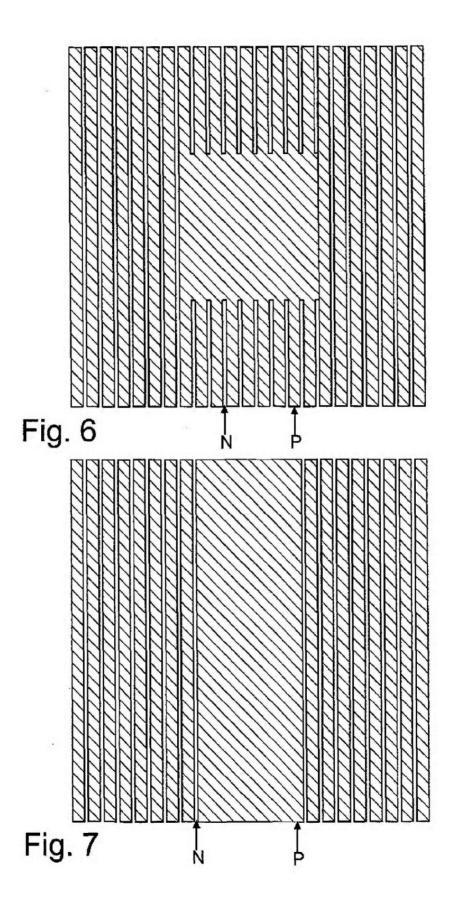

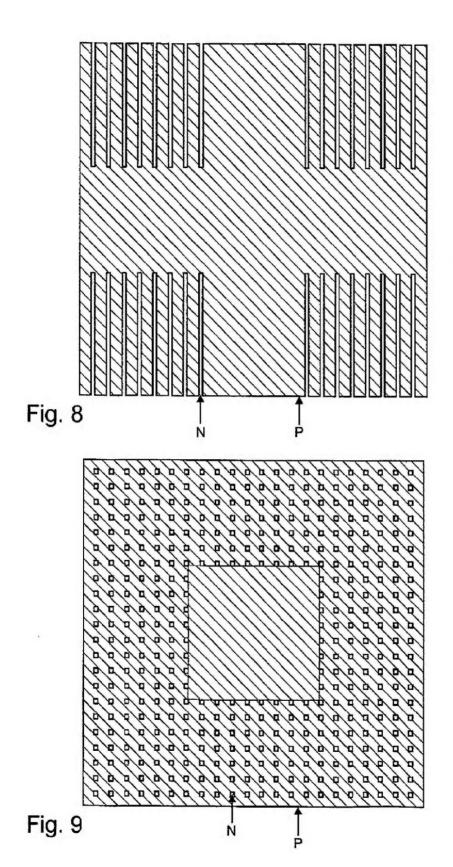

Las figuras 4 a 9 muestran las vistas superiores sobre las superficies modeladas en los laterales posteriores de diversos dispositivos semiconductores.

Los símbolos de referencia usados en las figuras y su significado se resumen en la lista de símbolos de referencia adjunta en el presente documento. Los dibujos son sólo esquemáticos y no a escala. Por lo general, se dan los mismos símbolos de referencia a las partes iguales o semejantes en funcionamiento. Las realizaciones descritas se entienden como ejemplos y no limitan la invención.

# 40 Modos de llevar a cabo la invención

Con respecto al diagrama de flujo mostrado en la figura 1, se describirá una secuencia de procesamiento para producir un dispositivo semiconductor tal como un RC-IGBT. La secuencia de procesamiento comprende las etapas del proceso para la generación de una superficie modelada que comprende al menos una zona del tipo-n y por lo menos una zona de tipo-p en un mismo lateral de un sustrato semiconductor de acuerdo con una realización de la presente invención.

Primero, se proporciona un sustrato semiconductor tal como una oblea de silicio (etapa S1). En este sustrato semiconductor, se realizan una pluralidad de etapas de procesamiento (la etapa 2 que incluye una pluralidad de subetapas S2a, S2b,..., S2n) con el fin de generar las estructuras del tamaño anterior del dispositivo semiconductor para preparase como diversas zonas adulteradas, capas dieléctricas y capas de metalización.

Después de que se complete el procesamiento del lateral anterior del dispositivo como los dispositivos del estado de la técnica convencional, el sustrato semiconductor puede estar diluido opcionalmente para un espesor final, por ejemplo, mediante molienda y/o grabado (etapa S3).

A continuación, para formar las estructuras laterales posteriores del dispositivo semiconductor, los iones de fósforo proporcionan en este caso el adulterante del segundo tipo de conductividad, es decir, una conductividad tipo-n, se implantan los iones en toda la superficie lateral posterior del sustrato de silicio (etapa S4) con una dosis de implantación típica que varía desde 1 x 10<sup>12</sup> cm<sup>-2</sup> hasta 1 x 10<sup>16</sup> cm<sup>-3</sup>. Las energías típicas de implantación varían desde 50 keV hasta 600 keV.

Más tarde, los iones de boro que forman en este caso el adulterante del primer tipo de conductividad, es decir, de la conductividad de tipo-p, se implantan en todo el lateral posterior del sustrato de silicio (etapa S5). Las dosis de implantación típicas varían desde 1 x 10<sup>13</sup> cm<sup>-3</sup> hasta 1 x 10<sup>16</sup> cm<sup>-3</sup>. Las energías de implantación típicas varían desde 5 keV hasta 200 keV. Puede que tengan que optimizarse las energías y las dosis de ambas especies para el

siguiente proceso de activación del adulterante.

10

15

20

25

30

35

40

45

50

55

A continuación, se aplica el recocido láser (etapa S6) de una manera que sólo las zonas que forman los futuros ánodos del IGBT, es decir, las zonas de tipo-p en la superficie lateral posterior del sustrato, se exponen a un rayo láser enfocado. El rayo láser puede proporcionarse mediante una exploración de luz verde (~520 nm) un láser de tipo-YAG que tiene una densidad de potencia de láser típica entre 1 y 4 J/cm² con una duración de la pulsación de 200 - 600 ns y una anchura de tamaño de punto típicamente de alrededor de 40 μm. Como alternativa, puede usarse un láser ultravioleta exciplex pulsado (~308 nm) que tiene una densidad de potencia del láser típica de entre 1 - 7 J/cm² con una duración de la pulsación de 100 -200 ns y un tamaño del punto de hasta 1 cm². Debido a tal irradiación láser, una zona delgada que tiene típicamente un espesor de 20 - 1000 nm para el láser verde y de 10 - 20 nm el láser exciplex por debajo de la superficie irradiada, se calienta temporalmente a temperaturas muy elevadas de 900 - 1000°C y de este modo puede incluso fundirse. Así, los iones de boro previamente implantados pero aún no activados pueden activarse localmente en las zonas irradiadas. Por consiguiente, las zonas que forman los futuros ánodos (zonas del tipo-p) pueden estar formadas por boro altamente activado por medio del rayo láser aplicado selectivamente, mientras que aquellas zonas de los futuros cátodos del IGBT no se exponen al rayo láser.

A continuación, las etapas de procesamiento adicionales (la etapa S7, que puede incluir una pluralidad de subetapas S7a, S7b,..., S7N) pueden realizarse, por ejemplo, para formar una pila de varias capas de metal que formen un contacto lateral posterior del dispositivo semiconductor final.

Así, los contactos de metal depositados después del recocido láser pueden, a continuación, sinterizarse a temperaturas por debajo de 550 °C. Cuando el fósforo previamente implantado en la superficie lateral posterior puede significativamente activarse ya a 400 - 500 °C, tal etapa de sinterización (etapa S8) puede servir, al mismo tiempo, para activar el adulterante fósforo con el fin de generar con ello las zonas catódicas del dispositivo semiconductor. Sin embargo, cuando la activación del boro es baja a bajas temperaturas entre 400 y 500 °C e incluso cae al aumentar la temperatura hasta 700 °C para aumentar de nuevo por encima de 900 °C, la etapa de sinterización de baja temperatura no puede activar totalmente el boro implantado. La activación total del boro sólo se puede conseguir mediante el calentamiento hasta, por ejemplo, 900 - 1000°C (o superior en el caso de fusión por rayo láser) como es el caso de la etapa de activación del recocido láser (etapa S6) descrita anteriormente.

Por consiguiente, finalmente, se puede obtener un dispositivo semiconductor con una superficie lateral posterior modelada. Debido a la mayor concentración de iones de boro en comparación con la concentración de iones de fósforo después de las etapas de implantación (etapas S4, S5), en las posiciones de activación de boro aumentadas, los aceptantes de boro creados pueden compensar a los donantes de fósforo. Para conseguir este efecto, las dosis de implantación y las energías de ambos, la implantación del boro y del fósforo, requieren de un diseño adecuado y, por lo tanto, puede tener que optimizarse.

En referencia a las figuras 2, 3a y 3b, se describirá un dispositivo 1 semiconductor en la forma de un IGBT que tiene una superficie 3 modelada en su lateral posterior, puesto que puede generarse por un método de producción de acuerdo con una realización de la presente invención.

En un lateral 5 anterior de un sustrato 7 semiconductor proporcionado por una oblea de silicio, una pluralidad de diferentes zonas adulteradas n, n<sup>++</sup>, p, p<sup>+</sup>, p<sup>-</sup> están formadas por técnicas de difusión y/o de implantación. Además, se forman una pluralidad de capas dieléctricas 19, 21, 23, tales como una capa de PSG (fósforo-silicato-vidrio), una capa de óxido de puerta y/o una capa de SiN (Nitruro de silicio), capas 25 de semiconductores tales como una capa poli (silicio policristalino) y/o una capa SIPOS (silicio policristalino semiaislado), y/o capas 27 de metal tales como una capa de Al (aluminio) y/o una capa de Ni (níquel) y posiblemente capas adicionales tales como una capa 29 de pasivación fabricada de poliamida. Todas estas capas y sus respectivas etapas de producción pueden ser la técnica anterior. Por consiguiente, la estructura de tamaño anterior del IGBT puede ser convencional y puede procesarse antes de procesar el lateral posterior del IGBT.

En el lateral 9 posterior del sustrato 7 semiconductor, se pueden generar varias capas de adulterante n, n<sup>+</sup> y p<sup>+</sup>. En particular, cerca de una superficie lateral posterior del sustrato 7 semiconductor, se puede proporcionar una capa 11 delgada superficial a la que se han implantado tanto, los iones de boro y los iones de fósforo. A partir de esta capa 11, se pueden generar tanto, una zona 13 de tipo-n<sup>+</sup> como una zona 15 de tipo-p<sup>+</sup>, dependiendo de las etapas del proceso realizadas después de la implantación de los iones. En esta superficie 3 lateral posterior modelada se aplica con el fin de formar contactos eléctricos, una pila 17 que comprende varias capas de metalización hechas de Al (aluminio), Ti (titanio), Ni (níquel) y/o Ag (plata).

60 El sustrato tiene un espesor de entre 50 y 250 μm. El método propuesto en el presente documento puede ser específicamente adecuado para tales sustratos delgados, ya que proporcionan una caída de bajo voltaje en un estado de encendido (ON).

Como se ha explicado con respecto al diagrama mostrado en la figura 3a, se puede proporcionar una zona 13 de tipo-n<sup>+</sup> mediante la activación sólo de los átomos de fósforo. Estas zonas 13 se envían a una etapa de sinterizado a aproximadamente 500 °C solamente y los átomos del boro implantado en estas zonas 13 parciales nunca

experimentan altas temperaturas de más de 900 °C. Por lo tanto, no se activan una mayor parte de los átomos del boro implantado en una zona superficial delgada con una profundidad de aproximadamente 400 nm. Mientras que sólo se activa en esta zona una menor parte de los átomos de boro con una concentración de menos de 3 x  $10^{16}$  cm<sup>-3</sup>, se activan la mayor parte de los átomos de fósforo implantados que tienen una concentración de adulterante de más de 2 x  $10^{17}$  cm<sup>-3</sup>. De esta manera, el tipo de conductividad resultante en esta zona 13 es la conductividad de tipo-n.

Una zona 15 adyacente parcial se ha irradiado con un rayo láser durante una etapa de recocido láser y de este modo se ha calentado temporalmente a temperaturas por encima de 900 °C. Como se describió con respecto al diagrama mostrado en la figura 3b, los átomos de boro implantados en la zona delgada superficial están, por lo tanto, activados casi por completo. Por consiguiente, la concentración de adulterante de boro activo alcanza valores de hasta más de 2 x 10<sup>19</sup> cm<sup>-3</sup> y por tanto es posible compensar el exceso del adulterante de fósforo con concentraciones de menos de 1 x 10<sup>19</sup> cm<sup>-3</sup> en esta zona superficial. Por consiguiente, en las áreas 15 parciales después de haberse sometido tanto, a una etapa de recocido láser a alta temperatura como a una etapa de sinterización a baja temperatura etapa, se formarán zonas de tipo-p<sup>+</sup> en la superficie lateral posterior del sustrato 7 semiconductor.

Las figuras 4 a 9 muestran las vistas superiores sobre las superficies 3 modeladas en los laterales posteriores de diversos dispositivos semiconductores. La figura 4 muestra un diseño de banda RC-IGBT. La figura 5 muestra un diseño de celda RC-IGBT. Las figuras 6 a 8 muestran diseños híbridos BIGT. La figura 9 muestra un diseño de celda BIGT. Las zonas tipo-p (indicadas como zonas sombreadas) son las zonas en las que se han activado con el rayo láser los adulterantes tipo-p.

Por último, cabe mencionar que el método descrito anteriormente puede combinarse con otro método de etapas como la implantación de hidrógeno y que la geometría de las zonas de tipo-p activadas por el rayo láser pueden seleccionarse por un software de control de la fuente del rayo láser y, por lo tanto, puede ser muy flexible con un coste mínimo. El método propuesto tiene por objeto cubrir todas y cada una de las adaptaciones de las variaciones de diversas realizaciones, por ejemplo, el procesamiento de los "ánodos cortos" de IGBT para reducir las pérdidas de conmutación, reducir las oscilaciones o diodos, etc.

Mediante el método como se ha descrito anteriormente se crea un dispositivo semiconductor con una zona 15 parcial p-adulterada y una zona 13 n-adulterada. Sin embargo, también es posible intercambiar los tipos de adulterante de estas zonas, es decir, tener un n-adulterante como el primer tipo de conductividad y tener un p-adulterante como el segundo tipo de conductividad. En este caso, una zona 15 parcial n-adulterada se activa localmente mediante el calentamiento de las zonas parciales de la superficie a una primera temperatura con el uso de un rayo láser y una zona 13 p-adulterada mediante el calentamiento del sustrato a una cierta temperatura que es menor que la primera temperatura.

Típicamente, para la creación de la zona 15 y/o la zona 13 parcial se aplica un adulterante para cada zona. Sin embargo, también es posible aplicar una pluralidad de tales adulterantes. Como un ejemplo, esto puede hacerse mediante la aplicación de adulterantes de boro y aluminio como adulterantes del primer tipo de conductividad y/o fósforo y arsénico como adulterantes del segundo tipo de conductividad.

# Lista de signos de referencia

15

20

25

30

35

|    | Lista de signos de referencia |                                        |

|----|-------------------------------|----------------------------------------|

| 45 |                               | -                                      |

|    | 1                             | dispositivo semiconductor              |

|    | 3                             | superficie de modelado                 |

|    | 5                             | superficie anterior                    |

|    | 7                             | sustrato del semiconductor             |

| 50 | 9                             | superficie posterior                   |

|    | 11                            | capa superficial                       |

|    | 13                            | zona del segundo tipo de conductividad |

|    | 15                            | zona del primer tipo de conductividad  |

|    | 17                            | pila de contacto de metal              |

| 55 | 19                            | capa dieléctrica                       |

|    | 21                            | capa dieléctrica                       |

|    | 23                            | capa dieléctrica                       |

|    | 25                            | capa del semiconductor                 |

|    | 27                            | capa de metal                          |

| 60 | 29                            | capa de pasivación                     |

#### REIVINDICACIONES

- 1. Un método para producir un dispositivo (1) semiconductor con una superficie (3) modelada que comprende al menos una zona (15) parcial adulterada con un adulterante de un primer tipo de conductividad y al menos una zona (13) adulterada con un adulterante de un segundo tipo de conductividad en el mismo lateral de un sustrato (7) semiconductor, comprendiendo el método:

- implantar el adulterante del primer tipo de conductividad e implantar el adulterante del segundo tipo de conductividad en la superficie (3) a modelar;

- activar localmente el adulterante del primer tipo de conductividad mediante el calentamiento local de al menos la zona (15) parcial de la superficie para que se modele a una primera temperatura con el uso de un rayo láser;

- activar el adulterante del segundo tipo de conductividad mediante el calentamiento del sustrato (7) a una segunda temperatura que es menor que la primera temperatura,

en el que el adulterante del primer tipo de conductividad se implanta y se activa en las zonas (15) parciales para una concentración de adulterante mayor que el adulterante del segundo tipo de conductividad, de esta manera, se compensa en exceso localmente el adulterante del segundo tipo de conductividad.

- 20 2. El método de la reivindicación 1, en el que el adulterante del primer tipo de conductividad es al menos un adulterante de tipo-p formado de boro y de aluminio.

- 3. El método de una de las reivindicaciones 1 a 2, en el que el adulterante del segundo tipo de conductividad es al menos un adulterante de tipo-n formado de fósforo y arsénico.

- 4. El método de una de las reivindicaciones 1 a 3, en el que la primera temperatura está por encima de 850 °C.

- 5. El método de una de las reivindicaciones 1 a 4, en el que la segunda temperatura está por debajo de 650 °C.

- 6. El método de una de las reivindicaciones 1 a 5, en el que el adulterante del primer tipo de conductividad se implanta con al menos una de una dosis que va desde 1e13/cm² hasta 1e16/cm² y una energía que va desde 5 keV hasta 200 keV.

- 7. El método de una de las reivindicaciones 1 a 6, en el que el adulterante del segundo tipo de conductividad se implanta con al menos una de una dosis que va desde 1e12/cm² hasta 1e16/cm² y una energía que va desde 50 keV hasta 600 keV.

- 8. El método de una de las reivindicaciones 1 a 7, en el que el adulterante del primer tipo de conductividad se implanta a una profundidad menor que el adulterante del segundo tipo de conductividad.

- 9. El método de una de las reivindicaciones 1 a 8, en el que las áreas en las que se implanta el adulterante del primer tipo de conductividad y las áreas en las que se implanta el adulterante del segundo tipo de conductividad al menos se superponen parcialmente.

- 45 10. El método de una de las reivindicaciones 1 a 9, en el que la etapa del proceso de la activación local del adulterante del primer tipo de conductividad se realiza mediante la exploración de un rayo láser de un aparato de recocido láser a lo largo de las zonas parciales que se activan localmente.

- 11. El método de la reivindicación 10, en el que una energía láser y una velocidad de exploración se adaptan de tal

manera que una capa (11) superficial del sustrato se calienta temporalmente a la primera temperatura, la parte superficial tiene una profundidad de menos de 1 μm.

- 12. El método de una de las reivindicaciones 1 a 11, en el que la etapa del proceso de calentamiento del sustrato (7) a la segunda temperatura se realiza como una etapa de sinterización posterior a la etapa de calentamiento local de las zonas (15) parciales de la superficie (3) que se modelan a la primera temperatura con el uso del rayo láser.

- 13. El método de la reivindicación 12, que comprende además las etapas de proceso para la generación de las estructuras laterales anteriores, en el que las etapas del proceso de implantación y activación se realizan después de las etapas del proceso para la generación de las estructuras laterales anteriores.

- 14. El método de una de las reivindicaciones 1 a 13, en el que el dispositivo semiconductor (1) es un transistor bipolar de puerta aislada de conducción inversa (RC-IGBT) y un transistor bipolar de puerta aislada bimodal (BIGT) y en el que el lateral que tiene el modelado es un lateral posterior del dispositivo semiconductor (1).

- 15. El método de una de las reivindicaciones 1 a 13, en el que el dispositivo semiconductor (1) es un diodo.

15

10

5

25

40

60