OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 388 085

51 Int. Cl.: H03L 7/189

(2006.01)

| 1 4 | $\sim 1$ |  |

|-----|----------|--|

|     |          |  |

|     |          |  |

|     |          |  |

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- 96 Número de solicitud europea: 08727967 .5

- 96 Fecha de presentación: 18.01.2008

- Número de publicación de la solicitud: 2115871

Fecha de publicación de la solicitud: 11.11.2009

- 54 Título: Procedimiento y aparato para el ajuste dinámico de la escala de frecuencias de bucles de sincronización de fase para microprocesadores

- 30 Prioridad: 19.01.2007 US 624995

73) Titular/es:

QUALCOMM INCORPORATED ATTN: INTERNATIONAL IP ADMINISTRATION 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121, US

- Fecha de publicación de la mención BOPI: 08.10.2012

- 72 Inventor/es:

DAI, Liang; LEWIS, Brandon Wayne; BRIDGES, Jeffrey Todd y CHEN, Weihua

- Fecha de la publicación del folleto de la patente: **08.10.2012**

- (74) Agente/Representante:

Carpintero López, Mario

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

Procedimientos y aparato para el ajuste dinámico de la escala de frecuencias de bucles de sincronización de fase para microprocesadores

#### Campo de la divulgación

5 La presente divulgación versa, en general, acerca del campo de los bucles de sincronización de fase para cronometrar microprocesadores y, en particular, acerca de procedimientos y un aparato para el ajuste dinámico de la escala de frecuencias de bucles de sincronización de fase para microprocesadores.

#### **Antecedentes**

- Los microprocesadores llevan a cabo tareas de cálculo en una amplia variedad de aplicaciones. Casi siempre es deseable un rendimiento mayor del procesador para permitir una operación más rápida y/o un aumento de la funcionalidad mediante cambios en el soporte lógico. En muchas aplicaciones integradas, tales como dispositivos electrónicos portátiles, la conservación de la energía también es una meta importante en el diseño y la implementación de los procesadores.

- Muchos procesadores modernos emplean técnicas de ajuste dinámico de la escala de tensión y frecuencia que incluyen variar los niveles operativos de frecuencia y tensión de un procesador dependiendo de la demanda de proceso para ahorrar en el consumo de energía. Cuando un procesador funciona con una frecuencia de sincronización más lenta, pueden utilizarse menores tensiones operativas para cargar los circuitos, lo que da como resultado una utilización de menor potencia.

- Una técnica convencional para variar la frecuencia incluye un bucle de sincronización de fase (PLL) programable que es ejecutado a una frecuencia, suspendido en su operación, reprogramado para que opere a una frecuencia diferente mientras el PLL está suspendido y reiniciado a la nueva frecuencia deseada. Este enfoque puede causar fluctuaciones grandes de corriente entre las frecuencias operativas, lo que da como resultado la necesidad de utilizar una fuente de alimentación más robusta. También puede dar como resultado la detención de la operación del procesador, al ser impulsado por la salida del PLL durante muchos ciclos durante las fases de operación de reprogramación y reinicio.

- Los PLL contienen osciladores cuya frecuencia puede ser controlada por la tensión o la corriente. Los osciladores están diseñados para operar dentro de una intervalo diseñado de frecuencias operativas. Por ejemplo, un oscilador puede estar diseñado para operar entre 400 MHz y 800 MHz, mientras que otro oscilador puede estar diseñado para operar entre 800 MHz y 1200 MHz. Existe una solución de compromiso en rendimiento si alguien fuese a diseñar un oscilador que operase en el intervalo entre 400 MHz and 1200 MHz. El ancho del intervalo operativo de un oscilador es directamente proporcional a sus características de su fluctuación negativa. Por lo tanto, cuando mayor sea el intervalo operativo de un oscilador particular, mayores serán sus correspondientes características de fluctuación. Por lo tanto, existe la necesidad de generar frecuencias variantes de reloj en un amplio intervalo de frecuencias que tenga una características de fluctuación baja.

- El artículo "W-band synthesised signal generator using fundamental voltage controlled oscillators", de Molnar J A et. al (publicado el 22 de septiembre de 1997), describe un generador "mejorado" de señales sintetizadas de la banda W. El generador de señales incluye una sección de osciladores, una "sección de PLL" y una sección de control de modulación/salida.

- El documento WO 01/63783 A describe una técnica para llevar a cabo saltos de frecuencia basados en ranuras de tiempo en un sistema de transmisión de radio. La técnica usa dos sintetizadores de frecuencia, que están sintonizados alternativamente en canales de frecuencias de radio seleccionadas por adelantado de las respectivas ranuras de tiempo y que son usados alternativamente por un transceptor del sistema de transmisión de radio para transformar ráfagas de la banda base a los canales de frecuencias de radio seleccionadas.

- El documento US 2005/104665 A1 describe técnicas para seleccionar y calibrar un oscilador de una pluralidad de osciladores controlados por tensión para proporcionar una frecuencia seleccionada.

El documento US-A-5838205 describe un sistema PLL 200 que incluye dos PLL intercalados entre sí. El primer PLL incluye un primer detector 202 de fase, un primer VCO 206 y divisores programables 208 y 210 de frecuencias. El segundo PLL incluye un segundo detector 212 de fase, un segundo VCO 216 y divisores programables 218 y 220 de frecuencias.

### 50 Resumen

30

En las reivindicaciones independientes se exponen aspectos de la presente invención.

En un ejemplo, se da a conocer un bucle de sincronización de fase que emplea una pluralidad de complejos de osciladores. El bucle de sincronización de fase incluye a salida de reloj y una pluralidad de complejos de osciladores

operables para generar señales de salida. El bucle de sincronización de fase incluye, además, lógica de control que está configurada para acoplar selectivamente una señal de salida de uno de los osciladores de la pluralidad de complejos de osciladores a la salida de reloj.

- En otro ejemplo, el bucle de sincronización de fase incluye una entrada para recibir una señal de referencia, una salida de reloj y una vía de retroacción para sincronizar una señal en fase con la señal de referencia. El bucle de sincronización de fase incluye, además, una pluralidad de complejos de osciladores operables para generar señales de salida y acoplarse por separado a la vía de retroacción y la salida de reloj. El bucle de sincronización de fase también incluye lógica de control configurada para acoplar selectivamente una señal de salida de un primer oscilador de la pluralidad de complejos de osciladores a la salida de reloj.

- 10 En otro ejemplo, se da a conocer un procedimiento de variación de la frecuencia de la salida de un bucle de sincronización de fase. En este procedimiento, se introduce una frecuencia deseada a la que se desee que opere una señal de salida del bucle de sincronización de fase. Se desacopla un complejo de osciladores de una vía de retroacción del bucle de sincronización de fase. Se ajusta un control del complejo desacoplado de osciladores para generar una señal como salida para el bucle de sincronización de fase. El complejo de osciladores es acoplado a la 15 vía de retroacción para sincronizar la señal en fase con una señal de referencia cuando la señal tiene una frecuencia dentro del intervalo de la frecuencia deseada. En otro aspecto, se da a conocer un procedimiento de variación de la frecuencia de la salida de un bucle de sincronización de fase. En este procedimiento, un primer complejo de osciladores está acoplado a la salida del bucle de sincronización de fase. El primer complejo de osciladores está desacoplado de una vía de retroacción del bucle de sincronización de fase. Se introduce una frecuencia deseada a 20 la que se desee que opere una señal de salida del bucle de sincronización de fase. Se enciende un segundo complejo de osciladores. El segundo complejo de osciladores es controlado digitalmente para generar una señal en un intervalo de frecuencias que contiene la frecuencia deseada. El primer complejo de osciladores es desacoplado de la salida del bucle de sincronización de fase. El segundo complejo de osciladores es acoplado a la salida del bucle de sincronización de fase.

- Se entiende que otras realizaciones resultarán inmediatamente evidentes para los expertos en la técnica a partir de la siguiente descripción detallada, en la que diversas realizaciones son mostradas y descritas a título de ilustración. Como se captará, la invención es susceptible de otras realizaciones diferentes y sus varios detalles son susceptibles de modificación en diversos otros aspectos, todo sin apartarse de las enseñanzas de la invención. En consecuencia, ha de considerarse que los dibujos y la descripción detallada son de naturaleza ilustrativa y no restrictiva.

### 30 Breve descripción de los dibujos

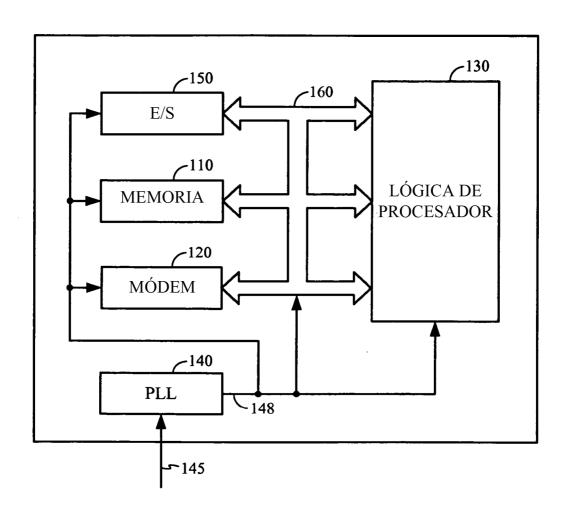

- La Fig. 1 es un diagrama funcional de bloques de un procesador.

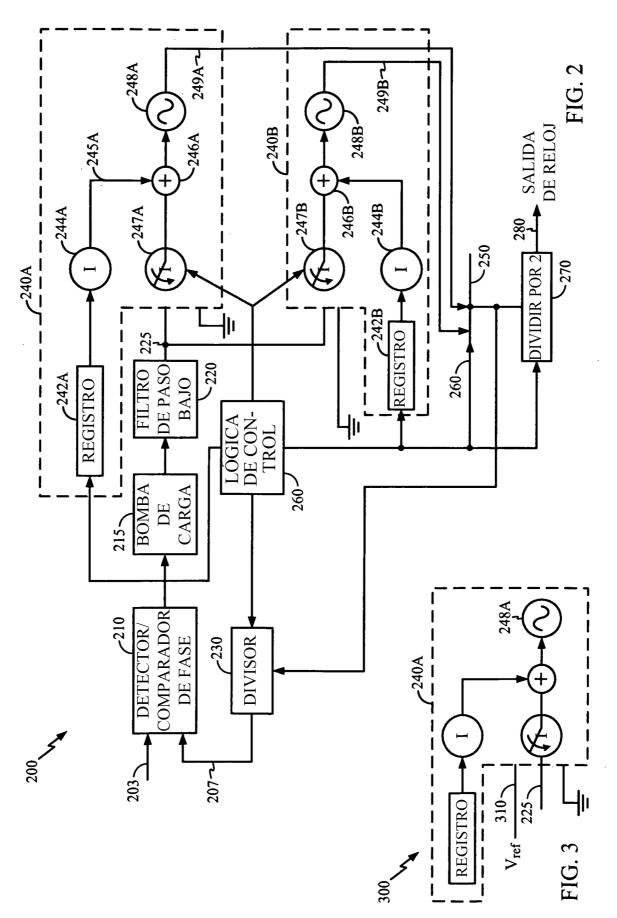

- La Fig. 2 es un ejemplo del bucle de sincronización de fase ilustrado en la Fig. 1.

- La Fig. 3 es una alternativa del complejo de osciladores ilustrado en la Fig. 2.

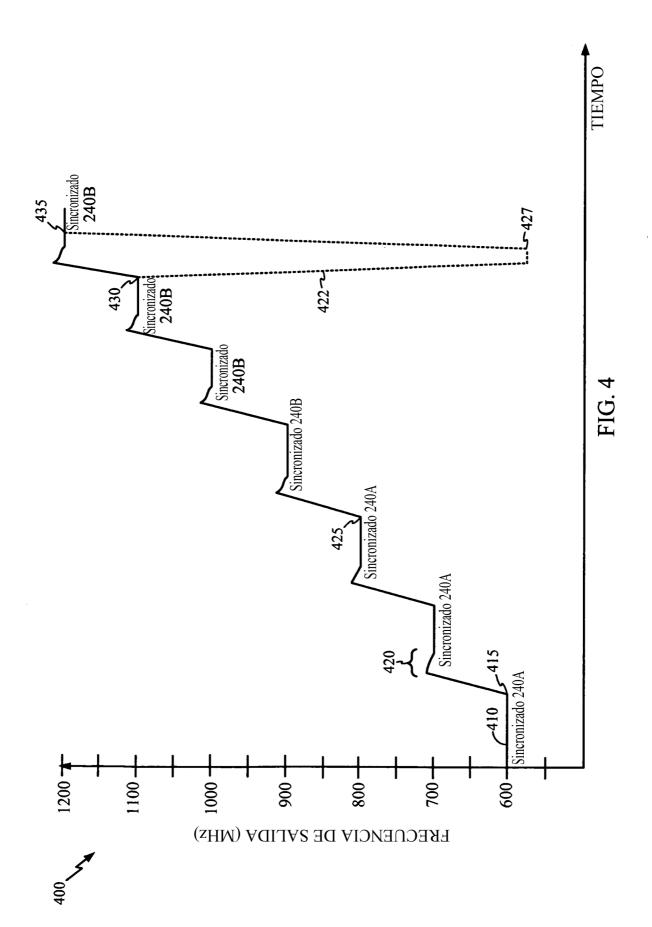

- La Fig. 4 es un gráfico de una señal ejemplar de salida del bucle de sincronización de fase de la Fig. 1 en el tiempo.

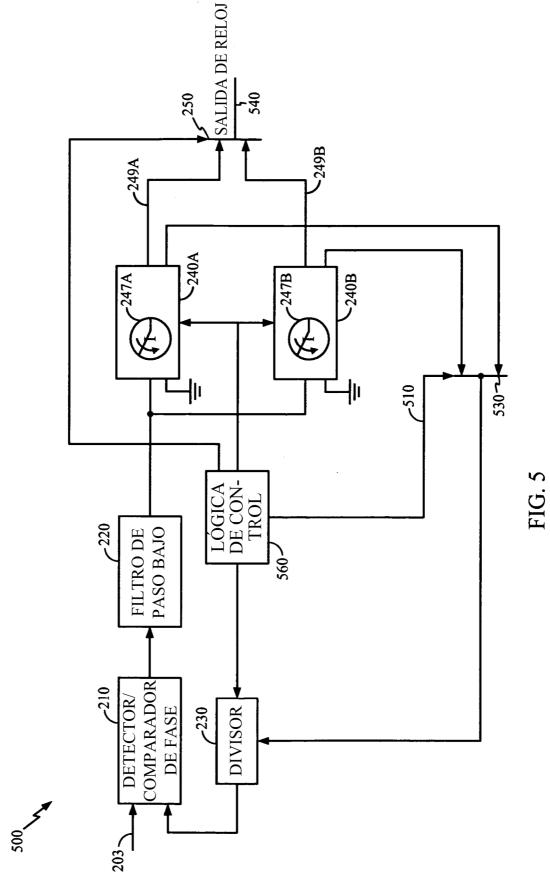

- La Fig. 5 es una realización del bucle de sincronización de fase ilustrado en la Fig. 1 que acopla selectivamente dos osciladores a las vías de retroacción y salida.

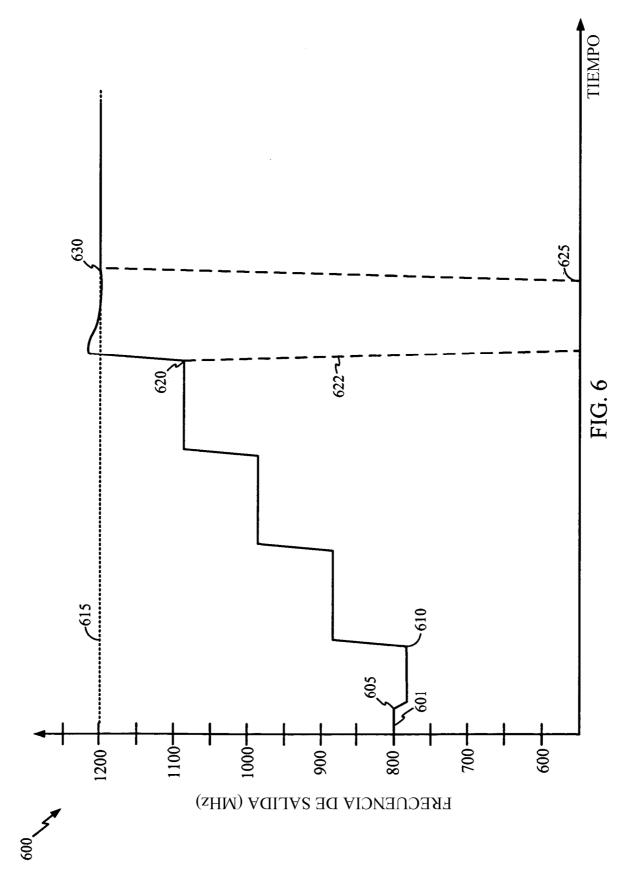

- La Fig. 6 es un gráfico de una señal ejemplar de salida que ilustra una operación de cambio de tensión simple de un bucle de sincronización de fase.

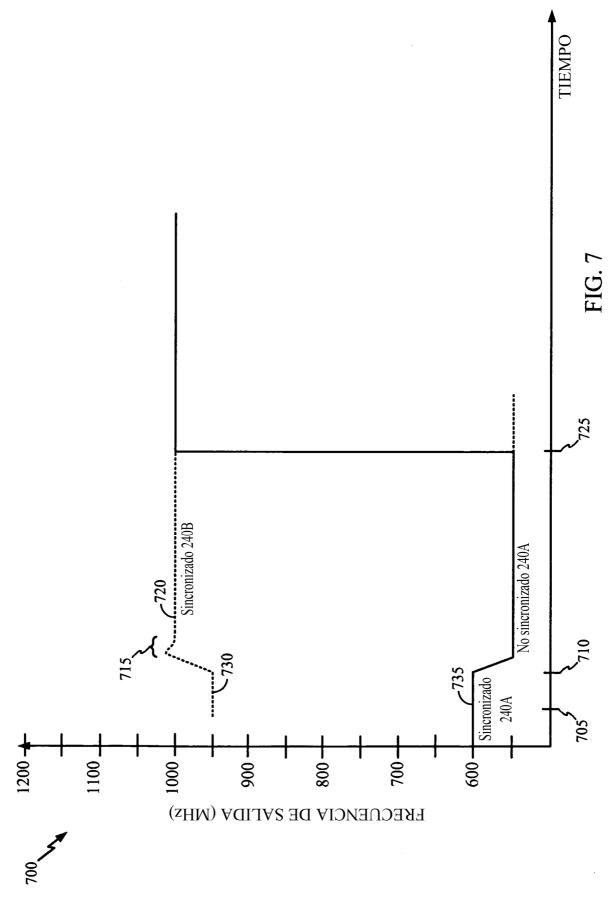

- La Fig. 7 es un gráfico de una señal ejemplar de salida que ilustra una operación de salto de un bucle de 40 sincronización de fase.

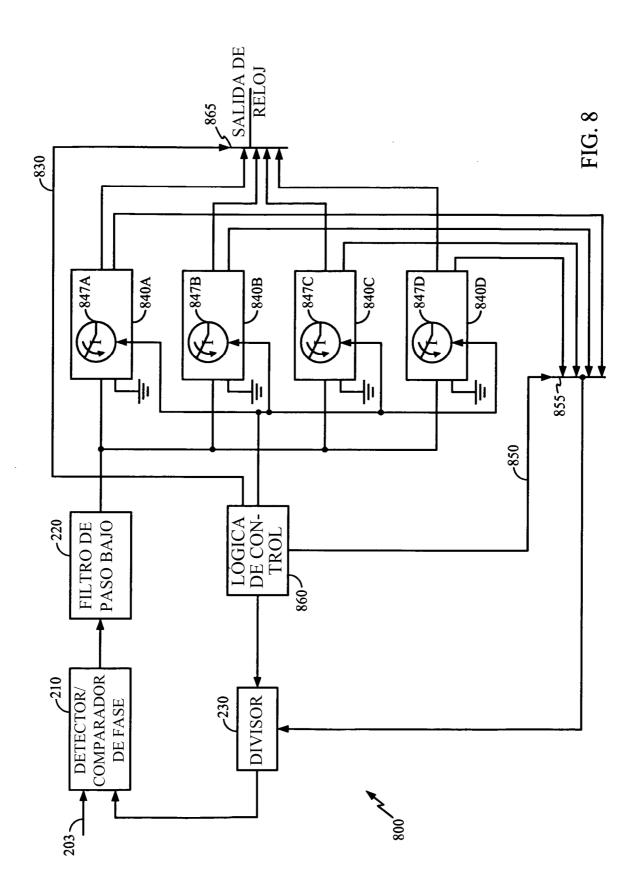

- La Fig. 8 es otra realización del bucle de sincronización de fase ilustrado en la Fig. 1.

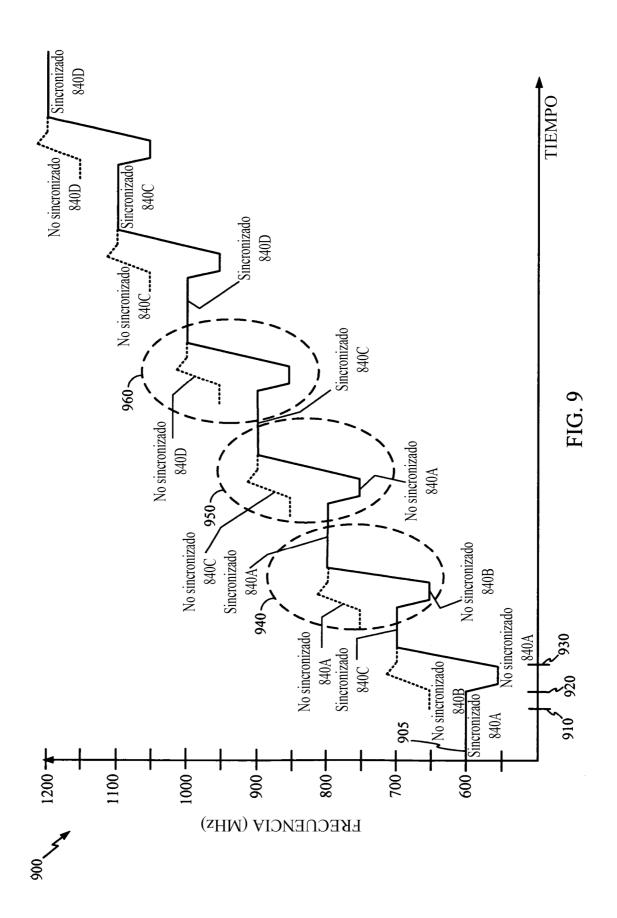

- La Fig. 9 es un gráfico de una señal ejemplar de salida que ilustra una operación de cambio de tensión sincronizado de un bucle de sincronización de fase.

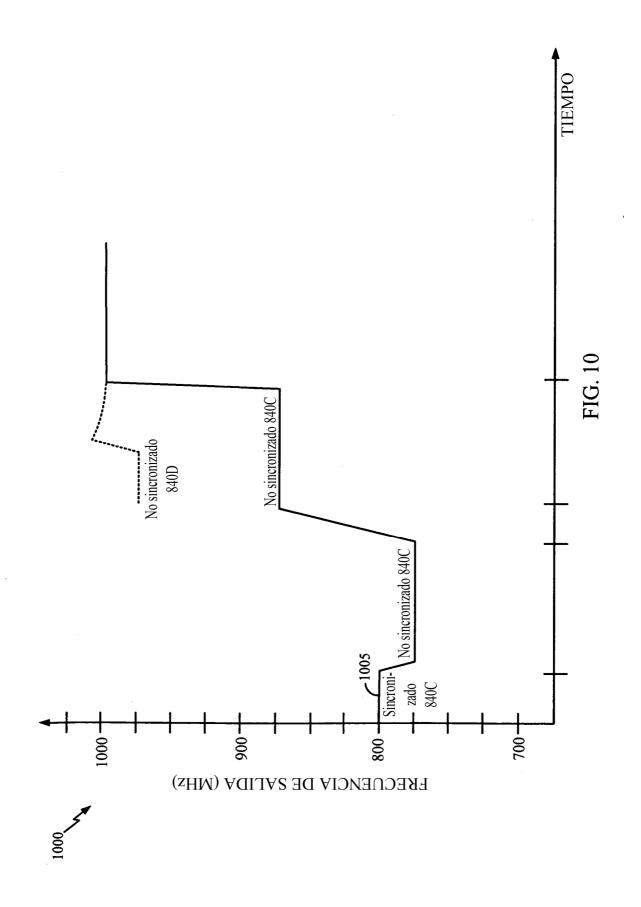

- La Fig. 10 es un gráfico de una señal ejemplar de salida que ilustra una operación de cambio de tensión complejo de un bucle de sincronización de fase.

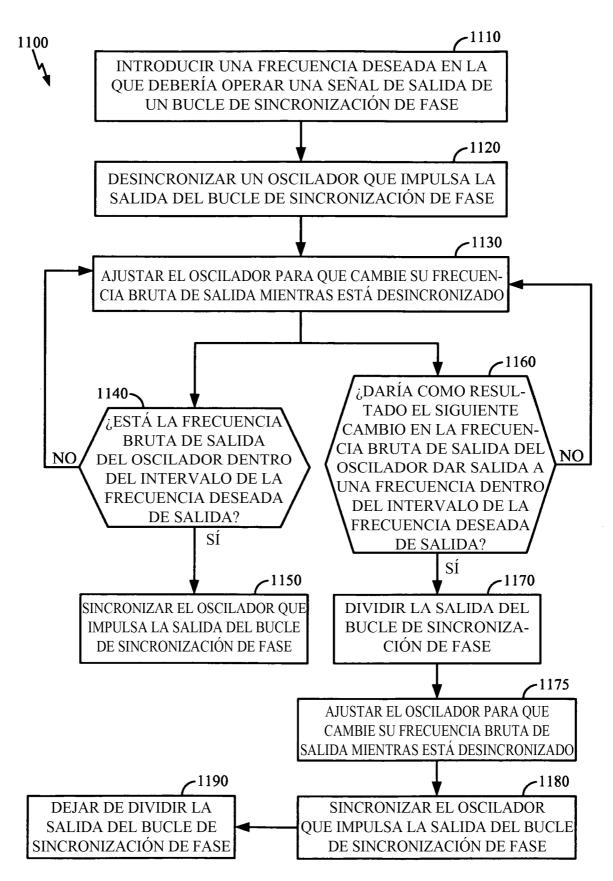

- La Fig. 11 es un diagrama de flujo que ilustra un procedimiento de cambio de tensión simple para variar la frecuencia de la salida de un bucle de sincronización de fase.

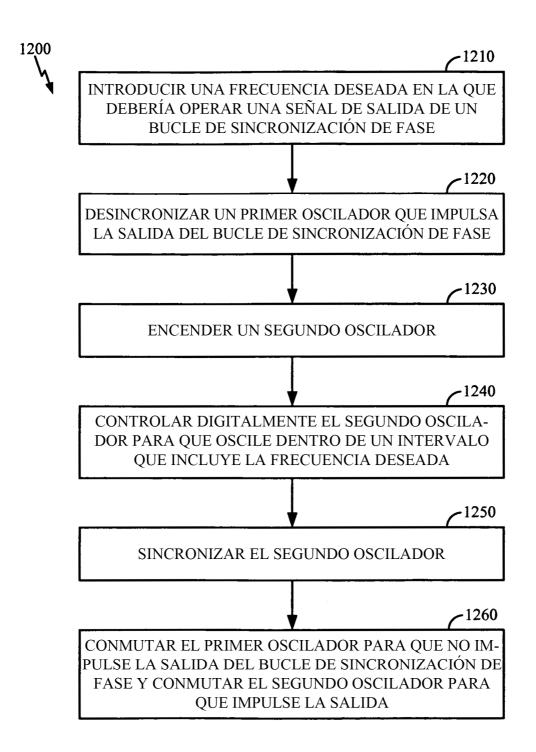

- La Fig. 12 es un diagrama de flujo que ilustra un procedimiento de salto para variar la frecuencia de la salida de un bucle de sincronización de fase.

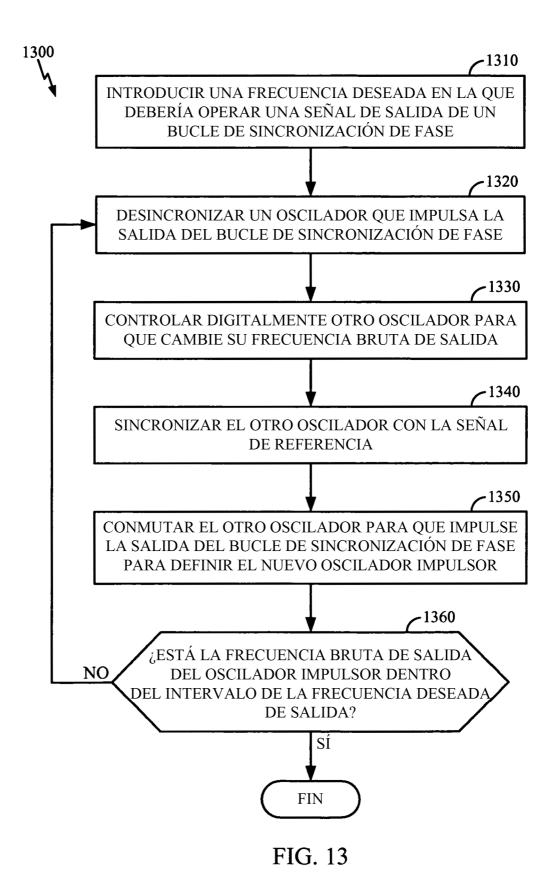

- La Fig. 13 es un diagrama de flujo que ilustra un procedimiento de cambio de tensión sincronizado para variar la frecuencia de la salida de un bucle de sincronización de fase.

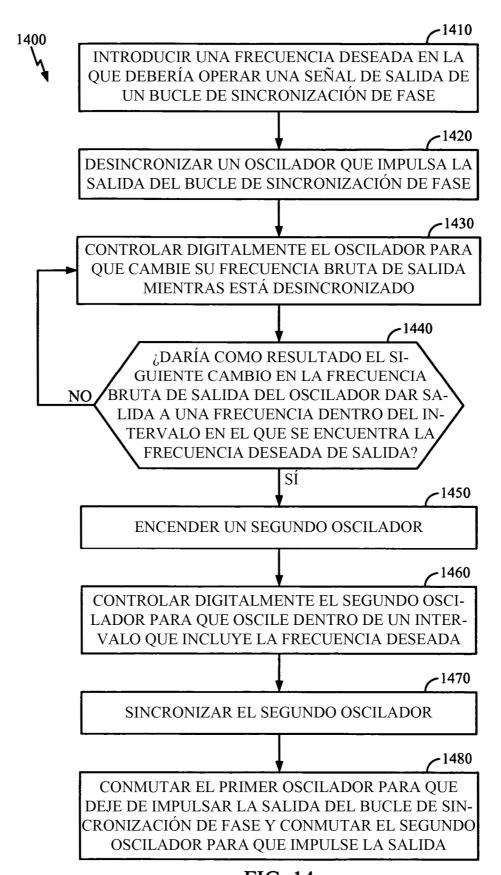

La Fig. 14 es un diagrama de flujo que ilustra un procedimiento de cambio de tensión complejo para variar la frecuencia de la salida de un bucle de sincronización de fase.

### Descripción detallada

10

25

30

35

40

45

50

55

La Fig. 1 representa un diagrama funcional de bloques de un procesador ejemplar 100 en el que las realizaciones pueden ser empleadas. El procesador 100 puede emplearse en dispositivos cableados tales como estaciones base, ordenadores personales (PC) y similares y en dispositivos inalámbricos tales como un teléfono móvil, un ordenador portátil, una agenda electrónica, PC de bolsillo y similares. El procesador 100 incluye un bucle 140 de sincronización de fase (PLL), lógica 130 de procesador, un módem 120, memoria 110 y circuitería 150 de entrada/salida (E/S). El módem 120 recibe señales moduladas y las convierte en señales de banda base. La memoria 110 almacena datos e instrucciones para la lógica 130 de procesador. La lógica 130 de procesador ejecuta instrucciones almacenadas en la memoria 110 y envía datos e información de control a la circuitería 150 de E/S. La circuitería 150 de E/S incluye circuitos que se interconectan con pantallas, dispositivos de audio y similares. La lógica 130 de procesador se comunica con el módem 120, la memoria 110 y la circuitería 150 de E/S por medio de un bus 160 del sistema.

El PLL 140 recibe una señal 145 de reloj de referencia. La señal 145 de reloj de referencia puede ser proporcionada por un cristal oscilante externo al procesador 100. El PLL 140 genera una señal 148 de reloj que es una frecuencia múltiplo de la señal de referencia para activar los dispositivos síncronos tales como la lógica 130 de procesador, el módem 120, la memoria 110, la circuitería 150 de E/S y el bus 160 del sistema. El PLL 140 es programable y puede variar automáticamente la frecuencia de la señal 148 de reloj dependiendo de las demandas de proceso o de factores ambientales que afecten al procesador 100. El PLL 140 será descrito adicionalmente con la exposición de las Figuras 2-10.

Los expertos en la técnica reconocerán que son posibles numerosas variaciones del procesador 100. Por ejemplo, puede haber más de un bucle de sincronización de fase para controlar por separado diversos elementos dentro del procesador, incluyendo el bus 160 del sistema. Además, pueden omitirse de una realización particular uno o más de los bloques funcionales representados en el procesador 100. Otros bloques funcionales que pueden residir dentro de los componentes del procesador 100 no tienen relación con la divulgación y son omitidos en aras de la claridad. Por ejemplo, la lógica 130 de procesador puede incluir un procesamiento en cadena de etapas múltiples, una memoria tampón de traducción lateral, una memoria intermedia de datos y similares.

La Fig. 2 es un ejemplo del bucle de sincronización de fase ilustrado en la Fig. 1. El PLL 200 incluye un detector de fase/comparador 210, una bomba 215 de carga, un filtro 220 de paso bajo, un divisor 230, lógica 260 de control, complejos 240A-240B de osciladores y un multiplexor 250 sin interferencias. Los complejos 240A-240B de osciladores incluyen los osciladores 248A-240B y ajustan en bruto la frecuencia de salida de los osciladores para que esté dentro de un intervalo de frecuencias seleccionado. En aras de la simplicidad, aquí solo se describirá con detalle el complejo 240A de osciladores, pero el complejo 240B de osciladores, adecuadamente, puede ser similar y emplear componentes similares, salvo que el complejo 240A de osciladores incluye un oscilador 248A controlado por corriente que está graduado para operar en un intervalo de frecuencias de gama baja y que el complejo 240B de osciladores incluye un oscilador 248B controlado por corriente que está graduado para operar en un intervalo de frecuencias de gama alta.

Además, el complejo 240A de osciladores incluye un registro 242A de cinco bits, una fuente 244A de control de la corriente, un sumador 246A y un conmutador controlable 247A. En un ejemplo alternativo, la fuente 244A de control de la corriente y el oscilador 248A controlado por corriente pueden ser sustituidos con una fuente de control de tensión y un oscilador controlado por tensión, dependiendo de la aplicación particular y de las limitaciones del diseño total. El complejo 240A de osciladores está controlado digitalmente, porque la fuente 244A de control de la corriente genera una corriente 245A de polarización en respuesta al valor del registro 242A de cinco bits. El registro 242A de cinco bits se establece por programa y su valor puede cambiarse con base en la carga del procesador, condiciones ambientales o ambas. Un valor particular del registro 242A de cinco bits corresponde a un intervalo particular de frecuencias dentro del cual se desea que opere la salida de reloj del PLL 200. El oscilador 248A controlado por corriente está diseñado para oscilar en el intervalo de gama baja, aproximadamente entre 400 y 800 MHz. A título de ejemplo, dados los treinta y dos valores diferentes del registro 242A de cinco bits y el intervalo operativo de 400 MHz del oscilador 248A, cada valor particular del registro 242A de cinco bits corresponde a un ancho del intervalo de salida de aproximadamente 12,5 MHz. Se hace notar que el tamaño del registro 242A de cinco bits y, por ende, los anchos del intervalo de salida, pueden variar dependiendo de las limitaciones de diseño. Cuando el conmutador controlable 247A está conectado a tierra y, por ejemplo, el valor del registro 242A de cinco bits es dos, se fijará la salida 249A de oscilador del oscilador 248A controlado por corriente a un valor relativamente constante en algún punto entre 425 MHz y 437,5 MHz. La salida 249A del oscilador está acoplada con el multiplexor 250 sin interferencias, que multiplexa las salidas de los complejos 240A y 240B de osciladores.

Similarmente, en lo que respecta al complejo 240B de osciladores que contiene un oscilador 248B diseñado para oscilar en un intervalo de frecuencias más elevado, cuando el conmutador controlable 247B está conectado a tierra y, por ejemplo, el valor del registro 242B de cinco bits es dos, la salida 249B de oscilador del oscilador 248B controlado por corriente fluctuará entre 825 MHz y 837,5 MHz.

Para estabilizar y sincronizar la salida de reloj, se hace pasar la salida de reloj por una vía de retroacción compartida definida por el divisor 230, el detector de fase/comparador 210, la bomba 215 de carga y el filtro 220 de paso bajo. El divisor 230 es programable y divide la salida del multiplexor 250 en una cantidad correspondiente al complejo 240A o 240B de osciladores dividida por una señal 203 de referencia para generar una señal 207 de retroacción.

El detector de fase/comparador 210 recibe como entrada una señal 203 de referencia tal como señal externa 145 y una señal 207 de retroacción. El detector de fase/comparador 210 compara la fase entre la señal externa 203 y la señal 207 de retroacción para generar una señal diferencial. La bomba 215 de carga recibe la señal diferencial y genera una corriente de control. El filtro 220 de paso bajo recibe la corriente de control y atenúa las frecuencias mayores que una frecuencia de corte para aplanar entradas abruptas de control procedentes de la bomba 215 de carga para generar una corriente atenuada 225 de control.

Cuando el complejo 240A de osciladores se acopla al filtro 220 de paso bajo a través del conmutador programable 247A, la corriente atenuada 225 de control se suma, ya sea positiva o negativamente, con la corriente 245A de polarización. La corriente sumada impulsa al oscilador 248A controlado por corriente para que sincronice la señal 249A del oscilador con la señal 203 de referencia. Se hace notar que los conmutadores 247A y 247B están conectados al filtro 220 de paso bajo de una manera mutuamente excluyente. En este ejemplo, resulta una salida sincronizada cuando tanto el correspondiente conmutador de un complejo de osciladores está conectado al filtro 220 de paso bajo como la salida del mismo complejo de osciladores está seleccionada por medio del multiplexor 250 sin interferencias.

15

25

30

35

40

45

50

55

La salida del multiplexor 250 sin interferencias se dirige a través de un circuito opcional 270 de división por dos antes de ser enviada a dispositivos síncronos. El circuito opcional 270 de división por dos excluye la exposición a dispositivos síncronos que pueden no estar diseñados para gestionar frecuencias transitorias de alta velocidad y será descrito en relación con la Fig. 6.

La lógica 260 de control se acopla a los conmutadores 247A-247B y al multiplexor 250 sin interferencias. Para evitar impulsar la salida del bucle de sincronización de fase por múltiples osciladores, la operación de conmutación entre las salidas de los complejos de osciladores es demorada tres o más ciclos de reloj del oscilador. Con este fin, la lógica 260 de control puede incluir una máquina con un número de estados finitos para garantizar que no se producen impulsos cortos ni ciclos cortos cuando se conmutan las salidas de los complejos 240A-240B de osciladores a través del multiplexor 250.

La lógica 260 de control controla los conmutadores 247A-247B independientemente. En particular, la lógica 260 de control determina si conectar los conmutadores 247A-247B a tierra y a la vía de retroacción compartida. La lógica 260 de control también controla el circuito 270 de división por dos durante un procedimiento de cambio de tensión simple de control por rampa del reloj descrito en relación con la Fig. 6. La lógica 260 de control puede controlar opcionalmente el contenido de los registros 242A y 242B para lograr diversos procedimientos de control por rampa del reloj descritos en lo que sigue. La lógica 260 de control recibe como entrada información que indica la frecuencia deseada en la que debería operar el bucle de sincronización de fase. Esta información de entrada puede basarse en la carga del procesador, en condiciones ambientales o en ambas. La lógica 260 de control puede también informar al dispositivo cuando se ha logrado la frecuencia diana.

La Fig. 3 es una alternativa del complejo 300 de osciladores ilustrado en la Fig. 2 que se despliega en un circuito de bucle de sincronización de fase. El complejo 240A de osciladores puede conectarse a la tensión de referencia V<sub>ref</sub> 310, la tensión nominal que cabría esperar del bucle de control cuando está sincronizado. El oscilador 248A puede acoplarse a V<sub>ref</sub> 310 durante la calibración de los valores de los registros en la inicialización del PLL. Durante la calibración, se establece la tensión de referencia V<sub>ref</sub> 310 y se escalonan las corrientes de ajuste en bruto en su intervalo. Se mide la frecuencia resultante de los ICO para cada configuración del registro. Durante la operación en estado estacionario del PLL, si se desea una nueva frecuencia, se escoge el valor del registro que produjo una frecuencia más cercana a esa frecuencia deseada con la correspondiente entrada de V<sub>ref</sub> junto con la debida configuración del divisor.

La Fig. 4 es un gráfico 400 de la frecuencia de una señal ejemplar de salida de reloj del bucle de sincronización de fase de la Fig. 1 en el tiempo. Debería hacerse notar que la forma de onda representada en la Fig. 4 con trazo continuo es sin que se seleccione el circuito opcional 270 de división por dos. En este ejemplo, la señal de reloj de salida en la referencia 410 opera a 600 MHz y se desea que pase a operar a 1,2 GHz. En la referencia 410, la señal de reloj de salida es impulsada por el complejo 240A de osciladores. Además, el complejo 240A de osciladores está conectado al filtro 220 de paso bajo. En la referencia 415, se incrementa el registro 242A (y se especifica una correspondiente cantidad divisora para el divisor 230) para aumentar la correspondiente corriente de polarización del oscilador 248A y, así, causar un aumento en la frecuencia de la señal de reloj de salida. Durante el instante 420, el oscilador 248A está en vía de sincronización con la señal externa 203 de referencia. Este ciclo de operación en una salida sincronizada, aumentando la corriente de polarización y volviendo a sincronizar con ella por parte de los complejos 240A de osciladores se repite hasta la referencia 425. En la referencia 425, se desea aumentar la frecuencia de salida de reloj más allá del valor nominal del oscilador 248A. En 425, la lógica 260 de control establece la polarización fijando el valor del registro 242B, establece la cantidad divisora, selecciona el complejo 240B de

osciladores para impulsar la salida de reloj conmutando el conmutador 247A a tierra, conmuta el conmutador 247B a la vía de retroacción y selecciona la salida 249B del oscilador para que impulse la salida de reloj. El complejo 240B de osciladores sube hasta 1,2 GHz haciendo que el registro 242B se incremente a lo largo de tres ciclos más.

En la referencia 430, en un ejemplo, no se utiliza el circuito opcional 270 de división por dos. En este ejemplo, la señal 280 de salida de reloj seguirá la salida 249B del oscilador (ilustrada como una línea continua en la Fig. 4). Este ejemplo tiene aplicación particular cuando los circuitos síncronos que están impulsados por la señal 280 de reloj de salida están diseñados para gestionar los sobreimpulsos a frecuencias elevadas.

5

10

15

20

25

30

35

40

45

50

55

En otro ejemplo, en la referencia 430, la lógica 260 de control incrementa el registro 242B para que alcance su frecuencia operativa diana. También en la referencia 430, la lógica 260 de control activa el circuito 270 de división por dos para que divida por dos la frecuencia de reloj de salida, tal como se muestra con la línea discontinua 422. En la referencia 435, la salida 249B del oscilador se sincroniza con la señal 203 de referencia. En la referencia 427, la lógica 260 de control desactiva el circuito 270 de división por dos para permitir que la salida de reloj aumente hasta la frecuencia diana sincronizada de salida. Se hace notar que, aunque en la Fig. 1 se muestra un circuito 270 de división por dos, pueden utilizarse otros divisores, incluyendo un divisor fraccionario o cualquier otro circuito divisor que reduzca la frecuencia de la señal de reloj de salida. Causar la caída de la frecuencia de salida de reloj para permitir que el oscilador se sincronice en la frecuencia diana protege los circuitos síncronos, que pueden no estar diseñados para gestionar sobreimpulsos de frecuencia en una frecuencia operativa tan elevada. Aunque los circuitos síncronos estén diseñados para gestionar sobreimpulsos de la frecuencia diana, tal diseño requiere típicamente el aumento de la tensión operativa de los circuitos síncronos para hacerlo. Causar la caída de la frecuencia de salida de reloj según se describe elimina la necesidad de que los circuitos síncronos operativos utilicen esta tensión operativa incrementada.

La Fig. 5 es una realización del bucle de sincronización de fase ilustrado en la Fig. 1 que acopla selectivamente dos osciladores a las vías de retroacción y salida independientemente. La Fig. 5 contiene todos los elementos descritos en la Fig. 1, con la excepción del circuito 270 de división por dos. Además, el bucle 500 de sincronización de fase incluye un multiplexor 530 sin interferencias, que permite un acoplamiento independiente de los osciladores entre la vía de retroacción definida por el divisor 230, el detector 210 de fase, el filtro 220 de paso bajo, y la salida de uno de los complejos 240A-240B de osciladores. A título de ejemplo, la lógica 560 de control puede estar configurada para seleccionar la salida del complejo 240A de osciladores para que esté conectada a la salida de reloj 540 por el multiplexor controlador 250 sin interferencias mientras se selecciona la salida del complejo 240B de osciladores para que esté conectada a la vía de retroacción por el multiplexor 530 sin interferencias y el conmutador 247B. El bucle 500 de sincronización de fase elimina los sobreimpulsos cuando la salida de reloj cambia su impulso entre complejos de osciladores. Además, esta realización permite que la salida de reloj funcione sin sincronización, tal como se describe en relación con la Fig. 6.

La Fig. 6 es un gráfico 600 de una señal ejemplar de reloj salida que implementa un procedimiento de cambio de tensión simple de variación del reloj de salida para alcanzar una frecuencia diana 615. El gráfico 600 traza la salida del oscilador para el complejo 240B de osciladores y la señal 540 de reloj de salida en el dominio frecuencial. En el gráfico 600, la señal 540 de reloj de salida es impulsada por el complejo 240B de osciladores. En la referencia 601, la salida del complejo 240B de osciladores impulsa la señal 540 de reloj de salida para que opere a 800 MHz. En la referencia 605, la técnica de cambio de tensión simple empieza conmutando 247A a tierra y seleccionando el complejo 240A de osciladores para que se conecte a la vía de retroacción. En consecuencia, cae la frecuencia del complejo 240B de osciladores y, por ende, la señal 540 de reloj de salida y funciona sin sincronización a una frecuencia ligeramente menor. La expresión sin sincronización se refiere a impulsar la salida de reloj de un PLL por medio de un oscilador que no está acoplado a la vía de retroacción del PLL. Las personas con dominio de la técnica apreciarán que la expresión sin sincronización también puede incluir el desacoplamiento de una señal de un PLL de la vía de retroacción de un bucle de sincronización de fase. Se hace notar que una salida de reloj no sincronizada para una tensión especificada de polarización generalmente opera a una frecuencia menor que una salida sincronizada para la misma tensión especificada de polarización.

La caída sigue estando dentro del intervalo definido por el valor del registro 242B debido al complejo 240B de osciladores. En la referencia 610, el registro 242B es implementado por la lógica 560 de control, haciendo que tanto la salida 249B del oscilador como la señal 540 del reloj de salida aumenten para operar en el siguiente intervalo de frecuencias operativas. En otras realizaciones, el aumento en el intervalo de frecuencias operativas puede incluir saltarse el siguiente intervalo de frecuencias operativas. El registro 242B se incrementado continuamente para lograr una frecuencia de salida de aproximadamente 5 MHz/µsec. Dado que el bucle de sincronización de fase opera mientras no está sincronizado, la frecuencia operativa en cada incremento es un poco menor de lo que habría sido operando sincronizado. Además, mientras el complejo 240B de osciladores impulsa la salida sin acoplarse a la vía de retroacción, la cantidad divisora es inmaterial durante el control por rampa del complejo 240B de osciladores.

Se hace notar además que el tamaño del incremento entre cada nivel o etapa de salida de reloj ilustrados en las Figuras 4 y 6 se selecciona con fines ilustrativos y puede no correlacionarse directamente con los intervalos de anchura de frecuencia definidos por los valores del registro de cinco bits. Además, las características de frecuencia

de los osciladores no son tan lineales como se muestra en las Figuras 4 y 6. La curva de frecuencia del oscilador es típicamente arqueada, pero, según se ilustra, es monótona.

La Fig. 7 es un gráfico 700 de una señal ejemplar de salida que ilustra un procedimiento de variación del reloj para alcanzar una frecuencia diana de 1 GHz. La salida de reloj ilustrada en la Fig. 7 puede ser generada adecuadamente por el bucle 500 de sincronización de fase. El gráfico 700 ilustra un salto desde una salida de reloj operativa de 600 MHz hasta 1 GHz. El gráfico 700 traza la frecuencia 735 de salida del complejo 240A de osciladores y la frecuencia 730 de salida del complejo 240A de osciladores. La línea continua indica la frecuencia 540 de reloj de salida del bucle 500 de sincronización de fase. La línea punteada indica que no se selecciona el respectivo complejo de osciladores para que sea la salida del bucle 600 de sincronización de fase.

5

30

35

40

45

50

55

10 En el instante 705, el complejo 240A de osciladores está sincronizado a 600 MHz y está seleccionado para impulsar la salida de reloj. Además, el complejo 240B de osciladores opera sin sincronización y no seleccionado a menos de 1 GHz. Si el complejo 240B de osciladores no está ya encendido, el correspondiente registro puede ser modificado a un valor que haga que el complejo 240B de osciladores opere a menos de 1 GHz. En el instante 710, el bucle de retroacción es desconectado del complejo 240A de osciladores, desincronizando su operación y haciendo que la salida de reloj caiga de 600 MHz. Además, se conecta el bucle de retroacción al complejo 240B de osciladores y se 15 especifica la cantidad divisora para el divisor 230, elevando la salida del complejo 240B de osciladores. Durante el periodo de tiempo 715, el complejo 240B de osciladores está en vía de sincronizarse con la señal 203 de referencia. Entretanto, la salida del complejo 240A de osciladores permanece seleccionada para impulsar la salida de reloj a menos de 600 MHz. En el instante 725 después de que el complejo 240B de osciladores se haya sincronizado, la 20 lógica 560 de control selecciona el complejo 240B de osciladores para impulsar la salida de reloj conmutando el multiplexor 250, haciendo que la salida de reloj aumente desde menos de 600 MHz hasta 1 GHz sin los sobreimpulsos experimentados por la señal de salida de reloj. El complejo 240A de osciladores puede ser apagado mientras el complejo 240B de osciladores impulsa la salida de reloj hasta que el complejo 240A de osciladores haya de proporcionar la siguiente frecuencia diana.

Debería hacerse notar que el bucle 500 de sincronización de fase puede generar una salida de reloj que salte entre dos combinaciones cualesquiera de frecuencias de reloj de salida en cualquiera de las dos direcciones, en las que una frecuencia de reloj de salida es impulsada por un complejo de osciladores y la otra frecuencia de reloj de salida es impulsada por el otro complejo de osciladores.

La Fig. 8 es otra realización del bucle de sincronización de fase ilustrado en la Fig. 1. El bucle 800 de sincronización de fase incluye elementos de retroacción similares a los descritos en la Fig. 2. El bucle 800 de sincronización de fase también incluye los complejos 840A-840D de osciladores, la lógica 860 de control y multiplexores 855 y 865 sin interferencias. Los complejos 840A y 840B de osciladores, denominados colectivamente complejos de osciladores de gama baja, están graduados para hacer oscilar señales a frecuencias entre 400 MHz y 800 MHz. Los complejos 840C y 840D de osciladores, denominados colectivamente complejos de osciladores de gama alta, están graduados para hacer oscilar señales a frecuencias entre 800 MHz y 1200 MHz. Cada uno de los complejos de osciladores está acoplado a multiplexores 855 y 865. La lógica 860 de control está configurada para conectar uno cualquiera de los complejos de osciladores a la salida de reloj del bucle 800 de sincronización de fase. Además, la lógica 860 de control está configurada para conectar independientemente uno cualquiera de los complejos de osciladores a la vía de retroacción del bucle 800 de sincronización de fase. La lógica 860 de control puede conectar el mismo complejo de osciladores tanto a la salida de reloj como a la vía de retroacción o puede conectar un complejo de osciladores a la vía de retroacción y otro complejo de osciladores a la salida de reloj.

La lógica 860 de control puede producir diversos procedimiento de cambio de tensión del reloj variando qué oscilador impulsa una vía de retroacción y qué oscilador impulsa la salida del PLL. La Fig. 9 es un gráfico de una señal ejemplar de salida que ilustra un procedimiento de cambio de tensión sincronizado generado por el bucle 800 de sincronización de fase. La lógica 860 de control controla una secuencia de conexión y desconexión de complejos de osciladores del mismo intervalo (es decir, del complejo de osciladores de gama baja) para elevar la frecuencia de reloj de salida. Al hacerlo, se general la salida 905 de reloj conmutando entre complejos de osciladores.

Al leer la Fig. 9, la línea continua indica el reloj 905 de salida del bucle 800 de sincronización de fase. La línea punteada indica que no se selecciona el respectivo complejo de osciladores para que sea la salida del bucle 800 de sincronización de fase.

Antes del instante 910, el complejo 840A de osciladores está sincronizado y seleccionado para que impulse la salida 905 de reloj. En el instante 910, se enciende y se desincroniza el oscilador dentro del complejo 840B de osciladores, el otro circuito de polarización de gama baja. El complejo 840B de osciladores es inicializado por su registro para que opere dentro del intervalo de frecuencias de aproximadamente 700 MHz. En el instante 920, la lógica 860 de control desconecta el complejo 840A de osciladores de la vía de retroacción, dando como resultado una caída en la salida 905 de reloj. Además, en el instante 920, la lógica 860 de control conecta el complejo 840B de osciladores a la vía de retroacción y programa el divisor 230, dando como resultado que la salida del complejo 840B de osciladores aumente hasta aproximadamente 700 MHz.

En el instante 930, se sincroniza el complejo 840B de osciladores. La lógica 860 de control desconecta el complejo 840A de osciladores de la salida de reloj y conecta el complejo 840B de osciladores a la salida de reloj, dando como resultado un aumento de la frecuencia de 700 MHz sin que la salida de reloj experimente sobreimpulsos de frecuencia. En esta señal ejemplar 905 de salida, este ciclo de cambio entre complejos de osciladores se repite cinco veces más hasta que la salida 905 de reloj opere a 1,2GHz. La Fig. 9 también ilustra el cambio entre complejos de osciladores de gama baja (ilustrados como la región 940), complejos de osciladores de gama alta (ilustrados como la región 950).

La Fig. 10 es un gráfico de una señal ejemplar 1005 de salida que ilustra un procedimiento de cambio de tensión complejo de un bucle de sincronización de fase. El procedimiento de cambio de tensión complejo es similar el procedimiento de cambio de tensión simple descrito en la Fig. 6, salvo en que el bucle 800 de sincronización de fase elimina los sobreimpulsos de la señal de salida de reloj conmutando a otro complejo de osciladores. Aunque las anteriores formas de onda ejemplares de salida de reloj han sido ilustradas progresando generalmente de manera ascendente, las personas con un dominio normal de la técnica apreciarán que las formas de onda ejemplares de salida de reloj pueden progresar, alternativamente, de manera descendente.

10

15

20

25

30

35

40

45

50

55

60

La Fig. 11 es un diagrama de flujo que ilustra un procedimiento 1100 de cambio de tensión simple para variar la frecuencia de la salida de un bucle de sincronización de fase. En el bloque 1110, se presenta una frecuencia deseada en la que debería operar una señal de salida de un bucle de sincronización de fase. A título de ejemplo, la carga de un procesador puede haber aumentado, requiriendo así ciclos más rápidos de reloj para procesar la carga en un periodo de tiempo más corto. En el bloque 1120, se desincroniza un oscilador que impulsa la salida del bucle de sincronización de fase de una señal de referencia tal como la señal 203 de referencia. Desincronizar el oscilador impulsor da como resultado una caída de la frecuencia en la salida del bucle de sincronización de fase. En el bloque 1130, se modifica un medio de control digital, tal como el registro 242A, que contra el oscilador impulsor, para que cambie su frecuencia bruta de salida, haciendo que la señal de salida del bucle de sincronización de fase aumente o disminuya en frecuencia, dependiendo del cambio en el oscilador impulsor. En la Fig. 11 se ilustran dos ejemplos de un procedimiento de cambio de tensión simple. Los bloques 1140 y 1150 definen un ejemplo, mientras que los bloques 1160, 1170, 1180 y 1190 definen otro.

En el bloque 1140, el procedimiento 1100 determina si la frecuencia bruta de salida del oscilador está dentro del intervalo de la frecuencia deseada de salida. A título de ejemplo, una frecuencia deseada puede especificar 1,1 GHz. El procedimiento determina si el intervalo definido por el valor del registro que contra el correspondiente complejo de osciladores incluye la frecuencia de 1,1 GHz. Si lo incluye, el procedimiento 1100 prosigue al bloque 1150, en el que el oscilador impulsor se sincroniza con la señal de referencia estableciendo una cantidad divisora y acoplando el oscilador impulsor a una vía de retroacción del bucle de sincronización de fase. Si no lo incluye, el procedimiento 1100 prosigue al bloque 1130 para modificar el medio digital, tal como el valor de registro en el registro 242A. Si se desea elevar la tensión de la salida del bucle de sincronización de fase, el valor incrementado del registro hará que la salida del reloj salte hacia arriba hasta el siguiente intervalo bruto de frecuencias. Si se desea reducir la tensión de la salida del bucle de sincronización de fase, el valor decrementado del registro hará que la salida del reloj salte hacia abajo hasta el siguiente intervalo bruto de frecuencias.

En el segundo ejemplo, y volviendo al bloque 1130, el procedimiento 1100 prosigue al bloque 1160. En el bloque 1160, el procedimiento 1100 lleva a cabo una función de búsqueda anticipada determinando si el siguiente cambio en la frecuencia bruta de salida del oscilador daría como resultado dar salida a una frecuencia dentro del intervalo de la frecuencia deseada de salida. En caso negativo, el procedimiento 1100 prosigue al bloque 1130, en el que se ajusta el oscilador para que opere en el siguiente intervalo de frecuencias. En caso afirmativo, el procedimiento 1100 prosigue al bloque 1170, en el que se divide la salida del bucle de sincronización de. Por ejemplo, la salida puede ser dividida habilitando un circuito de división por dos como circuito 270. El circuito de división por dos, en un ejemplo, puede ser habilitado antes de la última etapa sin sincronización. En otro ejemplo, el circuito de división por dos puede ser habilitado después de la última etapa sin sincronización. En ambos ejemplos, el circuito de división por dos es habilitado antes de conmutar el bucle a la configuración sincronizada. En el bloque 1175, se ajusta el oscilador que impulsa la salida del bucle de sincronización de fase a través del divisor para que su frecuencia de salida esté dentro del intervalo de la frecuencia deseada de salida. En el bloque 1180, el oscilador que impulsa la salida del bucle de sincronización de fase es sincronizado con la señal de referencia estableciendo la cantidad divisora y conectado el oscilador impulsor a la vía de retroacción del bucle de sincronización de fase. Una vez que el oscilador está sincronizado, el procedimiento 1100 prosique al bloque 1190, en el que la salida del bucle de sincronización de fase ya no se divide. Por ejemplo, la salida puede no ser ya dividida deshabilitando el circuito 270 de división por dos.

La Fig. 12 es un diagrama de flujo que ilustra un procedimiento 1200 de salto para variar la frecuencia de la salida de un bucle de sincronización de fase. En el bloque 1210, se introduce una frecuencia deseada en la que debería operar la salida del bucle de sincronización de fase. En el bloque 1220, se desincroniza de una señal de referencia un primer oscilador que impulsa la salida del bucle de sincronización de fase. En el bloque 1230, se enciende un segundo oscilador. El segundo oscilador no se conecta para impulsar la salida del bucle de sincronización de fase. En el bloque 1240, se controla digitalmente el segundo oscilador para que oscile dentro de un intervalo de

frecuencias que incluye la frecuencia deseada. En el bloque 1250, se sincroniza el segundo oscilador con una señal de referencia conectándolo independientemente desde el primer oscilador con una vía de retroacción del bucle de sincronización de fase. En el bloque 1260, se conmuta el primer oscilador para que no impulse la salida del bucle de sincronización de fase y se conmuta el segundo oscilador para que impulse la salida del bucle de sincronización de fase. Opcionalmente, puede entonces apagarse el primer oscilador.

5

10

15

20

25

30

35

40

45

50

La Fig. 13 es un diagrama de flujo que ilustra un procedimiento de cambio de tensión sincronizado para variar la frecuencia de la salida de un bucle de sincronización de fase. En el bloque 1310, se introduce una frecuencia deseada en la que debería operar una señal de salida de un bucle de sincronización de fase. En el bloque 1320, se desincroniza de una señal de referencia un oscilador que impulsa la salida del bucle de sincronización de fase. En el bloque 1330, se controla digitalmente otro oscilador para que cambie su frecuencia bruta de salida. Dependiendo de la dirección deseada del cambio de tensión de la salida, el cambio puede ser hacia una frecuencia mayor o menor. En el bloque 1340, se sincroniza el otro oscilador con la señal de referencia. A título de ejemplo, el otro oscilador se conecta a la vía de retroacción del bucle de sincronización de fase. En el bloque 1350, una vez sincronizado, se conmuta el otro oscilador para que impulse la salida del bucle de sincronización de fase. En el bloque 1360, el procedimiento 1300 determina si la frecuencia bruta de salida del oscilador impulsor está dentro del intervalo de la frecuencia deseada de salida. Si lo está, el procedimiento 1360 finaliza. Si no, el procedimiento 1300 prosigue al bloque 1320, en el que se desincroniza el oscilador que impulsa la salida del bucle de sincronización de fase.

La Fig. 14 es un diagrama de flujo que ilustra un procedimiento 1400 de cambio de tensión complejo para variar la frecuencia de la salida de un bucle de sincronización de fase. En el bloque 1410, se introduce una frecuencia deseada en la que debería operar una señal de salida de un bucle de sincronización de fase. En el bloque 1420, se desincroniza de una señal de referencia un oscilador que impulsa la salida del bucle de sincronización de fase. En el bloque 1430, se controla digitalmente otro oscilador para que cambie su frecuencia bruta de salida mientras está desincronizado de la vía de retroacción del bucle de sincronización de fase. En el bloque 1440, el procedimiento 1400 realiza una función de búsqueda anticipada. En particular, determina si el siguiente cambio en la frecuencia bruta de salida del oscilador daría como resultado dar salida a una frecuencia dentro del intervalo en el que se encuentra la frecuencia deseada de salida. Si no lo está, el procedimiento 1400 prosigue al bloque 1430 para cambiar la frecuencia bruta de salida mientras está desincronizado.

Si lo está, el procedimiento 1400 prosigue al bloque 1450, en el que se enciende el segundo oscilador. En el bloque 1460, se controla digitalmente el segundo oscilador para que oscile en un intervalo que incluye la frecuencia deseada. En el bloque 1470, se sincroniza el segundo oscilador con la señal de referencia. En 1480, se conmuta el primer oscilador para que deje de impulsar la salida del bucle de sincronización de fase y se conmuta el segundo oscilador para que impulse la salida.

Los diversos bloques lógicos ilustrativos, módulos, circuitos, elementos y/o componentes descritos en conexión con las realizaciones dadas a conocer en el presente documento pueden ser implementados o llevados a cabo con un procesador de uso general, un procesador de señales digitales (DSP), un circuito integrado para aplicaciones específicas (ASIC), una matriz de puertas programables in situ (FPGA) u otro componente lógico programable, una puerta discreta o lógica de transistor, componentes discretos de soporte físico o cualquier combinación de los mismos diseñada para llevar a cabo las funciones descritas en el presente documento. Un procesador de uso general puede ser un microprocesador, pero, de forma alternativa, el procesador puede ser cualquier procesador, controlador, microcontrolador o máquina de estado convencionales. Un procesador también puede ser implementado como una combinación de componentes de cálculo; por ejemplo, una combinación de un DSP y un microprocesador, una pluralidad de microprocesadores, uno o más microprocesadores en unión de un núcleo de DSP o cualquier otra configuración de ese tipo.

Los procedimientos descritos en conexión con las realizaciones dadas a conocer en el presente documento pueden ser implementados directamente en soporte físico, en un módulo de soporte lógico ejecutado por un procesador o en una combinación de los dos. Un módulo de soporte lógico puede residir en memoria RAM, memoria flash, memoria ROM, memoria EPROM, registros, un disco duro, un disco extraíble, un CD-ROM o cualquier otra forma de medio de almacenamiento conocida en la técnica. Un medio de almacenamiento puede estar acoplado con el procesador, de tal modo que el procesador pueda leer información del medio de almacenamiento y escribir información en el mismo. De forma alternativa, el medio de almacenamiento puede ser integral al procesador.

Aunque se da a conocer la invención en el contexto de realizaciones, se reconocerá que las personas con un dominio normal de la técnica pueden emplear una amplia variedad de implementaciones coherentes con la anterior exposición y con las reivindicaciones que siguen a continuación.

### REIVINDICACIONES

1. Un procedimiento de variación de la frecuencia de una salida (280, 540) de reloj de un bucle de sincronización de fase PLL (140, 200, 500, 800) que incluye un detector (210) de fase que tiene un puerto de entrada de referencia para una señal (145, 203) de referencia y un puerto de entrada de retroacción para una señal (207) de retroacción, que comprende:

acoplar una salida de un primer complejo (240A) de osciladores a la salida (280, 540) de reloj del PLL para impulsar la salida (280, 540) de reloj, estando desacoplada la salida del primer complejo (240A) de osciladores de una vía de retroacción del PLL, estando conectada dicha vía de retroacción al puerto de entrada de retroacción del detector (210) de fase y siendo operable para sincronizar la salida (280, 540) de reloj en fase con la señal (145, 203) de referencia;

introducir (1210, 1310, 1410) en la lógica (260, 560) de control del PLL una frecuencia deseada en la que debería operar la salida (280, 540) de reloj del PLL;

encender (1230, 1450) un segundo complejo (240B) de osciladores;

controlar digitalmente (1240, 1330, 1460) el segundo complejo (240B) de osciladores para generar una señal en el intervalo de frecuencias que contiene la frecuencia deseada;

acoplar una salida del segundo complejo (240B) de osciladores a la vía de retroacción del PLL mientras se mantiene la salida del primer complejo (240A) de osciladores acoplada para impulsar la salida (280, 540) de reloj del PPL y se mantiene la salida del primer complejo (240A) de osciladores desacoplada de la vía de retroacción:

desacoplar (1260, 1480) la salida del primer complejo (240A) de osciladores de la salida (280, 540) de reloj del PLL (140, 200, 500, 800); y

acoplar (1260, 1350, 1480) la salida del segundo complejo (240B) de osciladores a la salida (280, 540) de reloj del PLL para impulsar la salida (280, 540) de reloj.

- 2. Un procedimiento de variación de la frecuencia de una salida (280, 540) de reloj de un bucle de sincronización de fase PLL (140, 200, 500, 800) que incluye un detector (210) de fase que tiene un puerto de entrada de referencia para una señal (145, 203) de referencia y un puerto de entrada de retroacción para una señal (207) de retroacción, que comprende:

- acoplar una salida de un primer complejo (240A) de osciladores a la salida (280, 540) de reloj del PLL para impulsar la salida (280, 540) de reloj, estando desacoplada la salida del primer complejo (240A) de osciladores de una vía de retroacción del PLL, estando conectada dicha vía de retroacción al puerto de entrada de retroacción del detector (210) de fase y siendo operable para sincronizar la salida (280, 540) de reloj en fase con la señal (145, 203) de referencia;

- introducir (1210, 1310, 1410) en la lógica (260, 560) de control del PLL una frecuencia deseada en la que debería operar la salida (280, 540) de reloj del PLL;

- 35 encender (1230, 1450) un segundo complejo (240B) de osciladores;

- acoplar una salida del segundo complejo (240B) de osciladores a la vía de retroacción del PLL mientras se mantiene la salida del primer complejo (240A) de osciladores acoplada para impulsar la salida (280, 540) de reloj del PPL y se mantiene la salida del primer complejo (240A) de osciladores desacoplada de la vía de retroacción:

- 40 controlar digitalmente (1240, 1330, 1460) el segundo complejo (240B) de osciladores para generar una señal en el intervalo de frecuencias que contiene la frecuencia deseada;

- desacoplar (1260, 1480) la salida del primer complejo (240A) de osciladores de la salida (280, 540) de reloj del PLL: v

- acoplar (1260, 1350, 1480) la salida del segundo complejo (240B) de osciladores a la salida (280, 540) de reloj del PLL para impulsar la salida (280, 540) de reloj.

- 3. El procedimiento de las reivindicaciones 1 o 2 que, además, comprende el apagado del primer complejo (240A) de osciladores después de que el segundo complejo (240B) de osciladores se acopla a la salida de reloj del PLL (140, 200, 500, 800).

- 4. Un bucle de sincronización de fase PLL (140, 200, 500, 800) que comprende:

- 50 una salida (280, 540) de reloj;

5

10

15

20

30

45

55

un detector (210) de fase que tiene un puerto de entrada de referencia para una señal (145, 203) de referencia y un puerto de entrada de retroacción para una señal (207) de retroacción;

un primer complejo (240A) de osciladores conectado al detector (210) de fase;

un segundo complejo (240B) de osciladores conectado al detector (210) de fase en paralelo con el primer complejo (240A) de osciladores;

una vía de retroacción conectada al puerto de entrada de retroacción del detector (210) de fase y para sincronizar la salida (280, 540) de reloj en fase con la señal (145, 203) de referencia; y

lógica (260, 560) de control operable para acoplar selectivamente ya sea una salida del primer complejo (240A) de osciladores o una salida del segundo complejo (240B) de osciladores a la salida (280, 540) de

reloj para impulsar la salida (280, 540) de reloj, y para acoplar selectivamente ya sea la salida del primer complejo (240A) de osciladores o la salida del segundo complejo (240B) de osciladores para suministrar dicha señal (207) de retroacción por medio de la vía de retroacción a dicho puerto de entrada de retroacción.

caracterizado porque la lógica (260, 560) de control está configurada para, en secuencia:

5

10

15

20

25

desacoplar la salida del primer complejo (240A) de osciladores de dicha vía de retroacción mientras se mantiene la salida del primer complejo (240A) de osciladores acoplada para impulsar la salida (280, 540) de reloj del PLL;

acoplar la salida del segundo complejo (240B) de osciladores a la vía de retroacción mientras se mantiene la salida (280, 540) de reloj del PLL impulsada por el primer complejo (240A) de osciladores y se mantiene la salida del primer complejo (240A) de osciladores desacoplada de la vía de retroacción; desacoplar la salida del primer complejo (240A) de osciladores de la salida (280, 540) de reloj del PLL; y acoplar la salida del segundo complejo (240B) de osciladores a la salida (280, 540) de reloj del PLL para impulsar la salida (280, 540) de reloj.

- 5. El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 que, además, comprende:

- un multiplexor (250) configurado para acoplar la salida (249A, 249B) de uno cualquiera de los complejos (240A, 240B) de osciladores primero y segundo a la salida (280, 540) de reloj.

- **6.** El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 en el que un complejo (240A, 240B) de osciladores incluye un registro (242A, 242B) configurado para almacenar un valor correspondiente a un intervalo específico de frecuencias.

- 7. El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 que, además, comprende:

un circuito (270) de división por dos acoplado a la lógica (260, 560) de control, estando configurada además la lógica (260, 560) de control para activar el circuito (270) de división por dos para disminuir la frecuencia de la salida (280, 540) de reloj mientras el primer complejo (240A) de osciladores se sincroniza a una frecuencia más elevada.

8. El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 que, además, comprende:

un medio (247A, 247B) de conmutación para acoplar selectivamente la entrada de uno cualquiera de los complejos (240A, 240B) de osciladores primero y segundo a la vía de retroacción.

- 9. El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 que, además, comprende:

- 30 un multiplexor (530) configurado para acoplar la salida de uno cualquiera de los complejos (240A, 240B) de osciladores primero y segundo a la vía de retroacción.

- **10.** El bucle (140, 200, 500, 800) de sincronización de fase de la reivindicación 4 en el que la vía de retroacción incluye un divisor (230), un detector (210) de fase y un filtro (220) de bucle.

- Un medio legible por ordenador que comprende instrucciones que, cuando son ejecutadas por un procesador,

dan como resultado la realización de las etapas de procedimiento de cualquiera de las reivindicaciones 1 a 3.

FIG. 1

FIG. 11

FIG. 12

FIG. 14