OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 389 797

51 Int. Cl.: H04N 7/26

(2006.01)

| _    |                                |

|------|--------------------------------|

| 12   |                                |

| (12) | TRADUCCIÓN DE PATENTE EUROPEA  |

|      | INADOCCION DE FATEINTE EUROFEA |

T3

- 96 Número de solicitud europea: 99113786 .0

- 96 Fecha de presentación: 01.03.1994

- Número de publicación de la solicitud: 0954182

Fecha de publicación de la solicitud: 03.11.1999

- (54) Título: Aparato para evitar errores de redondeo en la transformación inversa de coeficientes de transformada de una señal de imagen en movimiento

- 30 Prioridad: 01.03.1993 JP 4020393 19.03.1993 JP 5990993

73 Titular/es:

SONY CORPORATION (100.0%) 7-35 KITASHINAGAWA 6-CHOME SHINAGAWA-KU TOKYO 141, JP

- 45 Fecha de publicación de la mención BOPI: 31.10.2012

- (72) Inventor/es:

SUZUKI, TERUHIKO; YAGASAKI, YOICHI; SUDO, TATSUYA y OKAZAKI, TORU

- Fecha de la publicación del folleto de la patente: **31.10.2012**

- (74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

ES 2 389 797 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

#### **DESCRIPCIÓN**

Aparato para evitar errores de redondeo en la transformada inversa de coeficientes de transformada de una señal de imagen en movimiento.

5

10

15

Las transformadas ortogonales se utilizan en diversas aplicaciones en muchos sistemas de tratamiento digital de señal. Las transformadas ortogonales permiten la realización del tratamiento de señal en el dominio de la frecuencia. La transformada rápida de Fourier (FFT –"Fast Fourier Transform") y la transformada de coseno discreta (DCT-"discrete cosine transform"), etc., son tipos muy conocidos de transformadas ortogonales. Una transformada ortogonal analiza, por ejemplo, un fragmento de una señal en el dominio del tiempo para obtener componentes de frecuencia (que varían dependiendo de la función de transformada ortogonal aplicada) e indican el espectro (es decir, la distribución de energía en función de la frecuencia) del fragmento de señal original en el dominio del tiempo. Tratando de diversos modos las componentes de frecuencia (denominadas usualmente coeficientes de transformada) que resultan de la transformación ortogonal del fragmento de señal, puede reducirse la redundancia del fragmento de señal original. En otras palabras, mediante la transformación ortogonal del fragmento de señal original puede representarse con menos bits de los que se han utilizado para representar el fragmento de señal original. Además, realizando la transformada ortogonal inversa de los coeficientes de transformada, puede recuperarse el fragmento de señal original en el dominio del tiempo.

20

Los aparatos para comprimir una señal de imagen en movimiento y para expandir una señal de imagen en movimiento comprimida, son ejemplos comunes de sistemas de tratamiento de señal digital que utilizan tratamiento de transformada ortogonal.

25

Es conocido que la potencia de señal de señales que tienen una alta correlación se concentra en las frecuencias más bajas en el dominio de la frecuencia. A medida que aumenta la concentración de potencia de señal en un eje de coordenadas específico (por ejemplo, el eje de frecuencias), puede reducirse progresivamente la redundancia de la señal, y la señal puede comprimirse más eficientemente.

Puesto que una señal de imagen con movimiento está en general altamente correlacionada, tanto espacialmente como en el tiempo, puede aplicarse tratamiento de transformada ortogonal para concentrar la potencia de señal en un eje de coordenadas específico, y la señal de imagen con movimiento puede comprimirse con una alta eficiencia.

35 r

Hasta ahora, se ha requerido una cantidad extremadamente grande de información para representar imágenes con movimiento, utilizando, por ejemplo, una señal de video según la norma NTSC. Debido a esto, el registro de una señal de imagen con movimiento ha requerido un medio de registro con una capacidad de almacenamiento muy alta si se desea que el medio proporcione un medio de registro aceptablemente largo. Adicionalmente, la frecuencia de muestreo de información a la cual se registra y se reproduce de tal medio la señal de imagen con movimiento ha sido muy alta. Se han requerido hasta ahora cintas magnéticas o discos ópticos de dimensiones físicas grandes para almacenar señales de imagen con movimiento.

40

Si se desea registrar una señal de imagen con movimiento sobre un medio de registro más compacto con un tiempo de registro aceptablemente largo, debe aplicarse compresión de señal a la señal de imagen con movimiento para reducir la cantidad de información que es necesario almacenar. Adicionalmente, debe disponerse de un aparato que sea capaz de expandir la señal de imagen con movimiento comprimida reproducida del medio de registro compacto.

45

Para cumplir los requerimientos que se acaban de describir, han sido propuestos diversos sistemas de compresión de señal de imagen con movimiento que explotan la correlación entre y dentro de las porciones de la señal de imagen con movimiento que representan las imágenes que constituyen la señal de imagen con movimiento. Por ejemplo, los sistemas de compresión de señal de imagen con movimiento propuestos por el Grupo de Expertos de Imagen en Movimiento (MPEG –"Moving Picture Experts Group") son ampliamente conocidos. Puesto que el sistema MPEG ha sido descrito ampliamente en diversas publicaciones impresas, no se repetirá en la presente memoria una explicación detallada de dicho sistema.

55

50

La siguiente descripción se referirá frecuentemente a una "imagen". Puesto que las técnicas de tratamiento de señal descritas en la presente memoria se refieren al tratamiento de una señal de imagen con movimiento que representa una imagen en movimiento, ha de entenderse que la palabra "imagen", en el sentido en que se utiliza en general en la presente memoria, se refiere a una porción de una señal de imagen con movimiento que representa una imagen de la imagen en movimiento. Además, una señal de imagen con movimiento puede representar una imagen de la imagen en movimiento en la forma de un cuadro o un campo. Salvo indicación en otro sentido, una "imagen" significa un campo o un cuadro.

65

60

El sistema MPEG determina primero las diferencias entre las imágenes que constituyen la señal de imagen con movimiento para reducir la redundancia de la señal de imagen con movimiento en el dominio del tiempo. A continuación, el sistema MPEG reduce la redundancia de la señal de imagen con movimiento en el dominio espacial aplicando tratamiento por transformada ortogonal a bloques de diferencias entre imágenes en el dominio del espacio. El sistema MPEG aplica tratamiento por transformada de coseno discreta (DCT –"discrete cosine transform") como tratamiento de transformada ortogonal. Reduciendo la redundancia tanto en el dominio del tiempo como en el dominio del espacio, la imagen con movimiento es comprimida con una eficiencia extremadamente alta. La señal de imagen con movimiento comprimida resultante del proceso de compresión que se acaba de describir, puede registrarse a continuación sobre un medio de registro, o transmitirse a través de un medio de transmisión adecuado.

5

20

45

50

55

60

65

Cuando la señal de imagen con movimiento es reproducida del medio de registro, o es recibida del medio de transmisión, se extraen de la señal de imagen con movimiento comprimida los bloques de coeficientes de transformada resultantes de la transformada de coseno discreta. Los coeficientes de transformada son tratados utilizando una transformada ortogonal inversa (una transformada de coseno discreta inversa (IDCT –"inverse discrete cosine transform") en el sistema MPEG) para recuperar bloques de diferencias entre imágenes en el curso de la reconstrucción de las imágenes en la señal de imagen con movimiento original.

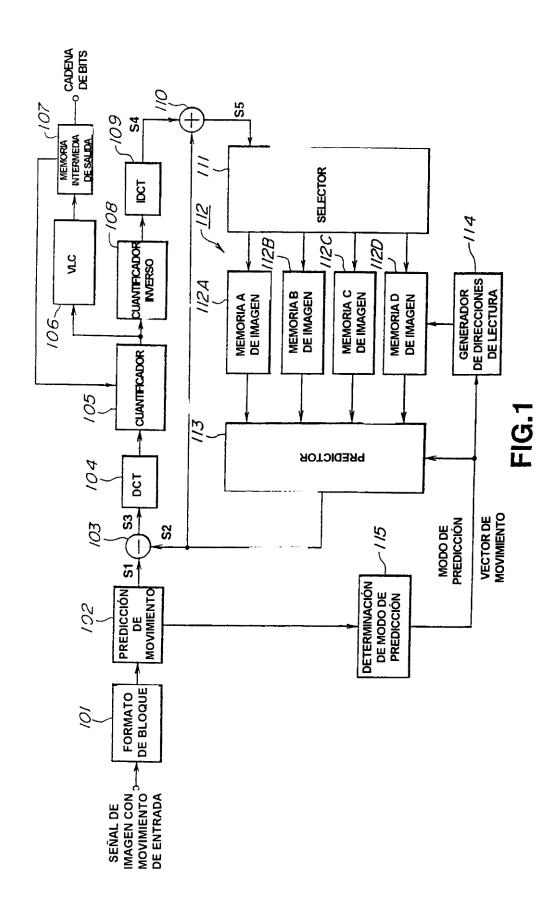

En la figura 1 se muestra un ejemplo del diseño constructivo de un aparato compresor de señal de imagen con movimiento basado en el sistema MPEG. En el compresor ilustrado en la figura 1, se aplica una señal de imagen con movimiento digital al circuito 101 formateador de bloques, donde es convertida de un formato de video normalizado, por ejemplo, un formato de señal de video según la norma NTSC, a un formato de bloques para proporcionar una señal de imagen con movimiento en bloques. En esta técnica, cada imagen de la señal de imagen con movimiento es dividida en el dominio del espacio, es decir horizontal y verticalmente, en macrobloques de, por ejemplo, 16 x 16 elementos de imagen. Los macrobloques son también subdivididos en bloques de 8 x 8 elementos de imagen.

El aparato representado en la figura 1 comprime cada imagen de la señal de imagen con movimiento bloque por bloque hasta que han sido tratados todos los bloques que constituyen la imagen. El aparato trata a continuación otra imagen de la señal de imagen con movimiento, que puede ser o no la siguiente imagen de la secuencia de imágenes que constituyen la imagen en movimiento. En la siguiente descripción del aparato ilustrado en la figura 1, se describirá la compresión de un bloque de elementos de imagen en una imagen. El bloque de elementos de imagen que se está comprimiendo es el bloque de imagen en curso, que es un bloque de la imagen en curso. La señal de imagen con movimiento organizada en bloques se aplica al predictor 102 de movimiento. El predictor 102 de movimiento aplica la imagen en curso, que incluye el bloque S1 de imagen en curso, bloque por bloque al circuito 103 de cálculo de bloques de diferencia.

Cuando el circuito 103 de cálculo de bloques de diferencia recibe el bloque de imagen en curso del predictor 102 de movimiento, recibe también el bloque S2 de adaptación correspondiente al bloque de imagen en curso procedente del predictor 102 de movimiento. El bloque S2 de adaptación se deduce de las imágenes reconstruidas almacenadas en el bloque 112 de memoria de imagen por el predictor 113. El circuito 103 de cálculo de bloques de diferencia determina la diferencia elemento de imagen por elemento de imagen entre el bloque S1 de imagen en curso y su bloque S2 de adaptación correspondiente. El bloque de diferencias resultante, el bloque S3 de diferencias, se aplica al circuito 104 de transformada ortogonal.

El circuito 104 de transformada ortogonal, que es normalmente un circuito de transformada de coseno discreta (DCT), aplica tratamiento de transformada ortogonal al bloque S3 de diferencias, e introduce el bloque resultante de coeficientes de transformada en el cuantificador 105. El cuantificador 105 cuantifica el bloque de coeficientes de transformada para generar un bloque de coeficientes de transformada cuantificados. El codificador 106 de longitud variable somete al bloque de coeficientes de transformada cuantificados generados por el cuantificador 105, a codificación de longitud variable, tal como codificación de Huffman, codificación de longitud de ventana móvil, etc. El bloque resultante de coeficientes de transformada codificados se introduce a continuación, por ejemplo, en una vía de transmisión digital, a través de la memoria intermedia 107 de salida.

Una señal de control que indica el número de bits almacenados en la memoria intermedia 107 de salida, se realimenta al cuantificador 105. El cuantificador 105 ajusta el tamaño de incremento de cuantificación en respuesta a la señal de control para evitar el desbordamiento de la memoria intermedia 107 de salida. Un aumento o disminución de la magnitud del incremento de cuantificación disminuye o aumenta, respectivamente, el número de bits introducidos en la memoria intermedia 107 de salida.

El bloque de coeficientes de transformada cuantificados se transfiere también desde el cuantificador 105 hasta el cuantificador inverso 108, que forma parte del decodificador local utilizado en el compresor para deducir de los coeficientes de transformada cuantificados las imágenes reconstruidas utilizadas en la codificación predictiva. El cuantificador inverso 108 cuantifica inversamente el bloque de coeficientes de transformada cuantificados realizando un tratamiento complementario del tratamiento de cuantificación realizado por el cuantificador 105. El bloque resultante de coeficientes de transformada se suministra al circuito 109 de transformada ortogonal inversa, donde es sometido a transformada ortogonal inversa por tratamiento complementario del tratamiento de transformada ortogonal realizado por el circuito 104 de transformada ortogonal. El bloque S4 de diferencias restaurado resultante es suministrado al sumador 110.

El sumador 110 recibe también el bloque S2 de adaptación correspondiente al bloque S1 de imagen en curso de una de las memorias de imagen del grupo 112 de memorias de imagen seleccionado por el predictor 113. El sumador 110 realiza la suma elemento de imagen por elemento de imagen entre el bloque S4 de diferencias restaurado, generado por el circuito 109 de transformada ortogonal inversa, y el bloque S2 de adaptación procedente del grupo 112 de memorias de imagen para obtener el bloque S5 de imagen reconstruido. El bloque S5 de imagen reconstruido es suministrado a una de las memorias 112A a 112D seleccionada por el selector 111, donde se almacena.

5

15

20

25

30

35

40

45

50

55

60

65

El bloque S5 de imagen reconstruido es almacenado en la memoria de imagen seleccionada, donde forma un bloque (correspondiente al bloque en curso) de la imagen que se está reconstruyendo, bloque por bloque, a partir de los bloques de imagen reconstruida almacenados en la memoria de imagen seleccionada. Cuando está completa, la imagen reconstruida será utilizada para obtener bloques de adaptación para realizar la codificación predictiva para comprimir otras imágenes de la señal de imagen con movimiento.

El predictor 102 de movimiento determina, para cada macrobloque de la imagen en curso, un vector de movimiento entre el macrobloque de las imágenes en curso y diferentes macrobloques de las otras imágenes de la señal de imagen con movimiento almacenados. El predictor 102 de movimiento genera también una suma de los valores absolutos de las diferencias (la "suma de valores absolutos de diferencias") entre los elementos de imagen de cada macrobloque de la imagen en curso y los diferentes macrobloques de las otras imágenes. Cada suma de valores absolutos de diferencias indica el grado de concordancia entre cada macrobloque de la imagen en curso y los macrobloques de las otras imágenes. El predictor 102 de movimiento introduce cada vector de movimiento y su correspondiente suma de valores absolutos de diferencias en el circuito 115 de determinación de modo de predicción.

El circuito 115 de determinación de modo de predicción utiliza los datos recibidos del predictor 102 de movimiento para determinar el modo de predicción que será utilizado para la codificación predictiva de la imagen en curso con relación a una o más de otras imágenes reconstruidas. La imagen en curso puede ser codificada predictivamente utilizando cualquiera de los siguientes modos de predicción:

- (1) Modo intra imágenes, en el cual la imagen se comprime por sí misma, sin referencia a otras imágenes cualesquiera. Una imagen codificada de este modo se denomina imagen I.

- (2) Modo de predicción de avance, en el cual la predicción se realiza con referencia a una imagen reconstruida que se produce anteriormente en la imagen en movimiento. Una imagen codificada de este modo se denomina imagen P.

- (3) Modo de predicción bidireccional, en el cual la predicción bloque por bloque se realiza con respecto a un bloque de referencia deducido de una imagen reconstruida que aparece anteriormente en la imagen en movimiento y una imagen reconstruida que aparece posteriormente en la imagen en movimiento, o realizando una operación lineal elemento de imagen por elemento de imagen (por ejemplo, un cálculo de valor medio) entre una imagen reconstruida anterior y una imagen reconstruida posterior. Una imagen codificada de este modo se denomina imagen B.

En otras palabras, una imagen I es una imagen en la cual se ha completado la codificación intra imágenes dentro de la imagen. Una imagen P se obtiene por predicción a partir de una imagen I o una imagen P que aparecen anteriormente en la imagen en movimiento. Una imagen B se obtiene por predicción bloque por bloque utilizando una imagen I o una imagen P anteriores o posteriores o utilizando un bloque obtenido realizando una operación lineal utilizando una imagen I reconstruida o una imagen P reconstruida que aparecen anteriormente en la imagen en movimiento, y a partir de una imagen I reconstruida o una imagen P reconstruida que aparecen posteriormente en la imagen en movimiento.

El circuito 115 de determinación de modo de predicción proporciona el modo de predicción y el correspondiente vector de movimiento al predictor 113 y al generador 114 de direcciones de lectura. El generador 114 de direcciones de lectura proporciona direcciones de lectura al grupo 112 de memorias de imagen en respuesta al vector de movimiento, cuyas direcciones sirven para hacer que sea leído un bloque de la imagen reconstruida almacenado en cada memoria 112A a 112D de imagen. La posición del bloque de lectura en la imagen reconstruida está designada por el vector de movimiento. El predictor 113 selecciona uno de los bloques de lectura de las memorias 112A a 112D de imagen en respuesta a la señal PM de modo de predicción recibida del circuito 115 de determinación de modo de predicción. El bloque de lectura seleccionado proporciona el bloque S2 de adaptación para el bloque S1 de imagen en curso. Cuando el bloque de imagen en curso forma parte de una imagen B, el predictor realiza también operaciones lineales sobre los bloques de lectura de las memorias 112A a 112D de imagen para proporcionar el bloque de adaptación requerido. El predictor suministra el bloque S2 de adaptación al circuito 103 de cálculo de bloques de diferencia y al sumador 110.

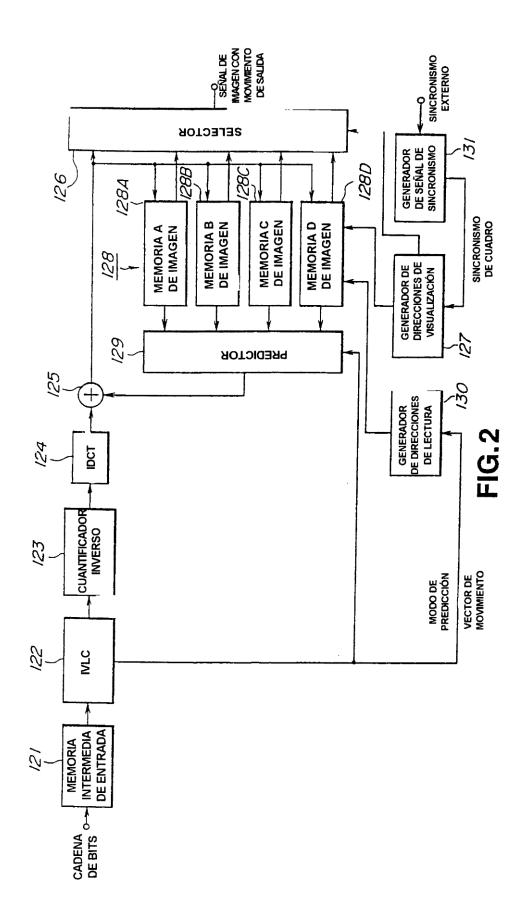

En la figura 2 se muestra un ejemplo del diseño constructivo de un aparato expansor de señal de imagen con movimiento comprimida, basado en el sistema MPEG. En este aparato, la señal de imagen con movimiento

comprimida obtenida directamente del compresor o por reproducción de la misma de un medio de registro, es suministrada como cadena de bits a la memoria intermedia 121 de entrada, donde se almacena transitoriamente. La señal digital comprimida incluye bloques de coeficientes de transformada codificados (incluyendo un bloque de coeficientes de transformada codificados que representa el bloque en curso), e información de modo de predicción, información de magnitud de incremento de cuantificación, y un vector de movimiento para cada bloque.

5

10

55

60

65

La señal de imagen con movimiento comprimida es leída de la memoria intermedia 121 de entrada por imágenes individuales y es suministrada a un codificador inverso 122 de longitud variable (IVLC –"inverse variable-length coder"). El codificador inverso 122 de longitud variable aplica un tratamiento de codificación inversa de longitud variable a la señal de imagen con movimiento comprimida, y separa la señal de imagen con movimiento comprimida en sus componentes, que incluyen bloques de coeficientes de transformada cuantificados e información de modo de predicción, información de magnitud de incremento de cuantificación, y un vector de movimiento para cada bloque.

Cada bloque de coeficientes de transformada codificados se introduce en el cuantificador inverso 123, que utiliza la información de magnitud de incremento de cuantificación para el bloque para cuantificar inversamente el bloque de coeficientes de transformada cuantificados para proporcionar un bloque de coeficientes de transformada. El circuito 124 de transformada ortogonal inversa aplica un tratamiento de transformada ortogonal inversa, normalmente un tratamiento de transformada de coseno discreta inversa, al bloque de coeficientes de transformada para obtener un bloque de diferencias restaurado. El cuantificador inverso 123 y el circuito 124 de transformada ortogonal inversa aplican, respectivamente, un tratamiento complementario del aplicado por el cuantificador 105 y por el circuito 104 de transformada ortogonal en el compresor representado en la figura 1.

El generador 130 de direcciones de lectura proporciona una dirección de lectura a las memorias 128A a 128D de imagen en respuesta al vector de movimiento correspondiente al bloque en curso recibido del codificador inverso 122 de longitud variable. En respuesta a la dirección de lectura, cada una de las memorias 128A a 128D de imagen lee un bloque de la imagen reconstruida almacenada en las mismas. El predictor 129 selecciona uno de los bloques de lectura de las memorias 128A a 128D de imagen en respuesta a la señal PM de modo de predicción, recibida también del codificador inverso 122 de longitud variable. El bloque de lectura seleccionado proporciona el bloque de adaptación para reconstruir el bloque en curso. Cuando el bloque en curso forma parte de una imagen codificada como imagen B, el predictor realiza también operaciones lineales sobre los bloques de lectura de las memorias 112A a 112D de imagen para obtener el bloque de adaptación. El predictor 129 suministra el bloque de adaptación al sumador 125.

El sumador 125 realiza una suma elemento de imagen por elemento de imagen entre el bloque de diferencias restaurado generado por el circuito 124 de transformada ortogonal inversa, y el bloque de adaptación generado por el predictor 129 para reconstruir el bloque de imagen en curso de la imagen en curso. El selector 126 suministra el bloque de imagen en curso reconstruido para almacenamiento en la memoria de las memorias 128A a 128D de imagen en la cual se está reconstruyendo la imagen en curso. El bloque de imagen en curso reconstruido se almacena en la memoria de imagen seleccionada en la posición del bloque de imagen en curso en la imagen en curso reconstruida. Cuando todos los bloques reconstruidos de la imagen en curso han sido almacenados en la memorias 128A a 128D de imagen seleccionada, la imagen en curso reconstruida está preparada para lectura, y también para ser utilizada como imagen de referencia para reconstruir otras imágenes que aparecen anterior o posteriormente en la imagen en movimiento.

Las imágenes reconstruidas almacenadas en las memorias 128A a 128D de imagen son leídas como señal de imagen con movimiento de salida a través del selector 126 en respuesta a direcciones de lectura generadas por el generador 127 de direcciones de visualización. Un convertidor de exploración (no representado) convierte la señal de imagen con movimiento de salida, leída de las memorias 128A a 128D de imagen, al formato de trama del formato de señal de video deseado, por ejemplo el formato NTSC. La señal de imagen con movimiento de salida resultante puede ser visualizada entonces en un dispositivo de visualización adecuado, por ejemplo un CRT o tubo de rayos catódicos ("cathodic ray tube"), etc. En este ejemplo, el generador 131 de señal de sincronismo está sincronizado con una fuente de sincronismo externa, y genera periódicamente una señal de sincronismo de cuadro para ser aplicada al generador 127 de direcciones de visualización. El generador 127 de direcciones de visualización genera direcciones de lectura en sincronismo con la señal de sincronismo de cuadro.

Los circuitos de transformada ortogonal, por ejemplo los circuitos de transformada de coseno discreta y de transformada de coseno discreta inversa utilizados en el compresor y en el expansor descritos anteriormente, respectivamente, realizan operaciones aritméticas sobre valores de elemento de imagen y coeficientes de transformada representados por números enteros que tienen un número finito de bits. De este modo, las operaciones de transformación ortogonal realizadas por los circuitos de transformada ortogonal pueden truncar el número de bits. Por esta razón, una diferencia en la precisión de la operación de transformada ortogonal utilizando números reales, o una diferencia en la configuración del circuito utilizado para realizar la operación de transformada ortogonal, pueden cambiar el resultado de la operación de transformada ortogonal. Esto puede dar lugar a una desadaptación entre el compresor y el expansor, y a desadaptaciones entre expansores que expanden una señal comprimida común.

Por ejemplo, en el compresor, el bloque de diferencias deducido de la señal de imagen con movimiento es transformado ortogonalmente, y se aplica un tratamiento predeterminado para cuantificar los coeficientes de transformada resultantes en el curso de la generación de la señal de imagen con movimiento comprimida. A continuación, en el expansor, si la precisión de las operaciones con números reales o la configuración del circuito de transformada ortogonal inversa no corresponden a las del compresor, es posible entonces que la salida del expansor difiera de la entrada al compresor. Por tanto, la salida del expansor puede depender de la precisión y de la configuración del aparato utilizado para el expansor.

5

20

25

30

35

45

50

55

60

65

La precisión operacional o la configuración de una transformada ortogonal inversa pueden variar dependiendo del aparato utilizado para realizar la transformada ortogonal inversa. Por ejemplo, la transformación inversa de un bloque de coeficientes de transformada utilizando dos disposiciones constructivas diferentes del mismo tipo de circuito de transformada ortogonal inversa, puede producir resultados diferentes. Tal diferencia en los resultados se denomina error de desadaptación de transformada ortogonal inversa ("error de desadaptación").

El sistema MPEG define la precisión operacional con la cual han de realizarse la transformada de coseno discreta y la transformada de coseno discreta inversa, pero no define el método operacional ni la configuración. Esto se debe a que los circuitos y métodos para la realización de transformadas de coseno discretas y transformadas de coseno discretas inversas fueron desarrollados antes de establecerse las normas MPEG.

En el sistema MPEG, como se ha descrito anteriormente, el compresor implementa, por ejemplo, la codificación predictiva entre imágenes con compensación de movimiento para obtener la señal de imagen con movimiento. En esta técnica, la señal de imagen con movimiento es dividida en bloques, se obtiene un bloque de diferencias del bloque de imagen en curso, y se obtiene un bloque de adaptación aplicando compensación de movimiento a una imagen reconstruida, el bloque de diferencias es transformado ortogonalmente utilizando el tratamiento de transformada de coseno discreta, los coeficientes de transformada resultantes son cuantificados, los coeficientes de transformada cuantificados son sometidos a codificación de longitud variable, y los coeficientes de transformada codificados son ensamblados con información de modo de predicción, información de magnitud de incremento de cuantificación y vectores de movimiento, para proporcionar la señal de imagen con movimiento comprimida.

El expansor aplica codificación de longitud variable inversa a los coeficientes de transformada codificados, cuantificación inversa a los coeficientes de transformada cuantificados resultantes de la codificación de longitud variable inversa, y tratamiento de transformada de coseno discreta inversa a los coeficientes de transformada resultantes de la cuantificación inversa. El bloque de diferencias restaurado resultante se añade a un bloque de adaptación obtenido aplicando compensación de movimiento a la imagen reconstruida en respuesta al vector de movimiento. El bloque de imagen reconstruido resultante se almacena como bloque de una imagen reconstruida, que proporciona una imagen de la señal de imagen con movimiento de salida, y también está disponible para ser utilizada como imagen de referencia.

40 El compresor incluye un decodificador local que deduce, de los coeficientes de transformada cuantificados, imágenes reconstruidas para ser utilizadas en la realización de la codificación predictiva. El decodificador local incluye un cuantificador inverso y un circuito de transformada ortogonal inversa.

Si la configuración del circuito de transformada de coseno discreta inversa en el decodificador local es diferente de la del circuito de transformada de coseno discreta inversa utilizado en el expansor, existen casos en los cuales las imágenes reconstruidas generadas por el decodificador local en el compresor son diferentes de las imágenes reconstruidas generadas por el expansor. La dependencia del tratamiento de transformada de coseno discreta inversa de la implementación puede originar problemas cuando la señal de imagen con movimiento comprimida generada por un compresor que cumple la norma MPEG es registrada en un medio de registro, tal como un disco óptico, etc., para distribución al público. Cuando la señal de imagen con movimiento comprimida reproducida del disco óptico es expandida por expansores fabricados y comercializados por diferentes fabricantes, la imagen reconstruida puede ser diferente de la imagen original. Adicionalmente, las diferencias pueden depender del expansor real utilizado. Pueden producirse incompatibilidades similares entre expansores diferentes cuando la señal de imagen con movimiento comprimida es distribuida por un sistema de distribución, tal como un sistema de difusión terrestre o por satélite, un sistema telefónico, un sistema ISDN (Red Digital de Servicios Integrados –"Integrated Services Digital Network"), un sistema de distribución por cable o por fibra óptica, etc.

Los errores de desadaptación son particularmente problemáticos cuando se realiza una codificación predictiva inter imágenes. La codificación predictiva inter imágenes puede ser una codificación inter campos o una codificación inter cuadros. La codificación predictiva inter imágenes puede hacer que los errores de desadaptación se acumulen hasta un punto que produzcan defectos fatales en las imágenes reconstruidas.

En la compresión de señal de imagen con movimiento realizada por el sistema MPEG, cada secuencia de video se divide en Grupos de Imágenes (GOPs –"Groups of Pictures") de, por ejemplo, ocho o doce imágenes. Cada imagen se clasifica como imagen I, imagen P o imagen B, como se ha descrito anteriormente.

# ES 2 389 797 T3

Una imagen B no se utiliza como imagen de referencia para realizar la predicción de movimiento. Por tanto, un error de desadaptación que se produzca en una imagen B no origina errores en otras imágenes.

Cuando se produce un error de desadaptación en una imagen P, la imagen que contiene el error de desadaptación se almacena en la memoria de imagen para ser utilizada en la codificación predictiva. Consiguientemente, cuando se realiza la codificación predictiva inter imágenes, el error contenido en la imagen P almacenada en la memoria de imagen se distribuye gradualmente hacia las imágenes P y las imágenes B deducidas de la misma por la codificación predictiva. El error se acumula hasta que la imagen es sustituida por una imagen I o por una imagen P que no contienen tal error.

Similarmente, cuando se produce un error de desadaptación en una imagen I, la imagen reconstruida que contiene el error de desadaptación se almacena en la memoria de imagen para ser utilizada en la codificación predictiva. Consiguientemente, cuando se realiza la codificación predictiva inter imágenes, el error contenido en la imagen I almacenada en la memoria de imagen se distribuye hacia las imágenes P e imágenes B deducidas de la misma por la codificación predictiva. El error se acumula hasta que la imagen es sustituida por una nueva imagen I que carece de tal error.

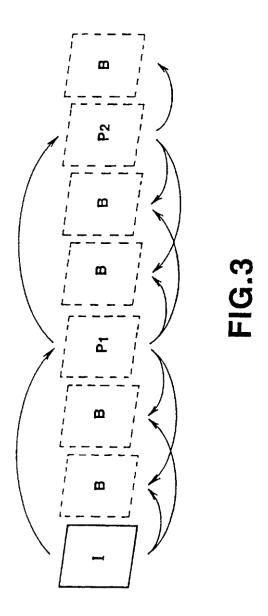

- La acumulación de error se ilustra en la figura 3. En la figura 3, si el error de desadaptación en la decodificación de una imagen I es EI, y el error de desadaptación en la decodificación de la imagen P P1 es EP1, el valor del error en la imagen P reconstruida P1 es EI + EP1. Adicionalmente, cuando el error de desadaptación en la decodificación de la imagen P P2 es EP2, el valor del error en la imagen P reconstruida P2 es EI + EP1 + EP2. Incluso si los errores de desadaptación individuales son pequeños, la acumulación gradual de estos errores dará lugar a un gran error.

- Los errores de desadaptación producidos por el tratamiento de transformada de coseno discreta inversa utilizado en los decodificadores MPEG tanto en el compresor como en el expansor, pueden ser clasificados en dos tipos diferentes:

- Tipo (1): Errores resultantes de una precisión de cálculo insuficiente.

15

30

35

40

45

50

Tipo (2): Errores resultantes de diferencias sistemáticas en el redondeo.

La norma MPEG establece un requerimiento para la precisión de las operaciones. Sin embargo, este requerimiento no es tan riguroso que pueda garantizar que no se produzca un error de desadaptación. Por consiguiente, puede producirse un error de desadaptación de tipo (1) entre dispositivos de transformada de coseno discreta inversa cuya precisión de cálculo satisfaga el requerimiento de la norma MPEG.

Las salidas del tratamiento de transformada de coseno discreta inversa son números enteros. Por tanto, después de realizarse el tratamiento de transformada de coseno discreta inversa utilizando números reales, los resultados del tratamiento deben redondearse. En general, los resultados del tratamiento se redondean al número entero más próximo. Sin embargo, se produce un problema cuando el resultado del tratamiento matemático es de la forma \*.5, donde \* es un número entero. La norma MPEG no define como deberá redondearse un resultado de tratamiento de la forma \*.5. Algunos dispositivos de transformada de coseno discreta inversa redondean \*.5 hacia arriba, y otros dispositivos de transformada de coseno discreta inversa redondean \*.5 hacia abajo. Adicionalmente, existen casos en los cuales el redondeo hacia arriba o el redondeo hacia abajo dependen del signo del resultado del tratamiento. Los errores de desadaptación resultantes de los errores de redondeo sistemáticos que se acaban de describir son errores de desadaptación del tipo (2).

Los errores de desadaptación del tipo (1) difieren de los errores de desadaptación del tipo (2) en que los errores del tipo (1) se producen aleatoriamente, mientras que los errores del tipo (2) son sistemáticos. Debido a que los errores de tipo (1) son aleatorios, los errores positivos y negativos se producen aproximadamente con la misma probabilidad. Por tanto, cuando se realiza la codificación predictiva durante un tiempo largo, puede suponerse que se cancelan los errores de desadaptación de tipo (1).

Por otra parte, puesto que los errores de desadaptación de tipo (2) son sistemáticos y son inherentes al propio tratamiento de transformada de coseno discreta inversa, tales errores tienen coherentemente la misma polaridad. Consiguientemente, cuando se realiza la codificación predictiva durante un tiempo largo, los errores de desadaptación serán acumulativos en una dirección. Aunque cada error de desadaptación de tipo (2) es solamente +1 o -1, si se acumulan muchos errores de desadaptación en una dirección, el error de desadaptación acumulativo será grande.

Puesto que los errores de desadaptación de tipo (1), aunque se generan incidentalmente, se cancelan con el tiempo, dichos errores no presentan relativamente problemas. Por otra parte, puesto que los errores de desadaptación de tipo (2) se acumulan en una dirección, los errores de desadaptación de tipo (2) son problemáticos. Debido a esto, es deseable evitar que se produzcan errores de desadaptación acumulativos del tipo (2).

Ha sido propuesto en el sistema MPEG1 realizar el tratamiento antes de los cálculos de transformada de coseno discreta inversa para evitar que se produzcan errores de desadaptación de tipo (2). El tratamiento ajusta los coeficientes de transformada de todas las componentes a un valor impar, excepto para el coeficiente de transformada de la componente (0,0) de un macrobloque de una imagen codificada según el sistema intra imágenes (un "macrobloque intra"). En un macrobloque intra, la componente (0,0) es la componente continua. Como se muestra en la figura 4, por ejemplo, los coeficientes de transformada de las componentes (0,1), (7,1), (2,3), (5,3), (1,5), (6,5), (3,7) y (4,7) son todos inicialmente iguales a 568. Puesto que este es un número par, el pretratamiento fija los valores de esos coeficientes a un valor impar, por ejemplo 567. Cuando se aplica tratamiento de transformada de coseno discreta inversa a los coeficientes de transformada pretratados, nunca se producen resultados fraccionarios.

10

15

5

Puesto que la componente continua del macrobloque intra es muy importante para el aspecto de la imagen obtenida de la señal de imagen con movimiento comprimida, su precisión está limitada solamente a ocho bits. Dicha magnitud no se somete a conversión a un valor impar, puesto que esto degradaría la precisión de esta componente importante. Por otra parte, todos los coeficientes de transformada resultantes de transformar un macrobloque de una imagen codificada utilizando codificación inter imágenes (un "macrobloque no intra"), se someten a un tratamiento similar al de los coeficientes de transformada de las componentes, que no correspondan a la componente continua, de un macrobloque intra para restringir los coeficientes de transformada solamente a valores impares.

20

El tratamiento según el cual los valores de los coeficientes de transformada sometidos a tratamiento de transformada de coseno discreta inversa se fijan todos en un valor impar, se denomina tratamiento de conversión a valor impar.

25

Mediante la aplicación del tratamiento de conversión a valor impar, el tratamiento de transformada de coseno discreta inversa tanto en el compresor como en el expansor realizará el redondeo de acuerdo con una regla común. Esto hará posible mantener una calidad de imagen coherente entre expansores diferentes.

30

Sin embargo, a pesar del tratamiento de conversión a valor impar descrito anteriormente, los errores de desadaptación de tipo (2) acumulativos descritos anteriormente se producirán aun en procesadores MPEG, porque el tratamiento de transformada de coseno discreta inversa puede producir aun resultados del tipo \*.5, donde \* indica un número entero. Las circunstancias que conducen a un resultado de \*.5 se describirán a continuación utilizando como ejemplo la transformada de coseno discreta inversa bidimensional de 8 x 8 utilizada en el sistema MPEG.

La transformada de coseno discreta inversa bidimensional de 8 x 8 se expresa mediante la siguiente ecuación:

$$f(x,y) = \frac{1}{4} \sum_{u=0}^{7} \sum_{v=0}^{7} C(u)C(v)F(u,v)\cos\left[\frac{(2x+1)ux\pi}{16}\right] \cos\left[\frac{(2y+1)vy\pi}{16}\right]$$

$$u,v,x,y = 0,1,...,7 \qquad ... (1)$$

$$C(u),C(v) = \frac{1}{\sqrt{2}}(u,v=0)$$

$= I(u,v \neq 0)$

35

En la ecuación anterior, F(u, v) indica los coeficientes de la transformada de coseno discreta sometidos a la transformada de coseno discreta inversa bidimensional. En la ecuación (1), cada valor de salida de la transformada de coseno discreta inversa es un número real, es decir un número racional o un número irracional. Debido a que \*.5 es un número racional, haciendo que el valor de salida de la transformada de coseno discreta inversa sea un número irracional, se evitará la generación de un error de desadaptación acumulativo. Por otra parte, cuando el valor de salida es un número racional, es posible que el valor de salida sea \*.5.

40

45

Los coeficientes F(0,0), F(0,4), F(4,0), F(4,4) de la transformada de coseno discreta son coeficientes de transformada de coseno discreta especiales. Cuando cualquiera de estos coeficientes de transformada de coseno discreta tiene un valor no nulo, el valor de salida de la transformada de coseno discreta inversa es un número racional. Los valores de salida de la transformada de coseno discreta inversa en este caso están expresados por la ecuación (2).

$$f(x,y) = \frac{1}{4}F(0,0)$$

$$f(x,y) = \frac{1}{4\sqrt{2}}F(0,4)\cos\frac{2y+1}{4}\pi$$

$$f(x,y) = \frac{1}{4\sqrt{2}}F(0,4)\cos\frac{2x+1}{4}\pi$$

$$f(x,y) = \frac{1}{4}F(4,4)\cos\frac{2x+1}{4}\pi\cos\frac{2y+1}{4}\pi$$

$$donde\cos\frac{2x+1}{4}\pi = +\frac{1}{\sqrt{2}}$$

... (2)

De este modo, cuando solamente tiene un valor no nulo uno de los coeficientes especiales F(0,0), F(0,4), F(4,0), F(4,4) de transformada de coseno discreta que es múltiplo de 4, pero no múltiplo de 8, el valor de salida es de la forma \*.5.

5 Cuando los cuatro coeficientes especiales de transformada de coseno discreta son los únicos coeficientes con un valor no nulo, el valor de salida de la transformada de coseno discreta inversa está expresado por la ecuación (3).

$$F(x,y) = \frac{1}{4}F(0,0) + \frac{1}{4\sqrt{2}}F(0,4)\cos\frac{2y+1}{4}\pi + \frac{1}{4\sqrt{2}}F(4,0)\cos\frac{2x+1}{2}\pi$$

$$+ \frac{1}{4}F(4,4)\cos\frac{2x+1}{4}\pi\cos\frac{2y+1}{4}\pi \qquad ... (3)$$

Con diferentes combinaciones de x e y, la función f(x,y) de la ecuación (3) puede tener los siguientes valores:

$$\frac{1}{8}[F(0,0) + F(0,4) + F(4,0) + F(4,4)]$$

$$\frac{1}{8}[F(0,0) + F(0,4) - F(4,0) - F(4,4)]$$

$$\frac{1}{8}[F(0,0) - F(0,4) + F(4,0) - F(4,4)] \qquad ... (4)$$

$$\frac{1}{8}[F(0,0) - F(0,4) - F(4,0) + F(4,4)]$$

De este modo, cuando los valores de los cuatro coeficientes especiales son tales que cualquiera de las expresiones establecidas en la ecuación (4) es múltiplo de 4 pero no es múltiplo de 8, se producirá un resultado de la forma \*.5.

Así, cuando los cuatro coeficientes especiales tienen valores no nulos, existe una alta probabilidad de que el valor de salida de la transformada de coseno discreta inversa sea de la forma \*.5.

También, diversos pares simétricos de coeficientes de transformada de coseno discreta con valores no nulos, diferentes de los cuatro coeficientes especiales que se acaban de comentar, pueden producir un valor de salida de la forma \*.5:

10

- (1) cuando el par de coeficientes X(2n+1, 2m+1), X(2m+1, 2n+1) tienen los mismos valores no nulos y el valor es múltiplo de 4 pero no múltiplo de 8, o

- (2) cuando el par de coeficientes X(2n+1, 2n+1), X(8-2n-1, 8-2n-1) tienen los mismos valores no nulos, y el valor es múltiplo de 4 pero no múltiplo de 8.

15

En las anteriores expresiones, X(i, j) es el coeficiente de transformada de una componente de una transformada de coseno discreta bidimensional de 8 x 8.

Cuando es comprimida una señal de imagen con movimiento real por el compresor de acuerdo con el sistema MPEG, se generan frecuentemente coeficientes de transformada de coseno discreta no nulos en las configuraciones que se acaban de mencionar, que pueden producir un valor de salida de transformada de coseno discreta inversa de la forma \*.5. Además, los valores de los cuatro coeficientes especiales son no nulos la mayor parte del tiempo.

Puesto que la causa más común de un resultado \*.5 es la combinación de coeficientes de transformada de coseno discreta en la cual los valores de los cuatro coeficientes especiales no son nulos, el hecho de evitar que se produzca un error de desadaptación en respuesta a los cuatro coeficientes especiales reducirá sustancialmente la probabilidad de que aparezca un error de desadaptación.

En la figura 5 se muestra el método de tratamiento mediante el cual se cuantifican inversamente según la norma MPEG1 un macro bloque intra y un macro bloque no intra. En la figura 5, QAC(i, j) es el coeficiente de transformada de coseno discreta de orden (i, j), Wi(i, j) es el elemento de orden (i, j) de una matriz de ponderación, mquant es el coeficiente de cuantificación, y rec(i, j) es el coeficiente de transformada de coseno discreta cuantificado inversamente de orden (i, j). El método de tratamiento está escrito en la sintaxis del lenguaje de programación C. La sintaxis de este lenguaje está expuesta en la divulgación de Herbert Schildt: "Using Turbo C" (Uso del Turbo C),

35 Osborne McGraw Hill (1988), especialmente en las páginas 83-87.

Los coeficientes de transformada de coseno discreta cuantificados son cuantificados inversamente, y los coeficientes de transformada de coseno discreta resultantes son sometidos a continuación a tratamiento de transformada de coseno discreta inversa. Sin embargo, en el sistema MPEG1, a los coeficientes de transformada de coseno discreta que tienen un valor par se les suma +1 o -1 para asegurar que los coeficientes de transformada de coseno discreta sometidos a tratamiento de transformada de coseno discreta inversa tienen todos valores impares. Como resultado de esta operación, por ejemplo, cuando solamente el primero de los cuatro coeficientes especiales F(0,0) tiene un valor no nulo, porque se produce un error de desadaptación cuando F(0,0) es múltiplo de cuatro pero no es múltiplo de ocho, si los coeficientes de transformada de coseno discreta se tratan de modo que tengan todos un valor impar, el resultado, cuando el coeficiente de transformada de coseno discreta se somete a tratamiento de transformada de coseno discreta inversa, no puede ser igual a \*.5. Similarmente, cuando solamente uno de los otros cuatro coeficientes especiales F(0,4), F(4,0), F(4,4) tiene un valor no nulo, se producirá un error de desadaptación. Sin embargo, cuando varios de los cuatro coeficientes especiales tienen un valor no nulo, como puede verse en la figura 4, o cuando se producen pares de coeficientes dispuestos simétricamente, como en los casos (1) y (2) mencionados anteriormente, el hecho de hacer que todos los coeficientes de transformada de coseno discreta tengan un valor impar no impedirá que se produzca un error de desadaptación.

Por tanto, el proceso de conversión a valor impar del sistema MPEG1 no evitará que se produzca un error de desadaptación acumulativo cuando dos o más de los coeficientes de transformada de coseno discreta tienen un valor no nulo. Además, el tratamiento de conversión a valor impar del sistema MPEG1 reduce en un factor de 2 la resolución de los coeficientes de transformada cuantificados, puesto que no se admiten coeficientes de transformada con valores pares. Esto degrada la calidad de la imagen. Si se requiere una alta calidad de imagen, esto es un problema. Es claramente deseable un modo de evitar errores de desadaptación acumulativos mejor que el propuesto en la norma MPEG1.

60

65

40

45

50

La invención proporciona un circuito de conversión a valor impar de la suma, destinado a recibir un bloque de coeficientes de transformada de coseno discreta (DCT –"discrete cosine transform") y tratarlos con el fin de suministrar como salida un bloque de coeficientes de transformada de coseno discreta convertidos a valor impar en la suma, al objeto de evitar que se produzca un error de desadaptación cuando los coeficientes de transformada de coseno discreta convertidos a valor impar en la suma son transformados de forma ortogonal inversa mediante un

tratamiento de transformada de coseno discreta inversa, de tal manera que dicho circuito comprende: un acumulador para determinar la suma de los coeficientes de transformada de coseno discreta del bloque de coeficientes de transformada de coseno discreta; un circuito de determinación de paridad, destinado a juzgar o determinar si la suma de los coeficientes de transformada de coseno discreta determinada por el acumulador es un número impar o un número par; y un inversor de paridad, destinado a cambiar la paridad de al menos uno de los coeficientes de transformada de coseno discreta del bloque con el fin de hacer que la paridad de la suma de los coeficientes de transformada de coseno discreta sea impar solo cuando el circuito de determinación de paridad determine que la paridad de la suma de los coeficientes de transformada de coseno discreta es par.

10 Se describirá ahora el modo en que el invento evita los errores de desadaptación acumulativos.

Un examen de la ecuación (4) muestra que se produce desadaptación cuando las expresiones de la ecuación generan un resultado de (2n + 1)/2, donde n es un número entero cualquiera.

15 La ecuación (4) puede resumirse como:

5

20

45

50

60

$$f(x, y) = 1/8 ACC$$

donde ACC es la suma de todos los coeficientes.

La configuración de desadaptación más frecuente es:

$$f(x, y) = 1/8 ACC = (2n + 1)/2 = 1/8 (4*(2n + 1))$$

De esta expresión puede deducirse que, si ACC se convierte en un número impar, nunca se producirá un error de desadaptación.

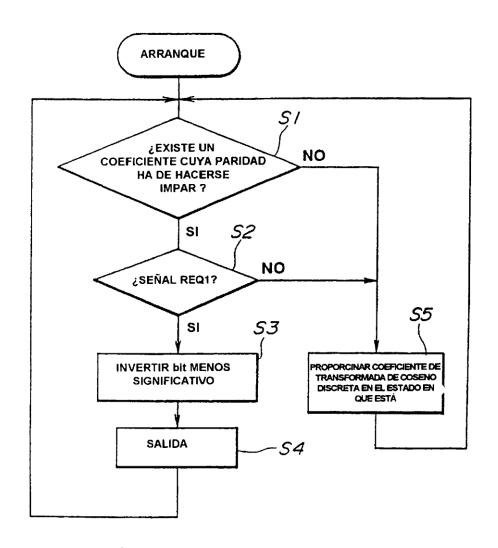

Consiguientemente, este invento utiliza un esquema para cuantificar inversamente los coeficientes de transformada de coseno discreta, y, a continuación, antes del tratamiento de transformada de coseno discreta inversa, para 30 calcular la suma de los coeficientes de transformada de coseno discreta. Si la suma de coeficientes de transformada de coseno discreta tienen valor par (es decir, la paridad de la suma es par), la paridad de uno de los coeficientes de transformada de coseno discreta se cambia para hacer impar la suma de los coeficientes de transformada de coseno discreta (es decir, para hacer impar la paridad de la suma). Es suficiente cambiar solamente la paridad de uno de los coeficientes de transformada de coseno discreta para hacer impar la suma de los coeficientes de 35 transformada de coseno discreta. Además, puede cambiarse la paridad del coeficiente que tiene la menor influencia en el valor de salida de la transformada de coseno discreta inversa. En otras palabras, este invento, al comprobar la paridad de la suma de los coeficientes de transformada de coseno discreta antes del tratamiento de transformada de coseno discreta inversa y, si la paridad de la suma es par, al cambiar la paridad de uno de los coeficientes de transformada de coseno discreta para hacer impar la suma de los coeficientes de transformada de coseno discreta, 40 evita eficazmente la aparición de errores de desadaptación.

Debe hacerse énfasis en que, de acuerdo con el invento, es suficiente cambiar la paridad de solamente uno de los coeficientes de transformada de coseno discreta para hacer impar la suma de los coeficientes de transformada de coseno discreta. El sistema MPEG1 hace impares todos los coeficientes de transformada de coseno discreta, lo cual reduce la resolución de los coeficientes de transformada de coseno discreta sometidos a tratamiento de transformada de coseno discreta inversa en un factor de dos. El procedimiento de evitación de errores de desadaptación de acuerdo con el invento, por otra parte, hace impar la suma de los coeficientes de transformada de coseno discreta de un modo tal que no disminuyen sustancialmente las precisiones de los valores de entrada y salida de la transformada de coseno discreta inversa. Cuando se aplica el método de acuerdo con el invento a un compresor de señal de imagen con movimiento, a un expansor de señal de imagen con movimiento comprimida, o a un aparato para transmitir una señal de imagen con movimiento comprimida, se hace mínima la degradación de la calidad de imagen.

Adicionalmente, cuando se aplica el invento al sistema MPEG, el incremento de cuantificación mínimo puede ser igual a 1, en contraste con el método de la técnica anterior en el cual el incremento mínimo de cuantificación era igual a 2.

Se describirá adicionalmente el invento en lo que sigue de la presente memoria, con referencia a la siguiente exposición de realizaciones a modo de ejemplo y a los dibujos que se acompañan, en los cuales:

La figura 1 es un diagrama de bloques que muestra la configuración de un aparato compresor convencional de señal de imagen con movimiento de acuerdo con el sistema MPEG.

La figura 2 es un diagrama de bloques que muestra la configuración de un aparato expansor convencional de señal de imagen con movimiento de acuerdo con el sistema MPEG.

La figura 3 ilustra la secuencia según la cual es comprimida una señal de imagen con movimiento en el

sistema MPEG.

5

10

15

25

35

40

45

50

55

La figura 4 muestra ejemplos reales de los valores de coeficientes de transformada de coseno discreta (DCT –"discrete cosine transform").

La figura 5 ilustra las operaciones de tratamiento utilizadas para cuantificar inversamente tanto macro bloques intra como macro bloques no intra en el sistema MPEG1 convencional.

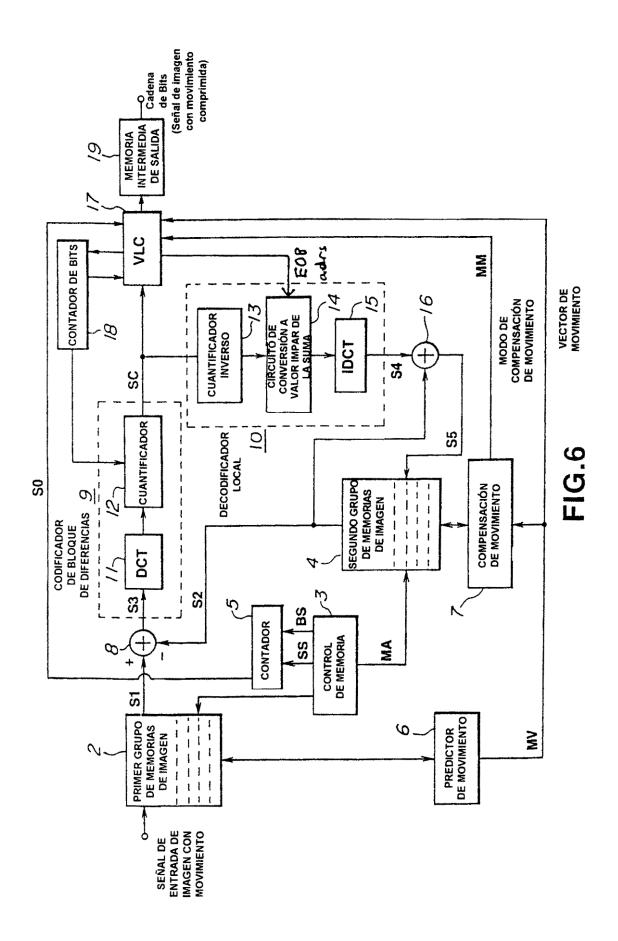

La figura 6 es un diagrama de bloques que muestra la configuración de una primera realización de un aparato compresor de señal de imagen con movimiento de acuerdo con el invento.

La figura 7 ilustra como se lee un bloque de coeficientes de transformada de coseno discreta utilizando exploración en zigzag.

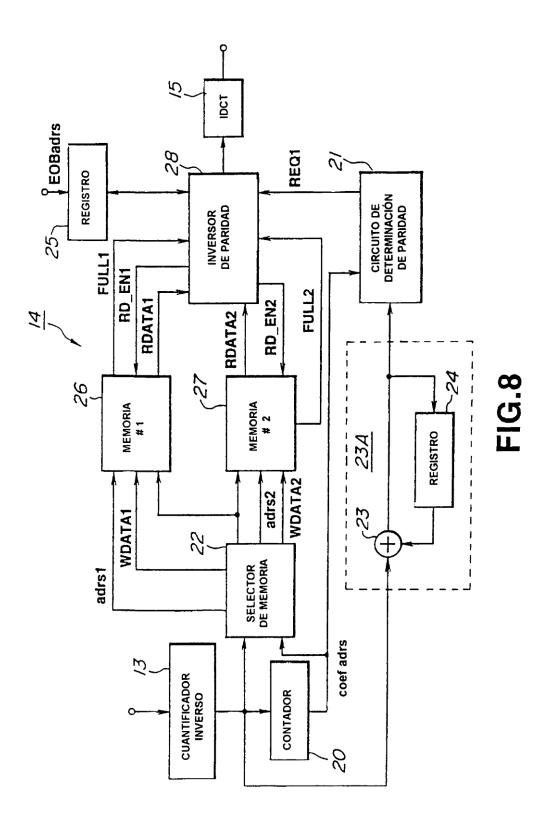

La figura 8 es un diagrama de bloques de una primera realización práctica del circuito 14 de conversión a valor impar de la suma representado en la figura 6.

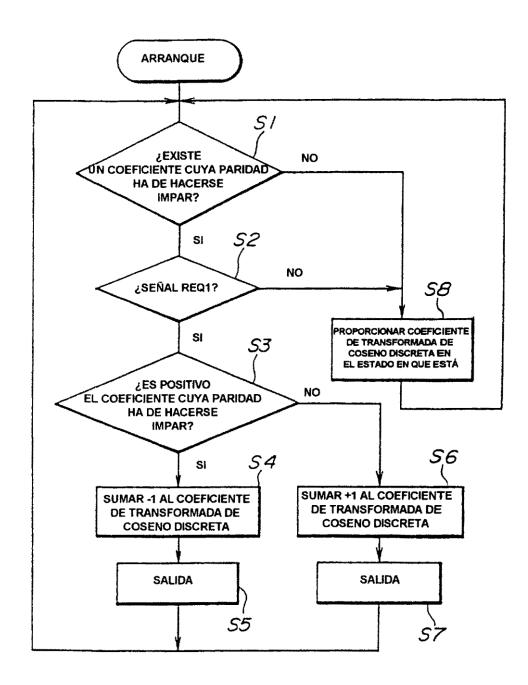

La figura 9 es un diagrama de flujo que ilustra el funcionamiento del circuito 14 de conversión a valor impar de la suma representado en la figura 8.

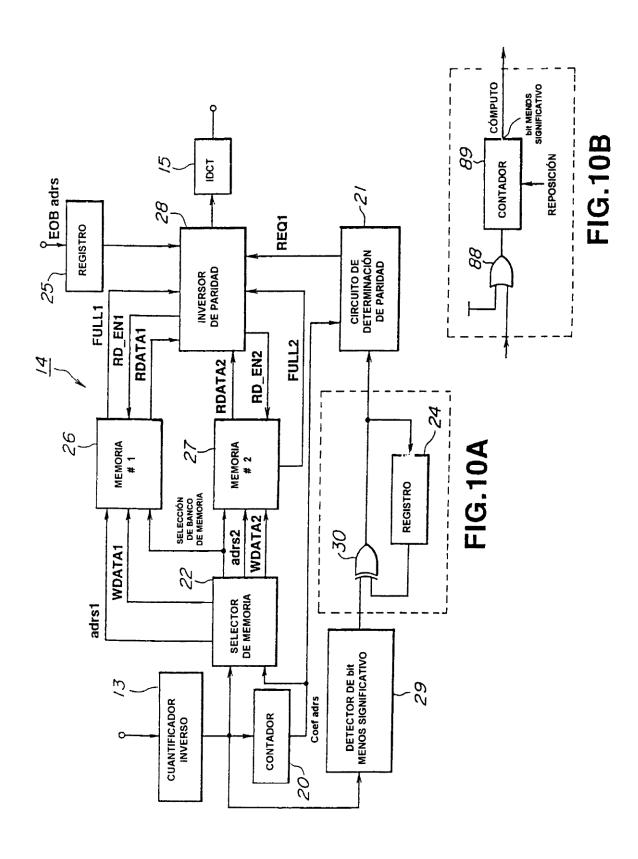

La figura 10A es un diagrama de bloques de una segunda realización del circuito de conversión a valor impar de la suma representado en la figura 6.

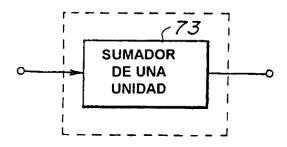

La figura 10B muestra una variante de la segunda realización del circuito de conversión a valor impar de la suma representado en la figura 6.

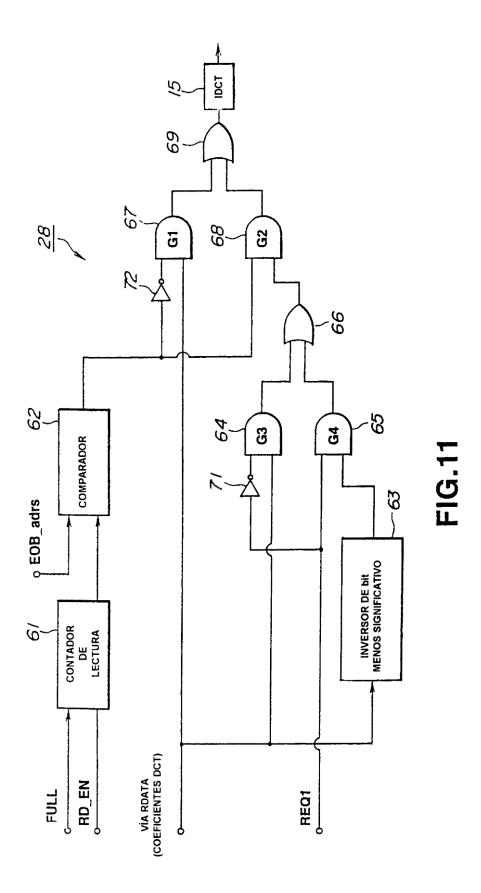

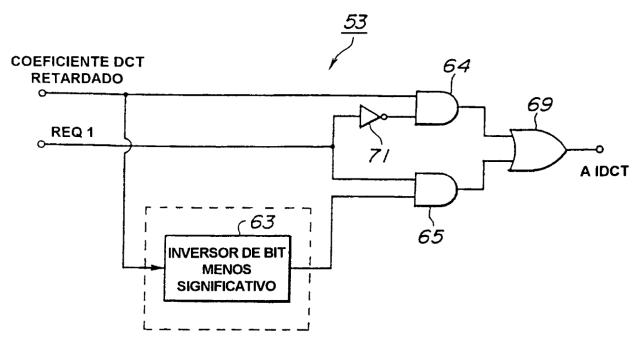

La figura 11 es un diagrama de bloques que muestra una primera realización del inversor de paridad representado en la figura 8.

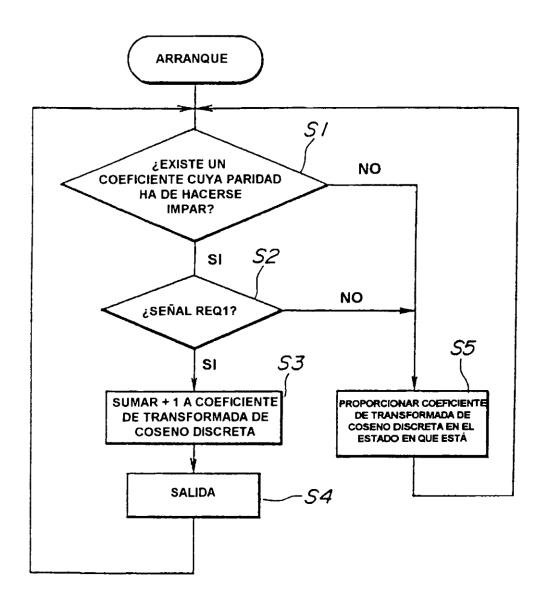

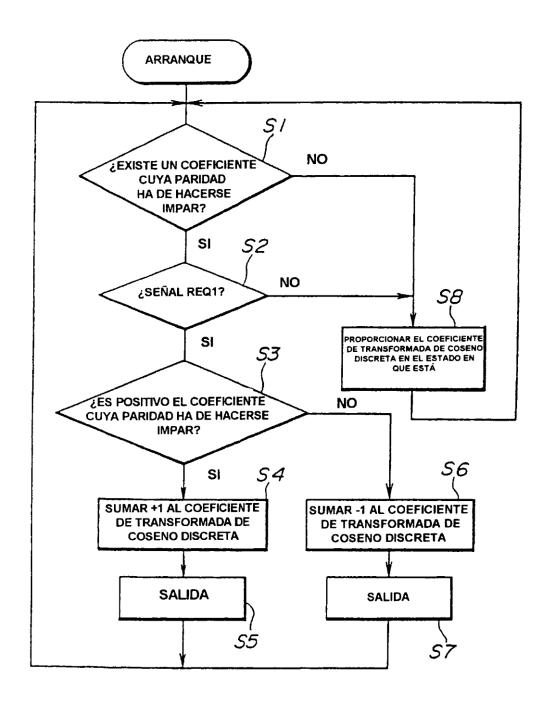

La figura 12 es un diagrama de flujo para explicar el funcionamiento de una segunda realización del inversor de paridad mencionado anteriormente.

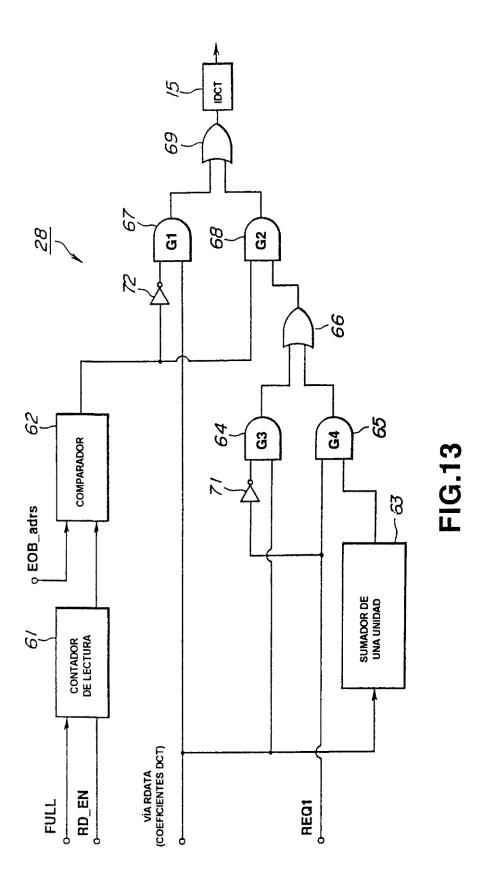

La figura 13 es un diagrama de bloques de la segunda realización del inversor de paridad mencionado anteriormente.

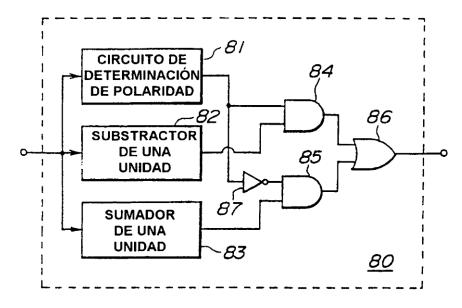

La figura 14 es un diagrama de flujo para explicar el funcionamiento de una tercera realización del inversor de paridad mencionado anteriormente.

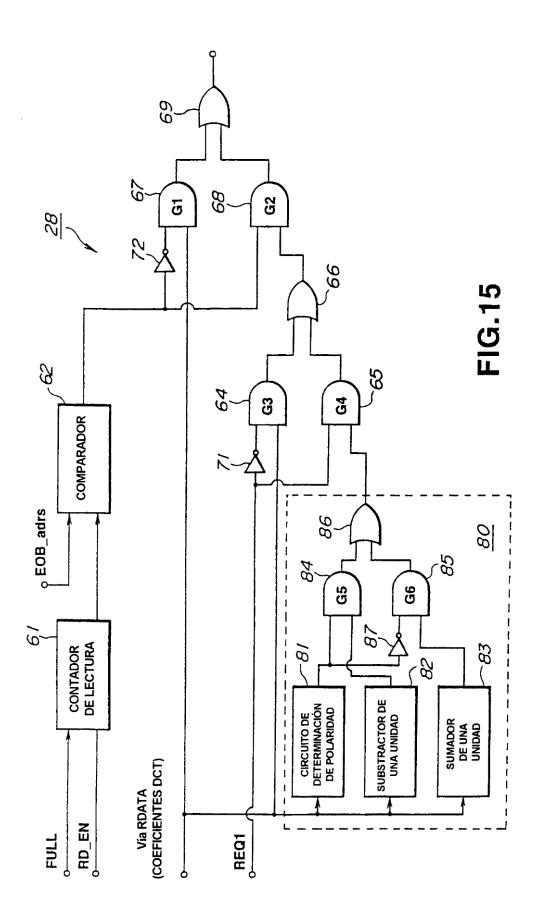

La figura 15 es un diagrama de bloques de la tercera realización del inversor de paridad mencionado anteriormente.

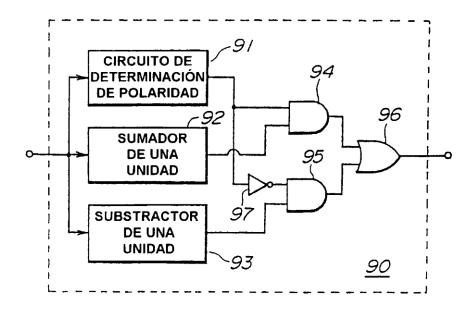

La figura 16 es un diagrama de flujo para explicar el funcionamiento de una cuarta realización del inversor de paridad mencionado anteriormente.

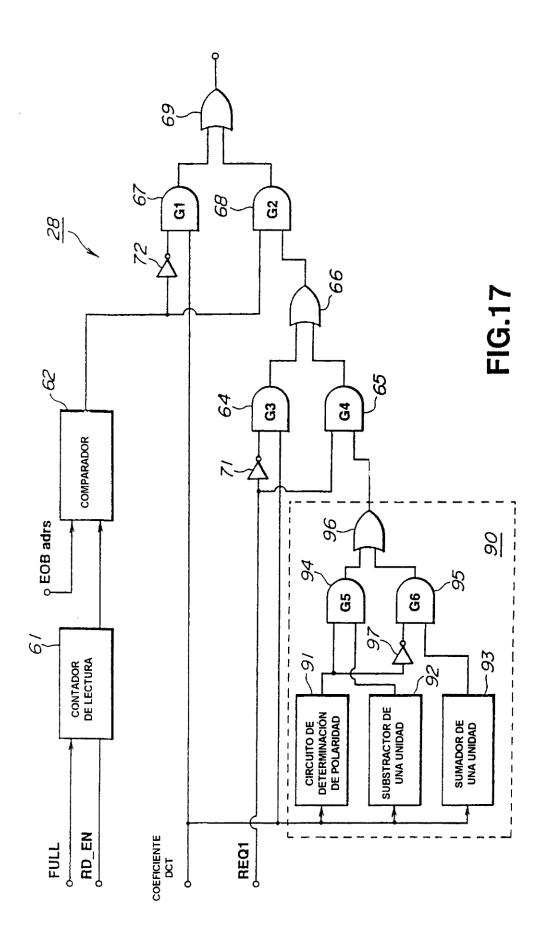

La figura 17 es un diagrama de bloques de la cuarta realización del inversor de paridad mencionado anteriormente.

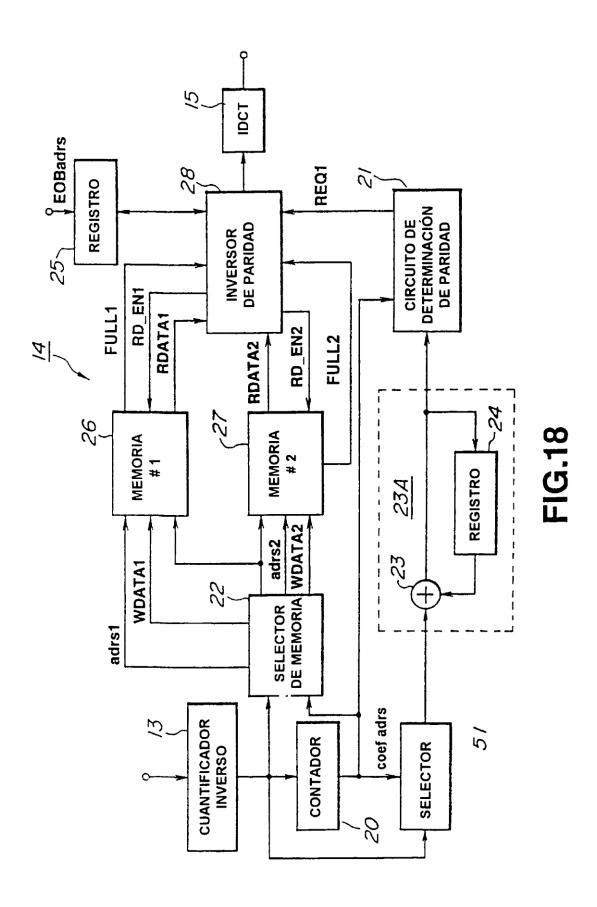

La figura 18 es un diagrama de bloques de una tercera realización del circuito de conversión a valor impar de la suma representado en la figura 6.

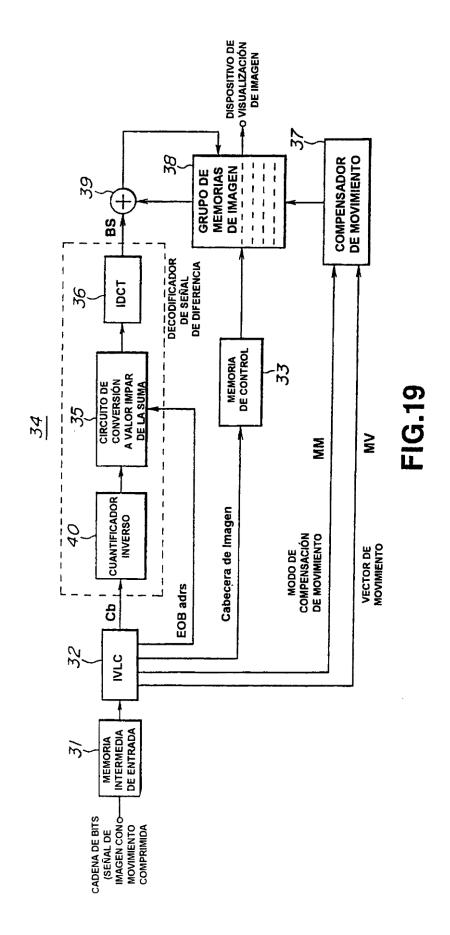

La figura 19 es un diagrama que muestra la configuración del primer aparato descompresor de señal de imagen con movimiento comprimida, proporcionado a modo de ejemplo, de acuerdo con el invento.

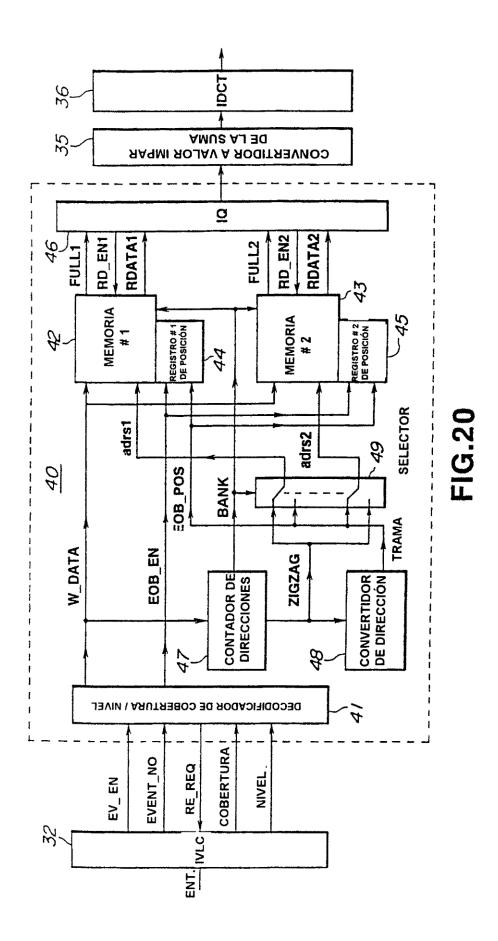

La figura 20 es un diagrama de bloques de un cuantificador inverso y convertidor de suma en número impar incluido en el aparato descompresor de señal de imagen con movimiento comprimida representado en la figura 19.

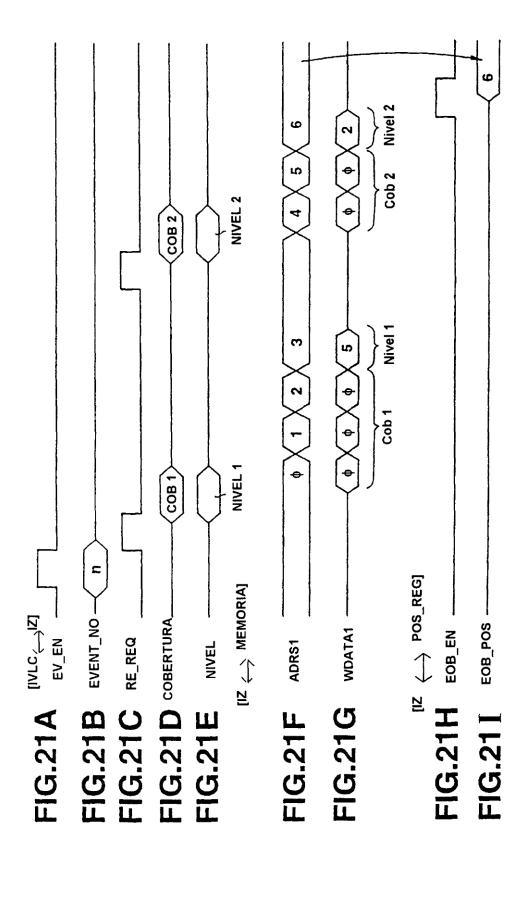

La figura 21 es un diagrama de temporización que explica el funcionamiento del cuantificador inverso y convertidor de suma en número impar mencionado anteriormente.

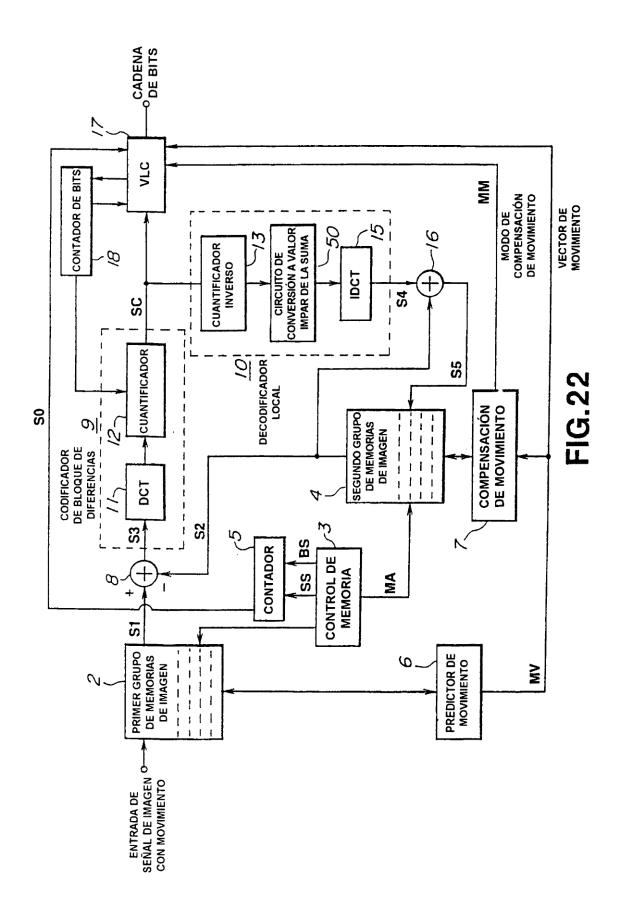

La figura 22 es un diagrama de bloques que muestra la configuración de un segundo aparato compresor de señal de imagen con movimiento, proporcionado a modo de ejemplo, de acuerdo con el invento.

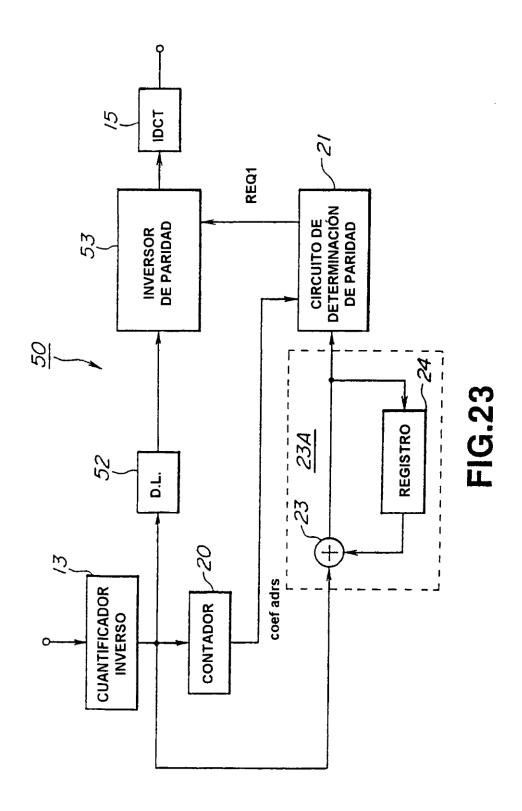

La figura 23 es un diagrama de bloques que muestra una primera realización del circuito convertidor de suma en número impar, perteneciente al aparato compresor de señal de imagen con movimiento ilustrado en la figura 22.

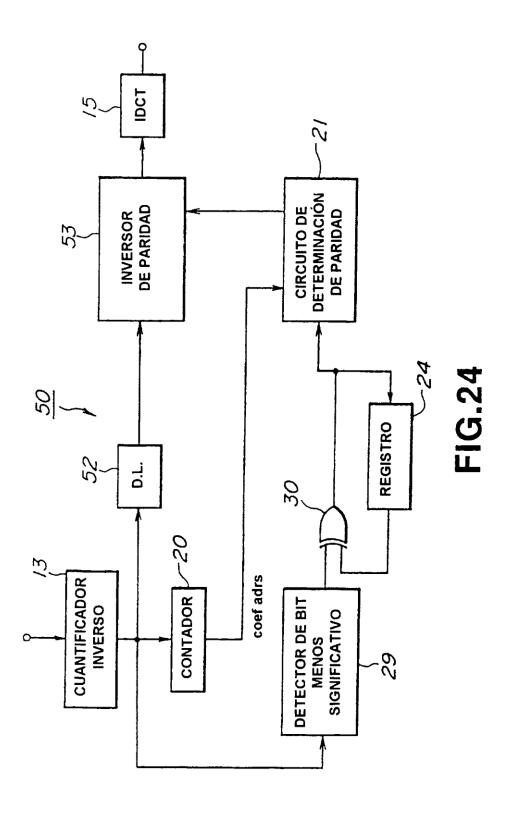

La figura 24 es un diagrama de bloques que muestra una segunda realización del circuito convertidor de suma en número impar, perteneciente al aparato compresor de señal de imagen con movimiento ilustrado en la figura 22.

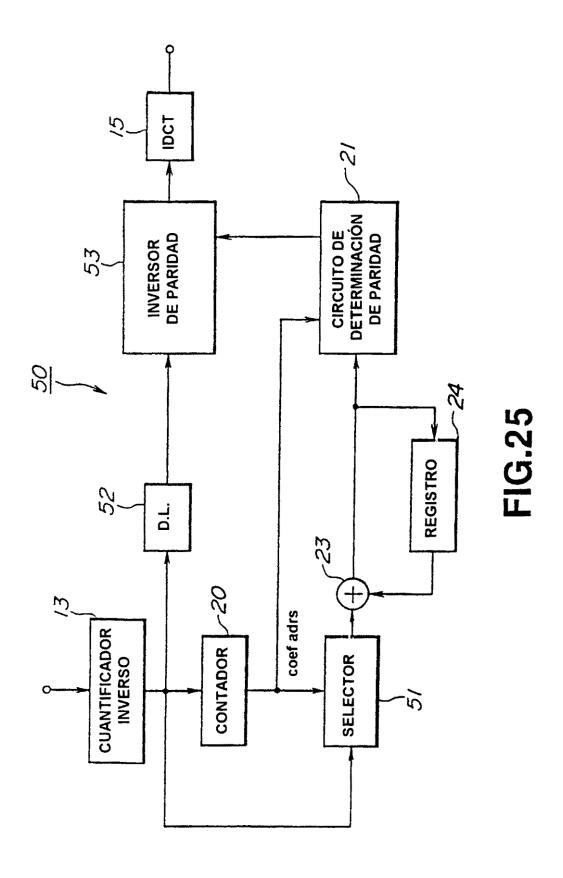

La figura 25 es un diagrama de bloques que muestra una tercera realización del circuito convertidor de suma en número impar, perteneciente al aparato compresor de señal de imagen con movimiento ilustrado en la figura 22.

La figura 26 es un diagrama de bloques que representa una realización del inversor de paridad incluido en los circuitos de conversión a valor impar de la suma ilustrados en las figuras 23-25.

La figura 27 muestra una primera variante del inversor de paridad representado en la figura 26.

La figura 28 representa una segunda variante del inversor de paridad ilustrado en la figura 26.

La figura 29 representa una tercera variante del inversor de paridad ilustrado en la figura 26.

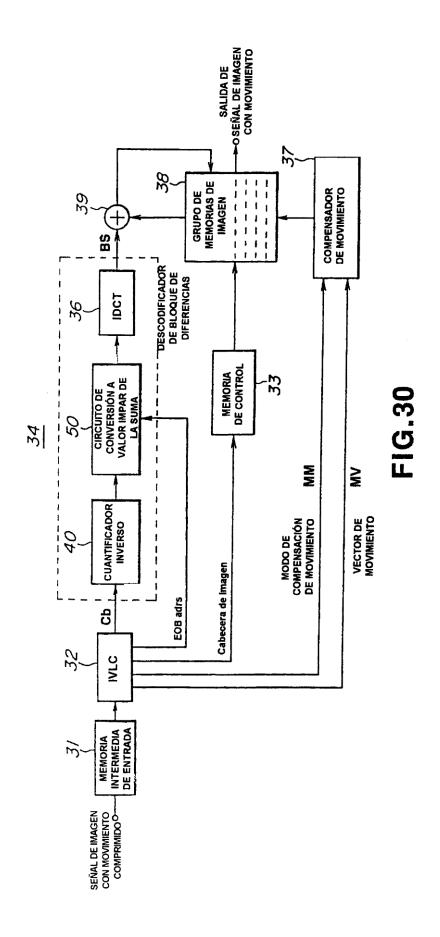

La figura 30 es un diagrama de bloques que muestra la configuración de un segundo aparato expansor de señal de imagen con movimiento comprimida, proporcionado a modo de ejemplo, de acuerdo con el invento.

Se describirán ahora con referencia a los dibujos realizaciones de un método de transformada de coseno discreta inversa, un aparato de transformada de coseno discreta inversa proporcionado a modo de ejemplo, un aparato compresor de señal de imagen con movimiento, un aparato descompresor de señal de imagen con movimiento comprimida, y un aparato de transmisión.

El invento se aplica a un sistema de codificación híbrido en el cual se combina la codificación predictiva con compensación de movimiento con el tratamiento de transformada de coseno discreta (DCT –"discrete cosine transform"). El sistema de codificación híbrido se describe en la norma ISO-IEC/JTC1/SC2/WG11 (popularmente denominada MPEG). La configuración básica del sistema híbrido de codificación MPEG es bien conocida. El informe de la norma VG11 incluye un glosario de términos útil que se utiliza en la presente memoria.

La codificación predictiva con compensación de movimiento es un método para reducir la redundancia de una señal de imagen con movimiento, explotando la correlación de la señal de imagen con movimiento en el dominio del tiempo. La predicción para compensación de movimiento de la imagen en curso (es decir, la imagen que se está codificando en cada momento) se realiza utilizando otra imagen, ya decodificada, de la señal de imagen con movimiento como imagen de referencia. Los errores resultantes de predicción con compensación de movimiento se incluyen en la señal comprimida junto con un vector de movimiento y un modo de predicción, etc. Esto reduce notablemente la cantidad de información en la señal de imagen con movimiento comprimida que se requiere para representar la imagen en curso.

La señal de error de predicción con compensación de movimiento es comprimida utilizando un compresor de señal que explota la correlación espacial de cada imagen que constituye la imagen en movimiento. El compresor de señal de diferencia incluye típicamente un circuito de transformada ortogonal, tal como un circuito de cálculo de la transformada de coseno discreta, y un cuantificador. La transformada de coseno discreta es una forma de transformada ortogonal que concentra la potencia de la señal en componentes de frecuencia específicas como resultado de la correlación bidimensional intra imágenes (cuadro o campo) de la imagen. De este modo, solamente están incluidos en la señal comprimida, bien sea directamente o después de compresión adicional, los coeficientes concentrados y distribuidos. Esto reduce adicionalmente la cantidad de información en la señal de imagen con movimiento comprimida que se requiere para representar la imagen en curso.

La codificación predictiva con compensación de movimiento inter imágenes puede realizarse entre cuadros de la señal de imagen con movimiento. Alternativamente, si la señal de imagen con movimiento es una señal entrelazada, la codificación predictiva con compensación de movimiento puede realizarse entre campos. Adicionalmente, la codificación predictiva con compensación de movimiento inter imágenes puede conmutarse adaptativamente entre codificación inter cuadros y codificación inter campos, dependiendo de las propiedades de la señal de imagen con movimiento.

#### 1. Primera Realización

5

10

15

20

25

30

45

50

55

60

65

En la figura 6 se muestra la configuración práctica del aparato compresor de señal de imagen con movimiento al cual se aplica el invento como se define en las reivindicaciones anexas. En el aparato representado en la figura 6, la señal de imagen con movimiento se divide en imágenes, y es comprimida imagen por imagen. Cada imagen se divide en bloques de imagen, y la imagen se comprime bloque por bloque. El bloque de imagen que se está comprimiendo en cada momento se denominará bloque de imagen en curso. El bloque de imagen en curso es un bloque de una imagen denominada imagen en curso.

La señal de imagen con movimiento, normalmente una señal de video, se suministra al primer grupo 2 de memorias de imagen, en el que se almacenan transitoriamente varias imágenes de la señal de imagen con movimiento. El controlador 3 de memoria controla la lectura de imágenes del primer grupo 2 de memorias de imagen y del segundo grupo 4 de memorias de imagen. El controlador 3 de memoria suministra también la señal SS de iniciación de línea de bloques y la señal BS de iniciación de macrobloque al contador 5 de líneas matriciales/macrobloques. El controlador de memoria suministra estas señales, respectivamente, en sincronismo con cada línea de bloques y cada macrobloque de cada imagen (por ejemplo, la imagen en curso) leída del primer grupo 2 de memorias de imagen para compresión. Una línea de bloques es una fila horizontal de bloques que cubre el ancho de la imagen.

El predictor 6 de movimiento efectúa la predicción de movimiento realizando la adaptación de bloques entre el bloque de imagen en curso y varios bloques de las imágenes anterior y siguiente almacenadas en el primer grupo 2 de memorias de imagen. La adaptación de bloques se realiza utilizando bloques de, por ejemplo, 16 x 16 elementos de imagen. La señal de indicación de imagen de referencia con predicción de movimiento generada por el controlador 3 de memoria, selecciona los bloques de las imágenes anterior y siguiente almacenadas en el primer grupo 2 de memorias de imagen para comprobar su adaptación con el bloque en curso. El predictor 6 de movimiento suministra a un compensador 7 de movimiento, como vector MV de movimiento, la posición de un bloque en una de las imágenes anterior o siguiente almacenadas en el primer grupo 2 de memorias de imagen, para la cual son mínimas las diferencias entre el bloque y el bloque de imagen en curso, es decir los errores de predicción de movimiento.

En respuesta al vector MV de movimiento, el compensador 7 de movimiento hace que sea leído un bloque de cada una de las imágenes reconstruidas almacenadas en el segundo grupo 4 de memorias de imagen como bloque de adaptación potencial. La posición en las imágenes reconstruidas de la que se leen los bloques de adaptación potenciales está especificada por el vector MV de movimiento. La señal de indicación de imagen de referencia con

compensación de movimiento generada por el controlador 3 de memoria selecciona entonces uno de los bloques de adaptación potenciales leídos del segundo grupo 4 de memorias de imagen, como bloque de adaptación para el bloque en curso. Las imágenes reconstruidas almacenadas en el segundo grupo 4 de memorias de imagen son imágenes que han sido reconstruidas decodificando localmente los coeficientes de transformada de coseno discreta cuantificados generados por el codificador 9 de bloques de diferencias, que se describirá posteriormente.

5

10

15

40

45

50

55

60

65

La imagen reconstruida, de la cual es seleccionado el bloque de adaptación por la señal de indicación de imagen de referencia con compensación de movimiento, depende del modo de predicción de la imagen en curso. En el modo de predicción de avance, el bloque de adaptación se selecciona de una imagen reconstruida anterior. En el modo de predicción bidireccional, el bloque de adaptación se selecciona de una imagen reconstruida anterior y una imagen reconstruida futura, o bien puede generarse realizando una operación lineal (por ejemplo, cálculo del valor medio) sobre bloques de una imagen reconstruida anterior y una imagen reconstruida futura. Finalmente, cuando la imagen en curso es codificada en el modo de codificación intra imágenes, es decir la imagen es codificada sin predicción, se utiliza un bloque nulo, en el cual todos los valores de elementos de imagen están puestos a cero, como bloque de adaptación. Los bloques de adaptación leídos del segundo grupo 4 de memorias de imagen son modificados adaptativamente de tal modo que se selecciona para cada bloque de la señal de imagen con movimiento un bloque de adaptación que se adapta óptimamente.

El compensador 7 de movimiento selecciona el modo de predicción para cada imagen calculando primero la suma de los valores absolutos de las diferencias elemento de imagen por elemento de imagen en curso y los bloques de adaptación potenciales generados en los diferentes modos de predicción. A continuación, el compensador 7 de movimiento selecciona el modo de predicción para el cual esta suma es mínima. El compensador 7 de movimiento suministra la señal MM de modo de predicción, que indica el modo de predicción seleccionado, al codificador 17 de longitud variable (que se describirá posteriormente). El compensador 7 de movimiento hace también que el segundo grupo 4 de memorias de imagen suministre al circuito 8 generador de diferencias el bloque S2 de adaptación correspondiente al modo de predicción seleccionado.

El circuito 8 generador de diferencias recibe también el bloque S1 de imagen en curso de la señal de imagen con movimiento leída del primer grupo 2 de memorias de imagen, y calcula las diferencias elemento de imagen por elemento de imagen entre el bloque S1 de imagen en curso y el bloque S2 de adaptación. El circuito 8 generador de diferencias suministra al codificador 9 de bloques de diferencias el bloque S3 de diferencias resultante. El codificador 9 de bloques de diferencias comprime el bloque S3 de diferencias para formar el bloque SC de coeficientes de transformada cuantificados. El bloque SC de coeficientes de transformada cuantificados es suministrado al decodificador local 10, en el que es expandido para proporcionar el bloque S4 de diferencias recuperado. El decodificador local 10 del aparato compresor de señal de imagen con movimiento tiene una configuración similar a la del aparato expansor de señal de imagen con movimiento comprimida, que se describirá posteriormente, pero difiere en los detalles.

Se describirán ahora el codificador 9 de bloques de diferencias y el decodificador local 10.

El codificador 9 de bloques de diferencias comprende el circuito 11 de transformación de coseno discreta y el cuantificador 12, como se muestra en la figura 6. El circuito 11 de transformación de coseno discreta utiliza tratamiento de transformada de coseno discreta para transformar ortogonalmente el bloque S3 de diferencias proporcionado por el circuito 8 generador de diferencias. El circuito 11 de transformación de coseno discreta suministra el bloque resultante de coeficientes de transformada de coseno discreta al cuantificador 12. El cuantificador 12 cuantifica el bloque de coeficientes de transformada de coseno discreta para proporcionar el bloque SC de coeficientes de transformada cuantificados.

El decodificador local 10 comprende el cuantificador inverso 13, el circuito 14 de conversión a valor impar de suma y el circuito 15 de transformada de coseno discreta inversa, como se muestra en la figura 6. El cuantificador inverso 13 utiliza una tabla de cuantificación para cuantificar inversamente el bloque SC de coeficientes de transformada cuantificados generado por el cuantificador 12. El circuito 14 de conversión a valor impar de suma realiza una operación de inversión de paridad sobre el bloque resultante de coeficientes de transformada de coseno discreta cuando la suma de los mismos no es un número impar. Esto evita que se produzca un error de desadaptación cuando el bloque de coeficientes de transformada de coseno discreta cuya suma se ha convertido en un valor impar es sometido a transformada ortogonal inversa. El circuito 15 de transformada de coseno discreta inversa (IDCT – "inverse discrete cosine transform") realiza un tratamiento de transformada de coseno discreta inversa sobre el bloque de coeficientes de transformada de coseno discreta cuya suma ha sido convertida en un valor impar y que son generados por el circuito 14 de conversión a valor impar de suma, para proporcionar un bloque de diferencias recuperado.

Se describirá ahora la cuantificación realizada por el cuantificador 12. Cada bloque de coeficientes de transformada de coseno discreta de 8 x 8 es cuantificado. Cada bloque de una imagen comprimida en el modo de codificación intra imágenes (una imagen I) se denomina macrobloque intra. Cada bloque comprimido en un modo de codificación inter imágenes se denomina macrobloque no intra. Cuando es transformado ortogonalmente un macrobloque intra,

el coeficiente de transformada de coseno discreta de la componente (0,0) es el coeficiente de continua. El coeficiente de continua es cuantificado dividiendo por 8 dicho coeficiente, con redondeo, cuando se cuantifica con una precisión de ocho bits, por 4 cuando se cuantifica con una precisión de nueve bits, por 2 cuando se cuantifica con una precisión de once bits. La componente continua de un macro bloque intra se cuantifica de acuerdo con las siguientes ecuaciones, que están escritas en la sintaxis del lenguaje de programación C:

5

15

50

donde dc es el coeficiente de continua y QDC es el coeficiente de continua cuantificado.

Los coeficientes de transformada de coseno discreta, diferentes del coeficiente de continua, resultantes de transformar ortogonalmente un macrobloque intra (las "componentes de alterna"), son cuantificados determinando los factores de cuantificación ac (i,j) por ponderación de los coeficientes ac(i, j) de transformada de coseno discreta por la matriz Wi de ponderación, de acuerdo con la siguiente ecuación:

$$ac^{-}(i,j) = (16^{+} ac(i,j)) // Wi(i,j)$$

... (6)

Los coeficientes de la matriz Wi de ponderación son los siguientes:

A continuación, utilizando la ecuación siguiente, se cuantifican los factores ac (i,j) de cuantificación para determinar los niveles QAC(i, j) de cuantificación de los respectivos coeficientes de alterna.

$$QAC(i, j) = \frac{ac^{*}(i, j) + sign(ac^{*}(i, j)) * ((p * mquant)//q)}{(2 * mquant)} \dots (8)$$

En la ecuación anterior, p y q son números enteros fijos arbitrarios, por ejemplo p = 3 y q = 4, y mquant es el coeficiente de cuantificación.

Los coeficientes de transformada de coseno discreta resultantes de transformar ortogonalmente un macrobloque de codificación inter imágenes (un "macrobloque no intra") son cuantificados determinando los factores ac (i,j) de cuantificación mediante la ponderación de todos los coeficientes de transformada de coseno discreta obtenidos por transformación del macrobloque no intra, por la matriz Wn de ponderación de acuerdo con la ecuación siguiente:

$$ac^{-}(i,j) = (16^{+}ac(i,j)) // Wn(i,j)$$

... (9)

Los coeficientes de la matriz Wn de ponderación son los siguientes:

19 20 21 22 23 24 26 27

20 21 22 23 25 26 27 28

5 21 22 23 24 26 27 28 30

22 23 24 26 27 28 30 31

23 24 25 27 28 30 31 33

10

A continuación, utilizando la ecuación siguiente, se cuantifican los factores ac (i,j) de cuantificación para determinar los niveles QAC(i, j) de cuantificación de los coeficientes de alterna.

QAC(i,j) =  $ac^{-}(i,j) / (2^{+} mquant)$ if (mquant==odd)

=  $(ac^{-}(i,j)+1 / (2^{+} mquant)$ 20

if (mquant==even AND ac-<0)

=  $(ac^{-}(i,j)-1 / (2^{+} mquant)$ if (mquant==even AND ac->0)

25

45

50

55

60

Los niveles QAC(i, j) de cuantificación resultantes se suministran al codificador 17 de longitud variable y al decodificador local 10 como el bloque anteriormente descrito de coeficientes SC de transformada de coseno discreta cuantificados.

El codificador 17 de longitud variable aplica codificación de longitud variable al bloque de coeficientes de transformada de coseno discreta. El codificador 17 de longitud variable determina diferencias entre los coeficientes de transformada cuantificados en los cuatro bloques de luminancia que constituyen cada macrobloque y el coeficiente de continua del respectivo macrobloque intra. El codificador de longitud variable utiliza a continuación una tabla de codificación de longitud variable para aplicar codificación de longitud variable a los valores de diferencia resultantes. Esta técnica aprovecha la alta correlación existente entre los cuatro bloques de luminancia adyacentes, lo cual significa que los coeficientes de continua tienen sustancialmente el mismo valor. El codificador 17 de longitud variable determina también las diferencias entre los coeficientes cuantificados de dos bloques de diferencia de color, y utiliza la tabla de codificación de longitud variable para aplicar codificación de longitud variable a los valores de diferencia resultantes.

40 La tabla de codificación de longitud variable para los coeficientes de luminancia y la correspondiente a las diferencias de color son diferentes entre sí.

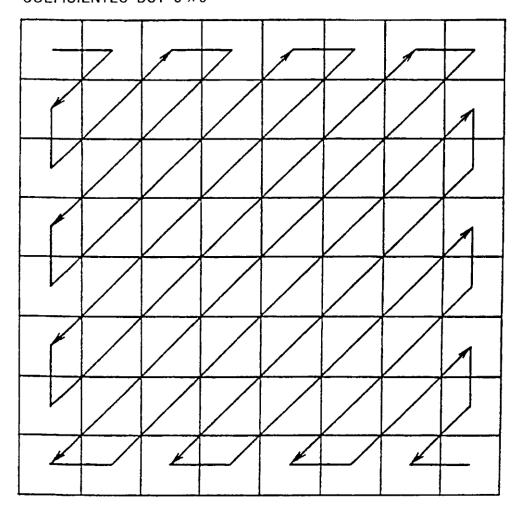

El codificador 17 de longitud variable aplica codificación de longitud variable al bloque de coeficientes de transformada de coseno discreta cuantificados leyendo el bloque de coeficientes de transformada de coseno discreta cuantificados en orden de exploración en zigzag, comenzando con el coeficiente de transformada de coseno discreta de la componente (0,0), como se muestra en la figura 7. El bloque de coeficientes de transformada de coseno discreta cuantificados se lee en zigzag porque los coeficientes de transformada de coseno discreta no nulos resultantes del tratamiento de transformada de coseno discreta están concentrados en general en la proximidad de la componente (0,0). De este modo, la lectura de los coeficientes de transformada de coseno discreta en zigzag aumenta la eficiencia de la codificación de longitud variable aumentando el campo de coeficientes de transformada de coseno discreta nulos consecutivos leídos entre cada uno de los coeficientes de transformada de coseno discreta no nulos.

El codificador 17 de longitud variable lee los coeficientes de transformada de coseno discreta en zigzag y determina el valor (en otras palabras, el nivel) de cada coeficiente de transformada de coseno discreta no nulo, y el número (en otras palabras, el campo de cobertura) de los coeficientes de transformada de coseno discreta nulos que le preceden. Este procedimiento realiza la codificación de longitud variable bidimensional del bloque de coeficientes de transformada de coseno discreta. Después de la codificación, los coeficientes del bloque se expresan mediante el número del campo de cobertura y pares de niveles. El codificador 17 de longitud variable añade también un código de dos bits (EOB) que indica el coeficiente de transformada de coseno discreta no nulo. El codificador 17 de longitud variable suministra a un convertidor de direcciones (no representado) la dirección del último coeficiente no nulo en orden de exploración en zigzag. El convertidor de direcciones convierte la dirección en orden de exploración en zigzag en una dirección, EOB\_adrs, en orden de exploración de trama. El codificador 17 de longitud variable suministra la dirección EOB\_adrs al circuito 14 de conversión a valor impar de suma.

# ES 2 389 797 T3

El circuito 14 de conversión a valor impar de suma almacena la dirección EOB\_adrs en orden de exploración de trama en el registro 25 representado, por ejemplo, en la figura 8, que se describirá posteriormente.

Se describirá ahora el cuantificador inverso 13. El cuantificador inverso 13 recibe el bloque SC de coeficientes de transformada de coseno discreta cuantificados procedente del codificador 10 de bloque de diferencias, y cuantifica inversamente el bloque de coeficientes de transformada de coseno discreta cuantificados para proporcionar un bloque de coeficientes de transformada de coseno discreta. En la práctica, el cuantificador inverso 13 cuantifica inversamente los coeficientes de continua cuantificados resultantes de transformar ortogonalmente un macrobloque intra utilizando el tratamiento definido por la ecuación (12) para proporcionar coeficientes de continua respectivos. El cuantificador inverso 13 cuantifica también inversamente los coeficientes de alterna resultantes de transformar ortogonalmente un macrobloque intra utilizando el tratamiento definido en la ecuación (13). Finalmente, el cuantificador inverso 13 cuantifica inversamente todos los coeficientes cuantificados resultantes de transformar ortogonalmente un macrobloque no intra utilizando el tratamiento definido en la ecuación (14).

```

15

rec(0, 0) = 8 * QDC

rec(0, 0) = 4 * QDC (9 bits)

rec(0, 0) = 2 * QDC (10 bits)

20

... (12)

rec(0, 0) = 1 * QDC (11 bits)

rec(i, j) = (mquant * 2 * QAC(i, j) * Wi(i, j)) / 16

25

if(QAC(i, j) == 0)

rec(i, j) = 0

... (13)

30

if(QAC(i,j) > 0)

rec(i,j) = ((2*QAC(i,j)+1)*mquant*Wn(i,j))/16

if(QAC(i,j) < 0)

35

rec(i,j) = ((2*QAC(i,j)-1)*mguant*Wn(i,j))/16

if(QAC(i, j) == 0)

... (14)

40

rec(i,j) = 0

```

45

50

55

El bloque resultante de coeficientes de transformada de coseno discreta es transferido desde el cuantificador inverso 13 hasta el circuito 14 de conversión a valor impar de suma, de cuya transferencia se ilustra un ejemplo práctico en la figura 8.