OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 390 311

(2011.01)

51 Int. Cl.: H04B 1/7075

**H04B 1/708** (2011.01) **H04B 1/709** (2011.01)

**G06F 17/15** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Número de solicitud europea: 08751488 .1

- 96 Fecha de presentación: 29.02.2008

- Número de publicación de la solicitud: 2272174

Fecha de publicación de la solicitud: 12.01.2011

- 54 Título: Aparato y procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos

- 45 Fecha de publicación de la mención BOPI: **08.11.2012**

73) Titular/es:

SELEX ELSAG S.P.A. (100.0%) Via Giacomo Puccini 2 16154 Genova, IT

- 45 Fecha de la publicación del folleto de la patente: **08.11.2012**

- 72 Inventor/es:

**TEDESCHI, RAFFAELE**

Agente/Representante:

**TEMIÑO CENICEROS, Ignacio**

ES 2 390 311 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

### **DESCRIPCIÓN**

Aparato y procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos.

#### 5 CAMPO DE LA INVENCION

La presente invención se refiere a un aparato y un procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos, y más particularmente un aparato y un procedimiento para adquirir una secuencia de pseudo ruido (PN) en sistemas de telecomunicaciones que emplean una modulación aperiódica 10 de espectro ensanchado por secuencia directa (DSSS).

#### **ANTECEDENTES DE LA INVENCION**

Como se conoce, en un sistema de comunicaciones de espectro ensanchado, un transmisor propaga una señal de 15 información sobre un amplio ancho de banda y un receptor, tras la recepción de la señal de información, desensancha la señal de información en la banda ancha original.

Una técnica posible para ensanchar la banda ancha de una señal se denomina espectro ensanchado por secuencia directa (DSSS).

20

En un sistema que emplea una técnica de DSSS, antes de la transmisión, se multiplica una señal de información de banda estrecha por un código de propagación para ensanchar su energía sobre una banda más ancha, generando de esta manera una señal de información de banda ancha. Después de la recepción, la señal de información de banda ancha se multiplica de nuevo por el mismo código de propagación usado en la transmisión, recuperando de este modo la señal de información de banda estrecha original.

Los sistemas de comunicaciones DSSS permiten un aumento de la inmunidad de la señal útil frente a señales interferentes de banda estrecha; cuando la señal recibida se multiplica por el código de propagación, la energía de la señal interferente se ensancha en una banda que es más amplia que la banda de señal útil. Después, un filtro de 30 banda estrecha pasa la señal útil y rechaza la mayor parte de la señal interferente.

Normalmente, se usan secuencias de ruido pseudo-aleatorias (PN) como códigos de propagación. El periodo de un bit de la secuencia (PN) normalmente se denomina tiempo de chip o periodo de chip (T<sub>c</sub>), y el periodo de un bit de la señal de información no ensanchada se denomina habitualmente tiempo de bit o periodo de bit (T<sub>B</sub>). Por consiguiente, los bits de la secuencia PN se denominan chips, así como los bits de la señal de información de banda ancha, que también se denominan chips, para distinguirlos de los bits de la señal de información no ensanchada.

Además, el tiempo de chip  $(T_c)$  es inferior al tiempo de bit  $(T_B)$  y su relación  $T_B/T_c$  se denomina factor de ensanchamiento N; el valor de N también representa la longitud en chips de un bit de la señal de información no 40 ensanchada.

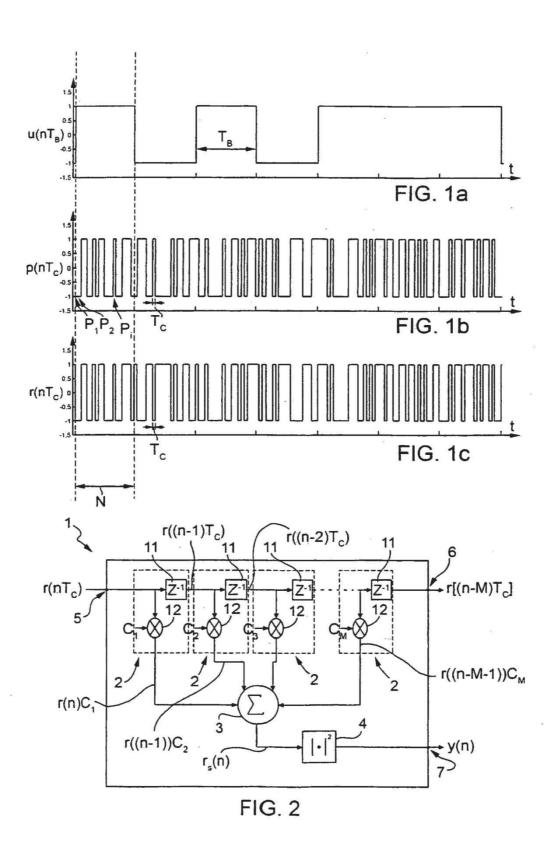

Para una mejor comprensión de las formas de onda usadas en los sistemas de comunicaciones DSSS, se hace referencia a las figuras 1a-1c. En detalle, la figura 1a muestra una señal no ensanchada u(nT<sub>B</sub>), que es una señal de información que se transmitirá; la figura 1b muestra una secuencia PN p(nT<sub>c</sub>), usada para ensanchar la señal no ensanchada formada por una pluralidad de chips p<sub>i</sub>; y la figura 1c muestra una señal de espectro ensanchado r(nT<sub>c</sub>)= u(nT<sub>B</sub>)·p(nT<sub>c</sub>), resultante del ensanchamiento. Como se observa, la secuencia PN p(nT<sub>c</sub>) tiene un periodo N<sub>c</sub> que es independiente de la señal no ensanchada u(nT<sub>B</sub>). En este caso particular, el factor de ensanchamiento es N = 20.

- 50 Existen dos tipologías de sistemas DSSS: sistemas DSSS periódicos, en los que el tiempo de bit es igual a o múltiplo de la extensión de tiempo de la secuencia PN completa, y sistemas DSS aperiódicos, en los que no existe relación entre el tiempo de bit y la extensión de tiempo de la secuencia PN. Se usan comúnmente sistemas DSSS aperiódicos junto con códigos concatenados.

- 55 Para que el sistema funcione eficazmente, el receptor debe ser capaz de realizar una adquisición sincronizada, es decir, debe ser capaz de generar una replica local de la secuencia PN usada en la transmisión y después sincronizar la fase de la replica local con la fase de la secuencia PN contenida en la señal recibida.

La adquisición de la sincronización en un sistema DSSS se divide normalmente en dos operaciones, normalmente

denominadas operación de adquisición y de seguimiento. Durante la operación de adquisición, la señal de información recibida y la replica local de la secuencia PN se alinean toscamente dentro de un error aceptable predeterminado (por ejemplo, 1/2 de un tiempo de chip). Durante la operación de seguimiento, se realiza una alineación más fina entre la señal de información recibida y la replica local de la secuencia PN y se mantiene con el 5 tiempo.

Al considerar la operación de adquisición, existen tres técnicas principales: Búsqueda en serie, búsqueda secuencial y técnica de filtro adaptado. En un sistema que emplea la técnica de filtro adaptado, la señal de información recibida se suministra secuencialmente a un correlador cuyos coeficientes son una replica exacta de la secuencia PN (es decir, un filtro adaptado). El filtro adaptado genera una señal de salida que es máxima cuando la secuencia PN contenida en la señal recibida se alinea (en fase) con los coeficientes del correlador. Esta técnica permite detectar la fase de la secuencia PN contenida en la señal de información recibida y después alinear la replica local, con el fin de desensanchar la señal de información recibida y recuperar la señal de información de banda estrecha original.

- 15 En particular, la técnica de filtro adaptado ofrece los mejores rendimientos en cuando a velocidad de adquisición en condiciones de una baja relación señal a ruido (SN) y se ve menos afectada por problemas de adquisición perdida y/o falsa. Sin embargo, la característica más limitante de la técnica de filtro adaptado es la gran cantidad de recursos computacionales requeridos para su implementación y el hecho de que no puede usarse en sistemas DSSS aperiódicos.

- Hoy en día el interés hacia esta técnica está considerablemente en aumento, en su mayor parte debido a los avances en los recursos computacionales, ya que puede obtenerse a partir de dispositivos lógicos programables o matrices de puertas programables en campo (FPGA), y una reducción del coste de los mismos.

- 25 El documento WO 99/41846 es un ejemplo de un detector DSSS para detectar una sincronización entre una secuencia de ensanchamiento de señal de espectro ensanchado. El detector comprende al menos una ramificación que comprende una pluralidad de correladores conectados en cascada entre sí y separados unos de otros por un bloque de retardo de ramificación. Cada correlador correlaciona chips de la secuencia de ensanchamiento con chips de la señal de espectro ensanchado y genera su propio valor de correlación. Los medios de detección de 30 concordancia reciben los valores de correlación y detectan cuando los chips de la secuencia de ensanchamiento están alineados con los chips de la señal de espectro ensanchado.

- Como se conoce, en un sistema DSSS aperiódico, la secuencia PN experimenta una modulación de señal debido a la señal de información que se está transmitiendo. Considerando que la señal de información es una palabra digital 35 de 1 a 0, y suponiendo que 1 se transmite con un signo positivo y 0 se transmite con un signo negativo, una porción de la secuencia PN puede modularse y transmitirse con un signo positivo, mientras que la otra porción puede modularse y transmitirse con un signo negativo.

- La secuencia PN se somete de este modo a una modulación de señal impredecible debido a los bits de la señal de 40 información, ya que no existe relación entre la duración de la secuencia PN y la duración de cada bit de la señal de información. En el receptor, por lo tanto, se desconoce en que punto de la secuencia PN puede haber un cambio de signo.

- La técnica de filtro adaptado no se puede aplicar con sistemas DSSS aperiódicos ya que, incluso cuando la secuencia PN está alineada perfectamente con la señal de información, la salida del correlador puede no ser máxima. De hecho, la parte modulada positivamente de la secuencia PN contenida en la señal de información recibida se correlaciona con los coeficientes del filtro adaptado generando una salida con un signo positivo, mientras que la parte modulada negativamente de la secuencia PN genera una salida con un signo negativo. Por lo tanto, es posible sobre la base exclusiva de la salida del filtro adaptado discriminar entre secuencias PN que se correlacionan con los coeficientes del filtro y aquellas secuencias PN que no se correlacionan con ellos.

#### **OBJETO Y RESUMEN DE LA INVENCIÓN**

El objetivo de la presente invención es superar las limitaciones de la técnica del filtro adaptado de acuerdo con la técnica anterior proponiendo un sistema y un procedimiento que aplique la técnica del filtro adaptado a sistemas DSSS aperiódicos.

De acuerdo con la invención, se proporciona un aparato y un procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos, como se define respectivamente en las reivindicaciones 1 y 13.

# **DESCRIPCIÓN DE LAS FIGURAS**

Para un mejor entendimiento de la presente invención, a continuación se describirán las realizaciones preferidas, 5 que se interpretan puramente a modo de ejemplo y no pretenden interpretarse como limitantes, con referencia a los dibujos adjuntos (ninguno está a escala), en los que:

- las figuras 1a-1c muestran ejemplos de una señal no ensanchada, una secuencia de ensanchamiento y una señal de espectro ensanchado;

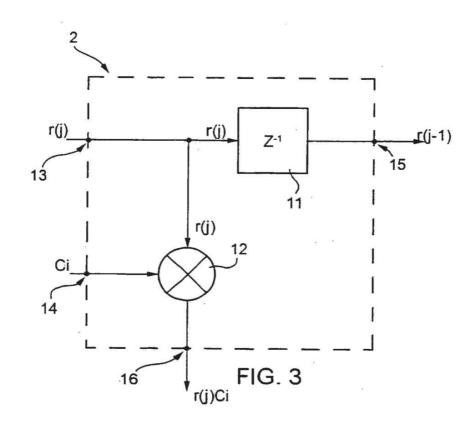

- 10 la figura 2 muestra una representación esquemática de un correlador parcial adaptado;

- la figura 3 muestra una representación esquemática de una porción del correlador parcial adaptado de la figura 2;

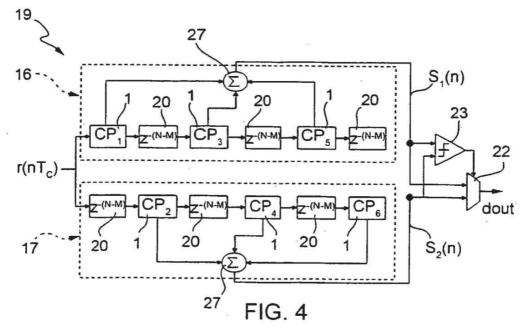

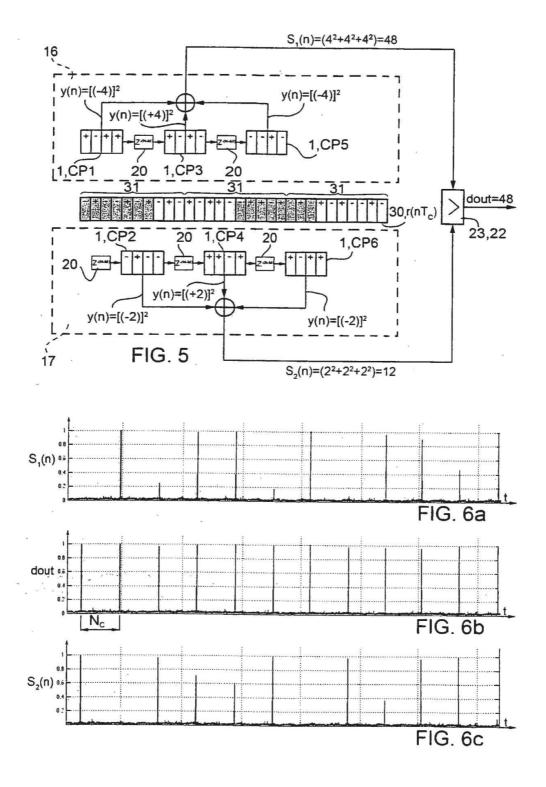

- la figura 4 muestra una representación esquemática de un detector que comprende una pluralidad de correladores parciales adaptados de acuerdo con una primera realización de la presente invención;

- la figura 5 muestra el detector de la figura 4 y los resultados del cálculo generados por sus componentes durante el 15 uso, en el caso de una única secuencia PN ejemplar, en un instante de tiempo;

- las figuras 6a-6c son representaciones gráficas normalizadas de los resultados de los cálculos frente al tiempo obtenidos con el detector de la figura 4;

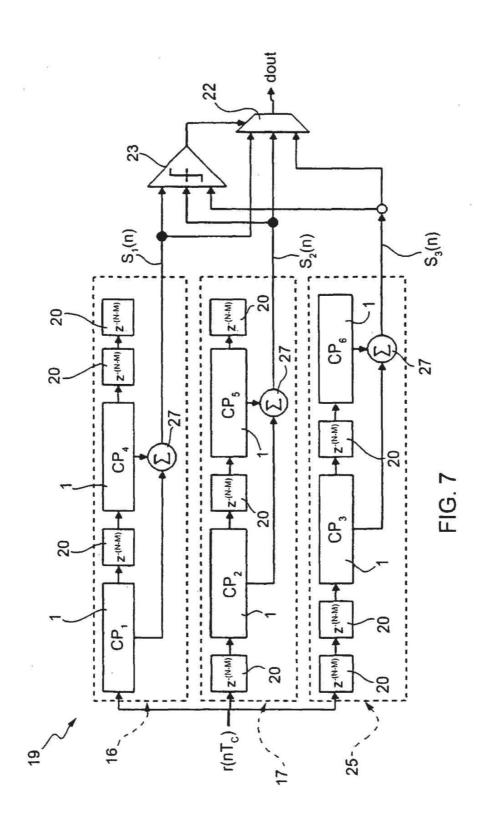

- la figura 7 muestra una representación esquemática de un detector que comprende una pluralidad de correladores parciales adaptados de acuerdo con otra realización de la presente invención; y

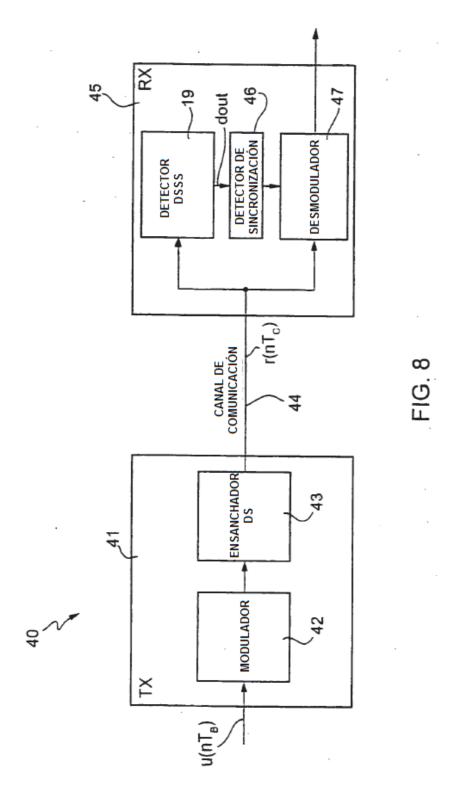

- 20 la figura 8 muestra un sistema de transmisión que incorpora el presente detector.

#### **DESCRIPCIÓN DETALLADA DE LA INVENCIÓN**

La figura 2 muestra un correlador 1, cuyos coeficientes se obtienen a partir de únicamente una parte de la secuencia 25 de ensanchamiento, que comprende un número M de fases 2 conectadas en cascada entre sí, un sumador 3 y un bloque de módulo cuadrado 4.

En detalle, el correlador 1 tiene un puerto de entrada de correlador 5 para recibir una señal de espectro ensanchado r(nT<sub>c</sub>), formado por una pluralidad de muestras de señal (o chips) r(n), y un primer y un segundo puerto de salida de 30 correlador 6, 7, siendo respectivamente la salida de la cascada de fases 2 y la salida del bloque de módulo cuadrado 4

En detalle, la figura 3, cada fase 2 comprende un elemento de retardo 11; un multiplicador 12; una primera entrada 13 que recibe, en cada instante de tiempo, una muestra de señal (es decir, un chip de la señal de espectro 35 ensanchado) r(j), conectada al elemento de retardo 11 y al multiplicador 12; una segunda entrada 14, que recibe un coeficiente propio c<sub>i</sub>, conectada al multiplicador 12; una primera salida 15, conectada al elemento de retardo 11; y una segunda salida 16, conectada al multiplicador 12. Por lo tanto, cada muestra de señal r(j) se suministra tanto al multiplicador 12 como al elemento de retardo 11.

40 El multiplicador 12 multiplica la muestra de señal r(j) por el coeficiente c<sub>i</sub>, produciendo de este modo en la segunda salida 16 un producto de muestra r(j)·c<sub>i</sub>; el elemento de retardo 11 introduce un retardo igual a un tiempo de chip a la muestra de señal r(j), produciendo de este modo en la primera salida 15 una muestra de señal retardada r(j-1).

Con referencia a la figura 2, se introduce una señal de espectro ensanchado r(nT<sub>c</sub>) en la fase izquierda 2 del 45 correlador 1 a través de la entrada del correlador 5, donde la señal de espectro ensanchado r(nT<sub>c</sub>) se procesa como se describe con referencia a la figura 3. Después, la salida 15 de la fase izquierda 2 se introduce en las fases siguientes 2 y se somete a los mismos procedimientos que se describen con referencia a la figura 3, generando una señal de información retardada de M chips r((n-M)T<sub>c</sub>) en la salida 6 del correlador 1. Además, cada fase 2 genera un producto de muestra respectivo r(n-i-1)·c<sub>i</sub>, variando i de 1 a M.

Los productos de muestra  $r(n)\cdot c_i$ ,  $r(n-1)\cdot c_2$ , ...,  $r(n-M-1)\cdot c_M$  se introducen en el sumador 3, que genera una señal de suma  $r_s(n)$  que se procesa por el bloque de módulo cuadrado 4, que calcula el módulo y la potencia cuadrada, y genera una señal de salida de correlador y(n) en el segundo puerto de salida de correlador 7:

$$y(n) = |r(n) \cdot c_1 + r(n-1) \cdot c_2 + ... + r(n-M-1) \cdot c_M|^2$$

55

El número M de fases 2 para cada correlador 1 se selecciona de acuerdo con la siguiente fórmula (1):

$$M = (k/,) \cdot N \qquad (1)$$

en la que k y m son números positivos y N es el factor de ensanchamiento o, de forma equivalente, la longitud, en 5 chips, de un bit de información de la señal de información de banda estrecha original, como se muestra en la figura 1c. k y m se selecciona en la fase de diseño como una compensación entre la complejidad y la robustez de ruido, de forma que (k/m)<1, como se analiza en más detalle en lo sucesivo en este documento. Se deduce que M<N.

Usando el correlador 1 de la figura 2 es posible formar un detector que incluya una o más ramificaciones, cada una 10 formada por la conexión en cascada de una pluralidad de correladores parciales adaptados 1. En este caso, m en la fórmula (1) representa el número de ramificaciones y k está relacionado con la longitud de cada correlador 1, como es evidente a partir de los siguientes ejemplos. Incluso si el detector puede funcionar con únicamente una ramificación, un número mayor de ramificaciones (igual a m) mejora su rendimiento en cuanto a robustez de ruido y la velocidad de adquisición de la secuencia de ensanchamiento, pero aumenta la complejidad del sistema y el coste 15 computacional. Por lo tanto, el número óptimo de ramificaciones debe escogerse caso por caso de acuerdo con los recursos de hardware disponibles y las limitaciones del diseño.

La figura 4 muestra una realización de un detector 19 formado por dos ramificaciones paralelas 16, 17 (es decir, m = 2); además, ya que la relación k/m de la fórmula (1) debe ser inferior a uno, se deduce que el único valor aceptable 20 para k es uno. Por lo tanto, de acuerdo con la fórmula (1), M = (1/2)N, y cada correlador 1 tiene un número M de fases 2 igual a un medio la longitud de bits de información (calculada en número de chips).

El número de correladores parciales adaptados 1 que pertenece a cada ramificación 16, 17 es variable, por ejemplo, puede ser igual a tres, dando un número total de correladores parciales adaptados 1 de seis. Para mayor claridad, 25 en la figura 4, los correladores parciales adaptados 1 de la primera ramificación 16 se identifican por CP1, CP3, CP5, mientras que los correladores parciales adaptados 1 de la segunda ramificación 17 se identifican por CP2, CP4, CP6.

Los coeficientes  $c_i$  de CP1-CP6 se toman de la secuencia PN (o, si es necesario, de secuencias PN más 30 consecutivas).

Cada correlador 1, que tiene M fases 2, necesita una secuencia de M coeficientes  $c_i$ . Supongamos que la secuencia PN sea la siguiente:

35

En la primera ramificación 16, los coeficientes  $c_i$  de CP1 se seleccionan como los primeros M chips  $p_i$  de la secuencia PN, es decir:

$$p_i\Big|_{i=1}^M$$

;

40 los coeficientes ci de CP3 se seleccionan como los M chips pi partiendo del chip (N+1) de la secuencia PN, es decir:

$$p_i|_{i=1+N}^{M+N} = p_i|_{i=2M+1}^{3M}$$

;

los coeficientes  $c_i$  de CP5 se seleccionan como los M chips  $p_i$  partiendo del chip (2N+1) de la secuencia PN, es decir:

$$p_i\Big|_{i=1+2N}^{M+2N}=p_i\Big|_{i=4M+1}^{5M}$$

.

De forma análoga, en la segunda ramificación 17 (es decir, CP2, CP4, CP6), los coeficientes c<sub>i</sub> se toman de los chips de la secuencia PN en grupos de M, partiendo del chip (N-M+1). En detalle, los coeficientes c<sub>i</sub> de CP2 corresponden a:

$$p_i|_{i=M+1}^{2M}$$

los coeficientes ci de CP4 corresponden a:

$$p_i\Big|_{i=3M+1}^{4M}$$

los coeficientes ci de CP6 corresponden a:

$$P_i|_{i=SM+1}^{6M}$$

5

Por lo tanto, de acuerdo con la realización de la figura 4, los coeficientes de CP1 son:

$$(c_1 \ c_2 \ ... \ c_M) = (p_1 \ p_2 \ ... \ p_M);$$

los coeficientes de CP2 son:

$$(C_{M+1} C_{M+2} ... C_{2M}) = (p_{M+1} p_{M+2} ... p_{2M});$$

los coeficientes de CP3 son:

$$(C_{2M+1} \ C_{2M+2} \ ... \ C_{3M}) = (p_{2M+1} \ p_{2M+2} \ ... \ p_{3M});$$

los coeficientes de CP4 son:

$$(C_{3M+1} \ C_{3M+2} \ \dots \ C_{4M}) = (p_{3M+1} \ p_{3M+2} \ \dots \ p_{4M});$$

15 los coeficientes de CP5 son:

$$(C_{4M+1} \ C_{4M+2} \ ... \ C_{5M}) = (p_{4M+1} \ p_{4M+2} \ ... \ p_{5M});$$

los coeficientes de CP6 son:

$$(C_{5M+1} C_{5M+2} ... C_{6M}) = (p_{5M+1} p_{5M+2} ... p_{6M})$$

.

20 Para cada ramificación 16, 17, los correladores parciales adaptados 1 se separan por y se conectan a un bloque de retardo 20 que introduce un retarde de (N-M) chips. Por lo tanto, el correlador 1 y el bloque de retardo 20 están conectados en cascada entre sí.

Una de las ramificaciones (por ejemplo, la primera ramificación 16) recibe la señal de espectro ensanchado no 25 retardada r(nT<sub>c</sub>), mientras que la otra ramificación (la segunda ramificación 17) recibe en la entrada una copia retardada (N-M) de la señal de información r(nT<sub>c</sub>), es decir, r((n-(N-M))T<sub>c</sub>).

Por lo tanto, cuando los chips pi de la secuencia PN contenida en la señal recibida se alinean con los coeficientes ci de los correladores parciales adaptados 1, existe al menos una de las ramificaciones del detector 19 en la que todos los correladores parciales adaptados 1 reciben una señal de entrada respectiva (que es una porción de la señal de espectro ensanchado r(nT<sub>c</sub>) y sus copias retardadas) que está alineada, con el mismo signo, a los coeficientes respectivos ci. Debido a la modulación de los signos a causa de los chips de la señal recibida, el signo de correlación puede diferir de un correlador 1 a otro, pero esto es irrelevante, ya que la dependencia del signo se elimina por el bloque de módulo cuadrado 4 que pertenece a cada correlador 1.

35

Las señales de salida de correlador y(n) de los correladores parciales adaptados 1 que pertenecen a la primera ramificación 16 se añaden mediante un circuito de adición 27, para reducir el efecto negativo del ruido, obteniendo una señal de suma de detector s1(n). Para este fin, cuando mayor es el número de correladores parciales adaptados 1 en una ramificación, mayor es la eficacia del rechazo del ruido. Sin embargo, el coste computacional puede 40 aumentar significativamente.

## ES 2 390 311 T3

De forma análoga, las señales de salida y(n) de los correladores parciales adaptados 1 que pertenecen a la segunda ramificación 17 también se añaden juntas, obteniendo una segunda señal de suma s2(n).

- 5 Después, la primera y segunda señales de suma s1(n) y s2(n) se introducen en un multiplexor 22 y en un comparador 23. El comparador 23 detecta la mayor de la primera y la segunda señales de suma s1(n) y s2(n) y, por consiguiente, la conduce al multiplexor 22 para que la salida del detector d<sub>out</sub> sea la mayor de la primera y la segunda señales de suma s1(n) y s2(n).

- 10 Ya que durante la adquisición de sincronización se produce una salida del detector d<sub>out</sub> en cada instante de tiempo, debe implementarse un comparador de umbral adecuado y/o un filtro para discriminar entre salidas falsas y salidas máximas, generándose la última a consecuencia de las alineaciones entre los coeficientes c<sub>i</sub> de los correladores 1 de una de las ramificaciones y las muestras de señales r(n) introducidas en cada correlador respectivo 1.

- 15 La figura 5 muestra, esquemáticamente, la operación del detector 19 de la figura 4 en un momento ejemplar. En este ejemplo, el periodo N<sub>c</sub> de la secuencia PN se selecciona igual a diez (es decir, una secuencia PN se forma por diez chips), la longitud N, en número de chips de un bit de la señal no ensanchada, se ha supuesto igual a ocho y, en consecuencia, M es cuatro.

- 20 Para mayor claridad, la señal de espectro ensanchado recibida r(nT<sub>c</sub>) se muestra gráficamente como un vector 30 de valores +1 y -1, que representan respectivamente los valores digitales 1 y 0 (en la figura 5, el valor +1 se representa con el signo +, mientras que el valor -1 con el signo -). De forma análoga, la secuencia de coeficientes c<sub>i</sub> de cada correlador 1 se representa gráficamente en el interior de cada correlador 1 como una secuencia de valores +1 y -1, representando los valores digitales 1 y 0 (también en este caso, en la figura 5, el valor +1 se representa como +, mientras que el valor -1 como -). Además, cada muestra de señal r(n) se muestra alineada gráficamente con el coeficiente respectivo c<sub>i</sub> por el que la misma muestra de señal se multiplica en el instante considerado.

En la figura 5, la secuencia PN es un vector de 10 chips:

30 (+1-1+1+1-1+1-1+1-1).

55

Los cuatro coeficientes  $c_i$  para cada correlador 1 se toman, como se ha explicado, a partir de secuencias PN más consecutivas.

35 Las muestras de señal de la señal de espectro ensanchado recibida r(nT<sub>c</sub>) que durante la transmisión se modulan positivamente, se representan en sitios del vector 30 que tienen un fondo negro, mientras que las muestras de señal que se modulan negativamente (es decir, experimentaron una variación de signo), se representan en sitios del vector 30 que tienen un fondo gris. Para mayor claridad, la secuencia PN contenida en la señal de espectro ensanchado recibida, en la figura 5, se indica como un vector PN 31, formada por diez muestras de señal 40 consecutivas, moduladas positiva o negativamente como ya se ha descrito.

Como puede observarse claramente, las salidas de correlador y(n) de los correladores CP1, CP3, CP5 son máximas (iguales al módulo cuadrado de ±4), indicando una concordancia completa entre los coeficientes c<sub>i</sub> y las muestras de señal alineadas. En este caso, la alineación se verifica incluso para aquellas muestras de señal r(n) moduladas negativamente (tales como en los correladores CP1 y CP5), ya que la operación de módulo cuadrado (véase el bloque de módulo cuadrado 4, figura 2) elimina la dependencia del signo.

Por el contrario, las señales de salida de correlador y(n) de los correladores CP2, CP4, CP6 no son máximas, ya que tiene lugar una variación del signo a lo largo de las muestras de señal r(n) alineadas con los coeficientes c<sub>i</sub> de CP2, 50 CP4 y CP6.

Aquí, la salida del detector  $d_{out}$ , que el máximo entre la primera y segunda señales de suma s1(n) y s2(n) de las dos ramificaciones 16, 17, es por lo tanto, la suma de todas las sales de salida de correlador y(n) de la primera ramificación 16.

La figura 6a-6c muestra una forma de onda ejemplar de la salida del detector  $d_{out}$  enfrentada a la primera y segunda salidas s1(n), s2(n) de la primera y segunda ramificaciones 16, 17, en instantes de tiempo posteriores. Para mayor claridad, el valor máximo alcanzado por las formas de onda s1(n), s2(n) y  $d_{out}$  se normaliza a 1.

7

La salida del detector d<sub>out</sub>, figura 6b, presenta una serie de picos de correlación, indicando cada uno la aparición de una concordancia entre las muestras de señal recibidas r(n) y los coeficientes c<sub>i</sub> de todos los correladores parciales adaptados 1 de al menos una de las ramificaciones del detector 19. Los picos de correlación en la forma de onda de la salida del detector d<sub>out</sub> son periódicos, en particular el periodo de los picos de correlación es el periodo N<sub>c</sub> de la secuencia PN.

Es evidente que pueden hacerse numerosas modificaciones y variantes a la realización descrita, estando todas dentro del alcance de la invención, como se define en las reivindicaciones adjuntas.

10 En particular, el detector 19 puede tener más de dos ramificaciones, o únicamente una ramificación, y cada correlador 1 en cada ramificación puede tener un número M de fases 2 distinto de M = (1/2)N.

Por ejemplo, en el caso de una única ramificación, la fórmula (1) se reduce a M<N.

15 En otro ejemplo, seleccionando k = 2 y m = 3, el detector 19 tiene tres ramificaciones y, de acuerdo con la fórmula (1), M = (2/3)N. Además, el número de correladores parciales adaptados 1 en cada ramificación puede ser cualquiera. Por ejemplo, la figura 7 muestra una realización en la que el detector 19 tiene tres ramificaciones 16, 17 y 25. Cada ramificación 16, 17, 25 comprende dos correladores parciales adaptados 1, para un número total de seis correladores parciales adaptados 1. Los correladores parciales adaptados 1 de la primera ramificación 16 son CP1 y 20 CP4, los de la segunda ramificación 17 son CP2 y CP5, los de la tercera ramificación 25 son CP3 y CP6.

El criterio para seleccionar los coeficientes c<sub>i</sub> de cada uno de los correladores parciales adaptados 1 es el mismo que el ya descrito con referencia a la realización de la figura 4.

25 En particular, partiendo de la primera ramificación 16, los coeficientes c<sub>i</sub> de CP1, se seleccionan como los primeros M chips consecutivos p<sub>i</sub> de la secuencia PN; los coeficientes c<sub>i</sub> de CP2 de la segunda ramificación 17 son los M chips consecutivos p<sub>i</sub> de la secuencia PN que parte del chip (N-M+1) p<sub>i</sub> de la secuencia PN; los coeficientes c<sub>i</sub> de CP3 de la tercera ramificación 25 son los M chips consecutivos p<sub>i</sub> de la secuencia PN que parte del elemento (2(N-M)+1) de la secuencia PN; el primer coeficiente cl del segundo correlador 1 en cada ramificación (CP4 para la primera ramificación 16, CP5 para la segunda ramificación 17, CP6 para la tercera ramificación 25) se separa N chips p<sub>i</sub> con respecto al primer coeficiente del correlador anterior 1 en la misma ramificación.

De forma análoga, en caso de más de dos correladores parciales adaptados 1, el tercer y posteriores correladores parciales adaptados 1 reciben los coeficientes c<sub>i</sub> que son N chips separados con respecto al primer coeficiente del 35 correlador 1 inmediatamente anterior en la misma ramificación.

La segunda ramificación 17 recibe una copia retardada de la señal de espectro ensanchado r(nT<sub>c</sub>) en virtud de la presencia de un bloque de retardo 20 por delante del correlador parcial adaptado CP2; la tercera ramificación 25 tiene dos bloques de retardo iniciales 20 antes del correlador parcial adaptado CP3, para retrasar la señal de 40 espectro ensanchado r(nTc) por 2(N-M) chips de la señal de espectro ensanchado r(nTc).

Generalmente, en caso de m ramificaciones, la ramificación recibe una copia retardada (m-1)(N-M) de la señal de espectro ensanchado original.

- 45 Además, la detección de la concordancia puede variar con respecto a la solución mostrada. Por ejemplo, las salidas de los correladores 1 de la única ramificación o de cada ramificación pueden compararse con un umbral, y la concordancia se detecta cuando todas las salidas de la única ramificación o de una ramificación exceden el umbral.

- La invención encuentra una aplicación preferida en los receptores de módem DSSS para sistemas de telecomunicaciones de espectro ensanchado, como se muestra esquemáticamente en la figura 8. Aquí, el sistema 40 comprende un transmisor 41, incluyendo un modulador 42 y un ensanchador de secuencia directa (DS) 43 para generar la señal de espectro ensanchado r(nTc) que se transmitirá; un canal de comunicación 44, en el que la señal de espectro ensanchado se transmite; y un receptor 45, por ejemplo, un módem DSSS, que recibe la señal de espectro ensanchado y que comprende el detector 19 de la figura 4 o la figura 7, un detector de sincronización 46 y un desmodulador 47. En este caso, el detector de sincronización 46 recibe la salida del detector dout, determina la sincronización en base a la salida del detector dout y controla el desmodulador 47 para que el último pueda realizar una adquisición sincronizada de la señal de espectro ensanchado.

#### **REIVINDICACIONES**

- Un detector DSSS (19) para detectar una sincronización entre una señal de espectro ensanchado (r(nT<sub>c</sub>)), que tiene una pluralidad de chips, r(n), y un valor del factor de ensanchamiento, N, y una secuencia de ensanchamiento, PN, que tiene una pluralidad de chips, p<sub>i</sub>, comprendiendo el detector DSSS (19) al menos una ramificación (16) adaptada para recibir la señal de espectro ensanchado, comprendiendo la al menos una ramificación una pluralidad de correladores (1), incluyendo cada correlador un número, M, de fases de correlación (2) que es inferior a dicho valor del factor de ensanchamiento, N, estando los correladores (1) conectados en cascada entre sí y separados entre sí por un bloque de retardo de ramificación (20), estando dicho bloque de retardo de ramificación (20) adaptado para retardar la señal de espectro ensanchado recibida por una cantidad de retardo, N-M, que es inferior al valor del factor de ensanchamiento, N, comprendiendo cada correlador (1) medios de correlación (3, 4, 12) para correlacionar chips de la secuencia de ensanchamiento con chips de la señal de espectro ensanchado y generar cada una un valor de correlación propio (y(n)),

- comprendiendo adicionalmente el detector DSSS (19) medios de detección de concordancia (27, 22, 23) para recibir 15 dichos valores de correlación y detectar cuando dichos chips de la secuencia de ensanchamiento están alineados con dichos chips de la señal de espectro ensanchado.

- Un detector DSSS de acuerdo con la reivindicación 1, en el que dichos medios de detección de concordancia (27, 22, 23) comprenden un elemento sumador de ramificación (27) adaptado para recibir dichos

valores de correlación y generar una señal de suma de ramificación (s1(n)); y un detector de máximo (23) adaptado para detectar un máximo de dicha señal de suma de ramificación.

- 3. Un detector DSSS de acuerdo con la reivindicación 1 ó 2, en el que cada fase de correlación (2) tiene una entrada de fase (13) configurada para recibir un chip, r(n), r(n-1), ..., r(n-M-1), de la señal de espectro ensanchado (r(nT<sub>c</sub>)), a elemento de retardo del correlador (11) conectado a dicha entrada de fase, un elemento de correlación de chips (12) conectado a dicha entrada de fase y configurado para correlacionar un chip de la señal de espectro ensanchado con un coeficiente propio, c<sub>1</sub>, c<sub>2</sub>, ..., c<sub>M</sub>, una primera salida de datos (16) conectada a dicho elemento de correlación de chips (12) y que transmite un chip correlacionado, r(n)·c<sub>1</sub>, r(n-1)·c<sub>2</sub>, ..., r(n-M-1)·c<sub>M</sub>, y una segunda salida de datos (15) conectada a dicho elemento de retardo de correlador (11) y a una fase de correlación posterior (2); comprendiendo adicionalmente el correlador (1) un elemento de suma (3) adaptado para recibir dichos chips correlación y calcular una suma de correlación (r<sub>s</sub>(n)) y un elemento de módulo (4) adaptado para recibir dicha suma de correlación y calcular el valor de correlación (y(n)).

- 4. Un detector DSSS de acuerdo con la reivindicación 3, en el que los elementos de correlación son 35 multiplicadores (12).

- 5. Un detector DSSS de acuerdo con la reivindicación 3 ó 4, en el que dichos coeficientes (c<sub>1</sub>, c<sub>2</sub>, ..., c<sub>M</sub>) de dichas fases de correlación (2) se seleccionan entre los chips (p<sub>i</sub>) de dicha secuencia de ensanchamiento, PN, y en el que los coeficientes, c<sub>1</sub>, c<sub>2</sub>, ..., c<sub>M</sub>, de un primer correlador (1) de dicha pluralidad de correladores (1) son iguales a los primeros chips M, p<sub>1</sub>, p<sub>2</sub>, ..., p<sub>M</sub>, de dicha secuencia de ensanchamiento, PN, y los coeficientes de los correladores posteriores (1) son iguales a M chips posteriores de dicha secuencia de ensanchamiento, separados por N chips con respecto a los coeficientes correspondientes de un correlador inmediatamente anterior (1), siendo M el número de fases de correlación (2) en cada correlador (1), y siendo N el valor del factor de ensanchamiento.

- 45 6. Un detector DSSS de acuerdo con la reivindicación 5, en el que cada bloque de retardo de ramificación (20) está adaptado para generar un retardo de N-M chips.

- 7. Un detector DSSS de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende m-1 ramificaciones adicionales (17, 25), con m ≥ 2, recibiendo cada ramificación adicionalmente dicha señal de espectro ensanchado (r(nT<sub>c</sub>)) e incluyendo una pluralidad de correladores (1) conectados en cascada entre sí y separados unos de otros por un bloque de retardo de ramificación (20), comprendiendo cada correlador de las ramificaciones adicionales medios de correlación (3, 4, 12) para correlacionar chips, p<sub>i</sub>, de la secuencia de ensanchamiento, PN, con chips de la señal de espectro ensanchado.

- 55 8. Un detector DSSS de acuerdo con la reivindicación 7, que depende de la reivindicación 4, en el que los correladores (1) de dichas ramificaciones adicionales (17, 25) comprenden cada una M fases de correlación (2), en las que

## ES 2 390 311 T3

k es un número positivo, m es el número de ramificaciones que incluye dicha al menos una ramificación (16) y dichas ramificaciones adicionales (17, 25), N es el factor de ensanchamiento de la señal de espectro ensanchado, y (k/m)<1.

Un detector DSSS de acuerdo con la reivindicación 8, en el que la señal de espectro ensanchado (r(nT<sub>c</sub>)) introducida en la ramificación m (16; 17; 25) se retrasa por (m-1)(N-M) chips.

- 10. Un detector DSSS de acuerdo con cualquiera de las reivindicaciones 7-9, que dependen de la 10 reivindicación 3, en el que cada ramificación adicional (17, 25) comprende un elemento sumador de ramificación adicional (27) conectado a dichos correladores (1) de una ramificación adicional propia y adaptado para generar una señal de suma de ramificación propia (s2 (n), s3 (n)); y un detector de máximo (22, 23) adaptado para detectar un máximo entre dichas señales de suma de ramificaciones (s1(n), s2(n), s3(n)).

- 15 11. Un detector DSSS de acuerdo con la reivindicación 10, en el que dicho detector de máximo (22, 23) comprende un comparador (23) adaptado para generar una señal de ramificación máxima, comprendiendo adicionalmente el detector un multiplexor (22) adaptado para recibir dicha señal de ramificación máxima y dichas señales de suma de ramificaciones (s<sub>1</sub>(n), s<sub>2</sub> (n), s<sub>3</sub>(n)) y para transmitir una señal de suma de ramificaciones máxima (d<sub>out</sub>) en respuesta a la señal de ramificación máxima.

- 12. Un módem DSSS que comprende un detector DSSS (19) de acuerdo con cualquiera de las reivindicaciones 1-11 y un desmodulador (47) adaptado para recibir dicha señal de espectro ensanchado (r(nT<sub>c</sub>)) y la señal de suma de ramificación máxima (d<sub>out</sub>).

- 25 13. Un procedimiento de detección de una sincronización entre una señal de espectro ensanchado (r(nT<sub>c</sub>)), que tiene una pluralidad de chips, r(n), y un valor del factor de ensanchamiento, N, y una secuencia de ensanchamiento, PN, que tiene una pluralidad de chips, p<sub>i</sub>, que comprende las etapas de:

- a. recibir la señal de espectro ensanchado (r(nT<sub>c</sub>)) por una pluralidad de correladores (1) conectados en cascada

30 entre sí, incluyendo cada correlador un número (M) de fases de correlación (2) que es inferior a dicho valor del factor de ensanchamiento, N;

- b. generar al menos una señal retardada,  $r((n-1)T_c)$ , a partir de la señal de espectro ensanchado  $(r(nT_c))$  que retarda la señal de espectro ensanchado recibida por una cantidad de retardo, N-M, que es inferior al valor del factor de ensanchamiento. N:

- 35 c. correlacionar la señal de espectro ensanchado y la señal retardada con chips de la secuencia de ensanchamiento para generar valores de correlación (y(n)); y

- d. detectar una concordancia entre la señal de espectro ensanchado y la secuencia de ensanchamiento en base a dichos valores de correlación.

- 40 14. Un procedimiento de acuerdo con la reivindicación 13, en el que la etapa de detectar una concordancia comprende la adición de dichos valores de correlación (y(n)) para generar una primera señal de suma de ramificación (s1(n)) y la detección de un máximo de dicha señal de suma de ramificación.

- 15. Un procedimiento de acuerdo con la reivindicación 13 ó 14, en el que dicha al menos una señal retardada, r((n-1)T<sub>c</sub>), se retrasa para generar al menos una señal retardada adicional, r((n-2)T<sub>c</sub>), y el procedimiento comprende la etapa de correlacionar la señal retardada adicional con chips adicionales (p<sub>i</sub>) de la secuencia de ensanchamiento para generar valores de correlación adicionales (y(n)).

- 16. Un procedimiento de acuerdo con cualquiera de las reivindicaciones 13-15, en el que la etapa de correlacionar comprende recibir un chip r(n), r(n-1), ..., r(n-M-1) de la señal de espectro ensanchado (r(nTc)) o señales retardadas, r((n-1)T<sub>c</sub>), r((n-2)T<sub>c</sub>), en una fase de correlación (2), retrasar el chip recibido, suministrar el chip retardado recibido a una fase de correlación posterior (2), realizar una correlación de chips entre el chip recibido y un coeficiente, c<sub>1</sub>, c<sub>2</sub>, ..., c<sub>M</sub>, suministrar el resultado de la correlación de chips, r(n)·c<sub>1</sub>, r(n-1)·c<sub>2</sub>, ..., r(n-M-1)·c<sub>M</sub>, a un elemento de suma (3), calcular una suma de correlación (s1(n)) y calcular dicho valor de correlación (y(n)).

- 17. Un procedimiento de acuerdo con la reivindicación 16, que depende de la reivindicación 15, en el que la correlación de chips se realiza mediante M fases de correlación (2), estando seleccionados los coeficientes, c<sub>1</sub>, c<sub>2</sub>, ..., c<sub>M</sub>, de dichas fases de correlación (2) entre los chips de dicha secuencia de ensanchamiento, PN, y en el que las etapas de correlacionar la señal de espectro ensanchado (r(nT<sub>c</sub>)), correlacionar la al menos una señal retardada,

10

## ES 2 390 311 T3

r((n-1)T<sub>c</sub>), y correlacionar la al menos una señal retardada adicional, r((n-2)T<sub>c</sub>), se realizan mediante una pluralidad de correladores (1), en el que los coeficientes de un primer correlador de dicha pluralidad de correladores son iguales a los primeros M chips, p<sub>1</sub>, p<sub>2</sub>, ..., p<sub>M</sub>, de dicha secuencia de ensanchamiento PN, y los coeficientes de los correladores posteriores son iguales a los M chips posteriores de dicha secuencia de ensanchamiento, separados por N chips con respecto a los coeficientes correspondientes de un correlador inmediatamente anterior, donde N es el valor del factor de ensanchamiento.

- 18. Un procedimiento de acuerdo con la reivindicación 17, en el que las etapas de retrasar la señal de espectro ensanchado (r(nT<sub>c</sub>)) y retrasar la al menos una señal retardada, r((n-1)T<sub>c</sub>), comprende generar un retardo 10 de N-M chips.

- 19. Un procedimiento de acuerdo con cualquiera de las reivindicaciones 13-18, generando al menos una señal de ramificación retardada, r((n-M)T<sub>c</sub>), a partir de la señal de espectro ensanchado; correlacionando la señal de ramificación retardada con chips, p<sub>i</sub>, de la secuencia de ensanchamiento, PN, para generar los segundos valores de correlación (y(n)); sumando dichos segundos valores de correlación para obtener unos segundos valores de suma de ramificación (s2(n)); comparando dichos primeros (s1(n)) y segundos (s2(n)) valores de suma de ramificación; transmitiendo el mayor del primer y el segundo valores de suma de ramificación; generando una secuencia (d<sub>out</sub>) de valores de suma de ramificación máxima y detectando una sincronización en base a dicha secuencia (d<sub>out</sub>).

16