# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 392 543

61 Int. Cl.:

H04W 52/12 (2009.01) H04B 17/00 (2006.01) H04W 52/56 (2009.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Número de solicitud europea: 06742957 .1

- 96 Fecha de presentación: **18.05.2006**

- Número de publicación de la solicitud: 1882314

Fecha de publicación de la solicitud: 30.01.2008

- (54) Título: Método y aparato para la estimación de la tasa de error en un canal de comunicación

- (30) Prioridad:

20.05.2005 US 683203 P 07.12.2005 US 296560

- (45) Fecha de publicación de la mención BOPI:

- 11.12.2012

- (45) Fecha de la publicación del folleto de la patente: 11.12.2012

(73) Titular/es:

TELEFONAKTIEBOLAGET L- M ERICSSON (PUBL) (100.0%)

164 83 Stockholm, SE

(72) Inventor/es:

ANDERSSON, LENNART; WANG, YI-PIN, ERIC y BOTTOMLEY, GREGORY, E.

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

#### **DESCRIPCION**

Método y aparato para la estimación de la tasa de error en un canal de comunicación.

#### 5 ANTECEDENTES

La presente invención se refiere a sistemas de comunicación inalámbrica, y particularmente se refiere a la estimación de las tasas de error en los canales de comunicación.

- La estimación de la tasa de error sirve para muchos propósitos en sistemas de comunicación inalámbrica. Como ejemplo, los mecanismos de control de la potencia de transmisión que se emplean ampliamente en redes de comunicación celular basadas en Acceso Múltiple por División de Código (CDMA) usan la tasa de error en los canales como una variable de control en sus algoritmos de ajuste de la potencia. Más en particular, las estaciones base de radio basadas en CDMA controlan generalmente las potencias de transmisión del enlace inverso de las estaciones móviles soportadas por aquellas, basándose en la transmisión a las estaciones móviles de bits de Control de la Potencia de Transmisión (TPC). Similarmente, cada estación móvil controla generalmente la potencia de transmisión del enlace directo que le transmite la(s) estación(es) base de radio sobre un canal dedicado al tráfico de enlace directo transmitiendo bits a la estación(es) base de radio.

- Los bits de TPC trasmitidos toman generalmente uno de estos dos valores: un "1" lógico o comando "UP" para indicar que el transmisor distante debe aumentar su potencia de transmisión, y un "0" lógico o comando "DOWN" para indicar que el transmisor distante debe disminuir su potencial de transmisión. El valor de cada bit deTPC se determina comparando la señal piloto recibida con una intensidad de la señal objetivo, expresada usualmente como una Relación Señal/Ruido. Para un intervalo de medición dado, el receptor compara la intensidad recibida de la señal piloto con el objetivo y transmite un comando DOWN si la intensidad recibida de la señal piloto está por encima del objetivo y transmite un comando UP si la intensidad recibida de la señal piloto esta por debajo del objetivo. Haciendo la comparación muchas veces por segundo, el receptor genera un flujo estable de bits de TPC, manteniendo por ello la intensidad recibida de la señal piloto en el objetivo. Generalmente el transmisor que transmite la señal piloto también transmite uno o más canales de tráfico según relaciones definidas de potencia de tráfico a piloto, significando que el control de potencia de la señal piloto sirve como un control de potencia del canal(es) asociado de tráfico.

- Tal tratamiento de la intensidad recibida de la señal hace que el control de potencia lleve la etiqueta de "lazo interno" y, como el nombre sugiere, el control de potencia del lazo interno generalmente se empareja con el control de potencia del "lazo externo". Aunque el proceso de controlar la potencia del lazo interno asegura que la intensidad recibida de la señal piloto se mantiene en el objetivo, el proceso de controlar la potencia del lazo externo asegura que el objetivo adecuado está siendo usado por el control de potencia del lazo interno.

- Por ejemplo, el control de potencia del lazo externo computa o predice normalmente una tasa de error para los datos que se están recibiendo en asociación con la recepción de la señal piloto y la compara con un límite definido de error superior, por ejemplo, 10%. Tales tasas de error se expresan usualmente como Tasas de Error de Bloque (BLERs) o Tasas de Error de Bit (BERs). Independientemente de si la tasa de error excede el límite definido superior, el control de potencia del lazo externo ajusta el objetivo del lazo interno hacia arriba.

- 45 Por el contrario, si la tasa de error cae por debajo de un límite inferior, por ejemplo, 1%, el control de potencia del lazo externo ajusta el objetivo del lazo interno hacia abajo.

- Implícita en la anterior descripción del control de potencia del lazo externo, existe la disponibilidad de tener datos "codificados" para determinar las tasas de error en la recepción, es decir, datos que incluyen o están acompañados de información de detección de error y/o de corrección de error. Sin datos codificados o conocidos, tales como bits piloto, no existe variable explícita de control para evaluar el rendimiento de errores en la recepción y por ello no existe base explícita para determinar los ajustes de subir y bajar el objetivo de control de potencia del lazo interno. El Canal Físico Dedicado Fraccional (F-DPCH) recientemente introducido en las normas CDMA de Banda Ancha (WCDMA) incluye información del control de potencia (por ejemplo, bits de TPC), pero no incluye datos con información de corrección del error. De este modo, el F-DPCH ejemplifica el tipo de canal que complica el método tradicional de control de potencia de lazo interno/externo.

- La solicitud de patente publicada WO 2005/013536 describe un método para controlar la potencia del lazo externo en un sistema de comunicación inalámbrica. El método usa un CRC para ajustar una SIR objetivo para un canal codificado de transporte compuesto si el CRC está disponible. Si el CRC no está disponible, el método usa mediciones de calidad del canal codificado de transporte compuesto para calcular la SIR objetivo. Sin embargo, no describe un esquema de control de potencia para un canal control de potencia, ni lo describe usando la tasa de error de los comandos de control de potencia.

#### **SUMARIO**

5

35

40

45

50

65

La presente invención se refiere a un método de acuerdo con la reivindicación independiente 1, a un circuito de control de potencia de acuerdo con la reivindicación independiente 20, a un dispositivo de comunicación inalámbrica de acuerdo con la reivindicación 36 y a un medio interpretable por ordenador de acuerdo con la reivindicación 37. Las ventajosas realizaciones se definen en las reivindicaciones dependientes.

En una realización que se muestra en esta memoria, un método de generar realimentación de control de potencia del transmisor para un canal de control de potencia comprende recibir comandos de control de potencia sobre el canal de control de potencia, estimar la calidad de una señal para el canal de control de potencia, estimar una tasa de error de comando (CER) para los comandos de control de potencia recibidos, ajustar una calidad objetivo de la señal comparando la CER estimada con la CER objetivo, y generar realimentación de control de potencia del transmisor para el canal de control de potencia comparando la calidad estimada de la señal con una calidad objetivo de la señal. Ajustar la calidad objetivo de la señal puede comprender aumentar la calidad objetivo de la señal si la CER estimada excede la CER objetivo y disminuir la calidad objetivo de la señal si la CER estimada es menor que la CER objetivo. Obsérvese que, en esta y en otras realizaciones, las calidades de la señal estimada y de la señal objetivo pueden, por ejemplo, expresarse como relaciones señal/interferencia (SiRs), en donde la interferencia puede incluir deterioros tales como interferencia entre células, interferencia intra células, y ruido térmico.

Los comandos de control de potencia recibidos en una o más realizaciones comprenden nominalmente símbolos de bits coincidentes. En tales realizaciones, un método para estimar una CER para los comandos de control de potencia comprende calcular una probabilidad de error en la recepción para los comandos de control de potencia recibidos como una función de detectar bits no coincidentes en los comandos de control de potencia recibidos, y mapear la probabilidad de error en la recepción con un valor CER correspondiente de acuerdo como una función definida de mapeo de probabilidad/CER. La función de mapeo de probabilidad/CER se puede implementar usando una tabla de búsqueda de datos indexada por valores de probabilidad por ejemplo, o usando una función polinómica basada en la curva de mapeo de probabilidad/CER.

En otras realizaciones, los comandos de control de potencia comprenden símbolos, al menos algunos de los cuales incluyen bits conocidos, por ejemplo, bits de referencia, o los comandos de control de potencia se intercalan con símbolos de referencia. En tales casos, la estimación de CER puede comprender la detección de errores de recepción de los bits de referencia/símbolos.

Aún en otras realizaciones, la estimación de CER comprende mapear la calidad estimada de la señal con un valor correspondiente de CER de acuerdo con una función definida de mapeo de la calidad de la señal/CER.

En tales realizaciones, se puede preconfigurar un transceptor de comunicación inalámbrica con una CER objetivo, o con un valor correspondientemente mapeado o correlacionado de la calidad de la señal, o el mapeo se puede hacer dinámicamente para permitir ajustar dinámicamente la CER objetivo.

Un dispositivo de comunicación inalámbrica puede implementar cualquiera de las anteriores realizaciones, o variantes de ellas, tales como incluir un circuito de control de potencia configurado adecuadamente. En una realización, el circuito de control de potencia comprende uno o más circuitos de tratamiento, incluyendo un circuito de estimación de la calidad de la señal configurado para estimar la calidad de la señal para el canal de control de potencia, un circuito de estimación de CER configurado para estimar la CER para los comandos de control de potencia recibidos un circuito de control de potencia del lazo externo configurado para ajustar la calidad objetivo de la señal, y un circuito de control de potencia del lazo interno configurado para generar la realimentación de control de la potencia del transmisor. El circuito de control de potencia del lazo externo y el circuito de estimación de CER se pueden omitir en realizaciones en las que el circuito de control de potencia del lazo interno use un valor mapeado de la calidad de la señal como su calidad objetivo de la señal.

Por supuesto, la presente invención no se limita a las características y ventajas anteriores.

Los expertos en la técnica apreciarán las características y ventajas adicionales de la presente invención después de leer las siguientes explicaciones, y tras ver los dibujos que se acompañan.

#### BREVE DESCRIPCION DE LOS DIBUJOS

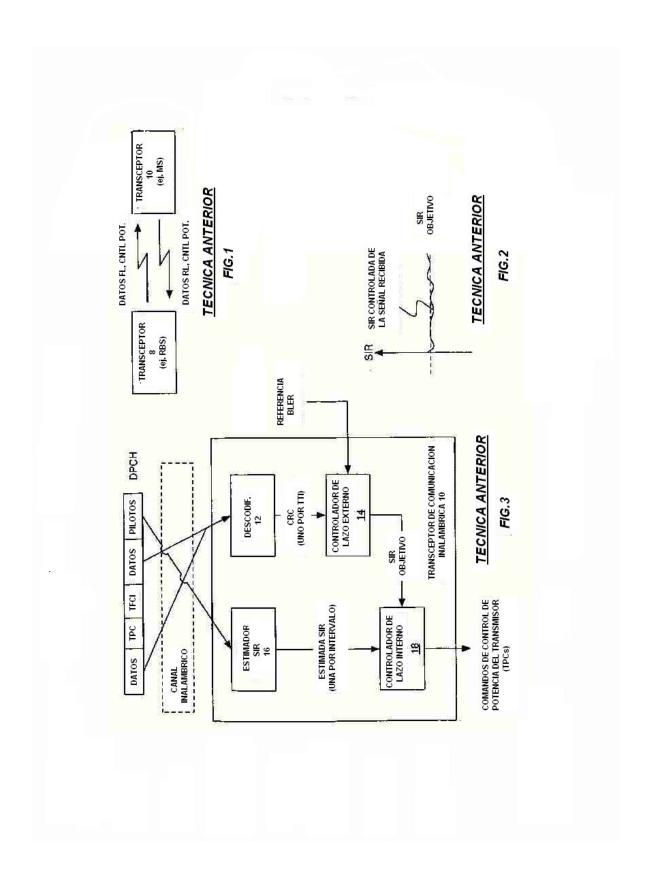

Las figuras 1 a 3 se refieren a la generación convencional de realimentación de control de potencia para un canal de control de potencia que incluye codificación de errores para estimación BER.

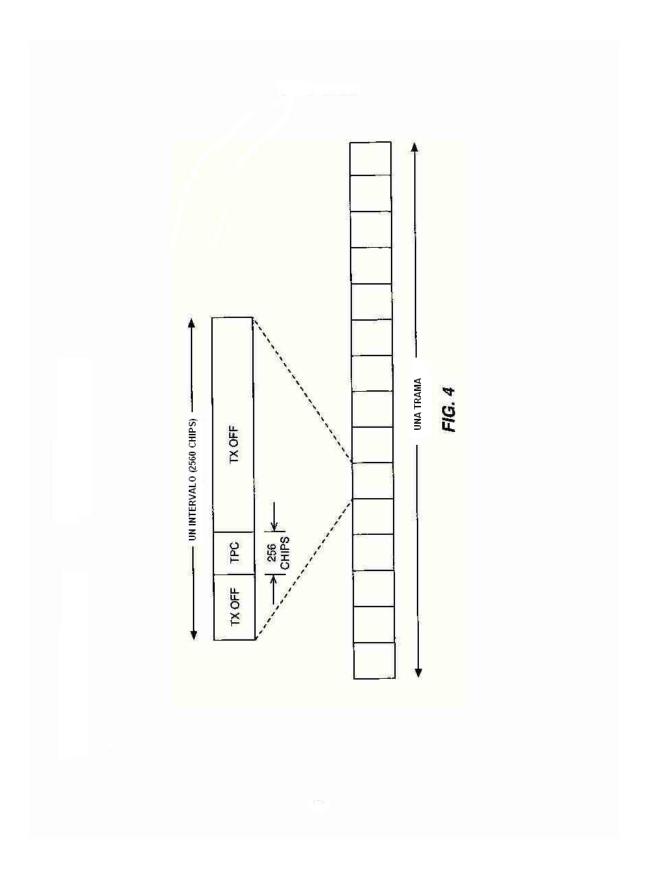

La figura 4 es un diagrama lógico de un F-DPCH, tal como usan los sistemas WCDMA, en el que el canal de control de potencia carece de codificación de errores que de otro modo podría servir como base para la estimación de la tasa de errores para ser usada en generar realimentación de control de potencia.

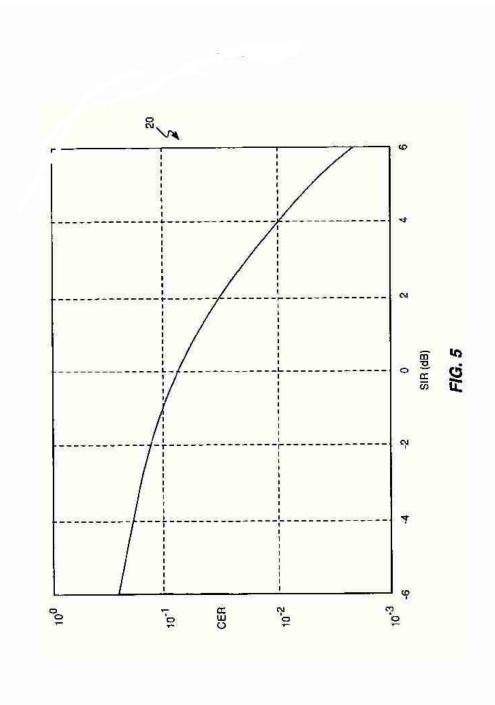

La figura 5 es un gráfico de una función definida de mapeo de la calidad de la señal/tasa de error de

comando, en el que la calidad de la señal se expresa en términos de relación señal/interferencia (SIR).

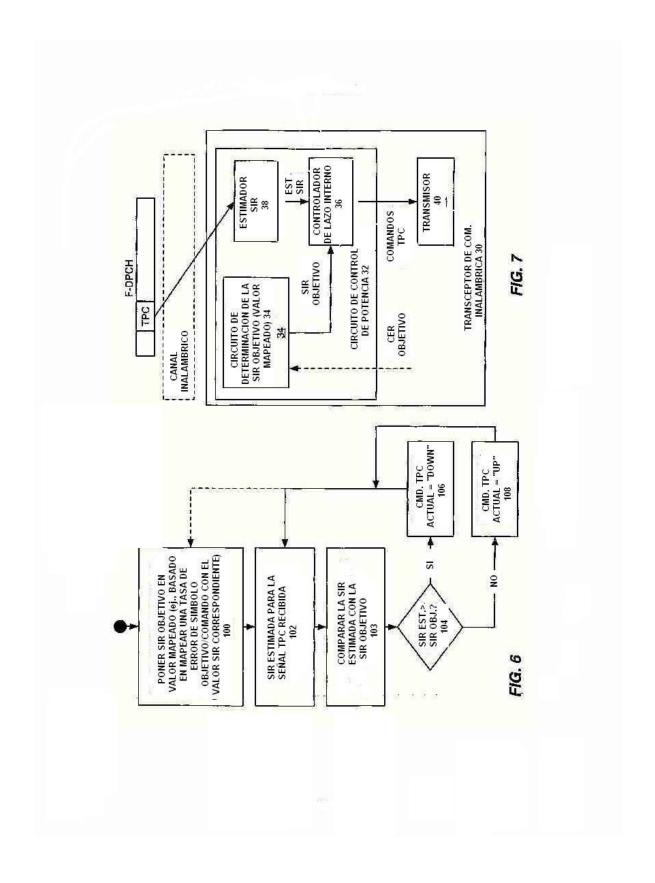

La figura 6 es un diagrama lógico de flujo que ilustra la lógica de tratamiento de una realización de generar realimentación de control de potencia del transmisor, tal como para los comandos de control de potencia recibidos en un F-DPCH en sistemas WCDMA, basándose en el uso de una función definida de mapeo de SIR/CER, tal como la mostrada en la figura 5.

La figura 7 es un diagrama de bloques que ilustra una realización de una disposición funcional de circuito que puede ser implementada en un circuito de control de potencia configurado de acuerdo con la lógica de tratamiento de la figura 6.

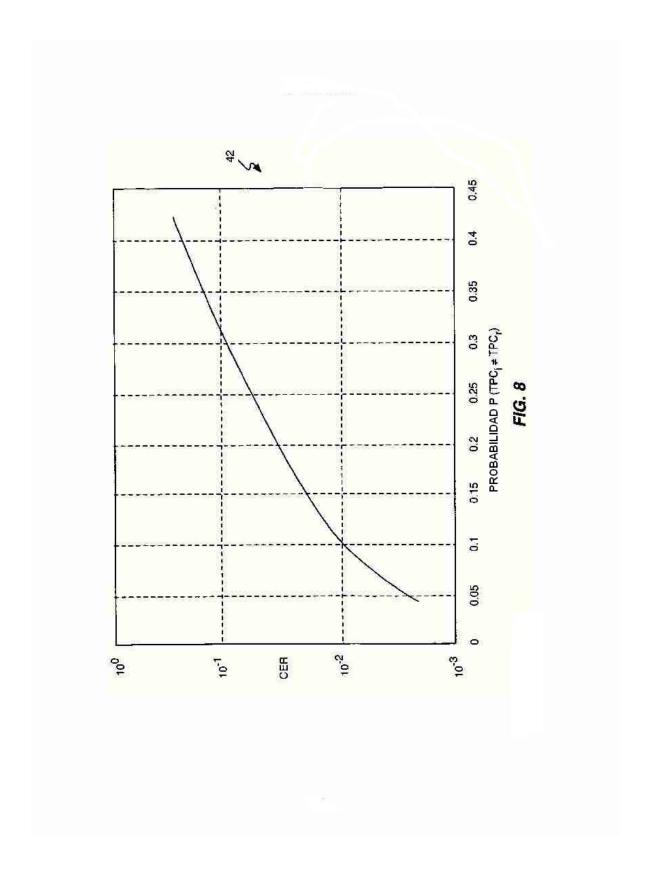

La figura 8 es un gráfico de una función definida (error de recepción) de mapeo de probabilidad/CER.

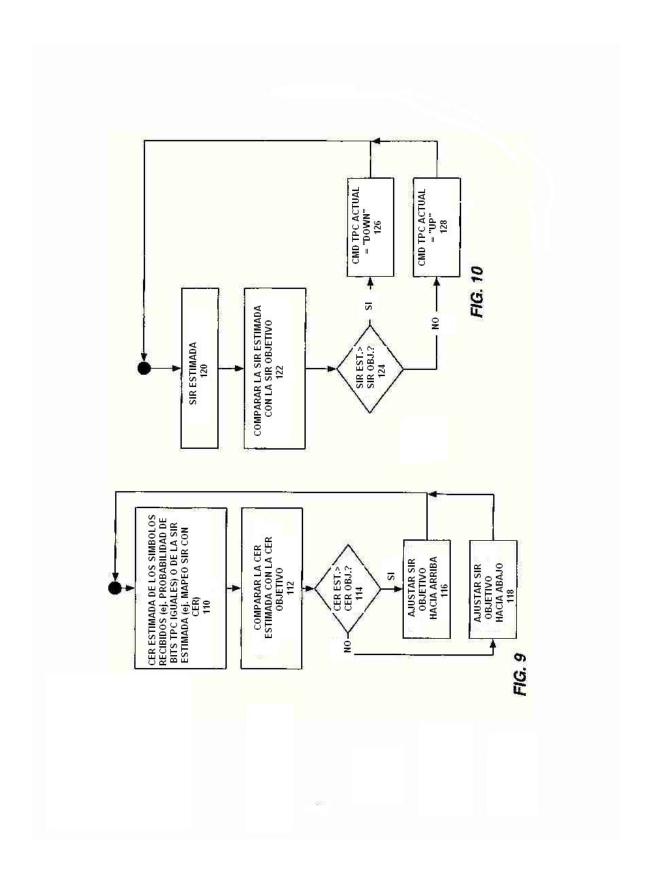

Las figuras 9 y 10 son diagramas lógicos de flujo que ilustran la lógica de tratamiento de una realización de generar una realimentación de control de potencia del transmisor, tal como para los comandos de control de potencia recibidos en un F-DPCH en sistemas WCDMA, basándose en el uso de una función definida de mapeo de probabilidad/CER, tal como la mostrada en la figura 8.

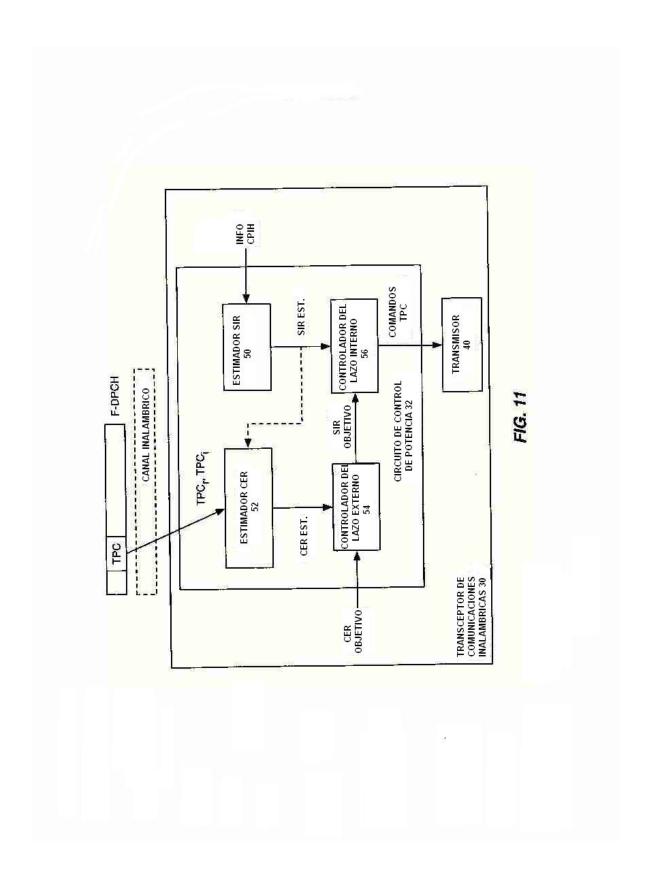

La figura 11 es un diagrama de bloques que ilustra una realización de una disposición funcional del circuito que se puede implementar en un circuito de control de potencia configurado de acuerdo con la lógica de tratamiento de las figuras 9 y 10.

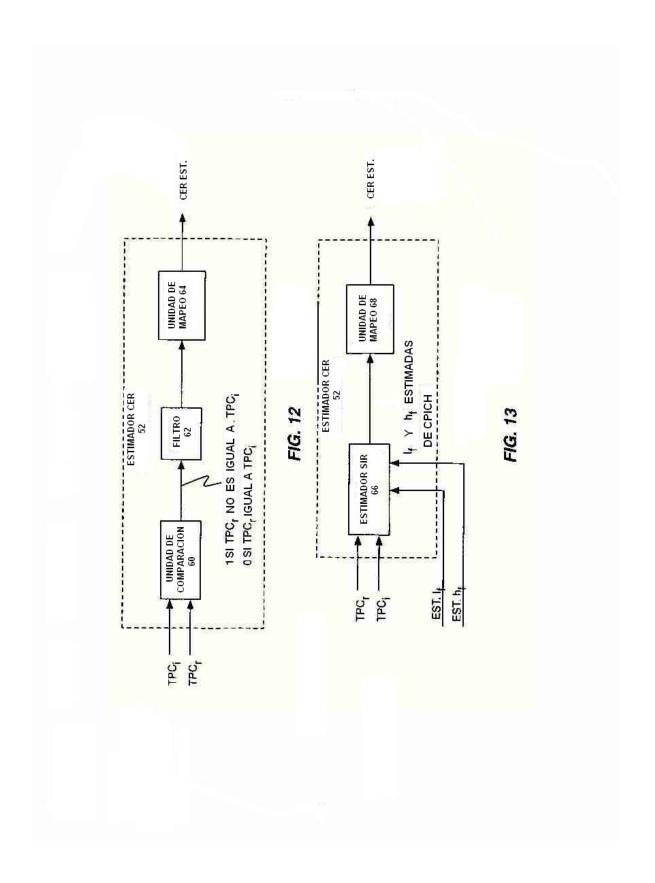

La figura 12 es un diagrama de bloques que ilustra una realización de un circuito de estimación de CER.

La figura 13 es un diagrama de bloques que ilustra otra realización de un circuito de estimación de CER.

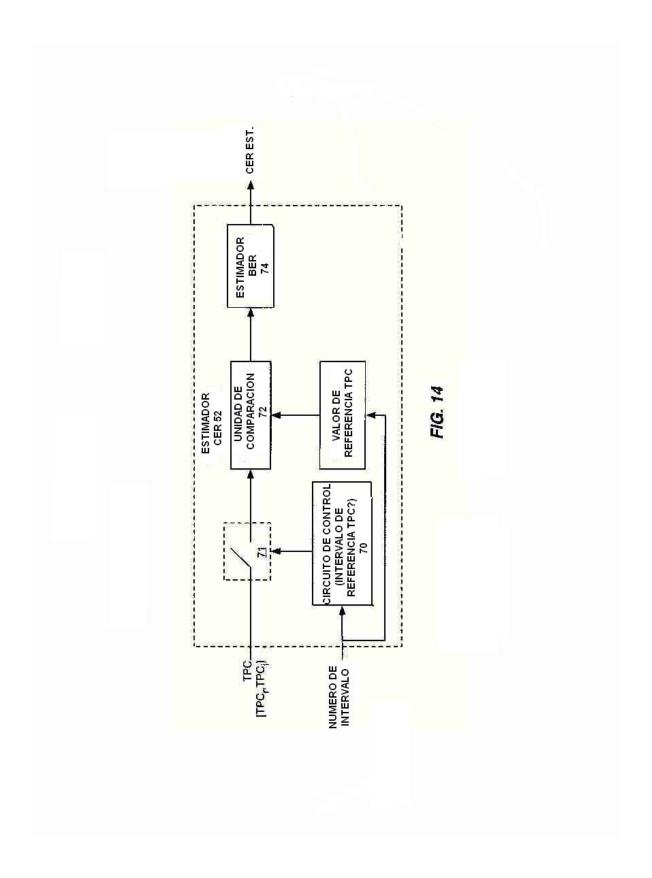

La figura 14 es un diagrama de bloques que ilustra otra realización más de un circuito de estimación de CER.

#### **DESCRIPCION DETALLADA**

5

10

15

20

25

30

35

40

45

50

55

60

65

La figura 1 ilustra un enfoque convencional para controlar la potencia de transmisión del enlace directo (FL) y del enlace inverso (RL) como se adopta en redes de comunicación inalámbrica basadas en CDMA. Un primer transceptor 8 (por ejemplo, una estación base de radio o RBS) transmite datos FL y comandos de control de potencia a un segundo transceptor 10 (por ejemplo, una estación móvil o MS). A su vez, el segundo transceptor 10 transmite datos RL y comandos de control de potencia al primer transceptor 8. Dentro de este planteamiento, el segundo transceptor 10 ajusta su potencia de transmisión RL hacia arriba y hacia abajo en respuesta a los comandos de control de potencia recibidos por él en el FL del primer transceptor 8. Recíprocamente, el primer transceptor 8 ajusta su potencia de transmisión FL hacia arriba y hacia abajo en respuesta a los comandos de control de potencia recibidos por él en el RL del segundo transceptor 10.

El primer transceptor 8 genera los comandos de control de potencia que se envían al segundo transceptor 10 en el FL basándose en si está recibiendo las transmisiones RL del segundo transceptor 10 por encima o por debajo de una calidad objetivo de la señal, expresada usualmente en dBs. A su vez, el segundo transceptor 10 genera los comandos de control de potencia que se envían al primer transceptor 8 en el RL basándose en si está recibiendo las transmisiones FL del primer transceptor 8 por encima o por debajo de una calidad objetivo de la señal. Así, cada transceptor proporciona al otro la realimentación del control de potencia para asegurar que sus respectivas transmisiones se reciben con intensidades de señal aceptables. La figura 2 ilustra el control de potencia de este modo, en el que la SIR controlada de una señal recibida se mantiene en o alrededor de la SIR objetivo por medio del empleo de la realimentación de control de potencia.

La figura 3 usa el transceptor 10 como base para ilustrar más detalles de un método convencional de control de potencia. Como se ilustra, el transceptor 10 recibe una señal de comunicación (se muestra un Canal Físico Dedicado (DPCH)) que incluye datos (tráfico de usuario), pilotos y comandos de control de potencia. El transceptor 10 usa la información recibida piloto para estimar las propiedades del canal inalámbrico, y entonces descodifica los datos recibidos usando las estimadas del canal y la información de error de corrección/detección incluida en los datos. Más en particular, un descodificador 12 usa la Comprobación Cíclica Redundante (CRC) u otra información de codificación de error para detectar errores recibidos en los datos y un controlador de lazo externo 14 usa esa información para medir una tasa de error en los datos recibidos, que se puede expresar de diversos modos, tales como una Tasa de Error de Bloque (BLER), una Tasa de Error de Trama (FER) o una Tasa de Error de Bit (BER).

Independientemente, un controlador 14 de lazo externo compara la tasa medida de error con una tasa de referencia de error (por ejemplo, una BLER de referencia u objetivo). Si la tasa medida de error excede la tasa objetivo de error, el controlador de lazo externo 14 ajusta una SIR objetivo hacia arriba. Por el contrario, si la tasa medida de error está por debajo de la misma o de una tasa objetivo de error diferente, el controlador 14 de lazo externo ajusta la SIR objetivo hacia abajo. Por ejemplo, si la tasa medida de error excede el 10%, el controlador 14 de lazo externo ajusta la SIR objetivo hacia arriba y si la tasa medida de error cae por debajo del 1%, el controlador 14 de lazo externo ajusta la SIR objetivo hacia abajo. Tal ajuste corriente de la SIR objetivo influye sobre la potencia de transmisión del transmisor distante, ya que un controlador 18 de lazo interno genera comandos de control de potencia de transmisión para el transmisor distante como valores "subir" o "bajar", dependiendo de si la calidad de la señal, por ejemplo, SIR, está por encima o por debajo de la SIR objetivo.

Dos puntos notables sobresalen en el contexto del control convencional de potencia como se acaba de describir. Primero, los bits de control de potencia enviados desde el transceptor 8 al transceptor 10 para controlar la potencia

de transmisión del transceptor 10 se incluyen dentro de los datos que se están enviando al transceptor 10. Dado que el transceptor 10 proporciona realimentación de control de potencia para asegurar que el transceptor 8 transmite estos datos con una potencia lo suficientemente alta para asegurar la recepción fiable de los datos, la información de control de potencia del transceptor 8 se envía "automáticamente" con una potencia de transmisión que asegure la recepción fiable en el transceptor 10. Segundo, la base total para ajustar la SIR objetivo en el transceptor 10 es si la tasa medida de error para los datos recibidos está por encima o por debajo de tasas aceptables (objetivo). Sin la habilidad para hacer tales mediciones, el controlador 14 de lazo externo no dispondría de base para ajustar la SIR objetivo usada por el controlador 18 de lazo interno.

5

45

65

Teniendo en cuenta estos puntos, cualquier experto en la técnica reconocerá los desafíos que surgen al generar realimentación de control de potencia para señales recibidas y que la ausencia de error en los datos codificados o conocidos se puede usar como base para determinar los BLER, FER, etc., de las señales recibidas. A modo de ejemplo no restrictivo, la figura 4 ilustra un Canal Físico Dedicado Fraccional (F-DPCH), que es un tipo de canal definido por las normas WCDMA para transportar información de control de potencia a un cierto número de transceptores distantes.

Por ejemplo, una estación base en una red WCDMA puede usar un F-DPCH para transmitir información de control de potencia a una pluralidad de estaciones móviles.

- Dado que la información transmitida de control de potencia se usa para controlar las potencias de transmisión de enlace inverso de esas estaciones móviles, es importante que la información de control de potencia se transmita con el nivel de potencia apropiado. Sin embargo, es difícil para las estaciones móviles determinar si la información entrante de control de potencia en el F-DPCH recibido se está transmitiendo con una potencia suficientemente alta, porque no existen datos de error-codificados o conocidos que se puedan evaluar como una indicación de las tasas de error de datos recibidas. Más en particular, en lo que respecta al F-DPCH, una estación móvil dada simplemente recibe comandos de control de potencia entrantes y se le deja sin ningún mecanismo claro de generar realimentación de control de potencia que asegure que aquellos comandos entrantes de control de potencia (es decir, TPCs) se le están transmitiendo a ella por la estación base de radio con el nivel de potencia correcto.

- De acuerdo con una realización para generar realimentación de control de potencia como se enseña en la presente memoria, un transceptor de comunicaciones (por ejemplo, estación móvil, estación base de radio, etc.) ajusta su potencia de transmisión en respuesta a comandos entrantes de control de potencia recibidos sobre un canal de control de potencia, y genera realimentación de control de potencia para el transmisor distante que origina esos comandos basándose en estimar una calidad de señal, tal como una SIR, para el canal de control de potencia, y genera la realimentación de control de potencia de transmisión comparando la SIR estimada con una SIR objetivo determinada mediante el mapeo de una CER objetivo con un valor de SIR correspondiente de acuerdo con una función de mapeo definida de SIR/CER. Es decir, la estación móvil se programa con, o calcula dinámicamente, una CER objetivo que representa, por ejemplo, el límite superior en tasas tolerables (control de potencia) de error de comando. La función de mapeo de SIR/CER proporciona así la base para identificar el valor SIR correspondiente a la CER objetivo.

La figura 5 ilustra una función de mapeo 20 de SIR/CER, mostrada como una representación logarítmica de CER con respecto a SIR. Se ve que una CER dada, por ejemplo 10<sup>-1</sup> (10%), puede ser directamente mapeada con un valor SIR correspondiente. Así, si la estación móvil usa el valor SIR mapeado como su SIR objetivo para generar realimentación de control de potencia de transmisión para el canal de control de potencia recibida, se asegura generalmente que la CER de los comandos de control de potencia recibidos sobre ese canal de control de potencia no excederá el valor objetivo CER.

La figura 6 ilustra la lógica de tratamiento para implementar el control de potencia basándose en una SIR objetivo "mapeada", en la que el tratamiento comienza ajustando la SIR objetivo basándose en un valor mapeado (es decir, ajustando la SIR objetivo basándose en mapear una CER objetivo con el valor SIR correspondiente de acuerdo con un mapeo definido de SIR/CER (Etapa 100)). El tratamiento continúa con la estimación de la SIR real de la señal recibida, por ejemplo, del símbolo TPC transportado por el canal de control de potencia recibida (Etapa 102). El tratamiento continúa con una comparación entre la SIR estimada y la SIR objetivo (mapeada) (Etapas 103 y 104). Si la SIR estimada está por encima de la SIR objetivo, la lógica de control de potencia sitúa su comando de salida TPC como "DOWN" (Etapa 106). Al contrario, si la SIR estimada está por debajo de la SIR objetivo, la lógica de control de potencia sitúa su comando de salida como "UP" (Etapa 108). De este modo, los comandos UP y DOWN de flujos lógicos de control de potencia vuelven al transmisor distante, en respuesta para determinar si la SIR estimada para el canal de control de potencia recibida está por encima o por debajo de la SIR objetivo ajustada por medio de la relación de mapeo de SIR/CER.

Para comprender mejor este enfoque del tratamiento, puede ser muy útil proporcionar detalles en el contexto de los comandos de control de potencia entrantes en una estación móvil en particular sobre un F-DPCH, pero se debe comprender que esto no es un ejemplo restrictivo de generar realimentación de control de potencia como se enseña en esta memoria. Los comandos de control de potencia sobre un F-DPCH se transmiten como símbolos. Más en

particular, cada comando de control de potencia comprende un símbolo de comando de TPC de 2 bits. Suponiendo que la estación móvil use alguna forma de receptor RAKE, el símbolo TPC recibido por cada sub-receptor (RAKE), y<sub>f</sub> (k), puede ser modelado como

5  $y_f(k) = g(k)h_f(k)u(k) + e_f(k)$  Ec.1

donde u(k) es el símbolo trasmitido, e<sub>f</sub>(k) es la interferencia Gaussiana, h<sub>f</sub>(k)es la respuesta estimada de canal desde el Canal Piloto Común (CPICH) recibido en asociación con el F-DPCH, y g(t)>0 es el desplazamiento de la ganancia real usado en el F-DPCH relativo al CPICH.

Además, para la Ec.1, obsérvese que el valor esperado y el valor varianza, respectivamente, resultan

$E(e_f) = 0 Ec.2$

$E\left(\left|e_f\right|^2\right) = I_f$  Ec. 3

15

20

30

35

40

45

donde  $I_f$  es la potencia de la interferencia por símbolo recibido en el sub-receptor f del receptor. Obsérvese, también, que un F-DPCH con un factor de difusión de 256, una relación entre la interferencia Gaussiana  $e_f(k)$  y la relación

Señal/Ruido (SIR) por símbolo,  $N_0$ , para el sub-receptor f del receptor se pueden expresar como

$$\frac{\left|gh_f\right|^2}{I_f} = \left(\frac{E_s}{N_o}\right)_f = 256 \cdot \left(\frac{E_c}{I_o}\right)_f$$

Ec.4

donde  $E_s$  es la energía recibida de la señal por símbolo,  $E_c$  es la energía recibida de la señal por chip,  $N_0$  es la potencia recibida de ruido, y  $I_0$  es la potencia recibida de interferencia.

Teniendo en cuenta lo anterior, un punto de partida en el análisis de la determinación de la tasa de error para el F-DPCH comienza con observar que son posibles dos diferentes símbolos de comando TPC, pero la modulación subyacente de símbolo es la misma para ambos símbolos de comando. Así, los símbolos de comando TPC se pueden expresar como

$u = u_0$ . TPC Ec.5

donde TPC € [-1.1] es el comando TPC (donde -1 representa un lógico bajo y viceversa) y el símbolo de modulación base (sin signo) es

$u_o = \frac{\left(1+i\right)}{\sqrt{2}}$  Ec.6

Los comandos recibidos TPC (por ejemplo, los símbolos TPC recibidos) se pueden estimar usando máxima combinación de relación como

5

$$TPC_{est} = sign\left(Re\left(u_o^* \sum_{f=1}^{N_f} \frac{\hat{y}_f \hat{h}_f^*}{\hat{I}_f}\right)\right)$$

Ec.7

donde  $\widehat{h_f}$   $\widehat{y}$   $\widehat{l_f}$  se pueden estimar del CPICH. De la ecuación 7 se ve que el receptor no necesita conocer el valor del desplazamiento g de la ganancia para descodificar los símbolos recibidos TCP; por el contrario, es suficiente 10 conocer que g>0.

Los bits individuales del símbolo TCP, TCP<sub>i</sub> y TCP<sub>i</sub> se pueden estimar como

$$TPC_{est,r} = \text{Re} \sum_{f=1}^{N_f} \frac{\hat{y}_f \hat{h}_f^*}{\hat{I}_f}$$

Ec.8

У

$$TPC_{est,i} = \operatorname{Im} \sum_{f=1}^{N_f} \frac{\hat{y}_f \hat{h}_f^*}{\hat{I}_f}$$

Ec.9

20

15

Además, ambos bits transmitidos en cada símbolo TPC son, por definición, iguales. Por ello, cada símbolo TPC estimado se puede expresar como

$$TPC_{est} = sign\left(Re\left(u_o^* \cdot \left(TPC_{est,r} + i \cdot TPC_{est,i}\right)\right)\right)$$

Ec.10

30

donde ambos  $h_{fy}I_f$  se estiman basándose en el CPICH.

Teniendo en cuenta las relaciones anteriores, la SIR del F-DPCH se puede estimar como

$$\frac{\hat{E}_s}{\hat{N}_o} = \left(-N_f + \sum_{f=1}^{N_f} \frac{\left|y_f\right|^2}{\hat{I}_f}\right)$$

Ec.11

40

Obsérvese que es posible usar la potencia recibida de la señal | | directamente sin computar una estimación de canal, porque con sólo un símbolo TCP  $|(gh_I)_{est}| = |y_f|_{est} = |y_f|_{est}$  También, hay que observar que la estimación obtenida en la ecuación 11 se puede mejorar usando ambos bits piloto en los bits CPICH y TPC. Además, una estimación SIR que utiliza la estimación del canal CPICH y una estimación del desplazamiento g de la ganancia se puede obtener como

$$\frac{\hat{E}_s}{\hat{N}_o} = \left(-N_f + \hat{g}^2 \sum_{f=1}^{N_f} \frac{\left|\hat{h}_f\right|^2}{\hat{I}_f}\right)$$

Ec.12

donde el desplazamiento estimado de la ganancia 🗿 se puede determinar mediante filtrado y enviado delante de los comandos previamente transmitidos por la estación móvil (a la estación base). Continuando con el análisis, el desplazamiento estimado de la ganancia se puede calcular como

5

10

$$\hat{g}(k) = \alpha \cdot 10^{\frac{-1.7PC(k-d)}{10}} \cdot \hat{g}(k-1) + (1-\alpha) \cdot \frac{\left| u_o^* \sum_{f} \frac{y_f(k) \hat{h}_f^*(k)}{\hat{I}_f(k)} \right|}{\left| \sum_{f} \frac{\left| \hat{h}_f(k) \right|^2}{\hat{I}_f(k)} \right|}$$

Ec.13

donde d es un retardo del comando de TPC y α es una constante del filtro seleccionada.

En otra realización que basa la estimación SIR para el F-DPCH sobre el CPICH, las salidas del receptor (RAKE) para el símbolo de TCP recibido en el intervalo *késimo* de la trama *iésima* se puede expresar como,

$$z_i(k) = \lambda g_i(k)c_i(k)u_i(k) + e_i(k)$$

Ec.14

20

25

donde  $\lambda$  es un nivel inicial de la ganancia del F–DPCH,  $g_i(k)$  es el desplazamiento de la ganancia determinado por los comandos de TPC del enlace inverso,  $c_i(k)$  se determina por medio de la respuesta de la red y combinando las ponderaciones,  $u_i(k)$  es el valor del símbolo TPC y  $e_i(k)$  es la muestra de ruido. Aquí la respuesta de la red cuenta para la forma de onda del impulso del transmisor, canal de radio y forma de onda recibida. El análisis supone que  $g_i(k)$  sigue los comandos de TPC del enlace inverso (enviado por la estación móvil) y, como resultado, el producto de  $g_i(k)$ ,  $c_i(k)$  y  $u_i(k)$  es decir  $v_i(k) = g_i(k)c_i(k)u_i(k)$ , se supone conocido. Para evitar la propagación del error debido a errores de recepción del comando TPC del enlace inverso o que la estación base no siga los comandos de TPC del enlace inverso, el desplazamiento de la ganancia  $g_i(k)$  se puede reponer a 1 durante el último intervalo de cada trama F-DPCH, es decir,  $g_i(M-1) = 1$ , donde M es el número de intervalos por trama.

30

Reuniendo  $z_i(k)$ ,  $v_i(k)$  y  $e_i(k)$  de todos los intervalos de una trama en un vector,

$$z_{i} = \lambda v_{i} \div e_{i}$$

Ec.15

La estimación mínimo cuadrática (LS) belsada en la écruadió se puede expresar como

40

$$\hat{\lambda}(i) = \frac{\text{Re}(\mathbf{v}_i^H \mathbf{z}_i)}{\left|\mathbf{v}_i\right|^2}$$

Ec.16

Se puede mostrar que el estimador en la ecuación 16 es también un estimador de error mínimo cuadrático medio (MMSE).

de trama i es

De acuerdo con tal estimación, la diferencia estimada de la ganancia (i - 1) de la trama *i*-1se puede usar para producir una estimación SIR, que se puede expresar como una estimada de la SIR en cada intervalo en la trama *i*. Por ejemplo, si se usa RAKE o la combinación G-RAKE, el símbolo de SIR para el símbolo de TPC en el intervalo *k*

50

$$\hat{\gamma}_i(k) = \frac{\hat{\lambda}_{i-1}^2 g_i^2(k) \mathbf{w}^H \mathbf{h} \mathbf{h}^H \mathbf{w}}{\mathbf{w}^H \mathbf{R} \mathbf{w}}$$

Ec.17

donde  $\mathbf{w}$  es la ponderación combinativa,  $\mathbf{h}$  es la respuesta de la red y  $\mathbf{R}$  es la matriz de covarianza para la interferencia desde diferentes sub-receptores. Las estimadas de  $\mathbf{h}$  y  $\mathbf{R}$  se pueden obtener del CPICH.

Obsérvese que el desplazamiento de potencia entre el CPICH y el F-DPCH durante el primer intervalo de una trama es doblado en λ. Además, obsérvese que la expresión

$$\frac{\mathbf{w}^H \mathbf{h} \mathbf{h}^H \mathbf{w}}{\mathbf{w}^H \mathbf{p} \mathbf{w}}$$

Ec.18

corresponde al símbolo SIR del CPICH. Si se usa la combinación Generalizada de RAKE (G-RAKE), esto se simplifica a

$$\hat{\gamma}_i(k) = \hat{\lambda}_{i-1}^2 g_i^2(k) \mathbf{h}^H \mathbf{R}^{-1} \mathbf{h}$$

Ec.19

donde, de nuevo  $\mathbf{h}^{\mathbf{H}} \mathbf{R}^{-1}$   $\mathbf{h}$  corresponde al símbolo SIR del CPICH.

Usando el marco analítico anterior, y volviendo al gráfico de la figura 5, se comprenderá que un mapa de ruido blanco Gaussiano aditivo (AWGN) entre la SIR y la CER es relativamente independiente del canal, haciendo posible mapear directamente la CER objetivo con una SIR objetivo, haciendo por ello superfluo el control convencional de potencia del lazo externo.

(Obsérvese, también, que el mapa AWGN es válido obviamente para un canal AWGN, pero también es una buena aproximación para otros tipos de canales). Más en particular, suponiendo que  $h_f$  y  $l_f$  son buenas aproximaciones de  $h_f$  y  $l_f$  se puede realizar que

$$TPC_{est} = sign(TPC + n)$$

Ec.20

donde

10

15

25

30

35

$$n = \operatorname{Re}\left(\frac{u_o^{\bullet} \cdot \sum_{f} \frac{h_f^{\bullet} e_f}{I_f}}{g \cdot \sum_{f} \frac{\left|h_f^{\circ}\right|^2}{I_f}}\right)$$

Ec.21

La tasa de error del comando de TPC (CER) se puede expresar por consiguiente como

$$CER = \frac{1}{2} \cdot P(|n| > 1) = P(n > 1)$$

Ec.22

Y la varianza de n (suponiendo ruido de sub-receptor no correlacionado) viene dada por

50

$$E(n^2) = \frac{1}{2\left(g^2 \cdot \sum_f \frac{\left|h_f\right|^2}{I_f}\right)} = \frac{1}{2 \cdot E_s/N_o}$$

Ec.23

5

10

15

30

35

40

45

50

55

60

Así, con la ecuación 23, la CER se da como una función de SIR ( No ), tal como se refleja en la figura 5, y se ve que este mapeo funcional se puede usar para identificar una SIR objetivo para el control de potencia del lazo interno que corresponde a la deseada (objetivo) CER.

La figura 7 ilustra una realización de un transceptor de comunicación inalámbrica 30 que comprende todo o parte de un dispositivo o sistema de comunicación inalámbrica. A modo de ejemplo no restrictivo, tal dispositivo puede comprender una estación móvil, tal como un radioteléfono celular, o puede comprender un buscapersonas inalámbrico, un Asistente Digital Portátil (PDA), un ordenador portátil o un ordenador de bolsillo o un módulo de comunicación según esta memoria. En cualquier caso, el transceptor 30 está configurado para generar la realimentación de control de potencia de transmisión para un canal de control de potencia recibida (por ejemplo, una señal recibida F-DPCH) de acuerdo con el mapeo de SIR/CER descrito anteriormente.

Más detalladamente, el transceptor 30, que puede ser una estación móvil, incluye un circuito de control de potencia 32 que incluye uno o más circuitos de tratamiento configurados para recibir comandos de control de potencia sobre el canal de control de potencia, para estimar una SIR para el canal de control de potencia, y para generar la realimentación de control de la potencia transmitida para el canal de control de potencia comparando la SIR estimada con una SIR objetivo determinada mediante el mapeo de una CER objetivo con un valor de SIR correspondiente de acuerdo con una función de mapeo de SIR/CER definida. La función de mapeo de SIR/CER puede ser, por ejemplo, como se muestra en la figura 5, y la estimación de la SIR puede ser, por ejemplo, la dada por la ecuación 11.

Se debe comprender que el circuito de control de potencia 32 puede comprender uno o más microprocesadores, Procesadores Digitales de Señal (DSPs), u otros tipos de circuitos de tratamiento. (En general, se debe comprender que el circuito de control de potencia 32 se puede implementar en hardware, en software o esencialmente en cualquier combinación de los mismos).

En al menos una disposición funcional del circuito, el circuito de control de potencia 32 comprende un circuito 34 de determinación de una SIR objetivo, un controlador 36 del lazo interno y un circuito 38 de estimación de la SIR. El circuito 34 de determinación de la SIR objetivo puede comprender un circuito de búsqueda de memoria que está configurado para leer un valor SIR premapeado de la memoria, o puede comprender un circuito funcional de mapeado que esté configurado para determinar la SIR objetivo por medio de mapear una CER objetivo con el correspondiente valor de la SIR de acuerdo con una función polinómica o una función de búsqueda de tablas que incorpore una función de mapeo de SIR/CER.

El controlador 36 del lazo interno usa así la SIR objetivo (mapeada) para comparación con la SIR estimada, y genera la realimentación de control de potencia para el canal de control de potencia recibida en forma de comandos de TPC, que pueden ser transmitidos por un circuito transmisor 40 del transceptor 30. El circuito 38 de estimación de la 38 proporciona estimaciones de la SIR al controlador 36 del lazo interno basándose, por ejemplo, en aplicar la ecuación 11 y/o la ecuación 12.

La figura 8 ilustra otra realización basándose en mapeo, en la que se muestra una función de mapeo 42 de probabilidad/CER como un gráfico logarítmico de la CER en función de la probabilidad P de error en la recepción del comando de control de potencia, que es la probabilidad de haber bits de TPC desiguales en un símbolo TPC. Por ejemplo, se ve que una CER del 10% corresponde a una probabilidad de error en la recepción del comando de aproximadamente 30% y una CER de un 1% corresponde a una probabilidad de error en la recepción de un 10%.

Se debe observar que circuito de control de potencia 32 se puede configurar para detectar bits no coincidentes basándose en comparaciones de valor de bit mediante hardware (por ejemplo, +1, -1) o comparaciones de valor de bit mediante software (por ejemplo, +0,99, +0,33). Para la detección de la no coincidencia de valores por software, por ejemplo, el circuito de control de potencia 32 se puede configurar para detectar no coincidencias de bit TPC en un símbolo recibido TPC basándose en evaluar la distancia entre valores software de los bits de TPC. Además, en una o más realizaciones, el circuito de control de potencia 32 se puede configurar para estimar el error relativo de bits por software y mapearlo o correlacionarlo con la CER. La distribución del error relativo de bit por software se puede cuantificar usando una medida de la varianza (como una medida intermedia) antes de mapearla dentro de

una CER. En otra realización, el circuito de control de potencia 32 se puede configurar para detectar comandos de control de potencia recibidos erróneamente por medio de detectar bits no coincidentes y contar los errores de no coincidencia.

La figura 9 ilustra una realización de la lógica de tratamiento basándose en la función de mapeo de probabilidad/CER que se puede incorporar en el circuito de control de potencia 32 del transceptor 30. El tratamiento comienza con la estimación de la CER basándose en la determinación de la probabilidad de error en la recepción para los comandos de control de potencia recibidos sobre el canal de control de potencia (Etapa 110). Obsérvese, también, en una variación de esta realización, que la CER se puede estimar a partir de la SIR estimada, como se detalló en el contexto de la función de mapeo 20 de SIR/CER ilustrada en la figura 5.

El tratamiento continúa con una comparación de la CER estimada con la CER objetivo (Etapa 112), que se puede almacenar en una memoria del transceptor 30 como un valor preconfigurado, o como un valor recibido o actualizado dinámicamente. Si la CER estimada es mayor que la CER objetivo (Etapa 114), el circuito de control de potencia 32 ajusta la SIR objetivo hacia arriba (Etapa 116).

Por el contrario, si la CER estimada es menor que la CER objetivo, o menor que una fracción definida de la CER objetivo, el circuito de control de potencia 32 ajusta la SIR objetivo hacia abajo (Etapa 118).

Se debe comprender que se contemplan en esta memoria variaciones de esta lógica. Por ejemplo, en adición al uso de diferentes niveles de umbral de la CER objetivo para aumentar y disminuir la SIR objetivo (por ejemplo, aumentar la SIR objetivo si la estimada CER > diez por ciento, disminuir la SIR objetivo si la estimada CER < uno por ciento) el circuito de control de potencia puede generar más de dos estados de comando. Como ejemplo, se pueden generar comandos de TPC tales como UP, DOWN y HOLD, de manera que permite que el transmisor distante conserve sus ajustes actuales de potencia de transmisión, con tal de que la SIR estimada en el transceptor 30 permanezca dentro de un intervalo entre las SIRs objetivo definidas superior e inferior.

En cualquier caso, en el que la figura 9 ilustra la porción del lazo externo del control de potencia, la figura 10 ilustra la porción complementaria del lazo interno, que se puede configurar para ser ejecutado simultáneamente con el proceso de control de potencia del lazo externo de la figura 9, pero generalmente a una más alta frecuencia de ejecución. Por ejemplo, la lógica de la figura 10 puede operar a 800 Hz o más, de forma que se genera un nuevo comando de TPC por el circuito de control de potencia 32 al menos cada 1,25 ms. En contraste, el ajuste del control de potencia del lazo externo de la SIR objetivo ilustrado en la figura 9 puede ejecutarse cada 20 ms, 50 ms, o a alguna otra tasa inferior.

Independientemente de su frecuencia de ejecución, el circuito de control de potencia 32 realiza la lógica de tratamiento del lazo interno de la figura 10 estimando la calidad de la señal, tal como la SIR, para los símbolos de TPC recibidos en el canal de control de potencia recibida para el actual intervalo de tiempo (intervalo, trama, etc.) (Etapa 120), y comparando la calidad estimada de la señal con la calidad objetivo de la señal (como se determinó de acuerdo con la lógica de tratamiento de la figura 9) (Etapa 122). Por ejemplo, una SIR estimada se puede comparar con una SIR objetivo. Si la SIR estimada es mayor que la SIR objetivo (Etapa124), se genera el comando de TPC para el intervalo actual del comando como un comando DOWN (Etapa 126). Al contrario, si la SIR estimada no es mayor que la SIR objetivo, se genera el comando de TPC para el intervalo actual del comando como un comando UP (Etapa 128) para hacer que el transmisor distante aumente incrementalmente la potencia de transmisión asignada a la transmisión del canal de control de potencia recibida en el transceptor 30. Por supuesto, como se indicó anteriormente, estados adicionales de comando, tales como HOLD, se pueden implementar en algunas realizaciones.

La figura 11 ilustra una realización del circuito de control de potencia 32 que está configurado para realizar la lógica de tratamiento de las figuras 9 y 10, o variaciones de esa lógica. En la realización ilustrada, el circuito de control de potencia 32 comprende un circuito 50 de estimación de la SIR, un circuito 52 de estimación de la CER, un controlador 54 del lazo externo y un controlador 56 del lazo interno.

El circuito 52 de estimación de la CER se puede configurar para basar su estimación en el conocimiento de que ambos bits del comando de TPC de los comandos de control de potencia entrantes en el canal de control de potencia recibida son iguales. (Obsérvese que esta condición se mantiene verdadera para los símbolos de dos bits del comando de control de potencia definidos por las normas WCDMA para el control de potencia sobre un F-DPCH, pero puede no ser verdadera en otros casos, en cuyo caso se pueden usar otras bases para la estimación de CER).

Conociendo que los 2 bits de cada comando de control de potencia recibida son por definición iguales, la probabilidad de que se reciban bits de comando desiguales se puede convertir en una CER estimada de acuerdo con la función probabilidad/CER 42 ilustrada en la figura 8. Este enfoque se basa en la realización de que la relación entre la probabilidad de recibir bits de comando desiguales y la CER es relativamente independiente del canal.

65

15

30

35

40

45

Suponiendo que el ruido en los dos bits de TPC estimados por software en un comando de control de potencia recibida dado no esté correlacionado, entonces la probabilidad de que los 2 bits estimados mediante hardware sean desiguales, TPC<sub>15</sub> e [1, -1] viene dada por

5

$$\zeta = P(TPC_r \neq TPC_i) = \frac{SIR}{\pi} \int_{x_1 = -\infty}^{0} e^{\frac{-(x_1 - 1) \cdot SIR}{2}} dx_1 \cdot \int_{x_2 = 0}^{\infty} e^{\frac{-(x_2 - 1) \cdot SIR}{2}} dx_2$$

Ec.24

10

donde  $SIR=E_b/N_0$  es la SIR de los bits de TPC estimados, y donde las variables  $x_1$  y  $x_2$  representan los bits de TPC recibidos en un comando de control de potencia dado cuando los bits transmitidos de ese comando son ambos igual a uno. La CER viene dada así por

15

$$CER = \frac{SIR}{2\pi} \int_{x_1 = -\infty}^{0} \int_{x_2 = -\infty}^{-x_1} e^{\frac{-(x_1 + x_2 - 2) \cdot SIR}{2}} dx_1 dx_2$$

Ec.25

20

Una aproximación polinómica adecuada de la función 42 de mapeo de la probabilidad/CER, para el intervalo ilustrado en la figura 8, viene dada por

25

$$CER_{est} = 2.31 \cdot \zeta^3 + 0.141 \cdot \zeta - 4.91 \cdot 10^{-3}$$

30

donde la probabilidad de error en la recepción del comando para bits de TPC desiguales se puede estimar como

$$\hat{\zeta}_k = \alpha \cdot \hat{\zeta}_{k-1} + (1 - \alpha) \frac{1}{2} |TPC_r - TPC_i|$$

Ec.27

35

y donde  $\infty[0,1]$  es una constante del filtro (para un filtro de ponderación exponencial). Para aplicaciones WCDMA, un valor adecuado es  $\alpha$  = 0,99 correspondiente a una constante de tiempo de 100 intervalos, que complementa la ocurrencia esperada de entre 10 y 30 errores de recepción (bits desiguales de comando de TPC) durante esta constante de tiempo. Esta frecuencia de ocurrencia de error de recepción generalmente debería ser suficiente para un buen rendimiento de la estimación de la CER.

40

La figura 12 ilustra una realización complementaria del circuito 52 de estimación de la CER, que comprende una unidad de comparación 60, un filtro 62 y una unidad de mapeo 64. La unidad de comparación 60 compara los bits de los comandos de TPC entrantes para detectar la recepción (errónea) de bits desiguales, y proporciona un "1" al filtro 62 si los bits de un comando de TPC recibido dado son desiguales, y proporciona un "0 "en caso contrario. A su vez, el filtro 62 filtra esta salida 1/0 de la unidad de comparación 60 y proporciona la salida filtrada (por ejemplo, ecuación 27) a la unidad de mapeo 64. La unidad de mapeo 64 usa la salida filtrada para estimar la CER del canal de control de potencia recibida de acuerdo con, por ejemplo, la ecuación 26.

50

45

La figura 13 ilustra otra realización del circuito 52 de estimación de la CER que usa un mapeo de SIR/CER. Así, la realización ilustrada del circuito 52 de estimación de la CER comprende (o está asociada con) un circuito 66 de

estimación de la SIR, que usa los comandos de TPC recibidos y las estimaciones de h y f como obtenidas del CPICH para generar una estimación de la SIR para el canal de control de potencia recibida. Una unidad de mapeo 68 usa la estimada de la SIR para identificar el valor correspondiente de la CER de acuerdo con, por ejemplo, la función de mapeo 20 ilustrada en la figura 5.

5

10

15

20

25

30

45

50

55

60

65

La figura 14 ilustra aún otra realización, que está basada en la transmisión de valores conocidos de bits de TPC sobre el canal de control de potencia, de manera que el circuito de control de potencia 32 puede usar su conocimiento *a priori* de los bits conocidos. Para tales realizaciones, el circuito de estimación 52 puede comprender un circuito de control de conmutación 70 (para controlar el conmutador 71 ilustrado), una unidad de comparación 72 y un estimador 74 de la BER. Durante la operación, el circuito de control 70 usa el valor numérico del intervalo para distinguir entre bits de comando de TPC y bits de referencia conocidos y usa esta información para controlar el conmutador 71, que determina si la unidad de comparación 72 contiene el(los) bit(s) actual como comando o como bits de referencia (por ejemplo, la unidad de comparación 72 se puede configurar para comparar los bits transmitidos (como recibidos) con el valor esperado de esos bits.

Para los bits de referencia, la unidad de comparación 72 determina si el bit de referencia fue recibido con su valor adecuado, y proporciona tal indicación al estimador 74 de la BER, que mantiene una estimación de la tasa de error de bit para el canal de control de potencia recibida. La estimada de la BER se puede usar como la estimada de la CER para el control de potencia del lazo externo por medio del circuito de control de potencia 32.

En una realización de este enfoque, los símbolos de referencia se transmiten sobre el canal de control de potencia en posiciones de comando no TPC. Haciéndolo así, se cambia el esquema normalizado de transmisión de comando definido por el F-DPCH, y además se reduce el número de intervalos de transmisión disponibles en el F-DPCH para controlar la potencia de diferentes estaciones móviles.

Según esto, en la realización, los bits de TPC en intervalos predefinidos de cada trama tienen valores predefinidos, que son conocidos por el receptor 30. Estos bits de TPC predefinidos sirven como bits de referencia, haciendo posible que el circuito de control de potencia 32 estime una BER/CER directamente, basándose en la detección de errores de bits. En tales contextos, un símbolo por trama con bits conocidos puede ser suficiente para una estimación de BER precisa, ya que esa tasa es aproximadamente la tasa a la cual se reciben los indicadores de error de bloque para la estimación de la BER en el control convencional de potencia de lazo externo basado en DPCHs. Sin embargo, se debe observar que se puede usar más de un bit conocido por trama para aumentar la tasa de control del lazo externo y/o para mejorar el proceso de estimación de BER/CER.

Como otro elemento de mejora, los bits conocidos pueden ser transmitidos simétricamente. Es decir, los bits conocidos transmitidos sobre el canal de control de potencia pueden comprender una mezcla equilibrada de comandos UP y DOWN, de forma que la transmisión de comandos de TPC conocidos como bits de referencia no predisponen el control real de potencia arriba o abajo (por ejemplo, la media de bits conocidos diferente de cero). Por ejemplo, se podría usar un número par de símbolos conocidos (intervalos) en cada trama, y hacer la mitad de ellos comandos UP y la otra mitad comandos DOWN.

Tal idea se puede también aplicar en el nivel de bits dejando que cada símbolo de referencia tenga la secuencia de bits (1, -1) o (-1,1). Estos emparejamientos de bits serían, con igual probabilidad, interpretados como comandos UP o como comandos DOWN. El número permitido de símbolos de referencia durante una trama no se limitará, en este caso, a un número par.

En otra realización alternativa más, el dispositivo o sistema que transmite el canal de control de potencia al transceptor 30 puede incluir un bit conocido (referencia) y 1 bit de comando (TPC) en símbolos seleccionados de los símbolos transmitidos. Es decir, para al menos alguno de los símbolos transmitidos en el canal de control de potencia, un bit representa un comando de control de potencia, y un bit representa un bit de referencia conocido *a priori* en el transceptor 30. Con tales realizaciones, debe haber generalmente un número par de intervalos divididos de este modo y un número igual de bits de referencia con los valores 1 y -1.

Así pues, en general, la presente invención como se enseña aquí comprende la generación de la realimentación de control de potencia para una señal recibida de comunicación que no incluye datos codificados de error que por otra parte se podrían usar para determinar una BER/CER como base para controlar la generación de la realimentación de control de potencia. Así, en una o más realizaciones, la realimentación del control de potencia se implementa fijando el objetivo SIR del lazo interno como el valor SIR determinado por una función de mapeo de SIR/CER. Tales realizaciones eliminan efectivamente el control de potencia del lazo externo, porque el lazo interno objetivo se mapea directamente de una CER objetivo deseada. Otras realizaciones usan el control de potencia del lazo interno y del lazo externo, pero estiman la CER para el canal de control de potencia recibida basándose en la determinar una probabilidad de error de recepción para los comandos de control de potencia recibidos y mapear esa probabilidad con una CER estimada de acuerdo con una función de mapeo de probabilidad/CER (una variación de esta realización usa el mapeo de SIR/CER). Sin embargo, en otras realizaciones, el canal de control de potencia incluye bits de referencia y estos se usan para determinar estimadas BER/CER para el canal de control de potencia, las

cuales se usan entonces para ajustar el lazo interno objetivo.

Por consiguiente, se debe comprender que la presente invención es capaz de numerosas variaciones de implementación y no está limitada por la exposición precedente, o por los dibujos que se acompañan. Más bien, la presente invención sólo está limitada por las reivindicaciones siguientes.

#### **REIVINDICACIONES**

1. Un método para generar realimentación de control de potencia de transmisión para un canal de control de potencia, que comprende:

5

la recepción de comandos de control de potencia sobre el canal de control de potencia;

la estimación (120; 102) de la calidad de una señal para el canal de control de potencia;

la determinación de la calidad de una señal objetivo usando una tasa objetivo de error de comando comparando (110,112, 114,116,118) una tasa estimada de error de comando para los comandos de control de potencia recibidos con la tasa objetivo de error de comando, o mapeando (100) la tasa objetivo de error de comando con un valor correspondiente de calidad de la señal de acuerdo con una función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando; y

5

la generación (126,128; 106,108) de realimentación de control de potencia de transmisión para el canal de control de potencia comparando (122,124; 103,104) la calidad estimada de la señal con la calidad objetivo de la señal.

15

20

30

10

- 2. El método de la reivindicación 1, en el que los comandos de control de potencia recibidos comprenden nominalmente símbolos de bits coincidentes, y en el que la tasa estimada de error de comando se estima (110) calculando la probabilidad de un error en la recepción para los comandos de control de potencia recibidos como una función de la detección de bits no coincidentes en los comandos de control de potencia recibidos, y mapeando la probabilidad de error en la recepción con un valor correspondiente de tasa de error de comando de acuerdo con una función de mapeo (42) definida de la probabilidad con la tasa de error de comando.

- **3.** El método de la reivindicación 2, en el que la función de mapeo (42) definida de la probabilidad con la tasa de error de comando comprende una expresión polinómica definida o una tabla de búsqueda de datos.

- **4.** El método de la reivindicación 2, en el que el cálculo de la probabilidad de error en la recepción comprende generar un valor de diferencia para cada comando de control de potencia recibido, en el que el valor de diferencia es distinto de cero si el comando de control de potencia recibido incluye bits no coincidentes, y filtrar los valores de diferencia de acuerdo con un filtro de ponderación exponencial para obtener la probabilidad de error en la recepción.

- **5.** El método de la reivindicación 2, en el que la detección de bits no coincidentes en los comandos de control de potencia recibidos comprende detectar errores de bits por hardware.

- 35 6. El método de la reivindicación 2, en el que la detección de los bits no coincidentes en los comandos de control de potencia recibidos comprende detectar errores de bits por software.

- 7. El método de la reivindicación 6, en el que mapear la probabilidad de error en la recepción con un valor correspondiente de la tasa de error de comando de acuerdo con una función de mapeo definida de la probabilidad con la tasa de error de comando comprende estimar un error relativo de bit por software y mapear el error relativo de bits por software con una tasa de error de comando.

- **8.** El método de la reivindicación 7, que comprende además cuantificar una distribución del error relativo de bits por software usando una medida de varianza, de manera que mapear el error relativo de bits por software con una tasa de error de comando comprende mapear un valor de error relativo cuantificado de bits por software con una tasa de error de comando.

- **9.** El método de la reivindicación 1, en el que al menos alguno de los comandos de control de potencia incluye bits de referencia, y en el que la estimación de una tasa de error de comando comprende la detección de errores de recepción de los bits de referencia.

- **10.** El método de la reivindicación 1, que comprende además recibir símbolos de referencia sobre el canal de control de potencia, y en el que la tasa estimada de error de comando se estima (110) detectando errores de recepción de los símbolos de referencia.

55

45

50

- **11.** El método de la reivindicación 1, en el que la tasa estimada de error de comando se estima (110) mapeando la calidad estimada de la señal con un valor correspondiente de la tasa de error de comando de acuerdo con una función de mapeo (20) definida de la calidad de la señal recibida con la tasa de error de comando.

- 60 12. El método de la reivindicación 1, en el que generar (126,128:106,108) la realimentación del control de potencia de transmisión comprende generar comandos de control de control de potencia de transmisión de la realimentación como valores de indicación por arriba o por debajo basándose en determinar si la calidad estimada de la señal está por debajo o por encima de la calidad objetivo de la señal.

- **13.** El método de la reivindicación 1, en el que estimar (120; 102) la calidad de una señal para el canal de control de potencia comprende estimar una relación señal/interferencia para el canal de control de potencia, y en el que la calidad objetivo de la señal comprende una relación de señal objetivo/interferencia.

- 5 14. El método de la reivindicación 1, en el que estimar (120; 102) la calidad de una señal para el canal de control de potencia comprende deducir una estimación de la calidad de la señal para el canal de control de potencia basándose en un canal piloto común recibido.

- 15. El método de la reivindicación 14, en el que deducir una estimación de calidad de la señal para el canal de control de potencia basándose en una señal recibida de canal piloto común comprende calcular un desplazamiento de ganancia entre el control de potencia y los canales piloto comunes.

- **16.** El método de la reivindicación 15, en el que calcular un desplazamiento de la ganancia entre el control de potencia y los canales piloto comunes comprende calcular el desplazamiento de la ganancia basándose en las salidas del receptor.

- 17. El método de la reivindicación 1, en el que el canal de control de potencia comprende un Canal Físico Dedicado Fraccional (F-DPCH) en una red de comunicación de Acceso Múltiple por División de Código de Banda Ancha (W-CDMA).

- 18. El método de la reivindicación 1, en el que se determina la calidad objetivo de una señal usando una tasa objetivo de error de comando mapeando (100) la tasa objetivo de error de comando con un valor correspondiente de calidad de la señal de acuerdo con una función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando; el método comprende además determinar el valor correspondiente de calidad de la señal usando la tasa objetivo de error de comando para acceder a una tabla de búsqueda de datos que incorpora la función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando.

- 19. El método de la reivindicación 1, en el que se determina la calidad objetivo de una señal usando una tasa objetivo de error de comando mapeando (100) la tasa objetivo de error de comando con un valor correspondiente de calidad de la señal de acuerdo con una función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando; el método comprende además determinar el valor correspondiente de calidad de la señal usando la tasa objetivo de error de comando como un valor de entrada a una función polinómica que incorpora la función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando.

- **20.** Un circuito (32) de control de potencia para ser usado en un dispositivo (30) o sistema de comunicación inalámbrica, comprendiendo dicho circuito de control de potencia uno o más circuitos de tratamiento (50,52, 54,56; 36,38) configurado para:

- recibir comandos de control de potencia trasmitidos a un dispositivo o sistema de comunicación inalámbrica sobre un canal de control de potencia;

- estimar la calidad de una señal para el canal de control de potencia;

15

20

25

30

- determinar la calidad objetivo de una señal usando una tasa objetivo de error de comando comparando una tasa estimada de error de comando para los comando de control de potencia recibidos con una tasa objetivo de error de comando, o

- mapeando la tasa objetivo de error de comando con un valor correspondiente de calidad de la señal de acuerdo con una función de mapeo (20) definida de la calidad de la señal con la tasa de error de comando; y generar realimentación de control de potencia del transmisor para el canal de control de potencia comparando la calidad estimada de la señal con la calidad objetivo de la señal.

- 21. El circuito de control de potencia de la reivindicación 20, en el que el uno o más circuitos de tratamiento comprenden un circuito (50) de estimación de la calidad de la señal configurado para estimar la calidad de la señal para el canal de control de potencia, un circuito (52) de estimación de la tasa de error de comando configurado para estimar la tasa de error de comando para los comando de control de potencia recibidos, un circuito (54) de control de potencia del lazo externo, configurado para ajustar la calidad objetivo de la señal, y un circuito (56) de control de potencia del lazo interno, configurado para generar la realimentación de control de potencia del transmisor.

- 22. El circuito de control de potencia de la reivindicación 20, en el que los comandos de control de potencia recibidos comprenden nominalmente símbolos de bits coincidentes, y en el que el circuito (52) de estimación de la tasa de error de comando está configurado para calcular una probabilidad de error en la recepción para los comandos de control de potencia recibidos, como una función de detección de bits no coincidentes en los comandos de control de potencia recibidos, y estimar la tasa de error de comando mapeando la probabilidad de error en la recepción con un valor correspondiente de la tasa de error de comando de acuerdo con una función de mapeo (42) definida de la probabilidad con la tasa de error de comando.

- 65 23. El circuito de control de potencia de la reivindicación 22, en el que el circuito (52) de estimación de la tasa de

error de comando está configurado para implementar la función de mapeo (42) definida de la probabilidad con la tasa de error de comando como una expresión definida polinómica o como una tabla de búsqueda de datos.

- 24. El circuito de control de potencia de la reivindicación 22, en el que el circuito (52) de estimación de la tasa de error de comando está configurado para calcular la probabilidad de error en la recepción generando un valor de diferencia para cada comando de control de potencia recibido, en el que el valor de diferencia es distinto de cero si el comando de control de potencia recibido incluye bits no coincidentes, y filtrando los valores de diferencia de acuerdo con un filtro de ponderación exponencial para obtener la probabilidad de error en la recepción.

- 25. El circuito de control de potencia de la reivindicación 22, en el que el circuito (52) de estimación de la tasa de error de comando está configurado para detectar bits no coincidentes en los comandos de control de potencia recibidos basándose en la detección de errores de bits por hardware.

- **26.** El circuito de control de potencia de la reivindicación 22, en el que el circuito (52) de estimación de la tasa de error de comando está configurado para detectar bits no coincidentes en los comandos de control de potencia recibidos basándose en la detección de errores de bits por software.

- 27. El circuito de control de potencia de la reivindicación 26, en el que el circuito (52) de estimación de la tasa de error de comando está configurado para mapear la probabilidad de error en la recepción con un valor correspondiente de la tasa de error de comando de acuerdo con una función definida de mapeo (42) de la probabilidad con la tasa de error de comando basándose en la estimación de un error relativo de bits por software y mapeando el error relativo de bits por software con una tasa de error de comando.

- 28. El circuito de control de potencia de la reivindicación 26, en el que el circuito (52) de estimación de la tasa de error de comando está configurado además para cuantificar una distribución del error relativo de bits por software usando una medida de varianza, de forma que mapear el error relativo de bit por software con una tasa de error de comando comprende mapear un valor cuantificado relativo de error de bit por software con una tasa de error de comando.

- 29. El circuito de control de potencia de la reivindicación 21, en el que al menos alguno de los comandos de control de potencia incluye bits de referencia, y en el que el circuito (52) de estimación de la tasa de error de comando está configurado para estimar la tasa de error de comando como una función de detectar errores de recepción de los bits de referencia.

- 35. El circuito de control de potencia de la reivindicación 20, en el que los símbolos de referencia se reciben sobre el canal de control de potencia, y en el que el circuito (32) de control de potencia está configurado para estimar la tasa de error de comando como una función de detectar errores de recepción de los símbolos de referencia.

- **31.** El circuito de control de potencia de la reivindicación 20, en el que circuito (32) de control de potencia está configurado para estimar la tasa de error de comando mapeando la calidad estimada de la señal con un valor correspondiente de la tasa de error de comando de acuerdo con una función de mapeo definida (20) de la calidad de la señal con la tasa de error de comando.

- **32.** El circuito de control de potencia de la reivindicación 20, en el que el circuito (32) de control de potencia está configurado para generar la realimentación de control de potencia del transmisor como valores indicativos por arriba o por abajo basándose en determinar si la calidad estimada de la señal está por abajo o por arriba de la calidad objetivo de la señal.

- **33.** El circuito de control de potencia de la reivindicación 20, en el que el circuito (32) de control de potencia está configurado para estimar la calidad de la señal como una relación señal/interferencia para el canal de control de potencia, y en el que la calidad objetivo de la señal comprende una relación objetivo señal/interferencia.

- 34. El circuito de control de potencia de la reivindicación 20, que comprende además un circuito de mapeo (34) configurado para determinar el valor correspondiente de calidad de la señal usando la tasa objetivo de error de comando para acceder a una tabla de búsqueda de datos que incorpora la función de mapeo definida (20) de la calidad de la señal con la tasa de error de comando.

- **35.** El circuito de control de potencia de la reivindicación 20, que comprende además un circuito de mapeo (34) configurado para determinar el valor correspondiente de calidad de la señal usando la tasa objetivo de error de comando como un valor de entrada a una función polinómica que incorpora la función de mapeo definida (20) de la calidad de la señal con la tasa de error de comando.

- **36.** Un dispositivo de comunicación inalámbrica (30) que comprende un circuito (32) de control de potencia de acuerdo con cualquiera de las reivindicaciones 20-35.

65

**37.** Un medio interpretable por ordenador que almacena un programa de ordenador para generar realimentación de control de potencia del transmisor para un canal de control de potencia, comprendiendo el programa de ordenador instrucciones de programa para implementar el método de acuerdo con cualquiera de las reivindicaciones 1-19.