# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 394 262

51 Int. Cl.:

H04L 7/10 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

96 Fecha de presentación y número de la solicitud europea: 27.10.2009 E 09824721 (6)

(97) Fecha y número de publicación de la solicitud europea: 28.07.2010 EP 2211524

(54) Título: Dispositivo de transmisor, dispositivo de receptor y sistema de comunicación

(30) Prioridad:

05.11.2008 JP 2008284519

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 30.01.2013

(73) Titular/es:

THINE ELECTRONICS, INC. (100.0%) 9-1 Kanda-mitoshiro-cho Chiyoda-kuTokyo101-0053, JP

(72) Inventor/es:

AKITA HIRONOBU; ISHIZONE, YOHEI; OZAWA, SEIICHI Y MIURA, SATOSHI

(74) Agente/Representante:

PÉREZ BARQUÍN, Eliana

## **DESCRIPCIÓN**

Dispositivo de transmisor, dispositivo de receptor y sistema de comunicación

#### 5 Campo técnico

La presente invención se refiere a un dispositivo de transmisión, un dispositivo de recepción y un sistema de comunicación que incluye los dispositivos anteriores.

#### 10 Técnica anterior

Con anterioridad, se conoce la tecnología de recuperación de datos de reloj (CDR: Recuperación de Datos de Reloj). Con esta tecnología de CDR, en un sistema en el que se proporciona una línea de señal serie unidireccional de alta velocidad y una línea de señal de control de baja velocidad entre el dispositivo de transmisión y el dispositivo de recepción, una señal de datos serie incluida en una señal de reloj es enviada desde el dispositivo de transmisión a través de la línea de señal serie de alta velocidad, y el dispositivo de recepción restablece los datos y restaura la señal de reloj en base a la señal de datos serie. A continuación, el sistema reproduce la señal recuperada (señal de reloj de recuperación), compara la fase del borde de los datos y la señal de reloj para ajustar la fase, y adquiere con ello datos seguros.

20

25

30

15

Mientras tanto, si la tasa de bits de la señal de datos serie que es enviada desde el dispositivo de transmisión cambia, se reproduce una señal de reloj anormal en el dispositivo de recepción, y se pueden adquirir datos erróneos. Con el fin de subsanar el problema anterior, el dispositivo de recepción implementa un procesamiento para confirmar la tasa de bits cambiada que ha sido enviada desde el dispositivo de transmisión, y el dispositivo de transmisión envía una señal de datos serie que incluye la tasa de bits cambiada hasta el dispositivo de recepción después del procesamiento anterior.

Con el fin de implementar el procesamiento anterior, es necesario transferir un comando tal como un aviso de cambio de tasa de bits o similar entre el dispositivo de transmisión y el dispositivo de recepción. De ese modo, por ejemplo, el puerto de visualización descrito en el documento 1 no patente, está dotado de una línea de señal serie de alta velocidad, y de una línea de señal de control de baja velocidad capacitadas para una comunicación interactiva. El puerto de visualización descrito en el citado documento 1 no patente, está capacitado para transferir un comando para confirmación de la tasa de bits por la línea de señal de control de comunicación interactiva.

35 El documento patente 1 divulga un procedimiento de recuperación de señal de reloj y un aparato de transmisión/recepción asociado para una señal de video digital. El aparato de transmisión divulgado introduce un código de reloj en la señal de video digital que indica la tasa de datos de la señal de reloj. El código de reloj es utilizado por el aparato de recepción para generar una señal de reloj en base a la señal de reloj de referencia.

## 40 DOCUMENTOS DE LA TÉCNICA ANTERIOR

## Documento no patente

Documento no patente 1: "Estándar de Puerto de Visualización VESA", Fig. 1-1, Fig. 3-10, [online], 11 Enero de 2008, Video Electronics Standards Association, [Buscado el 4 de noviembre de 2008], Internet <URL: https://fs16.formsite.com/VESA/form608559305/secure index html>.

## Documento patente

50 Documento patente 1: EP 1478119 A2.

#### Descripción de la invención

# Problemas a ser resueltos por la invención

55

60

Sin embargo, con la tecnología convencional citada anteriormente, se requiere un circuito de control que permita la comunicación interactiva y, además de que el tamaño del circuito resulta incrementado, existe el problema de que se debe establecer un protocolo complicado con el fin de impedir que las señales (comandos) enviadas desde el dispositivo de transmisión y el dispositivo de recepción colisionen en la línea de transmisión. Mientras tanto, aunque existe también una configuración de provisión por separado de dos líneas de señal de control para las direcciones respectivas, en especial desde el dispositivo de transmisión hasta el dispositivo de recepción hasta el dispositivo de transmisión, el incremento del número de líneas de señales de control es indeseable desde la perspectiva del incremento de costes y de consumo de potencia.

65 La presente invención ha sido ideada con el fin de subsanar los problemas anteriores. Así, un objeto de esta invención consiste en proporcionar un dispositivo de transmisión, un dispositivo de recepción y un sistema de

comunicación que tengan una configuración simple y que estén capacitados para ejecutar de forma fiable la confirmación de la tasa de bits cambiada.

#### Medios para resolver el problema

5

10

15

20

25

45

50

55

60

El sistema de comunicación de la presente invención está caracterizado porque comprende el dispositivo de transmisión y el dispositivo de recepción que siguen. Específicamente, el dispositivo de transmisión de la presente invención comprende: una unidad de transmisión de señal para enviar una señal de datos serie incorporada en una señal de reloj hasta un dispositivo de recepción; una unidad de comando de transmisión de aviso de cambio para enviar desde su salida hasta la unidad de transmisión de señal, una señal de control para su envío por la unidad de transmisión de señal hasta el dispositivo de recepción de una señal de datos serie que ha sido establecida como un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj cuando se cambia una tasa de bits de una señal de datos serie que va a ser enviada por la unidad de transmisión de señal; y una unidad de creación de datos de entrenamiento para crear datos de entrenamiento para confirmar la tasa de bits cambiada en el dispositivo de recepción después de que la señal de control ha sido presentada a la salida de la unidad de comando de transmisión de aviso de cambio, y provocar que la unidad de transmisión de señal envíe los datos de entrenamiento al dispositivo de recepción.

Adicionalmente, el dispositivo de recepción de la presente invención comprende: una unidad de recepción de señal para recibir una señal de datos serie incluida en una señal de reloj procedente de un dispositivo de transmisión, una unidad de determinación de valor constante de señal recibida para determinar si la señal de datos serie recibida por la unidad de recepción de señal es un valor constante a través de un período de un múltiplo constante de un ciclo de reloj, siendo dicho valor constante indicativo de un cambio en una tasa de bits de la señal de datos serie; y una unidad de recuperación de señal de reloj para recibir datos de entrenamiento que van a ser usados para confirmar la tasa de bits cambiada procedente del dispositivo de transmisión y confirmar la tasa de bits cambiada cuando la unidad de determinación de valor constante de señal recibida determine que la señal de datos serie es un valor constante.

El sistema de comunicación que comprende el dispositivo de transmisión y el dispositivo de recepción mencionados 30 anteriormente envía, al dispositivo de recepción, una señal de datos serie que ha sido establecida como un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj cuando va a ser cambiada una tasa de bits de una señal de datos serie que va a ser enviada desde la unidad de transmisión de señal. El dispositivo de recepción que recibió la señal de datos serie recibe los datos de entrenamiento procedentes del dispositivo de transmisión si se determina que la señal de datos serie es un valor constante a través de un período 35 de un múltiplo constante de un ciclo de la señal de reloj, y procede al procesamiento de confirmación de la tasa de bits cambiada. En consecuencia, el dispositivo de recepción está capacitado para reconocer el cambio de la tasa de bits mediante la recepción de la señal de datos serie y proceder a su procesamiento para confirmar la tasa de bits cambiada sin tener que recibir una señal desde el dispositivo de transmisión que indique que la tasa de bits va a ser cambiada. De ese modo, la confirmación de la tasa de bits cambiada puede ser ejecutada de forma fiable con una 40 simple configuración convencional sin tener que incrementar la línea de señal de control o habilitar una comunicación interactiva.

Además, el sistema de comunicación de la presente invención está caracterizado porque comprende el dispositivo de transmisión y el dispositivo de recepción que siguen. Específicamente, el dispositivo de transmisión de la presente invención comprende además una unidad de determinación de inicio de entrenamiento para recibir, desde el dispositivo de recepción, y disponer a la entrada de una señal de petición de inicio de entrenamiento indicativa de que se requieren desde el dispositivo de recepción los datos de entrenamiento para confirmar la tasa de bits cambiada, en el que, cuando la unidad de determinación de inicio de entrenamiento recibe la señal de petición de inicio de entrenamiento procedente del dispositivo de recepción, la unidad de creación de datos de entrenamiento provoca que la unidad de transmisión de señal envíe los datos de entrenamiento al dispositivo de recepción.

Adicionalmente, el dispositivo de recepción de la presente invención comprende además una unidad de petición de señal de inicio de entrenamiento para enviar una señal de petición de inicio de entrenamiento para solicitar datos de entrenamiento que van a ser usados para confirmar la tasa de bits cambiada y solicitar al dispositivo de transmisión los datos de entrenamiento cuando la unidad de determinación de valor constante de señal recibida determine que la señal de datos serie es un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloi.

Con el sistema de comunicación que comprende el dispositivo de transmisión y el dispositivo de recepción descritos anteriormente, el dispositivo de recepción envía una señal de petición de inicio de entrenamiento al dispositivo tras la determinación de que la señal de datos serie es un valor constante; es decir, tras la confirmación de que la tasa de bits ha sido cambiada, y el dispositivo de transmisión recibe la señal de petición de inicio de entrenamiento y envía a continuación datos de entrenamiento al dispositivo de recepción. En consecuencia, el dispositivo de transmisión enviará los datos de entrenamiento al dispositivo de recepción después de que el dispositivo de recepción reconozca de forma fiable el cambio de la tasa de bits. En consecuencia, es posible impedir que el dispositivo de transmisión envíe erróneamente los datos de entrenamiento o los datos de la tasa de bits cambiada con anterioridad a que el

dispositivo de recepción reconozca el cambio de la tasa de bits.

Además, el sistema de comunicación de la presente invención está caracterizado porque comprende el dispositivo de transmisión y el dispositivo de recepción que siguen. Específicamente, cuando la unidad de determinación de inicio de entrenamiento recibe una señal de fin de entrenamiento indicativa de que la confirmación de la tasa de bits cambiada está completa desde el dispositivo de recepción, la unidad de transmisión de señal incluida en el dispositivo de transmisión de la presente invención envía una señal de datos serie de la tasa de bits cambiada al dispositivo de recepción.

Además, la unidad de petición de señal de inicio de entrenamiento incluida en el dispositivo de recepción de la presente invención introduce una señal de aviso final indicativa de que la confirmación de la tasa de bits cambiada presente en la salida de la unidad de recuperación de reloj está completa, envía una señal de fin de entrenamiento al dispositivo de transmisión de acuerdo con la señal de aviso final, y notifica con ello al dispositivo de transmisión de que la confirmación de la tasa de bits cambiada está completa.

Con el sistema de comunicación que comprende el dispositivo de transmisión y el dispositivo de recepción que anteceden, el dispositivo de recepción envía una señal de fin de entrenamiento al dispositivo de transmisión que indica que la confirmación de la tasa de bits está completa, y el dispositivo de transmisión envía la señal de datos serie de la tasa de bits cambiada después de la recepción de la señal de fin de entrenamiento que antecede. Por consiguiente, es posible impedir que el dispositivo de transmisión envíe erróneamente una señal de datos serie de la tasa de bits cambiada al dispositivo de recepción con anterioridad a la confirmación de que la tasa de bits está completa.

Además, el dispositivo de transmisión de la presente invención comprende adicionalmente una unidad de determinación de tasa de bits para presentar a la entrada una señal de datos paralelo y determinar si existe algún cambio en la tasa de bits de la señal de datos paralelo, y presentar a la salida información de cambio de tasa de bits para la unidad de comando de transmisión de aviso de cambio tras la determinación de que la tasa de bits de la señal de datos paralelo ha cambiado, en el que, la unidad de comando de transmisión de aviso de cambio, tras la recepción de la información de cambio de tasa de bits procedente de la unidad de determinación de tasa de bits, presenta a la salida la señal de control para la unidad de transmisión de señal.

Además, con el dispositivo de transmisión de la presente invención, la unidad de determinación de tasa de bits puede ser configurada a modo de circuito de fase sincronizada (PLL). En el caso que antecede, se utiliza con preferencia una señal de sincronización del circuito de sincronización de fase como información de cambio de tasa de bits.

## Efecto de la invención

15

20

35

45

55

De acuerdo con la presente invención, la confirmación de la tasa de bits cambiada puede ser ejecutada de manera 40 fiable con una configuración simple.

## Breve descripción de los dibujos

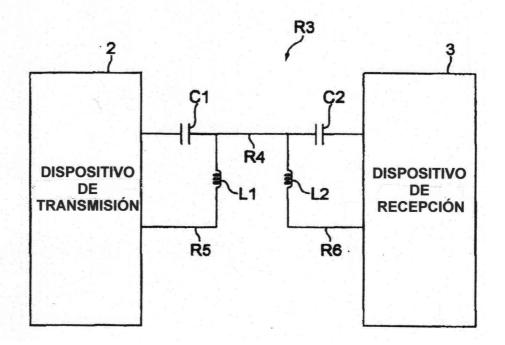

La figura 1 es un diagrama de configuración del sistema de comunicación de acuerdo con la presente realización.

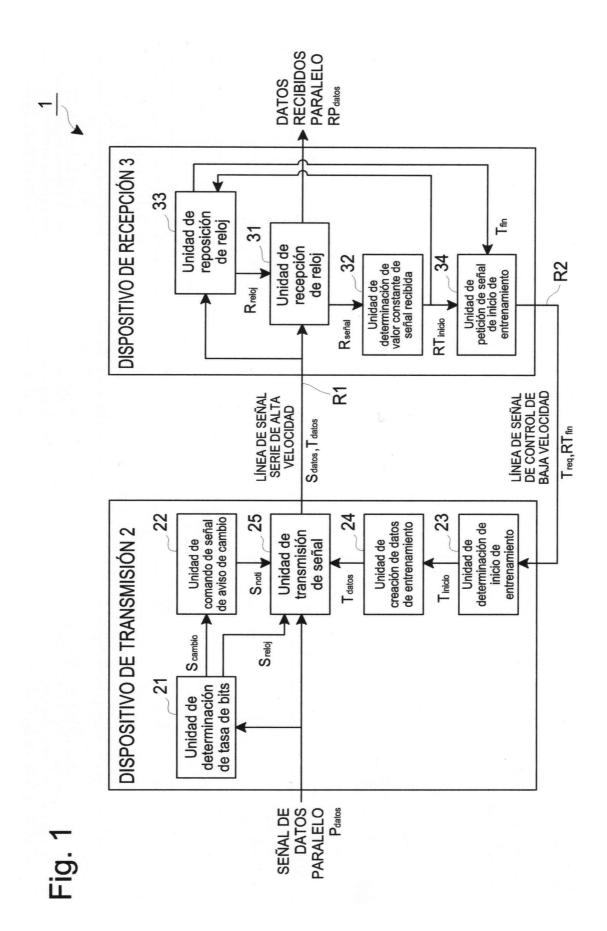

La figura 2 es un diagrama de tiempos que muestra un ejemplo de la restauración de la señal de datos y de la señal de reloj.

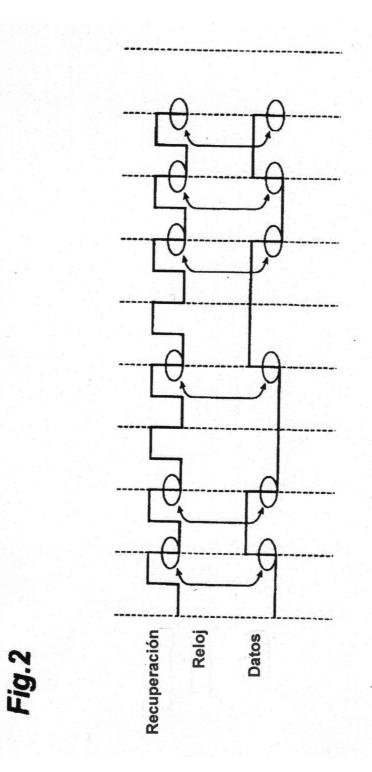

La figura 3 es un diagrama secuencial que muestra el procesamiento que va a ser realizado por el sistema de 50 comunicación.

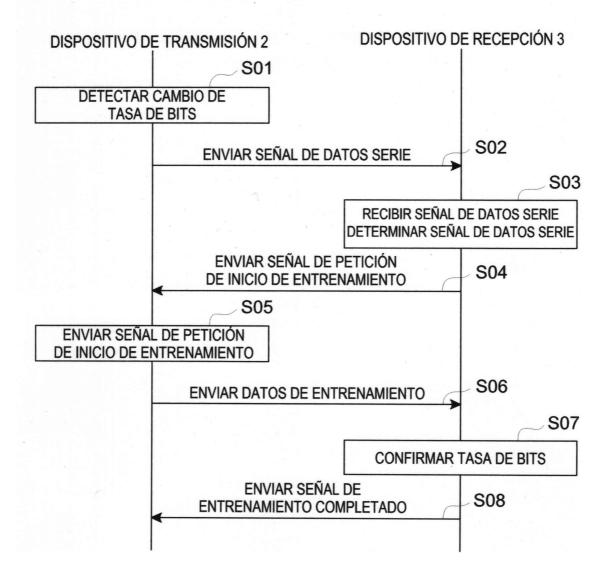

La figura 4 es un diagrama que muestra la configuración de la línea de señal de acuerdo con un ejemplo modificado.

# Mejor modo de llevar a cabo la invención

El mejor modo de llevar a cabo la presente invención va a ser explicado ahora con referencia a los dibujos anexos. Eventualmente, los mismos componentes durante la explicación de los dibujos están indicados con los mismos números de referencia, y se omite la explicación redundante de los mismos.

La figura 1 es un diagrama de configuración del sistema de comunicación de acuerdo con la presente realización. El sistema 1 de comunicación mostrado en la figura comprende un dispositivo 2 de transmisión y un dispositivo 3 de recepción. El dispositivo 2 de transmisión y el dispositivo 3 de recepción están conectados por medio de una línea R1 de señal serie de alta velocidad, y una línea R2 de señal de control de velocidad más baja que la línea R1 de señal serie de alta velocidad. La línea R1 de señal serie de alta velocidad es una línea de señal para transmitir señales enviadas desde el dispositivo 2 de transmisión hasta el dispositivo 3 de recepción. La línea R2 de señal de control de baja velocidad es una línea de señal para la transmisión de señales enviadas desde el dispositivo 3 de

recepción hasta el dispositivo 2 de transmisión.

10

15

45

50

55

60

65

El dispositivo 2 de transmisión comprende una unidad 21 de determinación de tasa de bits, una unidad 22 de comando de señal de aviso de cambio, una unidad 23 de determinación de inicio de entrenamiento, una unidad 24 de creación de datos de entrenamiento, y una unidad 25 de transmisión de señal. El dispositivo 2 de transmisión es un dispositivo para enviar, por ejemplo, datos de imagen (video) hasta el dispositivo 3 de recepción.

La unidad 21 de determinación de tasa de bits posee un suministro de entrada de una señal P<sub>datos</sub> de datos paralelo que ha sido la entrada en el dispositivo 2 de transmisión para determinar la tasa de bits de la señal P<sub>datos</sub> de datos paralelo, y presenta a la salida la información S<sub>reloj</sub> de tasa de bits relacionada con la tasa de bits para la unidad 25 de transmisión de señal. La unidad 21 de determinación de tasa de bits determina si existe algún cambio en la tasa de bits de la señal P<sub>datos</sub> de datos paralelo y, tras determinar que la tasa de bits de la señal P<sub>datos</sub> de datos paralelo ha cambiado, presenta a la salida la información S<sub>cambio</sub> de cambio de tasa de bits para la unidad 22 de comando de señal de aviso de cambio. La señal P<sub>datos</sub> de datos paralelo se suministra como entrada al dispositivo 2 de transmisión a través de una línea de señal (bus paralelo) que está configurada a partir de una pluralidad de líneas de señal, y los datos que van a ser enviados por una única línea de señal no se limitan a 1 bit por reloj, pudiendo ser una pluralidad de bits por reloj.

La unidad 22 de comando de señal de aviso de cambio es alimentada a la entrada con la información S<sub>cambio</sub> de cambio de tasa de bits que fue presentada a la salida de la unidad 21 de determinación de tasa de bits, y presenta a la salida para la unidad 25 de transmisión de señal una señal S<sub>noti</sub> de control para controlar la señal S<sub>datos</sub> de datos serie que va a ser enviada al dispositivo 3 de recepción de modo que sea un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj.

La unidad 23 de determinación de inicio de entrenamiento que recibe desde el dispositivo 3 de recepción, y que dispone a la entrada de, una señal T<sub>req</sub> de petición de inicio de entrenamiento que fue enviada a través de la línea R2 de señal de control, determina que el entrenamiento ha de ser iniciado de acuerdo con la señal T<sub>req</sub> de petición de inicio de entrenamiento, y presenta a la salida la señal T<sub>inicio</sub> de inicio de entrenamiento para la unidad 24 de creación de datos de entrenamiento. La unidad 23 de determinación de inicio de entrenamiento recibe desde el dispositivo 3 de recepción, y dispone a su entrada de, una señal RT<sub>fin</sub> de fin de entrenamiento que fue enviada a través de la línea R2 de señal de control, y presenta a la salida la señal RT<sub>fin</sub> de fin de entrenamiento para la unidad 25 de transmisión de señal a través de la unidad 24 de creación de datos de entrenamiento. El entrenamiento va a ser descrito en lo que sigue.

La unidad 24 de creación de datos de entrenamiento posee a la entrada la señal T<sub>inicio</sub> de inicio de entrenamiento que fue presentada a la salida de la unidad 23 de determinación de inicio de entrenamiento, y presenta a la salida datos T<sub>datos</sub> de entrenamiento que van a ser usados en el entrenamiento por la unidad 25 de transmisión de señal de acuerdo con la señal T<sub>inicio</sub> de inicio de entrenamiento. Los datos T<sub>datos</sub> de entrenamiento que van a ser usados en el entrenamiento son, de manera más específica, una señal correspondiente a la tasa de bits, y son datos (patrón de entrenamiento) en los que, por ejemplo, el "1" y el "0" están en serie, tal como "1010...".

La unidad 25 de transmisión de señal que posee a la entrada una señal  $P_{datos}$  de datos paralelo que fue presentada a la entrada en el dispositivo 2 de transmisión, convierte la señal  $P_{datos}$  de datos paralelo en una señal  $S_{datos}$  de datos serie de acuerdo con la información  $S_{reloj}$  de tasa de bits que fue presentada a la salida de la unidad 21 de determinación de tasa de bits, y la envía al dispositivo 3 de recepción a través de la línea R1 de señal serie de alta velocidad. Además, la unidad 25 de transmisión de señal posee a la entrada una señal  $S_{noti}$  de control que fue presentada a la salida de la unidad 22 de comando de señal de aviso de cambio, crea una señal  $S_{datos}$  de datos serie para establecer un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj de acuerdo con la señal  $S_{noti}$  de control, y envía ésta al dispositivo 3 de recepción a través de la línea R1 de señal serie de alta velocidad. Específicamente, la unidad 25 de transmisión de señal establece la señal  $S_{datos}$  de datos serie de modo que será de nivel bajo a través de un múltiplo constante de un ciclo de la señal de reloj. El período del múltiplo constante se establece adecuadamente de acuerdo con el sistema que va a ser configurado y, por ejemplo, si el período máximo del nivel bajo de la señal de datos serie se establece en 6 ciclos de la señal de reloj, se establece en aproximadamente varias veces dichos 6 ciclos.

Además, la unidad 25 de transmisión de señal interrumpe la transmisión de la señal  $S_{datos}$  de datos serie presentando a la entrada los datos  $T_{datos}$  de entrenamiento que fueron presentados a la salida de la unidad 24 de creación de datos de entrenamiento, y envía los datos  $R_{datos}$  de entrenamiento al dispositivo 3 de recepción a través de la línea R1 de señal serie de alta velocidad. Además, cuando la unidad 25 de transmisión de señal posee a la entrada, a través de la unidad 24 de creación de datos de entrenamiento, la señal  $RT_{fin}$  de final de entrenamiento que fue presentada a la salida de la unidad 23 de determinación de inicio de entrenamiento, interrumpe la transmisión de los datos  $T_{datos}$  de entrenamiento y resume la transmisión de la señal  $S_{datos}$  de datos serie.

El dispositivo 3 de recepción se configura con la inclusión de una unidad 31 de recepción de señal, una unidad 32 de determinación de valor constante de la señal recibida, una unidad 33 de recuperación de señal de reloj, y una unidad 34 de petición de señal de inicio de entrenamiento. La unidad 3 de recepción recibe datos de imagen procedentes de

la unidad 2 de transmisión y presenta a su salida tales datos de imagen. La unidad 3 de recepción configura una parte de, por ejemplo, un panel LCD (Visualizador de Cristal Líquido).

La unidad 31 de recepción de señal recibe y posee en su entrada, la señal S<sub>datos</sub> de datos serie que fue enviada desde el dispositivo 2 de transmisión a través de la línea R1 de señal serie de alta velocidad, y crea los datos RP<sub>datos</sub> paralelo recibidos tras la adquisición, desde la señal S<sub>datos</sub> de datos serie, de datos basados en la señal de reloj R<sub>reloj</sub> de recuperación (descrita más adelante) que está presente en la salida de la unidad 33 de recuperación de señal de reloj. Específicamente, la unidad 31 de recepción de señal adquiere datos precisos procedentes de la señal S<sub>datos</sub> de datos serie utilizando una señal de reloj indicada mediante la señal de reloj de recuperación R<sub>reloj</sub>, y crea los datos adquiridos y la señal de reloj según los datos RP<sub>datos</sub> paralelo recibidos. Los datos RP<sub>datos</sub> paralelo recibidos están presentes a la salida, por ejemplo, como datos de imagen para la unidad de visualización de un LCD. Además, la unidad 31 de recepción de señal presenta en su salida la señal S<sub>datos</sub> de datos serie de entrada como señal R<sub>señal</sub> de determinación para la unidad 32 de determinación de valor constante de la señal recibida.

10

25

30

35

40

45

50

La unidad 32 de determinación de valor constante de señal recibida posee a la entrada la señal R<sub>señal</sub> de determinación que fue presentada a la salida de la unidad 31 de recepción de señal, y determina, en base a la señal R<sub>señal</sub> de determinación, si la señal S<sub>datos</sub> de datos serie es un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj. Si la unidad 32 de determinación de valor constante de la señal recibida determina que la señal S<sub>datos</sub> de datos serie es un valor constante, presenta en la salida la señal RT<sub>inicio</sub> de inicio de entrenamiento para la unidad 33 de recuperación de señal de reloj y para la unidad 34 de petición de señal de inicio de entrenamiento.

La unidad 33 de recuperación de la señal de reloj recibe desde el dispositivo 2 de transmisión, y posee en la entrada, la señal S<sub>datos</sub> de datos serie incluida en una señal de reloj que fue enviada a través de la línea R1 de señal serie de alta velocidad, y restablece y reproduce la señal de reloj R<sub>reloj</sub> de recuperación a partir de la señal S<sub>datos</sub> de datos serie de entrada. Esto va a ser explicado ahora con detalle con referencia a la figura 2. La figura 2 es un diagrama de tiempos que muestra un ejemplo de la restauración de los datos y la señal de reloj. Según se muestra en la figura 2, la unidad 34 de recuperación de señal de reloj reproduce la misma frecuencia de reloj que la tasa de bits de datos mediante comparación de la fase del borde de la señal de reloj de recuperación restablecida (indicada con flechas en esta figura) y del borde de los datos, y ajusta con ello la fase. La señal de reloj de recuperación R<sub>reloj</sub> se utiliza como señal de reloj de muestreo puesto que crea una señal RP<sub>datos</sub> paralelo recibida a partir de la señal S<sub>datos</sub> de datos serie en la unidad 31 de recepción de señal.

Además, si una señal RT<sub>inicio</sub> de inicio de entrenamiento se encuentra presente a la salida de la unidad 32 de determinación de valor constante de la señal recibida, la unidad 33 de recuperación de señal de reloj posee a la entrada la señal RT<sub>inicio</sub> de inicio de entrenamiento y conmuta al modo de entrenamiento. La unidad 33 de recuperación de señal de reloj recibe desde el dispositivo 2 de transmisión y posee en su entrada, los datos T<sub>datos</sub> de entrenamiento que fueron enviados a través de la línea R1 de señal serie de alta velocidad, e implementa el entrenamiento en base a los datos T<sub>datos</sub> de entrenamiento. El entrenamiento se refiere al proceso de aprendizaje para tratar la señal S<sub>datos</sub> de datos serie de la tasa de bits cambiada mediante reconocimiento del patrón de entrenamiento (por ejemplo, "1010...") que está representado en los datos T<sub>datos</sub> de entrenamiento. Cuando el entrenamiento está completo, la unidad 33 de recuperación de señal de reloj presenta a la salida una señal T<sub>fin</sub> de aviso de finalización, que indica que el entrenamiento se ha completado a la unidad 34 de petición de señal de inicio de entrenamiento.

La unidad 34 de petición de señal de inicio de entrenamiento dispone a la entrada de la señal RT<sub>inicio</sub> de señal de inicio de entrenamiento que fue presentada a la salida de la unidad 32 de determinación de valor constante de la señal recibida, y dispone en su salida la señal T<sub>req</sub> de petición de inicio de entrenamiento para el dispositivo 2 de transmisión a través de la línea R2 de señal de control de acuerdo con la señal RT<sub>inicio</sub> de inicio de entrenamiento. Además, la unidad 34 de petición de señal de inicio de entrenamiento posee en su entrada la señal T<sub>fin</sub> de aviso de finalización que fue presentada a la salida de la unidad 33 de recuperación de señal de reloj, y envía la señal RT<sub>fin</sub> de final de entrenamiento al dispositivo 2 de transmisión a través de la línea R2 de señal de control de acuerdo con la señal T<sub>fin</sub> de aviso de finalización.

Ahora se va a explicar el procesamiento que va a ser realizado por el sistema 1 de comunicación que incluye al dispositivo 2 de transmisión y al dispositivo 3 de recepción, configurado según se ha descrito en lo que antecede. La figura 3 es un diagrama secuencial que muestra el procesamiento del sistema de comunicación.

En la figura 3, en la parte delantera, la unidad 21 de determinación de tasa de bits detecta el cambio en la tasa de bits de la señal S<sub>datos</sub> de datos serie que va a ser enviada desde la unidad 25 de transmisión del dispositivo 2 de transmisión (S01). A continuación, cuando cambia la tasa de bits, la unidad 25 de transmisión de señal envía una señal S<sub>datos</sub> de datos serie que se establece de modo que sea un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj, hasta el dispositivo 3 de recepción (S02).

Posteriormente, la unidad 31 de recepción de señal del dispositivo 3 de recepción recibe la señal S<sub>datos</sub> de datos serie y la unidad 32 de determinación de valor constante de la señal recibida determina, en base a la señal S<sub>datos</sub> de

datos serie recibida, si la señal  $S_{datos}$  de datos serie es un valor constante a través del período de un múltiplo constante de un ciclo de la señal de reloj (S03).

Si se determina que la señal  $S_{datos}$  de datos serie es un valor constante, la unidad 34 de petición de señal de inicio de entrenamiento envía al dispositivo 2 de transmisión una señal  $T_{req}$  de petición de inicio de entrenamiento para solicitar los datos  $T_{datos}$  de entrenamiento que van a ser usados en la confirmación de la tasa de bits cambiada (S04).

La unidad 23 de determinación de inicio de entrenamiento del dispositivo 2 de transmisión recibe la señal  $T_{req}$  de petición de inicio de entrenamiento que fue enviada desde el dispositivo 3 de recepción (S05), y la unidad 25 de transmisión de señal envía los datos  $T_{datos}$  de entrenamiento al dispositivo 3 de recepción de acuerdo con la señal  $T_{req}$  de petición de inicio de entrenamiento (S06). A continuación, la unidad 33 de recuperación de señal de reloj del dispositivo 3 de recepción recibe los datos  $T_{datos}$  de entrenamiento que fueron enviados desde el dispositivo 2 de transmisión, y de ese modo se implementa la confirmación de la tasa de bits (S07). Después de que el entrenamiento por parte de la unidad 33 de recuperación de señal de reloj se ha completado, la unidad 34 de petición de señal de inicio de entrenamiento envía una señal  $RT_{fin}$  de fin de entrenamiento al dispositivo 2 de transmisión (S08).

10

15

20

30

35

45

50

55

60

65

En consecuencia, el sistema 1 de comunicación que incluye el dispositivo 2 de transmisión y el dispositivo 3 de recepción de la presente realización envía, hasta el dispositivo 3 de recepción, una señal S<sub>datos</sub> de datos serie que ha sido establecida como un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj cuando una tasa de bits de una señal S<sub>datos</sub> de datos serie ha de ser cambiada en el dispositivo 2 de transmisión. A continuación, el dispositivo 3 de recepción que recibió la señal S<sub>datos</sub> de datos serie recibe los datos T<sub>datos</sub> de entrenamiento procedentes del dispositivo 2 de transmisión si se determina que la señal S<sub>datos</sub> de datos serie es un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj, y procede al procesamiento de confirmación de la tasa de bits cambiada. En consecuencia, el dispositivo 3 de recepción está capacitado para reconocer el cambio de la tasa de bits con la recepción de la señal S<sub>datos</sub> de datos serie, y proceder a su procesamiento para confirmar la tasa de bits cambiada sin tener que recibir, a través de una vía diferente, una señal desde el dispositivo 2 que indique que la tasa de bits va a ser cambiada. De ese modo, se puede llevar a cabo de forma fiable la confirmación de la tasa de bits cambiada con una configuración convencional simple sin tener que incrementar la comunicación por la línea de señal de control o habilitar una comunicación interactiva.

Además, el dispositivo 3 de recepción envía una señal  $T_{req}$  de petición de inicio de entrenamiento al dispositivo 2 de transmisión tras la determinación de que la señal  $S_{datos}$  de datos serie es un valor constante; es decir, tras confirmar que la tasa de bits ha sido cambiada, y el dispositivo 2 de transmisión ha recibido la señal  $T_{req}$  de petición de inicio de entrenamiento y haya enviado a continuación los datos  $T_{datos}$  de entrenamiento al dispositivo 3 de recepción. En consecuencia, el dispositivo 2 de transmisión enviará los datos  $T_{datos}$  de entrenamiento al dispositivo 3 de recepción después de que el dispositivo 3 de recepción reconozca de manera fiable el cambio de la tasa de bits.

40 Por consiguiente, es posible impedir que el dispositivo 2 de transmisión envíe erróneamente los datos T<sub>datos</sub> de entrenamiento o los datos de la tasa de bits cambiada antes de que el dispositivo 3 de recepción reconozca el cambio de la tasa de bits.

Además, el dispositivo 3 de recepción envía una señal RT<sub>fin</sub> de fin de entrenamiento al dispositivo 2 de transmisión indicando la confirmación de que la tasa de bits está completa, y el dispositivo 2 de transmisión envía la señal S<sub>datos</sub> de datos serie de la tasa de bits cambiada después de la recepción de la señal RT<sub>fin</sub> de fin de entrenamiento mencionada anteriormente. En consecuencia, es posible impedir que el dispositivo 2 de transmisión envíe erróneamente una señal S<sub>datos</sub> de datos serie de la tasa de bits cambiada al dispositivo 3 de recepción con anterioridad a la confirmación de que la tasa de bits está completa.

Eventualmente, la presente invención no se limita a la realización que antecede. Por ejemplo, en la realización anterior, aunque la unidad 21 de determinación de tasa de bits haya detectado el cambio de tasa de bits y determine el valor cambiado en la tasa de bits, el dispositivo 2 de transmisión puede detectar el cambio en la tasa de bits al recibir un aviso que indique que la tasa de bits va a ser cambiada.

Adicionalmente, en la realización que antecede, la unidad 21 de determinación de tasa de bits puede estar configurada a modo de PLL (Circuito de Fase Sincronizada). En el caso anterior, como resultado de usar la función de determinación del PLL, la señal de sincronización del PLL puede ser usada como información de cambio de la tasa de bits. Con el PLL, si se cambia la tasa de bits de la señal P<sub>datos</sub> de datos paralelo de entrada, se obtiene como resultado un estado no sincronizado. La detección de un estado no sincronizado en el PLL es conocido públicamente, y se omite la explicación detalladla del mismo, aunque se describe un ejemplo en lo que sigue. Un detector de fase (PD: Detector de fase) en el PLL, compara la fase del bloque incluida en la señal P<sub>datos</sub> de datos paralelo de entrada y la señal de reloj que está presente en la salida del VCO (Oscilador Controlado por Tensión), y detecta el estado no sincronizado y determina que la tasa de datos ha cambiado, por ejemplo, cuando sigue un estado de alto nivel o un estado de bajo nivel en la señal de reloj incluida en la señal P<sub>datos</sub> de datos paralelo, o cuando la entrada consiste solamente en la señal de reloj que fue presentada en la salida del VCO. Si el detector de

fase determina que la tasa de bits de la señal  $P_{datos}$  de datos paralelo ha cambiado (detecta un estado no sincronizado), presenta a la salida la información  $S_{cambio}$  de cambio de tasa de bits para la unidad 22 de comando de señal de aviso de cambio.

- Además, los datos S<sub>datos</sub> serie del valor constante que va a ser enviado por el dispositivo 2 de transmisión, adicionalmente al estado de 0 y 1 como estado de transmisión de datos normales, a saber un estado en el que el par de la señal diferencial son del mismo potencial, un estado en el que ambos son de alta impedancia, y un estado en el que la tensión común es considerablemente diferente, serán reconocidos por el dispositivo 3 de recepción como cambio en la resolución, y pueden ser aplicados como una realización de la presente invención. Además, si los datos S<sub>datos</sub> serie del valor constante son enviados durante un período de tiempo dado, y se sabe por anticipado que el dispositivo 3 de recepción dispondrá en la salida la señal RT<sub>inicio</sub> de manera fiable, el dispositivo 2 de transmisión puede disponer en la salida T<sub>datos</sub> con anterioridad a recibir T<sub>req</sub> después del envío de los datos S<sub>datos</sub> serie del valor constante durante un período de tiempo dado.

- 15 Además, en la realización anterior, aunque el dispositivo 2 de transmisión y el dispositivo 3 de recepción están conectados a través de la línea R1 de señal serie de alta velocidad y de la línea R2 de señal de control de baja velocidad, la configuración puede ser también, por ejemplo, según se muestra en la figura 4. Con la línea R3 de señal mostrada en la figura 4, dos capacidades, a saber la capacidad C1 y la capacidad C2, están conectadas en serie en la primera línea R4 de señal. Adicionalmente, un extremo de la segunda línea de señal R5 que ha de ser 20 conectada al dispositivo 2 de transmisión y un extremo de la segunda línea de señal R6 que ha de ser conectada al dispositivo 3 de recepción, están conectados entre la capacidad C1 y la capacidad C2 de la primera línea de señal L4. Un inductor L1 se ha conectado en serie en la segunda línea de señal R5. Además, un inductor L2 se ha conectado en serie en la segunda línea de señal R6. De acuerdo con esta clase de configuración, la señal S<sub>datos</sub> de datos serie puede ser enviada desde el dispositivo 3 de transmisión hasta el dispositivo 4 de recepción, y las señales 25 de control y similares pueden ser enviadas desde el dispositivo 3 de recepción hasta el dispositivo 2 de transmisión utilizando la línea de señal R3. Se pueden conectar también elementos resistivos como sustitutos de los inductores L1, L2.

- Adicionalmente, aunque la realización que antecede está basada en comunicación inalámbrica, puede ser aplicada también a comunicación alámbrica.

## Explicación de los números de referencia

sistema de comunicación; 2, dispositivo de transmisión; 3, dispositivo de recepción; 21, unidad de determinación de tasa de bits; 22, unidad de comando de señal de aviso de cambio (unidad de comando de transmisión de aviso de cambio); 23, unidad de determinación de inicio de entrenamiento; 24, unidad de creación de datos de entrenamiento; 25, unidad de transmisión de señal; 31, unidad de recepción de señal; 32, unidad de determinación de valor constante de la señal recibida; 33, unidad de recuperación de la señal de reloj; 34, unidad de petición de señal de inicio de entrenamiento; S<sub>datos</sub>, señal de datos serie; S<sub>noti</sub>, señal de control; T<sub>datos</sub>, datos de entrenamiento;

T<sub>req</sub>, señal de petición de inicio de entrenamiento; T<sub>fin</sub>, señal de aviso de finalización; RT<sub>fin</sub>, señal de fin de entrenamiento.

## REIVINDICACIONES

- 1.- Un dispositivo (2) de transmisión, que comprende:

- 5 una unidad (25) de transmisión de señal, para enviar una señal de datos serie incluida en una señal de reloj hasta un dispositivo (3) de recepción;

- una unidad (22) de comando de transmisión de aviso de cambio, para presentar en la salida para la unidad de transmisión de señal, una señal de control para el envío por la unidad (25) de transmisión de señal hasta el dispositivo (3) de recepción de una señal de datos serie que ha sido establecida como un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj cuando ha cambiado la tasa de bits de una señal de datos serie que va a ser enviada por la unidad (25) de transmisión de señal, y

- una unidad (24) de creación de datos de entrenamiento, para crear datos de entrenamiento para confirmar la tasa de bits cambiada en el dispositivo (3) de recepción después de que la señal de control haya sido dispuesta en la salida de la unidad (22) de comando de transmisión de aviso de cambio, y provocar que la unidad (25) de transmisión de señal envíe los datos de entrenamiento al dispositivo (3) de recepción.

- 2.- El dispositivo (2) de transmisión de acuerdo con la reivindicación 1, que comprende además una unidad (23) de determinación de inicio de entrenamiento para recibir, desde el dispositivo (3) de recepción, y disponer a la entrada de una señal de petición de inicio de entrenamiento indicativa de que los datos de entrenamiento para confirmación de la tasa de bit cambiada han sido solicitados desde el dispositivo (3) de recepción; en el que, cuando la unidad (23) de determinación de inicio de entrenamiento recibe la señal de petición de inicio de entrenamiento desde el dispositivo (3) de recepción, la unidad (24) de creación de datos de entrenamiento provoca que la unidad (25) de transmisión de señal envíe los datos de entrenamiento al dispositivo (3) de recepción.

- 3.- El dispositivo (2) de transmisión de acuerdo con la reivindicación 2, en el que, cuando la unidad (23) de determinación de inicio de entrenamiento recibe una señal de fin de entrenamiento indicativa de la confirmación de que la tasa de bits cambiada está completa desde el dispositivo (3) de recepción, la unidad (23) de transmisión de señal envía una señal de datos serie de la tasa de bits cambiada hasta el dispositivo (3) de recepción.

- 4.- El dispositivo (2) de transmisión de acuerdo con una cualquiera de las reivindicaciones 1 a 3, que comprende además una unidad (21) de determinación de tasa de bits para presentar a la entrada una señal de datos paralelo y determinar si existe algún cambio en la tasa de bits de la señal de datos paralelo, y presentar a la salida información de cambio de tasa de bits para la unidad (22) de comando de transmisión de aviso de cambio tras la determinación de que la tasa de bits de la señal de datos paralelo ha cambiado; en el que, la unidad (22) de comando de transmisión de aviso de cambio, tras la recepción de la información de cambio de la tasa de bits procedente de la unidad (21) de determinación de tasa de bits, presenta en la salida la señal de control para la unidad (23) de transmisión de señal.

- 5.- El dispositivo (2) de transmisión de acuerdo con la reivindicación 4, en el que la unidad (21) de determinación de tasa de bits está configurada según un circuito de fase sincronizada (PLL).

- 6.- El dispositivo (2) de transmisión de acuerdo con la reivindicación 5, en el que una señal de sincronización del circuito de fase sincronizada se utiliza como información de cambio de la tasa de bits.

- 7.- Un dispositivo (3) de recepción, que comprende:

30

35

40

55

60

- una unidad (31) de recepción de señal, para recibir una señal de datos serie incluida en una señal de reloj procedente de un dispositivo (2) de transmisión;

- una unidad (32) de determinación de valor constante de la señal recibida, para determinar si la señal de datos serie recibida por la unidad (31) de recepción de señal es un valor constante a través de un período de un múltiplo constante de un ciclo de la señal de reloj, indicando dicho valor constante un cambio en una tasa de bits de la señal de datos serie; y

- una unidad (33) de recuperación de señal de reloj, para recibir datos de entrenamiento que van a ser usados para confirmar la tasa de bits cambiada procedente del dispositivo (2) de transmisión, y para confirmar la tasa de bits cambiada cuando la unidad (32) de determinación de valor constante de la señal recibida determina que la señal de datos serie es un valor constante.

- 8.- El dispositivo (3) de recepción de acuerdo con la reivindicación 7, que comprende además una unidad (34) de petición de señal de inicio de entrenamiento para enviar una señal de petición de inicio de entrenamiento para solicitar datos de entrenamiento que van a ser usados para confirmar la tasa de bits cambiada, y solicitar al dispositivo (2) de transmisión los datos de entrenamiento cuando la unidad (32) de determinación de valor constante de la señal recibida determina que la señal de datos serie es un valor constante a través de un período de un

múltiplo constante de un ciclo de la señal de reloj.

- 9.- El dispositivo (3) de recepción de acuerdo con la reivindicación 8, en el que la unidad (34) de petición de señal de inicio de entrenamiento presenta en la entrada una señal de aviso de finalización indicativa de que la confirmación de la tasa de bits cambiada que se encuentra en la salida de la unidad (33) de recuperación de la señal de reloj está completa, envía una señal de fin de entrenamiento al dispositivo (2) de transmisión de acuerdo con la señal de aviso de finalización, y notifica con ello al dispositivo (2) de transmisión que la confirmación de tasa de bits cambiada está completa.

- 10 10.- Un sistema (1) de comunicación, que comprende:

15

25

- el dispositivo (2) de transmisión de acuerdo con la reivindicación 1, y

- el dispositivo (3) de recepción de acuerdo con la reivindicación 7.

- 11.- Un sistema (1) de comunicación, que comprende:

- el dispositivo (2) de transmisión de acuerdo con la reivindicación 2, y

- 20 el dispositivo (3) de recepción de acuerdo con la reivindicación 8.

- 12.- Un sistema (1) de comunicación, que comprende:

- el dispositivo (2) de transmisión de acuerdo con la reivindicación 3, y

- el dispositivo (3) de recepción de acuerdo con la reivindicación 9.

12

Fig. 3

Fig.4