# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 394 818

21 Número de solicitud: 201100439

61 Int. Cl.:

H03F 3/04 (2006.01)

(12)

#### SOLICITUD DE PATENTE

A2

(22) Fecha de presentación:

14.04.2011

(43) Fecha de publicación de la solicitud:

05.02.2013

(71) Solicitantes:

RUANO MOYANO, José (100.0%) SIERRA NEVADA, 6, 1. 08207 SABADELL (Barcelona) ES

(72) Inventor/es:

**RUANO MOYANO, José**

54 Título: AMPLIFICADOR OPERACIONAL

## (57) Resumen:

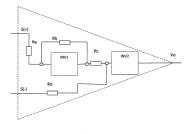

Amplificador operacional, comprende de dos inversores, y cuatro resistencias. La entrada no inversora de amplificador operacional enlaza con una resistencia y esta a su vez con la entrada de uno de los inversores, conectada esta entrada a la salida de este inversor a través de otra resistencia, constituyendo una realimentación. La salida de este inversor enlaza con la entrada un segundo inversor, a través de otra resistencia. Esta misma entrada está conectada a una resistencia cuyo otro extremo está conectado a la entrada inversora del amplificador operacional. La salida del segundo inversor es la salida de este amplificador operacional.

rig.

## **DESCRIPCIÓN**

#### AMPLIFICADOR OPERACIONAL

El objeto de la presente invención, es un amplificador operacional, de una gran sencillez tecnológica, por tanto de menor coste de fabricación.

5

10

15

20

25

30

#### **ANTECEDENTES**

Los amplificadores operacionales que hay actualmente en el mercado, requieren de decenas de transistores. Mientras que el propuesto en la presente invención sólo requiere de ocho transistores.

#### DESCRIPCIÓN DE LA INVENCIÓN

El amplificador operacional de la presente invención, comprende de dos inversores, y cuatro resistencias. La entrada no inversora de amplificador operacional enlaza con una resistencia y esta a su vez con la entrada de uno de los inversores, conectada esta entrada a la salida de este inversor a través de otra resistencia, constituyendo una realimentación. La salida de este inversor enlaza con la entrada del segundo inversor, a través de otra resistencia. Esta misma entrada está conectada a una resistencia cuyo otro extremo está conectado a la entrada inversora del amplificador operacional. La salida del segundo inversor es la salida de este amplificador operacional.

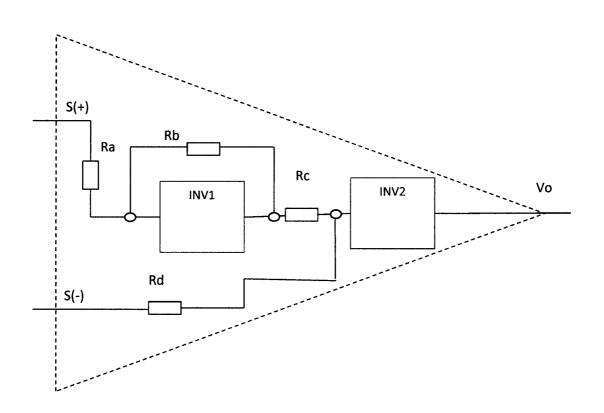

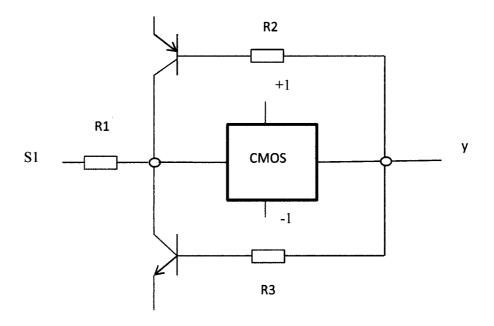

Los inversores están construidos a través de una estructura CMOS de dos transistores Mosfet, uno canal n y otro de canal p. Cuya puerta está conectada al colector de un transistor pnp, y al colector de un transistor npn, y a una resistencia cuyo otro extremo conecta con la entrada del inversor. Las bases de los transistores pnp, y npn enlazan con la salida del CMOS, a cada una a través de una resistencia respectivamente, constituyendo la salida del

## ES 2 394 818 A2

inversor. Siendo este inversor de alta impedancia de entrada.

Con el primer inversor realimentado se consigue que la tensión en su entrada sea cero, luego si se plantea la ecuación aplicando el método de nudos, se tiene que la salida de este primer inversor, proporcionalmente opuesta a la tensión en la entrada no inversora del amplificador operacional.

El segundo inversor sin realimentar, actúa como comparador. Si la tensión en la entrada no inversora del amplificador operacional es mayor que la entrada inversora, la salida adoptará el nivel alto de tensión, en caso contrario el nivel bajo.

Si el amplificador operacional se realimenta 15 negativamente, se tiene un seguidor de tensión. Igualmente, se puede ir obteniendo todas las aplicaciones propias del amplificador operacional.

Los inversores inventados, gracias a los dos transistores pnp, y npn. Este inversor se aproxime mucho al ideal, en el que su función de transferencia es la de un escalón.

## BREVE DESCRIPCIÓN DE LOS DIBUJOS

Los presentes dibujos se presentan a modo de ejemplos no limitativos.

Fig.1: Esquema del amplificador operacional

Fig.2: Esquema de un inversor

20

Fig.3: Esquema de una estructura CMOS

## DESCRIPCIÓN DE UNA REALIZACIÓN PREFERIDA

En este apartado, mostraremos una forma de calcular los componentes que integran el amplificador operacional.

En el diseño de un inversor (fig.2), se utilizarán un transistor pnp y otro npn complementarios. Las resistencias R2 y R3 tendrán el mismo valor. Aunque se pudiera utilizar un potenciómetro para un mayor ajuste. Donde un extremo del potenciómetro iría conectada a una de las bases, y el otro a la otra base del otro transistor, estando la salida del potenciómetro o punto móvil, conectada a la salida de la estructura CMOS.

Cuanto mayor sea R1,R2,R3 mejor. Mayor será la impedancia de entrada del amplificador operacional, y menor consumo tendrá.

15

20

La impedancia de salida del inversor es muy pequeña, debido a que la salida es al de una estructura CMOS.

En el diseño del amplificador operacional, los valores de las resistencias Ra,Rb,Rc,Rd son iguales y muy grandes, pero menores que la R1 del inversor al que van conectadas. Esto hará que el amplificador operacional tenga una impedancia de entrada muy grande.

#### REIVINDICACIONES

1° Amplificador operacional (1), comprende de dos inversores, y cuatro resistencias. La entrada  $(S_{(+)})$  no inversora del amplificador operacional enlaza con una resistencia(Ra) y esta a su vez con la entrada de uno de los inversores(INV1), conectada esta entrada a la salida de través de otra resistencia inversor а constituyendo una realimentación. La salida de inversor enlaza con la entrada un segundo inversor (INV2), a través de otra resistencia (Rc). Esta misma entrada está conectada a una resistencia (Rd) cuyo otro extremo está conectado a la entrada  $(S_{(-)})$  inversora del amplificador operacional. La salida del segundo inversor (INV2) es la salida (Vo) de este amplificador operacional.

10

15

20

25

2° Amplificador operacional según reivindicación anterior, en el que los inversores (2) están construidos a través de una estructura CMOS(3) de dos transistores Mosfet, uno de canal n y otro de canal p. Cuya puerta está conectada al colector de un transistor pnp, y al colector de un transistor npn, y enlaza con la entrada (S1) del inversor a través de una resistencia (R3). Las bases de los transistores pnp, y npn enlazan con la salida del CMOS (y), cada una a través de una resistencia (R1)(R2) respectivamente, siendo esta salida la salida del inversor.

Fig. 1

Fig. 2

Fig. 3