# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 398 127

51 Int. Cl.:

H04L 12/403 (2006.01) B60H 1/00 (2006.01) G06F 12/08 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

- (96) Fecha de presentación y número de la solicitud europea: 25.09.2007 E 07820547 (3)

(97) Fecha y número de publicación de la concesión europea: 02.01.2013 EP 2087655

- (54) Título: Procedimiento para la emisión de un bloque de transmisión de datos y procedimiento y sistema para la transmisión de un bloque de transmisión de datos

- (30) Prioridad:

31.10.2006 DE 102006051866

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 13.03.2013

(73) Titular/es:

ROBERT BOSCH GMBH (100.0%) POSTFACH 30 02 20 70442 STUTTGART, DE

(72) Inventor/es:

**NEWALD, JOSEF**

(74) Agente/Representante:

CARVAJAL Y URQUIJO, Isabel

#### **DESCRIPCIÓN**

Procedimiento para la emisión de un bloque de transmisión de datos y procedimiento y sistema para la transmisión de un bloque de transmisión de datos

Estado de la técnica

5 La presente invención se refiere a un procedimiento para la emisión de un bloque de transmisión de datos y a un procedimiento y a un sistema para la transmisión de bloques de transmisión de datos, en particular por medio de un bus Flexray.

El bus Flexray y el protocolo Flexray correspondiente se describen, por ejemplo, en la publicación EP 1 355 456 A1.

De acuerdo con el protocolo Flexray que trabaja con un procedimiento múltiple por división de tiempo se transmiten cuadros o bloques de transmisión de datos en un ciclo de comunicación con un segmento estático y/o un segmento dinámico.

En el sentido de esta solicitud, las expresiones cuadro, cuadro de datos, bloque de transmisión de datos, marco, noticia y mensaje son sinónimos y designan lo mismo.

El bloque de transmisión de datos contiene en este caso un segmento de cabecera (Header), un segmento de datos (Payload) y un segmento de suma de control (CRC Data). Un segmento de datos contiene una o varias unidades de datos, que pueden presentar también un tamaño diferente. El bloque de transmisión de datos es transmitido desde un primer dispositivo de emisión/recepción o nodo, que está acoplado con el bus Flexray, a un segundo dispositivo de emisión/recepción o nodo, que está acoplado de la misma manera con el bus Flexray.

Para la indicación de si la unidad de datos respectiva es actual o se transmiten datos anticuados en el lugar de la unidad de datos correspondientes en el bloque de transmisión de datos, se puede prever también un bit de validez. Un bit de validez colocado en uno indica que la unidad de datos correspondiente es válida. Un bit de validez colocado en cero indica, en cambio, que la unidad de datos correspondiente no es válida.

No obstante, todos los datos de validez de un bloque de transmisión de datos deben borrarse antes de una nueva escritura y emisión siguiente, para evitar que se envíen unidades de datos no válidas con bits de validez correspondientes, que presentan todavía un uno. Se puede plantear un problema en el lado del receptor especialmente cuando un bit de validez, que debería haberse borrado, no se ha podido borrar oportunamente antes de la emisión. Aquí se pueden producir en el lado del receptor errores no detectables

La publicación US-B1-7 110 457 muestra un procedimiento y un sistema de acuerdo con el preámbulo de las reivindicaciones 1, 8 y 10.

30 Ventajas de la invención

25

35

50

El procedimiento de acuerdo con la invención para la emisión de un bloque de transmisión de datos con las características de la reivindicación 1 y el procedimiento o bien el sistema de acuerdo con la invención para la transmisión de un bloque de transmisión de datos con las características de la reivindicación 8 o bien con las características de la reivindicación 10 presenta la ventaja de que se puede prescindir del borrado del bit de validez convencional respectivo. De acuerdo con la invención, tampoco debe realizarse la administración costosa del borrado del bit de validez.

Además, de acuerdo con la invención, puede realizarse siempre una manifestación segura en el lado del receptor de si la unidad de datos de un bloque de transmisión de datos recibido presenta datos válidos o no válidos.

La idea en la que se basa la presente invención consiste esencialmente en prever en cada caso una fecha de validez para unidades de datos predeterminadas que, en virtud de su importancia, su relevancia para la seguridad o similar deben dotarse con una indicación de validez, conteniendo la fecha de validez una información del historial, que indica una modificación de la fecha de validez, en particular después de un nuevo proceso de escritura de la unidad de datos correspondiente.

De acuerdo con la invención, como configuraciones de la fecha de validez se proponen un bit oscilante o un contador de N-bits, siendo ambos adecuados para preparar, además de la información de validez, para la unidad de datos correspondiente, también una información de historial.

De acuerdo con ello, se propone un procedimiento para la emisión de un bloque de transmisión de datos, en el que el bloque de transmisión de datos presenta al menos un segmento de datos con un número predeterminado de una o varias unidades de datos que deben identificarse con una indicación de validez y un segmento de cabecera, conteniendo el procedimiento las siguientes etapas:

- a) escritura de una unidad de datos en una primera zona, predeterminada para el segmento de datos, de un registro de salida, desde el que se envía el bloque de transmisión de datos registrado en memoria intermedia en un instante de emisión predeterminado por medio de un procedimiento múltiple por división de tiempo a través de un sistema de bus;

- escritura de una fecha de validez configurada como un bit oscilante o como un contador de N-bits en una segunda zona, predeterminada para el segmento de cabecera, del registro de salida, indicando la fecha de validez respectiva la validez de la unidad de datos escrita correspondiente. En este caso, el segmento de cabecera puede estar dispuesto, por ejemplo en la zona del segmento de datos (Payload) y/o en la zona de cabecera (Header) del cuadro Flexray;

- 10 c) liberación para la emisión del bloque de transmisión de datos registrado en memoria intermedia en el registro de salida, después de que la unidad de datos respectiva y la fecha de validez correspondiente están escritas en el registro de salida;

- d) repetición de las etapas (a)-(c) hasta que están escritos el número predeterminado de las unidades de datos y los datos de validez correspondientes o se ha alcanzado el instante de emisión predeterminado; y

- e) emisión del bloque de transmisión de datos liberado, registrado en memoria intermedia en el registro de salida, en el instante de la emisión.

Por lo demás, se propone un procedimiento para la transmisión de bloques de transmisión de datos, que presenta las siguientes etapas:

- emisión de un bloque de transmisión de datos por medio de un primer dispositivo de emisión/recepción de acuerdo con el procedimiento descrito anteriormente para la emisión de un bloque de transmisión de datos;

- recepción del bloque de transmisión de datos emitido por medio de un segundo dispositivo de emisión/recepción, que está acoplado por medio de un sistema de bus con el primer dispositivo de emisión/recepción;

- verificación de los datos de validez contenidos en el bloque de transmisión de datos recibido; y

- extracción y registro en memoria de las unidades de datos, cuya fecha de validez correspondiente es válida, y desecho de las unidades de datos, cuyo dato de validez correspondiente no es válido, a través del segundo dispositivo de emisión/recepción.

Además, se propone un sistema para la transmisión de un bloque de transmisión de datos, en el que el bloque de transmisión de datos presenta al menos un segmento de datos con un número predeterminado de una o varias unidades de datos que deben identificarse con una indicación de validez y un segmento de cabecera con:

- un primer dispositivo de emisión/recepción, que es adecuado para realizar un procedimiento para la emisión de un bloque de transmisión de datos de acuerdo con la reivindicación 1 o una o varias de las reivindicaciones 2 a 7:

- un sistema de bus, que acopla el primer dispositivo de emisión/recepción al menos con un segundo dispositivo de emisión/recepción; y

- el segundo dispositivo de emisión/recepción, que presenta:

5

15

20

25

30

35

40

- un primer medio, que recibe el bloque de transmisión de datos emitido por el primer dispositivo de emisión/recepción;

- un segundo medio, que verifica los datos de validez contenidos en el bloque de transmisión de datos recibido; y

- un tercer medio, que es adecuado para extraer y memorizar las unidades de datos, cuya fecha de validez correspondiente es válida, y desechar aquellas unidades de datos, cuya fecha de validez correspondiente no es válida.

En las reivindicaciones dependientes se encuentran desarrollos y configuraciones ventajosos del procedimiento indicado en la reivindicación 1 o bien en la reivindicación 8 y del sistema indicado en la reivindicación 10 para la emisión o bien la transmisión de un bloque de transmisión de datos.

De acuerdo con un desarrollo preferido de la invención, el bloque de transmisión de datos presenta un segmento de suma de control, en el que la suma de control es calculada sobre al menos una parte predeterminada del segmento de datos y/o del segmento de cabecera y la suma de control calculada es memorizada en una tercera zona,

predeterminada para el segmento de suma de control, de la memoria intermedia de salida. La suma de control es, por ejemplo, una suma de control CRC (CRC: Chequeo de Redundancia Cíclico). Las sumas de control CRC se emplean especialmente en la detección de errores. Teóricamente también pueden servir para la corrección de errores, pero la distancia Hamming (corrección de errores) en el protocolo Flexray no es suficiente, en general, para ello y el gasto a tal fin es muy alto.

De acuerdo con una configuración preferida de la invención, el sistema de bus está configurado como un sistema de bus Flexray.

De acuerdo con otra configuración preferida, la fecha de validez está configurada como bit oscilante, en el que el bit oscilante respectivo es conmutado en cada escritura de la unidad de datos correspondiente. Por lo tanto, el bit oscilante se coloca después de cada proceso de escritura de forma alterna en el valor 0 y a continuación en el valor 1. De acuerdo con ello, también de forma alterna se interpretan el valor 0 y a continuación el valor 1 como válidos. Por consiguiente, el significado del bit oscilante se invierte periódicamente. De manera más ventajosa, a través de la configuración del bit oscilante se pueden detectar aquellos errores, en los que la fecha de validez presenta un valor predeterminado durante un periodo de tiempo prolongado independientemente de la unidad de datos correspondiente descrita.

De acuerdo con otra configuración preferida, la fecha de validez está configurada como el contador de N-bits, en el que el contador de N-bits correspondiente se incrementa o decrementa en cada escritura de la unidad de datos correspondiente en la medida de una zona de contador predeterminada. Como consecuencia de la redundancia resultante a través de los N bits resulta una seguridad más elevada. Por ejemplo, en un contador de 8 bits resulta una elevación de la seguridad en el factor de aproximadamente 250. Con preferencia, el contador de N bits respectivo se incrementa o decrementa en uno en cada escritura de la unidad de datos correspondiente.

De acuerdo con otra configuración preferida, los contadores de N-bits para las diferentes unidades de datos son inicializados en cada caso con otro valor de inicialización. De esta manera, los diferentes contadores de N-bits se pueden distinguir bien unos de los otros.

De acuerdo con otro desarrollo preferido, en el que la fecha de validez está configurada como el contador de N-bits, el contador de N-bits respectivo se incrementa o decrementa en cada escritura de la unidad de datos correspondiente en la medida de una zona predeterminada del contador por medio del primer dispositivo de emisión/recepción y el estado respectivo del contador de N-bits es memorizado por medio de un dispositivo de memoria del segundo dispositivo de emisión/recepción. Por lo tanto, de manera más ventajosa, el segundo dispositivo de emisión/recepción, que recibe el bloque de transmisión de datos emitido por el primer dispositivo de emisión/recepción, puede comparar en cada caso el valor actual del contador de N-bits con el valor precedente del contador de N-bits y de esta manera establecer una modificación potencial del mismo.

De acuerdo con otro desarrollo preferido, el segundo dispositivo de emisión/recepción presenta un dispositivo de memoria, que es adecuado para memorizar en cada caso el estado del contador de una fecha de validez configurada como contador de N-bits.

De acuerdo con otro desarrollo preferido, en el que el sistema de bus está configurado como un sistema de bus Flexray, el primer dispositivo de emisión/recepción y/o el segundo dispositivo de emisión/recepción presenta un dispositivo de control de la comunicación Flexray.

# Dibujos

5

10

15

20

35

45

40 Los ejemplos de realización de la invención se representan en los dibujos y se explican en detalle en la siguiente descripción. En este caso:

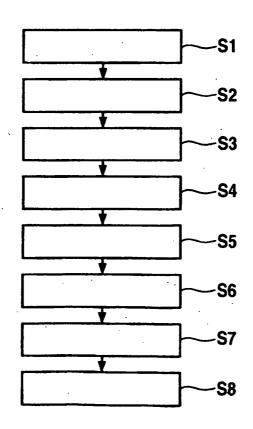

La figura 1 muestra un diagrama de flujo esquemático de un primer ejemplo de realización del procedimiento de acuerdo con la invención.

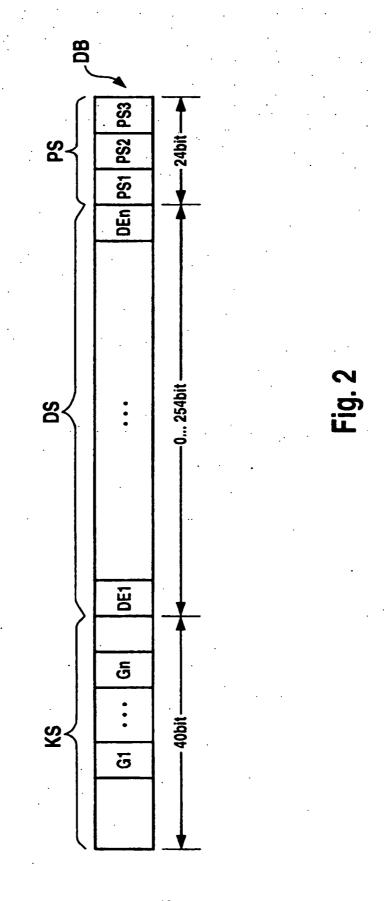

La figura 2 muestra un diagrama de bloques esquemático de un ejemplo de realización preferido del formato del bloque de transmisión de datos de acuerdo con la presente invención.

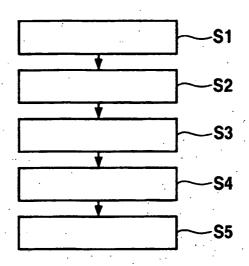

La figura 3 muestra un diagrama de flujo esquemático de un segundo ejemplo de realización del procedimiento de acuerdo con la invención; y

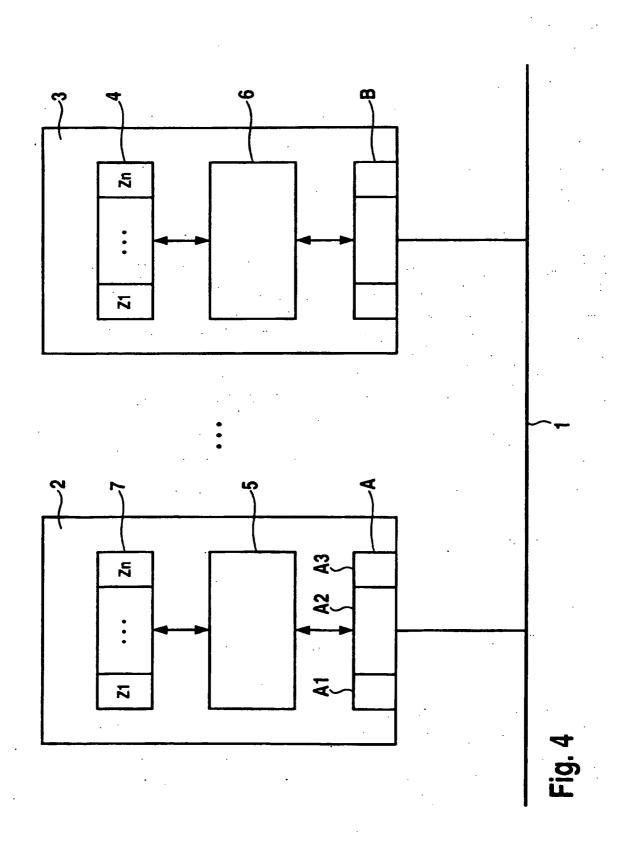

La figura 4 muestra un diagrama de flujo esquemático de un ejemplo de realización preferido del sistema para la transmisión de bloques de transmisión de datos de acuerdo con la presente invención.

## 50 Descripción de los ejemplos de realización

En las figuras, los mismos signos de referencia designan componentes iguales o funcionalmente iguales.

En la figura 1 se representa un diagrama de flujo esquemático de un primer ejemplo de realización del procedimiento de acuerdo con la invención para la emisión de un bloque de transmisión de datos DB. El bloque de transmisión de datos DB presenta al menos un segmento de datos DS con un número predeterminado de una o varias unidades de datos DE1-DEn que deben identificarse con una indicación de validez y un segmento de cabecera KS (ver la figura 2).

A continuación se describe el procedimiento de acuerdo con la invención con la ayuda del diagrama de bloques en la figura 1 con referencia al diagrama de bloques esquemático del formato del bloque de datos de transmisión DB según la figura 2 y con referencia al diagrama de bloques esquemático del sistema según la figura 4. El primer ejemplo de realización del procedimiento de acuerdo con la invención según la figura 1 presenta las siguientes etapas del procedimiento S1-S5:

### Etapa del procedimiento S1:

5

10

15

25

30

35

45

Se escribe una unidad de datos DE1-DEn en una primera zona A1 predeterminada para el segmento de datos DS de una memoria intermedia de salida A, a partir de la cual se envía el bloque de transmisión de datos DB memorizado temporalmente en un instante de emisión predeterminado por medio de un procedimiento múltiple por división de tiempo a través de un sistema de bus 1. El bloque de transmisión de datos DB puede presentar, además de una o varias unidades de datos que deben identificarse con una indicación de validez, también otras unidades de datos que no deben asegurarse. Con preferencia, el sistema de bus 1 es un sistema de bus Flexray.

#### Etapa del procedimiento S2:

Una fecha de validez G1-Gn configurada como un bit oscilante o como un contador de N-bits es descrita en una segunda zona A2 predeterminada para el segmento de cabecera KS de la memoria intermedia de salida A, en la que la fecha de validez G1-Gn respectiva indica la validez de la unidad de datos DE1-DEn descrita correspondiente.

De acuerdo con una primera alternativa de la presente invención, la fecha de calidez G1-Gn puede estar configurada como bit oscilante, de manera que el bit oscilante respectivo se conmuta en cada escritura de la unidad de datos DE1-DEn correspondiente. Como segunda alternativa de la presente invención, la fecha de validez G1-Gn puede estar configurada como contador de N-bits, de manera que el contador de N-bits respectivo es incrementado o decrementado en cada escritura de la unidad de datos DE1-DEn correspondiente en la medida de una zona predeterminada del contador.

Con preferencia, los contadores de N-bits para las diferentes unidades de datos DE1-DEn son inicializados, respectivamente, con un valor de inicialización diferente para su distinción. En particular, el contador de N-bits respectivo es incrementado o decrementado en uno en cada escritura de la unidad de datos DE1-DEn correspondiente.

## Etapa del procedimiento S3:

El bloque de transmisión de datos DB memorizado temporalmente en la memoria intermedia de salida A es liberado para la emisión, después de que la unidad de datos DE1-DEn respectiva y la fecha de validez G1-Gn correspondiente están descritas en la memoria intermedia de salida.

## Etapa del procedimiento S4:

Se repiten las etapas del procedimiento S1 a S3 hasta que e han descrito el número predeterminado de las unidades de datos DE1-DEn y los datos de validez G1-Gn correspondientes o se ha alcanzado el instante de emisión correspondiente, que está definido a través del procedimiento múltiple por división de tiempo.

#### 40 Etapa del procedimiento S5:

El bloque de transmisión de datos DB memorizado temporalmente en la memoria intermedia de salida A es enviado en el instante de emisión a través del sistema de bus 1.

En la figura 3 se representa un diagrama de flujo esquemático de un segundo ejemplo de realización del procedimiento de acuerdo con la invención. El segundo ejemplo de realización según la figura 3 presenta las etapas del procedimiento S1 a S8. En este caso, las etapas del procedimiento S1 a S5 según la figura 3 corresponden a las etapas del procedimiento S1 a S5 según la figura 1. Por razones de claridades prescinde de su representación de nuevo. El segundo ejemplo de realización del procedimiento de acuerdo con la invención según la figura 3 presenta, por lo tanto, las etapas del procedimiento S1 a S5, que se han explicado ya en detalle con referencia a la figura 1, y las siguientes etapas del procedimiento S6 a S7.

## 50 Etapa del procedimiento S6:

El bloque de transmisión de datos DB emitido desde el primer dispositivo de emisión/recepción 2 es recibido por un

# ES 2 398 127 T3

segundo dispositivo de emisión/recepción 3. A tal fin, el primer dispositivo de emisión/recepción 2 está acoplado por medio de un sistema de bus 1 con el segundo dispositivo de emisión/recepción 3.

#### Etapa del procedimiento S7:

Los datos de validez G1-Gn, contenidos en el bloque de transmisión de datos DB recibido, son verificados con respecto a su validez.

#### Etapa del procedimiento S8:

5

Aquellas unidades de datos DE1-DEn, cuya fecha de validez G1-Gn correspondiente es válida, son extraídas y memorizadas. Aquellas unidades de datos DE1-DEn, cuya fecha de validez G1-Gn correspondiente no es válida, son desechadas con preferencia.

- De manera preferida, en el caso de que la fecha de validez G1-Gn esté configurada como contador de N-bits, el contador de N-bits correspondiente se incrementa o de una manera correspondiente se decrementa con cada escritura de la unidad de datos DE1-DEn correspondiente en la medida de una zona predeterminada del contador por medio del primer dispositivo de emisión/recepción 2 y el estadio respectivo del contador de N-bits es memorizado por medio de un dispositivo de memoria 4 del segundo dispositivo de emisión/recepción 3.

- La figura 4 muestra un diagrama de bloques esquemático de un ejemplo de realización preferido del sistema para la transmisión de bloques de transmisión de datos DB, que presentan en cada caso al menos un segmento de datos DS con un número predeterminado de una o varias unidades de datos DE1-DEn que deben identificarse con una indicación de validez y un segmento de cabecera KS. El sistema de acuerdo con la figura 4 presenta un número predeterminado de dispositivos de emisión/recepción 2, 3, que están acoplados entre sí a través de un sistema de bus 1. Sin limitación de la generalidad, en la figura 4 solamente se representan un primer dispositivo de emisión/recepción 2 y un segundo dispositivo de emisión/recepción 3.

- El primer dispositivo de emisión/recepción 2 es adecuado para realizar un procedimiento para la emisión de un bloque de transmisión de datos, como se describe con referencia a la figura 1.

- El segundo dispositivo de emisión/recepción 3 presenta al menos un primer medio, un segundo medio y un tercer medio. El primer medio es adecuado para recibir el bloque de transmisión de datos FB enviado por el primer dispositivo de emisión/recepción 2. El segundo medio es adecuado para verificar los datos de validez G1-Gn contenidos en el bloque de transmisión de datos DB recibido. Además, el tercer medio es adecuado para extraer y memorizar las unidades de datos DE1-DEn, cuya fecha de validez G1-Gn correspondiente es válida, y especialmente aquellas unidades de datos DE1-DEn, cuya fecha de validez correspondiente no es válida.

- Con preferencia, el segundo dispositivo de emisión/recepción 3 presenta un dispositivo de memoria 4, que es adecuado para memorizar en cada caso un estado de contador Z1-Zn de una fecha de validez G1-Gn configurada como contador de N-bits. De esta manera, se posibilita al segundo dispositivo de emisión/recepción 3 comparar el estado respectivo del contador Z1-Zn del contador de N-bits respectivo de la unidad de datos DE1-DEn recibida actualmente con el contador de N-bits de la unidad de datos DE1-DEn recibida anteriormente.

- Con preferencia, la primera instalación de emisión/recepción 2 y el segundo dispositivo de emisión/recepción 3 presentan un dispositivo de control de la comunicación Flexray 5, 6. El primer dispositivo de control de la comunicación Flexray 5 es especialmente adecuado para controlar la memoria intermedia de salida A y un segundo dispositivo de memoria 7, que memoriza temporalmente con preferencia los estados respectivos del contador Z1-Zn. El segundo dispositivo de control de la comunicación Flexray 6 es especialmente adecuado para controlar una memoria intermedia de entrada B y el primer dispositivo de memoria 4.

Aunque la presente invenciones ha descrito anteriormente con la ayuda de los ejemplos de realización preferidos, no está limitada a ello, sino que se puede modificar de múltiples maneras.

### REIVINDICACIONES

1.- Procedimiento para la emisión de un bloque de transmisión de datos (DB), que presenta al menos un segmento de datos (DS) con un número predeterminado de una o varias unidades de datos (DE1-DEn) que deben identificarse con una indicación de validez y un segmento de cabecera (KS), en el que el procedimiento se caracteriza porque incluye las siguientes etapas:

5

15

20

25

30

35

45

50

- a) escritura de una unidad de datos (DE1-DEn) en una primera zona (A), predeterminada para el segmento de datos (DS), de un registro de salida (A1), desde el que se envía el bloque de transmisión de datos (DB) registrado en memoria intermedia en un instante de emisión predeterminado por medio de un procedimiento múltiple por división de tiempo a través de un sistema de bus (1);

- b) escritura de una fecha de validez (G1-Gn) configurada como un bit oscilante o como un contador de N-bits en una segunda zona (A2), predeterminada para el segmento de cabecera (KS), del registro de salida (A), indicando la fecha de validez (G1-Gn) respectiva la validez de la unidad de datos (DE1-DEn) escrita correspondiente;

- c) liberación para la emisión del bloque de transmisión de datos (DB) registrado en memoria intermedia en el registro de salida (A), después de que la unidad de datos (DE1-DEn) respectiva y la fecha de validez (G1-Gn) correspondiente están escritas en el registro de salida (A);

- d) repetición de las etapas (a)-(c) hasta que el número predeterminado de las unidades de datos (DE1-DEn) y los datos de validez (G1-Gn) correspondientes están escritos o se ha alcanzado el instante de emisión predeterminado; y

- e) emisión del bloque de transmisión de datos (DB) liberado, registrado en memoria intermedia en el registro de salida (A), en el instante de la emisión.

- 2.- Procedimiento de acuerdo con la reivindicación 1, en el que el bloque de transmisión de datos (DB) presenta un segmento de suma de control (PS), en el que la suma de control (PS1-PS3) es calculada a través de al menos una parte predeterminada del segmento de datos (DS) y/o del segmento de cabecera (KS) y la suma de control (PS1-PS3) calculada es memorizada en una tercera zona (A3), predeterminada para el segmento de suma de control (PS), del registro de salida (A).

- 3.- Procedimiento de acuerdo con la reivindicación 1 ó 2, en el que el sistema de bus (1) está configurado como un sistema de bus Flexray.

- 4.- Procedimiento de acuerdo con la reivindicación 1 o una de las reivindicaciones 2 ó 3, en el que la fecha de validez (G1-Gn) está configurada como bit oscilante, en el que el bit oscilante respectivo es conmutado en cada escritura de la unidad de datos (DE1-DEn) correspondiente.

- 5.- Procedimiento de acuerdo con la reivindicación 1 o una de las reivindicaciones 2 ó 3, en el que la fecha de validez (G1-Gn) está configurada como contador de N-bits, en e que el contador de N-bits respectivo es incrementado o decrementado con cada escritura de la unidad de datos (DE1-DEn) en la medida de una zona predeterminada del contador.

- 6.- Procedimiento de acuerdo con la reivindicación 5, en el que los contadores de N-bits son inicializados para las diferentes unidades de datos (DE1-DEn), respectivamente, con un valor de inicialización diferente.

- 7.- Procedimiento de acuerdo con la reivindicación 5 ó 6, en el que el contador de N-bits respectivo es incrementado o decrementado en uno con cada escritura de la unidad de datos (DE1-DEn) correspondiente.

- 40 8.- Procedimiento para la transmisión de bloques de transmisión de datos (DB), con las etapas:

- a) emisión de un bloque de transmisión de datos (DB) por medio de un primer dispositivo de emisión/ recepción (2) de acuerdo con el procedimiento para la emisión de un bloque de transmisión de datos (DB) de acuerdo con la reivindicación 1 o una o varias de las reivindicaciones 2 a 7;

- b) recepción del bloque de transmisión de datos (DB) emitido por medio de un segundo dispositivo de emisión/ recepción (3), que está acoplado por medio del sistema de bus (1) con el primer dispositivo de emisión/ recepción (2);

- c) verificación de los datos de validez (G1-Gn)contenidos en el bloque de transmisión de datos (DB) recibido;

y

- d) extracción y registro en memoria de las unidades de datos (DE1-DEn), cuya fecha de validez (G1-Gn) correspondiente es válida, y desecho de las unidades de datos (DE1-DEn), cuyo dato de validez (G1-Gn)

# ES 2 398 127 T3

correspondiente no es válido, a través del segundo dispositivo de emisión/recepción (3).

- 9.- Procedimiento de acuerdo con la reivindicación 8, en el que la fecha de validez (G1-Gn) está configurada como contador de N-bits, en el que el contador de N-bits correspondiente es incrementado o decrementado en cada escritura de la unidad de datos (DE1-DEn) correspondiente con una zona de contador predeterminada por medio del primer dispositivo de emisión/recepción (2) y el estado respectivo del contador de N-bits es memorizado por medio de u dispositivo de memoria (4) del segundo dispositivo de emisión/recepción (3).

- 10.- Sistema para la transmisión de un bloque de transmisión de datos (DB), que presenta al menos un segmento de datos (DS) con un número predeterminado de una o varias unidades de datos (DE1-DEn) que deben identificarse con una indicación de validez y un segmento de cabecera (KS), en el que el sistema se caracteriza porque incluye las siguientes característica:

- a) un primer dispositivo de emisión/recepción (2), que es adecuado para realizar un procedimiento para la emisión de un bloque de transmisión de datos (DB) de acuerdo con la reivindicación 1 o una o varias de las reivindicaciones 2 a 7;

- b) un sistema de bus (1), que acopla el primer dispositivo de emisión/recepción (2) al menos con un segundo dispositivo de emisión/recepción (3); y

- c) el segundo dispositivo de emisión/recepción (3), que presenta:

- (c1) un primer medio, que recibe el bloque de transmisión de datos (DB) emitido por el primer dispositivo de emisión/recepción (2);

- (c2) un segundo medio, que verifica los datos de validez (G1-Gn) contenidos en el bloque de transmisión de datos recibido (DB); y

- (c3) un tercer medio, que es adecuado para extraer y memorizar las unidades de datos (DE1-DEn), cuya fecha de validez (G1-Gn) correspondiente es válida, y desechar aquellas unidades de datos (DE1-DEn), cuya fecha de validez (G1-Gn) correspondiente no es válida.

- 11.- Sistema de acuerdo con la reivindicación 10, en el que el segundo dispositivo de emisión/recepción (3) presenta un dispositivo de memoria (4), que es adecuado para memorizar en cada caso un estado del contador (Z1-Zn)de una fecha de validez (G1-Gn)configurada como contador de N-bits.

- 12.- Sistema de acuerdo con la reivindicación 10 u 11, en el que el sistema de bus (1) está configurado como un sistema de bus Flexray y el primer dispositivo de emisión/recepción (2) y/o el segundo dispositivo de emisión/recepción (3) presenta un dispositivo de control de la comunicación Flexray (5, 6).

30

5

10

15

20

Fig. 1

Fig. 3