# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 406 422

61 Int. Cl.:

**G10L 19/00** (2013.01) **G10L 21/02** (2013.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

**T3**

96 Fecha de presentación y número de la solicitud europea: 24.06.2008 E 08767224 (2)

97 Fecha y número de publicación de la concesión europea: 27.02.2013 EP 2313885

(54) Título: Esquema multimodo para codificación mejorada de audio

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **06.06.2013**

(73) Titular/es:

TELEFONAKTIEBOLAGET L M ERICSSON (PUBL) (100.0%) 164 83 Stockholm, SE

(72) Inventor/es:

GRANCHAROV, VOLODYA; BRUHN, STEFAN y POBLOTH, HARALD

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

#### **DESCRIPCIÓN**

Esquema multimodo para codificación mejorada de audio

#### Campo técnico

La presente invención se refiere a un esquema mejorado para codificación de audio. En particular, la presente invención se refiere a un dispositivo codificador y a un método para la codificación de una señal de entrada en un sistema codificador.

#### **Antecedentes**

5

10

15

20

25

30

35

40

Una solución convencional para la codificación, por ejemplo de audio, es cuantificar zonas de baja frecuencia de la señal de entrada en un codificador, y reconstruir zonas de alta frecuencia del espectro en el descodificador, en función de un libro de códigos de reconstrucción. De este modo, todos los bits son asignados a las componentes de frecuencia inferiores a un umbral de frecuencia predefinido o índice, y en el descodificador los componentes de frecuencia restantes (no cuantificados) se reconstruyen a partir de los componentes de frecuencia cuantificados.

Una solución más avanzada, que es adecuada para velocidades binarias variables, es detectar dinámicamente las zonas a cuantificar y las zonas a reconstruir en base, por ejemplo, a la energía de las bandas de frecuencia de la entrada.

Además, se ha propuesto ajustar el tamaño de las zonas a cuantificar en base al grado de dificultad para codificar dichas zonas en la señal de entrada en cuestión. La zona es menor cuando contiene un espectro que es difícil de cuantificar, y viceversa.

En la memoria US 2007/019086 A1 se da a conocer un ejemplo de un esquema conocido de codificación de audio que permite la utilización de parámetros de codificación.

A pesar de lo mencionado anteriormente, sigue existiendo la necesidad de un esquema mejorado para codificación de audio.

#### Compendio

Por consiguiente, es un objetivo de la presente invención dar a conocer un dispositivo codificador y un método para disponer un esquema de codificación que permita una calidad de audio mejorada en un terminal receptor.

Se da a conocer un método para codificar una señal de entrada en un sistema codificador, según la reivindicación 1. El método comprende aplicar un primer modo a la señal de entrada para formar una primera salida y aplicar un segundo modo a la señal de entrada para formar una segunda salida. A continuación se forma una primera salida procesada a partir de por lo menos una parte de la primera salida, y se forma una segunda salida procesada a partir de por lo menos una parte de la segunda salida. Formar una segunda salida procesada comprende estimar una parte de la señal de entrada a partir de por lo menos una parte de la segunda salida.

A continuación, se determina un modo óptimo en base a la primera salida procesada y la segunda salida procesada, y se selecciona la salida de acuerdo con el modo óptimo. Además, se da a conocer un dispositivo codificador según la reivindicación 7. El dispositivo codificador comprende un controlador y una unidad codificadora conectada al controlador. La unidad codificadora está dispuesta para aplicar un primer modo a una señal de entrada a efectos de formar una primera salida, y está dispuesta para aplicar un segundo modo a la señal de entrada a efectos de formar una segunda salida. El controlador está dispuesto para formar una primera salida procesada a partir de por lo menos una parte de la primera salida, y una segunda salida procesada a partir de por lo menos una parte de la segunda salida procesada comprende estimar una parte de la señal de entrada a partir de por lo menos una parte de la segunda salida. Además, el controlador está dispuesto para determinar un modo óptimo en base a la primera salida procesada y a la segunda salida procesada, y está dispuesto para seleccionar la salida en función del modo óptimo.

Una ventaja importante de la presente invención es que se selecciona un modo óptimo para la codificación a partir de una serie de modos, de manera que se mejora la calidad de una transmisión de señal de audio.

Durante la cuantificación de una señal de entrada, se introducen errores de cuantificación debido al número limitado de bits disponibles. Puede obtenerse una precisión mayor para la cuantificación mediante el recurso de cuantificar solamente una parte seleccionada de la señal de entrada y reconstruir la parte restante. La reconstrucción de una señal, por ejemplo componentes de alta frecuencia desconocidos a partir de componentes de baja frecuencia cuantificados conocidos, introduce artefactos de reconstrucción en la señal de salida resultante. Por lo tanto, existe un compromiso entre errores de cuantificación y artefactos de reconstrucción cuando se codifica una señal de entrada.

Según la presente invención, un modo óptimo correspondiente a una salida óptima es determinado y seleccionado a partir de una serie de modos que incluyen un primer modo y un segundo modo en base a un proceso, que por

ejemplo incluye descodificación, de las salidas resultantes de la aplicación de dicha serie de modos a la señal de entrada.

#### Breve descripción de los dibujos

Las anteriores y otras características y ventajas de la presente invención resultarán evidentes para los expertos en la materia mediante la siguiente descripción detallada de realizaciones a modo de ejemplo de la misma, haciendo referencia a los dibujos adjuntos, en los cuales:

|    | la figura 1               | muestra esquemáticamente una realización del dispositivo codificador según la presente invención, |

|----|---------------------------|---------------------------------------------------------------------------------------------------|

|    | la figura 2               | muestra esquemáticamente una realización del dispositivo codificador según la presente invención, |

|    | la figura 3               | muestra esquemáticamente una realización de una unidad codificadora de la figura 1,               |

| 10 | la figura 4               | muestra esquemáticamente una realización de un controlador de la figura 1,                        |

|    | la figura 5               | muestra esquemáticamente una realización de una unidad codificadora de la figura 2,               |

|    | la figura 6               | muestra esquemáticamente una realización de un controlador de la figura 2,                        |

|    | la figura 7<br>invención; | muestra esquemáticamente una realización de un dispositivo codificador según la presente          |

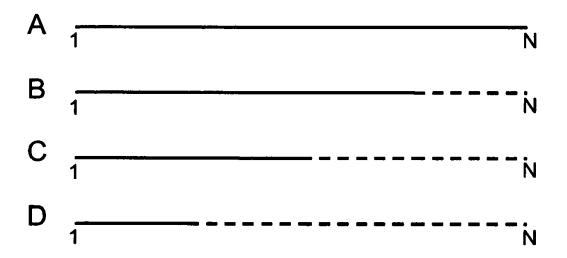

| 15 | la figura 8 invención,    | muestra diferentes modos aplicados en el dispositivo codificador y el método según la presente    |

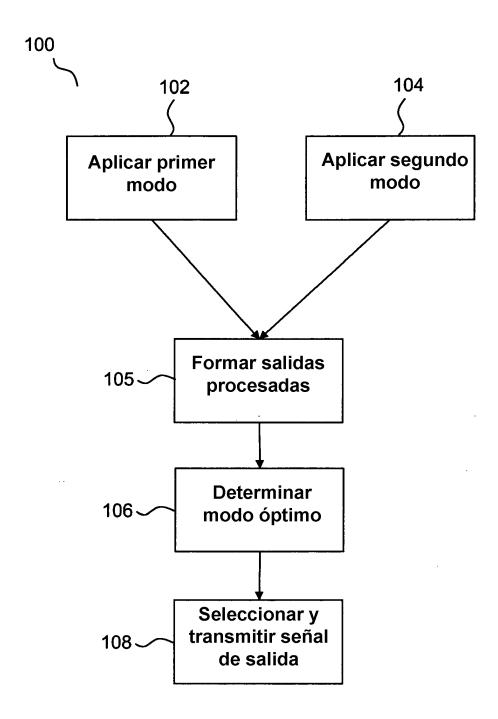

|    | la figura 9               | muestra esquemáticamente una realización del método según la presente invención,                  |

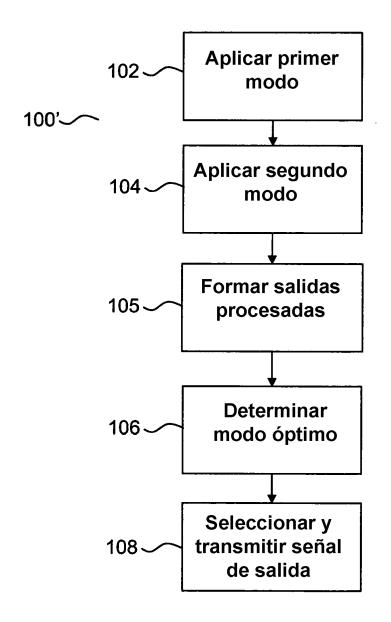

|    | la figura 10              | muestra esquemáticamente una realización del método según la presente invención, y                |

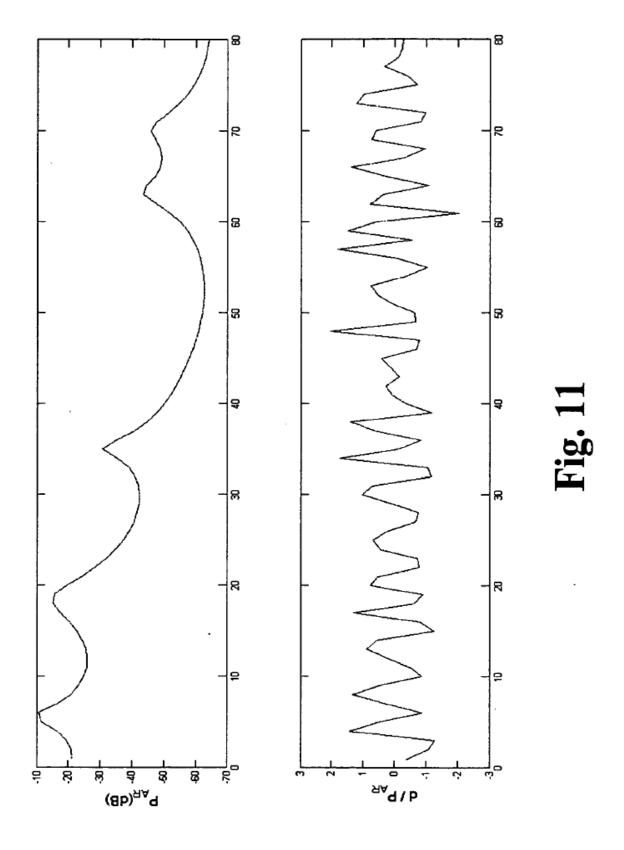

|    | la figura 11              | muestra una envolvente del espectro y un residuo comprimido para una trama de voz de 20 ms.       |

#### 20 Abreviaturas

AR autorregresivo

BWE extensión del ancho de banda

DFT transformada de Fourier discreta

GMM modelos mixtos gaussianos

25 KLT transformada de Karhunen Loève

MDCT transformada de coseno discreta modificada

SBR replicación de la banda espectral

SQ cuantificador escalar

VQ cuantificador vectorial

## 30 Descripción detallada

35

40

Las figuras son esquemáticas y están simplificadas por claridad, y muestran simplemente los detalles que son esenciales para la comprensión de la invención, habiéndose omitido otros. A través de toda la descripción, se utilizan los mismos numerales de referencia para partes idénticas o correspondientes.

El método según la invención comprende la aplicación de la serie de modos que incluyen un primer modo y un segundo modo, a la señal de entrada. La señal de entrada puede ser preprocesada, por ejemplo mediante la aplicación de una envolvente espectral antes de la aplicación de los modos.

Aplicar un modo a una señal de entrada puede comprender cuantificar una parte seleccionada de la señal de entrada, por ejemplo aplicar un primer modo a la señal de entrada puede comprender cuantificar una primera parte de la señal de entrada y/o aplicar un segundo modo la señal de entrada puede comprender cuantificar una segunda parte de la señal de entrada. La primera parte y la segunda parte pueden solapar.

Un ejemplo de modo consiste en que se cuantifican las frecuencias o los coeficientes de la señal de entrada menores o iguales a un umbral de cuantificación, quedando para ser reconstruidas las frecuencias o coeficientes superiores al umbral de cuantificación. Diferentes umbrales de cuantificación pueden caracterizar modos diferentes.

En el método, formar una segunda salida procesada puede comprender reconstruir una parte de la señal de entrada utilizando extensión del ancho de banda.

En el método según la invención, un número adecuado M de modos puede aplicarse a la señal de entrada para formar M salidas. En una realización, una selección de salidas o preferiblemente todas se procesan para formar salidas procesadas. Dichas salidas seleccionadas o preferiblemente todas, procesadas, pueden formar parcial o totalmente bases para la determinación del modo óptimo.

En el método, la determinación del modo óptimo puede comprender determinar un modo óptimo en base a un criterio de selección calculado a partir de la señal de entrada y de la primera salida procesada y la segunda salida procesada.

10 El criterio de selección puede definirse como un problema de minimización dado como:

$$m^{(*)} = \arg\min_{m} D(\underline{X}, \underline{Y}_{m,proc}),$$

donde m(\*) es el modo óptimo, D es la distorsión, m = (1,...,M) es el índice sobre M modos,  $X = (x_0,...,x_{N-1})$  es la señal de entrada, e  $Y_{m,proc} = (y_0,...,y_{N-1})_{m,proc}$  es la salida procesada para el modo m.

Si el cálculo del criterio D(X, Y<sub>m,proc</sub>) para todos los modos M implica una complejidad demasiado elevada, es posible calcular el criterio para solamente un subconjunto de todos los modos y/o para solamente un subconjunto de coeficientes. A continuación, puede interpolarse el criterio para los modos restantes. Esto permite disponer de más modos a elegir que criterios a calcular, y ahorra el cálculo de D y Y<sub>m,proc</sub> para los modos para los que se ha interpolado del criterio. En otras palabras: se consigue una alta resolución en la transición de codificación a BWE, mientras que se mantiene a un nivel reducido la complejidad computacional del algoritmo.

20 En una realización, el criterio de selección puede definirse como un problema de minimización dado como:

$$m^{(*)} = \arg\min_{m} D(\underline{X}, \underline{Y}_{m,proc}),$$

donde m(\*) es el modo óptimo, D es la distorsión, m es el índice sobre M modos,  $X = (x_0,...,x_{N-1})$  es la señal de entrada, e  $Y_{m,proc} = (y_0,...,y_{N-1})_{m,proc}$  es la salida procesada para el modo m.

La distorsión D puede para por lo menos un modo por ejemplo seleccionado, o para todos los modos, estar dada por:

$$D = \frac{1}{N} \sum_{n=0}^{N-1} (x_n^* - y_n^*)^{\beta_n} ,$$

donde N es el número de coeficientes en la señal de entrada,

$$x_0^* = \left| x_0 \right|$$

y  $x_n^* = (1 - \alpha_n) \left| x_n \right| + \alpha_n x_{n-1}^*$  para todo  $1 \le n < N$  ,

$$y_0^* = |y_0| \in y_n^* = (1 - \alpha_n)|y_n| + \alpha_n y_{n-1}^*$$

para todo  $1 \le n < N$ .

30 El factor de ponderación  $\alpha_n$  puede estar dado por:  $\alpha_n = \left(\frac{n}{N}\right)^6$  y/o

el factor de penalización  $\beta_n$  puede ser una constante, por ejemplo  $\beta_n$  = 2, o preferiblemente estar dado por:

$$\beta_n = \begin{cases} 4, & \text{si } (x_n^* - y_n^*) < 0 \\ 2, & \text{si } (x_n^* - y_n^*) \ge 0 \end{cases}.$$

En una realización, la distorsión D puede para por lo menos un modo por ejemplo seleccionado, o para todos los modos, estar dada por:

$$D = \frac{1}{N_{I}} \sum_{n \in I} (x_{n}^{*} - y_{n}^{*})^{\beta_{n}} ,$$

25

donde N es el número de coeficientes en la señal de entrada, I es un subconjunto de enteros desde 0 hasta N-1,  $N_l$  es el número de elementos en I,

$$x_0^* = |x_0| \text{ y } x_n^* = (1 - \alpha_n)|x_n| + \alpha_n x_{n-1}^* \text{ para todo } 1 \le n < N$$

$$y_0^* = |y_0| \in y_n^* = (1 - \alpha_n)|y_n| + \alpha_n y_{n-1}^*$$

para todo  $1 \le n < N$ .

5 El factor de ponderación  $\alpha_{\rm n}$  puede estar dado por:  $\alpha_{\rm n} = \left(\frac{n}{N}\right)^6$  y/o

15

20

25

35

45

el factor de penalización  $\beta_n$  puede ser una constante o preferiblemente estar dado por:

$$\beta_n = \begin{cases} 4, & \text{si } (x_n^* - y_n^*) < 0 \\ 2, & \text{si } (x_n^* - y_n^*) \ge 0 \end{cases}.$$

En una realización, puede estimarse la distorsión D para por lo menos un modo por ejemplo seleccionado, o para todos los modos.

El método puede incluir la etapa de incluir la señal de salida seleccionada de acuerdo con el modo óptimo en una señal de salida del dispositivo codificador, es decir transmitir la señal de salida seleccionada. Con la señal de salida seleccionada puede transmitirse información sobre el modo óptimo seleccionado.

Habitualmente, la señal de entrada es dividida en tramas mediante el dispositivo de codificación. A continuación, puede determinarse el modo óptimo para cada trama, o a una frecuencia seleccionada, por ejemplo de una determinación de salida por cada diez tramas de la señal de entrada.

En la codificación de audio, normalmente la señal de audio es digitalizada y transformada, por ejemplo mediante transformada de coseno discreta modificada (MDCT, Modified Discrete Cosine Transform).

Preferiblemente, la señal de entrada al dispositivo codificador es una señal de entrada digitalizada y transformada. Si la señal de entrada está en el dominio de tiempo, el dispositivo codificador puede comprender una unidad de transformación, por ejemplo una unidad MDCT, para proporcionar una señal de entrada transformada a una unidad codificadora o un preprocesador.

Preferiblemente, los modos a aplicar a la señal de entrada están caracterizados por las dimensiones del vector de la señal de entrada que se consideran para la cuantificación, por ejemplo un primer conjunto de dimensiones consideradas para la cuantificación está asociado con un primer modo, un segundo conjunto de dimensiones consideradas para la cuantificación está asociado con un segundo modo, etc. Los diferentes conjuntos pueden solapar, es decir, compartir algunos elementos. El número óptimo de modos dependerá del presupuesto de bits y de limitaciones sobre la complejidad computacional. El número de modos puede ser cualquier entero positivo mayor que dos. En la presente descripción se consideran dos modos por simplicidad, y en otras partes se consideran cuatro modos a título ilustrativo.

30 El dispositivo codificador según la invención puede disponerse para llevar a cabo las etapas del método según la invención.

La unidad codificadora del dispositivo codificador puede comprender uno o varios codificadores que incluyen un codificador que está adaptado para aplicar en serie una serie de modos, por ejemplo el primer modo y el segundo modo, y enviar en serie las salidas, por ejemplo la primera salida y la segunda salida, al controlador, por ejemplo sobre una primera conexión. La codificación puede comprender cuantificación, compresión y/o normalización.

La unidad codificadora puede comprender un primer codificador y un segundo codificador, en la que el primer codificador está dispuesto para aplicar el primer modo y para enviar la primera salida al controlador sobre una primera conexión, y el segundo codificador está dispuesto para aplicar el segundo modo y para enviar la segunda salida al controlador sobre una segunda conexión.

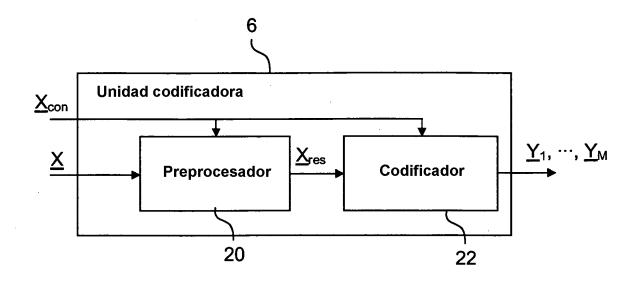

La unidad codificadora puede comprender un preprocesador. El preprocesador puede estar adaptado para aplicar una envolvente espectral a la señal de entrada y alimentar la señal residual resultante al codificador o codificadores.

El controlador puede estar adaptado para determinar el modo óptimo entre los modos aplicados y enviar la señal de salida correspondiente. El controlador puede comprender por lo menos un descodificador dispuesto para procesar salidas, por ejemplo la primera salida y la segunda salida, de acuerdo con los modos correspondientes, por ejemplo de acuerdo con el primer y segundo modos, respectivamente. Además, el controlador puede comprender un procesador dispuesto para determinar el modo óptimo en base a un criterio de selección calculado a partir de la

señal de entrada y de las salidas procesadas o descodificadas, por ejemplo la primera salida procesada y la segunda salida procesada. La salida procesada de por lo menos una de las salidas puede comprender una parte reconstruida, es decir una parte de la señal descodificada o procesada es estimada o reconstruida, por ejemplo mediante extensión del ancho de banda. Los libros de códigos de reconstrucción del transmisor y el receptor para un modo dado se generan a partir de la salida que proporciona la unidad codificadora para el modo en cuestión. El propósito preferido para estos libros de códigos es estimar las dimensiones del vector de entrada que no se consideran para la cuantificación. En caso de que el vector de entrada sea una representación en el dominio de frecuencias, esto corresponde a una extensión del ancho de banda.

El dispositivo codificador puede implementarse en un sistema codificador.

5

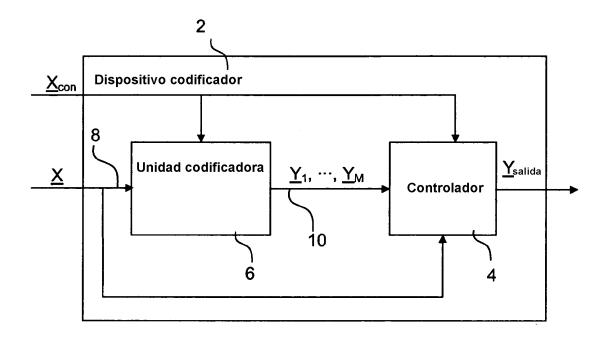

- La figura 1 muestra una realización de un dispositivo codificador según la presente invención. El dispositivo codificador 2 comprende un controlador 4 y una unidad codificadora 6. La señal de entrada X al dispositivo codificador es una señal de entrada digitalizada y preferiblemente transformada. Preferiblemente, la señal de entrada X ha sido transformada utilizando MDC, si bien pueden utilizarse otros esquemas de transformación adecuados, tal como DFT, transformadas de ondícula, o la KLT. La señal de entrada X es alimentada a la unidad codificadora 6 sobre la conexión 8, en serie o bien en paralelo. La unidad codificadora 6 está dispuesta para aplicar una serie M de modos a la señal de entrada. Las salidas Y<sub>1</sub>, Y<sub>2</sub>, ..., Y<sub>M</sub> de la unidad codificadora 6 son alimentadas al controlador 4 sobre la conexión 10. Las salidas Y<sub>1</sub>, Y<sub>2</sub>, ..., Y<sub>M</sub> pueden ser alimentadas en serie tal como se muestra la figura 1, o bien en paralelo tal como se muestra en la figura 2, entre la unidad codificadora 6 y el controlador 4.

- 20 En la unidad codificadora 6, los coeficientes de la señal de entrada X son preprocesados opcionalmente en un preprocesador aplanando los coeficientes de la señal de entrada X mediante una envolvente del espectro. La señal preprocesada o aplanada se denomina asimismo la señal residual X<sub>res</sub>. A continuación, la señal preprocesada es codificada y cuantificada de acuerdo con diferentes modos que incluyen el primer modo A y el segundo modo B en la unidad codificadora 6, y las señales de salida son entregadas al controlador 4.

- En una realización preferida, el número de modos es de dos, es decir la unidad codificadora 6 aplica un primer modo A y un segundo modo B a la señal de entrada y alimenta las salidas Y<sub>1</sub> y Y<sub>2</sub> al controlador 4. En otra realización preferida, el número de modos es de tres, es decir la unidad codificadora 6 aplica un primer modo A, un segundo modo B y un tercer modo C a la señal de entrada y alimenta a las salidas Y<sub>1</sub>, Y<sub>2</sub> e Y<sub>3</sub> al controlador 4.

- El número de modos que se aplica es un compromiso entre la calidad de la codificación y la capacidad de codificación de la unidad codificadora 6. En una realización, la aplicación de cuatro modos A, B, C y D ha demostrado ser un compromiso razonable. Con el continuo aumento en la capacidad de codificación, se contemplan un gran número de modos, tal como cinco, seis, siete, ocho, nueve, diez o más.

- El controlador 4 está dispuesto para determinar el modo óptimo de los modos aplicados en la unidad codificadora 6. El controlador 4 procesa las salidas Y<sub>1</sub>, Y<sub>2</sub>, ..., Y<sub>M</sub> y forma salidas procesadas (Y<sub>m,proc</sub>, m =1, ..., m=1, ..., M) a partir de por lo menos una parte de las salidas respectivas. El procesamiento de por lo menos una de las salidas comprende estimar una parte de la señal de entrada a partir de por lo menos una parte de la salida que es procesada. El controlador 4 está dispuesto para determinar un modo óptimo en base a por lo menos una primera salida procesada y una segunda salida procesada.

- El modo óptimo se selecciona como aquel que minimiza un criterio de selección, por ejemplo un criterio de selección 40 predefinido. En una realización, el modo óptimo se selecciona como uno que maximiza un criterio de selección.

- El controlador 4 está adaptado adicionalmente para incluir la salida correspondiente al modo óptimo, por ejemplo la salida  $Y_1$  si el primer modo A es el modo óptimo, en la señal  $Y_{\text{salida}}$  de salida del codificador.

- Preferiblemente, la señal de salida Y<sub>salida</sub> del codificador comprende información sobre el modo óptimo. Alternativamente o en combinación, la señal de salida Y<sub>salida</sub> del codificador puede comprender información sobre el preprocesamiento de la señal de entrada X. La señal de salida Y<sub>salida</sub> del codificador es transmitida a un receptor y reconstruida o descodificada de acuerdo con un libro de códigos de reconstrucción del receptor, preferiblemente de acuerdo con información sobre el modo óptimo y/o el preprocesamiento de la señal de entrada X. Preferiblemente, el libro de códigos de reconstrucción del transmisor y el libro de códigos de reconstrucción del receptor son idénticos.

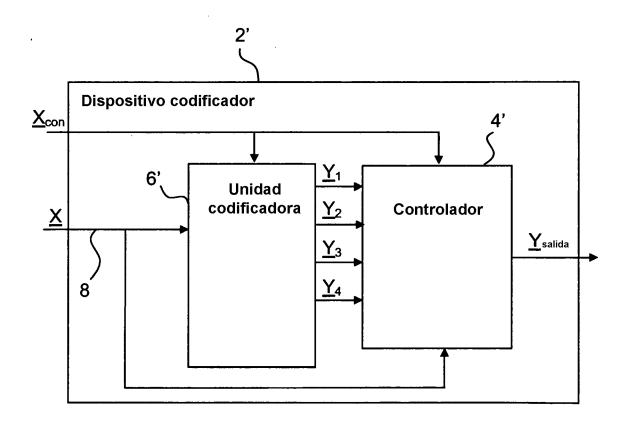

- La figura 2 muestra una realización del dispositivo codificador según la presente invención, en la que el dispositivo codificador está adaptado para aplicar cuatro modos a la señal de entrada X. El dispositivo codificador 2' es similar al dispositivo codificador 2, con componentes similares excepto que las salidas Y<sub>1</sub>-Y<sub>4</sub> son alimentadas en paralelo desde la unidad codificadora 6' al controlador 4', en lugar de en serie como en la figura 1. En la realización mostrada, se aplican cuatro modos diferentes a la señal de entrada.

- En las realizaciones mostradas en las figuras 1 y 2, se aplica una envolvente espectral a la señal de entrada X en un preprocesador dispuesto en la unidad codificadora o dispuesto como una unidad de preprocesador conectada a la unidad codificadora en el dispositivo codificador. En una realización, el preprocesador es una unidad independiente externa al dispositivo codificador, omitiendo por lo tanto la necesidad del preprocesamiento de la señal de entrada X.

La envolvente espectral puede definirse de varias maneras. La envolvente espectral puede ser estática y estar predefinida. Sin embargo, la envolvente espectral puede determinarse o calcularse dinámicamente en base a propiedades de la señal de entrada, en el dominio de frecuencia o bien en el dominio de tiempo. Por consiguiente, las propiedades de la envolvente espectral pueden controlarse en función de una señal de control externa X<sub>con</sub>, por ejemplo desde el controlador externo al dispositivo codificador que se muestra en la figura 1 o desde el controlador 4. En una realización, las propiedades de la envolvente espectral se controlan en base a la respuesta en frecuencia de coeficientes AR. La envolvente espectral puede calcularse agrupando coeficientes MDCT y calculando la energía media en cada grupo. Estos grupos pueden ser de longitud uniforme, o la longitud puede crecer hacia frecuencias elevadas.

La figura 3 muestra una realización de la unidad codificadora 6 de la figura 1. La unidad codificadora 6 comprende un preprocesador opcional 20 y un codificador 22. La señal de entrada X es alimentada al preprocesador 20, que está adaptado para aplicar una envolvente espectral a la señal de entrada X y alimentar la señal residual X<sub>res</sub> al codificador 22. El codificador 22 está adaptado para codificar o cuantificar la señal residual X<sub>res</sub> de acuerdo con M modos diferentes, y enviar en serie las salidas resultantes al controlador, tal como se muestra en la figura 1. El preprocesador 20 y el codificador 22 están controlados mediante la señal de control X<sub>con</sub>. X<sub>con</sub> puede comprender variables de control desde un controlador externo al dispositivo codificador y/o variables de control desde el controlador 4.

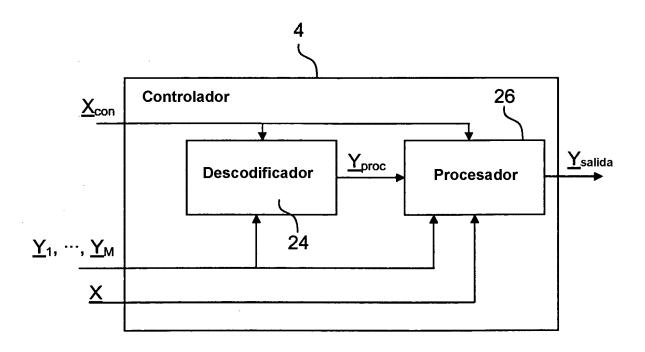

La figura 4 muestra una realización del controlador 4 en la figura 1. El controlador 4 comprende un descodificador 24 y un procesador 26. Las salidas  $Y_1, Y_2, ..., Y_M$  son procesadas en el descodificador 24, que descodifica las salidas  $Y_1, Y_2, ..., Y_M$  de acuerdo con un libro de códigos de reconstrucción del transmisor, que incluye la estimación de por lo menos una parte de la señal de entrada. Las salidas procesadas y descodificadas  $Y_{m,proc}$  para todos los modos M son alimentadas en serie al procesador 26, que está adaptado para determinar el modo óptimo en base a las señales procesadas  $Y_{m,proc}$  para todos los modos o los modos seleccionados y a la señal de entrada X.

En la realización mostrada, el controlador 4 está adaptado para resolver el problema de minimización proporcionado mediante  $m(^*)$  = arg  $min_m$   $D(X, Y_{m,proc})$ , donde  $m(^*)$  es el modo óptimo, D es la distorsión, m = (1,...,M) es el índice sobre M modos,  $X = (x_0,...,x_{N-1})$  es la señal de entrada, e  $Y_{m,proc} = (y_0,...,y_{N-1})_{m,proc}$  es la salida procesada para el modo m

La distorsión D está dada por:

20

25

40

45

$$D = \frac{1}{N} \sum_{n=0}^{N-1} (x_n^* - y_n^*)^{\beta_n} ,$$

30 donde N es el número de coeficientes en la señal de entrada, es decir la dimensión del vector,

$$\begin{aligned} x_0^* &= \left| x_0 \right| \; \text{y} \; x_n^* = (1 - \alpha_n) \left| x_n \right| + \alpha_n x_{n-1}^* \; \text{para todo} \; 1 \leq n < N \; , \\ y_0^* &= \left| y_0 \right| \; \text{e} \; \; y_n^* = (1 - \alpha_n) \left| y_n \right| + \alpha_n y_{n-1}^* \; \text{para todo} \; 1 \leq n < N \; . \\ \\ \alpha_n &= \left( \frac{n}{N} \right)^6 , \; \; \text{y} \quad \beta_n = \begin{cases} 4, \; \text{si} \; \; (x_n^* - y_n^*) < 0 \\ 2, \; \text{si} \; \; (x_n^* - y_n^*) \geq 0 \end{cases} . \end{aligned}$$

En una realización  $\beta_n$  es un valor constante, por ejemplo  $\beta_n$  = 2 para todo n.

Se elimina el signo de los coeficientes vectoriales, y estos son suavizados. En esta realización, el factor de ponderación  $\alpha_n$  aumenta hacia frecuencias elevadas (con N - la dimensión del vector), si bien el factor de ponderación  $\alpha_n$  puede adoptar cualquier forma adecuada.

El "factor de penalizaciónβ n puede añadir penalizaciones mayores para "nuevos" componentes espectrales, y menores para componentes espectrales "perdidos", tal como se indicado anteriormente, o viceversa. Dicho factor de penalización no han sido aplicado anteriormente al campo de la codificación de voz/audio.

Cuando el cálculo del criterio  $D(X,Y_{m,proc})$  para todos los modos M involucra una complejidad demasiado elevada, es posible calcular el criterio para solamente un subconjunto de los modos. A continuación, el criterio para los modos restantes puede interpolarse u omitirse. Esto permite disponer de más modos a elegir que criterios a calcular, y ahorra el cálculo de D e  $Y_{m,proc}$  para los modos para los que se ha interpolado del criterio. En otras palabras: se consigue una alta resolución en la transición de codificación a extensión del ancho de banda (BWE, bandwidth extension), mientras que la complejidad computacional del algoritmo se mantiene a un nivel reducido. El controlador 4 está adaptado adicionalmente para incluir la salida según el modo óptimo en la señal de salida  $Y_{\text{salida}}$  del codificador. La señal de control  $X_{\text{con}}$  puede comprender información acerca de la envolvente espectral aplicada en el

## ES 2 406 422 T3

preprocesador 20. La señal de salida  $Y_{\text{salida}}$  del codificador puede comprender información acerca del modo óptimo y/o información sobre la envolvente espectral aplicada en el preprocesador 20.

Es una ventaja importante de la invención que la determinación del modo óptimo se basa en una comparación de la señal de entrada y la señal de salida descodificada, en lugar de adaptar dinámicamente la codificación o la cuantificación en función de las propiedades de la señal de entrada, tal como propone la técnica anterior.

5

10

15

30

35

40

45

55

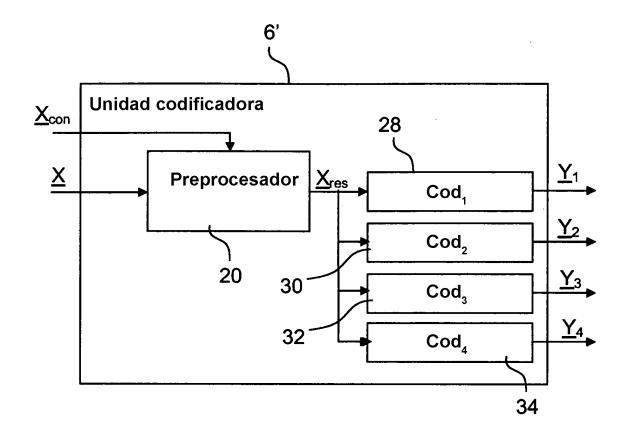

La figura 5 muestra una realización de la unidad codificadora 6' de la figura 2. La unidad codificadora 6' comprende un preprocesador opcional 20 y cuatro codificadores 28, 30, 32 y 34, uno para cada modo. La señal de entrada X es alimentada al preprocesador 20 que está adaptado para aplicar una envolvente espectral a la señal de entrada X, en función de una señal de control  $X_{con}$  y/o de parámetros operativos predefinidos. La señal residual  $X_{res}$  o la señal de entrada X en el caso del preprocesador, es omitida y a continuación alimentada a los codificadores 28, 30, 32 y 34. Los codificadores 28, 30, 32 y 34 codifican la señal residual  $X_{res}$  o una señal de entrada X aplicando cuatro modos diferentes a la señal residual  $X_{res}$  o a la señal de entrada X. Las salidas  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$  son alimentadas en paralelo al controlador. Cada uno de los codificadores 28, 30, 32 y 34 pueden estar adaptados para codificar según una serie de modos y alimentar una serie de salidas en serie al controlador. Por consiguiente, puede utilizarse una combinación de alimentaciones en serie y paralelo de las señales de salida Y al controlador.

En la realización mostrada, los codificadores 28, 30, 32 y 34 funcionan de acuerdo con parámetros operativos predefinidos, si bien el funcionamiento de los codificadores 28, 30, 32 y 34 puede controlarse dinámicamente mediante la señal de control  $X_{con}$ .

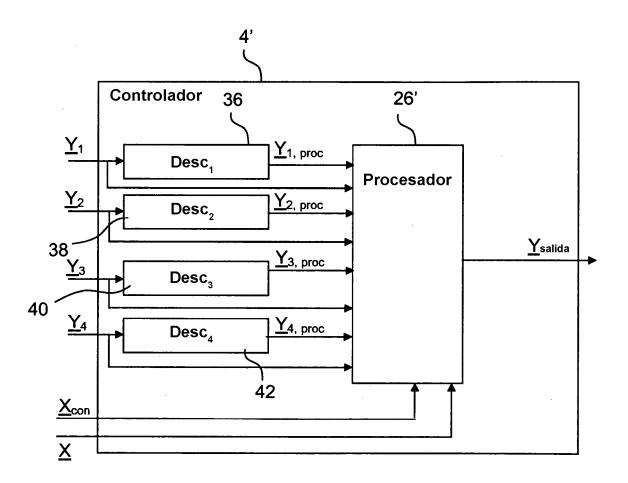

La figura 6 muestra una realización del controlador 4' de la figura 2. El controlador 4' es similar al controlador 4 descrito en relación con la figura 4, excepto en que se dispone un descodificador 36, 38, 40, 42 para cada salida Y<sub>1</sub>, Y<sub>2</sub>, Y<sub>3</sub>, Y<sub>4</sub>, de manera que las salidas son procesadas o descodificadas en paralelo, y no en serie como el controlador 4. El controlador 4' comprende adicionalmente un procesador 26' que está adaptado para determinar el modo óptimo en base a las señales procesadas Y<sub>m,proc</sub> para todos los modos o los modos seleccionados, y a la señal de entrada X. Los descodificadores 36, 38, 40, 42 procesan o descodifican las salidas Y<sub>1</sub>, Y<sub>2</sub>, Y<sub>3</sub>, Y<sub>4</sub> de acuerdo con un libro de códigos de reconstrucción del transmisor. Los descodificadores 36, 38, 40, 42 pueden estar adaptados cada uno de ellos para descodificar una serie de salidas que son alimentadas en serie a los descodificadores 36, 38, 40, 42.

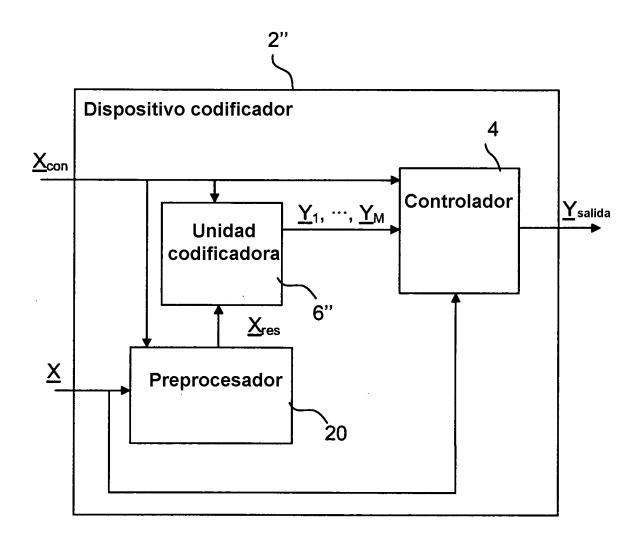

La figura 7 muestra una realización del dispositivo codificador acorde con la invención. En el dispositivo codificador 2", la señal de entrada X es preprocesada con una envolvente espectral y la señal residual  $X_{res}$  es alimentada a la unidad codificadora 6".

La figura 8 muestra un ejemplo de cuatro modos diferentes A, B, C y D. Cuando se aplica el primer modo A en uno de los dispositivos codificadores 2, 2', 2", toda la señal de entrada, opcionalmente preprocesada, es cuantificada tal como se muestra con la línea continua, de manera que los bits disponibles están expandidos sobre todas las dimensiones 0 a N - 1. En el segundo modo B, los bits disponibles se utilizan para la cuantificación de las tres primeras cuartas partes del vector, tal como se muestra mediante la línea continua, y las dimensiones o coeficientes restantes indicados mediante la línea de trazos, es decir las frecuencias correspondientes a la parte no cuantificada del vector, han de ser reconstruidas de acuerdo con un libro de códigos de reconstrucción. En el tercer modo C, los bits disponibles se utilizan para la cuantificación de la primera mitad del vector, y la mitad restante, es decir las frecuencias correspondientes a la parte no cuantificada del vector, han de ser reconstruidas o estimadas utilizando extensión del ancho de banda, es decir de acuerdo con un libro de códigos de reconstrucción. En el cuarto modo D, todos los bits son utilizados para la cuantificación de la primera cuarta parte del vector, y las dimensiones restantes son reconstruidas.

En general, reduciendo el presupuesto de bits la preferencia de los modos va desde cuantificar una parte mayor del espectro hacia una parte menor del espectro (con la secuencia de modos A -> D de la figura 8) dado que la percepción humana es más sensible a errores de estructura fina en las zonas de baja frecuencia. Si hay suficientes bits disponibles, y las zonas de baja frecuencia se cuantifican con resolución suficiente, los modos preferidos en el ejemplo anterior serán A y B. Aumentando la autosimilaridad de la señal, la preferencia va desde codificar una gran parte del espectro a una parte menor del mismo (A -> D en el ejemplo de la figura 8), dado que el proceso de reconstrucción introduce menos artefactos.

Examinando todos los modos, el dispositivo codificador equilibra entre cuantificación de alta resolución de las zonas de baja frecuencia e introducción de artefactos en zonas de alta frecuencia, mejorando la calidad de la señal codificada.

Las figuras 9 y 10 muestran realizaciones del método para codificar una señal de entrada en un sistema codificador, según la presente invención. Los métodos 100, 100' comprenden una etapa 102 de aplicación de un primer modo a la señal de entrada X o al residuo de la señal de entrada, para formar una primera salida. El método comprende adicionalmente una etapa 104 de aplicación de un segundo modo a la señal de entrada o al residuo de la señal de entrada, para formar una segunda salida. Las etapas 102 y 104 pueden llevarse a cabo en paralelo tal como en la figura 9, o en serie tal como en la figura 10. Pueden aplicarse modos adicionales en paralelo o en serie. Las etapas

102 y 104 comprenden partes de cuantificación de la señal de entrada o de la señal residual de la señal de entrada, es decir la cuantificación de una primera parte de la señal de entrada para el primer modo y la cuantificación de una segunda parte de la señal de entrada para el segundo modo.

Tras la aplicación de los modos o durante la misma, el método 100, 100' avanza a la etapa 105 de formación de una primera salida procesada a partir de por lo menos una parte de la primera salida, y una segunda salida procesada a partir de por lo menos una parte de la segunda salida, en el que la formación de una segunda salida procesada comprende la estimación de una parte de la señal de entrada a partir de por lo menos una parte de la segunda salida. A continuación, en la etapa 106 se determina un modo activo en base a la primera salida procesada y a la segunda salida procesada. En las realizaciones mostradas, la etapa 106 comprende resolver el problema de minimización dado por m(\*) = arg min $_m$   $D(X,Y_{m,proc})$ , donde m(\*) es el modo óptimo, D en la distorsión, y D en la distorsión, y D0 es el índice sobre D10 nuevos (D10 es el metodo óptimo, D20 en la distorsión, y D30 es el índice sobre D30 nuevos (D31 es el metodo óptimo, D31 es el índice sobre D32 en esta realización ).

[0069]  $X=(x_0,...,x_{N-1})$  es la señal de entrada e  $Y_{m,proc}=(y_0,...,y_{N-1})_{m,proc}$  es la salida procesada para el modo m. La señal residual  $X_{res}$  de la señal de entrada puede sustituir a la señal de entrada X.

La distorsión D está dada por:

5

10

15

25

30

$$D = \frac{1}{N} \sum_{n=0}^{N-1} (x_n^* - y_n^*)^{\beta_n} ,$$

donde N es el número de coeficientes en la señal de entrada, es decir la dimensión del vector,

$$x_0^\star = \left| x_0 \right| \text{ y } x_n^\star = (1 - \alpha_n) \left| x_n \right| + \alpha_n x_{n-1}^\star \text{ para todo } 1 \leq n < N$$

,

$$y_0^* = |y_0| \in y_n^* = (1 - \alpha_n)|y_n| + \alpha_n y_{n-1}^*$$

para todo  $1 \le n < N$ .

$$\alpha_{n} = \left(\frac{n}{N}\right)^{6}, \quad y \quad \beta_{n} = \begin{cases} 4, \text{ si } (x_{n}^{*} - y_{n}^{*}) < 0\\ 2, \text{ si } (x_{n}^{*} - y_{n}^{*}) \ge 0 \end{cases}$$

Tras la determinación del modo óptimo en la etapa 106, el método 100, 100' avanza a la etapa 108 de selección de la salida acorde con el modo óptimo. La etapa 108 comprende transmitir o indicar información acerca del modo seleccionado junto con la transmisión de la señal de salida seleccionada.

El método según la presente invención puede aplicarse a cada trama de la señal de entrada o a una cierta frecuencia, por ejemplo el método puede aplicarse a cada décima trama y el modo óptimo aplicarse a las tramas hasta la siguiente determinación del modo óptimo.

El esquema multimodo acorde con la presente invención, mediante cuantificación residual, ofrece una calidad mejorada en los esquemas de codificación de audio por transformadas. La mejora procede de la selección del modo óptimo, para las características presentes de velocidad binaria y fuente de entrada.

Se realizaron simulaciones con la envolvente del espectro y el residuo comprimido de la figura 11, los modos acordes con la figura 8, y fuentes de banda ancha. La tabla 1 y la tabla 2 proporcionan estadísticas de la selección de modo con la velocidad binaria y el tipo de fuente (voz - varón alemán y música - castañuelas).

La tabla 3 muestra la mejora global de la calidad del esquema multimodo en comparación con las soluciones convencionales.

Tabla 1: voz – varón alemán

|         | Modo A | Modo B | Modo C | Modo D |

|---------|--------|--------|--------|--------|

| 12kb/s  | 4,8%   | 14,6%  | 11,3%  | 69,4%  |

| 22 kb/s | 16,7%  | 7,9%   | 26,3%  | 49,2%  |

| 32 kb/s | 15,2%  | 16,7%  | 51,8%  | 16,4%  |

Tabla 2: música - castañuelas

|         | Modo A | Modo B | Modo C | Modo D |

|---------|--------|--------|--------|--------|

| 12 kb/s | 3,4%   | 4,2%   | 6,3%   | 86,1%  |

| 22 kb/s | 3,6%   | 24,5%  | 35,7%  | 36,2%  |

| 32 kb/s | 3,2%   | 55,7%  | 36,9%  | 4,2%   |

Tabla 3: resultados, WB-PESQ según ITU-T Rec, P.862,2

|        | Esquema multimodo | Cuantificar espectro completo | Cuantificar la mitad inferior y reconstruir la mitad superior del espectro |

|--------|-------------------|-------------------------------|----------------------------------------------------------------------------|

| 12kb/s | 3,528             | 3,387                         | 3,399                                                                      |

| 22kb/s | 3,819             | 3,592                         | 3,739                                                                      |

| 32kb/s | 3,876             | 3,775                         | 3,864                                                                      |

El libro de códigos de reconstrucción del transmisor y el receptor puede generarse a partir de los coeficientes espectrales en las zonas cuantificadas del espectro. Normalmente, los algoritmos de cuantificación distribuirán el presupuesto total de bits disponible para solamente un subconjunto de los coeficientes en las zonas cuantificadas. Normalmente, los coeficientes restantes se ponen a cero o bien se aproximan mediante algún otro algoritmo, por ejemplo, algoritmos de relleno de ruido. Para los libros de códigos de reconstrucción esto abre varias alternativas sobre cómo construir el libro de códigos de reconstrucción. Los coeficientes en las zonas cuantificadas del espectro que no reciben ningún bit pueden omitirse en el libro de códigos de reconstrucción, pueden ponerse a cero o bien puede utilizarse su valor estimado.

Los coeficientes espectrales recibidos de este modo no necesariamente se utilizan directamente para reconstruir zonas de alta frecuencia, sino que pueden procesarse para crear un libro de códigos de reconstrucción. Un ejemplo de un proceso de este tipo consiste en dos etapas: 1) Compresión del diez por ciento superior de los coeficientes con los valores absolutos mayores. Los 0,1 N coeficientes con el mayor valor absoluto se configuran al máximo valor absoluto de los coeficientes restantes. 2) Atenuación global de energía (solamente se retiene el 70% del nivel inicial).

La atenuación del vector en el libro de códigos de reconstrucción conduce habitualmente a una pérdida de energía en la parte de alta frecuencia del espectro. En el descodificador, esto puede compensarse con un filtro de compensación de inclinación de la forma

$$H(z) = 1 - \mu \cdot z^{-1}$$

,

donde  $\mu$  puede tener cualquier valor adecuado, por ejemplo  $\mu$  = 0,4.

Una forma alternativa de un filtro que compensa la pérdida de alta frecuencia es

$$H(z) = \alpha \cdot z^{-1} - \beta + \alpha \cdot z^{+1},$$

donde por ejemplo  $\alpha = 0.0825 \text{ y } \beta = 0.5825.$

5

10

15

20

30

Estos filtros de compensación de inclinación pueden combinarse con filtros posteriores convencionales formantes o de tono.

En el lado del receptor, el descodificador obtiene la información de modo a partir de la información de modo incluida en la señal recibida, definiendo de esa manera qué partes del espectro de la señal de entrada han sido cuantificadas en el descodificador y cuáles deberán ser reconstruidas. La parte cuantificada del espectro se utiliza directamente. A continuación, se genera el libro de códigos de reconstrucción tal como se ha explicado anteriormente, y se utiliza para poblar las partes no cuantificadas del espectro. A continuación pueden distinguirse dos situaciones: a) la zona extendida es mayor que el libro de códigos de reconstrucción, b) la zona extendida es menor que el libro de códigos de reconstrucción hasta que todo el espectro está poblado. Para el caso b) simplemente se trunca el libro de códigos de reconstrucción.

Volviendo al ejemplo de la figura 8, solamente 1/3 del libro de códigos de reconstrucción se utiliza para el modo B, para el modo C el libro de códigos de reconstrucción ajusta exactamente, y para el modo D el libro de códigos de reconstrucción ha de repetirse dos veces. En este caso, asumimos que los coeficientes en las zonas cuantificadas que no reciben bits para la cuantificación están incluidos en el libro de códigos de reconstrucción.

# ES 2 406 422 T3

Puede aplicarse el filtro opcional de compensación de inclinación y finalmente se impone la envolvente espectral sobre todo el espectro además de otras etapas de procesamiento opcionales, por ejemplo filtros posteriores, sin relación con la presente invención.

Debe observarse que además de las realizaciones ejemplares de la invención mostradas en los dibujos adjuntos, la invención puede realizarse en formas diferentes y no deberá interpretarse que está limitada a las realizaciones expuestas en la presente memoria.

El alcance de la presente invención está definido mediante las reivindicaciones adjuntas.

#### REIVINDICACIONES

- 1. Método para codificar una señal de entrada en un sistema codificador, en el que el método comprende las etapas de:

- aplicar (102) un primer modo de codificación a la señal de entrada (X), cuantificando una primera parte de la señal de entrada hasta un umbral de cuantificación que caracteriza el primer modo de codificación para formar una primera señal de salida (Y<sub>1</sub>)

- aplicar (104) un segundo modo de codificación a la señal de entrada (X), cuantificando una segunda parte de la señal de entrada hasta un umbral de cuantificación que caracteriza el segundo modo de codificación para formar una segunda señal de salida (Y<sub>2</sub>);

- formar (105) una primera salida procesada (Y<sub>1,proc</sub>) a partir de por lo menos una parte de la primera señal de salida (Y<sub>1</sub>), y una segunda salida procesada (Y<sub>2,proc</sub>) a partir de por lo menos una parte de la segunda señal de salida (Y<sub>2</sub>), en el que la formación de la segunda salida procesada comprende estimar una parte de la señal de entrada a partir de por lo menos una parte de la segunda señal de salida (Y<sub>2</sub>), reconstruyendo la parte de la señal de entrada por encima del umbral de cuantificación que caracteriza el segundo modo de codificación, utilizando extensión del ancho de banda;

- determinar (106) un modo óptimo de codificación en base a la primera salida procesada (Y<sub>1,proc</sub>) y a la segunda salida procesada (Y<sub>2,proc</sub>), y sobre un criterio de selección calculado a partir de la señal de entrada y las salidas procesadas, en el que el criterio de selección está definido como un problema de minimización dado como:

$$m^{(\bullet)} = \arg\min_{m} D(\underline{X}, \underline{Y}_{m,proc}),$$

- donde m(\*) es el modo óptimo m de codificación, D es la distorsión, m = (1,...,M) es el índice sobre M modos o m es el índice sobre un subconjunto de M modos, X =  $(x_0,...,x_{N-1})$  es la señal de entrada, e  $Y_{m,proc} = (y_0,...,y_{N-1})_{m,proc}$  es la salida procesada para el modo m, donde N es el número de coeficientes en la señal de entrada, y

- seleccionar (108) la señal de salida (Y<sub>1</sub>, Y<sub>2</sub>) de acuerdo con el modo óptimo de codificación.

30

- 2. Método según la reivindicación 1, en el que se aplican M > 2 modos en la señal de entrada para formar M señales de salida.

- 3. Método según cualquiera de las reivindicaciones precedentes, en el que la distorsión D para por lo menos un modo de codificación está dada por:

$$D = \frac{1}{N} \sum_{n=0}^{N-1} (x_n^* - y_n^*)^{\beta_n} ,$$

$$x_0^* = |x_0| \text{ y } x_n^* = (1 - \alpha_n)|x_n| + \alpha_n x_{n-1}^* \text{ para todo } 1 \le n < N ,$$

$$y_0^* = |y_0| \text{ e } y_n^* = (1 - \alpha_n)|y_n| + \alpha_n y_{n-1}^* \text{ para todo } 1 \le n < N .$$

$$\alpha_n = \left(\frac{n}{N}\right)^6, \text{ y } \beta_n = \begin{cases} 4, \text{ si } (x_n^* - y_n^*) < 0 \\ 2, \text{ si } (x_n^* - y_n^*) \ge 0 \end{cases} .$$

4. Método según cualquiera de las reivindicaciones precedentes, en el que la distorsión D para por lo menos un modo de codificación está dada por:

$$D = \frac{1}{N_L} \sum_{n \in L} (x_n^* - y_n^*)^{\mu_n} ,$$

donde N es el número de coeficientes en la señal de entrada, I es un subconjunto de enteros desde 0 hasta N-1, N<sub>1</sub> es el número de elementos en I.

$$x_0^* = |x_0| \text{ y } x_n^* = (1 - \alpha_n)|x_n| + \alpha_n x_{n-1}^* \text{ para todo } 1 \le n < N$$

,

$$y_0^* = |y_0| = y_n^* = (1 - \alpha_n)|y_n| + \alpha_n y_{n-1}^*$$

para todo  $1 \le n < N$ .

$$\alpha_{n} = \left(\frac{n}{N}\right)^{6}, \text{ y } \beta_{n} = \begin{cases} 4, \text{ si } (x_{n}^{*} - y_{n}^{*}) < 0\\ 2, \text{ si } (x_{n}^{*} - y_{n}^{*}) \ge 0 \end{cases}.$$

- 5. Método según cualquiera de las reivindicaciones precedentes, en el que la distorsión D se estima para por lo menos un modo de codificación.

- 6. Método según cualquiera de las reivindicaciones precedentes, que comprende además la etapa de transmitir información acerca del modo óptimo de codificación.

10

15

20

- 7. Dispositivo codificador (2, 2', 2')' que comprende un controlador (4, 4') y una unidad codificadora (6, 6') conectada al controlador (4, 4'), estando dispuesta la unidad codificadora para aplicar un primer modo de codificación a una señal de entrada (X), cuantificando una primera parte de la señal de entrada hasta un umbral de cuantificación que caracteriza el primer modo de codificación para formar la primera señal de salida (Y<sub>1</sub>), y estando dispuesta para aplicar un segundo modo de codificación a la señal de entrada (X), cuantificando una segunda parte de la señal de entrada hasta un umbral de cuantificación que caracteriza al segundo modo de codificación, para formar una segunda señal de salida (Y2), en el que el controlador (4, 4') está dispuesto para formar una primera salida procesada (Y<sub>1,proc</sub>) a partir de por lo menos una parte de la primera señal de salida (Y<sub>1</sub>), y una segunda salida procesada (Y<sub>2,proc</sub>) a partir de por lo menos una parte de la segunda señal de salida (Y<sub>2</sub>), en el que la formación de la segunda salida procesada comprende estimar una parte de la señal de entrada a partir de por lo menos una parte de la segunda señal de salida (Y2), reconstruyendo la parte de la señal de entrada que está por encima del umbral de cuantificación que caracteriza el segundo modo de codificación, utilizando extensión del ancho de banda, y determinar un modo óptimo de codificación en base a la primera salida procesada y la segunda salida procesada, y sobre un criterio de selección calculado a partir de la señal de entrada y las salidas procesadas, en el que el criterio de selección está definido como un problema de minimización dado por: m(\*) = arg min<sub>m</sub>  $D(X,Y_{m,proc})$ , donde m(\*) es el modo óptimo m de codificación, D es la distorsión, m=(1,...,M) es el índice sobre M modos o m es el índice sobre un subconjunto de M modos,  $X = (x_0, ..., x_{N-1})$  en la señal de entrada, e  $Y_{m,proc} = (y_0, ..., y_{N-1})_{m,proc}$  es la salida procesada para el modo m donde N es el número de coeficientes en la señal de entrada, y seleccionar la señal de salida (Y<sub>1</sub>, Y<sub>2</sub>) de acuerdo con el modo óptimo.

- 8. Dispositivo codificador según la reivindicación 7, en el que la unidad codificadora (6) comprende un codificador (22) que está adaptado para aplicar en serie el primer modo de codificación y el segundo modo de codificación y enviar en serie la primera señal de salida y la segunda señal de salida al controlador (4, 4') sobre una primera conexión (10).

- 9. Dispositivo codificador según la reivindicación 7, en el que la unidad codificadora (6) comprende un primer codificador (28) y un segundo codificador (30), en el que el primer codificador está dispuesto para aplicar el primer modo de codificación y para enviar la primera señal de salida al controlador sobre una primera conexión y el segundo codificador está dispuesto para aplicar el segundo modo de codificación y para enviar la segunda señal de salida al controlador sobre una segunda conexión.

- 35 10. Dispositivo codificador según cualquiera de las reivindicaciones 7 a 9, en el que el controlador (4, 4') comprende por lo menos un descodificador dispuesto para formar la primera salida procesada y la segunda salida procesada de acuerdo con el primer y el segundo modos de codificación respectivamente, y un procesador dispuesto para determinar el modo óptimo de codificación en base a un criterio de selección calculado a partir de la señal de entrada y la primera salida procesada y la segunda salida procesada.

- 40 11. Sistema codificador que comprende un dispositivo codificador según cualquiera de las reivindicaciones 7 a 10.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5

Fig. 6

**Fig. 7**

Fig. 8

Fig. 9

Fig. 10