# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 409 266

51 Int. Cl.:

**H03D 7/14** (2006.01) **H03D 7/16** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Fecha de presentación y número de la solicitud europea: 03.08.2009 E 09791103 (6)

- 97 Fecha y número de publicación de la concesión europea: 10.04.2013 EP 2316162

- (54) Título: Convertidor elevador y convertidor reductor con una transconductancia conmutada y una máscara de oscilador local

- (30) Prioridad:

01.08.2008 US 185048

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **26.06.2013**

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) Attn: International IP Administration 5775 Morehouse Drive San Diego, California 92121-1714, US

(72) Inventor/es:

**ASURI, BHUSHAN, SHANTI**

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

# **DESCRIPCIÓN**

Convertidor elevador y convertidor reductor con una transconductancia conmutada y una máscara de oscilador local

## **Antecedentes**

## I. Campo

10

15

20

25

30

35

40

45

50

55

5 La presente divulgación se refiere, en general, al campo de la electrónica y, más concretamente, a un convertidor elevador y a un convertidor reductor para un dispositivo de comunicación inalámbrica.

#### H. Antecedentes

Un dispositivo de comunicación inalámbrica, como por ejemplo un teléfono celular, típicamente incluye un transmisor y un receptor para dar soporte a una comunicación bidireccional. La transmisión puede elevar en frecuencia unas señales en banda base de salida en fase (I) y en cuadratura (Q) con unas señales del oscilador local (LO) de transmisión (TX) I y Q para obtener una señal de salida de radiofrecuencia (RF) que sea más apropiada para la transmisión a través de un canal inalámbrico. El receptor puede recibir una señal de entrada de RF por medio del canal inalámbrico y puede reducir en frecuencia la señal de entrada de RF con las señales del LO de recepción (RX) de las señales I y Q para obtener unas señales en banda base de entrada I y Q. Es conveniente llevar a cabo una elevación de frecuencia y una reducción de frecuencia de forma que se obtenga un rendimiento satisfactorio.

El documento US2006/135109 se refiere a un circuito mezclador que comprende un nodo de entrada para la recepción de una señal de entrada, un primer nodo de salida y un segundo nodo de salida, un medio de conversión de tensión a corriente y un medio de conmutación acoplados operativamente entre sí y al nodo de entrada, estando dispuestos el primer nodo de salida y el segundo nodo de salida para generar una señal de entrada mixta en el primer nodo de salida y en el segundo nodo de salida en respuesta a una señal del oscilador. El documento WO2007/053365 se refiere a un circuito de modulación para su uso en un transmisor de radiofrecuencia que incluye un circuito de oscilador local configurado para generar una o más señales del oscilador local a una frecuencia deseada y con un ciclo de trabajo al, o aproximadamente, veinticinco por ciento, y un modulador configurado para generar una o más señales moduladas sensibles a las una o más señales del oscilador local y una o más señales de información en banda base. MEI-LING YEH ET AL: "Mezclador de Conversión en Elevación en Cuadratura de 5 -GHz de Baja Tensión para un Transmisor Inalámbrico" ["A Low-Voltage T5-GHz Quadrature Up-Conversion Mixer for Wireless Transmitter", 2006 INTERNATIONAL CONFERENCE ON COMMUNICATIONS CIRCUITS AND SYSTEMS: GUILIN, GUANGXI, CHINA, 25 - 28 DE JUNIO DE 2006, IEEE SERVICE CENTER, PISCATAWAY, NJ. 1 de junio de 2006 (01-06-2006), páginas 2618-2622, XP031010962, ISBN: 978-0-7803-9584-8 divulga un mezclador de conversión en elevación en cuadratura de 5-GHZ de baja tensión para Transmisor Inalámbrico el cual implementa un híbrido "carrera de rata" de banda ancha de microondas de un elemento concentrado en miniatura y una red de desplazamiento de RLC para el LO y el diseño de cuarto de IF, respectivamente. El documento WO2007/063093 divulga un circuito de modulación para su uso en un transmisor de radiofrecuencia que incluye un circuito de oscilador local configurado para generar una o más señales de oscilador local a una frecuencia deseada con un ciclo de trabajo en o aproximadamente un veinticinco por ciento, y un modulador configurado para generar una o más señales moduladas sensibles a las una o más señales del oscilador local y una o más señales de información en banda base. El documento JP2005197836 divulga un convertidor de frecuencia utilizado para el receptor y el transmisor el cual está configurado mediante el apilamiento de una pluralidad de circuitos de conmutación de configuración de entrada / salida de equilibro doble. Así mismo, el convertidor de frecuencia está combinado con la pluralidad de circuitos de conmutación y un divisor de ¼ de frecuencia. Esto se ofrece como una solución al problema de la provisión de un receptor, el cual presenta un desplazamiento de cc reducido y la provisión de un receptor y un transmisor en el que el diseño de los dispositivos periféricos requeridos para la conversión de frecuencia es fácil y puede llevarse a cabo una reducción del consumo de energía.

#### <u>Sumario</u>

En la presente memoria, con referencia a las reivindicaciones adjuntas, se describen un convertidor elevador y un convertidor reductor que ofrecen un rendimiento satisfactorio. En un aspecto, el convertidor elevador y el convertidor reductor pueden, cada uno, implementar una transconductancia conmutada y / o una máscara de LO. La transconductancia g<sub>m</sub>. de un transistor es una función de una corriente de salida frente a una tensión de entrada y está relacionada con la ganancia del transistor. La transconductancia conmutada se refiere a la conmutación de la transconductancia de los transistores en banda base o de RF entre baja y alta con los transistores del LO acoplados a las fuentes de los transistores en banda base o de RF. Para un convertidor elevador, los transistores en banda base reciben señales en banda base I y Q y proporcionan una señal elevada en frecuencia. Para un convertidor reductor, los transistores de RF reciben una señal de entrada de RF y proporcionan unas señales en banda base I y Q reducidas en frecuencia. Los transistores del LO conmutan la transconductancia de los transistores en banda base o de RF y llevan a cabo una función de mezcla. La máscara del LO se refiere a las señales del LO de resincronización con una señal de VCO procedente de un oscilador con voltaje controlado (VCO), de manera que la transconductancia de los transistores en banda base o de RF es conmutada durante las transiciones de la señal del

VCO. La transconductancia conmutada y la máscara del LO pueden proporcionar diversas ventajas de acuerdo con lo descrito más adelante.

En un diseño, el convertidor elevador incluye unos primero, segundo, y tercer conjuntos de transistores. El primer conjunto de transistores recibe las señales en banda base y proporciona una señal elevada en frecuencia. El segundo conjunto de transistores se acopla a las fuentes de los transistores del primer conjunto y conmuta la transconductancia de los transistores del primer conjunto en base a las señales del LO del TX . El tercer conjunto de transistores se acopla al segundo conjunto de transistores y habilita e inhabilita los transistores del segundo conjunto en base a la señal del VCO del TX . Los transistores de los segundo y tercer conjuntos pueden operar como conmutadores.

En un diseño, el convertidor reductor incluye unos primero, segundo y tercer conjuntos de transistores. El primer conjunto de transistores recibe una señal modulada y proporciona unas señales en banda base. El segundo conjunto de transistores se acopla a las fuentes de los transistores del primer conjunto y conmuta la transconductancia de los transistores del primer conjunto en base a las señales del LO de RX. El tercer conjunto de transistores se acopla al segundo conjunto de transistores y habilita e inhabilita los transistores del segundo conjunto en base a una señal del VCO de RX. Los transistores del segundo y tercer conjunto pueden operar como conmutadores.

A continuación se describen con mayor detalle diversos aspectos y elementos característicos de la presente invención.

## Breve descripción de los dibujos

5

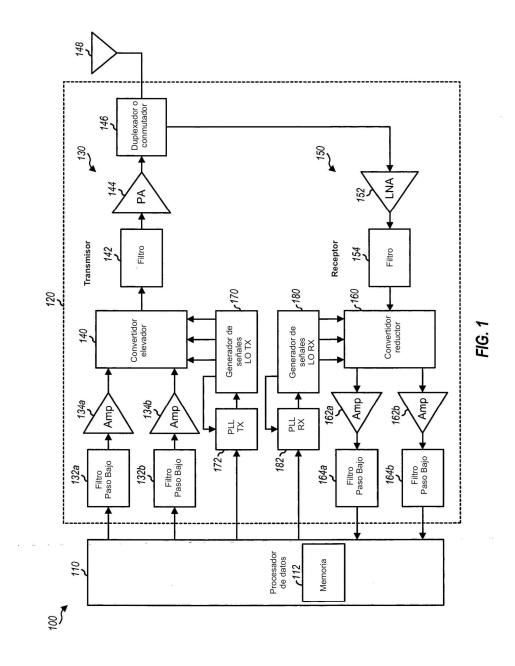

- La FIG. 1 muestra un diagrama de bloques de un dispositivo de comunicación inalámbrica.

- 20 La FIG. 2 muestra un diagrama de bloques de un generador de señales del LO.

- La FIG. 3 muestra un diagrama de temporización de señales I y Q y una señal del VCO.

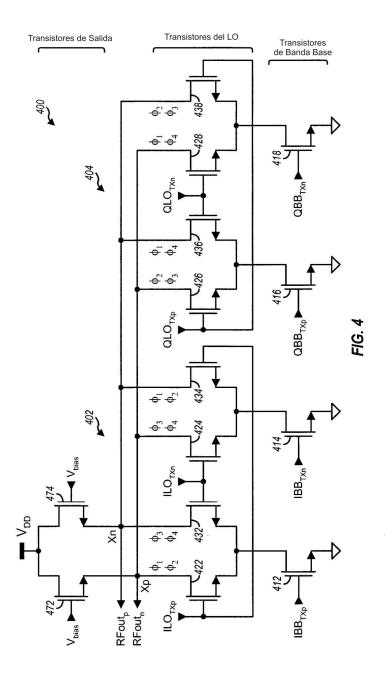

- La Fig. 4 muestra un convertidor elevador con unos mezcladores con célula de Gilbert.

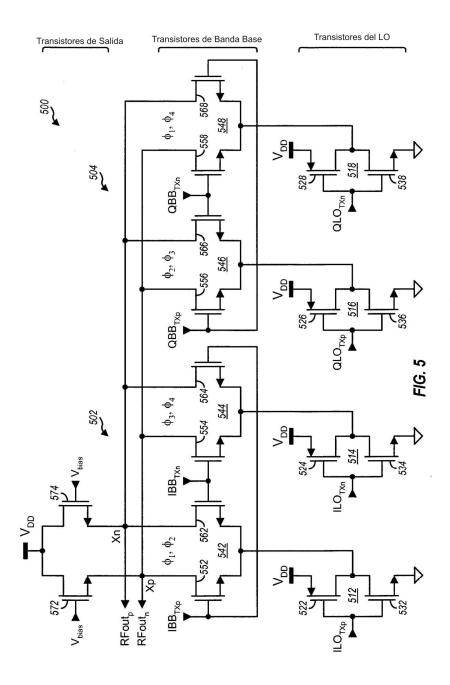

- LA Fig. 5 muestra un convertidor elevador con una transconductancia conmutada.

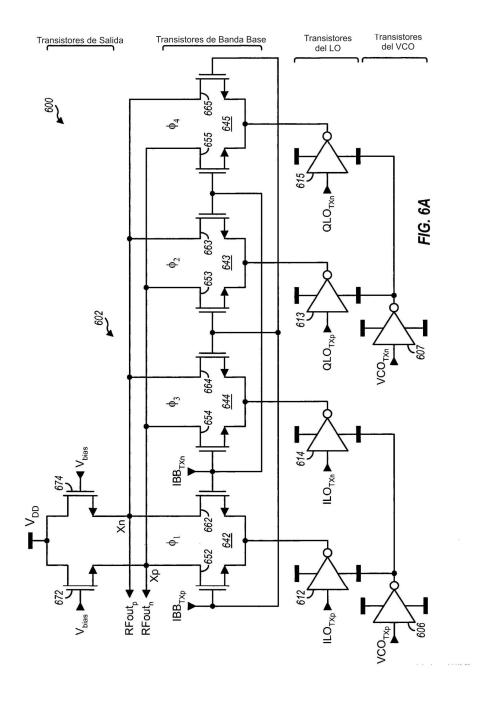

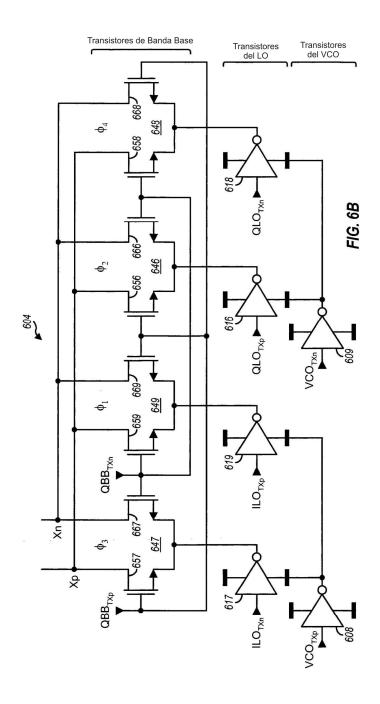

- Las FIGS. 6A y 6B muestran un convertidor elevador con una transconductancia conmutada y una máscara del LO.

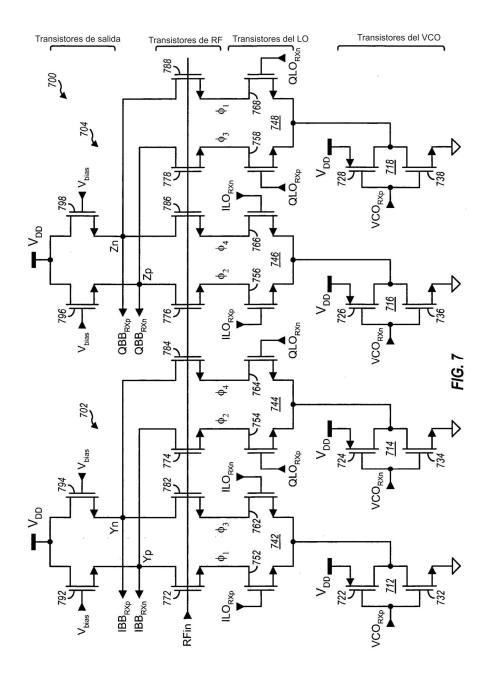

- 25 La FIG. 7 muestra un convertidor reductor con una transconductancia conmutada y una máscara del LO.

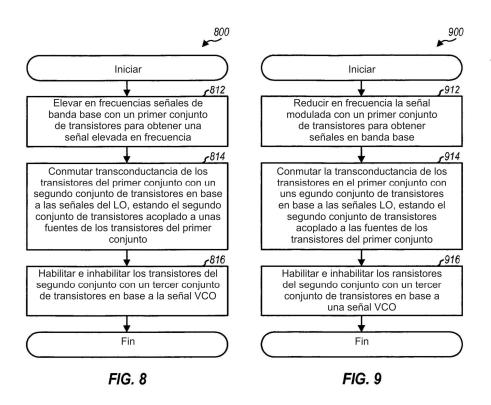

- La FIG. 8 muestra un procedimiento para llevar a cabo la conversión de elevación en frecuencia.

- La FIG. 9 muestra un procedimiento para llevar a cabo la conversión de reducción en frecuencia.

## Descripción detallada

40

45

El convertidor elevador y el convertidor reductor descritos en la presente memoria pueden ser utilizados para diversos dispositivos y sistemas de comunicación. Por ejemplo, el convertidor elevador y el convertidor reductor pueden ser utilizados en dispositivos de comunicación inalámbrica, teléfonos celulares, asistentes personales digitales (PDAs), dispositivos de mano, módems inalámbricos, computadoras portátiles, teléfonos inalámbricos, dispositivos Bluetooth, etc. Por razones de claridad, a continuación se describe el empleo del convertidor elevador y del convertidor reductor para un dispositivo de comunicación inalámbrica, el cual puede ser un teléfono celular o algún otro dispositivo.

La **FIG. 1** muestra un diagrama de bloques de un dispositivo 100 de comunicación inalámbrica. En este diseño, el dispositivo 100 inalámbrico incluye un procesador 110 de datos que incorpora una memoria 112 para almacenar datos y códigos de programa y un transceptor 120. El transceptor 120 incluye un transmisor 130 y un receptor 150 que soportan una comunicación bidireccional. En general, el dispositivo 100 inalámbrico puede incluir un número indeterminado de transmisores y un número indeterminado de receptores para un número indeterminado de sistemas de comunicación y de bandas de frecuencia.

Un transmisor o un receptor pueden ser implementados con una arquitectura superheterodina o una arquitectura de conversión directa. En la arquitectura superheterodina, una señal es convertida de frecuencia entre RF y banda base en múltiples etapas, por ejemplo, de RF a una frecuencia intermedia (IF) en una etapa y, a continuación, de la IF a banda base en otra etapa para un receptor. En la arquitectura de conversión directa, la cual se designa también como arquitectura de cero-IF una señal es convertida de frecuencia entre RF y banda base en una etapa. Las arquitecturas superheterodina y de conversión directa pueden utilizar diferentes bloques de circuito y / o presentar condicionamientos diferentes. En el diseño mostrado en la FIG. 1, el transmisor 130 y el receptor 150 son implementados con la arquitectura de conversión directa.

50 En la trayectoria de transmisión, el procesador 110 de datos procesa los datos que deben ser transmitidos y proporciona unas señales de salida analógicas I y Q al transmisor 130. Dentro del transmisor 130, unos filtros paso

bajo 132a y 132b filtran las señales de salida analógicas I y Q, respectivamente, para suprimir las imágenes provocadas por la conversión anterior digital - analógica. Los amplificadores (Amp) 134a y 134b amplifican las señales procedentes de los filtros de paso bajo 132a y 132b, respectivamente, y proporcionan unas señales en banda base I y Q. Un convertidor elevador 140 recibe las señales en banda base I y Q. las señales del TX del LO I y Q procedentes de un generador 170 de señales del LO, y posiblemente una señal del VCO del TX procedente de un VCO dentro del generador 170 de señales del LO. El convertidor elevador 140 convierte en elevación de frecuencia las señales en banda base I y Q con las señales del LO del TX I y Q y proporciona una señal elevada en frecuencia. El filtro 142 filtra la señal elevada en frecuencia para eliminar las imágenes provocadas por la conversión en elevación de frecuencia y eliminar el ruido en una banda de frecuencia de recepción. El filtro 142 puede ser un filtro de onda acústica de superficie (OAS) o algún otro tipo de filtro. Un amplificador de potencia (PA) 144 amplifica la señal procedente del filtro 142 para obtener el nivel de potencia deseado y proporciona una señal de RF de transmisión. La señal de RF de transmisión es encaminada a través de un duplexor o conmutador 146 y transmitida por medio de una antena 148.

En la trayectoria de recepción, la antena 148 recibe las señales transmitidas por las estaciones de base y proporciona una señal de RF recibida, la cual es encaminada a través del duplexor o conmutador 146 y suministrada a un amplificador de bajo ruido (LNA) 152. La señal de RF recibida es amplificada por el LNA 152 y filtrada por un filtro 154 para obtener una señal de entrada de RF. Un convertidor reductor 160 recibe la señal de entrada de RF, las señales del LO de RX I y Q procedentes de un generador 180 de señales del LO, y posiblemente una señal del VCO de RX procedente de un VCO situado dentro del generador 180 de señales del LO. El convertidor reductor 160 reduce en frecuencia la señal de entrada de RF con las señales del LO de RX I y Q y proporciona unas señales en banda base I y Q. Las señales en banda base I y Q son amplificadas por los amplificadores 162a y 162b y después filtradas por los filtros paso bajo 164a y 164b para obtener las señales de entrada analógicas I y Q, las cuales son suministradas al procesador 110 de datos.

El generador 170 de señales del LO genera las señales del TX I y Q utilizadas para la conversión de elevación en frecuencia. El generador 180 de señales del LO genera las señales del LO de RX I y Q utilizadas para la conversión de reducción de frecuencia. Cada señal del LO es una señal periódica con una frecuencia fundamental concreta. Las señales del LO del TX y las señales del LO de RX pueden tener (i) la misma frecuencia si el sistema utiliza la duplexación por división de tiempo (TDD) o (ii) frecuencias diferentes si el sistema utiliza la duplexación por división de frecuencia (FDD). Un bucle de enganche en fase (PLL) 172 recibe la información de temporización procedente del procesador 110 de datos y la señal del VCO del TX procedente del generador 170 de señales del LO. El PLL 172 genera una señal de control utilizada para ajustar la frecuencia y / o la fase de las señales del LO del TX procedente del generador 170 de señales del LO. De manera similar, un PLL 182 recibe la información de temporización procedente del procesador 110 de datos y la señal del VCO de RX procedente del generador 180 de señales del LO. El PLL 182 genera una señal de control utilizada para ajustar la frecuencia y / o la fase de las señales del LO de RX procedentes del generador 180 de señales del LO de RX procedentes del generador 180 de señales del LO.

La FIG. 1 muestra un diseño de transceptor ejemplar. En general, el acondicionamiento de las señales en un transmisor y en un receptor se puede llevar a cabo mediante una o más etapas de amplificador, filtro, convertidor elevador, convertidor reductor, etc. Estos bloques de circuito pueden ser dispuestos de manera diferente de la configuración mostrada en la FIG. 1. Así mismo, pueden, también, ser utilizados otros bloques de circuito no mostrados en la FIG. 1 para acondicionar las señales en el transmisor y el receptor. Algunos bloques de circuito de la FIG. 1 pueden, así mismo, ser omitidos. Por ejemplo, el filtro 142 puede ser omitido, y la salida del convertidor elevador 140 puede ser acoplada directamente al amplificador 144 de potencia. En otro ejemplo, el filtro 154 pude ser omitido y la salida del LNA 152 puede ser acoplada directamente al convertidor reductor 160. Todo o una porción del transceptor 120 puede ser implementada en uno o más circuitos integrados analógicos (ICs), ICs de RF (RFICs), ICs de señales combinadas, etc.

La **FIG. 2** muestra un diagrama de bloques de un diseño de un generador 170 de señales del LO de la FIG. 1. Dentro del generador 170 de señales del LO, un VCO 210 recibe una señal de control V<sub>CTRL</sub> procedente del PLL 172 y genera la señal del VCO del TX a una frecuencia de salida deseada, tal y como se determina por la señal de control. Un divisor / separador 220 recibe y divide la señal en frecuencia del VCO del TX (por ejemplo, mediante un factor de dos) y genera (i) una señal del LO del TX I diferencial compuesta por una señal, del LO del TX I, ILO<sub>TXp</sub>, y una señal del LO del TX Q diferencial compuesta por una señal del LO del TX Q no invertida, QLO<sub>Txp</sub>, y una señal del LO del TX Q invertida, QLO<sub>Txn</sub>. Las señales ILO<sub>Txp</sub>, QLO<sub>Txp</sub>, ILO<sub>Txn</sub> y QLO<sub>TXn</sub> están 90° fuera de fase unas respecto de otras, tal y como se muestra en la FIG. 2. En general, el divisor / separador 220 puede incluir un número indeterminado de divisores de frecuencia y un número indeterminado de separadores de señal. Una memoria intermedia 230 recibe, así mismo, la señal del VCO del TX y genera una señal del VCO del TX diferencial compuesta por una señal del VCO del TX no invertida, VCO<sub>Txp</sub>, y una señal del VCO del TX invertida, VCO<sub>Txp</sub>. Las señales VCO<sub>Txp</sub> y VCO<sub>Txn</sub> están 180° fuera de fase una respecto de otra. En la descripción de la presente memoria, el subíndice "p" indica una señal no invertida / positiva y el subíndice "n" indica una señal invertida / negativa. Una señal diferencial está compuesta por una señal no invertida y por una señal invertida (por ejemplo, las señales ILO<sub>Txp</sub> e ILO<sub>Txn</sub>), y una señal complementaria está compuesta por la señal invertida y por la señal no invertida (por ejemplo, las señales ILO<sub>Txn</sub> e ILO<sub>Txn</sub>).

La **FIG. 3** muestra un diagrama de temporización ejemplar de las señales del LO del TX I y Q y la señal del VCO del TX . La señal del VCO del TX puede ser dividida por un factor de dos en frecuencia para generar las señales del LO del TX . Las señales del LO del TX I y Q tendrían entonces una frecuencia que es la mitad de la frecuencia de la señal del VCO del TX . Las señales  $VCO_{Txp}$  y  $VCO_{Txn}$  se muestran en la parte superior de la FIG. 3. Las señales  $QLO_{Txp}$  y  $QLO_{Txn}$ . Cada ciclo de las señales del LO del TX puede ser dividido en cuatro fases. Una primera fase  $\phi_1$  abarca el periodo de tiempo desde el flanco de subida de la señal  $ILO_{Txp}$  en el tiempo  $T_1$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el flanco de subida de la señal  $QLO_{Txp}$  hasta el

10

15

20

25

30

35

40

45

50

55

60

El convertidor elevador 140 y el convertidor reductor 160 de la FIG. 1 pueden ser implementados con diversos diseños, los cuales pueden ofrecer diferentes prestaciones en términos de ruido y linealidad. El convertidor elevador 140 y el convertidor reductor 160 pueden, así mismo, ser implementados con diseños de una sola salida o con diseños diferenciales. A continuación se describen varios diseños diferenciales del convertidor elevador 140 y del convertidor reductor 160.

La **FIG. 4** muestra un diagrama esquemático de un convertidor y elevador 400 implementado con mezcladores con célula de Gilbert. El convertidor elevador 400 incluye un mezclador 402 de la señal I y un mezclador 404 de la señal Q, y un sumador implementado con unos nodos Xp y Xn adicionadores de corriente. El mezclador 402 de la señal I convierte una señal elevada en frecuencia en banda base I diferencial (compuesta por las señales  $IBB_{TXp}$ ) e  $IBB_{TXn}$ ) con la señal del LO I diferencial (compuesta por las señales  $ILO_{TXp}$  e  $ILO_{TXp}$ ) y proporciona una señal elevada en frecuencia I diferencial en los nodos Xp y Xn. Un mezclador 404 de señal Q eleva en frecuencia una señal en banda base Q diferencial (compuesta por las señales  $QBB_{TXp}$ ) con la señal del LO Q diferencial (compuesta por las señales  $QLO_{TXp}$ ) y  $QLO_{TXp}$ ) y proporciona una señal elevada en frecuencia Q diferencial en los nodos Xp y Xn. Las señales elevadas en frecuencia I y Q diferenciales son sumadas en los nodos Xp y Xn para obtener una señal elevada en frecuencia diferencial compuesta por las señales de RFout<sub>p</sub> y RFout<sub>p</sub>.

Dentro del mezclador 402 de la señal I, los transistores 412 y 414 de semiconductor de óxido de metal del canal N (NMOS) presentan sus fuentes acopladas a la tierra del circuito y sus puertas, que reciben, respectivamente, las señales  $IBB_{TXp}$  y  $IBB_{TXn}$ . Los términos "transistor" y "dispositivo" a menudo se utilizan de manera intercambiable, por ejemplo, los transistores MOS a menudo son designados como dispositivos MOS. Los transistores 422 y 432 NMOS presentan sus fuentes acopladas al sumidero del transistor 412 NMOS, recibiendo sus puertas las señales  $ILO_{TXp}$  e  $ILO_{TXn}$ , respectivamente, y sus sumideros acoplados a los nodos Xp y Xn, respectivamente. Los transistores 424 y 434 NMOS presentan sus fuentes acopladas al sumidero del transistor 414 NMOS, recibiendo sus puertas las señales  $ILO_{TXp}$ , respectivamente, y sus sumideros acoplados a los nodos Xp y Xn, respectivamente. Los transistores 472 y 474 NMOS presentan sus fuentes acopladas a los nodos Xp y Xn, respectivamente, recibiendo sus puertas una tensión de polarización,  $V_{bias}$ , y sus sumideros acoplados a un suministro de energía,  $V_{DD}$ .

Dentro del mezclador 404 de señal Q, los transistores 416 y 418 NMOS presentan sus fuentes acopladas a la tierra del circuito y recibiendo sus puertas las señales QBB $_{TXp}$  y QBB $_{TXn}$ , respectivamente. Los transistores 426 y 436 NMOS presentan sus fuentes acopladas al sumidero del transistor 416 NMOS, recibiendo sus puertas las señales QLO $_{TXp}$  y QLO $_{TXn}$ , respectivamente, y sus sumideros acoplados a los nodos, respectivamente, Xp y Xn. Los transistores 428 y 438 NMOS presentan sus fuentes acopladas al sumidero del transistor 418 NMOS, recibiendo sus puertas las señales QLO $_{TXp}$  y QLO $_{TXp}$ , respectivamente, y sus sumideros acoplados a los nodos Xp y Xn, respectivamente.

Los transistores 412 a 418 NMOS son transistores en banda base que suministran una amplificación para las señales en banda base I y Q. Los transistores 422 a 438 NMOS son transistores del LO que son operados en cascodo y llevan a cabo la orientación de la corriente para conseguir la función de mezcla para la elevación en frecuencia. Los transistores 472 y 474 NMOS son transistores de salida que proporcionan el accionamiento de la señal para la señal elevada en frecuencia.

El convertidor elevador 400 opera como sigue. Las fases en las cuales cada transistor del LO es habilitado se muestran en la FIG. 4. Durante la primera fase  $\phi_1$ , los transistores 422, 434, 436 y 428 NMOS son habilitados, la corriente es dirigida a través o bien del transistor 422 o del 434 NMOS dependiendo de la señal IBB, y la corriente es dirigida a través de o bien el transistor 436 o del 428 NMOS dependiendo de la señal QBB. Durante la segunda fase  $\phi_2$ , los transistores 422, 434, 426 y 438 son habilitados, la corriente es dirigida a través de o bien del transistor 422 o del 424 NMOS dependiendo de la señal IBB, y la corriente es dirigida a través de o bien el transistor 426 o el 438 dependiendo de la señal QBB. Durante la tercera fase  $\phi_3$ , los transistores 432, 424, 426 y 438 NMOS son habilitados, la corriente es dirigida a través de o bien el transistor 432 o 424 NMOS dependiendo de la señal IBB, y la corriente es dirigida a través de o bien el transistor 426 o el 438 NMOS dependiendo de la señal QBB. Durante la cuarta fase  $\phi_4$ , los transistores 432, 424, 436 y 428 NMOS son habilitados, la corriente es dirigida a través de o bien los transistores 432 o 424 NMOS dependiendo de la señal QBB.

El convertidor elevador 400 con los mezcladores con célula de Gilbert presenta varios inconvenientes. En primer lugar, los mezcladores con célula de Gilbert pueden generar un nivel de ruido relativamente alto en la banda de frecuencia de recepción, lo cual puede, a continuación, requerir el uso de un filtro OAS para el filtro 142 de la FIG. 1 para atenuar el ruido. En segundo lugar, el espacio de cabecera de tensión para los transistores en banda base en la FIG. 4 puede resultar restringido, especialmente con una tensión de suministro baja, dado que parte del margen de sobrecarga de la tensión se utiliza para los transistores del LO. En tercer lugar se puede necesitar el acoplamiento de los condensadores para acoplar en alterna las señales del LO del TX I y Q a los transistores del LO. Así mismo, la tensión de polarización para los transistores del LO puede requerir que sean ajustados de forma cuidadosa con el fin de obtener un rendimiento satisfactorio. En cuarto lugar, una elevada corriente puede ser consumida por cada mezclador. En quinto lugar, un factor de modulación *m* puede estar limitado por las exigencias de la linealidad en la trayectoria de transmisión global. El factor de modulación limitado puede traducirse en una potencia de salida inferior y en una relación señal / ruido (SRN) para la señal elevada en frecuencia.

10

15

20

25

40

La **FIG. 5** muestra un diagrama esquemático de un diseño de un convertidor elevador 500 con transconductancia conmutada. El convertidor elevador 500 puede ser utilizado para el convertidor elevador 140 de la FIG. 1 e incluye un mezclador 502 de señal I, un mezclador 504 de señal Q, y un sumador implementado con unos nodos Xp y Xn de adición de la corriente.

Dentro del mezclador 502 de señal I, está implementado un inversor 512 con un transistor 522 metal - óxido-semiconductor de canal P (PMOS) y un transistor 532 NMOS y recibe la señal ILO<sub>TXp</sub>. Los transistores 522 y 532 MOS presentan sus puertas acopladas entre sí y formando la entrada del inversor, sus sumideros acoplados entre sí formando la salida del inversor, y sus fuentes acopladas, a unos suministros de potencia superior e inferior, respectivamente. El suministro de potencia inferior está acoplado a un circuito de tierra en la FIG. 5 pero puede ser alguna otra tensión o señal. Los transistores 552 y 562 NMOS forman un par diferencial 542 y tienen sus fuentes acopladas a la salida del inversor 512, recibiendo sus puertas las señales IBB<sub>TXp</sub>, e IBB<sub>TXp</sub>, respectivamente, y sus sumideros acoplados a los nodos Xp y Xn, respectivamente. Un inversor 514 está implementado con un transistor 524 PMOS y un transistor 534 NMOS y recibe la señal TLO<sub>TXp</sub>. Los transistores 554 y 564 NMOS forman un par diferencial 544 y tienen sus fuentes acopladas a la salida del inversor 514, recibiendo sus puertas las señales IBB<sub>TXp</sub>, respectivamente, y sus sumideros están acoplados a los nodos Xp y Xn, respectivamente. Los transistores 572 y 574 NMOS tienen sus fuentes acopladas a los nodos Xp y Xn, recibiendo sus puertas la tensión de polarización  $V_{bias}$  y estando sus sumideros acoplados al suministro de potencia.

Dentro del mezclador 504 Q, un inversor 516 está implementado con un transistor 526 PMOS y un transistor 536 NMOS y recibe la señal QLO<sub>TXp</sub>. Los transistores 556 y 566 NMOS forman un par diferencial 546 y tienen sus fuentes acopladas a la salida del inversor 516, recibiendo sus puertas las señales QBB<sub>TXp</sub> y QBB<sub>TXn</sub>, respectivamente, y sus sumideros están acoplados a los nodos Xp y Xn, respectivamente. Un inversor 518 está implementado con un transistor 528 PMOS y un transistor 538 NMOS y recibe la señal QLO<sub>TXn</sub>. Los transistores 558 y 568 NMOS forman un par diferencial 548 y tienen sus fuentes acopladas a la salida del inversor 518, recibiendo sus puertas las señales QBB<sub>TXn</sub> y QBB<sub>TXp</sub>, respectivamente, y sus sumideros acoplados a los nodos Xp y Xn, respectivamente.

En el convertidor elevador 500, los pares diferenciales 542 y 544 accionan la salida del convertidor elevador con la polaridad opuesta de la señal en banda base I. La señal del LO del TX I selecciona el par diferencial 542 para la mitad del ciclo del LO (por ejemplo, las fases  $\phi_1$  y  $\phi_2$ ) y selecciona el par diferencial 544 para la otra mitad del ciclo del LO (por ejemplo las fases  $\phi_3$  y  $\phi_4$ ). De manera similar, los pares diferenciales 546 y 548 accionan la salida del convertidor elevador con una polaridad opuesta de la señal en banda base Q. La señal del LO del TX Q selecciona el par diferencial 546 para la mitad del ciclo del LO (por ejemplo, las fases  $\phi_2$  y  $\phi_3$ ) y selecciona el par diferencial 548 para la otra mitad del ciclo del LO (por ejemplo, las fases  $\phi_1$  y  $\phi_4$ ).

- Los transistores 522 a 538 MOS son los transistores del LO que llevan a cabo la conmutación de la transconductancia para conseguir la función de mezcla para la conversión elevada en frecuencia. Los transistores 552 a 568 NMOS son transistores en banda base que proporcionan la amplificación para las señales en banda base I y Q. Los transistores 572 y 574 NMOS son transistores de salida que suministran el accionamiento de la señal para la señal elevada en frecuencia.

- La FIG. 5 muestra un diseño específico con los transistores en banda base, los transistores del LO, y los transistores del VCO acoplados de una manera específica y con las señales específicas aplicadas a estos transistores. La señal elevada en frecuencia deseada puede, así mismo, ser obtenida con otras disposiciones de los transistores en banda base, los transistores del LO, y los transistores del VCO y / o mediante la aplicación de las señales a estos transistores de otras maneras.

- El convertidor elevador 500 opera como sigue. Cada uno de los cuatro inversores 512 a 518 pueden ser habilitados o inhabilitados en base a su señal del LO. Cada inversor está acoplado a un par diferencial respectivo y lleva a cabo la conmutación de transconductancia del par diferencial. La transconductancia del par diferencial es baja cuando la salida del inversor es alta y es alta cuando la salida del inversor es baja. Cada par diferencial con transconductancia alta amplifica su señal en banda base y acciona la salida del convertidor elevador. La función de mezcla se puede

conseguir mediante la conmutación de la transconductancia de pares diferenciales diferentes en diferentes fases de cada ciclo del LO.

El diagrama de temporización mostrado en la FIG. 3 puede ser utilizado para el convertidor elevador 500 de la FIG. 5, durante la primera fase  $\phi_1$  las salidas de los inversores 512 y 518 y son bajas y los transistores 552, 562, 558 y 568 NMOS tienen una elevada transconductancia y accionan la salida del convertidor elevador en base a la señal en banda base I y a la señal en banda base Q complementaria. Durante la segunda fase  $\phi_2$ , las salidas de los inversores 512 y 516 son bajas, y los transistores 552, 562, 556 y 566 NMOS tienen una elevada transconductancia y accionan la salida del convertidor elevador en base a las señales en banda base I y Q. Durante la tercera fase  $\phi_3$  la salida de los inversores 514 y 516 son bajas, y los transistores 554, 564, 556 y 566 NMOS tienen una elevada transconductancia y accionan la salida del convertidor elevador en base a la señal en banda base I complementaria y a la señal en banda base Q. Durante la cuarte fase  $\phi_4$ , la salidas de los inversores 514 y 518 son bajas, y los transistores 554, 564, 558 y 568 NMOS tienen una elevada transconductancia y accionan la salida del convertidor elevada en base a las señales en banda base complementaria I y Q.

5

10

15

20

25

30

35

40

45

60

El convertidor elevador 500 con una transconductancia conmutada presenta varias ventajas. En primer lugar, los transistores del LO están situados en las fuentes de los transistores en banda base (en lugar de los sumideros de los transistores en banda base tal y como se muestra en la FIG. 4). Esto hace posible que los transistores del LO sean operados como conmutadores que pueden ser accionados de raíl a raíl de manera similar a las puertas lógicas. Así mismo, la operación de los transistores del LO como conmutadores (en lugar de cómo transistores cascodo como se muestra en la FIG. 4) se traduce en que no se necesita ningún margen de sobrecarga de tensión para los transistores del LO. Esto proporciona más margen de sobrecarga de tensión para los transistores en banda base, lo cual puede reducir el ruido. Los transistores del LO en el convertidor elevador 500, así mismo, consumen menos energía que los transistores del convertidor elevador 400. En particular, los transistores del LO del convertidor 500 consumen  $I_{DC} \cdot r_{on}$ , donde  $I_{DC}$  es la corriente cuando se activa y  $r_{on}$  es la resistencia aplicada, la cual puede ser muy pequeña para los conmutadores. Así mismo, se puede mostrar que el ruido procedente de los transistores del LO puede ser suprimido, lo cual puede mejorar la calidad de la señal elevada en frecuencia. Así mismo, se pueden suprimir las fugas del LO del modo común a través de la capacitancia  $C_{gd}$  de la puerta al sumidero, lo cual puede ser beneficioso para los diseños de mezclador asimétrico.

Las **FIGS. 6A** y **6B**, muestran un diagrama esquemático de un diseño de un convertidor elevador 600 con una transconductancia conmutada y una máscara del LO. El convertidor elevador 600 puede, así mismo, ser utilizado para el convertidor elevador 140 de la FIG. 1 e incluye un mezclador 602 de señal I mostrado en la FIG. 6A, un mezclador 604 de señal Q mostrado en la FIG. 6B y un sumador implementado con una corriente que adiciona los nodos Xp y Xn mostrados en la FIG. 6A.

Como se muestra en la FIG. 6A el mezclador 602 de señal I incluye los inversores 612 y 614 y los transistores 652, 654, 662 y 664 NMOS que están acoplados de la misma manera que los inversores 512 y 514 y que los transistores 552, 554, 562 y 564 NMOS, respectivamente, para el mezclador 502 de señal I de la FIG. 5. El mezclador 602 de señal I incluye así mismo los inversores 613 y 615 y los transistores 653, 655, 663 y 665 NMOS que están acoplados de manera similar a la de los inversores 612 y 614 y los transistores y 652, 654, 662 y 664 NMOS, respectivamente. Las puertas de los transistores 652, 664, 653 y 665 NMOS reciben la señal IBB<sub>TXp</sub>, y las puertas de los transistores 632, 654, 663 y 655 NMOS reciben la señal IBB<sub>TXn</sub>. Los sumideros de los transistores 652, 654, 663 y 665 NMOS se acoplan al nodo Xp, y los sumideros de los transistores 662, 664, 663 y 665 NMOS se acoplan al nodo Xn.

El mezclador 602 de señal I incluye así mismo los inversores 606 y 607 que reciben la señal del VCO del TX diferencial y habilita e inhabilita los inversores 612 a 618. El inversor 606 incorpora su entrada que recibe la señal VCO<sub>TXp</sub> y su salida acoplada al suministro de potencia inferior de los inversores 612 y 614, los cuales se pueden corresponder con las fuentes de los transistores 532 y 534 NMOS de la FIG. 5. El inversor 607 tiene su entrada que recibe la señal VCO<sub>TXn</sub> y su salida acoplada al suministro de potencia inferior de los inversores 613 y 615. La salida de los inversores 606 y 607 pueden, así mismo, acoplarse al suministro de potencia superior de los inversores 612, 613, 614 y 615, los cuales pueden corresponderse con las fuentes de los transistores 522 a 528 PMOS de la FIG. 5.

Como se muestra en la FIG. 6B, el mezclador 604 de señal Q incluye los inversores 616 y 618 y los transistores 656, 658, 666 y 668 NMOS que están acoplados de la misma manera que los inversores 516 y 518 y que los transistores 556, 558, 566, y 568 NMOS, respectivamente, para el mezclador 504 de señal Q de la FIG. 5. El mezclador 604 de señal Q incluye así mismo los inversores 617 y 619 y los transistores 657, 659, 667 y 669 NMOS que están acoplados de manera similar a los inversores 616 y 618 y que los transistores 656, 658, 666,668 NMOS, respectivamente. Las puertas de los transistores 657, 669, 656 y 668 NMOS reciben la señal QBB<sub>TXp</sub>, y las puertas de los transistores 667, 659, 666 y 658 NMOS reciben la señal QBB<sub>TXn</sub>. Los sumideros de los transistores 657, 659, 656 y 658 NMOS se acoplan al nodo Xp y los sumideros de los transistores 667, 659, 666 y 668 NMOS se acoplan al nodo Xn.

El mezclador 604 de señal Q incluye así mismo los inversores 608 y 609. El inversor 608 tiene su entrada que recibe la señal  $VCO_{Txp}$  y su salida acoplada al suministro de potencia inferior de los inversores 617 y 619. El inversor 609 tiene su entrada que recibe la señal  $VCO_{Txp}$  y su salida acoplada al suministro de potencia inferior de los inversores

616 y 618. Los inversores 606 y 609 pueden, así mismo ser omitidos. En este caso, el inversor 606 de salida de la FIG. 6A puede estar acoplado al suministro de potencia inferior de los inversores 617 y 619, y el inversor 607 de salida puede estar acoplado al suministro de potencia inferior 616 y 618.

Los inversores 606 a 609 incluyen unos transistores del VCO que llevan a cabo la máscara del LO para reducir el ruido. Los inversores 612 a 619 incluyen unos transistores del LO que llevan a cabo la conmutación de la transconductancia para conseguir la función de mezcla para la conversión elevada en frecuencia. Los transistores 652 a 669 NMOS son transistores en banda base que proporcionan una amplificación para las señales en banda base I y Q. Los transistores 672 y 674 NMOS son transistores de salida que están acoplados de la misma manera que los transistores 572 y 574 NMOS, respectivamente, de la FIG. 5 y proporcionan el accionamiento de la señal para la señal elevada en frecuencia.

5

10

15

20

25

30

35

40

45

50

55

El mezclador 602 de señal I incluye los pares diferenciales 642, y 644 y los inversores 612 y 614, los cuales están incluidos en el mezclador 502 de señal I de la FIG. 5. El mezclador 602 de la señal I incluye así mismo los pares diferenciales 643 y 645 y los inversores 613 y 615 que soportan la máscara del LO. De manera similar, el mezclador 604 de señal Q incluye los pares diferenciales 646 y 648 y los inversores 616 y 618, los cuales están incluidos en el mezclador 504 de señal Q de la FIG. 5. El mezclador 604 de señal Q incluye así mismo los pares diferenciales 647 y 649 y los inversores 617 y 619 que soportan la máscara del LO.

Las FIGS. 6A y 6B muestran un diseño específico con los transistores en banda base, los transistores del LO y los transistores del VCO acoplados de manera específica y con unas señales aplicadas a estos transistores. La señal elevada en frecuencia deseada puede, asimismo, ser obtenida con otras disposiciones de los transistores en banda base, los transistores del LO, y los transistores del VCO y / o mediante la aplicación de las señales a estos transistores de otras maneras.

Del diagrama de temporización de la FIG. 3 puede ser utilizado tanto para el mezclador 602 de señal I de la FIG. 6A como para el mezclador 604 de señal Q de la FIG. 6B. El flanco de subida de la señal  $ILO_{Txp}$  puede producirse antes que el flanco de subida de la señal  $VCO_{Txp}$ . De manera similar, el flanco de subida de la señal  $VCO_{Txp}$  puede producirse antes que el flanco de subida de la señal  $VCO_{Txp}$ .

El mezclador 602 de señal I de la FIG. 6B opera como sigue. Para la primera fase φ 1, la transición de subida sobre la señal VCO<sub>TXo</sub> habilita los inversores 612 y 614. Dado que la señal ILO<sub>TXo</sub> es alta y que la señal ILO<sub>TXo</sub> es baja, el par diferencial 642 es habilitado y el par diferencial 644 es inhabilitado. Los transistores 652 y 662 NMOS accionan la salida del convertidor elevador en base a la señal en banda base I. Para la segunda fase φ 2, la transición de subida sobre la señal VCO<sub>TXn</sub> habilita los inversores 613 y 615. Dado que las señal QLO<sub>TXn</sub> es alta y que la señal QLO<sub>TXn</sub> es baja, el par diferencial 643 es habilitado, y el par diferencial 645 es inhabilitado. Los transistores 653 y 663 NMOS accionan la salida del convertidor elevador en base a la señal en banda base I. Para la tercera fase φ 3, la transición de subida sobre la señal VCO<sub>TXp</sub> habilita los transistores 612 y 614. Dado que la señal ILO<sub>TXp</sub> es baja y que la señal ILO<sub>TXn</sub> es alta, el par diferencial 642 es inhabilitado y el par diferencial 644 es habilitado. Los transistores 654 y 664 NMOS accionan la salida del convertidor elevador en base a la señal en banda base I complementaria. Para la cuarta fase  $\phi_4$ , la transición de subida sobre la señal VCO<sub>TXn</sub> habilita los inversores 613 v 615. Dado que la señal QLO<sub>TXo</sub> es baja y que la señal QLO<sub>TXo</sub> es alta, el par diferencial 643 es inhabilitado, y el par diferencial 645 es habilitado. Los transistores 655 y 665 NMOS accionan la salida del convertidor elevador en base a la señal en banda base I complementaria. Los pares diferenciales 642 y 643 son accionados por la señal en banda base I y son habilitados para un ciclo completo del VCO (o una mitad del ciclo del LO). Los pares diferenciales 644 y 645 son accionados por la señal en banda base I complementaria y son habilitados para el siguiente ciclo completo del VCO (o de la siguiente mitad del ciclo del LO).

El mezclador 604 de señal Q de la FIG. 6B opera de manera similar al mezclador 602 de señal I de la FIG. 6A.

Para el convertidor elevador 600 con la máscara del LO, las transiciones sobre la señal VCO son transiciones activas y determinan la fluctuación de fase en la señal elevada en frecuencia. Las señales del LO I y Q pueden ser generadas con un divisor de frecuencias y / o un separador de señales y pueden presentar una cantidad de ruido relativamente grande. Las señales del LO I y Q son de manera eficaz resincronizadas con la señal del VCO. Pares diferenciales diferentes de interés son activados en diferentes transiciones de la señal del VCO. Estas transiciones del VCO determinan el tiempo en el cual los pares diferenciales son activados (y, por tanto, la polaridad es conmutada).

El convertidor elevador 600 con la transconductancia conmutada y con la máscara del LO puede tener todas las ventajas descritas con anterioridad para el convertidor elevador 500 de la FIG. 5. El convertidor elevador 600 puede, así mismo, ofrecer otras ventajas debido a la máscara del LO. En particular, las transiciones activas en el convertidor elevador 600 pueden ser controladas por la señal del VCO. La máscara de las señales del LO con la señal del VCO puede suprimir el ruido procedente del divisor y / o del separador utilizado para generar las señales LO.

Un transmisor de ruido bajo puede ser implementado con el convertidor elevador 600 que presenta un rendimiento de ruido mejorado debido a (i) la supresión del ruido procedente del divisor y del separador utilizado para generar las señales del LO del TX I y Q y (ii) la reducción de la contribución del ruido procedente de los transistores en banda

base de los mezcladores. El rendimiento mejorado del ruido que se consigue con el convertidor elevador 600 puede hacer posible la retirada de un filtro OAS después del convertidor elevador (por ejemplo, el filtro 142 de la FIG. 1).

La FIG. 5 muestra un diseño ejemplar del convertidor elevador 500 con transconductancia conmutada. La FIG. 6 muestra un diseño ejemplar del convertidor elevador 600 con trasconductancia conmutada y máscara del LO. Un convertidor elevador con transconductancia conmutada y máscara del LO puede, así mismo, ser implementado con otros diseños, por ejemplo, disposiciones diferentes de los transistores en banda base, de los transistores del LO y de los transistores del VCO.

5

10

50

55

En general, un convertidor elevador pude incluir unos primero, segundo y tercer conjuntos de transistores. El primer conjunto de transistores puede recibir señales en banda base y suministrar una señal elevada en frecuencia. El segundo conjunto de transistores puede acoplarse a las fuentes del los transistores del primer conjunto y puede conmutar la transconductancia de los transistores del primer conjunto en base a las señales del LO del TX . El tercer conjunto de transistores puede acoplarse al segundo conjunto de transistores y puede habilitar e inhabilitar los transistores del segundo conjunto en base a una señal del VCO del TX . Los transistores de los segundo y tercer conjuntos pueden operar como conmutadores.

15 En un diseño, el primer conjunto de transistores incluye cuatro pares diferenciales. Un primer par diferencial (por ejemplo, el par diferencial 542 o 642) recibe las señales en banda base I invertidas y no invertidas. Un segundo par diferencial (por ejemplo el par diferencial 544 o 644) recibe las señales en banda base I invertidas y no invertidas. Un tercer par diferencial (por ejemplo el par diferencial 546 o 646) recibe las señales en banda base Q no invertidas e invertidas. Un cuarto par diferencial (por ejemplo, el par diferencial 548 o 648) recibe lase señales en banda base Q 20 invertidas y no invertidas. En un diseño, el segundo conjunto de transistores incluye cuatro pares de transistores acoplados como cuatro inversores. Un primer inversor (por ejemplo, el inversor 512 o 612) habilita e inhabilita el primer par diferencial en base a la señal del LO I no invertida. Un segundo inversor (por ejemplo, el inversor 514 o 614) habilita o inhabilita el segundo par diferencial en base a la señal del LO I. Un tercer inversor (por ejemplo el inversor 516 o 616) habilita e inhabilita el tercer par diferencial en base a la señal del LO Q invertida y no invertida. 25 Un cuarto inversor (por ejemplo, el inversor 518 o 618) habilita el inhabilita el cuarto par diferencial en base a una señal del LO Q. En un diseño, el tercer conjunto de transistores incluye dos pares de transistores acoplados como dos inversores. Un inversor (por ejemplo, el inversor 606) habilita e inhabilita los primero y segundo inversores en base a una señal del VCO no invertida. El otro inversor (por ejemplo, el inversor 609) habilita e inhabilita los tercero y cuarto inversores en base a la señal del VCO invertida. Los primero, segundo y tercer conjuntos pueden incluir transistores diferentes y / o adicionales. 30

La **FIG.** 7 muestra un diagrama esquemático de un diseño de un convertidor reductor 700 con transconductancia conmutada y máscara LO. El convertidor reductor 700 puede ser utilizado para el convertidor reductor 160 de la FIG. 1 e incluye un mezclador 702 de señal I y un mezclador 704 de señal Q.

Dentro del mezclador 702 de señal I, está implementado un inversor 712 con un transistor 722 PMOS y un transistor 732 NMOS y recibe una señal VCO<sub>RXp.</sub> Los transistores 752 y 762 NMOS forman un par diferencial 742 y tienen sus 35 fuentes acopladas a la salida del inversor 712 y sus puertas reciben las señales ILO<sub>RXn</sub>, respectivamente. Los transistores 772 y 782 NMOS tienen sus fuentes acopladas a los sumideros de los transistores 752 y 762 NMOS, respectivamente, recibiendo sus puertas la señal de entrada de RF, RFin, y sus sumideros están acoplados a los nodos Yp e Yn, respectivamente. Los transistores 792 y 794 NMOS tienen sus fuentes acopladas a los nodos 40 Yp e Yn, respectivamente, recibiendo sus puertas una tensión de polarización V<sub>bias</sub>, y sus sumideros están acoplados al suministro de potencia superior. Un inversor 714 es implementado con un transistor 724 PMOS y un transistor 734 NMOS y recibe una señal VCO<sub>RXn</sub>. Los transistores 754 y 764 NMOS forman un par diferencial 744 y tienen sus fuentes acopladas a la salida del inversor 714 recibiendo sus puertas las señales QLO<sub>RXD</sub> y QLO<sub>RXD</sub>, respectivamente. Los transistores 774 y 784 NMOS tienen sus fuentes acopladas a los sumideros de los transistores 754 y 764 NMOS, respectivamente, recibiendo sus puertas la señal de entrada de RF y sus sumideros acoplados a 45 los nodos Yp e Yn, respectivamente.

Dentro del mezclador 704 de señal Q, un inversor 716 es implementado con un transistor 726 PMOS y un transistor 736 NMOS y recibe la señal VCO<sub>RXn</sub>. Los transistores 756 y 766 NMOS forman un par diferencial 746 y tienen sus fuentes acopladas a la salida del inversor 716 recibiendo sus puertas las señales ILO<sub>RXp</sub> e ILO<sub>RXn</sub>, respectivamente. Los transistores 776 y 786 NMOS tienen sus fuentes acopladas a los sumideros de los transistores 756 y 766 NMOS, respectivamente, recibiendo sus puertas la señal de RFinf, y sus sumideros acoplados a los nodos Zp y Zn, respectivamente. Los transistores 796 y 798 NMOS tienen sus fuentes acopladas a los nodos Zp y Zn, respectivamente, recibiendo sus puertas la tensión  $V_{\text{bias}}$ , y sus sumideros acoplados al suministro de potencia superior. Un inversor 718 está implementado con un transistor 728 PMOS y un transistor 738 NMOS y recibe la señal  $VCO_{\text{RXp}}$ . Los transistores 758 y 768 NMOS forman un par diferencial 748 y tienen sus fuentes acopladas a la salida del inversor 718 y recibiendo sus puertas las señales  $QLO_{\text{RXp}}$  y  $QLO_{\text{RXn}}$ , respectivamente. Los transistores 778 y 788 NMOS tienen sus fuentes acopladas los sumideros de los transistores 755 y 768 NMOS, respectivamente, recibiendo sus puertas la señal de entrada de RF, y sus sumideros están acoplados a los nodos Zp y Zn, respectivamente.

Los transistores 722 a 738 MOS son transistores del VCO que llevan a cabo la máscara del LO para reducir el ruido. Los transistores 752 a 768 NMOS son transistores del LO que llevan a cabo la conmutación de la transconductancia parra conseguir la función de mezcla para la conversión en reducción de frecuencia. Los transistores 772 a 788 NMOS son transistores de RF que proporciona amplificación para la señal de entrada de RF. Los transistores 792 a 798 NMOS son transistores de salida que proporcionan el accionamiento de la señal para la señal reducida en frecuencia.

5

10

30

35

40

45

50

55

La FIG. 7 muestra un diseño específico con los transistores de RF, los transistores del LO y los transistores del VCO acoplados de una manera específica y con unas señales específicas acopladas a estos transistores. Las señales en banda base deseadas pueden, así mismo, obtenerse con otras disposiciones de los transistores de RF, los transistores del LO y los transistores del VCO y / o mediante la aplicación de las señales a estos transistores de otras maneras.

El diagrama de temporización de la FIG. 3 puede ser utilizado para el convertidor reductor 700, aunque con las señales  $VCO_{TXp}$ ,  $VCO_{TXn}$ ,  $ILO_{TXp}$ , I

El convertidor reductor 700 opera como sigue. Para la primera fase  $\phi_1$  la transición de subida sobre la señal VCO<sub>RXp</sub> 15 habilita los invesorres 712 y 718. Dado que las señales ILO<sub>RXp</sub> y QLO<sub>RXn</sub> son altas y que las señales ILO<sub>RXn</sub> y QLO<sub>RXp</sub> son bajas, los transistores 752 y 768 NMOS son habilitados y accionan los nodos Yp y Zn, respectivamente y los transistores 762 y 758 NMOS son inhabilitados. Para la segunda fase  $\phi_2$ , la transición de subida sobre la señal VCO<sub>RXn</sub> habilita los inversores 714 y 716. Dado que las señales ILO<sub>RXp</sub> y QLO<sub>RXp</sub> son altas y que las señales ILO<sub>RXn</sub> 20 y QLO<sub>RXn</sub> son bajas, los transistores 754 y 756 NMOS son habilitados y accionan los nodos Yp y Zp, respectivamente, y los transistores 764 y 766 NMOS son inhabilitados. Para la tercera fase 6 3 la transición de subida sobre la señal VCO<sub>RXp</sub> habilita los inversores 712 y 718. Dado que las señales ILO<sub>RXp</sub> y QLO<sub>RXp</sub> son altas y que las señales ILO<sub>RXp</sub> y QLO<sub>RXn</sub> son bajas, los transistores 762 y 758 NMOS son habilitados y accionan los nodos Yn y Zp, respectivamente y los transistores 752 y 768 NMOS son inhabilitados. Para la cuarta fáse  $\phi_4$  la transición de subida para la señal VCO<sub>RXn</sub> habilita los inversores 714 y 716. Dado que las señales ILO<sub>RXn</sub> y QLO<sub>RXn</sub> son altas y que las 25 señales ILO<sub>RXp</sub> y QLO<sub>RXp</sub> son bajas, los transistores 764 y 766 NMOS son habilitados y accionan los nodos Yn y Zn, respectivamente, y los transistores 754 y 756 NMOS son inhabilitados.

Un receptor de ruido bajo puede ser implementado con el convertidor reductor 700 que presente un rendimiento de ruido mejorado debido a (i) la supresión de ruido procedente del divisor y del separador utilizados para generar las señales del LO del RX I y Q y (ii) la reducción de la contribución de ruido procedente de los transistores RF de los mezcladores.

La FIG. 7 muestra un diseño ejemplar del convertidor reductor 700 con transconductancia conmutada y de la máscara del LO. Un convertidor reductor con transconductancia conmutada y / o máscara del LO pueden, así mismo, ser implementados con otros diseños, por ejemplo otras disposiciones de los transistores de RF de los transistores del LO y de los transistores del VCO.

En general, un convertidor reductor puede incluir unos primero, segundo y tercer conjuntos de transistores. El primer conjunto de transistores puede recibir una señal modulada y suministrar señales en banda base. El segundo conjunto de transistores se puede acoplar a las fuentes de transistores del primer conjunto y puede conmutar la transconductancia de los transistores del primer conjunto en base a las señales del LO del RX. El tercer conjunto de transistores puede acoplarse al segundo conjunto de transistores y puede habilitar e inhabilitar los transistores del segundo conjunto en base a la señal del VCO del RX.

En un diseño, el segundo conjunto de transistores incluye cuatro pares diferenciales. Un primer par diferencial (por ejemplo, el par diferencial 742) recibe unas señales del LO I no invertidas e invertidas. Un segundo par diferencial, (por ejemplo, el par diferencial 744) recibe unas señales del LO I no invertidas e invertidas. Un tercer par diferencial (por ejemplo, el par diferencial 746) recibe las señales del LO I no invertidas e invertidas. Un cuarto par diferencial (por ejemplo el par diferencial 748) recibe las señales del LO Q no invertidas e invertidas. En un diseño, el primer conjunto de transistores incluye cuatro pares de transistores (por ejemplo, los transistores 772 a 788) que tienen sus fuentes acopladas a los sumideros de los cuatro pares diferenciales. En un diseño, el tercer conjunto de transistores incluye cuatro pares de transistores acoplados como cuatro inversores (por ejemplo, los inversores 712 a 718). Estos cuatro inversos habilitan e inhabilitan los cuatro pares diferenciales en base a las señales del VCO no invertidas e invertidas. Los primero, segundo y tercer conjuntos pueden incluir transistores diferentes y / o adicionales.

La **FIG.** 8 muestra un diseño de un procedimiento 800 para llevar a cabo la conversión en elevación de frecuencia. Las señales en banda base pueden ser elevadas de frecuencia con un primer conjunto de transistores para obtener una señal elevada en frecuencia (bloque 812). El primer conjunto de transistores puede comprender los transistores en banda base de la FIG. 5 o de las FIGS. 6A y 6B. La señal modulada puede ser elevada en frecuencia directamente de banda base a RF (para una arquitectura de reducción en frecuencia directa) o de banda base o IF (para una arquitectura superheterodina).

La transconductancia de los transistores del primer conjunto puede ser conmutada con un segundo conjunto de transistores en base a las señales del LO, siendo acoplado el segundo conjunto de transistores a las fuentes de los transistores del primer conjunto (bloque 814). El segundo conjunto de transistores puede comprender los transistores del LO de la FIG. 5 o de las FIGS. 6A y 6B. Los transistores del segundo conjunto pueden ser habilitados o inhabilitados con un tercer conjunto de transistores en base a la señal del VCO (bloque 816). El tercer conjunto de transistores puede comprender los transistores del VCO dentro de los inversores 606 a 609 de las FIGS. 6A y 6B. Los transistores de los segundo y tercer conjuntos pueden operar como conmutadores. Las señales del LO pueden ser resincronizadas con la señal del VCO, y la transconductancia de los transistores del primer conjunto puede ser conmutada durante las transiciones de la señal del VCO.

- La **FIG. 9** muestra un diseño de un procedimiento 900 para llevar a cabo la conversión de reducción en frecuencia. Una señal modulada puede ser reducida en frecuencia con un primer conjunto de transistores para obtener señales en banda base (bloque 912). El primer conjunto de transistores puede comprender los transistores de RF de la FIG. 7. La señal modulada puede ser reducida en frecuencia directamente de RF a banda base (para una arquitectura de reducción en frecuencia directa) o de IF a banda base para una arquitectura superheterodina).

- La transconductancia de los transistores del primer conjunto puede ser conmutado con un segundo conjunto de transistores en base a las señales del LO, estando el segundo conjunto de transistores acoplado a las fuentes de los transistores del primer conjunto (bloque 914). El segundo conjunto de transistores puede comprender los transistores LO de la FIG. 7. Los transistores del segundo conjunto pueden ser habilitados e inhabilitados con un tercer conjunto de transistores en base a la señal del VCO (bloque 916). El tercer conjunto de transistores puede comprender los transistores del VCO de la FIG. 7. Las señales del LO pueden ser resincronizadas con la señal del VCO, y la transconductancia de los transistores del primer conjunto puede ser conmutada durante las transiciones de la señal del VCO.

- El convertidor elevador y el convertidor reductor descritos en la presente memoria pueden, cada uno, ser implementados sobre un IC, un IC analógico, un RFIC, un IC de señal mixta, un circuito integrado específico de la aplicación (ASIC), una placa de circuito impreso (PCB), un dispositivo electrónico, etc. El convertidor elevador y el convertidor reductor pueden, cada uno ser fabricados con diversas técnicas del procedimiento de IC, como por ejemplo un metal óxido semiconductor complementario (CMOS), NMOS, PMOS, un transistor de unión bipolar (BJT), bipolar CMOS (BiCMOS), germanio de silicio (SiGe), arseniuro de galio (GaAs), etc.

25

40

45

50

- Un aparato que implementa el convertidor elevador y el convertidor reductor descritos en la presente memoria puede ser un dispositivo autosuficiente o puede ser parte de un dispositivo mayor. El dispositivo puede ser (i) un IC autosuficiente, (ii) un conjunto de uno o más ICs que pueden incluir ICs de memoria para el almacenamiento de datos y / o instrucciones, (iii), un RFIC, como por ejemplo un receptor de RF, (RFC) o un transmisor / receptor de RF (RTR), (iv) un ASIC, como por ejemplo un módem de estación móvil (MSM), (v) un módulo que esté embebido dentro de otros dispositivos, (vi) un receptor, un teléfono celular, un dispositivo inalámbrico, un aparato telefónico o una unidad móvil, (vii) etc.

- En uno o más diseños ejemplares, las funciones descritas pueden ser implementadas en hardware, software, firmware o cualquier combinación de estos. Si se implementan en software las funciones pueden ser almacenadas en o transmitidas a través de una o más instrucciones o códigos sobre un medio legible por computadora. Los medios legibles por computadoras incluyen tantos medios de almacenamiento de computadora como medios de comunicación que incluyan cualquier medio que facilite la transferencia de un programa informático de un lugar a otro. Unos medios de almacenamiento pueden ser cualesquiera medios disponibles a los que se pueda acceder por una computadora. A modo de ejemplo, y no de limitación, dichos medios legibles por computadora pueden comprender una RAM, una ROM, una EEPROM, un CD-ROM, u otro almacenamiento de disco óptico, almacenamiento de disco magnético, u otros dispositivos de almacenamiento magnéticos o cualquier otro medio que pueda ser utilizado para incorporar o almacenar el código de almacenamiento deseado bajo la forma de instrucciones o estructuras de datos y a los que se pueda acceder por una computadora. Así mismo, cualquier conexión es pertinentemente designada como un medio legible por computadora. Por ejemplo, si el software es transmitido desde un sitio web, un servidor u otra fuente a distancia utilizando un cable coaxial, un cable de fibra óptica, un cable trenzado, un DSL, o sistemas técnicos inalámbricos, como por ejemplo, infrarrojos, radio y microondas se incluyen en la definición de medio. Disk y Disc, tal y como se utilizan en la presente memoria, incluyen el disco compacto (CD) el disco láser, el disco óptico, el disco versátil digital (DVD), el disco flexible y el disco Blue-ray en el que los disks generalmente reproducen datos de forma magnética, mientras que los disc reproducen datos de forma óptica con láseres. Deben, así mismo, ser incluidas combinaciones de los sistemas referidos dentro del alcance de los medios legibles por computadora.

- La descripción anterior de la divulgación se ofrece para hacer posible que cualquier persona experta en la materia ponga en práctica o utilice la divulgación. Diversas modificaciones respecto de la divulgación resultarán evidentes, sin dificultad, a los expertos en la materia, y los principios genéricos definidos en la presente memoria pueden ser aplicados a otras variantes sin apartarse del alcance de la divulgación. Por tanto, la divulgación no pretende quedar limitada a los ejemplos y diseños descritos en la presente memoria, sino que se le debe conceder el más amplio ámbito en consonancia con los principios y características novedosas divulgadas en la presente memoria.

## REIVINDICACIONES

1.- Un convertidor elevador (500, 600) para elevar en frecuencia unas señales en banda base en fase I y en cuadratura Q, que comprende:

un primer conjunto de transistores (542,544, 546, 548, 642, 644, 646, 648) configurados para recibir las señales I y Q y proporcionar una señal elevada en frecuencia, en el que, en uso, el primer conjunto de transistores recibe las señales I y Q, y

un segundo conjunto de transistores (512, 514, 516, 518) acoplados a las fuentes de los transistores del primer conjunto (542, 544, 546, 548, 642, 644, 646, 648) y configurados para conmutar la transconductancia de los transistores del primer conjunto (542, 544, 546, 548, 642, 644, 646, 648) en base a las señales de un oscilador local, LO, en el que, en uso, el segundo conjunto recibe las señales del LO en el que

el primer conjunto de transistores comprende

un primer par diferencial (542, 642) configurado para recibir señales en banda base en fase I no invertidas e invertidas, en el que, en uso, el primer par diferencial recibe señales en banda base en fase I no invertidas e invertidas.

un segundo par diferencial (544, 644) configurado para recibir las señales en banda base I invertidas y no invertidas, en el que, en uso, el segundo par diferencial recibe las señales en banda base en fase I invertidas y no invertidas,

un tercer par diferencial (546, 646) configurado para recibir unas señales en banda base en cuadratura Q no invertidas e invertidas, en el que, en uso, el tercer par diferencial recibe las señales en banda base en cuadratura Q no invertidas e invertidas,

У

un cuarto par diferencial (548, 648) configurado para recibir las señales en banda base Q invertidas y no invertidas, en el que, en uso, el cuarto par diferencial recibe las señales en banda base en cuadratura Q invertidas y no invertidas,

25

5

10

15

20

30

35

40

el segundo conjunto de transistores comprende

un primer par de transistores (512, 612) acoplado como un primer inversor y a unas fuentes del primer par diferencial y configurado para recibir una señal I no invertida del LO, en el que, en uso, el primer par de transistores recibe una señal I no invertida del LO;

un segundo par de transistores (514, 614) acoplado como un segundo inversor y a las fuentes del segundo par diferencial y configurado para recibir una señal I invertida del LO, en el que, en uso, el segundo par de transistores recibe una señal I invertida del LO;

un tercer par de transistores (516,616) acoplado como un tercer inversor y a las fuentes del tercer par diferencial y configurado para recibir una señal no invertida Q del LO, en el que, en uso, el tercer par de transistores recibe una señal I invertida del LO;

у

un cuarto par de transistores (518, 618) acoplado como un cuarto inversor y a las fuentes del cuarto par diferencial y configurado para recibir una señal Q invertida del LO, en el que, en uso, el cuarto par de transistores recibe una señal Q invertida del LO, comprendiendo así mismo, el convertidor elevador

un tercer conjunto de transistores (606, 607) acoplado al segundo conjunto de transistores y configurado para habilitar e inhabilitar los inversores del segundo conjunto en base a una señal de un oscilador controlado en tensión, VCO, en el que, en uso, el tercer conjunto de transistores recibe la señal del VCO y en el que los transistores de los primero, segundo y tercer conjuntos son transistores metal - óxido - semiconductor, MOS.

- 45 2.- El convertidor elevador de la reivindicación 1, en el que el tercer conjunto de transistores sincroniza las señales del LO con la señal del VCO procedente de un oscilador controlado en tensión, de tal manera que la transconductancia de los transistores del primer conjunto (542, 544, 546, 548, 642, 644, 646, 648) es conmutada durante las transiciones de la señal del VCO.

- 3.- El convertidor elevador de la reivindicación 1, en el que el primer conjunto de transistores comprende así mismo

- un quinto (643) y un sexto (645) pares diferenciales configurados para recibir la señal en banda base en fase I, y

# ES 2 409 266 T3

un séptimo (647) y un octavo (649) pares diferenciales configurados para recibir una señal diferencial en banda base en cuadratura Q.

- 4.- El convertidor elevador de la reivindicación 3, en el que el segundo conjunto de transistores comprende

- un quinto y un sexto pares de transistores (617, 619) acoplados como quinto y sexto inversores, respectivamente, y configurados para recibir señales I, y

- un séptimo y un octavo pares de transistores (613, 615) acoplados como séptimo y octavo inversores, respectivamente, y configurados para recibir las señales Q del LO, estando los primero a octavo inversores acoplados a las fuentes de los primero a octavo pares diferenciales, respectivamente.

- 5.- El convertidor elevador de la reivindicación 4, en el que el tercer conjunto de transistores comprende un par de transistores acoplado como noveno inversor (606) y configurado para recibir una señal del VCO del oscilador controlado en tensión, no invertida, y para habilitar e inhabilitar los primero (512, 612) y segundo (514, 614) pares de transistores; y

un par de transistores acoplados como un décimo inversor (607) y configurados para recibir una señal del VCO invertida y para habilitar e inhabilitar los guinto (613, 615) y sexto (617, 619) pares de transistores.

15 6.- El convertidor elevador de cualquier reivindicación precedente, que comprende así mismo:

5

25

30

35

40

un par de transistores (572, 574, 672, 674) acoplado a los sumideros de los transistores del primer conjunto (542, 544, 546, 548, 642, 643, 644, 645, 646, 647, 648, 649) y configurado para proporcionar una señal de accionamiento de la señal elevada en frecuencia.

- 7.- El convertidor elevador de cualquier reivindicación precedente, en el que los transistores del segundo conjunto operan como conmutadores.

- 8.- El convertidor elevador de cualquier reivindicación precedente, en el que los primero y segundo conjuntos de transistores comprenden transistores metal óxido semiconductor, MOS.

- 9.- El convertidor elevador de cualquier reivindicación precedente, en el que los primero y segundo conjuntos de transistores están configurados para elevar en frecuencia las señales en banda base directamente de la banda base a la radiofrecuencia, RF.

- 10.- Un circuito integrado que comprende el convertidor elevador de acuerdo con cualquiera de las Reivindicaciones 1 a 9.

- 11.- Un procedimiento para la elevación en frecuencia de señales en banda base en fase I y en cuadratura Q, que comprende:

- la recepción de las señales I y Q en un primer conjunto de transistores y la elevación en frecuencia de las señales I y Q recibidas con un primer conjunto de transistores para obtener una señal elevada en frecuencia; y

- la conmutación de la transconductancia de los transistores del primer conjunto con un segundo conjunto de transistores en base a las señales de un oscilador local, LO, estando el segundo conjunto de transistores acoplado a las fuentes de los transistores del primer conjunto, en el que

- el primer conjunto de transistores comprende

- un primer par diferencial (542, 642) configurado para recibir señales en banda base en fase I invertidas y no invertidas.

- un segundo par diferencial(544, 644) configurado para recibir las señales en banda base I invertidas y no invertidas,

- un tercer par diferencial (546, 646) configurado para recibir señales en banda base en cuadratura Q no invertidas e invertidas, y

- un cuarto par diferencial (548, 648) configurado para recibir las señales en banda base Q invertidas y no invertidas, y

- 45 el segundo conjunto de transistores comprende

- un primer par de transistores (512, 612) acoplado como un primer inversor y a las fuentes del primer diferencial y configurado para recibir una señal I no invertida del LO,

un segundo par de transistores (514, 614) acoplado como segundo inversor y a las fuentes del segundo par diferencial y configurado para recibir una señal I no invertida del LO,

un tercer par de transistores (516, 616) acoplado como un tercer inversor y a las fuentes del tercer par diferencial y configurado para recibir una señal Q no invertida, del LO, y

un cuarto par de transistores (518, 618) acoplado como un cuarto inversor y a las fuentes del cuarto par diferencial y configurado para recibir una señal Q invertida, del LO, y que comprende así mismo un tercer conjunto de transistores (606, 607) acoplado al segundo conjunto de transistores y configurados par habilitar e inhabilitar los inversores del segundo conjunto en base a una señal de un oscilador controlado en tensión, VCO,

en el que, en uso, el tercer conjunto de transistores recibe la señal del VCO y en el que los transistores de los primero, segundo y tercer conjuntos son transistores metal - óxido - semiconductor.

12.- Un convertidor reductor (700) para reducir en frecuencia una señal modulada para proporcionar una señal en banda base que comprende:

un primer conjunto de transistores (772 a 788) configurado para recibir una señal modulada y proporcionar unas señales en banda base en el que, en uso, el primer conjunto de transistores recibe una señal modulada y proporciona unas señales en banda base;

un segundo conjunto de transistores (752 a 768) acoplado a las fuentes de los transistores del primer conjunto y configurado para conmutar la transconductancia de los transistores del primer conjunto en base a las señales de un oscilador local, LO, en el que, en uso, el segundo conjunto de transistores está configurado para recibir las señales del LO y

un tercer conjunto de transistores (722 a 738) que comprende cuatro pares de transistores acoplados como cuatro inversores acoplados al segundo conjunto de transistores y configurados para, respectivamente, habilitar e inhabilitar los transistores del segundo conjunto en base a las señales del VCO del oscilador controlado en tensión no invertidas e invertidas, en el que

el segundo conjunto de transistores (752 - 768) comprende

un primer par diferencial (752, 762) configurado para recibir unas señales del LO en fase I no invertidas e invertidas.

un segundo par diferencial (754, 764) configurado para recibir unas señales del LO en cuadratura Q no invertidas e invertidas,

un tercer par diferencial (756, 766) , configurado para recibir las señales del LO I no invertidas e invertidas, y,

un cuarto par diferencial (758, 768) configurado para recibir las señales del LO Q no invertidas e invertidas; v

el primer conjunto de transistores comprende

un primer par de transistores (772, 782) que tienen las fuentes acopladas a los sumideros del primer par diferencial.

en el que la fuente del primer transistor del primer par de transistores está acoplada al sumidero del primer transistor del primer par diferencial y la fuente del segundo transistor del primer par de transistores está acoplada al sumidero del segundo transistor del primer par diferencial;

un segundo par de transistores (774,784) que tienen unas fuentes acopladas a los sumideros del segundo par diferencial, en el que la fuente del primer transistor del segundo par de transistores está acoplada al sumidero del primer transistor del segundo par diferencial y la fuente del segundo transistor del segundo par de transistores está acoplada al sumidero del segundo transistor del segundo par diferencial;

un tercer par de transistores (776, 786) que presentan unas fuentes acopladas a los sumideros del tercer par diferencial en el que la fuente del primer transistor del tercer par de transistores está acoplada al sumidero del primer transistor del tercer par diferencial y la fuente del segundo transistor del tercer par de transistores está acoplada al sumidero del segundo transistor del tercer par diferencial; y

un cuarto par de transistores (778, 788) que presentan unas fuentes acopladas a los sumideros del cuarto par diferencial y en el que la fuente del primer transistor del cuarto par de transistores está acoplada al sumidero del primer transistor del cuarto par diferencial y la fuente del segundo transistor del cuarto par de

14

10

5

15

20

25

30

35

40

45

50

# ES 2 409 266 T3

transistores está acoplada al sumidero del segundo transistor del cuarto par diferencial y en el que los transistores de los primero, segundo y tercer conjuntos son transistores metal - óxido - semiconductor.

- 13.- El convertidor reductor de la reivindicación 12, en el que el tercer conjunto de transistores comprende

- un primer par de transistores (722, 732) acoplado como un primer inversor y configurado para habilitar e inhabilitar el primer par diferencial en base a la señal del VCO no invertida,

- un segundo par de transistores (724, 734) acoplado como un segundo inversor y configurado para habilitar e inhabilitar el segundo par diferencial en base a una señal del VCO invertida,

- un tercer par de transistores (726, 736) acoplado como un tercer inversor y configurado para habilitar e inhabilitar el tercer par diferencial en base a la señal del VCO invertida, y

- un cuarto par de transistores (728, 738) acoplado como un cuarto inversor y configurado para habilitar e inhabilitar el cuarto par diferencial en base a la señal del VCO no invertida.

- 14.- El convertidor reductor de la reivindicación 13, en el que el tercer conjunto de transistores resincroniza las señales del LO con la señal del VCO, y en el que la transconductancia de los transistores del primer conjunto es conmutada durante las transiciones de la señal del VCO.

15

5