# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 421 618

61 Int. Cl.:

G06K 19/07 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 13.09.2011 E 11181125 (3)

(97) Fecha y número de publicación de la concesión europea: 17.04.2013 EP 2431925

54 Título: Procedimiento y dispositivo de modulación de carga activa por acoplamiento inductivo

(30) Prioridad:

21.09.2010 FR 1003754

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **04.09.2013**

(73) Titular/es:

INSIDE SECURE (100.0%) 41 Parc Club du Golf 13856 Aix-en-Provence Cedex 3, FR

(72) Inventor/es:

CHARRAT, BRUNO y PERNISEK, FLORIAN

(74) Agente/Representante:

LINAGE GONZÁLEZ, Rafael

#### **DESCRIPCIÓN**

Procedimiento y dispositivo de modulación de carga activa por acoplamiento inductivo

La presente invención se refiere a un procedimiento de emisión de datos por acoplamiento inductivo, que comprende las etapas que consisten en recibir una señal de la antena a través de un circuito inductivo de la antena en presencia de un campo magnético externo alternativo, extraer de la señal de la antena una primera señal periódica, producir una segunda señal periódica a través de un oscilador sincrónico que presenta una entrada de sincronización que recibe la primera señal periódica, poner el oscilador en un modo de libre oscilación, y aplicar en el circuito de la antena unas ráfagas de la segunda señal periódica para generar un campo magnético de modulación de carga activa.

La presente invención también se refiere a un dispositivo de emisión y recepción de datos diseñado para aplicar este procedimiento.

15

20

La presente invención se refiere, de forma general, a las técnicas de comunicación por acoplamiento inductivo, también denominadas "comunicaciones de campo cercano" o "NFC" (Near Field Communications). Las comunicaciones por acoplamiento inductivo generalmente hacen que intervenga un dispositivo denominado pasivo y un dispositivo denominado activo. Los dos dispositivos están equipados con una bobina de antena. El dispositivo activo emite un campo magnético oscilante, por ejemplo, a 13,56 MHz, y envía datos al dispositivo pasivo modulando el campo magnético. En el resto del documento se designa a este campo magnético como "campo magnético externo". El dispositivo pasivo envía datos al dispositivo mediante modulación de carga.

La modulación de carga puede ser pasiva o activa. La modulación de carga pasiva consiste en modificar la impedancia de la bobina de antena del dispositivo pasivo al ritmo de una señal, de modulación de carga, portadora de datos. Esta modulación de impedancia se refleja en la impedancia de la bobina de antena del dispositivo activo, por acoplamiento inductivo. El dispositivo activo, por lo tanto, puede extraer de su señal de antena la señal de modulación de carga utilizada por el dispositivo pasivo, y deducir de ésta los datos que el dispositivo pasivo le envía.

30 La modulación de carga activa consiste en emitir, al ritmo de la señal de modulación portadora de datos, unas ráfagas de campo magnético alternativo. El dispositivo activo percibe las ráfagas de campo magnético como una modulación de carga pasiva. Esta técnica la propuso la solicitante en la patente EP 1327222 (US 7098770 B2), véanse las figuras 4A a 4E, página 8 tabla 4, párrafo 074.

La modulación de carga activa ofrece, con respecto a la modulación de carga pasiva, una distancia de comunicación superior y/o una mejor transmisión de los datos en un entorno difícil, por ejemplo, un entorno alterado por masas metálicas generadoras de corrientes de Foucault. La modulación de carga activa necesita como contraprestación unos medios de excitación de la bobina de la antena y, por lo tanto, una fuente de corriente, pero consume mucha menos corriente que una emisión permanente de campo magnético.

40

Por lo tanto, un dispositivo de modulación de carga activa no puede ser únicamente pasivo en términos de alimentación eléctrica (un dispositivo únicamente pasivo se alimenta eléctricamente a través del campo magnético emitido por el dispositivo activo), aunque sin embargo se le considera como "pasivo" porque no emite el campo magnético externo necesario para la comunicación.

45

Para la obtención de una distancia de comunicación máxima, la modulación de carga activa también necesita que el campo magnético de modulación de carga esté en fase con el campo magnético externo emitido por el dispositivo activo. Unas rotaciones de fase entre el campo magnético de modulación de carga activa y el campo magnético externo podrían conllevar fluctuaciones indeseables en la distancia de comunicación.

50

La patente US 5.453.748 describe un transpondedor que comprende un oscilador local que genera una señal local, y un oscilador sincronizado. Un comparador compara la señal local con una señal de referencia recibida, y suministra una señal de comparación al oscilador sincronizado que se sincroniza con la señal de comparación y suministra una señal bloqueada. Un combinador recibe la señal local y la señal bloqueada y suministra una señal de respuesta del transpondedor.

55

60

La patente EP 1801741 describe un dispositivo NFC de modulación de carga activa que utiliza un bucle de fijación de fase para controlar la fase del campo magnético de modulación de la carga (véase Fig. 19 de este documento). El bucle de fijación de fase comprende un VCO (oscilador controlado por tensión), un comparador de fase y un filtro de paso bajo que suministra una tensión de control al VCO. El comparador de fase recibe, como frecuencia de referencia, una primera señal periódica que se extrae de la señal de la antena inducida por el campo magnético externo. El bucle de fijación de fase suministra una segunda señal periódica sincronizada en fase con la de la primera señal periódica. En el modo de emisión de datos, unas ráfagas de la segunda señal periódica se aplican al circuito de la antena para generar las ráfagas de campo magnético.

65

Cuando el dispositivo cambia al modo de emisión de datos, la primera señal periódica ya no se aplica al comparador

de fase y un circuito de muestreo HLD ("Sample Hold) mantiene la tensión de control aplicada al VCO. El bucle de fijación de fase cambia, de esta manera, de un modo de funcionamiento sincronizado a un modo de libre oscilación y permanece en este modo de funcionamiento hasta el fin de la emisión de datos.

- 5 Si se desea que las ráfagas de campo magnético estén en fase con el campo magnético externo, el bucle de fijación de fase debe presentar un deslizamiento de fase muy débil durante toda la duración del modo de emisión de datos, quesea al menos igual a la duración de emisión de una trama de datos. En la práctica, el desfase máximo tolerado en este período en general, es aproximadamente de ¼ del período del campo magnético que oscila a 13,56 MHz.

- A modo de ejemplo, una trama ISO 14443-A presenta una duración de aproximadamente 25,6 ms. La frecuencia de la señal periódica es de 13,56 MHz, el deslizamiento de fase del bucle de fijación de fase en modo de libre oscilación preferentemente no debe ser superior a 18 ns, es decir ¼ del período del campo magnético que oscila a 13,56 MHz.

- Ahora bien, obtener una estabilidad superior a 18 ns en una duración de 25,6 ms significa que el bucle de fijación de fase debe ofrecer una precisión extrema de aproximadamente 0,7 ppm ((18x10<sup>-9</sup>/25,6x10<sup>-3</sup>)\*10<sup>6</sup>). Una precisión de este tipo necesita una circuitería de muy alta calidad y costosa de realizar.

20

25

30

- Por lo tanto, podría recomendarse prever un medio que permita suministrar ráfagas de campo magnético que presenten un débil desfase con respecto al campo magnético externo, sin recurrir a una circuitería extremadamente precisa y costosa de realizar.

- A tal efecto, la presente invención propone utilizar un oscilador sincronizado y volver a sincronizar el oscilador con el campo magnético externo antes de la aplicación de cada ráfaga de señales periódicas suministradas por el oscilador, al circuito de antena.

- Más concretamente, algunos modos de realización de la invención se refieren a un procedimiento de emisión de datos por acoplamiento inductivo, que comprende las etapas que consisten en recibir una señal de la antena a través de un circuito de antena inductivo en presencia de un campo magnético externo alternativo, extraer de la señal de la antena una primera señal periódica, producir una segunda señal periódica a través de un oscilador sincronizado que presenta una entrada de sincronización que recibe la primera señal periódica, presentando el oscilador un modo de oscilación sincronizado en fase con la primera señal periódica y un modo de libre oscilación, y aplicar al circuito de la antena unas ráfagas de la segunda señal periódica para generar un campo magnético de modulación de carga activa. El procedimiento también comprende las etapas que consisten en poner el oscilador en modo de oscilación sincronizada antes de la aplicación de cada ráfaga de la segunda señal periódica al circuito de la antena, y poner el oscilador en un modo de libre oscilación durante la aplicación de una ráfaga de la segunda señal periódica al circuito de la antena.

- En un modo de realización, el procedimiento comprende la etapa que consiste en, después de la aplicación de una ráfaga de la segunda señal periódica en el circuito de la antena, mantener el oscilador en modo de libre oscilación durante un tiempo de estabilización de la señal de la antena, antes de volver a poner el oscilador en modo de oscilación sincronizado.

- En un modo de realización, el procedimiento comprende las etapas que consisten en suministrar una señal de modulación portadora de datos, aplicar la segunda señal periódica al circuito de antena cuando la señal de modulación presenta un primer valor lógico, generar una señal de enmascaramiento que tenga un valor de enmascaramiento al menos cuando la señal de modulación presenta el primer valor lógico, y bloquear la aplicación de la primera señal periódica a la entrada de sincronización del oscilador cuando la señal de enmascaramiento presenta el valor de enmascaramiento.

- 50 En un modo de realización, el procedimiento comprende la etapa que consiste en otorgar al valor de enmascaramiento de la señal de enmascaramiento una duración superior a la del primer valor lógico de la señal de modulación, con el fin de mantener el oscilador en modo de libre oscilación durante el tiempo de estabilización de la señal de antena.

- 55 En un modo de realización, el procedimiento comprende una etapa que consiste en desfasar la segunda señal periódica con respecto a la señal de la antena.

- Algunos modos de realización de la invención también se refieren a un dispositivo de emisión y recepción de datos por acoplamiento inductivo que comprende un circuito de la antena inductivo en el que aparece una señal de antena en presencia de un campo magnético externo alternativo, unos medios para extraer de la señal de antena una primera señal periódica, un oscilador sincronizado que presenta una entrada de sincronización que recibe la primera señal periódica, que suministra una segunda señal periódica, presentando el oscilador un modo de oscilación sincronizado en fase con la primera señal periódica y un modo de libre oscilación, y un circuito de modulación de carga activa, configurado para aplicar al circuito de la antena unas ráfagas de la segunda señal periódica y generar un campo magnético de modulación de carga activa. El dispositivo se configura para poner el oscilador en modo de oscilación sincronizada antes de la aplicación de cada ráfaga de la segunda señal periódica al circuito de la antena,

y poner el oscilador en modo de libre oscilación durante la aplicación de una ráfaga de la segunda señal periódica al circuito de la antena.

En un modo de realización, después de la aplicación de una ráfaga de la segunda señal periódica al circuito de la antena, el dispositivo se configura para mantener la oscilación en modo de libre oscilación durante un tiempo de estabilización de la señal de la antena, antes de volver a poner el oscilador en modo de oscilación sincronizada.

En un modo de realización, el dispositivo se configura para generar o recibir una señal de modulación de carga portadora de datos, aplicar la segunda señal periódica al circuito de antena cuando la señal de modulación presenta un primer valor lógico, generar una señal de enmascaramiento que tenga un valor de enmascaramiento al menos cuando la señal de modulación presenta el primer valor lógico, y bloquear la aplicación de la primera señal periódica a la entrada de sincronización del oscilador cuando la señal de enmascaramiento presenta el valor de enmascaramiento.

15 En un modo de realización, el dispositivo se configura para otorgar al valor de enmascaramiento de la señal de enmascaramiento una duración superior a la del primer valor lógico de la señal de modulación, con el fin de mantener el oscilador en modo de libre oscilación durante el tiempo de estabilización de la señal de antena.

En un modo de realización, el oscilador sincronizado es de tipo oscilador astable que presenta una frecuencia propia de auto-oscilación determinada por unos componentes del oscilador.

En un modo de realización, en el modo de oscilación sincronizada, el oscilador sincronizado es de tipo digital y se configura para retomar a la salida el período de la señal periódica aplicada a la entrada de la sincronización, y, en el modo de libre oscilación, reconstituir a la salida la frecuencia recibida a la entrada de la sincronización durante el modo de oscilación sincronizada.

En un modo de realización, el oscilador sincronizado comprende un bucle de fijación de fase que comprende un comparador de fase que suministra una señal de fase, un filtro de paso bajo que recibe la señal de fase y suministra una tensión de control, un oscilador controlado por tensión que recibe la tensión de control y suministra la segunda señal periódica, y unos medios para bloquear durante su paso en el modo de libre oscilación al comparador de fase y mantener a la entrada del oscilador controlado por tensión el valor de la tensión de control.

En un modo de realización, el dispositivo comprende unos medios para desfasar la segunda señal periódica con respecto a la señal de la antena.

Algunos modos de realización de la invención también se refieren a un dispositivo que comprende un dispositivo de emisión y recepción de datos de acuerdo con la invención, y al menos un procesador anfitrión que suministra al dispositivo los datos a emitir.

40 En un modo de realización, el dispositivo se monta dentro o sobre un soporte portátil.

10

25

30

35

50

Algunos modos de realización de la invención también se refieren a una tarjeta inteligente, que comprende al menos un procesador y un dispositivo de emisión y recepción de datos de acuerdo con la invención.

- 45 En el resto del documento se describen algunos modos de realización de un procedimiento y de un dispositivo de acuerdo con la invención, a modo no limitativo en relación con las figuras adjuntas, entre las que:

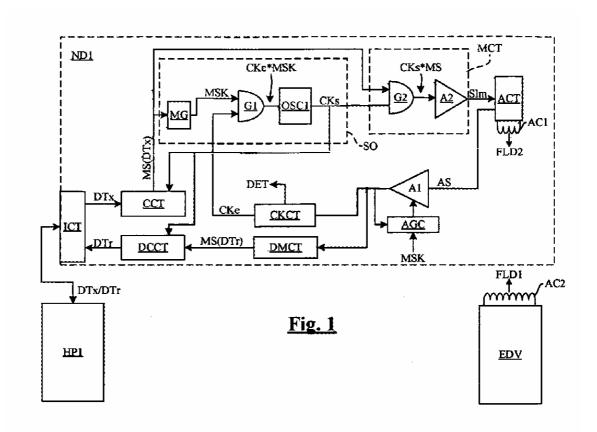

- la figura 1 representa un dispositivo NFC de emisión/recepción de datos de acuerdo con la invención que comprende un oscilador sincronizado,

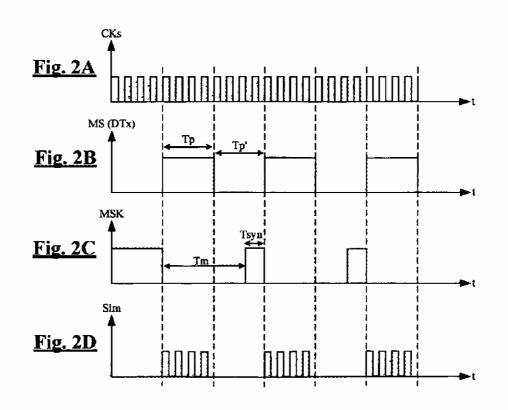

- las figuras 2A a 2D muestran unas señales que intervienen en el funcionamiento del dispositivo de la figura 1 durante la emisión de datos por modulación de carga activa,

- las figuras 3A a 3D muestran otras señales que intervienen en el funcionamiento del dispositivo de la figura 1 durante la emisión de datos por modulación de carga activa,

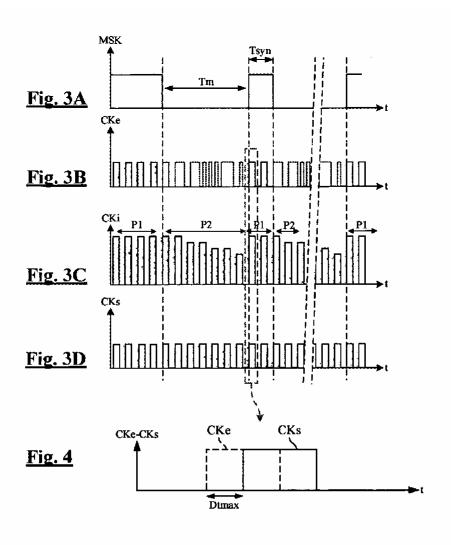

- la figura 4 muestra un error de fase entre una primera señal periódica y una segunda señal periódica que utiliza el dispositivo de la figura 1,

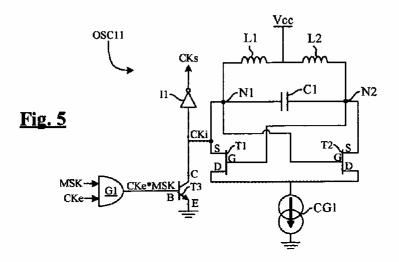

- 60 la figura 5 representa un primer ejemplo de realización de un oscilador sincronizado,

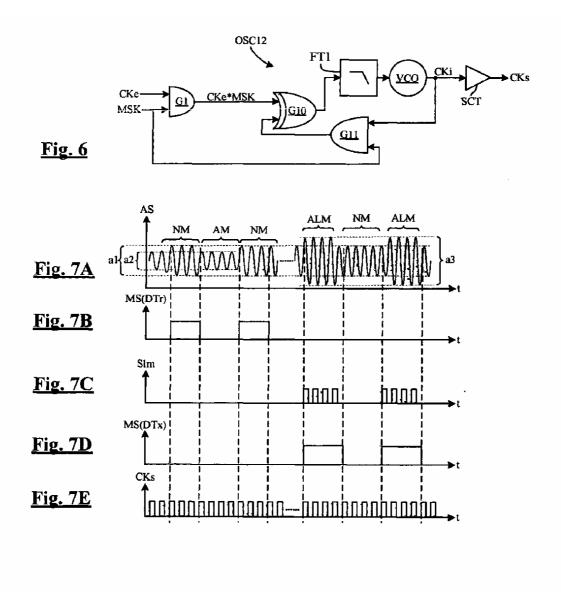

- la figura 6 representa un segundo ejemplo de realización de un oscilador sincronizado,

- la figura 7A muestra la forma de una señal de antena del dispositivo de la figura 1 durante la recepción y la emisión de datos, y las figuras 7B a 7E muestran unas señales asociadas a la señal de la antena,

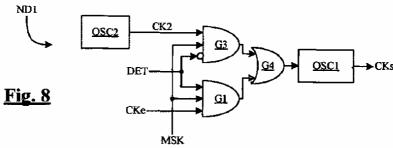

- la figura 8 representa una variante de realización de una parte del dispositivo de la figura 1,

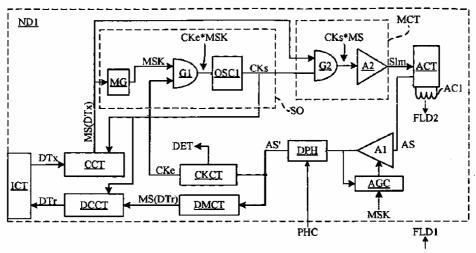

- la figura 9 representa otra variante de realización del dispositivo de la figura 1,

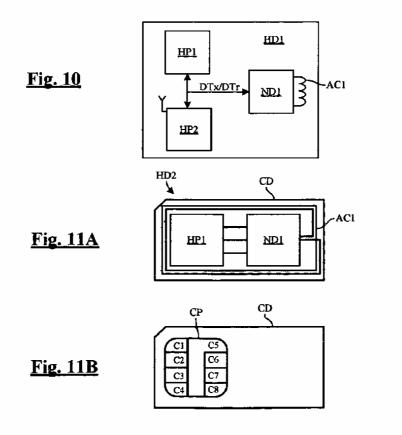

- la figura 10 muestra un ejemplo de dispositivo portátil que comprende un dispositivo de emisión/recepción de datos de acuerdo con la invención, y

- las figuras 11A, 11B son unas vistas desde arriba y desde debajo de otro ejemplo de dispositivo portátil que comprende un dispositivo de emisión/recepción de datos de acuerdo con la invención.

La figura 1 representa un dispositivo ND1 de emisión/recepción de datos de acuerdo con la invención, que funciona por acoplamiento inductivo. El dispositivo ND1 comprende:

- un circuito ICT de interfaz de comunicación de contacto.

- un circuito ACT de la antena sintonizado sobre una frecuencia portadora, que comprende una bobina AC1 de antena y que puede comprender otros componentes diversos, tales como condensadores y/o auto-inductancias,

- un circuito DMCT de demodulación acoplado a un circuito DCCT de decodificación, para recibir datos DTr a través del circuito de antena,

- un circuito CCT de codificación acoplado a un circuito MCT de modulación, para emitir datos DTx a través del circuito de antena,

- 25 un circuito CKCT de reloj, y

10

15

- un oscilador SO sincronizado.

- El circuito ICT de interfaz de comunicación de contacto permite unir el dispositivo ND1 al menos a un procesador HP1 anfitrión. El procesador HP1 anfitrión suministra los datos DTx y recibe los datos DTr. Los datos DTx/DTr en general, son datos de aplicación de una aplicación NFC (transacción, pago, intercambio de información, etc.). En una variante, el dispositivo ND1 puede ser autónomo y comprender un procesador interno configurado para gestionar aplicaciones sin contacto. El procesador interno genera entonces, él mismo, los datos DTx y trata los datos DTr.

- El circuito CKCT de reloj y el circuito DMCT demodulador reciben una señal AS de la antena presente en el circuito ACT de antena. La señal AS de la antena se extrae, por ejemplo, del circuito de antena a través de un amplificador A1 cuya ganancia se controla mediante un circuito AGC automático de control de ganancia. La señal AS de la antena aparece en presencia de un campo FLD1 magnético externo alternativo que emite un dispositivo EDV externo de tipo lector NFC, equipado con una bobina AC2 de antena y que funciona en modo activo (emisión permanente del campo magnético). El campo FLD1 oscila, por ejemplo, a una frecuencia portadora de 13,56 MHz (normas ISO 14443, ISO 13693, Sony Felica®).

- El circuito CKCT de reloj suministra una señal CKe de reloj externa, o "primera señal periódica", cuya frecuencia es por lo general idéntica a la frecuencia portadora, es decir, 13,56 MHz en el marco de las normas anteriormente mencionadas. En un modo de realización, el circuito CKCT también suministra una señal DET que presenta un valor determinado, por ejemplo 1, cuando se detecta el campo FLD2. La señal DET forma una señal de detección de portadora que puede ser útil en ciertos modos de realización del dispositivo ND1.

- El oscilador SO sincronizado recibe la señal CKe de reloj externa y suministra una señal CKs de reloj interna, o "segunda señal periódica". El oscilador SO presenta un modo de oscilación sincronizada en el que la fase de la señal CKs se ajusta sobre la de la señal CKe, y un modo de libre oscilación en el que la fase de la señal CKs ya no se ajusta sobre la señal CKe.

- Para el envío de datos DTr al dispositivo ND1, el dispositivo EDV externo aplica al campo FLD1 magnético una modulación, por ejemplo, una modulación de amplitud, a través de una señal MS(DTr) de modulación portadora de datos. La señal MS(DTr) se transfiere a la señal AS de la antena y se extrae de ésta mediante el circuito DMCT de demodulación, tras la supresión de la portadora. El circuito DMCT suministra la señal MS(DTr) de modulación al circuito DCCT, que decodifica y suministra los datos DTr al circuito ICT de interfaz de comunicación o al procesador interno del dispositivo ND1 si éste está equipado con un procesador de este tipo.

- Se suministran al circuito CCT de codificación los datos DTx a enviar al dispositivo EDV externo. Éste suministra entonces al circuito MCT de modulación una señal MS(DTx) de modulación portadora de datos. Esta señal MS(DTx) de modulación puede modularse con una subportadora derivada de la frecuencia portadora, por ejemplo, una subportadora de 848 kHz (ISO 14443) o de 424 kHz (ISO 15693) o estar sólo codificada en banda de base sin subportadora (Sony Felica®). Para generar la subportadora, el circuito MCT recibe la señal CKs de reloj interna

suministrada por el oscilador sincronizado.

El circuito MCT de modulación es, en este caso, un circuito de modulación de carga activa que aplica el procedimiento descrito por la solicitante en la patente EP 1 327 222 (US 7 098 770B2). El circuito MCT suministra al circuito ACT de antena una señal de modulación de carga SIm activa que comprende unas ráfagas (trenes de onda) de la señal CKs de reloj interna, entrecortadas por períodos de no-modulación en los que la señal SIm presenta un valor por defecto, por ejemplo, 0. El circuito MCT modulador comprende en este caso una puerta G2 lógica de tipo ET que recibe las señales CKs y MS(DTx) y que suministra la señal Sml, y un amplificador A2 que une la salida de la puerta G2 y el punto de aplicación de la señal Sml al circuito ACT de la antena.

10

La señal SIm, en este caso, es igual a 0 cuando la señal MS(DTx) es igual a 0, y vuelve a transferir la señal CKs cuando la señal MS(DTx) es igual a 1. De este modo, cuando la señal MS(DTx) es igual a 1, el circuito ACT de antena recibe una ráfaga de la señal CKs y la bobina AC1 de antena emite una ráfaga correspondiente con un campo FLD2 magnético. Las ráfagas de campo FLD2 magnético se detectan mediante el dispositivo EDV externo como una modulación de carga pasiva. De este modo, este último puede extraer de su propia señal de antena la señal MS(DTx), para deducir de ésta los datos DTx enviados por el dispositivo ND1.

20

15

El oscilador SO sincronizado comprende un circuito OSC1 oscilador que comprende una entrada de sincronización unida a la salida de un circuito G1 de enmascaramiento, en este caso una puerta ET. La puerta G1 recibe en sus entradas la señal CKe de reloj externa y una señal MSK de enmascaramiento. La señal MSK la suministra un generador MG de máscara a partir de la señal MS(DTx) de modulación. La señal MSK presenta un valor de enmascaramiento, en este caso 0, y un valor transparente, en este caso 1. El circuito OSC1 oscilador se sincroniza con una señal CKe de reloj externa cuando ésta no está enmascarada (MSK=1) en su entrada de sincronización y funciona en modo de libre oscilación cuando la señal CKe se enmascara (MSK=0).

25

En un modo de realización, la señal de enmascaramiento presenta el valor (MSK=0) de enmascaramiento únicamente cuando la señal MS(DTX) de modulación presenta un valor correspondiente a la emisión de una ráfaga de campo FLD2 magnético, en este caso 1, y presenta el valor (MSK=1) transparente en el caso contrario. En este caso, el circuito OSC1 oscilador funciona en modo de libre oscilación únicamente durante la emisión de una ráfaga de campo magnético.

30

En un modo de realización, la señal de enmascaramiento presenta el valor de enmascaramiento durante la emisión de una ráfaga de campo FLD2 magnético, y se mantiene en ese valor durante un intervalo de tiempo adicional en función de la emisión de la ráfaga con el fin de dejarle tiempo a la señal AS de antena para estabilizarse. Las figuras 2A a 2D ilustran este modo de realización. La figura 2A representa la señal CKs, la figura 2B la señal MS(DTx), la figura 2C la señal MSK y la figura 2D la señal SIm, compuesta por ráfagas de la señal CKs. Con el objetivo de simplificar el diseño, la frecuencia de la señal CKs no se representa a escala y la señal MS(DTx) se representa compuesta de franjas de valor lógico 1 con una duración Tp constante, separadas por un intervalo Tp' de tiempo constante. En la práctica, la señal MS(DTx) puede presentar cualquier otra forma en función de los datos DTx emitidos, de la codificación que se le aplica a los datos DTx, y de la forma en que se genera (en particular, con o sin subportadora).

40

35

La figura 2D muestra que las ráfagas de la señal CKs, de una duración Tp, se aplican al circuito de antena cuando la señal MS(DTx) de modulación vale 1 (se podría prever una convención inversa). La figura 2C muestra que la señal MSK se pone a 0 cuando la señal MS(DTx) es igual a 1, y se mantiene a 0 durante un tiempo Tm superior a Tp pero inferior a Tp+Tp'. La duración del período de resincronización, durante el cual el circuito oscilador está en modo de oscilación sincronizada (designado Tsyn en la figura 2C), es por lo tanto igual a Tp+Tp'-Tm.

50

45

Las figuras 3A a 3D muestran con más detalle el mecanismo de resincronización de la señal CKs con respecto a la señal CKe, entre la emisión de dos ráfagas de campo FLD2 magnético. La figura 3A representa la señal MSK y es idéntica a la figura 2C. La figura 3B representa la señal CKe y la figura 3D representa la señal CKs. La figura 3C representa una señal CKi de oscilación interna del circuito OSC1 oscilador. Las señales CKi y CKs son idénticas en frecuencia y sólo difieren en su amplitud, restituyendo la de la señal CKs en este caso al nivel lógico 1 ó 0.

60

55

La figura 3B muestra que la señal CKe de reloj externa presenta una fase que puede fluctuar durante los períodos de libre oscilación. De hecho, durante estos períodos, la señal CKs de reloj interna se inyecta en el circuito de antena y se superpone a la señal inducida por el campo FLD1 magnético externo. Aunque la señal CKs se sincronice con bastante precisión con la señal CKe de reloj externa, el desfase entre la señal inducida y la señal inyectada puede ser suficiente como para provocar una fluctuación de fase haciendo que la señal de la antena no sea apta para suministrar una señal CKe de reloj externa fiable. Las figuras 3C y 3D muestran por el contrario que la fase de la señal CKs de reloj interna permanece sustancialmente estable durante los períodos de libre oscilación (denotados con la referencia P2) gracias a los frecuentes períodos de resincronización (denotados con la referencia P1) de duración Tsyn.

65 La

La figura 4 representa el desfase máximo Dtmax (expresado en desajuste temporal) entre la señal CKs y la señal CKe, en el momento en el que la señal CKs se vuelve a sincronizar con la señal Cke, es decir cuando la señal MSK

volverá a ser igual a 1. El valor Dtmax depende de la precisión del circuito OSC1 oscilador que se selecciona en función de la aplicación pretendida. Por ejemplo, se puede aspirar a un desfase máximo de ¼ del período de la señal CKe.

Gracias a las resincronizaciones que intervienen antes de cada emisión de una ráfaga de campo FLD2 magnético, no es necesario que el circuito OSC1 oscilador presente una precisión extrema que asegure un desfase máximo de 1/4 de período a lo largo de toda una trama de datos DTx. La precisión necesaria se vuelve a llevar a la escala de un bit de datos DTx y más concretamente a la escala de la duración de una ráfaga de campo magnético, que podría representar sólo una fracción de bit DTx de acuerdo con la codificación utilizada (un dato binario puede eventualmente codificarse en varias ráfagas de campo magnético).

Pueden preverse diversos tipos de circuitos osciladores para realizar el oscilador OS sincronizado. A modo de ejemplo, la figura 5 muestra un circuito OSC11 oscilador que comprende un centro oscilador de tipo multivibrador astable (también denominado oscilador astable). Este centro de oscilador comprende dos auto-inductancias L1, L2, un condensador C1, dos transistores T1, T2 de tipo MOS y una fuente CG1 de corriente. La inductancia L1 se conecta entre un nodo de alimentación que recibe una tensión Vcc y un nodo N1. La inductancia L2 se conecta entre el nodo de alimentación en tensión Vcc y un nodo N2. El condensador C1 se conecta entre los nodos N1, N2. El transistor T1 tiene su fuente S conectada al nodo N1, su drenador D unido a masa, a través de la fuente CG1 de corriente, y su rejilla G conectada al nodo N2. El transistor T2 tiene su fuente S conectada al nodo N2, su drenador D unido a masa a través de la fuente CG1 de corriente y su rejilla G conectada al nodo N1.

15

20

25

30

35

40

45

50

55

65

Por otro lado, la entrada de sincronización del circuito OSC11 oscilador se forma mediante la base B de un transistor T3 bipolar cuyo emisor E se une a masa y cuyo colector C se une al nodo N1. La salida del circuito oscilador se forma con una puerta I1 inversora que suministra la señal CKs, cuya entrada se une al nodo N1, en el que la señal Cki de oscilación interna está presente.

Cuando la señal CKe se aplica a la base B del transistor T3 (MSK=1), la fase de la señal CKi en el nodo N1 se impone mediante la señal CKe. El centro del circuito oscilador entonces no funciona como un oscilador astable sino como un oscilador monoestable.

Cuando la señal MSK es igual a 0, el transistor T3 ya no es conductor y el centro del circuito oscilador funciona en modo oscilador astable y oscila libremente a una frecuencia de auto-oscilación. Esta frecuencia se regula lo más cerca posible de la frecuencia de la señal CKe (13,56 MHz en el marco de las normas anteriormente mencionadas) eligiendo apropiadamente las inductancias L1, L2 y el condensador C1.

En una variante de realización, el circuito OSC1 oscilador puede ser de tipo digital y en el modo de oscilación sincronizada, puede configurarse para analizar y memorizar la frecuencia de la señal CKe recibida a la entrada de sincronización, y retomar la señal CKe a su salida. Cuando cambia al modo de libre oscilación, el circuito oscilador reconstruye la señal CKs a partir de este valor memorizado.

Como otro ejemplo adicional de realización, la figura 6 muestra un circuito OSC12 oscilador que comprende un bucle de fijación de fase ("Phase Locked Loop"). El circuito OSC12 comprende una puerta G10 de tipo OU Exclusivo, un filtro FT1 de paso bajo activo, un VCO (oscilador controlado por tensión), un circuito SCT seguidor y una puerta G11 de tipo ET. El VCO suministra la señal CKi de oscilación interna. Ésta se aplica al circuito SCT cuya salida suministra la señal CKs de reloj interna. La señal CKi de oscilación interna también se reenvía a una entrada de la puerta G10 a través de la puerta G11, que recibe en otra entrada la señal MSK. Otra entrada de la puerta G10 forma la entrada de sincronización del circuito OSC12 y se une a la salida de la puerta G1, que suministra la señal CKe de reloj externa cuando la señal MSK es igual a 1. La puerta G10 forma un comparador de fase y su salida se envía a una entrada de control del VCO a través del filtro FT1 de paso bajo activo.

Cuando la señal MSK es igual a 1, la puerta G11 es conductora, la puerta G10 recibe a la vez la señal CKi y la señal CKe y suministra una señal de diferencia de fase. Esta señal diferencial forma, después del filtrado de paso bajo, una tensión de referencia del VCO. La señal Cki, de este modo, queda enganchada en fase a la señal CKe. Cuando la señal MSK pasa a 0, las salidas de las puertas G1 y G11 pasan a 0. La salida de la puerta G10 se fuerza a 0. Unos medios permiten mantener a la entrada del VCO la tensión de referencia que recibía antes del paso a 0 de la señal MSK. Estos medios comprenden, por ejemplo, una fuente de tensión dispuesta en el filtro FT1 de paso bajo activo, tal como una bomba de cargas. De este modo, el VCO sigue suministrando la señal CKi y mantiene la fase de la señal CKi próxima a la de la señal CKe.

Las figuras 7A a 7E ilustran de forma esquemática una secuencia de recepción de datos DTr (parte izquierda de las figuras) así como una secuencia de emisión de datos DTx (parte derecha de las figuras).

La figura 7A muestra la forma de la señal AS de la antena. La figura 7B representa la señal MS(DTx) de modulación extraída de la señal AS de la antena mediante el circuito DMCT. La figura 7C representa la señal MS de modulación Sml de carga activa que comprende unas ráfagas de la señal CKs. La figura 7D representa la señal MS(DTx) de modulación y la figura 7E representa la señal CKs. La señal AS es en este caso una señal alternativa de doble

alternancia que es la imagen del campo FLD1 magnético en modo recepción. Algunos modos de realización del circuito ACT de la antena pueden comprender, no obstante, un diodo de rectificación de la señal de la antena. En ese caso, éste es una señal de semi-alternancia.

Durante la recepción de datos DTr, el dispositivo EDV externo (véase la Fig. 1) modula la amplitud del campo FLD1 magnético con una profundidad de modulación que depende del protocolo de comunicación seleccionado, y la señal AS de la antena presenta una modulación de amplitud similar. Se distinguen períodos NM de no modulación en los que la amplitud de la señal de la antena es máxima y unos períodos AM de modulación en los que la amplitud de la señal de antena es mínima. Las máximas y mínimas de tensión de la señal AS dependen en la práctica de la distancia entre el dispositivo EDV externo y el dispositivo ND1.

Durante la emisión de datos DTx, la señal AS de la antena también presenta unos períodos NM de no modulación en los que su amplitud es idéntica a la observada durante los períodos de no modulación durante la recepción de datos. La amplitud de la señal de la antena entonces sólo dependerá del campo FLD1 magnético emitido por el dispositivo EDV externo y de la distancia entre los dos dispositivos. La señal AS también presenta unos períodos ALM de sobrevoltaje durante el envío de las ráfagas de campo FLD2 magnético. De hecho, la señal CKs se inyecta entonces al circuito de antena y se superpone a la señal inducida por el campo FLD1 magnético externo. La señal de la antena comprenderá entonces un componente inducido y un componente inyectado.

15

25

30

45

50

55

60

Para el experto en la materia resultará evidente que el dispositivo de emisión/recepción de datos ND1, de acuerdo con la invención, admite diversos modos de realización. En particular, el circuito MCT de modulación puede comprender, además de los medios de modulación de carga activa que acaban de describirse, unos medios de modulación de carga pasiva convencionales, tal como un interruptor de modulación de carga conectado al circuito ACT de la antena.

En una variante de realización, la señal MSK se aplica al circuito de control AGC de ganancia y éste se configura para forzar a 0 la salida del amplificador A2. En este caso, es posible que no resulte necesario impedir la aplicación de la señal CKe a la entrada de sincronización del circuito OSC1 oscilador, cambiando éste automáticamente al modo de libre oscilación cuando la señal CKe pasa a 0.

El dispositivo ND1 también puede comprender unos medios Vcc de extracción de una tensión de alimentación a partir de la señal de antena, tal como un circuito rectificador seguido de un condensador de alisado, para permitir al dispositivo ND1 funcionar en modo pasivo únicamente, en ausencia de una fuente de alimentación local.

En un modo de realización representado en la figura 8, el dispositivo ND1 también comprende un oscilador OSC2 que no está sincronizado con la señal CKe de reloj externa, por ejemplo, un oscilador de cuarzo. El oscilador OSC2 suministra una señal CK2 de reloj que permite al dispositivo DV1 funcionar en modo lector NFC para dialogar con un circuito integrado sin contacto pasivo o con un dispositivo similar configurado en modo pasivo. En este caso, el circuito OSC1 oscilador sincronizado puede seguir utilizándose para suministrar la señal CKs de reloj interna. La selección de la señal CKe o CK2 de reloj aplicada a la entrada de sincronización del circuito OSC1 puede hacerse a través de la señal DET descrita más arriba, dando prioridad al modo pasivo.

Asimismo con referencia a la figura 8, se añaden dos puertas G3 y G4 y la puerta G1 se modifica para presentar tres entradas. La puerta G3 es una puerta ET que presenta tres entradas de las cuales, es una entrada inversora. La puerta G4 es una puerta de tipo OU con dos entradas. La puerta G3 recibe en sus dos entradas no inversoras la señal CK2 y la señal MSK, y recibe la señal DET en su entrada inversora. La puerta G1 recibe en sus entradas las señales CK2, DET y CKe. Las salidas de las puertas G1 y G3 se aplican a la puerta G4 cuya salida se une a la entrada de sincronización del circuito OSC1 oscilador. Cuando la señal DET es igual a 1 (presencia de un campo FLD1 magnético externo), la salida de la puerta G3 se fuerza a 0 y el dispositivo funciona en modo pasivo de la forma descrita más arriba. Cuando la señal DET es igual a 0, la salida de la puerta G1 se fuerza a 0 y la señal MSK se fuerza a 1 mediante el circuito MG. La señal CK2 de reloj se aplica a la entrada del circuito OSC1 oscilador, para la emisión permanente del campo FLD1 magnético. La estructura de la puerta G2, que recibe las señales CKs y MS(DTx) y que suministra la señal Sml, puede modificarse con el fin de que ésta garantice una modulación de la señal CKs con una profundidad de modulación regulable inferior al 100%, en particular si el dispositivo debe realizarse de conformidad con las normas ISO 14443A y 14443B.

En el ejemplo de realización representado en la figura 9, el dispositivo ND1 comprende un desfasador DPH. Este desfasador, por ejemplo, se dispone a la salida del amplificador A1. El desfasador DPH aplica a la señal AS de antena un desfase Dp y suministra al circuito CKCT de reloj y al circuito DMCT demodulador una señal AS' de la antena desfasada. El desfase Dp puede fijarse y determinarse durante el diseño del desfasador DPH. Como alternativa, el desfase Dp puede determinarse dinámicamente mediante un control PHC aplicado al desfasador, que especifica el valor del desfase Dp, por ejemplo, entre 0 y 360º.

El desfasador DPH permite al dispositivo ND1 emitir unas ráfagas de campo FLD2 magnético que presentan el desfase Dp con respecto al campo FLD1 magnético externo. Esto permite, por ejemplo, en ciertas aplicaciones en las que la distancia de comunicación no debe sobrepasar cierto umbral (por ejemplo, por motivos de seguridad),

reducir la distancia de comunicación por debajo de ese umbral.

Este modo de realización muestra que el control de la fase de la señal CKs a través del oscilador SO sincronizado no sólo permite tener como objetivo un desplazamiento de fase nulo entre el campo FLD2 magnético y el campo FLD1 magnético. El control de la fase de la señal CKs a través del oscilador SO sincronizado también puede permitir el control de una desincronización voluntaria del campo FLD2 magnético con respecto al campo FLD1 magnético, a la vez que se mantiene a un valor lo más constante posible, el desfase Dp entre los dos campos magnéticos.

El dispositivo ND1 de emisión/recepción de datos, de acuerdo con la invención, también es capaz de diversas aplicaciones. En un ejemplo de aplicación representado en la figura 10, el dispositivo ND1 se integra en un dispositivo HD1 portátil y se une a uno o varios procesadores anfitrión, en este caso, dos procesadores HP1, HP2 anfitrión que utilizan el dispositivo ND1 como interfaz de comunicaciones sin contacto (interfaz NFC). El dispositivo HD1 portátil, por ejemplo, es un teléfono móvil, un reproductor portátil digital, un asistente (PDA) personal digital. El procesador HP1 puede ser el procesador anfitrión del dispositivo, o un procesador protegido, tal como un procesador de tarjeta SIM. El procesador HP2, por ejemplo, puede ser el procesador de banda de base de un teléfono móvil, garantizando asimismo unas comunicaciones por canal GSM.

En otro ejemplo de aplicación representado en las figuras 11A, 11B, el dispositivo ND1 está unido a un procesador HP1 anfitrión y el conjunto se integra en un soporte CD de plástico para formar una tarjeta HD2 inteligente. La bobina AC1 de antena, por ejemplo, es una bobina coplanaria que presenta una o varias espiras. En su cara trasera (Fig. 11B), la tarjeta HD2 está equipada con un grupo CP de contactos. La tarjeta HD2, por ejemplo, puede formar una tarjeta SIM NFC. El grupo de contactos puede comprender en este caso unos contactos C1 a C8, de conformidad con la norma ISO 7816. La tarjeta HD2 también puede formar una tarjeta de tipo SD que tiene por objeto insertarse en un dispositivo cualquiera (teléfono móvil, ordenador personal,...) en calidad de interfaz NFC de comunicaciones.

#### REIVINDICACIONES

- 1. Procedimiento de emisión de datos por acoplamiento inductivo, que comprende unas etapas que consisten en:

- recibir una señal (AS, AS') de antena a través de un circuito (ACT, AC1) de antena inductivo en presencia de un campo (FLD1) magnético externo alternativo,

- extraer de la señal (AS, AS') de antena una primera señal (CKe) periódica,

- producir una segunda señal (CKs) periódica mediante un oscilador (SO, OSC1) sincronizado que presenta una entrada de sincronización que recibe la primera señal (CKe) periódica, presentando el oscilador un modo de oscilación sincronizado en fase con la primera señal periódica y un modo de libre oscilación, y

- aplicar al circuito de antena unas ráfagas de la segunda señal (CKs) periódica para generar un campo (FLD2)

magnético de modulación de carga activa;

caracterizado porque comprende las etapas que consisten en:

- poner el oscilador en modo de oscilación sincronizada antes de la aplicación de cada ráfaga de la segunda señal (CKs) periódica al circuito de la antena, y

- poner el oscilador en un modo de libre oscilación durante la aplicación de una ráfaga de la segunda señal (CKs) periódica al circuito de antena.

- 25 2. Procedimiento de acuerdo con la reivindicación 1, que comprende la etapa que consiste en, después de la aplicación de una ráfaga de la segunda señal (CKs) periódica al circuito de antena, mantener el oscilador en modo de libre oscilación durante un tiempo de estabilización de la señal de antena, antes de volver a poner el oscilador en modo de oscilación sincronizada.

- 30 3. Procedimiento de acuerdo con una de las reivindicaciones 1 ó 2, que comprende unas etapas que consisten en:

- suministrar una señal (MS(DTx)) de modulación portadora de datos,

- aplicar la segunda señal (CKs) periódica al circuito de la antena cuando la señal (MS(DTx)) de modulación presenta un primer valor lógico,

- generar una señal de enmascaramiento que tenga un valor de enmascaramiento, al menos cuando la señal (MS(DTx)) de modulación presenta el primer valor lógico, y

- bloquear la aplicación de la primera señal (CKe) periódica a la entrada de sincronización del oscilador (SO, OSC1)

cuando la señal de enmascaramiento presenta el valor de enmascaramiento.

- Procedimiento de acuerdo con las reivindicaciones 2 y 3, que comprende una etapa que consiste en otorgar al valor de enmascaramiento de la señal de enmascaramiento una duración superior a la del primer valor lógico de la señal (MS(DTx)) de modulación, con el fin de mantener el oscilador en modo de libre oscilación durante el tiempo de estabilización de la señal de la antena.

- 5. Procedimiento de acuerdo con una de las reivindicaciones 1 a 4, que comprende una etapa que consiste en desfasar la segunda señal (CKs) periódica con respecto a la señal (AS) de antena.

- 6. Dispositivo (ND1) de emisión y recepción de datos por acoplamiento inductivo, que comprende:

- un circuito (ACT) de antena inductivo en el que aparece una señal (AS, AS') de antena en presencia de un campo magnético externo alternativo,

- unos medios (CKCT) para extraer de la señal (AS, AS') de antena una primera señal (CKe) periódica,

- un oscilador (SO, OSC1) sincronizado que presenta una entrada de sincronización que recibe una primera señal (CKe) periódica, que suministra una segunda señal (CKs) periódica, presentando el oscilador un modo de oscilación sincronizado en fase con la primera señal periódica y un modo de libre oscilación, y

- un circuito (MCT) de modulación de carga activa, configurado para aplicar al circuito de la antena unas ráfagas de la segunda señal (CKs) periódica y generar un campo (FLD2) magnético de modulación de carga activa;

- 65 dispositivo caracterizado porque está configurado para:

50

55

- poner el oscilador en modo de oscilación sincronizada antes de la aplicación de cada ráfaga de la segunda señal (CKs) periódica al circuito de la antena, y

- poner el oscilador en modo de libre oscilación durante la aplicación de una ráfaga de la segunda señal (CKs) periódica al circuito de la antena.

- 7. Dispositivo de acuerdo con la reivindicación 6, configurado para mantener, después de la aplicación de una ráfaga de la segunda señal (CKs) periódica al circuito de la antena, el oscilador en modo de libre oscilación durante un tiempo de estabilización de la señal de antena, antes de volver a poner el oscilador en modo de oscilación sincronizada.

- 8. Dispositivo de acuerdo con una de las reivindicaciones 6 y 7, configurado para:

10

15

45

60

- generar o recibir una señal (MS(DTx)) de modulación de la carga portadora de datos,

- aplicar la segunda señal (CKs) periódica al circuito de antena cuando la señal (MS(DTx)) de modulación presenta un primer valor lógico,

- generar una señal de enmascaramiento que tenga un valor de enmascaramiento al menos cuando la señal de 20 modulación presenta el primer valor lógico, y

- bloquear la aplicación de la primera señal (CKe) periódica a la entrada de sincronización del oscilador (SO, OSC1) cuando la señal de enmascaramiento presenta el valor de enmascaramiento.

- 9. Dispositivo de acuerdo con las reivindicaciones 7 y 8, configurado para otorgar al valor de enmascaramiento de la señal (MSK) de enmascaramiento una duración superior a la del primer valor lógico de la señal (MS(DTx)) de modulación, con el fin de mantener el oscilador en modo de libre oscilación durante el tiempo de estabilización de la señal de antena.

- 30 10. Dispositivo de acuerdo con una de las reivindicaciones 6 a 9, en el que el oscilador (SO, OSC1, OSC11) sincronizado es de tipo oscilador astable que presenta una frecuencia propia de auto-oscilación determinada por unos componentes (L1, L2, C1) del oscilador.

- 11. Dispositivo de acuerdo con una de las reivindicaciones 6 a 9, en el que el oscilador (SO, OSC1) sincronizado es de tipo digital y que en el modo de oscilación sincronizada, se configura para retomar a la salida el período de la señal (CKe) periódica aplicada a la entrada de sincronización, y, en el modo de libre oscilación, reconstituir a la salida, la frecuencia recibida a la entrada de sincronización durante el modo de oscilación sincronizada.

- 12. Dispositivo de acuerdo con una de las reivindicaciones 6 a 9, en el que el oscilador (SO, OSC1, OSC12) sincronizado comprende un bucle de fijación de fase que comprende:

- un comparador (G10) de fase que suministra una señal de fase,

- un filtro (FT1) de paso bajo activo que recibe la señal de fase y suministra una tensión de control,

- un oscilador (VCO) controlado por tensión que recibe la tensión de control y suministra la segunda señal (CKi, CKs) periódica, y

- unos medios (FT1) para bloquear, durante el paso al modo de libre oscilación, el comparador (G10) de fase y mantener a la entrada del oscilador (VCO) controlado por tensión el valor de la tensión de control.

- 13. Dispositivo de acuerdo con una de las reivindicaciones 6 a 12, que comprende unos medios (PDH) para desfasar la segunda señal (CKs) periódica con respecto a la señal (AS) de la antena.

- 55 14. Dispositivo (HD1, HD2) que comprende:

- un dispositivo (ND1) de emisión y recepción de datos de acuerdo con una de las reivindicaciones 6 a 13, y

- al menos un procesador (HP1, HP2) anfitrión que suministra al dispositivo unos datos (DTx) para emitir.

- 15. Dispositivo de acuerdo con la reivindicación 14, instalado dentro o sobre un soporte (CD) portátil.

- 16. Tarjeta (HD2) inteligente, que comprende al menos un procesador (HP1, HP2) y un dispositivo (ND1) de emisión y recepción de datos de acuerdo con una de las reivindicaciones 6 a 13.

Fig. 9