# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 434 765

51 Int. Cl.:

H04L 12/933 (2013.01) H04L 12/931 (2013.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

(96) Fecha de presentación y número de la solicitud europea: 14.12.2007 E 07869286 (0)

(97) Fecha y número de publicación de la concesión europea: 14.08.2013 EP 2095583

(54) Título: Retícula de expansión de matriz

(30) Prioridad:

19.12.2006 US 870721 P 20.12.2006 US 871100 P 20.12.2006 US 871103 P 04.12.2007 US 950230 04.12.2007 US 950272 04.12.2007 US 950253

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 17.12.2013

(73) Titular/es:

WILSON, KEVIN (50.0%) 8200 Greenboro Drive Suite 1400 Mclean, VA 22102, US y NGUYEN, NINH (50.0%)

(72) Inventor/es:

WILSON, KEVIN y NGUYEN, NINH

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

## **DESCRIPCIÓN**

Retícula de expansión de matriz

#### Campo de la invención

5

10

15

20

30

35

40

La presente invención se refiere en general a sistemas de conmutación de telecomunicaciones y más particularmente a una gran arquitectura de conmutación de conexión cruzada, rentable y eficiente.

#### Antecedentes de la invención

Los sistemas de conexión cruzada digitales son una parte integral de la moderna red de transporte de telecomunicaciones de hoy. Se utilizan cada vez más por todos los proveedores de servicios, incluidos los operadores de central, los operadores de larga distancia y los operadores de derivación competitivos. Los avances tecnológicos significativos han permitido a los sistemas de conexión cruzada digital evolucionar de aplicaciones de prueba y preparación de banda estrecha a conexión cruzada de señales de red más grandes en banda ancha y dominios de frecuencia de banda ancha.

Se utiliza un sistema de banda ancha normalmente para terminar señales eléctricas y ópticas SONET de alta velocidad con el fin de terminar la ruta y preparar señales de banda ancha de velocidad más baja. El sistema de banda ancha también soporta la monitorización del rendimiento y las funciones de acceso de prueba. Típicamente los sistemas de banda ancha de conexión cruzada utilizan, o arquitectura de una sola etapa o arquitectura de matriz de Clos de tres etapas. En la arquitectura de matriz de tres etapas, la conexión cruzada incluye conmutadores agrupados en una etapa inicial, una etapa central y una etapa de terminación. La arquitectura de matriz de tres etapas es la más adecuada para aplicaciones de máxima capacidad para conexión cruzada de un gran volumen de señales. La arquitectura de matriz de una sola etapa organiza las matrices de una sola etapa en filas y columnas, lo que resulta en un mayor número de conmutaciones que en la arquitectura de tres etapas.

El documento "Adaptive Routing in High-Radix Clos Network", John Kim et al, de noviembre de 2006, XP031044199 describe unas técnicas de enrutamiento adaptable en redes Clos para reducir la latencia y reducir la varianza en la latencia de los paquetes.

### 25 Compendio

Si bien la arquitectura Clos de tres etapas ha sido un elemento básico de las matrices de conexión cruzada de alta capacidad, los inventores han reconocido una necesidad de matrices de capacidad incluso más alta. Las realizaciones configuradas según la invención facilitan proporcionar tal capacidad.

Se proporciona una matriz de conmutación que comprende: (a) un multitud de matrices de conmutación de tres etapas; y (b) una matriz de conmutación de expansión, en la que una segunda etapa de cada una de las matrices de conmutación de tres etapas incluye una sección de expansión que comprende conmutadores que facilitan la interconexión de cada matriz de tres etapas a la matriz de conmutación de expansión; (c) en la que cada una de la multitud de matrices de conmutación de tres etapas comprende una matriz de primera etapa que tiene N entradas y K salidas y una matriz de tercera etapa que tiene K entradas y N salidas, cada matriz de segunda etapa de cada matriz de conmutación de tres etapas recibe M entradas locales de la matriz de la primera etapa y proporciona M salidas locales a la matriz de conmutación de la tercera etapa, cada matriz de conmutación de la segunda etapa además proporciona P salidas a la matriz de expansión y recibe P entradas desde la matriz de expansión, en las que K, N, M y P son enteros; y (d) en la que la matriz de conmutación comprende una multitud de nodos y en la que, en cada nodo, hay K matrices de segunda etapa, M matrices de primera etapa y M matrices de tercera etapa y en la que el número de matrices de conmutación de expansión en la matriz de expansión es igual a K x P.

Una selección de las características opcionales de las reivindicaciones se expone en las reivindicaciones dependientes.

## Descripción de los dibujos

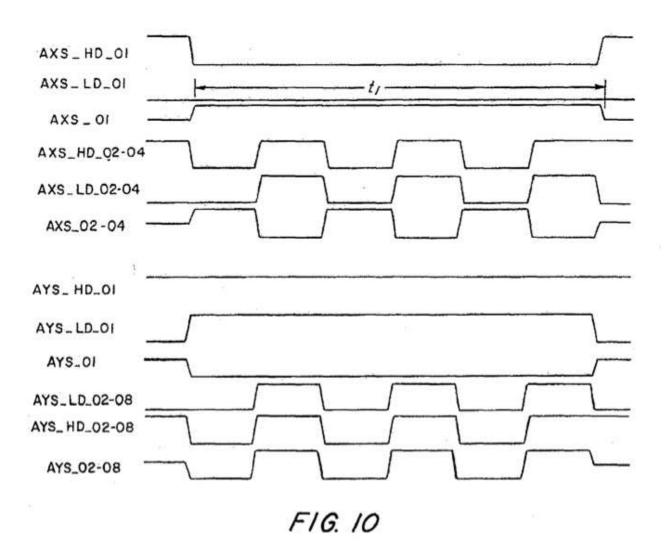

La Fig. 1 es un diagrama esquemático de una matriz de conmutación según una realización ilustrativa.

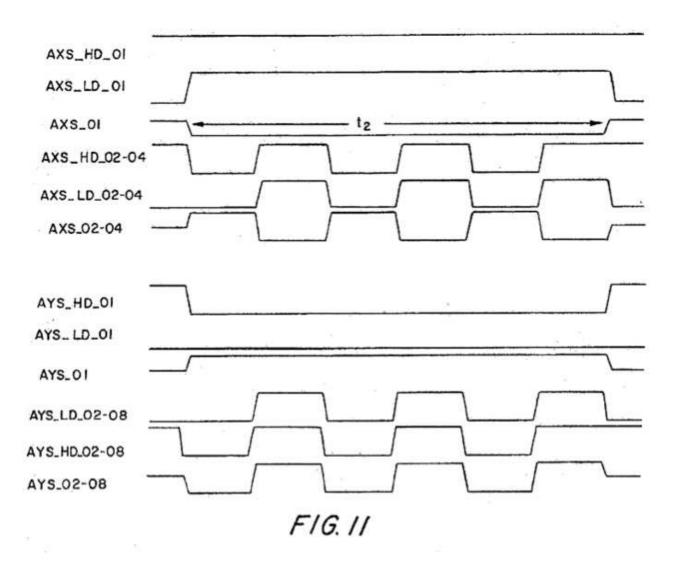

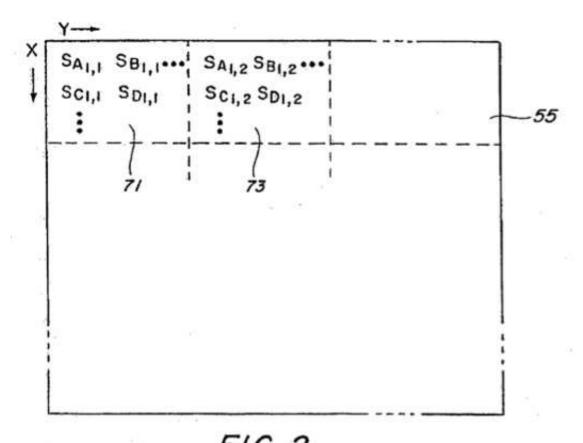

45 La Fig. 2 es un diagrama esquemático de una matriz de identificadores de conmutación según una realización illustrativa

La Fig. 3 es un diagrama de bloques de un procesador de ordenador y la memoria asociada según una realización ilustrativa.

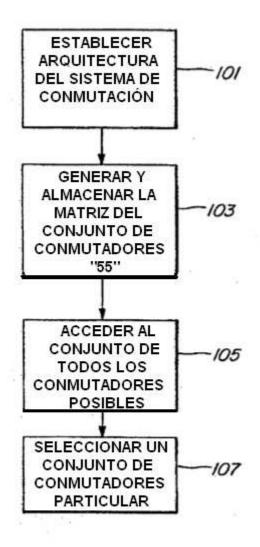

La Fig. 4 es un diagrama de flujo de un proceso de selección del conmutador que emplea la realización ilustrativa.

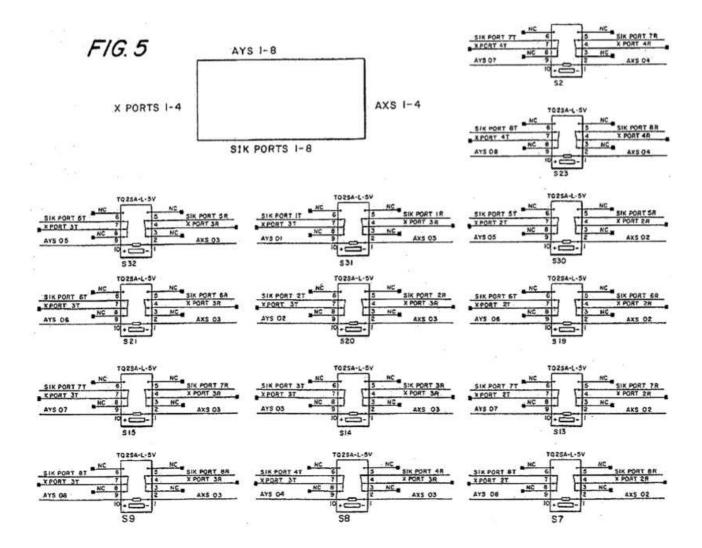

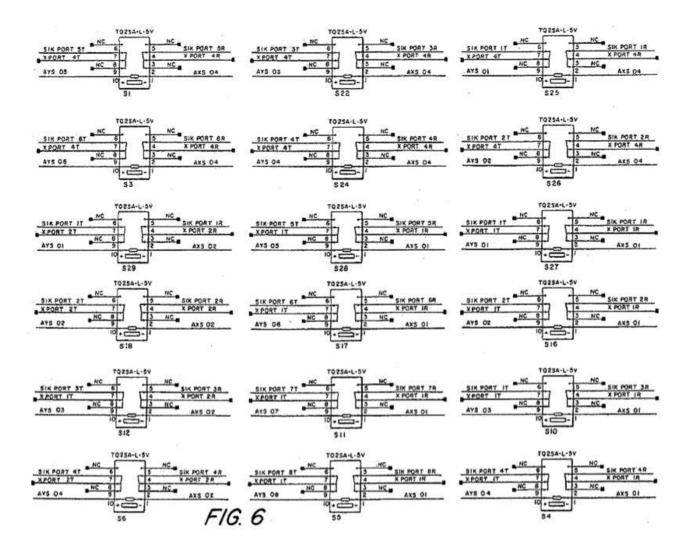

Las Figs. 5 y 6 comprenden un diagrama esquemático del circuito de una matriz de 32 conmutadores según una realización ilustrativa.

## ES 2 434 765 T3

Las Figs. 7 y 8 son diagramas de circuitos de los circuitos de control para los conmutadores de control tales como los descritos en las Figs. 5 y 6.

La Fig. 9 es una vista ampliada de uno de los conmutadores de la matriz mostrada en las Figs. 5 y 6.

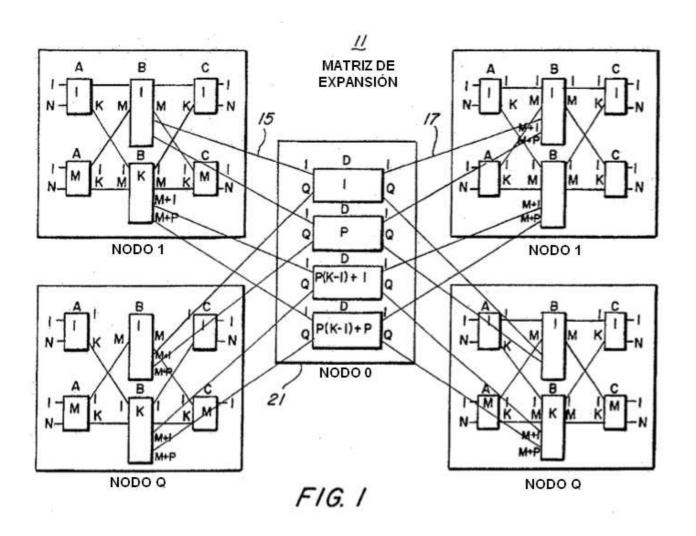

Las Figs. 10 y 11 son diagramas de forma de onda útiles para ilustrar un método para controlar conmutadores de la matriz de las Figs. 1 y 2 con un número reducido de controladores.

#### Descripción detallada

5

10

15

20

25

35

45

La Fig. 1 ilustra una red 11 de matrices de conmutación según una realización ilustrativa. El sistema 11 de la Fig. 1 es un sistema relativamente grande que comprende una multitud de Nodos 1...Q y una Matriz de Expansión 21 también identificada como Nodo 0. En la Fig. 1, cada uno de los nodos, por ejemplo el Nodo 1, se dibuja dos veces, una a la izquierda de la Matriz de Expansión 21 y otra a la derecha de la Matriz 21. Esta representación se emplea de manera que las interconexiones, por ejemplo, 15, 17, a la Matriz de Expansión desde el lado izquierdo y derecho de las matrices "B" en cada uno de los nodos no se superponen a otras partes del dibujo y por lo tanto se muestran más claramente.

Cada uno de los Nodos 1...Q tiene una estructura de tres etapas común formada por matrices de conmutación A, B y C, interconectadas como se muestra. La Matriz de Expansión comprende una columna de "D" matrices de conmutación. Las matrices A, B, C y D se definen como sigue:

Una matriz de tipo A tiene N entradas y K salidas.

Una matriz de tipo B tiene M+P entradas y M+P salidas.

Una matriz de tipo C tiene K entradas y N salidas.

Una matriz de tipo D tiene Q entradas y Q salidas.

Además, con respecto a la topología de la Fig. 1, puede observarse que el Nodo 1 hasta el Q tienen sólo matrices de tipo A, B y C, mientras que el Nodo 0 sólo tiene matrices de tipo D. En cuanto al número de matrices, hay M matrices de tipo A en cada uno desde el nodo 1 hasta el nodo Q, hay K matrices de tipo B en cada uno desde el Nodo 1 hasta el Nodo Q, hay M matrices de tipo C en cada uno desde el nodo 1 hasta el nodo Q y hay R matrices de tipo D en el Nodo 0 en el que R = K X P. Las diferentes matrices se pueden identificar como sigue:

$A_{(m)}$  denota una matriz m de tipo A en el nodo q donde m = 1...M; y q = 1...Q.

$B_{(k)}$  denota una matriz k de tipo B en el nodo q donde k = 1...K; y q = 1...Q.

$C_{(m)}$  denota una matriz m de tipo C en el nodo q donde m = 1...M; y q = 1...Q.

$D_{(r)}$  denota una matriz r de tipo D en el nodo 0 donde r = P(k-1)+p; k = 1...K; p = 1...P.

- 30 La interconexión de las respectivas matrices A, B, C y D se define como sigue:

- 1. La salida k de la matriz  $A_{(m)}$  en el nodo q se conecta a la entrada m de la matriz  $B_{(k)}$  en el mismo nodo q, donde m = 1...M y k = 1...K.

- 2. La salida m de la matriz  $B_{(k)}$  en el nodo q se conecta a la entrada k de la matriz  $C_{(m)}$  en el mismo nodo q, donde m=1...M y k=1...K.

- 3. La salida M+p de la matriz  $B_{(k)}$  en el Nodo q se conecta a la entrada q de la matriz  $D_{(r=P(k-1)+p)}$  en el Nodo 0, donde p=1...P; k=1...K; y q=1...Q.

- 4. La salida q de la matriz  $D_{(r=P(k-1)+p)}$  en el Nodo 0 se conecta a la entrada M+p de la matriz  $B_{(k)}$  en el Nodo q, donde q=1...Q; k=1...K; y p=1...P.

Por lo tanto, se observará que las salidas M+1...M+p en cada matriz del Nodo B izquierdo y las entradas M+1...M+p en cada matriz del Nodo B derecho facilitan la implementación de las matrices tipo D de la Matriz de Expansión.

En la matriz de conmutación de la Fig. 1, un conmutador es un dispositivo que se puede activar para conectar una entrada a una salida de la misma matriz. Cada conmutador se representa mediante la notación  $S_{(nodo, tipo de matriz, número de matriz, entrada, salida)}$  ( $S_{(node, array type, array number, input, output)}$ ). Por ejemplo,  $S_{(1, A, 2, 1, 3)}$  denota el conmutador que conecta la entrada 1 a la salida 3 de la matriz 2 de tipo A en el nodo 1;  $S_{(0, D, 3, 2, 5)}$  denota el conmutador que enlaza la entrada 2 con la entrada 5 de la matriz 3 de tipo D en el nodo 0.

Empleando la convención de notación de conmutación que se acaba de discutir, los conmutadores de las matrices A, B, C y D se identifican como sigue:

- 1. El conmutador que conecta la entrada x a la salida k de la matriz m de tipo A en el nodo q se identifica mediante S<sub>(q, A, m, x, k)</sub>, donde q = 1...Q; m = 1...M; x = 1...N; k = 1...K.

- 2. El conmutador que conecta la entrada m a la salida n de la matriz k de tipo B en el nodo q se identifica mediante S<sub>(q, B, k, m, n)</sub>, donde q = 1...Q; k = 1...K; m = 1...M; n = 1...M.

- 3. El conmutador que conecta la entrada k a la salida y de la matriz m de tipo C en el nodo q se identifica mediante S<sub>(q, C, m, k, y)</sub>, donde q = 1...Q; m = 1...M; k = 1...K; y = 1...N.

- 4. El conmutador que conecta la entrada p a la salida t de la matriz r de tipo D en el nodo 0 se identifica mediante S<sub>(0, D, r, p, t)</sub>, donde r = 1...P(k-1)+p; p = 1...P; t = 1...P.

Por otra parte, en la realización ilustrativa de la Fig. 1 en discusión, una entrada de una matriz de tipo A también se ve como una entrada de la red. Una salida de una matriz de tipo C también se ve como una salida de la red. La ruta (continuidad) entre una entrada de red y una salida de red (una entrada de una matriz de tipo A y una salida de una matriz de tipo C) se puede establecer mediante la conexión en serie cinco conmutadores (S1, S2, S3, S4 y S5) donde S1 es un conmutador que conecta una entrada y una salida de la 1ª matriz de tipo A; S2 es un conmutador que conecta una entrada y una salida de la 3ª matriz de tipo D; S4 es un conmutador que conecta una entrada y una salida de la 4ª matriz de tipo B; y S5 es un conmutador que conecta la entrada y la salida de la 5ª (la última) matriz de tipo C.

Como puede apreciarse, existe más de una ruta posible (más de un conjunto de conmutadores (S1, S2, S3, S4, S5)) entre dos puntos de I/O en la red. En la realización ilustrativa, el siguiente procedimiento se utiliza para determinar todas las rutas posibles (S1, S2, S3, S4, S5) entre dos puntos de I/O en la red.

20 Primero, se definen las siguientes constantes:

5

- Q = número de nodos de I/O en la red

- N = número de entradas de cada matriz de tipo A

- N = también el número de salidas de cada matriz de tipo C

- K = número de salidas de cada matriz de tipo A

- 25 K = también el número de entradas de cada matriz de tipo C

- M = número de entradas locales (desde la matriz de tipo A) en cada matriz de tipo B

- M = también el número de entradas locales (a la matriz de tipo C) en cada matriz de tipo B

- P = número de entradas externas (desde la matriz de tipo D) en cada matriz de tipo B

- P = número de salidas externas (a la matriz de tipo D) en cada matriz de tipo B

- 30 A continuación, para un puerto  $(X = 1...(N \times M \times Q))$  y para (k = 1...K), se definen una serie de valores para las variables q, m y n como sigue:

$$q = int(X/(N \times M \times Q)) + 1$$

$$m = int(X/(N \times M \times q)) + 1$$

$$n = X - int(X/(q \times m \times N)) \times N$$

En tal caso, el conjunto de todos los conmutadores S1, S2, S3, S4, S5 disponible para interconectar un puerto "X" seleccionado con un puerto "Y" seleccionado dentro del mismo Nodo se determina como sigue para (t = 1...M) y para un puerto (Y = 1...N):

$$S1 = S_{(q, A, m, n, k)}$$

(Ecuación 1)

40

$$S2 = S_{(q, B, k, m, t)}$$

(Ecuación 2)

$$S3 = S_{(0, D, 0, 0, 0)}$$

(Ecuación 3)

$$S4 = S_{(q, B, k, m, t)}$$

(Ecuación 4)

$$S5 = S_{(q, C, t, k, Y)}$$

(Ecuación 5)

y el conjunto de conmutadores S1, S2, S3, S4, S5 para conectar un puerto "X" en un Nodo con un puerto "Y" en un Nodo diferente se determina como sigue para (t = 1...F), para (h = 1...K) y para un puerto (Y = 1...N):

| $S1 = S_{(q, A, m, n, k)}$        | (Ecuación 6) |

|-----------------------------------|--------------|

| $S2 = S_{(q, B, k, m, t)}$        | (Ecuación 7) |

| $S3 = S_{(0, D, P(k-1)+t, q, w)}$ | (Ecuación 8) |

| $S4 = S_{(w, B, k, t, h)}$        | (Ecuación 9) |

5

10

15

20

25

30

35

40

45

50

55

$S5 = S_{(w, C, h, k, Y)}$  (Ecuación 10)

Como se apreciará por los expertos en la técnica, una tarea clave en un sistema tal como el que se ilustra en la Fig. 1 es seleccionar los conmutadores apropiados en los Nodos I...Q y en la Matriz de Expansión 21 para completar la conexión cruzada deseada. Por ejemplo, si se desea conectar el puerto "1" (Puerto "X", ("X" Port)) de la matriz A en el Nodo 1 al puerto "1" (Puerto "Y", ("Y" Port)) de la matriz C en el Nodo 1, deben seleccionarse los conmutadores apropiados en el Nodo 1 (y no conmutadores en la Matriz de Expansión 21) y cerrarse para crear la ruta de señal deseada. Por lo tanto, como se señaló anteriormente, un "ruta" puede comprender un grupo o conjunto de conmutadores en serie que enlazan un par deseado de puertos ("X" e "Y") a través del sistema de hardware.

Un enfoque para llevar a cabo la selección del conmutador y la tarea de interconexión que se acaba de discutir sería el de emplear software para determinar el grupo de conmutadores apropiado en tiempo real durante el funcionamiento de la matriz de conmutación de la Fig. 1. Este software crea una tremenda sobrecarga y complejidad del software. Según la realización preferida, este enfoque se evita mediante el empleo de software para primero crear un conjunto de identificadores de conmutación basado en la arquitectura del sistema de conmutación conocida, específica, que simplifica en gran medida la selección de los conmutadores apropiados para crear una ruta deseada durante el funcionamiento en tiempo real de un sistema implementado. Por lo tanto, una de tales matrices de identificadores de conmutación se determina y se almacena preferiblemente en el sistema como parte del proceso de fabricación del sistema antes de la implementación del sistema en un sitio de usuario final. Se puede utilizar a continuación una función de indexación relativamente directa para determinar aquellos conmutadores que pueden cerrarse para lograr una interconexión deseada.

Más particularmente, en la realización ilustrativa representada en las Figs. 2 y 3 y como se muestra en la Fig. 4, después de que se establece la arquitectura del sistema de conmutación (etapa 101), el software 61 que se ejecuta en un procesador 57 de ordenador genera una matriz 55 de identificadores de conmutación (etapa 103), y almacena la matriz 55 en la memoria 59. Como se muestra en la Fig. 2, la matriz 55 se divide en sub-matrices, por ejemplo, 71, 73. Cada sub-matriz contiene todos los conjuntos de conmutadores S1, S2, S3, S4, S5 que son capaces de conectar un Puerto "X" seleccionado a un Puerto "Y" seleccionado. Por ejemplo, todos los conjuntos de conmutadores  $S_{A(1,1)}...S_{N(1,1)}$  para conectar el Puerto 1 "X" al Puerto 1 "Y" se almacenan en la sub-matriz 71, mientras que todos los conjuntos  $S_{A(1,2)}...S_{N(1,2)}$  para conectar el Puerto 1 "X" al Puerto 2 "Y" se almacenan en la sub-matriz 73 y así sucesivamente. Cada sub-matriz se determina mediante las etapas de programación de software del software 61, que puede, por ejemplo, calcular ya sea las ecuaciones 1-5 o las ecuaciones 6-10 anteriores para el par de puertos particular (X, Y), en cuestión. Tal software puede escribirse, por ejemplo, en C++, o en cualquier otro lenguaje adecuado.

Una vez que la matriz de la Fig. 2 se ha generado, por ejemplo, previo al envío y la implementación de una matriz de conmutación tal como la que se muestra en la Fig. 1, el software 63 de selección del conmutador, que en realidad selecciona un conjunto de conmutadores particular (tal como el conjunto de conmutadores S<sub>A1,1</sub>) para establecer la conexión entre un par de puertos (tal como los puertos 1,1), solo necesita emplear un índice (por ejemplo, "1,1") durante el funcionamiento en tiempo real para acceder al conjunto 71 de todos los conmutadores posibles para establecer una conexión particular puerto a puerto (etapa 105, Fig. 4). A partir de entonces, en la etapa 107 de la figura. 4, por ejemplo, el software de selección del conmutador puede realizar un procedimiento de selección del conmutador particular que emplea varios criterios, tales como los que se conocen por los expertos en la técnica, para seleccionar un par particular de conmutadores entre los que estén disponibles.

La implementación de una arquitectura de conmutación de conexión cruzada tal como la que se muestra en la Fig. 1 puede mejorarse en ciertas realizaciones al implementar un enfoque de activación del dispositivo de conmutación que permita la eliminación de un número de controladores discretos al contrarrestar el control de las bobinas de los dispositivos EM parásitos con fuerza electromotriz modulada por impulsos (EMF, Modulated Electromotive Force) para contrarrestar la conmutación por simpatía de los dispositivos cercanos. Según una realización ilustrativa, el ciclo de trabajo de la EMF y la polaridad aplicada a las rutas parasitarias se determina mediante la tolerancia de la EMF de conmutación y la proximidad del dispositivo EM simpático a los dispositivos de destino dentro de una matriz base. El resultado es que los dispositivos EM en las rutas parasitarias no conmutan para cualquiera de los dos posibles estados iniciales y el número total de controladores necesarios para grandes matrices de dispositivos EM,

## ES 2 434 765 T3

tales como, por ejemplo, relés y solenoides, se reduce en gran medida. La implementación del enfoque anterior se ilustra en relación con las Figs. 5-11.

Las Figs. 5 y 6 representan una matriz de 32 dispositivos de conmutación S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>,... S<sub>32</sub>. Los dispositivos de conmutación particulares representados son conmutadores MEMS en ménsula, pero podrían ser otros tipos de conmutadores o relés en otras realizaciones.

5

10

15

20

25

30

55

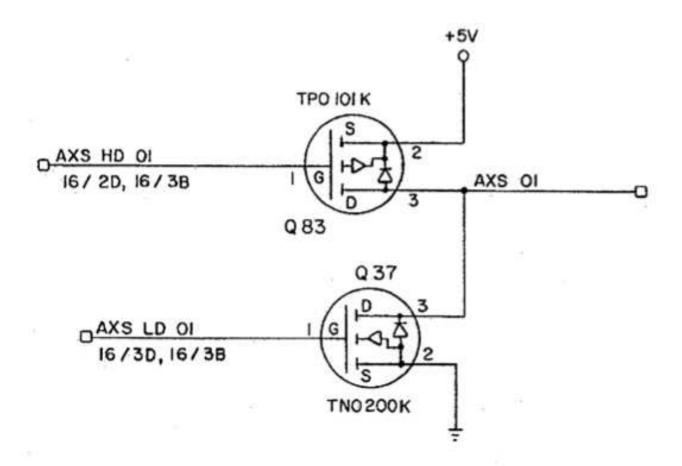

Cada uno de los conmutadores S<sub>1</sub>,... S<sub>32</sub> incluye una bobina de activación (por ejemplo, la 21 en la Fig. 9), que tiene terminales positivo ("Y") y negativo ("X"). Según la realización ilustrativa, ocho controladores terminales positivos y cuatro controladores terminales negativos bastan para conmutar ("cerrar") uno cualquiera de los 32 dispositivos de conmutación S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>,... S<sub>32</sub> seleccionado. Los ocho controladores positivos producen respectivamente señales de control, AYS\_01, AYS\_02, AYS\_03...AYS\_08; mientras los cuatros controladores negativos producen respectivamente cuatro señales de control AXS\_01, AXS\_02, AXS\_03 y AXS\_04.

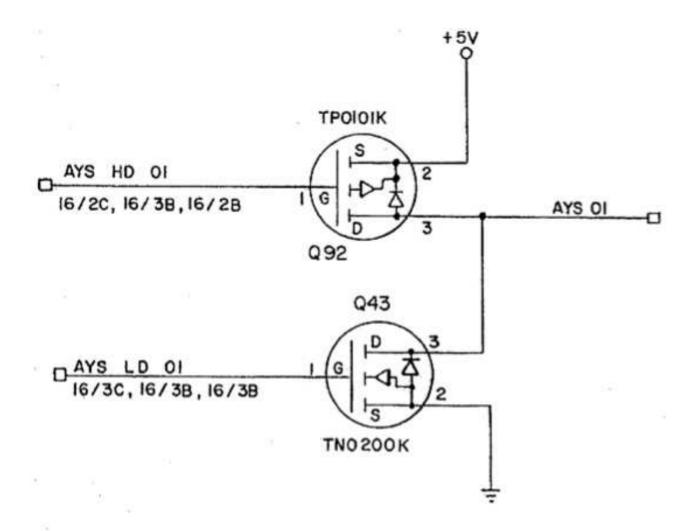

Las Figs. 7 y 8 representan un circuito controlador para generar señales de control AXS\_01 y AYS\_01, respectivamente. Estos circuitos de control pueden ser controladores MOSFET convencionales. El controlador de la Fig. 3 se activa mediante las señales de puerta AXS\_HD\_01 y AXS\_LD\_01, mientras que el de la Fig. 4 se activa mediante las señales de puerta AYS\_HD\_01 y AYS\_LD\_01.

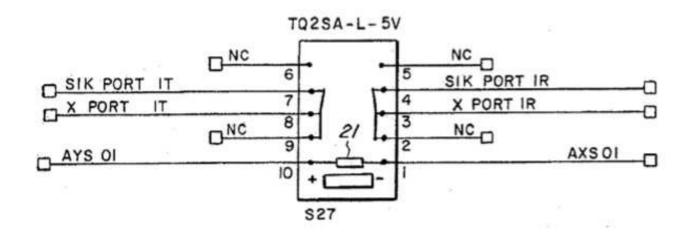

Un dispositivo de conmutación MEMS específico  $S_{27}$  se muestra aumentado en la Fig. 9. Se puede ver que la bobina 21 de este dispositivo de  $S_{27}$  se controla mediante las señales de control AYS\_01 y AXS\_01. Los terminales 7 y 4 son terminales de "señales de entrada" y los terminales 8 y 3 son "retornos de señales", respectivamente. Los campos magnéticos temporales creados por un pulso de energía en la bobina 21 inician las respectivas ménsulas  $S_{23}$ ,  $S_{24}$  para sacar y cerrar las rutas de señal respectivas. Las ménsulas 23, 24 se mantienen en su lugar mediante un imán fijo después de que termina el pulso de activación a la bobina 21.

La Fig. 10 ilustra las formas de onda del pulso utilizadas cuando se desea fijar el conmutador S<sub>27</sub>, es decir, cerrar las ménsulas 23, 24. Como se puede ver AXS\_01 aumenta hasta un nivel de tensión positivo constante durante un intervalo de tiempo t<sub>1</sub>, que puede ser por ejemplo, 200 microsegundos. Al mismo tiempo AYS\_01 cae a un nivel de tensión negativo constante en el mismo intervalo t<sub>1</sub>. Las otras señales de control "X" AXS\_02, AXS\_03 y AXS\_04 se pulsan con un tren de pulsos periódico que alterna entre un nivel de tensión negativo y un nivel de tensión positivo. Las otras señales de control "Y" AYS\_02...AYS-08 se controlan con un tren de pulsos que puede ser como, pero opuesto en polaridad, el que controla AXS\_02-04.

De esta manera, solo el conmutador S27 se proporciona con la energía necesaria para activarse o "cerrarse", mientras que la energía de pulso modulado impide la activación falsa de otros dispositivos de conmutación en la matriz. Como puede apreciarse, los otros tres conmutadores en S25, S29, S31 en la matriz de 32 conmutadores de las Figs. 5 y 6 se controlan mediante la salida AYS\_01 del circuito controlador que se muestra en la Fig. 8. Sin embargo, cada uno de estos otros conmutadores recibe una de las respectivas señales de control "X" modulada AXS\_02, AXS\_03 y AXS\_04, que impide la activación de estos tres conmutadores S25, S29, S31.

Para borrar o reiniciar S<sub>27</sub>, se utilizan las formas de onda de energía representadas en la Fig. 11. En este caso, AXS\_01 comprende un pulso negativo de duración t<sub>2</sub>, mientras AYS\_01 comprende un pulso positivo de duración t<sub>2</sub>. Las formas de onda para AXS\_02-04 y AYS\_02-08 son las mismas que las de la Fig. 10; por lo que se logra así reiniciar el conmutador S<sub>27</sub> sin activar en falso otros conmutadores en la matriz.

Con respecto al conmutador S<sub>27</sub>, el intervalo del pulso y el nivel de tensión suministrado mediante AXS\_01 y AYS\_01 puede ser el típicamente necesario para cerrar el conmutador. Tales niveles y duraciones generalmente variarán dependiendo del tipo de conmutador utilizado, por ejemplo, conmutadores MEMS o relés electromecánicos o solenoides. Además, los niveles de tensión y el ciclo de trabajo de las formas de onda moduladas por impulsos, por ejemplo, AXS\_02, AXS\_03, AXS\_04 en la Fig. 10, variará con la aplicación, pero se seleccionará en cada aplicación para ser suficiente para evitar la activación en falso de otros dispositivos en la matriz. Formas de onda análogas a las que se muestran en las Figs. 10 y 11 se utilizan para fijar y reiniciar cualquier dispositivo específico de los otros dispositivos de la matriz de 32 conmutadores. Con respecto a la matriz de las Figs. 5 y 6, puede observarse que tal matriz convencionalmente requeriría 4x8+4 (N·M+N) = 36 controladores, mientras que la realización ilustrativa emplea 12 controladores.

Los métodos según las realizaciones ilustrativas son eficaces en el direccionamiento de matrices de dispositivos EM que son simétricas (N=M), asimétricas (N>M o N<M), o asimétricas además de no ortogonales (una matriz compuesta de múltiples sub-matrices asimétricas con varios segmentos N o M).

Los expertos en la técnica apreciarán que se pueden configurar varias adaptaciones y modificaciones de la realización preferida que se acaba de describir. Por lo tanto, es de entenderse que, dentro del alcance de las reivindicaciones adjuntas, la invención puede realizarse distinta de lo específicamente descrito en la presente memoria.

## ES 2 434 765 T3

#### REIVINDICACIONES

- 1. Una matriz de conmutación que comprende:

- (a) una multitud de matrices de conmutación de tres etapas (Nodo 1...Nodo Q); y

- (b) una matriz de expansión (21), en la que una segunda etapa (B) de cada una de las matrices de conmutación de tres etapas (Nodo 1...Nodo Q) incluye una sección de expansión que comprende conmutadores que facilitan la interconexión de cada matriz de tres etapas (Nodo 1...Nodo Q) a la matriz de conmutación de expansión (21);

- (c) en la que cada una de la multitud de matrices de conmutación de tres etapas (Nodo 1...Nodo Q) comprende una matriz de primera etapa (A) que tiene N entradas y K salidas y una matriz de tercera etapa (C) que tiene K entradas y N salidas, cada matriz de segunda etapa (B) de cada matriz de conmutación de tres etapas (Nodo 1...Nodo Q) que recibe M entradas locales de la matriz de primera etapa (A) y que proporciona M salidas locales a la matriz de conmutación de tercera etapa (C), cada matriz de conmutación de la segunda etapa (B) que además proporciona P salidas a la matriz de expansión (21) y que recibe P entradas desde la matriz de expansión (21), en las que K, N, M y P son enteros; y

- (d) en la que la matriz de conmutación comprende una multitud de nodos y en la que, en cada nodo, hay K matrices de segunda etapa (B), M matrices de primera etapa (A) y M matrices de tercera etapa (C), y en la que el número de matrices de conmutación de expansión en la matriz de expansión (21) es igual a K x P.

- 2. La matriz de conmutación de la reivindicación 1:

- en la que la sección de expansión de cada matriz de segunda etapa (B) de cada matriz de conmutación de tres etapas (Nodo 1...Nodo Q) incluye un multitud de salidas de expansión, cada una conectada como una entrada a una respectiva matriz de conmutación de expansión (21) y en la que cada respectiva matriz de conmutación de expansión (21) proporciona una multitud de salidas de expansión, cada una conectada como un retorno de entrada a una respectiva matriz de conmutación de segunda etapa (B).

- 3. La matriz de conmutación de la reivindicación 1 o 2 en la que cada matriz de conmutación de expansión (21) es una matriz cuadrada (D) que tiene Q entradas y Q salidas, donde Q es un entero.

- 4. La matriz de conmutación de la reivindicación 1 o 2 en la que la matriz de expansión (21) comprende una sola columna de las matrices de conmutación cuadradas (D).

- 5. La matriz de conmutación de la reivindicación 1 o 2 en la que la matriz de expansión (21) incluye una multitud de matrices cuadradas (D), teniendo cada una Q entradas y Q salidas y en las que las segundas etapas (B) de las matrices de tres etapas (Nodo 1...Nodo Q) incluyen cada una 1...M+1...M+P etapas verticales conectadas a las matrices cuadradas de la matriz de expansión (21).

- 6. La matriz de conmutación de la reivindicación 4 en la que cada matriz cuadrada tiene Q entradas y Q salidas y en la que las segundas etapas de las matrices de tres etapas incluyen cada una 1...M+1...M+P etapas verticales que se conectan a las matrices cuadradas de la matriz de expansión.

35

5

10

15

20

25

30

FIG. 2

57

MEMORIA

SOFTWARE DE GENERACIÓN DE LA MATRIZ DE CONMUTACIÓN

MATRIZ

SOFTWARE DE SELECCIÓN DE CONMUTACIÓN

SOFTWARE DE SELECCIÓN DE CONMUTACIÓN

F/G. 3

FIG. 4

FIG. 7

F1G. 8

F1G. 9