# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 435 427

51 Int. Cl.:

**G06F 13/16** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 08.08.2007 E 07813910 (2)

(97) Fecha y número de publicación de la concesión europea: 18.09.2013 EP 2057548

(54) Título: Procedimiento y aparato para activar la señalización cooperativa de una interrupción de bus compartido en un subsistema de memoria multirrango

(30) Prioridad:

14.08.2006 US 822279 P 30.11.2006 US 565034

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 19.12.2013

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121, US

(72) Inventor/es:

WOLFORD, BARRY JOE y SULLIVAN, JR., JAMES EDWARD

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

### **DESCRIPCIÓN**

Procedimiento y aparato para activar la señalización cooperativa de una interrupción de bus compartido en un subsistema de memoria multirrango

#### Campo

10

15

20

25

30

45

50

55

5 La presente divulgación se refiere, en general, al campo de los sistemas de memoria y, más concretamente, a la señalización entre un controlador de la memoria y la memoria en un sistema de memoria.

#### **Antecedentes**

Los sistemas de memoria son utilizados ampliamente hoy en día en sistemas de procesamiento para almacenar los datos requeridos por diversas entidades de procesamiento. Un sistema de memoria incluye en términos generales, un controlador de la memoria que gestiona el acceso a la memoria. La memoria está típicamente configurada en una estructura de matriz conformada mediante filas y columnas de celdas de memoria, siendo capaz cada celda de memoria de almacenar un bit de datos. Se puede acceder a un bloque de celdas de memoria por una entidad de procesamiento, u otra fuente, suministrando la dirección adecuada al controlador de la memoria. La dirección procedente de la entidad de procesamiento puede ser enviada al controlador de la memoria a través de un bus con la dirección de fila que ocupa los bits de orden superior y la dirección de columna de inicio que ocupa los bits de orden inferior. El controlador de la memoria utiliza un esquema de multiplexación para enviar la dirección de fila a la memoria sequida por la dirección de columna de inicio.

Cuando una entidad de procesamiento solicita acceso a un bloque de memoria, envía un comando de leer o escribir al controlador de la memoria. Cada comando de leer y escribir incluye una dirección. La manera en que el controlador de la memoria ejecuta el comando depende de si la unidad de procesamiento está intentando a acceder a una página abierta de la memoria. Una "página" está normalmente asociada con una fila de memoria, y una "página abierta" significa que la memoria está apuntando a una fila de memoria y requiere solo la dirección de la columna de inicio y un Estroboscopio de Acceso a Columna (CAS) para acceder al bloque de memoria. Para acceder a una página de memoria abierta, el controlador de la memoria debe presentar la dirección de fila y un Estroboscopio de Acceso a Fila (RAS) a la memoria para desplazar el puntero antes de presentar la dirección de la columna de inicio y el CAS a la memoria.

Diversas memorias son utilizadas hoy en día en los sistemas de memoria. Una Memoria de Acceso Aleatorio Dinámica Síncrona (SDRAM) es solo un ejemplo. Cuando una entidad de procesamiento está escribiendo en una SDRAM o en otro dispositivo de memoria los datos son transmitidos a través de un bus de datos entre un controlador de la memoria y la memoria. Una máscara de datos puede ser utilizado por el controlador de la memoria para enmascarar los datos sobre el bus de datos. Cuando la máscara de datos es no aseverada, los datos dispuestos en el bus de datos se escribirán en la memoria. Cuando la máscara de datos es aseverada, los datos dispuestos sobre el bus de datos serán ignorados, y la operación de escritura no se llevará a cabo.

La máscara de datos se utiliza solo durante las operaciones de escritura. Cuando una unidad de procesamiento no está escribiendo en la SDRAM, u otro dispositivo de memoria, el controlador de la memoria sitúa en el estado triple la máscara de datos. De esta manera, existe una oportunidad para utilizar la máscara de datos para otras finalidades cuando la unidad de procesamiento no está llevando a cabo una operación de escritura. Mediante la utilización de la máscara de datos de la manera indicada, pueden producirse comunicaciones adicionales entre el controlador de la memoria y la memoria sin incrementar el número de clavijas en el dispositivo de memoria.

40 El documento US 5,860,080 divulga un sistema de memoria de acuerdo con el preámbulo de la reivindicación 1.

#### Sumario

Se divulga un sistema de memoria. El sistema de memoria incluye unos primero y segundo dispositivos de memoria, y un controlador de la memoria configurado para activar selectivamente uno de los dispositivos de memoria, teniendo el controlador de la memoria una primera línea acoplada a los primero y segundo dispositivos de memoria, y una segunda línea acoplada a los primero y segundo dispositivos de memoria. El primer dispositivo de memoria está configurado para proporcionar una notificación al controlador de la memoria sobre la primera línea y el segundo dispositivo de memoria está configurado para proporcionar una notificación al controlador de la memoria sobre la segunda línea. El primer dispositivo de memoria está también configurado para no cargar la primera línea y el segundo dispositivo de memoria está también configurado para no cargar la segunda línea cuando el controlador de la memoria está escribiendo en el dispositivo de memoria activado.

Se divulga un procedimiento de comunicación entre un controlador de la memoria y una memoria que presenta unos primero y segundo dispositivos de memoria. El controlador de la memoria incluye una línea acoplada a los primero y segundo dispositivos de memoria. El procedimiento incluye la provisión de una notificación desde el primer dispositivo de memoria hasta el controlador de la memoria sobre la primera línea, activando el segundo dispositivo de memoria con el fin de que el controlador de la memoria escriba en el segundo dispositivo de memoria, y la colocación

del primer dispositivo de memoria en un estado en el que no cargue la línea cuando el controlador de la memoria está escribiendo en el segundo dispositivo de memoria.

Otros aspectos de la presente invención se pondrán sin dificultad de manifiesto para los expertos en la materia a partir de la siguiente descripción detallada, en la que se muestran y describen, a modo de ilustración, diversas formas de realización de la invención. Como se advertirá, la invención es capaz de realizar otras y diferentes formas de realización y sus diversos detalles son susceptibles de modificación en otros diversos aspectos, sin que ninguno se aparte de la presente invención. De acuerdo con ello, los dibujos y la descripción detallada deben considerarse de naturaleza ilustrativa y no restrictiva.

La invención se define de acuerdo con el sistema de la reivindicación 1 y con el procedimiento de la reivindicación 8.

#### 10 Breve descripción de los dibujos

5

25

30

45

50

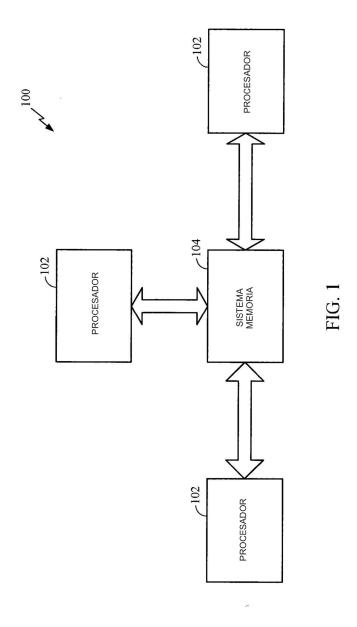

La FIG. 1 es un diagrama de bloques conceptual que ilustra un ejemplo de un sistema de procesamiento;

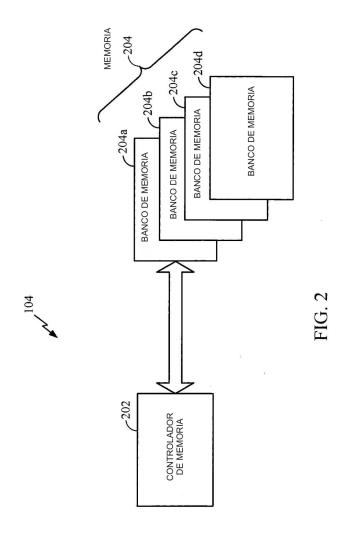

la FIG. 2 es un diagrama de bloques conceptual de un sistema de memoria;

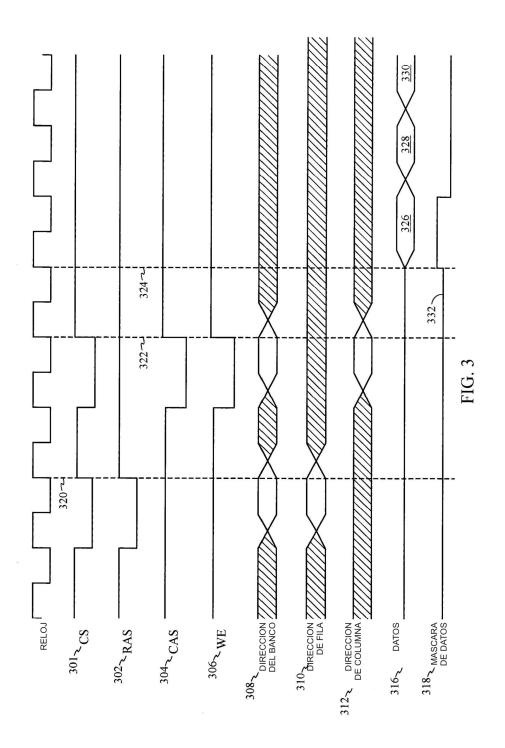

la FIG. 3 es un diagrama de temporización que ilustra un ejemplo de una operación de escritura en un sistema de memoria;

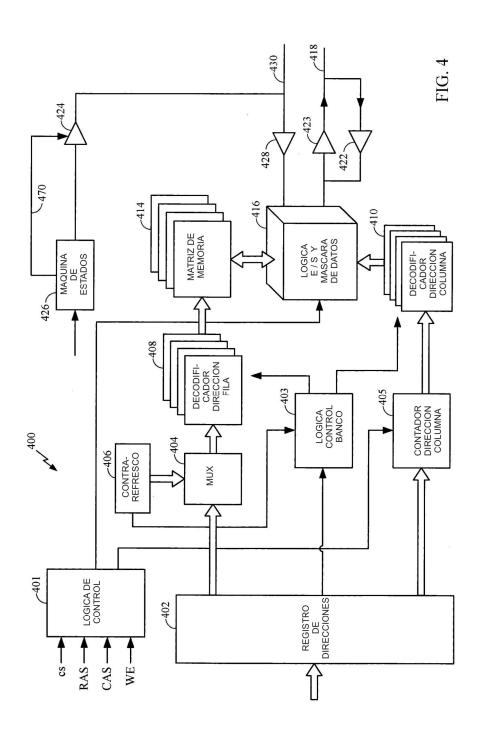

15 la FIG. 4 es un diagrama de bloques funcional que ilustra un ejemplo de un dispositivo de memoria;

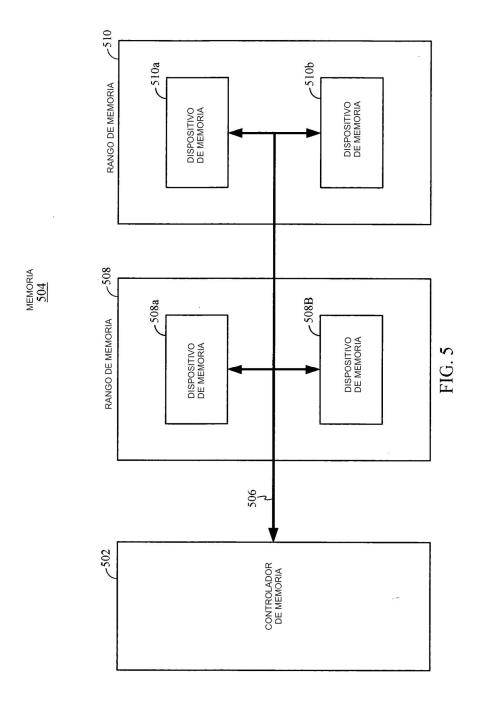

la FIG. 5 es un diagrama de bloques conceptual que ilustra otro ejemplo de un sistema de memoria;

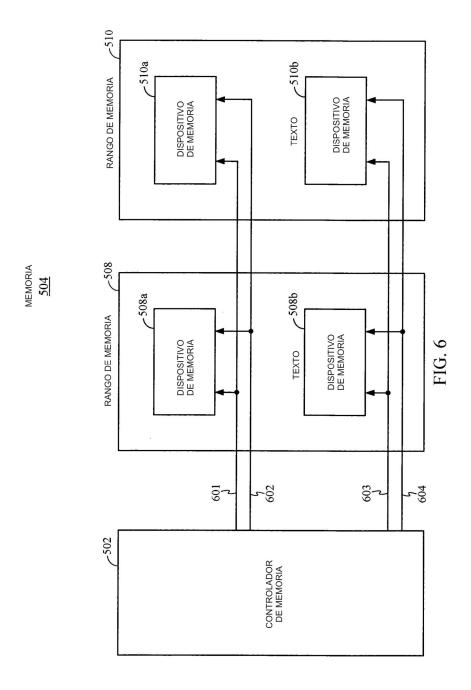

la FIG. 6 es un diagrama de bloques conceptual que ilustra un ejemplo de la señalización en el sistema de memoria de la FIG. 5; y

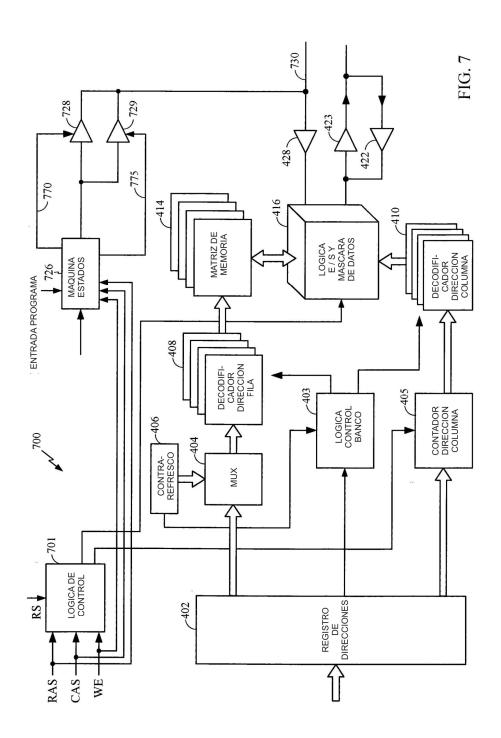

la FIG. 7 es un diagrama de bloques funcional que ilustra otro ejemplo de un dispositivo de memoria.

#### 20 Descripción detallada

La descripción detallada expuesta a continuación en combinación con los dibujos adjuntos tiene por objeto la descripción de diversas formas de realización de la presente invención y no pretende representar las únicas formas de realización en las cuales se pueda llevar a la práctica la presente invención. La descripción detallada incluye detalles específicos con el fin de proporcionar una cabal comprensión de la presente invención. Sin embargo, debe resultar evidente para los expertos en la materia que la presente invención puede llevarse a la práctica sin estos detalles específicos. En algunos casos, se muestran estructuras y componentes sobradamente conocidos en forma de diagrama de bloques con el fin de evitar oscurecer los conceptos de la presente invención.

La FIG. 1 es un diagrama de bloques conceptual que ilustra un ejemplo de un sistema de procesamiento. El sistema 100 de procesamiento puede ser un conjunto de dispositivos que cooperen para llevar a cabo una o más funciones de procesamiento. Aplicaciones típicas para el sistema 100 de procesamiento incluyen, pero no se limitan a, ordenadores de escritorio, ordenadores portátiles, servidores, teléfonos celulares, asistentes personales digitales (PDA), consolas para juegos, localizadores, módems, equipos de audio, dispositivos médicos, de automoción, equipos de vídeo, equipos industriales y cualquier otra máquina o dispositivo capaz de información de procesamiento, recuperación y almacenamiento.

El sistema 100 de procesamiento se muestra con un sistema 104 de memoria al que se puede acceder mediante un número indeterminado de entidades de procesamiento. En la configuración mostrada en la FIG. 1, se muestran tres procesadores 102 en comunicación con el sistema 104 de memoria. Cada procesador 102 puede ser un procesador de propósito general, como por ejemplo un microprocesador, o un procesador de propósito especial, como por ejemplo un procesador digital de la señal (DPS), un circuito integrado específico de la aplicación (ASIC), un controlador de acceso directo a memoria (DMA), un puente, un componente lógico programable o cualquier otra entidad que requiera acceso al sistema 104 de memoria.

La FIG. 2 es un diagrama de bloques conceptual de un sistema de memoria. El sistema 104 de memoria incluye un controlador 202 de la memoria que gestiona el acceso a la memoria 204. La memoria 204 se muestra en la FIG. 2 como un dispositivo de memoria de múltiples bancos con cuatro bancos 204a a 204d, pero puede tener un número indeterminado de bancos dependiendo de la aplicación concreta. El dispositivo de memoria multibanco puede ser considerado como una serie de memorias separadas integradas en una única pieza de silicio. En formas de realización alternativas del sistema 104 de memoria, el controlador 202 de la memoria puede estar configurado para gestionar el acceso a múltiples dispositivos de memoria, siendo cada dispositivo de memoria un banco único o un dispositivo de múltiples bancos. Los expertos en la materia apreciarán sin dificultad que los diversos conceptos descritos a lo largo de la presente divulgación pueden ser aplicados a sistema de memoria con diferentes configuraciones.

El controlador 202 de la memoria puede ser cualquier entidad que controle la operación de uno o más dispositivos de memoria incluyendo un chip de controlador de la memoria dedicado, un controlador que directamente controle la memoria, un conjunto de circuitos de controlador dispuestos sobre el dispositivo de memoria, o cualquier otra dispo-

sición apropiada. Cada dispositivo de memoria puede ser cualquier tipo de dispositivo de almacenamiento temporal, como por ejemplo una SDRAM, DRAM, o RAM, o un dispositivo de almacenamiento a largo plazo, como por ejemplo una memoria flash, una memoria ROM, una memoria EPROM, una memoria EEPROM, etc. En este ejemplo, los dispositivos de memoria se describirán en el contexto de una SDRAM, sin embargo, los diversos conceptos descritos a lo largo de la presente divulgación pueden extenderse a otros dispositivos de memoria.

5

10

30

35

40

45

50

55

60

Un ejemplo de una operación de escritura en el dispositivo de memoria se describirá con referencia al diagrama de temporización de la FIG. 3. El dispositivo de memoria es activado mediante la aserción de la selección de chip (CS) 301. Antes de que se pueda llevar a cabo una operación de lectura o escritura en un banco dentro del dispositivo de memoria, se debe abrir una fila en ese banco. Esto se lleva a cabo mediante el envío tanto de la dirección 308 del banco como de la dirección 310 de la fila hasta el dispositivo de memoria y aseverando el CS 301 y la RAS 302 mediante su inserción dentro de un estado de lógica "0" del tiempo 320. En este ejemplo, todas las señales de control, excepto por lo que se refiere a la máscara de datos son "aseveradas" con un estado de lógica "0", sin embargo, las polaridades pueden ser cambiadas en la práctica.

Una vez que una fila está abierta en un dispositivo de memoria, el controlador de la memoria puede escribir de o leer 15 a esa fila. En el tiempo 322, el controlador de la memoria inicia una operación de lectura mediante el envío de la dirección 308 de banco y de la dirección 312 de columna de inicio en el dispositivo de memoria y aseverando el CS 301, el CAS 304 y la activación de escritura (WE) 306. Después de un retardo predeterminado que sigue a la aserción de la WE 306, el controlador de la memoria comienza a transmitir los datos que deben ser escritos en el dispositivo de memoria sobre el bus 316 de datos (véase el tiempo 324). El dispositivo de memoria ignorará los datos 20 dispuestos sobre el bus 316, y no llevará a cabo una operación de escritura, cuando la máscara de datos es aseverada. En este ejemplo, la máscara de datos es aseverada (esto es, insertada en un estado de lógica "1") durante la primera ocupación 326 de datos. Como resultado de ello, esos datos no son escritos en el dispositivo de memoria. Durante las segunda 328 y tercera 330 ocupaciones de datos, la máscara de datos es no aseverada, y los datos transmitidos sobre el bus 316 son escritos en el dispositivo de memoria. Como se indicó con anterioridad, la polari-25 dad de una máscara de datos aseverada se escoge en este ejemplo por razones de conveniencia de la exposición, pero puede ser cualquier polaridad en la práctica. Antes de, por ejemplo, el tiempo 332, y el siguiente, la operación de escritura, el bus 316 de datos y la máscara 318 de datos no están cargadas, por ejemplo, accionadas en un estado de alta impedancia o estado triple.

La FIG. 4 es un diagrama de bloques funcional que ilustra un ejemplo 400 de memoria. El dispositivo 400 de memoria incluye una lógica 401 de control que recibe una CS, un RAS, un CAS y una WE procedente del controlador de la memoria (no mostrado) y genera los desencadenadores apropiados para llevar a cabo las operaciones de lectura y escritura.

El dispositivo 400 de memoria incluye también un registro 402 de memorias el cual recibe una dirección procedente del controlador de la memoria. El registro 402 de memorias separa las direcciones, enviando la dirección del banco a la lógica 403 de control del banco, la dirección de la fila a un multiplexador 404 y la dirección de la columna de inicio a un contador 405 de dirección de la columna. La lógica 403 de control del banco selecciona los descodificadores a partir de los descodificadores 408, 410 de dirección de fila y columna en base a la dirección del banco. El multiplexador 404 multiplexa la dirección de fila a partir del registro 402 de direcciones con la salida procedente de un contador 406 de refresco hasta el descodificador seleccionado existente en el descodificador 418 de dirección de fila. El contador 406 de refresco es utilizado para generar una serie de direcciones de fila durante un periodo de refresco. El descodificador seleccionado del descodificador 408 de dirección de fila descodificada es suministrada a la matriz 414 de memoria para abrir una fila en el banco de memoria controlado por el descodificador seleccionado del descodificador 408 de dirección de fila.

Una vez que la fila está abierta en el banco de memoria, la dirección de columna de inicio es generada de salida a partir del contador 405 de dirección de columna cuando recibe un desencadenador procedente de la lógica 401 de control. Posteriores desencadenadores procedentes de la lógica 401 de control son utilizados para incrementar el contador 405 de dirección de columna para crear una serie de direcciones de columna suficientes para acceder a un bloque de memoria de la fila de bancos de memoria para completar la operación de lectura y escritura. La dirección de columna es suministrada al descodificador en el descodificador 410 de dirección de columna seleccionado por la lógica 405 de control de banco. El descodificador seleccionado descodifica la dirección de columna y proporciona la dirección descodificada a una unidad 416 de E / S y de máscara de datos. Una señal procedente de la lógica 401 de control es también suministrada a la lógica 416 de E / S y de máscara de datos para indicar si la transacción del bus es una operación de lectura o escritura. En el caso de que sea una operación de lectura, el contenido de la matriz 414 de memoria especificada por la dirección del banco, fila, y columna es leída dentro de la lógica 416 de E / S y de máscara de datos antes de ser transmitida al controlador de la memoria por un excitador 423 del bus de datos a través de un excitador 418 del bus. En el caso de una operación de escritura, los datos situados en el bus 418 de datos son suministrados a la lógica 416 de E / S y de máscara de datos mediante un receptor 422 del bus. La máscara 430 de datos es también suministrada a la lógica 416 de E / S y de máscara de datos mediante un receptor 428 de la máscara de datos. Si la máscara de datos es no aseverada, la lógica 416 de E / S y de máscara de datos escribe los datos en la dirección especificada en la matriz 414 de memoria. Si, por otro lado, la máscara de datos es aseverada, los datos son ignorados y la operación de escritura no se lleva a cabo.

Como se analizó con anterioridad, la máscara de datos está en un estado triple excepto cuando el controlador de la memoria está escribiendo en el dispositivo 400 de memoria. Durante ese tiempo, la máscara de datos puede ser utilizada para proporcionar información o algún tipo de notificación al controlador de la memoria. En una configuración del dispositivo 400 de memoria, la máscara de datos puede ser utilizada para indicar al controlador de la memoria que ha habido un cambio en el estado del dispositivo 400 de memoria. Este concepto puede ser utilizado para eliminar la necesidad de que el controlador de la memoria sondee el estado del dispositivo 400 de memoria y provoque que el controlador de la memoria sea accionado por sucesos. A modo de ejemplo, y sin limitación, el dispositivo 400 de memoria puede utilizar la máscara de datos para indicar un cambio de la temperatura. Como alternativa, o además de, la máscara de datos puede ser utilizada para indicar un error en la temporización, como por ejemplo un error de refresco. La máscara de datos puede también ser utilizada para indicar un error ECC (código de corrección de errores). Los expertos en la materia estarán en condiciones de determinar sin dificultad la información o los tipos de notificaciones mejor indicados para cualquier aplicación concreta.

5

10

15

20

35

55

60

Una máquina 426 de estados, u otra entidad, es utilizada para vigilar los cambios del estado del dispositivo 400 de memoria. Cuando se detecta un cambio, una señal o interrupción es generada de salida procedente de la máquina 426 de estados y suministrada a la entrada del excitador 424 de la máscara de datos. La máquina 426 de estados proporciona también una señal 470 de activación al excitador 424 de la máscara de estados. La señal 470 de activación es inhabilitada a partir del excitador 424 de la máscara de datos cuando se está llevando a cabo una operación de escritura. Para inhabilitar la señal de activación, el excitador 424 de la máscara de datos es forzado hasta una condición de estado triple, la cual permite que el controlador de la memoria utilice la máscara de datos durante la operación de escritura. En una forma de realización, la máquina 426 de estados incluye un temporizador interno (no mostrado) cuya salida controla la señal de activación. El temporizador interno (no mostrado) es desencadenado o activado cuando la WE es aseverado y permanece activado durante un periodo de tiempo suficiente para completar la operación de escritura. La señal de activación es suprimida del excitador 424 de la máscara de datos mientras el temporizador interno (no mostrado) está activado.

La FIG. 5 es un diagrama de bloques conceptual que ilustra otro ejemplo de un sistema de memoria. En este ejemplo, un controlador 502 de la memoria es mostrado en comunicación con una memoria 504 de dos rangos sobre un bus 506 de datos de 32-bits. El primer rango 508 incluye dos dispositivos 508a - 508b de memoria con una anchura de 16-bits conectados entre sí para soportar una conexión de bus de 32-bits. A modo de ejemplo, el dispositivo 508a de memoria puede ser utilizado para los bits de orden inferior y el dispositivo 508b de memoria puede ser utilizado para los bits de orden superior de cualquier transacción del bus. El segundo rango 510 incluye también dos dispositivos 510a - 510b de memoria con una amplitud de 16-bits conectados entre sí de manera similar. Cada dispositivo 508a, 508b, 510a, 510b de memoria puede ser un dispositivo de banco único o de banco múltiple.

El esquema de señalización y direccionamiento entre el controlador 502 de la memoria y la memoria 504 es similar al descrito en conexión con la FIG. 3 con la una CS común para cada dispositivo de memoria de un rango. Esta CS común puede ser designada como una selección de rango (RS) porque selecciona todos los dispositivos de memoria de un rango. En este ejemplo, el controlador 502 de la memoria envía una dirección sobre un bus 506 de datos a los dispositivos de memoria del rango seleccionado y asevera un RAS para abrir una fila en un banco de un dispositivo de memoria y asevera un CAS para leer desde o escribir hacia esa fila. En el caso de una operación de escritura, el controlador de la memoria asevera también una WE.

40 La FIG. 6 es un diagrama de bloques conceptual que ilustra un ejemplo de la señalización de la máscara de datos del dispositivo del sistema de memoria de la FIG. 5. La máscara de datos puede ser suministrada para cada calle de bytes situada sobre el bus 506 de datos (véase la FIG. 5). Dado que hay cuatro calles de bytes sobre el bus (esto es, 32-bits), hay cuatro máscaras 601 a 604 de datos. Los dispositivos 508a, 510a de memoria conectados a las dos calles de bytes que acarrean los bits de orden inferior reciben dos máscaras 601, 602 de datos. Los dispositivos 45 508b, 510b de memoria conectados a las dos calles de bytes que acarrean los bits de orden superior reciben las otras dos máscaras 603, 604 de datos. Las cuatro máscaras 601 a 604 de datos son utilizadas para facilitar la transmisión de datos entre el controlador 502 de la memoria y la memoria 504 cuando solo se utiliza una porción del bus de datos. A modo de ejemplo, una transición del bus puede requerir solo la escritura de un único byte en la memoria 504. El controlador 502 de la memoria puede llevar a cabo esta transición del bus mediante la transmisión de 50 los datos mediante una única calle de bytes del bus de datos y aseverando la máscara de datos para las otras calles de bytes. Las máscaras de datos son utilizadas por el rango de memoria con la RS aseverada para determinar sobre qué calle de bytes los datos están siendo transmitidos.

Las máscaras 601 a 604 de datos pueden también ser utilizadas por la memoria 504 para indicar un cambio del estado de acuerdo con lo analizado con anterioridad en conexión con la FIG. 4. Una máscara de datos diferente puede ser asignada a cada dispositivo 508a – 508b, 510a – 510b de memoria para proporcionar una señal o una interrupción al controlador de la memoria cuando no se esté llevando a cabo una operación de escritura. A modo de ejemplo, la primera máscara 601 de datos puede ser asignada al dispositivo 508a de memoria manipulando los bits de orden inferior del primer rango 508, la segunda máscara 602 de datos puede ser asignada al dispositivo 510a de memoria que manipula los bits de orden inferior del segundo rango 510, la tercera máscara 603 de datos puede ser asignada al dispositivo 508b de memoria que manipula los bits de orden superior del primer rango 508, y la cuarta máscara 601 de datos puede ser asignada al dispositivo 510b de memoria que manipula los bits de orden superior del segundo rango 510. El controlador de la memoria puede determinar cuál de los cuatro dispositivos 508a – 508b.

510a – 510b está enviando información o una notificación en base a la concreta máscara de datos que acarrea la señal o la interrupción. Las cuatro máscaras 601 a 604 de datos pueden no ser cargadas por los dispositivos 508a, 508b, 510a, 510b de memoria durante una operación de escritura en cualquiera de los dispositivos de memoria. Pueden ser utilizados diversos procedimientos para asegurar que las máscaras 601 a 604 de datos no son cargadas por los dispositivos 508a, 508b, 510a, 510b de memoria durante una operación de escritura incluyendo la condición de alta impedancia de las líneas, la terminación de las líneas, las técnicas de conmutación, etc.

5

10

15

35

40

45

50

La FIG. 7 es un diagrama de bloques funcional de un dispositivo de memoria de la FIG. 6. En este ejemplo, la lógica 701 de control recibe el RAS, el CAS, y la WE desde el controlador de la memoria (no mostrado). Con la RS aseverada la lógica 701 de control genera los desencadenadores apropiados para llevar a cabo las operaciones de lectura y escritura. La lógica 701 de control no genera ningún desencadenador si la RS es denegada.

El RAS, el CAS, y la WE son suministradas a la máquina 726 de estados con independencia del estado de la RS. Como se expuso con anterioridad en conexión con la FIG. 4, la WE puede ser utilizada para desencadenar un temporizador interno (no mostrado) que suprima la señal de activación del excitador 728 de la máscara de datos mientras el temporizador interno está activado. El temporizador interno es activado durante un periodo de tiempo suficiente para completar una operación de escritura en un dispositivo de memoria en cualquier rango del sistema de memoria. Cuando el temporizador interno no está activado, el excitador 728 de la máscara de datos puede ser utilizado para enviar una interrupción o una señal al controlador de la memoria para suministrar una notificación de un cambio de estado.

En una forma de realización, la máscara de datos utilizada por el dispositivo 700 de memoria para indicar un cambio 20 de estado, es programable. En esta forma de realización, un excitador de la máscara de datos, ya sea el excitador 728 o 729 de la máscara de datos, son suministrados para cada cambio de estado. Como se muestra en la FIG. 7. un fabricante de equipamiento, un distribuidor, y / o un usuario pueden seleccionar uno de los dos excitadores de la máscara de datos para actuar como una interrupción a través de una entrada de programa en la máquina 726 de estados. En respuesta a la entrada de programa, la máguina 726 de estados puede seleccionar el excitador 728 de la máscara de estados mediante la activación de la señal 770 de activación para excitar la máscara 730 de datos. En 25 particular, la máquina 726 de estados activa el excitador 728 de la máscara de estados en tanto en cuanto el tiempo interno (no mostrado) esté activado. Mediante la inhabilitación de la señal 775 de activación, el otro excitador 729 de la máscara de datos es inhabilitado por la máquina 726 de estados, forzando a ese excitador 729 de la máscara de estados hasta una condición de estado triple. Un cambio de programación puede llevarse a cabo para seleccionar el 30 otro excitador de la máscara de estados para conectar el temporizador interno con el otro excitador de la máscara de estados e inhabilitar el excitador 728 original de la máguina de estados.

Los diversos bloques lógicos, módulos, circuitos, elementos, y / o componentes descritos ilustrativos en conexión con las formas de realización divulgadas en la presente memoria pueden ser implementados o ejecutados con un procesador de propósito general, un procesador digital de la señal (DSP), un circuito integrado específico de la aplicación (ASIC), una matriz de puertas programable sobre el terreno (FPGA) u otro componente lógico programable, puerta discreta o lógica de transistor, componentes de hardware discretos o cualquier combinación de estos diseñada para llevar a cabo las funciones descritas en la presente memoria. Un procesador de propósito general puede ser un microprocesador pero, como alternativa, el procesador puede ser cualquier procesador general, controlador, microcontrolador o máquina de estados. Un procesador puede también ser implementado como una combinación de componentes informáticos, por ejemplo una combinación de un DSP y un microprocesador, una pluralidad de microprocesadores, uno o más microprocesadores en combinación con un núcleo de DSP, o cualquier otra combinación de este tipo.

Los procedimientos o algoritmos descritos en conexión con las formas de realización divulgadas en la presente memoria pueden ser materializados directamente en hardware, en un módulo de software ejecutado por un procesador, o en una combinación de los dos. Un módulo de software puede residir en una memoria RAM, en una memoria flash, en una memoria ROM, en una memoria EPROM, en una memoria EEPROM, registros, disco duro, disco extraíble, un CD-ROM o cualquier otra forma de medio de almacenamiento conocido en la técnica. Un medio de almacenamiento puede ser acoplado en un procesador de manera que el procesador pueda leer información desde, y escribir información hacia, el medio de almacenamiento. Como alternativa, el medio de almacenamiento puede formar parte integrante del procesador.

#### REIVINDICACIONES

1.- Un sistema de memoria, que comprende:

5

10

30

35

50

unos primero y segundo dispositivos de memoria; y

un controlador de la memoria configurado para activar selectivamente uno de los dispositivos de memoria, incorporando el controlador de la memoria una primera línea acoplada a los primero y segundo dispositivos de memoria, y una segunda línea acoplada a los primero y segundo dispositivos de memoria; en el que el primer dispositivo de memoria está configurado para proporcionar una notificación al controlador de la memoria sobre la primera línea, y el segundo dispositivo de memoria está configurado para proporcionar una notificación al controlador de la memoria sobre la segunda línea, y caracterizado porque el primer dispositivo de memoria está configurado para no cargar la primera línea cuando el controlador de la memoria está escribiendo en el segundo dispositivo de memoria activado y el segundo dispositivo de memoria está configurado para no cargar la segunda línea cuando el controlador de la memoria está escribiendo en el primer dispositivo de memoria activado.

- 2.- El sistema de memoria de la reivindicación 1, en el que el primer dispositivo de memoria incluye un excitador configurado para proporcionar su notificación al controlador de la memoria sobre la primera línea y el segundo dispositivo de memoria incluye un excitador configurado para proporcionar su notificación al controlador de la memoria sobre la segunda línea, y en el que cada uno de los dispositivos de memoria está también configurado para poner en estado triple su excitador para no cargar las primera y segunda líneas cuando el controlador de la memoria está escribiendo en el dispositivo de memoria activado.

- 3.- El sistema de memoria de la reivindicación 2, en el que el primer dispositivo de memoria comprende también un medio para programar su excitador para proporcionar la notificación del primer dispositivo de memoria al controlador de la memoria, y el segundo dispositivo de memoria comprende un medio para programar su excitador para proporcionar la notificación del segundo dispositivo de memoria al controlador de la memoria.

- 4.- El sistema de memoria de la reivindicación 2, en el que el controlador de la memoria está también configurado para señalar una operación de escritura en un dispositivo de memoria activado, estando cada uno de los dispositivos de memoria configurado para poner en el estado triple su excitador en respuesta a la señal.

- 5.- El sistema de memoria de la reivindicación 1, que comprende también unos primero y segundo rangos, comprendiendo el primer rango una primera pluralidad de dispositivos de memoria que incluye el primer dispositivo de memoria, y comprendiendo el segundo rango una segunda pluralidad de dispositivos de memoria que incluye el segundo dispositivo de memoria, y en el que el controlador de la memoria está también configurado para activar el primer dispositivo de memoria mediante la activación del primer rango y activar el segundo dispositivo de memoria mediante la activación del segundo rango.

- 6.- El sistema de memoria de la reivindicación 1, en el que el controlador de la memoria está también configurado para proporcionar una máscara de datos sobre las primera y segunda líneas cuando el controlador de la memoria está escribiendo en el dispositivo de memoria activado.

- 7.- El sistema de memoria de la reivindicación 1, en el que la notificación proporcionada al controlador de la memoria por el primer dispositivo de memoria indica un cambio de estado del primer dispositivo de memoria y la notificación proporcionada al controlador de la memoria por el segundo dispositivo de memoria indica un cambio de estado del segundo dispositivo de memoria.

- 8.- Un procedimiento de comunicación entre un controlador de la memoria y una memoria que incorpora unos primero y segundo dispositivos de memoria, incorporando el controlador de la memoria una primera línea acoplada a los primero y segundo dispositivos de memoria y una segunda línea acoplada a los primero y segundo dispositivos de memoria, comprendiendo el procedimiento:

- la provisión de una notificación desde el primer dispositivo de memoria hasta el controlador de la memoria sobre la primera línea y una notificación desde el segundo dispositivo de memoria hasta el controlador de la memoria sobre la segunda línea;

la activación de manera selectiva del primer dispositivo de memoria o del segundo dispositivo de memoria con el fin de que el controlador de la memoria escriba en el dispositivo de memoria activado; y caracterizado por:

la colocación del primer dispositivo de memoria en un estado en el que no carga la primera línea cuando el controlador de la memoria está escribiendo en el segundo dispositivo de memoria activado; y

la colocación del segundo dispositivo de memoria en un estado en el que no carga la segunda línea cuando el controlador de la memoria está escribiendo en el primer dispositivo de memoria activado.

## ES 2 435 427 T3

- 9.- El procedimiento de la reivindicación 8, que comprende también la provisión de una máscara de datos desde el controlador de la memoria hasta el segundo dispositivo de memoria cuando el controlador de la memoria está escribiendo en el segundo dispositivo de memoria.

- 10.- El procedimiento de la reivindicación 8, que comprende también la señalización de una operación de escritura en el segundo dispositivo de memoria, y en el que el primer dispositivo de memoria utiliza la señal para colocarlo en un estado en el que no carga la línea cuando el controlador de la memoria está escribiendo en el segundo dispositivo de memoria.

- 11.- El procedimiento de la reivindicación 8, en el que la notificación proporcionada al controlador de la memoria por el primer dispositivo de memoria indica un cambio de estado del primer dispositivo de memoria.

10

5