**ESPAÑA**

11 Número de publicación: 2 439 262

61 Int. Cl.:

H04L 27/34 (2006.01) H04L 27/36 (2006.01) H04L 1/00 (2006.01) H03M 13/25 (2006.01) H03M 13/11 (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Fecha de presentación y número de la solicitud europea: 26.02.2009 E 09153765 (4)

- 97) Fecha y número de publicación de la concesión europea: 11.09.2013 EP 2096761

- (54) Título: Perforación de códigos LDPC en función del esquema de modulación

- (30) Prioridad:

26.02.2008 KR 20080017280 11.03.2008 KR 20080022472 18.03.2008 KR 20080025143

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 22.01.2014

(73) Titular/es:

SAMSUNG ELECTRONICS CO., LTD. (50.0%) 129, Samsung-ro, Yeongtong-gu Suwon-si, Gyeonggi-do, 443-742, KR y POSTECH ACADEMY-INDUSTRY FOUNDATION (50.0%)

(72) Inventor/es:

MYUNG, SEHO; KWON, HWAN-JOON; KIM, KYUNG-JOONG; AHN, SEOK-KI; YANG, KYEONG-CHEOL; KIM, JAE-YOEL y LEE, HAK-JU

(74) Agente/Representante:

CARVAJAL Y URQUIJO, Isabel

## **DESCRIPCIÓN**

Perforación de códigos LDPC en función del esquema de modulación

#### ANTECEDENTES DE LA INVENCIÓN

Campo de la Invención

20

25

30

35

40

45

50

La presente invención se refiere a un sistema de comunicación que utiliza códigos de comprobación de paridad de baja densidad (LDPC, Low-Density Parity-Check). Más en particular, la presente invención se refiere a un método de codificación/descodificación de canal y a un aparato para generar códigos LDPC con varias longitudes de palabra de código y tasas de código a partir de un código LDPC proporcionado en modulación de orden superior.

Descripción de la técnica relacionada

En los sistemas de comunicación inalámbricos, el rendimiento del enlace disminuye significativamente debido a diversos ruidos en los canales, al fenómeno de desvanecimiento y a la interferencia entre símbolos (ISI, Inter-Symbol Interference). Por lo tanto, para conseguir sistemas de comunicación digital de alta velocidad que requieren un caudal de datos y una fiabilidad elevados, tales como la comunicación móvil de siguiente generación, la difusión digital e internet portátil, es necesario desarrollar una tecnología para superar los ruidos de canal, el desvanecimiento y la ISI. Recientemente, se ha llevado a cabo un estudio intensivo sobre los códigos de corrección de errores como método para aumentar la fiabilidad de la comunicación mediante recuperar eficientemente información distorsionada.

El código LDPC, introducido en primer lugar por Gallager en la década de 1960, ha perdido importancia con el tiempo debido a la complejidad de su implementación, que no podía ser solucionada mediante la tecnología de entonces. Sin embargo, dado que el turbo código, que fue descubierto por Berrou, Glavieux, y Thitimajshima en 1993, presenta niveles de rendimiento que se aproximan al límite de Shannon del canal, se han llevado a cabo investigaciones sobre descodificación iterativa y codificación de canal basadas en un grafo, junto con análisis sobre el rendimiento y las características del turbo código. Con esto como impulso, el código LDPC ha vuelto a ser estudiado a finales de la década de 1990, demostrándose que el código LDPC tiene un rendimiento próximo al límite de Shannon del canal, si el código LDPC es sometido a descodificación mediante aplicación de descodificación iterativa en base a un algoritmo suma-producto sobre un grafo de Tanner (un caso especial de un grafo factor) correspondiente al código LDPC.

El código LDPC se representa habitualmente utilizando una técnica de representación de grafos, y muchas características pueden ser analizadas mediante los métodos basados en teoría de grafos, álgebra y teoría de probabilidades. En general, un modelo de grafos de los códigos de canal es útil para la descripción de los códigos, y mediante mapear la información sobre los bits codificados a los vértices en el grafo y mapear las relaciones entre los bits a las aristas en el grafo, es posible considerar el grafo como una red de comunicación en la que los vértices intercambian mensajes predeterminados a través de las aristas, posibilitando de este modo obtener un algoritmo de descodificación natural. Por ejemplo, un algoritmo de descodificación obtenido a partir de un grafo reticulado ("trellis"), que puede ser considerado una clase de grafo, puede incluir el muy conocido algoritmo de Viterbi y un algoritmo de Bahl, Cocke, Jelinek y Raviv (BCJR).

El código LDPC se define en general como una matriz de comprobación de paridad, y puede ser expresado utilizando un grafo bipartito, que se denomina un grafo de Tanner. El grafo bipartito es un grafo en el que los vértices que constituyen el grafo están divididos en dos tipos diferentes, y el código LDPC está representado por el grafo bipartito que consiste en vértices, de los que unos se denominan nodos variables y los otros nodos de comprobación. Los nodos variables están mapeados uno a uno a los bits codificados.

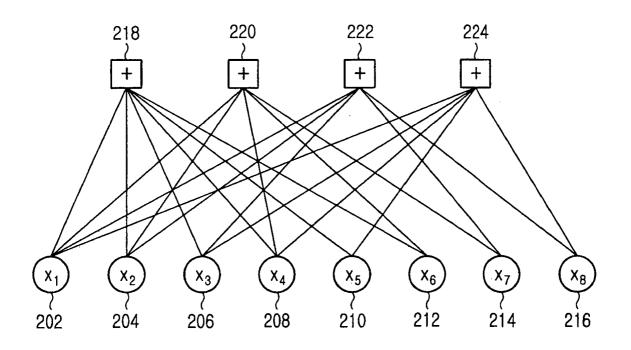

Se describirá un método de representación de grafos para el código LDPC haciendo referencia a las figuras 1 y 2.

La figura 1 muestra un ejemplo de una matriz de comprobación de paridad H<sub>1</sub> de un código LDPC con 4 filas y 8 columnas. Haciendo referencia a la figura 1, debido a que el número de columnas es 8, la matriz de comprobación de paridad H<sub>1</sub> significa un código LDPC que genera una palabra de código de longitud 8, y las columnas están mapeadas a 8 bits codificados en una relación de uno a uno.

La figura 2 muestra un grafo de Tanner correspondiente a la matriz de comprobación de paridad H<sub>1</sub> de la figura 1.

Haciendo referencia la figura 2, el grafo de Tanner del código LDPC incluye 8 nodos variables x<sub>1</sub> (202), x<sub>2</sub> (204), x<sub>3</sub> (206), x<sub>4</sub> (208), x<sub>5</sub> (210), x<sub>6</sub> (212), x<sub>7</sub> (214) y x<sub>8</sub> (216), y 4 nodos de comprobación 218, 220, 222 y 224. Una columna i-ésima y una fila j-estima en la matriz de comprobación de paridad H<sub>1</sub> del código LDPC son mapeadas a un nodo variable x<sub>i</sub> y a un nodo de comprobación j-ésimo, respectivamente. Además, un valor de 1, es decir, un valor distinto

de cero, en la posición en que se cruzan una columna i-ésima y una fila j-ésima en la matriz de comprobación de paridad H<sub>1</sub> del código LDPC, indica que existe una arista entre el nodo variable x<sub>i</sub> y el nodo de comprobación j-ésimo en el grafo de Tanner que se muestra en la figura 2.

En el grafo de Tanner del código LDPC, el grado del nodo variable y del nodo de comprobación indica el número de aristas contenidas en cada nodo respectivo, y el grado es igual al número de entradas distintas de cero en una columna o fila correspondiente al nodo pertinente en la matriz de comprobación de paridad del código LDPC. Por ejemplo, en la figura 2, los grados de los nodos variables x<sub>1</sub> (202), x<sub>2</sub> (204), x<sub>3</sub> (206), x<sub>4</sub> (208), x<sub>5</sub> (210), x<sub>6</sub> (212), x<sub>7</sub> (214) y x<sub>8</sub> (216) son 4, 3, 3, 3, 2, 2, 2 y 2, respectivamente, y los grados de los nodos de comprobación 218, 220, 222 y 224 son 6, 5, 5 y 5, respectivamente. Además, los números de las entradas distintas de cero en las columnas de la matriz de comprobación de paridad H<sub>1</sub> en la figura 1, que corresponden a los nodos variables en la figura 2, coinciden con sus grados 4, 3, 3, 3, 2, 2, 2 y 2, y los números de las entradas distintas de cero en las filas de la matriz de comprobación de paridad H<sub>1</sub> en la figura 1, que corresponden a los nodos de comprobación de la figura 2, coinciden con sus grados 6, 5, 5 y 5.

5

10

25

30

35

40

45

Para expresar la distribución de grados para los nodos del código LDPC, la relación del número de nodos variables de grado i respecto al número total de nodos variables se define como f<sub>i</sub>, y la relación del número de nodos de comprobación de grado j respecto al número total de nodos de comprobación se define como g<sub>i</sub>. Por ejemplo, para el código LDPC correspondiente a las figuras 1 y 2, f₂=4/8, f₃=3/8, f₄=1/8, y fị=0 para i≠2, 3, 4; y g₅=3/4, g₅=1/4, y g<sub>i</sub>=0 para j≠5, 6. Cuando la longitud del código LDPC, es decir, el número de columnas, se define como N, y el número de filas se define como N/2, la densidad de entradas distintas de cero en toda la matriz de comprobación de paridad que tiene la distribución de grados anterior se calcula tal como se muestra en la ecuación (1).

$$\frac{2f_2N + 3f_3N + 4f_4N}{N \cdot N/2} = \frac{5.25}{N} \qquad \dots \dots (1)$$

En la ecuación (1), cuando N aumenta, disminuye la densidad de 1's en la matriz de comprobación de paridad. En general, en relación con el código LDPC, dado que la longitud N de la palabra de código es inversamente proporcional a la densidad de entradas distintas de cero, un código LDPC con N grande tiene una densidad muy baja de entradas distintas de cero. El término 'baja densidad' para el código LDPC está originado en la relación mencionada anteriormente.

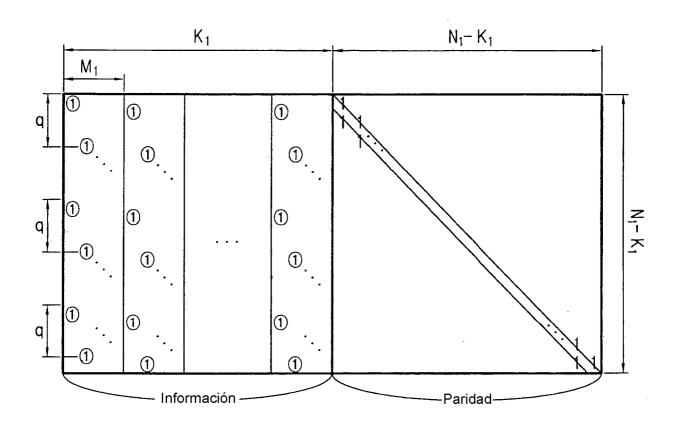

A continuación, haciendo referencia a la figura 3, se realizará una descripción de características de una matriz de comprobación de paridad de un código LDPC estructurado aplicable a la presente invención. La figura 3 muestra un código LDPC adoptado como la tecnología estándar de transmisión de difusión de señales digitales de videotransmisión por satélite de segunda generación (DVB-S2, Digital Video Broadcasting-Satellite transmission 2nd generation), que es uno de los estándares europeos de difusión digital.

En la figura 3, N1 y K1 indican una longitud de palabra de código y una longitud de información (una longitud de una palabra de información) de un código LDPC, respectivamente,  $(N_1-K_1)$  proporciona una longitud de paridad. Además, los enteros  $M_1$  y q se determinan de manera que satisfacen  $q=(N_1-K_1)/M_1$ . Preferentemente,  $K_1/M_1$  deberá ser asimismo un número entero. La matriz de comprobación de paridad en la figura 3 se denominará en el presente documento una primera matriz de comprobación de paridad  $H_1$ , sólo para mayor comodidad.

Haciendo referencia a la figura 3, una estructura de una parte de paridad, es decir, columna  $K_1$ -ésima hasta columna  $(N_1-1)$ -ésima, en la matriz de comprobación de paridad, tiene forma de diagonal doble. Por lo tanto, en relación con la distribución de grado sobre las columnas correspondientes a la parte de paridad, todas las columnas tienen grado '2', excepto la última columna, que tiene grado '1'.

En la matriz de comprobación de paridad, una estructura de una parte de información, es decir, la columna 0-ésima hasta la columna  $(K_1-1)$ -ésima, se forma utilizando las reglas siguientes.

Regla 1: se generan un total de  $K_1/M_1$  grupos de columnas mediante agrupar  $K_1$  columnas correspondientes a la palabra de información en la matriz de comprobación de paridad, en múltiples grupos compuestos, cada uno, de  $M_1$  columnas. Sigue un método para formar columnas pertenecientes a cada grupo de columnas en la siguiente regla 2.

Regla 2: se determinan en primer lugar las posiciones de 1's en cada columna 0-ésima en grupos de columnas i-ésimos (donde  $i=1,...,K_1/M_1$ ). Cuando un grado de una columna 0-ésima en cada grupo de columnas i-ésimo se

indica mediante  $D_i$ , si se asume que las posiciones de las filas con 1 son  $R_{i,0}^{(1)}, R_{i,0}^{(2)}, ..., R_{i,0}^{(D_i)}$ , las posiciones

$R_{i,j}^{(k)}(k=1,2,...,D_i)$  de las filas con 1 se definen según la ecuación (2), en una fila j-ésima (donde j=1, 2,...,M<sub>1</sub>-1) en un grupo de columnas i-ésimo.

$$R_{i,j}^{(k)} = R_{i,(j-1)}^{(k)} + q \operatorname{mod}(N_1 - K_1),$$

$$k = 1, 2, ..., D_i, \quad i = 1, ..., K_1 / M_1, \quad j = 1, ..., M_1 - 1$$

(2)

De acuerdo con las reglas anteriores, puede apreciarse que los grados de las columnas que pertenecen a un grupo de columnas i-ésimo son iguales a Di. Para una mejor comprensión de la estructura de un código DVB-S2 LDPC que almacena información sobre la matriz de comprobación de paridad de acuerdo con las reglas anteriores, se describirá el siguiente ejemplo detallado.

Como un ejemplo detallado, para N<sub>1</sub>=30, K<sub>1</sub>=15, M<sub>1</sub>=5 y q=3, pueden expresarse como sigue tres secuencias para la información sobre las posiciones de las filas con 1 para las columnas 0-ésimas en 3 grupos de columnas. En la presente descripción, estas secuencias se denominan por comodidad "secuencias de posición de ponderación-1".

10

20

25

30

35

$$R_{1,0}^{(1)} = 0, \ R_{1,0}^{(2)} = 1, \ R_{1,0}^{(3)} = 2,$$

$$R_{2,0}^{(1)} = 0$$

,  $R_{2,0}^{(2)} = 11$ ,  $R_{2,0}^{(3)} = 13$ ,

$$R_{3,0}^{(1)} = 0$$

,  $R_{3,0}^{(2)} = 10$ ,  $R_{3,0}^{(3)} = 14$ .

En relación con la secuencia de posición de ponderación-1 para las columnas 0-ésimas en cada grupo de columnas, solamente las secuencias de posición correspondientes pueden expresarse como sigue para cada grupo de columnas. Por ejemplo:

0 12

0 11 13

0 10 14.

En otras palabras, la secuencia de posición de ponderación-1 i-ésima en la línea i-ésima representa secuencialmente la información de las posiciones de las filas con 1 en el grupo de columnas i-ésimo.

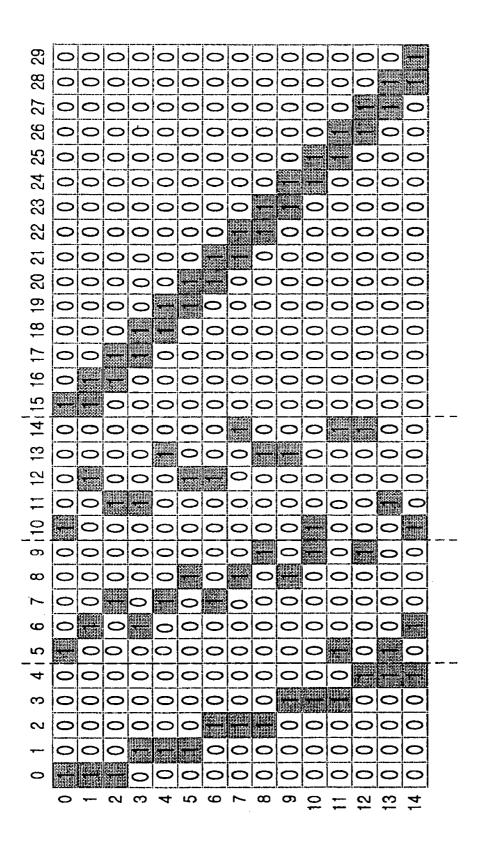

Es posible generar un código LDPC que tenga el mismo concepto que el de un código DVB-S2 LDPC de la figura 4, mediante formar una matriz de comprobación de paridad utilizando la información correspondiente al ejemplo detallado, y las reglas 1 y 2.

La solicitud de patente internacional WO 2007/091797 A (D1) se refiere a un método y un transmisor para adaptar el tamaño de una palabra de código codificada mediante un código de comprobación de paridad de baja densidad (LDPC) a un tamaño de un canal de transmisión en un sistema de comunicación móvil. Un método de ajuste del tamaño de palabra de código en un sistema de comunicación que soporta un esquema de codificación LDPC, comprende las etapas de codificar los datos de origen utilizando una matriz de comprobación de paridad, y ajustar el tamaño de la palabra de código codificada para hacerlo coincidir con un tamaño de un canal de transmisión que se determina en función de la capacidad del canal de transmisión, siendo ajustado el tamaño de la palabra de código codificada mediante la utilización de información asociada con ponderaciones de columna de la matriz de comprobación de paridad.

El documento "Variable Rate LDPC Codes for Wireless Applications", de M. Baldo y otros, en Proc. Softcom 2006, 1 de septiembre de 2006, páginas 301 a 305, XP031 059454, ISBN: 978-953-6114-90-0 (D2) describe códigos LDPC de tasa variable para aplicaciones inalámbricas, donde se requiere adaptación de enlace rápida para maximizar la eficiencia del sistema. En particular, el documento describe que puede utilizarse una denominada estrategia de "pseudo-perforación" como alternativa a soluciones más convencionales, asegurando un buen rendimiento y manteniendo al mismo tiempo una complejidad limitada.

La solicitud de patente de EE.UU. US 2007/226583 A1 (D3) describe un aparato y un método para transmitir/recibir señales en un sistema de comunicación. En un sistema de comunicación, un aparato de transmisión de señales incluye un codificador para codificar un vector de información en una palabra de código de comprobación de paridad

de baja densidad (LDPC) con un esquema de codificación LDPC, y un perforador para perforar la palabra de código LDPC en función de una tasa de codificación utilizada en un esquema de perforación. Un aparato de recepción de señal incluye un elemento de inserción para insertar símbolos '0' en una señal recibida, de acuerdo con una tasa de codificación utilizada en un aparato de transmisión de señal, y un descodificador para descodificar la señal con símbolos '0' introducidos con un esquema de descodificación correspondiente a un esquema de codificación de comprobación de paridad de baja densidad (LDPC) utilizado en el aparato de transmisión de señal, detectando de ese modo un vector de información.

La solicitud de patente de EE.UU. US 2007/101243 A1 (D4) describe un método para perforar una comprobación de paridad de baja densidad (LDPC). El método incluye a) establecer una longitud de palabra de código y el número total de nodos de bit a perforar; b) seleccionar un nodo de comprobación (o varios nodos de comprobación) con prioridad máxima excluyendo los nodos de comprobación comprobados por completo en la ronda actual; c) seleccionar un nodo de bit (o varios nodos de bit) con prioridad máxima excluyendo los nodos de bit comprobados por completo entre nodos de bit conectados al nodo de comprobación (o nodos de comprobación) seleccionado; d) determinar si el nodo de bit seleccionado es un nodo de bit a perforar, no es sistemático, no tiene activado un indicador de prohibición de perforación; e) perforar un nodo de bit asociado si el nodo de bit seleccionado es el nodo de bit a perforar, configurar nodos de bit no perforados conectados a dicho o nodo de comprobación seleccionado mediante un indicador de previsión de perforación, reduciendo en 1 el número de nodos de bit restantes a perforar y aumentando en 1 el número de nodos perforados conectados, del nodo de comprobación asociado; f) determinar si el número de bits restantes a perforar es mayor que 0; y g) volver a la etapa b) si el número de bits restantes a perforar no es mayor que 0.

El documento "Efficient Puncturing Method for Rate-Compatible Low-Density Parity-Check Codes", de H.Y. Park y otros, en IEEE Transactions on Wireless Communications, volumen 6, número 11, 1 de noviembre de 2007, páginas 3914 a 3919, XP011197001, ISSN: 1536-1276 (D5), describe un algoritmo que proporciona el orden de nodos variables para perforación en base a una función de coste propuesta. La función de coste intenta maximizar la fiabilidad mínima entre las proporcionadas por todos los nodos de comprobación. Asimismo, intenta asignar homogéneamente nodos de comprobación supervivientes a todos los nodos variables perforados. El algoritmo presenta la formación de un conjunto de parada a partir de los nodos variables perforados incluso cuando la cantidad de perforación es grande.

- 30 El documento "LDPC Codes in Communications and Broadcasting", de T. Ohtsuki en IEICE Trans. Commun., volumen E90B, número 3, 1 de marzo de 2007, describe las bases de los códigos LDPC y sus algoritmos de descodificación. Se presentan algunos códigos LDPC que tienen un buen rendimiento y están recibiendo mucha atención, en particular en los sistemas de comunicación. El documento repasa asimismo algunos códigos LDPC estandarizados, los códigos LDPC estandarizados en DVB-S2 y los códigos LDPC del estándar IEEE802.16e.

- 35 Se sabe que el código DVB-S2 LDPC diseñado de acuerdo con la regla 1 y la regla 2 puede ser codificado eficientemente utilizando la forma estructural. A continuación se describirán a modo de ejemplo las etapas respectivas en un proceso de realización de codificación LDPC utilizando la matriz de comprobación de paridad basada en DVB-S2.

- En la siguiente descripción, como un ejemplo detallado, un código DVB-S2 LDPC con N<sub>1</sub>=16200, K<sub>1</sub>=10800, M<sub>1</sub>=360 y q=15 es sometido a un proceso de codificación. Por comodidad, los bits de información que tienen una longitud K<sub>1</sub> se representan como (i<sub>0</sub>,i<sub>1</sub>,...,i<sub>K1-1</sub>), y los bits de paridad que tiene una longitud de (N<sub>1</sub>-K<sub>1</sub>) se expresan como (p<sub>0</sub>, p<sub>1</sub>,..., p<sub>N1-K1-1</sub>).

Etapa 1: un codificador LDPC inicializa bits de paridad, como sigue:

$$p_0 = p_1 = \dots = p_{N_1 - K_1 - 1} = 0$$

Etapa 2: el codificador LDPC lee información sobre filas donde hay un 1 en un grupo de columnas, a partir de una 0ésima secuencia de posición de ponderación-1 de entre las secuencias almacenadas que indican la matriz de comprobación de paridad.

0 2084 1613 1548 1286 1460 3196 4297 2481 3369 3451 4620 2622

$$R_{1,0}^{(1)} = 0$$

,  $R_{1,0}^{(2)} = 2048$ ,  $R_{1,0}^{(3)} = 1613$ ,  $R_{1,0}^{(4)} = 1548$ ,  $R_{1,0}^{(5)} = 1286$ ,

$$R_{\rm l,0}^{(6)}=1460,\ R_{\rm l,0}^{(7)}=3196,\ R_{\rm l,0}^{(8)}=4297,\ R_{\rm l,0}^{(9)}=2481,\ R_{\rm l,0}^{(10)}=3369,$$

5

10

15

20

25

$$R_{1,0}^{(11)} = 3451, \ R_{1,0}^{(12)} = 4620, \ R_{1,0}^{(13)} = 2622.$$

El codificador LDPC actualiza los bits de paridad específicos  $p_x$  de acuerdo con la ecuación (3) utilizando la información leída y el primer bit de información  $i_0$ . En la presente descripción, x indica un valor de  $R^{(k)}_{1,0}$  para k = 1, 2, ..., 13.

$$p_{0} = p_{0} \oplus i_{0}, \qquad p_{2084} = p_{2064} \oplus i_{0}, \quad p_{1613} = p_{1613} \oplus i_{0},$$

$$p_{1548} = p_{1548} \oplus i_{0}, \quad p_{1286} = p_{1286} \oplus i_{0}, \quad p_{1460} = p_{1460} \oplus i_{0},$$

$$p_{3196} = p_{3196} \oplus i_{0}, \quad p_{4297} = p_{4297} \oplus i_{0}, \quad p_{2481} = p_{2481} \oplus i_{0},$$

$$p_{3369} = p_{3369} \oplus i_{0}, \quad p_{3451} = p_{3451} \oplus i_{0}, \quad p_{4620} = p_{4620} \oplus i_{0},$$

$$p_{2622} = p_{2622} \oplus i_{0}$$

5

15

25

En la ecuación (3),  $p_x = p_x \oplus i_0$  puede expresarse asimismo como  $p_x \leftarrow p_x \oplus i_0$ ,  $y \oplus indica$  suma binaria.

Etapa 3: el codificador LDPC determina en primer lugar un valor de la ecuación (4) para los siguientes 359 bits de información i<sub>m</sub> (donde m=1, 2, ..., 359) después de i<sub>0</sub>.

$${x + (m \mod M_1) \times q} \mod (N_1 - K_1), M_1 = 360, m = 1, 2, ..., 359$$

.....(4)

En la ecuación (4), x indica un valor de  $R_{1,0}^{(k)}$  para k = 1, 2,..., 13. Debe observarse que la ecuación (4) es similar a la ecuación (2).

A continuación, el codificador LDPC realiza una operación similar a la ecuación (3) utilizando los valores encontrados en la ecuación (4). En otras palabras, el codificador LDPC actualiza los bits de paridad  $p_{(x+(m \mod N_1)\times q)\mod(N_1-K_1)}$  para  $i_m$ . Por ejemplo, para m=1, es decir, para  $i_1$ , el codificador LDPC actualiza los bits de paridad  $p_{(x+q)\mod(N_1-K_1)}$  tal como se define en la ecuación (5).

$$p_{15} = p_{15} \oplus i_{1}, \qquad p_{2099} = p_{2099} \oplus i_{1}, \quad p_{1628} = p_{1628} \oplus i_{1},$$

$$p_{1563} = p_{1563} \oplus i_{1}, \quad p_{1301} = p_{1301} \oplus i_{1}, \quad p_{1475} = p_{1475} \oplus i_{1},$$

$$p_{3211} = p_{3211} \oplus i_{1}, \quad p_{4312} = p_{4312} \oplus i_{1}, \quad p_{2496} = p_{2496} \oplus i_{1}, \quad \dots \dots (5)$$

$$p_{3384} = p_{3384} \oplus i_{1}, \quad p_{3466} = p_{3466} \oplus i_{1}, \quad p_{4635} = p_{4635} \oplus i_{1},$$

$$p_{2637} = p_{2637} \oplus i_{1}$$

Debe observarse que q = 15 en la ecuación (5). El codificador LDPC lleva a cabo el proceso anterior para m=1, 2, ..., 359 del mismo modo que se ha mostrado anteriormente.

Etapa 4: tal como en la etapa 2, el codificador LDPC lee información de la primera secuencia de posición de 20 ponderación-1  $R_{2,0}^{(k)}$  (k = 1, 2,..., 13) para un bit de información 361-ésimo i360, y actualiza los bits de paridad específicos px, donde x es  $R_{2,0}^{(k)}$ .

El codificador LDPC actualiza  $p_{\{x+(m \mod M1)xq\}\mod(N1-K1)}$ , m = 361, 362,..., 719 mediante aplicar de manera similar la ecuación (4) a los siguientes 359 bits de información  $i_{361}$ ,  $i_{362}$ , ...,  $i_{719}$  después de  $i_{360}$ .

Etapa 5: el codificador LDPC repite las etapas 2, 3 y 4 para todos los grupos teniendo cada uno 360 bits de información.

Etapa 6: el codificador LDPC determina finalmente bits de paridad utilizando la ecuación (6).

$$p_i = p_i \oplus p_{i-1}, i = 1, 2, ..., N_1 - K_1 - 1$$

(6)

Los bits de paridad p<sub>i</sub> de la ecuación (6) son bits de paridad que han sido sometidos totalmente a codificación LDPC.

Tal como se ha descrito anteriormente, DVB-S2 lleva a cabo la codificación mediante el proceso de las etapas 1 a 6.

Para aplicar el código LDPC al propio sistema de comunicación, el código LDPC debería estar diseñado para ser adecuado para la tasa de datos requerida en el sistema de comunicación. En particular, no sólo en un sistema de comunicación adaptativo que utilice solicitud de retransmisión automática híbrida (HARQ, Hybrid Automatic Retransmission reQuest) y modulación y codificación adaptativas (AMC, Adaptive Modulation and Coding), sino asimismo en un sistema de comunicación que soporte diversos servicios de difusión, se requieren códigos LDPC que tengan varias longitudes de palabra de código, para soportar varias tasas de datos en función de los requisitos del sistema.

Sin embargo, tal como se ha descrito anteriormente, el código LDPC utilizado en el sistema DVB-S2 tiene solamente dos tipos de longitudes de palabra de código debido a su utilización limitada, y cada tipo de código LDPC requiere de una matriz de comprobación de paridad independiente. Por estas razones, hace tiempo que existe en la técnica la necesidad de un método que soporte varias longitudes de palabra de código a efectos de aumentar la extensibilidad y flexibilidad del sistema. En particular, en el sistema DVB-S2, se requiere la transmisión de datos con varios cientos o miles de bits para la transmisión de información de señalización. Sin embargo, debido a que están disponibles solamente 16 200 y 64 800 para las longitudes del código DVB-S2 LDPC, sigue existiendo la necesidad de soportar varias longitudes de palabra de código. Además, dado que el almacenamiento de matrices de comprobación de paridad independientes para longitudes respectivas de palabra de código LDPC puede reducir la eficiencia de la memoria, existe la necesidad de un esquema que pueda soportar eficientemente varias longitudes de palabra de código a partir de una matriz de comprobación de paridad existente dada, sin diseñar una nueva matriz de comprobación de paridad.

## RESUMEN DE LA INVENCIÓN

15

20

Un aspecto de una realización de la presente invención es solucionar, por lo menos, los problemas y/o las desventajas mencionadas anteriormente y dar a conocer, por lo menos, las ventajas descritas a continuación. Por consiguiente, un aspecto de la presente invención es dar a conocer un método y un aparato de codificación/descodificación de canal para generar, a partir de un código LDPC dado, un código LDPC con una longitud de palabra de código diferente utilizando reducción o perforación determinadas teniendo en cuenta la modulación de orden superior en un sistema de comunicación que utiliza códigos LDPC.

Otro aspecto de una realización de la presente invención es dar a conocer un método y un aparato de codificación/descodificación de canal para garantizar un rendimiento óptimo, teniendo en cuenta una estructura DVB-S2 en un sistema de comunicación que utiliza códigos LDPC.

De acuerdo con un aspecto de la presente invención, se da a conocer un método para perforar bits de paridad asociados con una codificación de canal en un sistema de comunicación que utiliza un código de comprobación de paridad de baja densidad (LDPC), tal como el definido en la reivindicación 1.

De acuerdo con otro aspecto de la presente invención, se da a conocer un aparato para perforar bits de paridad asociados con una codificación de canal en un sistema de comunicación que utiliza un código de comprobación de paridad de baja densidad (LDPC) en un transmisor, tal como el definido en la reivindicación 3.

40 Otros aspectos, ventajas y características destacadas de la invención resultarán evidentes para los expertos en la materia a partir de la siguiente descripción detallada que, tomada junto con los dibujos adjuntos, da a conocer realizaciones de la invención.

## BREVE DESCRIPCIÓN DE LOS DIBUJOS

Los anteriores y otros aspectos, características y ventajas de ciertas realizaciones a modo de ejemplo de la presente invención resultarán más evidentes a partir de la siguiente descripción, tomada con los dibujos adjuntos, en los cuales:

la figura 1 es un ejemplo de una matriz de comprobación de paridad de un código LDPC de longitud 8;

la figura 2 es un grafo de Tanner que muestra una matriz de comprobación de paridad de un código LDPC de longitud 8;

la figura 3 muestra un código DVB-S2 LDPC;

la figura 4 es un ejemplo de una matriz de comprobación de paridad de un código DVB-S2 LDPC;

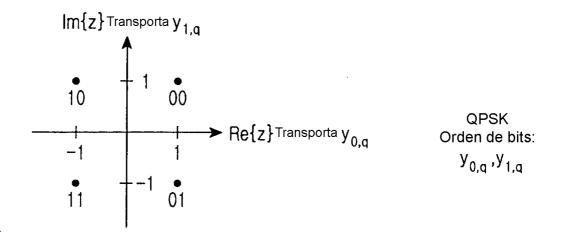

la figura 5A muestra una constelación de señales para modulación QPSK utilizada en un sistema de comunicación digital;

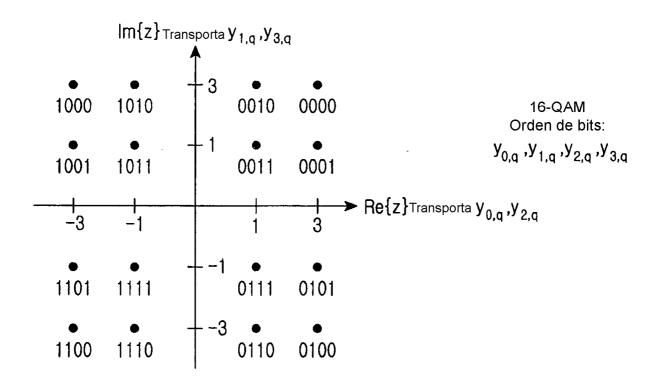

5 la figura 5B muestra una constelación de señales para modulación 16QAM utilizada en un sistema de comunicación digital;

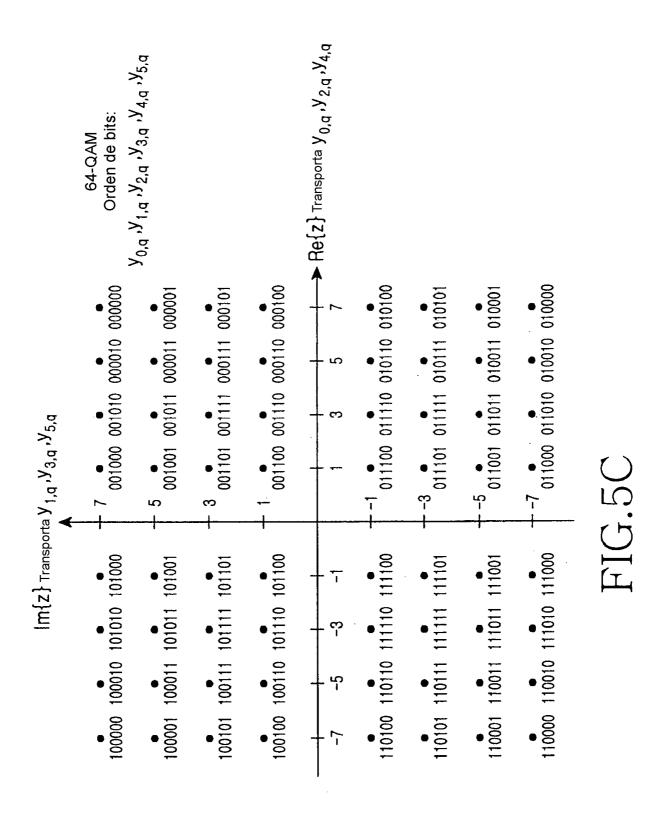

la figura 5C muestra una constelación de señales para modulación 64QAM utilizada en un sistema de comunicación digital;

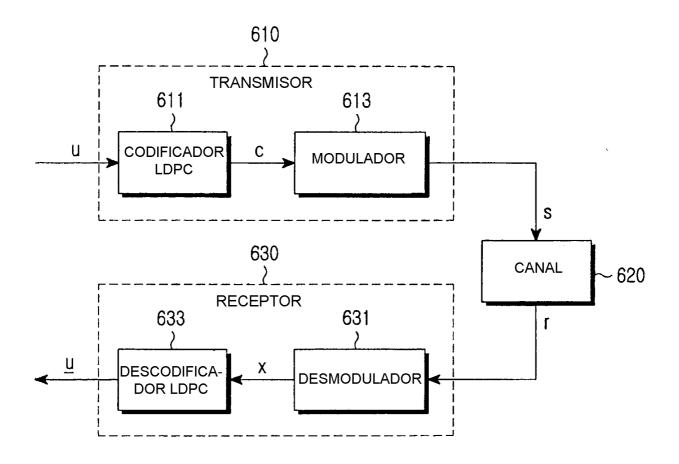

la figura 6 es un diagrama de bloques de un transceptor en un sistema de comunicación que utiliza un código LDPC;

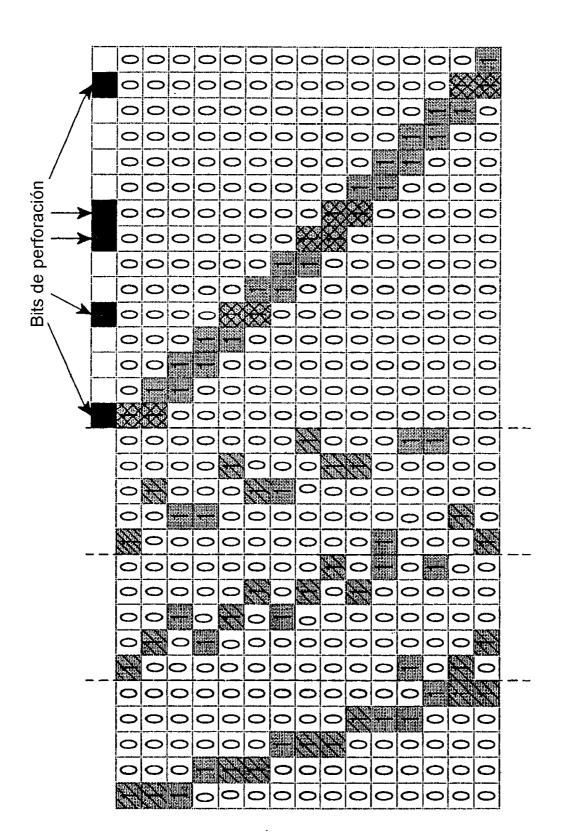

10 la figura 7 muestra un ejemplo en el que se aplica perforación aleatoria al código LDPC de la figura 4;

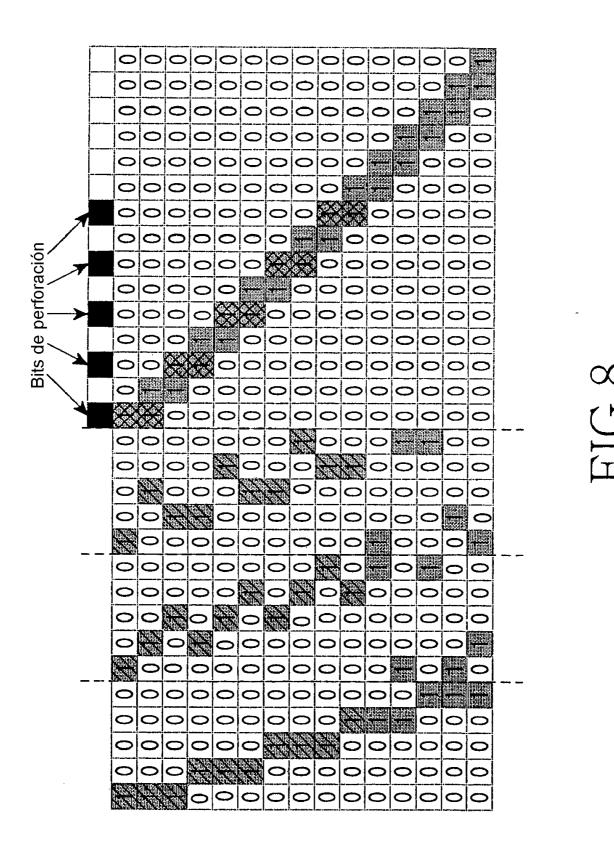

la figura 8 muestra otro ejemplo en el que se aplica perforación no aleatoria al código LDPC de la figura 4;

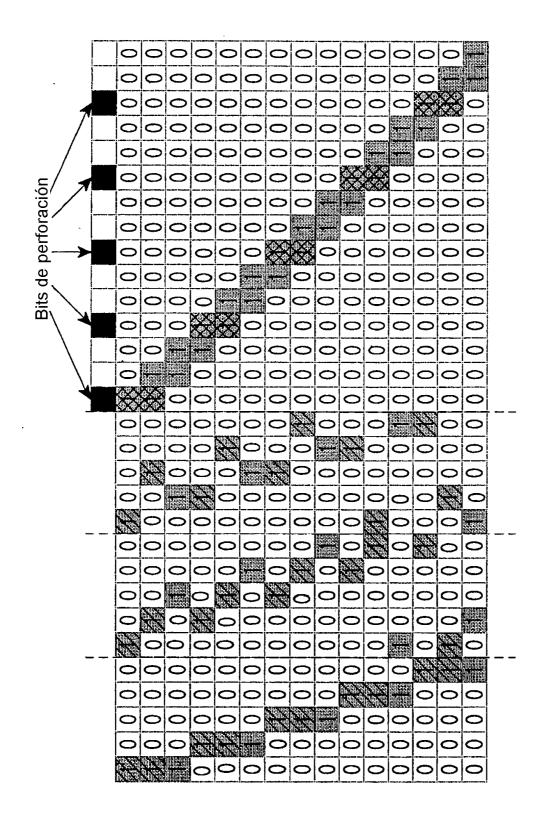

la figura 9 muestra otro ejemplo en el que se aplica perforación no aleatoria al código LDPC de la figura 4;

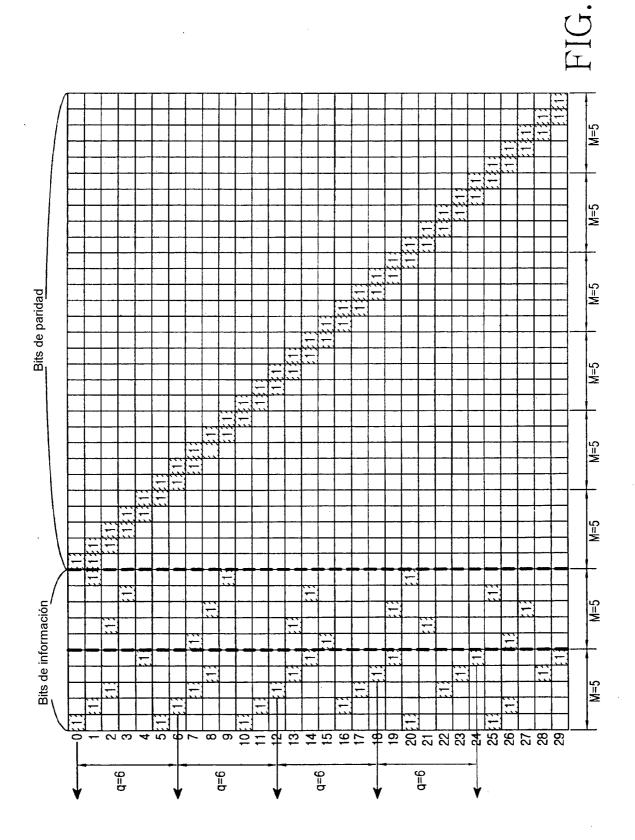

la figura 10 muestra otro ejemplo de una matriz de comprobación de paridad de un código DVB-S2 LDPC;

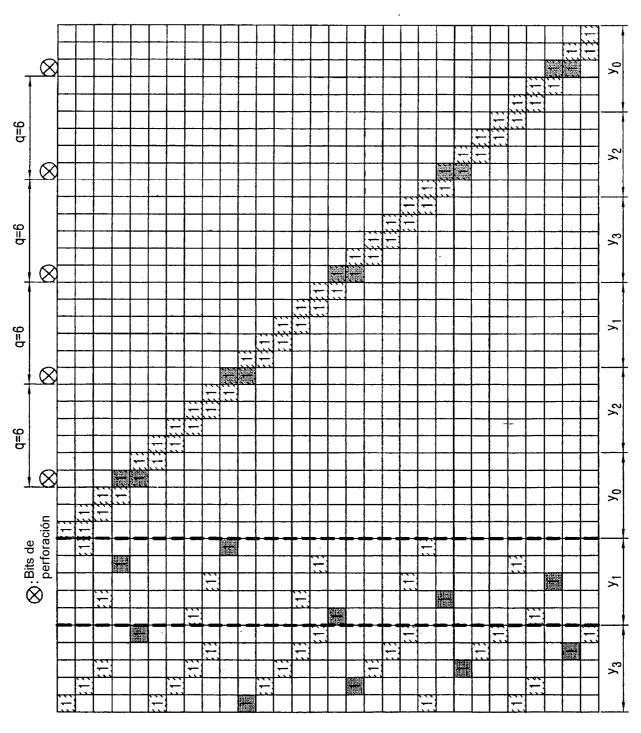

la figura 11 muestra un ejemplo de un patrón de perforación determinado considerando transmisión BPSK o QPSK en el código LDPC de la figura 10;

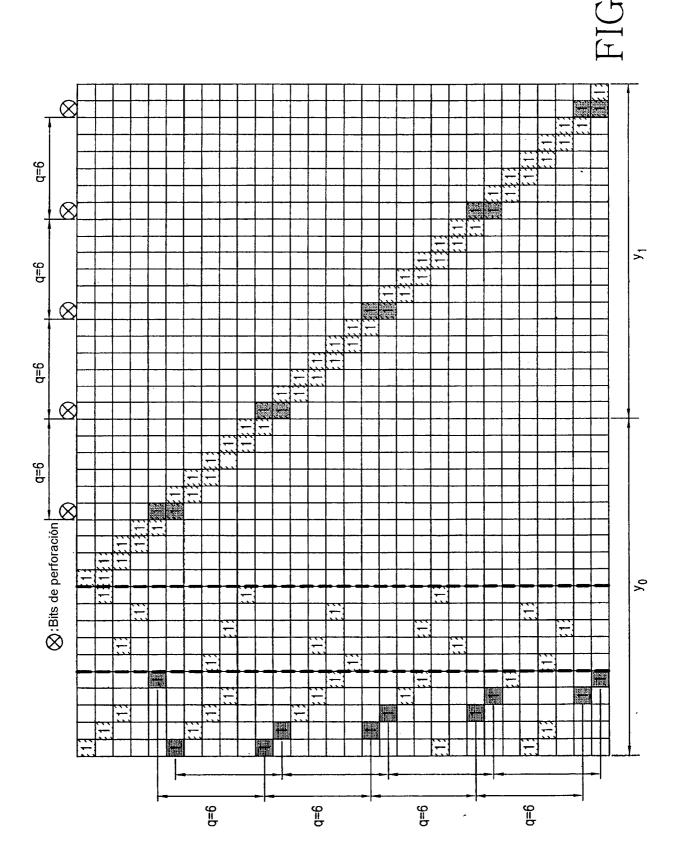

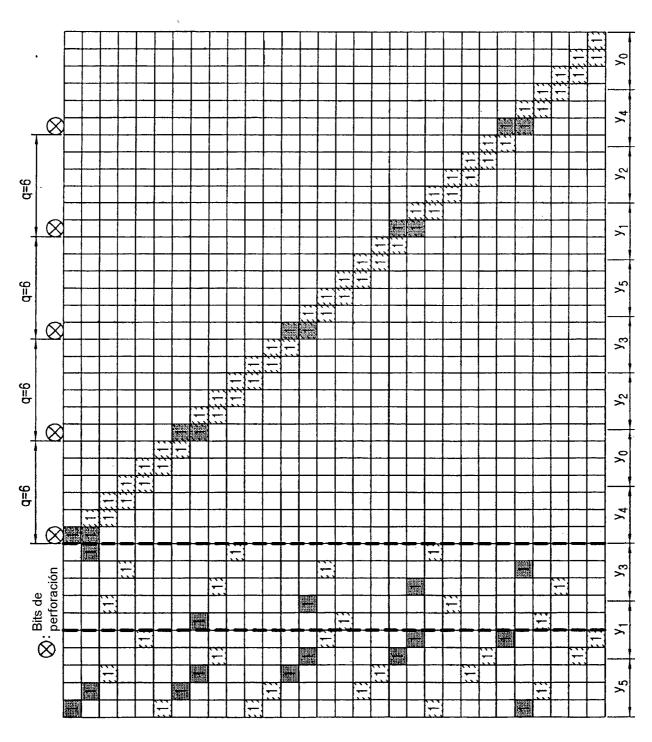

la figura 12A muestra un ejemplo de un patrón de perforación determinado considerando transmisión 16QAM en el código LDPC de la figura 10:

la figura 12B muestra un ejemplo de un patrón de perforación determinado considerando transmisión 64QAM en el código LDPC de la figura 10;

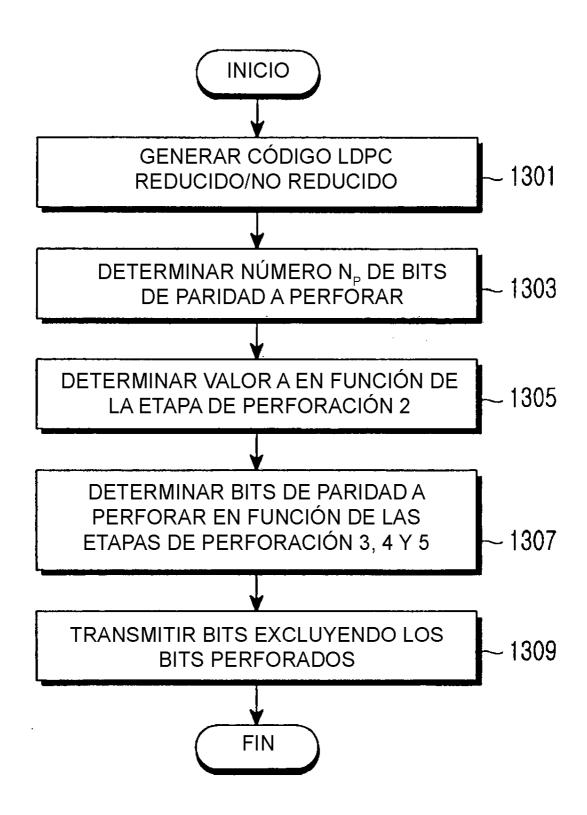

la figura 13 es un diagrama de flujo que muestra un método para generar un código LDPC con una longitud de palabra de código diferente a partir de una matriz de comprobación de paridad de un código LDPC almacenado, de acuerdo con una realización de la presente invención:

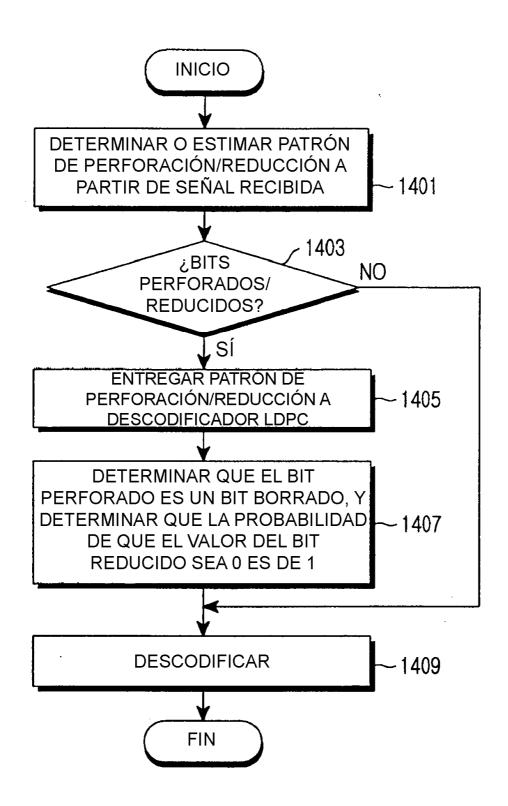

la figura 14 es un diagrama de flujo que muestra un método de descodificación LDPC en un aparato de recepción, de acuerdo con una realización de la presente invención;

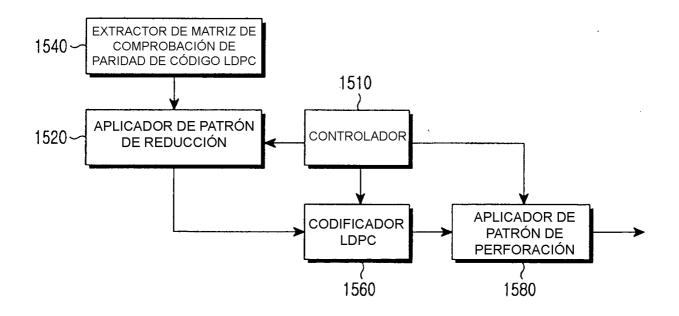

la figura 15 es un diagrama de bloques de un aparato de transmisión que utiliza un código LDPC perforado/reducido, de acuerdo con una realización de la presente invención; y

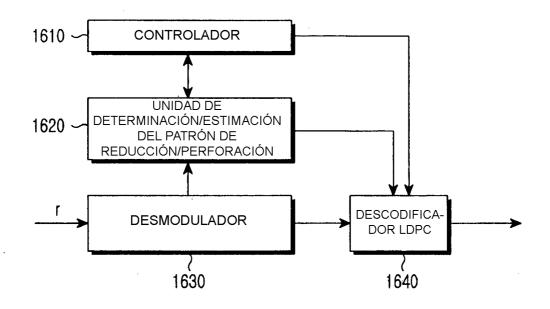

la figura 16 es un diagrama de bloques de un aparato de recepción que utiliza un código LDPC perforado/reducido, de acuerdo con una realización de la presente invención.

En la totalidad de los dibujos, se comprenderá que los mismos numerales de referencia se refieren a los mismos elementos, características y estructuras.

## DESCRIPCIÓN DETALLADA DE REALIZACIONES A MODO DE EJEMPLO

35

40

La siguiente descripción que hace referencia a los dibujos adjuntos, se da a conocer para ayudar a una comprensión exhaustiva de las realizaciones de la invención, que se define mediante las reivindicaciones y sus equivalentes. Ésta incluye diversos detalles específicos para ayudar a dicha comprensión, pero estos deben considerarse como meros ejemplos. Por consiguiente, los expertos en la materia reconocerán que pueden realizarse diversos cambios y modificaciones a las realizaciones descritas en el presente documento, sin apartarse del alcance de la invención. Además, se omiten las descripciones de funciones y construcciones bien conocidas para mayor claridad y concisión.

Los términos y las palabras utilizadas en la siguiente descripción y las reivindicaciones no se limitan a sus significados bibliográficos, sino que son utilizadas por el inventor únicamente para facilitar una comprensión clara y consistente de la invención. Por consiguiente, deberá ser evidente para los expertos en la materia que las siguiente descripción de realizaciones de la presente invención se proporciona solamente con propósitos ilustrativos y no con el propósito de limitar la invención, que se define mediante las reivindicaciones adjuntas y sus equivalentes.

Debe entenderse que las formas singulares "un", "una" y "el" y "la" incluyen sus equivalentes plurales, salvo que el contexto imponga claramente lo contrario. Por lo tanto, por ejemplo, la referencia a "una superficie componente" incluye la referencia a una o varias de dichas superficies.

A continuación se describirá la diferencia de fiabilidad en modulación de orden superior, antes de una descripción de la presente invención. Deberá prestarse la debida atención al diseño de un código LDPC debido a que las fiabilidades de los bits que componen los símbolos de modulación de orden superior son diferentes cuando se utiliza modulación de orden superior en el sistema de comunicación que requiere de códigos LDPC con varias longitudes de palabra de código, frente al sistema de comunicación que utiliza solamente codificación por desplazamiento de fase binario (BPSK, Binary Phase Shift Keying) o codificación por desplazamiento de fase en cuadratura (QPSK, Quadrature Phase Shift Keying).

Para explicar la diferencia de fiabilidad en modulación de orden superior, se proporcionará una descripción de constelaciones de señal para modulación de amplitud en cuadratura (QAM, Quadrature Amplitude Modulation), que es la modulación de orden superior utilizada normalmente en los sistemas de comunicación. Un símbolo modulado QAM consiste en una parte real y una parte imaginaria, y pueden generarse varios símbolos de modulación mediante diferenciar magnitudes y signos de sus partes reales de sus partes imaginarias. Se describirá QAM junto con modulación QPSK para considerar los detalles de las características de QAM.

La figura 5A muestra una constelación de señal para modulación QPSK general.

5

10

15

20

30

Haciendo referencia la figura 5A,  $y_0$  determina el signo de una parte real mientras que  $y_1$  determina el signo de una parte imaginaria. Es decir, el signo de la parte real es más (+) para  $y_0$ =0, y menos (-) para  $y_0$ =1. Asimismo, es signo de la parte imaginaria es más (+) para  $y_1$ =0, y menos (-) para  $y_1$ =1. Dado que  $y_0$  e  $y_1$  son iguales en probabilidad de aparición de errores, puesto que son bits de indicación de signo que indican signos respectivos de la parte real y la parte imaginaria, las fiabilidades de los bits ( $y_0$ ,  $y_1$ ) correspondientes a una señal de modulación son de igual importancia, en modulación QPSK. Para  $y_{0,q}$  y  $y_{1,q}$ , el segundo subíndice 'q' indica q-ésimas salidas de bits que constituyen una señal de modulación.

La figura 5B muestra una constelación de señal para modulación 16QAM general.

Haciendo referencia a 5B, el significado de  $(y_0, y_1, y_2, y_3)$  correspondiente a los bits de una señal de modulación, es el siguiente. Los bits  $y_0$  e  $y_2$  determinan el signo y la magnitud de la parte real, respectivamente, mientras que los bits  $y_1$  e  $y_3$  determinan el signo y la magnitud de la parte imaginaria, respectivamente. En otras palabras,  $y_0$  e  $y_1$  determinan signos de la parte real y la parte imaginaria de la señal de modulación, mientras que  $y_2$  e  $y_3$  determinan magnitudes de la parte real y la parte imaginaria de la señal de modulación. Debido a que distinguir el signo de una señal modulada es más fácil que distinguir la magnitud de la señal modulada,  $y_2$  e  $y_3$  están por encima de  $y_0$  e  $y_1$  en probabilidad de producción de errores. Por lo tanto, en términos de probabilidades de no aparición de errores (es decir, de fiabilidades) de los bits,  $y_0$ = $y_1$  > $y_2$ = $y_3$ . Es decir, los bits ( $y_0$ ,  $y_1$ ,  $y_2$ ,  $y_3$ ) que constituyen una señal de modulación QAM, a diferencia de los de una señal de modulación QPSK, tienen fiabilidades diferentes.

En modulación 16QAM, entre los 4 bits que constituyen una señal, 2 bits determinan signos de la parte real y la parte imaginaria de la señal, y los bits restantes tienen que determinar solamente las magnitudes de la parte real y la parte imaginaria de la señal. Por lo tanto, los órdenes de (y<sub>0</sub>, y<sub>1</sub>, y<sub>2</sub>, y<sub>3</sub>) y la función de cada bit están sujetos a cambios.

La figura 5C muestra una constelación de señal para modulación 64QAM general.

De (y<sub>0</sub>, y<sub>1</sub>, y<sub>2</sub>, y<sub>3</sub>, y<sub>4</sub>, y<sub>5</sub>), que corresponde a los bits de la señal de modulación, los bits y<sub>0</sub>, y<sub>2</sub> e y<sub>4</sub> determinan la magnitud y el signo de la parte real, e y<sub>1</sub>, y<sub>3</sub> e y<sub>5</sub> determinan la magnitud y el signo de la parte imaginaria. En este caso, y<sub>0</sub> e y<sub>1</sub> determinan signos de la parte real y la parte imaginaria, respectivamente, y una combinación de y<sub>2</sub> e y<sub>4</sub> y una combinación de y<sub>3</sub> e y<sub>5</sub> determinan magnitudes de la parte real y la parte imaginaria, respectivamente. Dado que distinguir los signos de una señal modulada es más sencillo que distinguir las magnitudes de dicha señal modulada, las fiabilidades de y<sub>0</sub> e y<sub>1</sub> son mayores que las fiabilidades de y<sub>2</sub>, y<sub>3</sub>, y<sub>4</sub> e y<sub>5</sub>. Los bits y<sub>2</sub> e y<sub>3</sub> se determinan en función de si la magnitud del símbolo modulado es mayor o igual que 4, y los bits y<sub>4</sub> e y<sub>5</sub> se determinan en función de si la magnitud del símbolo modulado está más cerca de 4 o de 0, con 2 centrado entre ambos, o más cerca de 4 o de 8, con 6 centrado entre ambos. Por lo tanto, el intervalo en el que la magnitud está determinada por y<sub>2</sub> e y<sub>3</sub> es 4, mientras que el intervalo para y<sub>4</sub> e y<sub>5</sub> es 2. Como resultado, la fiabilidad de y<sub>2</sub> e y<sub>3</sub> es mayor que la de y<sub>4</sub> e y<sub>5</sub>. Para concluir, y<sub>0</sub>=y<sub>1</sub> > y<sub>2</sub>=y<sub>3</sub> > y<sub>4</sub>=y<sub>5</sub> en términos de probabilidades de no aparición de errores (es decir, fiabilidades) de los bits.

En modulación 64QAM, de los 6 bits que constituyen una señal, 2 bits determinan signos de la parte real y la parte imaginaria de la señal, y 4 bits tienen que determinar solamente magnitudes de la parte real y la parte imaginaria de la señal. Por consiguiente, los órdenes de (y<sub>0</sub>, y<sub>1</sub>, y<sub>2</sub>, y<sub>3</sub>, y<sub>4</sub>, y<sub>5</sub>) y la función de cada bit están sujetos a cambios.

Asimismo, en una constelación de señal de 256QAM o superior, las funciones y las fiabilidades de los bits que constituyen una señal modulación son diferentes a las descritas anteriormente. Se omitirá una descripción detallada de las mismas.

Por lo tanto, la presente invención da a conocer un método y un aparato para soportar códigos LDPC con varias longitudes de palabra de código adecuadas para modulación de orden superior, utilizando una matriz de comprobación de paridad de un código LDPC estructurado, en una forma particular. Además, la presente invención da a conocer un aparato para soportar varias longitudes de palabra de código en función de un orden superior de modulación en un sistema de comunicación que utiliza un código LDPC en una forma particular, y un método para controlar el mismo. En particular, la presente invención da a conocer un método para generar un código LDPC utilizando una matriz de comprobación de paridad de un código LDPC dado, siendo el código LDPC generado menor que el código LDPC dado, y un aparato para lo mismo.

5

10

35

40

45

La figura 6 es un diagrama de bloques de un transceptor en un sistema de comunicación que utiliza un código LDPC.

Haciendo referencia a la figura 6, un mensaje u es introducido a un codificador LDPC 611 en un transmisor 610 antes de ser transmitido a un receptor 630. El codificador LDPC 611 codifica el mensaje de entrada u, y entrega la señal codificada c al modulador 613. El modulador 613 modula la señal codificada y transmite la señal modulada s al receptor 630 a través de un canal inalámbrico 620. Un desmodulador 631 en el receptor 630 desmodula la señal recibida r, y entrega la señal modulada x a un descodificador LDPC 633. El descodificador LDPC 633 encuentra una estimación <u>u</u> del mensaje en base a los datos recibidos a través del canal inalámbrico 620, mediante descodificar la señal desmodulada x.

El codificador LDPC 611 genera una matriz de comprobación de paridad en función de una longitud de palabra de código requerida por un sistema de comunicación, utilizando un esquema predeterminado. En particular, de acuerdo con una realización de la presente invención, el codificador LDPC 611 puede soportar varias longitudes de palabra de código utilizando el código LDPC, sin la necesidad de información adicional almacenada.

Según una realización de la presente invención, un método de obtención de varias longitudes de palabra de código a partir de un código LDPC dado utiliza reducción y perforación. El término "perforación", tal como se utiliza la presente descripción, indica un método que no transmite una parte especificada de una palabra de código LDPC después de generar la palabra de código LDPC a partir de una matriz de comprobación de paridad dada mediante realizar codificación LDPC. Por lo tanto, un receptor determina que los bits no transmitidos han sido borrados.

Para una mejor comprensión de la perforación, se describirá en mayor detalle a continuación una matriz de comprobación de paridad del código DVB-S2 LDPC mostrado en la figura 3.

En relación con la matriz de comprobación de paridad del código DVB-S2 LDPC mostrado en la figura 3, su longitud total es de  $N_1$ ,  $K_1$  columnas en la parte delantera de la matriz de comprobación de paridad correspondiente a bits de información ( $i_0$ ,  $i_1$ ..., $i_{K_1-1}$ ), y las columnas en la parte posterior restante correspondientes a bits de paridad ( $p_0$ ,  $p_1$ ,..., $p_{N_1-K_1-1}$ ) de longitud ( $N_1-K_1$ ).

De manera general, la perforación puede ser aplicada tanto a los bits de información como a los bits de paridad. Aunque normalmente la perforación y la reducción reducen las longitudes palabra de código, la perforación, a diferencia de la reducción, descrita anteriormente, no limita los valores de bits particulares. La perforación es un método para, simplemente, no transmitir bits de información particulares o partes particulares de bits de paridad generados, de manera que un receptor pueda borrar los bits correspondientes. En otras palabras, simplemente mediante no transmitir bits en las Np posiciones predefinidas en una palabra de código LDPC de longitud N1 generada, la perforación puede obtener el mismo efecto al obtenido mediante transmitir una palabra de código LDPC de longitud (N1-Np). Dado que las columnas correspondientes a los bits perforados en la matriz de comprobación de paridad se utilizan todas intactas en un proceso de descodificación, con las columnas borradas, la perforación es diferente a la reducción.

Además, debido a que la información de la posición para los bits perforados puede ser compartida o estimada en común mediante el transmisor y el receptor cuando el sistema es configurado, el receptor puede simplemente borrar los correspondientes bits perforados, antes de la descodificación.

En la técnica de perforación, debido a que la longitud de una palabra de código que el transmisor transmite realmente es de  $N_1$ - $N_p$ , y a que la longitud de una palabra de información es siempre de  $K_1$ , la tasa de código pasa a ser de  $K_1$ / $(N_1$ - $N_p$ ), que siempre es mayor que la primera tasa de código dada la  $K_1$ / $N_1$ .

A continuación se realizará una descripción de la técnica de reducción y la técnica de perforación adecuadas para el código DVB-S2 LDPC. El código DVB-S2 LDPC, que se ha descrito anteriormente, es un código LDPC que tiene

una estructura particular. Por lo tanto, comparado con el código LDPC normal, el código DVB-S2 LDPC puede ser sometido a reducción y perforación más eficientes.

Haciendo referencia a la figura 4, se proporcionará una descripción de las características de un código DVB-S2 LDPC al que se aplica perforación de paridad. Debe observarse que para el código DVB-S2 LDPC de la figura 4, N<sub>1</sub>=30, K<sub>1</sub>=15, M<sub>1</sub>=5 y q=3 y las secuencias de posición de ponderación-1 para las columnas 0-ésimas en tres grupos de columnas son las siguientes:

012

5

15

30

35

40

50

0 11 13

0 10 14

10 Una secuencia de posición de ponderación-1 i-ésima en una columna i-ésima representa secuencialmente la información sobre las posiciones de las filas con 1 en un grupo de columnas i-ésimo.

La figura 7 muestra un ejemplo en el que se aplica perforación aleatoria al código LDPC de la figura 4. Debido a que los bits de paridad perforados en la figura 7 están sujetos a un proceso de borrado en un descodificador, los bits de paridad perforados, en comparación con los otros bits no eliminados, no tienen un efecto mayor de mejora del rendimiento en un proceso de descodificación LDPC, de manera que sus fiabilidades disminuyen. Por consiguiente, los otros bits conectados directamente a los bits de paridad perforados, que tienen una fiabilidad reducida, acusan también una reducción en el efecto de mejora del rendimiento en el proceso de descodificación. La reducción en el efecto de mejora del rendimiento aumenta a medida que aumenta el número de aristas conectadas directamente a los bits perforados en el grafo de Tanner.

En la figura 7, por ejemplo, un bit de información 0-ésimo correspondiente a una columna 0-ésima está conectado directamente dos veces al bit de paridad perforado, un tercer bit de información correspondiente a una tercera columna está conectado directamente una vez al bit de paridad perforado, y un octavo bit de información correspondiente a una octava columna está conectado directamente tres veces al bit de paridad perforado. En este caso, el tercer, 0-ésimo y octavo bits de información son superiores en efecto de mejora del rendimiento para el proceso de descodificación. En otras palabras, cuando los grados de los nodos variables son iguales entre sí, el efecto de mejora del rendimiento disminuye a medida que aumenta el número de bits perforados conectados.

A partir de la figura 7, puede apreciarse que los números de bits de paridad perforados, que están conectados directamente a bits de información respectivos, son aleatorios debido al patrón de perforación aleatorio. Por lo tanto, existe una elevada probabilidad de que las fiabilidades de los bits de información respectivos sean asimismo aleatorias. En otras palabras, mientras que algunos bits de información pueden obtener un rendimiento de descodificación mejor que el necesario, otros bits de información pueden sufrir una degradación significativa del rendimiento. El patrón de perforación aleatorio puede conducir a una irregularidad considerable de las fiabilidades de los bits de información en el proceso de descodificación.

La figura 8 muestra un segundo ejemplo en el que se aplica perforación no aleatoria al código LDPC de la figura 4. Más específicamente, en el ejemplo mostrado en la figura 8 se aplica un patrón de perforación relativamente no aleatorio, en una forma particular.

Haciendo referencia a la figura 8, a pesar de que se aplica el patrón de perforación relativamente no aleatorio, las conexiones a los bits de información pueden ser significativamente irregulares en función del patrón de perforación correspondiente. El patrón de perforación no aleatorio de la figura 8 puede ser más irregular en comparación con el patrón de perforación aleatorio de la figura 7.

En el caso del código LDPC con una matriz de comprobación de paridad que tiene una estructura particular tal como el código DVB-S2 LDPC, las conexiones entre los bits de información y los bits de paridad perforados según el patrón de perforación pueden cambiar significativamente.

Las realizaciones de la presente invención proponen un patrón de perforación que proporciona un comportamiento de descodificación estable mediante suprimir al máximo la irregularidad de las fiabilidades de los bits de información en el proceso de descodificación, utilizando las características estructurales del código DVB-S2 LDPC.

La figura 9 muestra un tercer ejemplo en el que se aplica perforación no aleatoria al código LDPC de la figura 4. En el ejemplo de la figura 9, un patrón de perforación que mantiene un intervalo constante de 3 entre bits de paridad perforados desde q=3, que es una de las variables constituyentes, se aplica a la matriz de comprobación de paridad mostrada en la figura 4. Tal como puede verse en la figura 9, cada uno de los bits de información está conectado de la misma manera, y dos veces, al bit perforado.

La irregularidad entre los bits perforados y los bits de información se reduce notablemente cuando el intervalo entre los bits de paridad perforados se ajusta en función del valor de q debido a la estructura del código DVB-S2 LDPC. Esto se describe mejor haciendo referencia a la figura 3.

Haciendo referencia a las reglas 1 y 2 y a la figura 3, en relación con cada grupo de columnas, las posiciones de los '1's en la primera columna en el grupo de columnas correspondiente, determinan posiciones de '1's en las columnas restantes. Los índices de las filas en las que 1 está situado en las columnas restantes difieren exactamente en un múltiplo de q respecto de un índice de una fila en la que 1 está situado en la primera columna, en relación con módulo(N<sub>1</sub>-K<sub>1</sub>), donde N<sub>1</sub> indica la longitud de una palabra de código LDPC y K<sub>1</sub> indica la longitud de una palabra de información. Más específicamente, los índices de las filas en las que 1 está situado en dos columnas consecutivas en un grupo de columnas particular difieren entre sí exactamente en q, para módulo (N<sub>1</sub>-K<sub>1</sub>).

Otra característica del código DVB-S2 LDPC se encuentra en una submatriz correspondiente a la parte de paridad en la matriz de comprobación de paridad. Haciendo referencia a la figura 3, la parte de paridad tiene una estructura de una matriz triangular inferior en la que 1 se presenta en todas las partes diagonales y, en esta estructura, un bit de paridad i-ésimo corresponde a un '1' situado en una fila i-ésima.

En función de la característica estructural del código DVB-S2 LDPC, asumiendo que se perforan bits de paridad específicos, si se repite exactamente una perforación de paridad a intervalos de q, el número de aristas de bits de información conectadas a los bits de paridad perforados en un grupo de columnas particular es el más regular. Por ejemplo, asumiendo que un bit de paridad i-ésimo es perforado para 0≤i<q y un bit de paridad (i+kq)-ésimo es perforado repetidamente para 0≤k<M₁, si un cierto bit de información está conectado al bit de paridad i-ésimo, esto indica que '1' existe en una fila i-ésima para una columna correspondiente al bit de información. Por lo tanto, puede entenderse que hay '1' en la fila (i+kq)-ésima en una columna correspondiente a un bit de información que está separado mediante k del bit de información anterior entre las columnas en un grupo de columnas, de acuerdo con la regla 1 y la regla 2. Como resultado, el bit de información está conectado al bit (i+kq)-ésimo perforado.</li>

Para el código DVB-S2 LDPC, debido a que los grados de los nodos variables correspondientes a toda la palabra de información son iguales entre sí en un grupo de columnas, y en una fila hay distribuido un '1' o menos, cuando se aplica perforación q-periódica, los bits de información correspondientes a un grupo de columnas se conectan a un mismo número de bits perforados. Por lo tanto, las conexiones entre los bits perforados y los bits de información se regularizan, de manera que puede esperarse una descodificación estabilizada en el proceso de descodificación.

En lo descrito hasta aquí, puede apreciarse que para el código DVB-S2 LDPC, la técnica de perforación q-periódica puede contribuir a la mejora del rendimiento mediante hacer la mejor utilización de las características estructurales del código DVB-S2 LDPC. Sin embargo, hasta la fecha, en relación con el patrón de perforación optimizado obtenido considerando la perforación q-periódica, solamente se conocen los resultados obtenidos utilizando BPSK o QPSK.

Además del método de perforación q-periódica, se conocen métodos que optimizan el rendimiento en función de la tasa de código o la longitud de palabra de código cuando se aplica reducción o perforación al código LDPC general. Sin embargo, debido a que los métodos existentes conocidos de descubrimiento de un patrón de reducción/perforación llevan a cabo el proceso de optimización teniendo en cuenta solamente BPSK o QPSK, solamente podía existir un patrón de reducción/perforación optimizado para un código LDPC dado.

Sin embargo, el patrón de perforación/reducción optimizado obtenido cuando se utiliza modulación de orden superior y se determina un esquema de constelación de señal/mapeo de bits (mapeo de bits sobre la constelación de señal), puede ser diferente al obtenido utilizando modulación BPSK o QPSK.

En modulación BPSK o QPSK, debido a que las fiabilidades de los bits que constituyen un símbolo son iguales, las fiabilidades de los bits de una palabra de código son iguales asimismo en la palabra de código LDPC después de que ha sido sometida a reducción o perforación, de manera que no es necesario considerar un esquema de modulación en el proceso de descubrimiento del patrón de reducción/perforación. Sin embargo, tal como se ha descrito anteriormente, en la modulación de orden superior tal como 16QAM, 64QAM y 256QAM, debido a que las fiabilidades de los bits que componen un símbolo son diferentes, cuando se determina el esquema de modulación de orden superior y el esquema de constelación de señal/mapeo de bits, las fiabilidades de los bits de palabra de código en la palabra de código LDPC después de la aplicación de reducción o perforación pueden ser diferentes a las mismas antes de la aplicación de dicha perforación o reducción.

La figura 10 muestra otro ejemplo de una matriz de comprobación de paridad de un código DVB-S2 LDPC.

En la figura 10,  $N_1$ =40,  $K_1$ =10,  $M_1$ =5 y q=6 y las secuencias de posición de ponderación-1 para las columnas 0-ésimas en dos grupos de columnas de una palabra de información, son como sigue:

0 5 10 20 25

5

10

35

40

45

#### 7 15 26

15

20

25

30

35

45

50

Una secuencia de posición de ponderación-1 i-ésima en una columna i-ésima representa secuencialmente la información sobre las posiciones de las filas con 1 en un grupo de columnas i-ésimo.

Haciendo referencia a la figura 10, el grado de cada columna correspondiente al primer grupo de columnas es 5, y el grado de cada columna correspondiente al segundo grupo de columnas es 3. En general, en relación con un código LDPC, su efecto de mejora del rendimiento es excelente en un proceso de descodificación a medida que aumentan los grados. Por lo tanto, normalmente se espera que el rendimiento proporcionado después de la descodificación de los bits correspondientes al primer grupo de columnas sea superior comparado al del segundo grupo de columnas.

Haciendo referencia a la figura 11, se realizará a continuación una breve descripción de un patrón de perforación que es adecuado cuando se aplica modulación BPSK o QPSK al código LDPC con la matriz de comprobación de paridad de la figura 10. En la figura 11, y<sub>0</sub> e y<sub>1</sub> indican cada símbolo BPSK, o indican dos bits que componen un símbolo QPSK. Por lo tanto, y<sub>0</sub> y y<sub>1</sub> son iguales en cuanto a fiabilidad en la constelación de señal.

Haciendo referencia a la figura 11, después de que se ha perforado un bit de paridad correspondiente a una quinta columna en una submatriz correspondiente a un bit de paridad arbitrario, se perfora un bit de paridad cuatro veces en un periodo de q. En este caso, los bits de información correspondientes a las columnas de grado-5 están conectados a bits de paridad perforados mediante 2 aristas, y los bits de información correspondientes a las columnas de grado-3 no están conectados a bits de paridad perforados en el grafo de Tanner.

En general, los bits conectados a muchos bits perforados muestran un mal efecto de mejora del rendimiento en el proceso de descodificación. Sin embargo, en la figura 11, las columnas de grado-5 siguen teniendo 3 aristas que no están conectadas a los bits perforados, de manera que el rendimiento puede no reducirse significativamente en el proceso de descodificación. Además, dado que los bits de información en las columnas de grado-3 no están conectados directamente a los bits de paridad perforados, una degradación significativa del rendimiento puede no ocurrir de manera similar en el proceso de descodificación.

En la presente descripción se asume que las columnas de grado-5 son superiores a las columnas de grado-3 en términos del efecto de mejora del rendimiento en el proceso de descodificación. Sin embargo, esta hipótesis es válida solamente para BPSK o QPSK, y no puede ser aplicada siempre para modulación de orden superior general.

Por ejemplo, tal como se muestra en la figura 12A, la modulación 16QAM puede aplicarse al código LDPC con la matriz de comprobación de paridad de la figura 10. En la figura 12A,  $y_0$  e  $y_1$  indican bits de fiabilidad elevada que determinan signos de una parte real y una parte imaginaria en un símbolo 16QAM, respectivamente. Es decir, la relación de fiabilidad entre los bits se define como  $y_0 = y_1 > y_2 = y_3$ .

Haciendo referencia a la figura 12A, las columnas de grado-5 están mapeadas a  $y_3$  y las columnas de grado-3 están mapeadas a  $y_1$ . En otras palabras, las columnas de grado-5 están mapeadas a un bit de fiabilidad menor y las columnas de grado-3 están mapeadas a un bit de fiabilidad mayor en la constelación de señal.

En este caso, no puede concluirse que las columnas de grado-5 tengan un mayor efecto de mejora del rendimiento en el proceso de descodificación. Las razones son las siguientes. En vista de las características de la modulación 16QAM, dado que las columnas de grado-5 están mapeadas a información de fiabilidad menor en una señal recibida de un canal, su mejora de la fiabilidad se realiza muy lentamente en el proceso de descodificación. Por otra parte, las columnas de grado-3, aunque tienen un grado bajo, son mapeadas a información de fiabilidad menor, de manera que el efecto de mejora de la fiabilidad se produce muy rápido.

40 Tal como se ha descrito anteriormente, no puede garantizarse que los bits correspondientes a las columnas de grado superior tengan siempre un rendimiento superior en el código LDPC al que se aplica modulación de orden superior.

Haciendo referencia de nuevo a la figura 12A, en una implementación, después de que se perfora un bit de paridad correspondiente a una columna 4-ésima en una submatriz correspondiente a un bit de paridad arbitrario, se perfora un bit de paridad 4 veces a un periodo de q. En este caso, los bits de información tanto en las columnas de grado-5 como en las columnas de grado-3 están conectados a bits de paridad perforados mediante 1 arista en el grafo de Tanner.

En el patrón de perforación aplicado en la figura 11, los bits perforados están conectados solamente a las columnas de grado-5 debido a que el efecto de mejora del rendimiento de las columnas de grado-5 es alto, en modulación BPSK o QPSK. Sin embargo, en el patrón de perforación mostrado en la figura 12A, los bits perforados están distribuidos uniformemente considerando la diferencia entre fiabilidades correspondientes a cada grupo de columnas en base al esquema de modulación. En un análisis de este caso, dado que las columnas de grado-5 están

conectadas solamente a un bit perforado, existe una probabilidad elevada de que no se produzca más degradación significativa del rendimiento. Asimismo, aunque las columnas de grado-3 están conectadas a un bit perforado, corresponden a información de alta fiabilidad procedente de una señal recibida, de manera que existe una probabilidad elevada de que no se produzca una degradación significativa del rendimiento.

- De manera similar, incluso cuando se aplica modulación 64QAM al código LDPC con la matriz de comprobación de paridad de la figura 10, tal como se muestra en la figura 12B, las características pueden ser diferentes a las de BPSK, QPSK y 16QAM. En la figura 12B, y<sub>0</sub> e y<sub>1</sub> indican bits de fiabilidad elevada que determinan signos de una parte real y una parte imaginaria en un símbolo 64QAM, respectivamente. Es decir, la relación de fiabilidad entre los bits se define como y<sub>0</sub>= y<sub>1</sub> > y<sub>2</sub>=y<sub>3</sub> > y<sub>4</sub>=y<sub>5</sub>.

- La figura 12B muestra un ejemplo de un patrón de perforación obtenido considerando bits de paridad correspondientes a columnas de grado-2. En la figura 12A para 16QAM, aunque 3 bits entre los bits de paridad perforados están conectados a los bits y<sub>2</sub> e y<sub>3</sub> de fiabilidad mínima, dado que los bits de información correspondientes a las columnas de grado-5 o grado-3 tienen buen rendimiento, no se produce degradación del rendimiento. Sin embargo, en la figura 12B, cuando se aplica 64QAM, cuando demasiados bits de paridad están conectados a y<sub>4</sub> e y<sub>5</sub> con fiabilidades muy bajas, puede producirse una degradación del rendimiento. Por lo tanto, las fiabilidades correspondientes a los bits de paridad deberán asimismo considerarse cuidadosamente.

Cabe señalar, en las figuras 12A y 12B, que cuando la longitud de palabra de código del código LDPC se reduce debido a la reducción o perforación, los órdenes de los bits correspondientes a la constelación de señal son iguales, pero los bits disminuyen en una proporción predeterminada. Por ejemplo, en las figuras 12A y 12B, para un código LDPC, los órdenes (y<sub>3</sub>, y<sub>1</sub>, y<sub>0</sub>, y<sub>2</sub>, y<sub>1</sub>, y<sub>3</sub>, y<sub>2</sub>, y<sub>0</sub>) e (y<sub>5</sub>, y<sub>1</sub>, y<sub>3</sub>, y<sub>4</sub>, y<sub>0</sub>, y<sub>2</sub>, y<sub>3</sub>, y<sub>5</sub>, y<sub>1</sub>, y<sub>2</sub>, y<sub>4</sub>, y<sub>0</sub>) de bits correspondientes a las constelaciones de señal se mantienen, pero la proporción de los bits correspondientes a cada constelación de señal disminuye en proporción a la longitud de la palabra de código LDPC.

Tal como se ha descrito en las figuras 10, 11, 12A y 12B, es fácil suponer que podría el mismo patrón de perforación podría cambiar en función del esquema de modulación. Es decir, cuando se determina un esquema de modulación de orden superior y una constelación de señal/mapeo de bits para un código LDPC dado, el patrón de perforación óptimo está sujeto a cambios en función de las conexiones entre bits perforados y otros bits no perforados. Por lo tanto, deberían aplicarse diferentes patrones de perforación en función de los esquemas de modulación de transmisión, a efectos de minimizar la degradación del rendimiento causada por la perforación.

El proceso general para aplicar el esquema de perforación descrito anteriormente puede resumirse en 5 etapas, como sigue. Para mayor comodidad, en la presente descripción se asume que N<sub>1</sub> indica la longitud de una palabra de código LDPC, cada grupo de columnas incluye M<sub>1</sub> columnas y Np bits de paridad son sometidos a perforación. El siguiente proceso de perforación se muestra resumidamente en la figura 13.

Etapa de perforación 1

Un aparato de transmisión genera una palabra de código DVB-S2 LDPC reducida/no reducida, en la etapa 1301.

35 Etapa de perforación 2

El aparato de transmisión determina el número Np de bits de paridad a perforar en la etapa 1303, y encuentra

$$A = \left| \frac{N_p}{M_1} \right|$$

20

25

30

40

45

en la etapa 1305, donde  $^{\perp}$ x<sup>J</sup> es el máximo entero que es menor o igual que x.

Etapa de perforación 3

El aparato de transmisión determina los bits de paridad a perforar  $p_{i0}$ ,  $p_{i1}$ ,...,  $p_{iA-1}$  para  $0 \le x < A$  y  $0 \le i_x < q$ , de acuerdo con un esquema de modulación de transmisión, en la etapa 1307. Se asume que para  $0 \le x < q$ , se obtuvieron previamente valores de  $i_x$  utilizando un método de evolución de la densidad que considera el esquema de modulación de transmisión (en el presente documento, se da una relación de  $A \le q$ ).

Etapa de perforación 4

El aparato de transmisión aplica perforación a todos los bits de paridad p<sub>ix+kqB</sub> para 0≤x<A y 0≤k<M₁, en la etapa 1307. En este caso, la constante B es un entero predeterminado distinto de cero.

Etapa de perforación 5

El aparato de transmisión perfora adicionalmente los bits de paridad p<sub>iA</sub>+kqB para 0≤k<N<sub>p</sub>-AM₁, en la etapa 1307. A continuación, el aparato de transmisión transmite bits excepto para los bits perforados en la etapa 1309.

A partir de la etapa de perforación 1 hasta la etapa de perforación 5, se comprenderá que el patrón de perforación puede definirse con precisión cuando se conoce el número  $N_p$  de bits a perforar, la información secuencial que define valores de  $i_x$  y el valor de q.

5

Para describir ejemplos detallados en los que se llevan a cabo las etapas de perforación anteriores en función de los esquemas de modulación, en la tabla 1 se muestran patrones de perforación por debajo del óptimo (es decir, suboptimizados) para un código DVB-S2 LDPC con  $N_1$ =16200,  $K_1$ =7200,  $M_1$ =360 y q=25. A continuación se describirá en detalle un proceso de selección de patrones de perforación subóptimos.

En la tabla 1, (p<sub>0</sub>, p<sub>1</sub>, p<sub>2</sub>,..., p<sub>8999</sub>) indica todos los bits de paridad del código DVB-S2 LDPC, que están enumerados en una fila.

Tabla 1

| del códig | principales<br>o DVB-S2<br>PPC |                                                                                                                                                                                                                                          | N <sub>1</sub> =16200, K <sub>1</sub> =7200, M <sub>1</sub> =360, q=25 |                                                         |                                                       |                                                 |                                                             |                         |  |  |

|-----------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|-------------------------|--|--|

|           | ento de bits<br>aridad         | Define un conjunto P <sub>j</sub> que satisface las siguientes características para 0≤j <q=25: p<sub="">j={pk   k≡j mod 25, 0≤k&lt;9000 }. El conjunto P<sub>j</sub> es un conjunto que tiene 360 bits de paridad como entradas.</q=25:> |                                                                        |                                                         |                                                       |                                                 |                                                             |                         |  |  |

| Interva   | lo de N <sub>p</sub>           |                                                                                                                                                                                                                                          |                                                                        | Méto                                                    | do de perfor                                          | ación                                           |                                                             |                         |  |  |

| 0≤Νπ      | <9000                          | 360m) bits caso, π inc                                                                                                                                                                                                                   | de bits de pa<br>de paridad d<br>dica una fund                         | perfora<br>aridad P <sub>π(0)</sub> ,<br>de entre los b | $P_{\pi(1)}$ ,, $P_{\pi}$ bits de parida nutación que | (m-1), y perfo<br>ad correspon<br>e es un patro | ad corresponerar adicional<br>dientes a Pπ<br>ón de perfora | mente (N <sub>p</sub> - |  |  |

| π(0)      | π(1)                           | π(2)                                                                                                                                                                                                                                     | π(3)                                                                   | π(4)                                                    | π(5)                                                  | π(6)                                            | π(7)                                                        | π(8)                    |  |  |

| π(9)      | π(10)                          | π(11)                                                                                                                                                                                                                                    | π(12)                                                                  | π(13)                                                   | π(14)                                                 | π(15)                                           | π(16)                                                       | π(17)                   |  |  |

| π(18)     | π(19)                          | π(20)                                                                                                                                                                                                                                    | π(21)                                                                  | π(22)                                                   | π(23)                                                 | π(24)                                           | -                                                           | -                       |  |  |

|           | Rela                           | ción entre fur                                                                                                                                                                                                                           | iciones de pe                                                          | ermutación s                                            | uboptimizada                                          | as en BPSK/0                                    | QPSK                                                        |                         |  |  |

| 6         | 4                              | 18                                                                                                                                                                                                                                       | 9                                                                      | 13                                                      | 8                                                     | 15                                              | 20                                                          | 5                       |  |  |

| 17        | 2                              | 24                                                                                                                                                                                                                                       | 10                                                                     | 22                                                      | 12                                                    | 3                                               | 16                                                          | 23                      |  |  |

| 1         | 14                             | 0                                                                                                                                                                                                                                        | 21                                                                     | 19                                                      | 7                                                     | 11                                              | -                                                           | -                       |  |  |

|           | Re                             | elación entre                                                                                                                                                                                                                            | funciones de                                                           | permutación                                             | suboptimiza                                           | adas en 16Q                                     | AM                                                          | I                       |  |  |

| 6         | 4                              | 13                                                                                                                                                                                                                                       | 9                                                                      | 18                                                      | 8                                                     | 15                                              | 20                                                          | 5                       |  |  |

| 17        | 2                              | 24                                                                                                                                                                                                                                       | 22                                                                     | 14                                                      | 23                                                    | 3                                               | 19                                                          | 10                      |  |  |

| 1         | 12                             | 0                                                                                                                                                                                                                                        | 16                                                                     | 21                                                      | 7                                                     | 11                                              | -                                                           | -                       |  |  |

# (continuación)

| Relación entre funciones de permutación suboptimizadas en 64QAM |    |    |    |    |    |    |    |    |  |

|-----------------------------------------------------------------|----|----|----|----|----|----|----|----|--|

| 15                                                              | 3  | 23 | 6  | 13 | 18 | 1  | 9  | 17 |  |

| 8                                                               | 5  | 20 | 16 | 22 | 4  | 24 | 14 | 2  |  |

| 21                                                              | 12 | 7  | 10 | 19 | 11 | 0  | -  | -  |  |

Haciendo referencia a la tabla 1, puede apreciarse que cuando se determina la longitud de los bits de paridad a perforar, el proceso de perforación basado en patrones de perforación subóptimos se lleva a cabo mediante un proceso predeterminado independientemente del esquema de modulación, pero las relaciones entre las funciones de permutación que indican patrones de perforación optimizados son todas diferentes de acuerdo con los esquemas de modulación. Es decir, cuando se aplica el método de perforación sin tener en cuenta el esquema de modulación, puede producirse una degradación significativa del rendimiento en función de los esquemas de modulación.

5

15

A partir del proceso de perforación, puede apreciarse asimismo que AM<sub>1</sub> bits de paridad son perforados en la etapa de perforación 3 y la etapa de perforación 4, y N<sub>p</sub>-AM<sub>1</sub> bits de paridad son perforados en la etapa de perforación 5, de manera que se perfora un total de N<sub>p</sub> bits de paridad.

Los patrones de perforación subóptimos mostrados en la tabla 1 pueden no ser únicos en función de las condiciones para encontrar los patrones de perforación. Debido a que son posibles varias selecciones del proceso de selección de los patrones de perforación, que se describirá en detalle a continuación, pueden estar disponibles muchos patrones de perforación que muestran un buen rendimiento. De hecho, los patrones de perforación mostrados en la tabla 2 pueden proporcionar asimismo un rendimiento excelente, tal como los patrones de perforación definidos en la tabla 1.

Tabla 2

|                             | principales o<br>VB-S2 LDP0 |                                                                                                                |                                                                                                                                                                              | $N_1$ =16200, $K_1$ =7200, $M_1$ =360, q=25                                                 |                                                     |                                               |                                              |                              |                                                       |