# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 439 960

51 Int. Cl.:

G11C 5/04 (2006.01) G11C 5/02 (2006.01) H01L 25/065 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 11.12.2008 E 08863853 (1)

(97) Fecha y número de publicación de la concesión europea: 18.09.2013 EP 2223300

(54) Título: Almacenamiento de datos y estructuras apilables

(30) Prioridad:

20.12.2007 US 15345 28.02.2008 US 32203 07.07.2008 US 168354

Fecha de publicación y mención en BOPI de la traducción de la patente: 27.01.2014

(73) Titular/es:

MOSAID TECHNOLOGIES INCORPORATED (100.0%) 11 HINES ROAD, SUITE 203 OTTAWA, ON K2K 2X1, CA

(72) Inventor/es:

OH, HAKJUNE; KIM, JIN-KI y PYEON, HONG BEOM

(74) Agente/Representante:

FÀBREGA SABATÉ, Xavier

#### **DESCRIPCIÓN**

Almacenamiento de datos y estructuras apilables

#### 5 Descripción

#### **ANTECEDENTES**

La unión mediante hilo convencional (WB) es un procedimiento de hacer interconexiones con un chip semiconductor.

Un cable de unión está hecho generalmente de uno de los siguientes materiales: oro, aluminio o cobre. Los diámetros de los cables suelen comenzar en alrededor de 15 micrómetros y pueden ser de hasta varios cientos de micrómetros para aplicaciones de alta potencia.

Hay dos clases principales de unión de conductores: unión mediante bola y unión mediante cuña.

15

- La unión mediante bola generalmente se limita al uso del oro y cable de cobre, y requiere por lo general calor para hacer una unión respectiva. La unión mediante cuña puede utilizar ya sea oro o alambre de aluminio. Cuando se utiliza oro en la unión mediante cuña, se requiere calor para hacer un enlace respectivo.

- 20 En cualquiera de los tipos de unión mediante cables, el cable se une típicamente usando una combinación de calor, presión y energía ultrasónica para hacer una soldadura. La unión mediante cables se considera generalmente la tecnología más rentable y flexible de interconexión. La unión mediante cables se utiliza por lo tanto ampliamente para ensamblar la gran mayoría de los paquetes de semiconductores.

- Los chips de memoria convencionales en un denominado sistema " Paquete Multi-Chip (MCP)" se interconectan a menudo usando un esquema de interconexión en paralelo. Este procedimiento de conexión "multipunto" incluye interconectar los chips de memoria de tal manera que los datos de información y direcciones y las señales de control están acoplados a los chips en una manera paralela usando buses de señal comunes. Por ejemplo, cada chip de memoria puede incluir varias entradas y salidas para dar cabida a una transferencia paralela de información de control, información de dirección y de datos a través de un conjunto interconectado de dispositivos de memoria. Los sistemas de este tipo son conocidos de US 2004/0232 559, Según la cual los chips sucesivos en una pila están desplazados rotacionalmente con respecto a la otra, y desde US 2006/0001176.

- Se han desarrollado Paquetes-sobre-paquetes tridimensionales (PoPs) a en la industria de semiconductores de memoria en los esfuerzos para, por ejemplo, satisfacer la demanda de una mayor densidad de memoria y funcionalidad. De acuerdo con algunos desarrollos de ejemplo, un paquete-sobre-paquete tridimensional convencional se puede fabricar de la siguiente manera: Después de fabricar una oblea y separar la oblea en una pluralidad de chips individuales, un chip correspondiente puede estar unido y conectado eléctricamente a un sustrato. El chip puede encapsularse con una resina de moldeo para producir un paquete. El denominado paquete-sobre-paquete puede ser creado mediante apilamiento de los paquetes. Estos paquete-sobre-paquete emplean un marco de plomo o un sustrato tal como, por ejemplo, una placa de circuito o una placa de circuito impreso. Se pueden emplear un procedimiento de interconexión tal como, por ejemplo, unión mediante hilo (BM), unión automatizada mediante cinta (TAB), o unión por inversión de chip, para establecer conexiones eléctricas entre el chip y el sustrato.

45

50

35

40

Desafortunadamente, los diferentes procedimientos conocidos de fabricación de PoPs requieren el uso de procesos de fabricación complejos. Por otra parte, estos PoPs son bastante grandes en comparación con un chip estándar, reduciendo de este modo la densidad de montaje en el aparato externo. Además, los PoPs pueden incluir tantos chips interconectados con caminos de transmisión de señal largos. Los caminos largos pueden, por ejemplo, causar retardos de la señal que se podría esperar que bajen el rendimiento del sistema.

Sin embargo, los apilamientos de chips de memoria en Paquetes Multi-Chip apilados de tres dimensiones (MCP) al nivel de oblea o de chip tienen la ventaja de tener estructuras simples, tamaños más pequeños y procesos de fabricación simples. Además, un paquete multi-chip al nivel de oblea puede evitar retardos de la señal.

- Es posible clasificar los paquetes multi-chip en dos tipos. Uno de ellos es un paquete multi-chip formado mediante el apilamiento de diferentes tipos de chips, consiguiendo de esta manera multifuncionalidad. El otro es un paquete multi-chip formado por el apilamiento de los mismos tipos de chips, ampliando así la capacidad de memoria.

- Una NAND de memoria flash es un tipo de memoria no volátil de uso generalizado como medio de almacenamiento para electrónica de consumo, como cámaras digitales y reproductores portátiles de música digital, por ejemplo, de uso común.

- La densidad de un chip de memoria flash NAND actualmente disponible puede ser de hasta 32 Gbits (es decir, 4GBytes), por lo que es adecuado para su uso en unidades USB Flash populares ya que el tamaño de un chip es pequeño. Sin embargo, la reciente demanda de dispositivos de electrónica de consumo con funciones de música y

vídeo ha estimulado la demanda de ultra-alta capacidad para almacenar gran cantidad de datos, que no pueden ser satisfechas por el único chip de memoria flash NAND. Por lo tanto, se han interconectado entre sí varios chips de memoria flash NAND en un sistema de almacenamiento para aumentar la eficacia de la capacidad de almacenamiento disponible. En ciertos casos, pueden ser necesarias densidades de almacenamiento Flash de 250 GB o más para satisfacer las necesidades de almacenamiento de datos.

Breve descripción de los dibujos

A continuación se hará referencia a modo de ejemplo a los dibujos adjuntos, de los cuales:

La Figura 1 es un diagrama de ejemplo de un sistema de memoria según realizaciones en este documento;

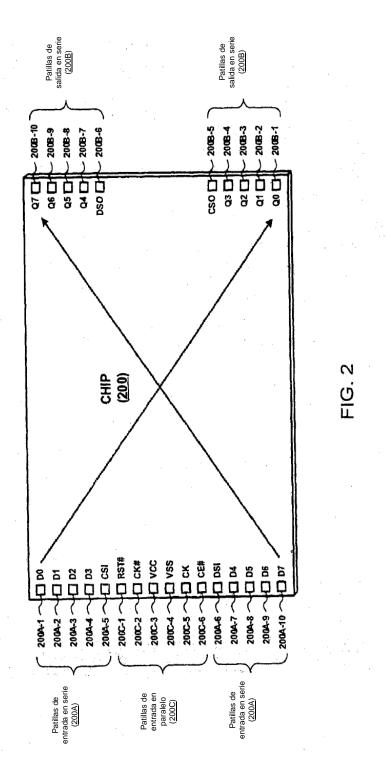

La Figura 2 es un diagrama de ejemplo de un dispositivo de memoria apilable y la correspondiente disposición de configuración de entrada/salida de acuerdo con las realizaciones en este documento;

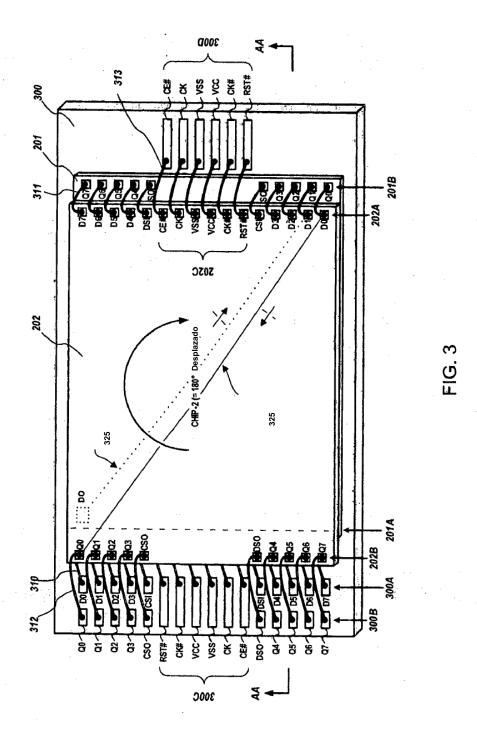

La Figura 3 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria apilado según realizaciones en este documento:

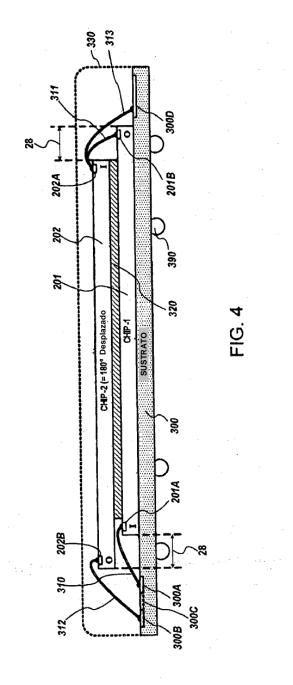

La Figura 4 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria 20 interconectados según realizaciones en este documento;

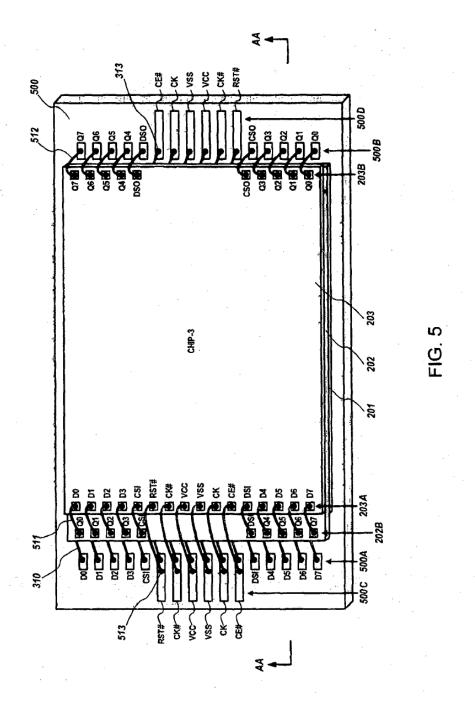

La Figura 5 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria incluyendo múltiples dispositivos de memoria apilados según realizaciones en este documento;

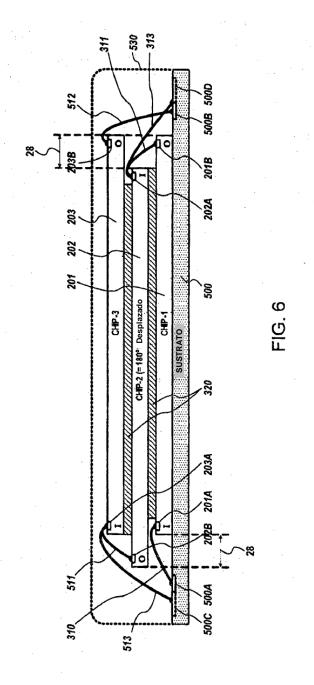

La Figura 6 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria 25 interconectados según realizaciones en este documento;

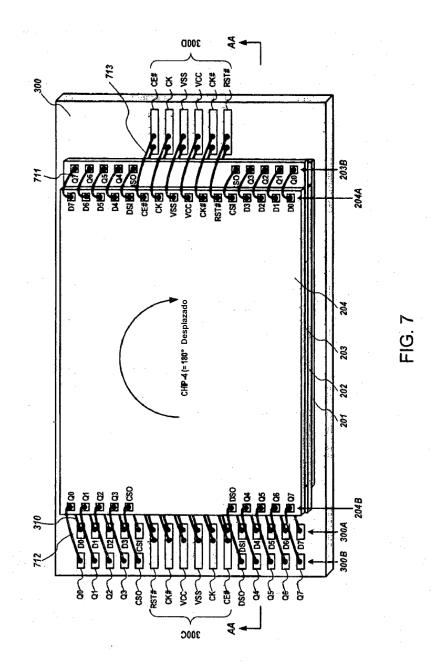

La Figura 7 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria que incluye múltiples dispositivos de memoria apilados según realizaciones en este documento;

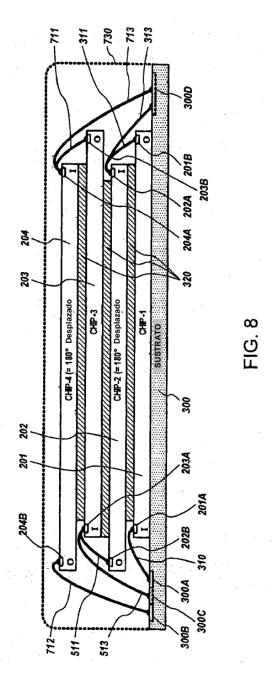

La Figura 8 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria interconectados según realizaciones en este documento;

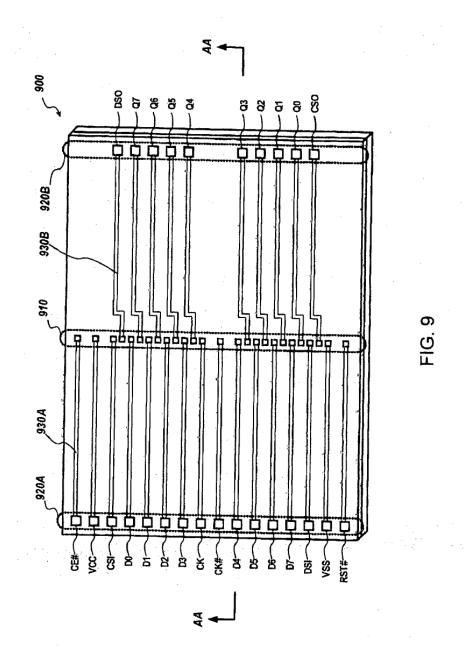

La Figura 9 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

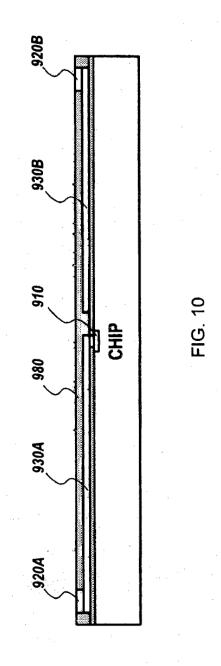

La Figura 10 es un ejemplo de diagrama en sección transversal de una capa de conectividad según realizaciones en este documento;

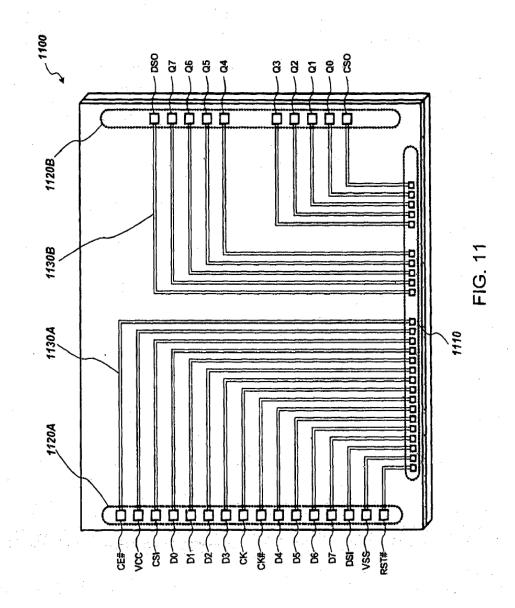

40 La Figura 11 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

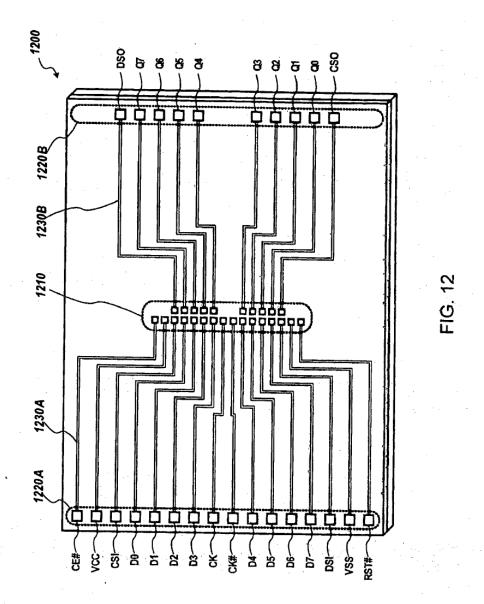

La Figura 12 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

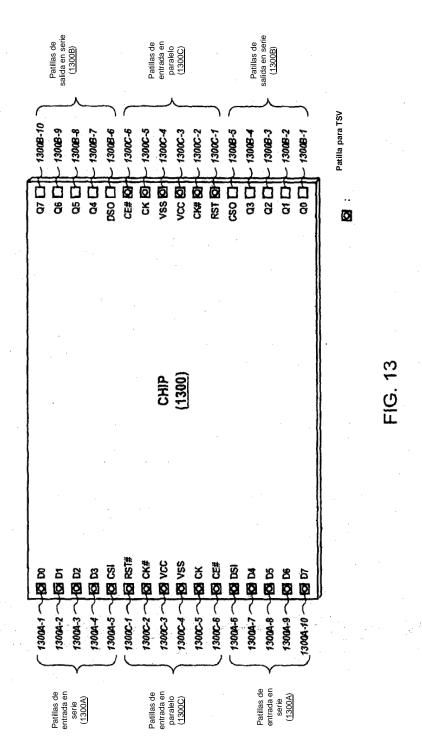

La Figura 13 es un diagrama de ejemplo en 3 dimensiones de un dispositivo de memoria y la disposición de agujeros de paso y patillas de superficie según realizaciones en este documento;

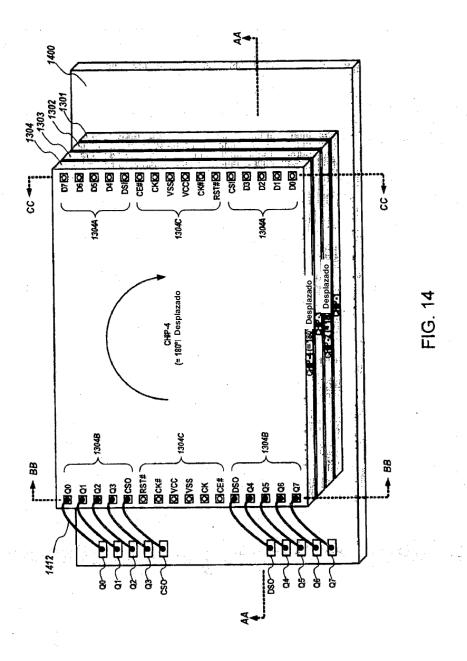

La Figura 14 es un diagrama de ejemplo en 3 dimensiones que ilustra un apilamiento de dispositivos de memoria según realizaciones en este documento;

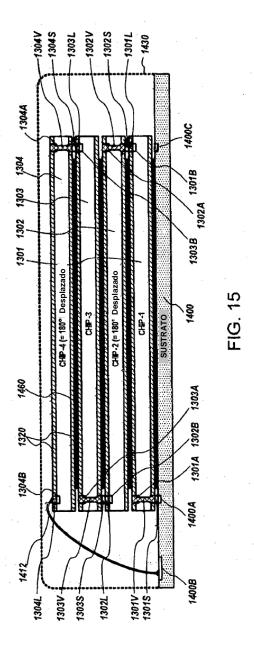

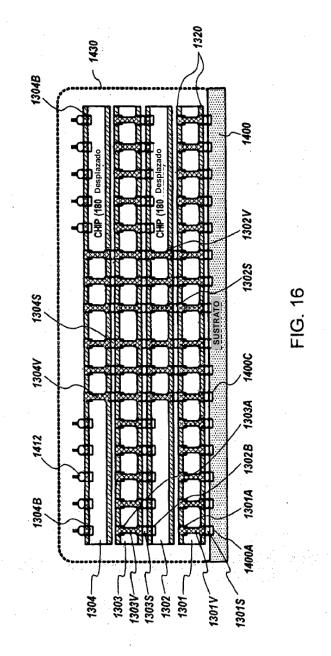

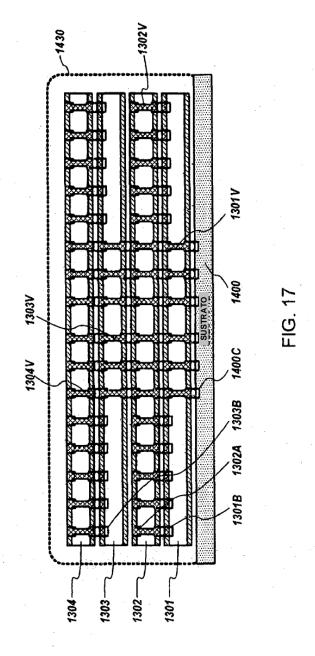

Las Figuras 15, 16, y 17 son ejemplos de diagramas de sección transversal que ilustran la conectividad asociada con una pila de dispositivos de memoria según realizaciones en este documento;

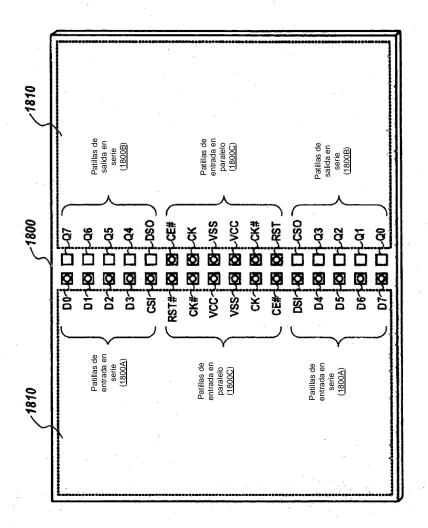

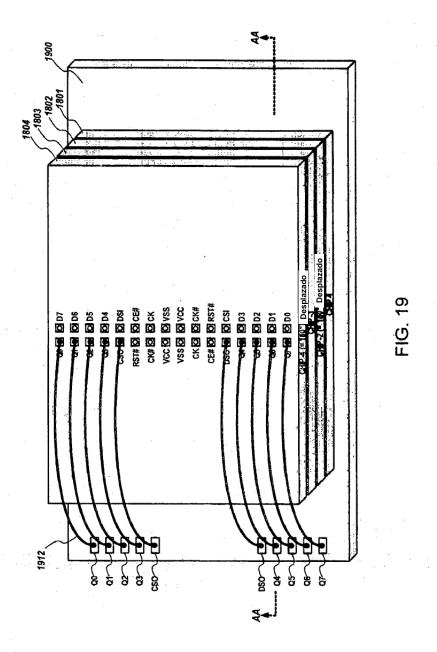

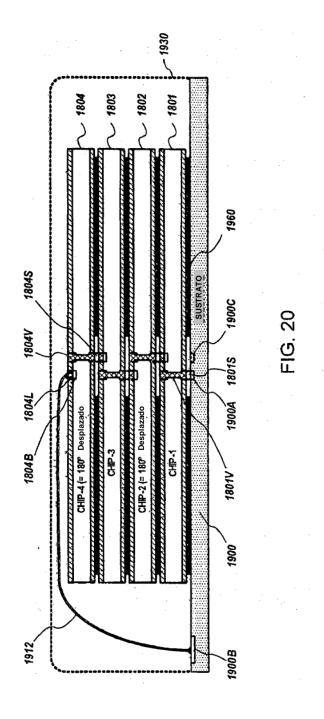

La Figura 18 es un diagrama de ejemplo que ilustra una disposición de configuración de múltiples entradas y múltiples salidas según realizaciones en este documento; La Figura 19 es un diagrama de ejemplo en 3 dimensiones que ilustra un apilamiento de dispositivos de memoria y la conectividad correspondiente según realizaciones en este documento;

60 La Figura 20 es un ejemplo de diagrama en sección transversal que ilustra la conectividad en una disposición en capas de múltiples dispositivos de memoria según realizaciones en este documento; y

La Figura 21 es un ejemplo de diseño de configuración de un dispositivo de memoria apilable según realizaciones en este documento:

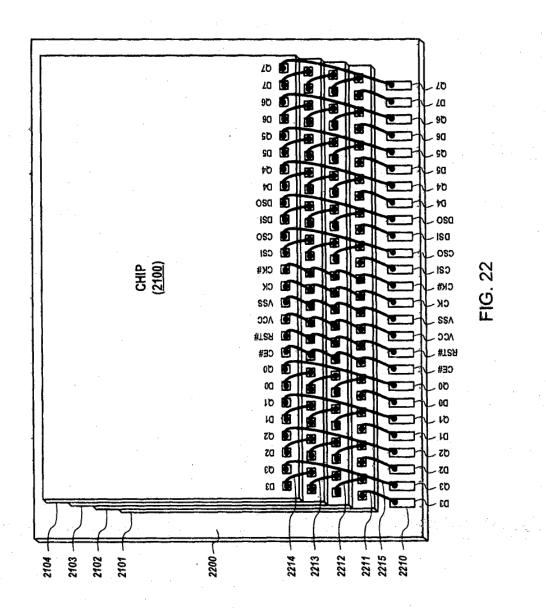

La Figura 22 es un diagrama de ejemplo en 3 dimensiones que ilustra un apilamiento de múltiples dispositivos de

3

10

15

30

35

45

50

55

memoria y la conectividad correspondiente según realizaciones en este documento;

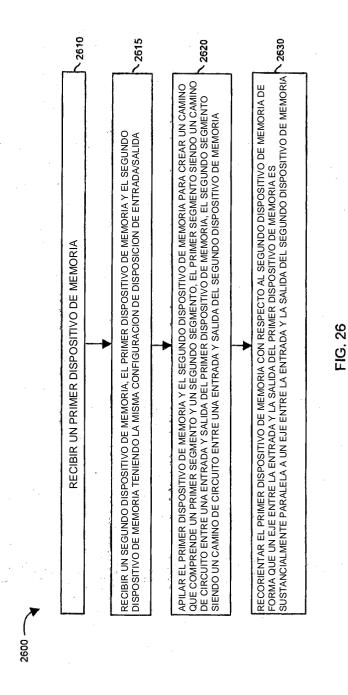

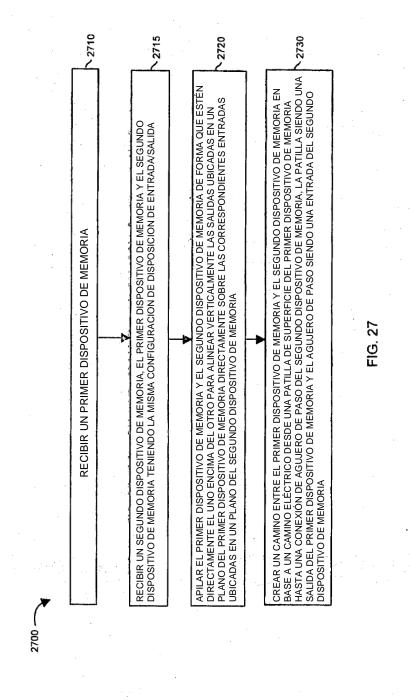

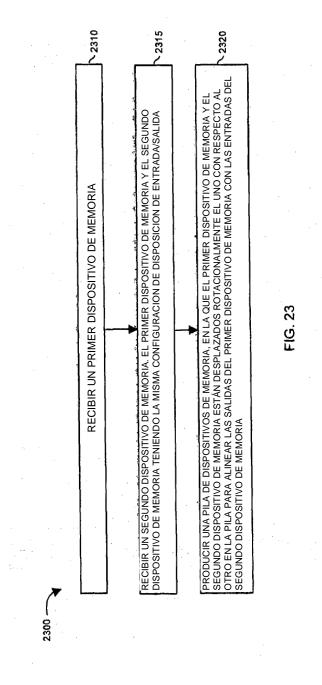

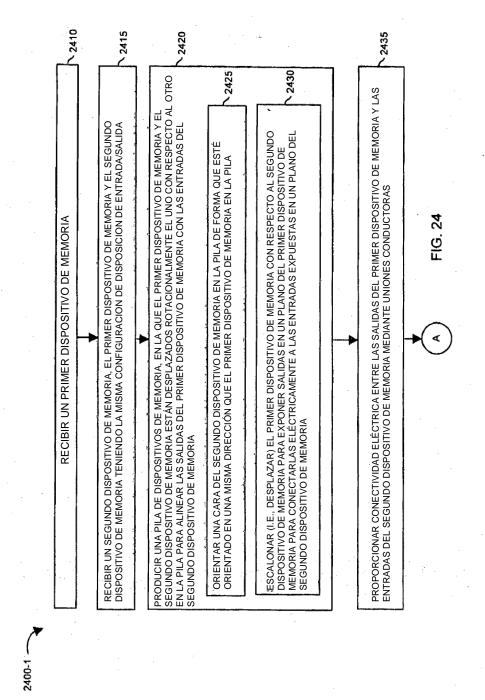

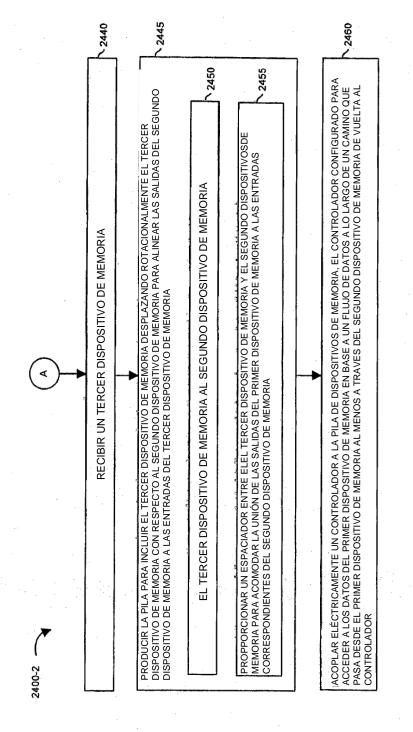

Las Figuras 23-27 son ejemplos de procedimientos asociados con la fabricación de uno o más dispositivos de memoria y/o sistemas de memoria según realizaciones en este documento; y

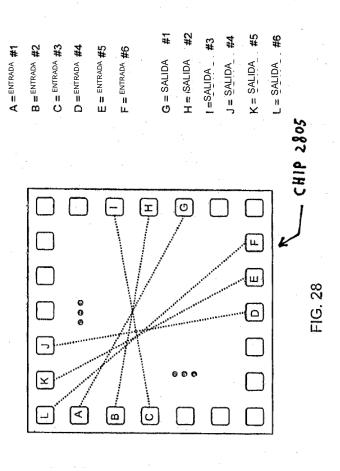

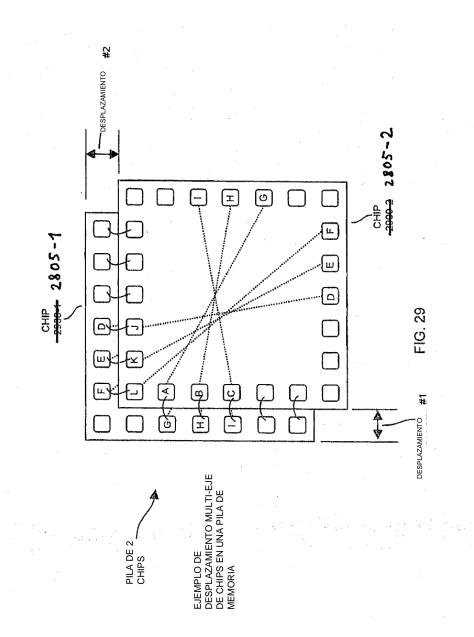

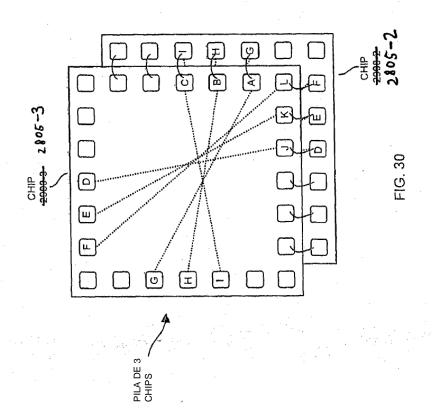

Las Figuras 28-30 son diagramas de ejemplo que ilustran los dispositivos de memoria apilables acuerdo con las realizaciones en este documento.

Descripción detallada de realizaciones ilustradas

5

15

20

25

45

55

60

10 Hav inconvenientes asociados con los procedimier

Hay inconvenientes asociados con los procedimientos convencionales de apilamiento de chips semiconductores para acomodar el almacenamiento de datos. Por ejemplo, a pesar de que un chip MCP apilados de 3-D puede emplear un número de memorias flash NAND para formar un sistema de almacenamiento de memoria, el sistema de almacenamiento respectivo puede no proporcionar un rendimiento requerido como resultado del gran número de interconexiones necesarias entre los dispositivos de memoria. Por lo tanto, la fabricación de una pila tridimensional de altas prestaciones de dispositivos de memoria puede ser un reto.

Hay otros inconvenientes asociados con el apilamiento de chips semiconductores. La fijación de una pila de dispositivos a la correspondiente placa de circuito impreso (PCB) o a un sustrato puede ser difícil. Además, debido a que hay muchas interconexiones entre los dispositivos de memoria en una pila efectos indeseables, tales como por ejemplo diafonía, pueden limitar el rendimiento de estos tipos de subsistemas de almacenamiento.

Un factor específico que limita el rendimiento de un sistema de almacenamiento de la memoria es los retardos de propagación. Los retardos de propagación causados por interconexiones muy cargadas y largas pueden limitar el número de chips que puede ser incorporado en un sistema de almacenamiento de memoria.

En general, las realizaciones la presente invención incluyen mejoras sobre los procedimientos, los sistemas convencionales, etc.

De acuerdo con la invención, tal y como se define en las reivindicaciones adjuntas, un sistema de almacenamiento de memoria incluye un apilamiento de un primer dispositivo de memoria y un segundo dispositivo de memoria. El primer dispositivo de memoria y el segundo dispositivo de memoria tienen una misma disposición de configuración de entrada/salida. Para formar la pila, el segundo dispositivo de memoria se fija al primer dispositivo de memoria. Para facilitar la conectividad entre las salidas del primer dispositivo de memoria y las entradas del segundo dispositivo de memoria, el segundo dispositivo de memoria está rotacionalmente desplazado con respecto al primer dispositivo de memoria con las entradas correspondientes del segundo dispositivo de memoria. El desplazamiento rotacional del segundo dispositivo de memoria con respecto al primer dispositivo de memoria en la pila resulta en la alineación sustancial de una o más salidas del primer dispositivo de memoria con una o más entradas respectivas del segundo dispositivo de memoria.

La pila de dispositivos de memoria puede incluir caminos que facilitan una o más configuraciones de conexión en serie entre el primer dispositivo de memoria y el segundo dispositivo de memoria.

Tal realización es útil respecto a procedimientos convencionales debido a que los dispositivos de memoria rotacionalmente desplazados (por ejemplo, alrededor de 180 grados) para alinear las entradas y salidas permiten crear una pila de almacenamiento de memoria sobre la base de dispositivos de memoria que tienen una disposición de configuración de entrada/salida común. La configuración común alivia la necesidad de almacenar dispositivos de memoria que tienen diferentes disposiciones de configuración de entrada/salida para crear una pila.

Tenga en cuenta que un controlador puede estar acoplado a la pila de diferentes maneras. Por ejemplo, el controlador y la pila se pueden unir a un sustrato tal como, por ejemplo, una placa de circuito impreso. Los caminos conductores en el sustrato pueden proporcionar conectividad entre el controlador y la pila de dispositivos de memoria.

Según otra realización, la pila puede incluir al controlador. En dicha realización, el controlador puede fijarse a un dispositivo de memoria en la pila tal como el primer o el último dispositivo de memoria en la pila (por ejemplo, dispositivo de memoria en ambos extremos de la pila).

Téngase en cuenta que la pila puede incluir generalmente cualquier número razonable de dispositivos de memoria. Por ejemplo, en una realización, la pila incluye un tercer dispositivo de memoria fijado al segundo dispositivo de memoria. El tercer dispositivo de memoria tiene la misma configuración de disposición de entrada/salida que el primer dispositivo de memoria y el segundo dispositivo de memoria. Para alinear las salidas del segundo dispositivo de memoria con las entradas correspondientes del tercer dispositivo de memoria, el tercer dispositivo de memoria en la pila está rotacionalmente desplazado con respecto al segundo dispositivo de memoria en la pila.

65 En consecuencia, las realizaciones en este documento incluyen compensar rotacionalmente cada dispositivo de memoria sucesivo en la pila para aumentar la expansión de una longitud de una configuración de conexión en serie

a través de la pila. En el ejemplo anterior, la adición de la tercera memoria y/o dispositivos de memoria posteriores a la pila extiende los uno o más caminos a través del primer dispositivo de memoria, el segundo dispositivo de memoria y el tercer dispositivo de memoria para el transporte de los datos.

- Los dispositivos de memoria (por ejemplo, el primer dispositivo de memoria, el segundo dispositivo de memoria, el tercer dispositivo de memoria, etc.) en la pila pueden ser de forma plana y tener caras respectivas superior e inferior. Es decir, los dispositivos de memoria pueden ser chips semiconductores cortados de una o más obleas. Los dispositivos de memoria pueden ser apilados unos encima de los otros, en donde una parte inferior respectiva de un dispositivo de memoria en la pila se fija a una parte superior de otro dispositivo de memoria en la pila de tal manera que la parte superior del primer dispositivo de memoria y la parte superior del segundo punto de dispositivo de memoria están orientadas en una misma dirección a lo largo de la pila. Cada uno de múltiples dispositivos de memoria en la pila puede estar orientado en la misma dirección a lo largo de la pila. Por lo tanto, la fabricación no necesita incluir un proceso de volteo complejo para voltear los chips con respecto a los otros.

- La disposición de configuración de entrada/salida de los dispositivos de memoria utilizadas en la pila incluye contactos de entrada y contactos de salida. Como se ha mencionado, la disposición de configuración de cada uno de los dispositivos de memoria es la misma. Cuando se crea, la pila incluye una o más conexiones de configuración en serie o caminos basados en conexiones (por ejemplo, enlaces de alambre, conexiones a través de agujeros, etc.) entre los contactos de entrada/salida. Por ejemplo, los uno o más caminos se pueden crear sobre la base de enlaces conductores entre los contactos de salida de un dispositivo de memoria en la pila con los contactos de entrada correspondientes de un dispositivo de memoria sucesivo en la pila.

Los uno o más caminos en la pila soportan la transmisión de datos a través de la pila. Un controlador está acoplado eléctricamente a los uno o más caminos en la pila para acceder a los datos almacenados en la pila.

25

30

50

55

60

- El controlador está acoplado a un dispositivo de memoria en la pila. El controlador está configurado para acceder a los datos del dispositivo de memoria en base a un flujo de datos a lo largo del camino a través de uno o más dispositivos de memoria en la pila. Por ejemplo, el controlador puede acceder a los datos del primer dispositivo de memoria en base a un transporte de datos a lo largo de uno o más caminos a través de por lo menos el segundo dispositivo de memoria al controlador. Una conexión entre un último dispositivo de memoria en la pila de hacia el controlador permite al controlador para datos desde los dispositivos de memoria en la pila en base a un flujo de datos a lo largo de los uno o más caminos.

- Un acoplamiento entre el controlador y, por ejemplo, el primer dispositivo de memoria de la pila permite al controlador transmitir datos a través de los dispositivos de memoria y por lo tanto almacenar datos en los dispositivos de memoria. El acoplamiento entre el último dispositivo de memoria en la pila al controlador permite al controlador recuperar los datos almacenados en los respectivos dispositivos de memoria.

- Cada dispositivo de memoria en la pila puede ser ajustado a un modo de paso a través o a un modo de acceso a memoria. En una realización, el modo de paso a través permite a un dispositivo de memoria correspondiente en la pila transmitir los datos recibidos en una entrada del dispositivo de memoria respectivo a lo largo de un camino de circuito hasta una salida del dispositivo de memoria respectivo. Por lo tanto, en realizaciones de ejemplo, el controlador puede hacer que los datos pasen a través de un primer dispositivo de memoria en la pila para su almacenamiento en un dispositivo de memoria de destino en la pila.

- En una realización, el modo de acceso a memoria asociada con un dispositivos de memoria permite i) recepción de datos en un camino y almacenamiento de datos en los circuitos de la memoria asociados con un dispositivo de memoria correspondiente en la pila, y ii) recuperación de datos de los circuitos de memoria en el dispositivo de memoria respectivo para su transmisión en el camino hacia una salida del dispositivo de memoria respectivo hacia el controlador. Por lo tanto, el controlador puede hacer que los datos se almacenen o recuperen de un dispositivo de memoria particular en la pila.

- Cada uno de los uno o más caminos a través de la pila puede incluir segmentos a través de los dispositivos de memoria. Por ejemplo, un camino a través de la pila puede incluir un primer segmento de camino y un segundo segmento de camino. El primer segmento de camino incluye un camino de circuito entre una entrada y salida del primer dispositivo de memoria. El segundo segmento de camino incluye un camino de circuito entre una entrada y la salida del segundo dispositivo de memoria. En base al desplazamiento del segundo dispositivo de memoria con respecto al primer dispositivo de memoria en el apilamiento, un eje entre la entrada y la salida del primer dispositivo de memoria en la pila puede ser paralelo a un eje entre la entrada y la salida de un segundo dispositivo de memoria (por ejemplo, sucesivas) dispositivo de memoria en la pila.

- En cumplimiento de tales realizaciones, una dirección de flujo de datos desde la entrada a la salida del primer dispositivo de memoria puede ser sustancialmente opuesta a una dirección de flujo de datos desde la entrada a la salida del segundo dispositivo de memoria. Por ejemplo, el primer segmento de camino de un camino dado (por ejemplo, una parte del camino en el primer dispositivo de memoria) a través de la pila puede atravesar diagonalmente un plano del primer dispositivo de memoria desde una entrada cerca de un primer borde de la

primera memoria dispositivo hasta una salida cerca de un segundo borde del primer dispositivo de memoria. El segundo segmento de camino del camino dado (por ejemplo, una parte del camino en el segundo dispositivo de memoria) a través de la pila puede atravesar diagonalmente un plano del segundo dispositivo de memoria desde una entrada cerca de un primer borde del segundo dispositivo de memoria hasta una salida cerca de un segundo borde del segundo dispositivo de memoria.

5

10

15

20

25

30

45

50

55

60

65

Tal y como se discutió previamente, apilar dispositivos de memoria incluye desplazar rotacionalmente cada dispositivo de memoria sucesivo en la pila. En otras realizaciones, ha de tenerse en cuenta que los dispositivos de memoria pueden estar escalonados o desplazados con respecto a un eje de apilamiento de manera que cada chip en las pilas crea un saliente respecto a otro chip en la pila. Por ejemplo, el segundo dispositivo de memoria en la pila puede estar escalonado o desplazado con respecto al primer dispositivo de memoria en la pila para exponer salidas en un plano del primer dispositivo de memoria para conectar eléctricamente las entradas en un plano del segundo dispositivo de memoria. El tercer dispositivo de memoria puede estar escalonado o desplazado con respecto al segundo dispositivo de memoria en la pila para exponer salidas en un plano del segundo dispositivo de memoria para conectarlas eléctricamente a las entradas en un plano del tercer dispositivo de memoria.

En general, el escalonamiento de los dispositivos de memoria se puede repetir a lo largo de la creación de la pila de modo que las salidas de un dispositivo de memoria estén expuestas para conectarlas a las entradas de un dispositivo de memoria sucesivo.

Cada par sucesivo de dispositivos de memoria en la pila puede conectarse eléctricamente entre sí. Por ejemplo, los enlaces conductores proporcionan conexión de las salidas en el plano del primer dispositivo de memoria a las entradas en el plano del segundo dispositivo de memoria. En una realización, las entradas y salidas de cada dispositivo de memoria son patillas de superficie. Los enlaces pueden ser cables de conexión que conectan una patilla de superficie de entrada de un dispositivo de memoria a una patilla de superficie de salida de otro dispositivo de memoria.

Cada par sucesivo de dispositivos de memoria en la pila puede conectarse eléctricamente entre sí. Por ejemplo, los enlaces conductores proporcionan conexión de las salidas en el plano del primer dispositivo de memoria a las entradas en el plano del segundo dispositivo de memoria. En una realización, las entradas y salidas de cada dispositivo de memoria son patillas de superficie. Los enlaces pueden ser enlaces de cable que conectan una patilla de superficie de entrada de un dispositivo de memoria a una patilla de superficie de salida de otro dispositivo de memoria.

De acuerdo con otra realización, nótese que, como alternativa a escalonar los dispositivos de memoria sucesivos en la pila para realizar las conexiones, los dispositivos de memoria pueden estar alineados en la pila de tal manera que las salidas situadas en una cara superior del primer dispositivo de memoria están alineadas verticalmente sobre entradas correspondientes situadas en la parte superior orientadas hacia el segundo dispositivo de memoria. De acuerdo con una realización, las entradas de la disposición de configuración de entrada/salida asociada con cada dispositivo de memoria se pueden configurar como conexiones con agujeros de paso. Las salidas de la disposición de configuración de entrada/salida asociadas con cada dispositivo de memoria pueden configurarse como patillas que dan soporte a la conectividad de superficie.

El uno o más caminos a través de la pila se pueden crear mediante conectando las salidas de un dispositivo de memoria en la pila a las entradas de un dispositivo de memoria sucesivo en la pila. Proporcionar, por ejemplo, material conductor entre una patilla de superficie y el agujero de conexión correspondiente puede crear una conexión de enlace entre los dispositivos de memoria.

Otras realizaciones de la presente invención incluyen un dispositivo de memoria, tal como, por ejemplo, un chip semiconductor. El chip semiconductor incluye una configuración de entrada-salida que incluye una o más entradas y una o más salidas. El chip semiconductor incluye un camino de circuito de entrada-salida respectivo entre pares de cada una de las entradas y las salidas para transmitir datos a través del chip semiconductor.

Las entradas del chip semiconductor se pueden configurar como conexiones de agujero de paso o caminos. Como su nombre lo indica, las conexiones de agujero de paso pasan de una cara superior hacia el chip semiconductor a través del chip semiconductor hasta una cara inferior del chip semiconductor. Las conexiones de agujero de paso también están conectadas eléctricamente a los circuitos en el chip semiconductor respectivo. Las conexiones de agujero de paso proporcionan, por lo tanto, una manera de conectar los circuitos internos del chip semiconductor a otra circuitería externa.

Las salidas del chip semiconductor se pueden configurar como patillas de contacto de superficie dispuestas en una superficie plana del chip semiconductor. Las conexiones de las patillas de superficie también están conectadas eléctricamente a los circuitos correspondientes en el chip semiconductor respectivo. Por lo tanto, similar a las conexiones de agujero de paso, las patillas de superficie proporcionan una manera de conectar los circuitos internos del chip semiconductor a otra circuitería externa.

La creación de un chip semiconductor incluyendo salidas de patilla de superficie y entradas de agujero de paso es útil porque una conexión entre un chip semiconductor y un siguiente chip semiconductor de la misma configuración de entrada/salida se puede conectar a través de un enlace entre una respectiva patilla de superficie y conexión de agujero de paso. Es decir, el conector de agujero de paso del chip semiconductor permite la conectividad entre la patilla de contacto de la superficie en la salida del chip semiconductor con un conector de agujero de paso en una entrada de otro chip semiconductor (que tiene la misma disposición de configuración).

5

10

15

20

25

30

35

40

55

60

Tal y como se discutió anteriormente, un dispositivo de memoria tal como, por ejemplo, un chip semiconductor puede incluir múltiples entradas y múltiples salidas. Cada una de las múltiples entradas se puede configurar como conectores o vías de agujero de paso. Cada una de las múltiples salidas puede configurarse como patillas de superficie. Las conexiones incluyen material conductor entre las conexiones a través del agujero y patillas de superficie correspondientes para crear caminos a través de la pila.

Más específicamente, otra realización de la presente memoria incluye un apilamiento del chip semiconductor como se discutió anteriormente. Por ejemplo, un sistema de almacenamiento de memoria de acuerdo con las realizaciones en este documento puede incluir un primer dispositivo de memoria y un segundo dispositivo de memoria que tiene una misma entrada/disposición de configuración de salida que la del primer dispositivo de memoria. El sistema de memoria de almacenamiento se puede configurar como una pila. La pila incluye el segundo dispositivo de memoria fijado al primer dispositivo de memoria. El segundo dispositivo de memoria está orientado en la pila para alinear las salidas del primer dispositivo de memoria. La pila incluye además la conectividad entre las salidas del primer dispositivo de memoria y las entradas del segundo dispositivo de memoria. Por ejemplo, como se mencionó anteriormente, la conectividad entre dispositivos de memoria puede incluir conexiones entre las patillas de superficie en un plano del primer dispositivo de memoria y los agujeros de paso del segundo dispositivo de memoria. En dicha realización, las patillas de superficie son salidas del primer dispositivo de memoria y los agujeros de paso son entradas del segundo dispositivo de memoria.

Para alinear las patillas de superficie del primer dispositivo de memoria con los correspondientes agujeros de paso del segundo dispositivo de memoria, la invención incluye desplazar rotacionalmente (una cantidad tal como, por ejemplo, alrededor de 180 grados) un dispositivo de memoria respecto a un dispositivo de memoria sucesivo en la pila. El desplazamiento de rotación puede llevarse a cabo alrededor de un eje de apilamiento, tal como por ejemplo, el eje a lo largo del cual los dispositivos de memoria se apilan los unos encima de los otros.

La conectividad entre dispositivos de memoria puede incluir, a modo de un ejemplo no limitativo, una primera conexión y una segunda conexión. En una realización, la primera conexión conecta una primera patilla de superficie del primer dispositivo de memoria a un primer agujero de paso del segundo dispositivo de memoria. La segunda conexión conecta una segunda patilla de superficie del primer dispositivo de memoria a un segundo agujero de paso del segundo dispositivo de memoria. La primera conexión puede ser parte de un segmento de camino a través de la pila, mientras que la segunda conexión puede ser parte de otro segmento de camino a través de la pila. Es decir, la primera conexión crea un primer camino conectando una primera salida del primer dispositivo de memoria a una primera entrada del segundo dispositivo de memoria, la segunda conexión creando un segundo camino conectando una segunda salida del primer dispositivo de memoria a un segundo de entrada del segundo dispositivo de memoria. Por supuesto, puede crearse cualquier número adecuado de caminos en la pila a través de conexiones entre los dispositivos de memoria.

En una línea similar a lo discutido anteriormente, la pila puede incluir un número de dispositivos de memoria adicionales que tienen la disposición de configuración más recientemente discutida de patillas de superficie y agujeros de paso. Por ejemplo, en una realización, la pila incluye un tercer dispositivo de memoria fijado al segundo dispositivo de memoria. El tercer dispositivo de memoria tiene la misma disposición de configuración de entrada/salida que el primer dispositivo de memoria y el segundo dispositivo de memoria. En dicha realización, la pila incluye la conectividad entre las salidas del segundo dispositivo de memoria y las entradas del tercer dispositivo de memoria. La conectividad incluye conexiones entre las patillas de superficie o salidas en un plano del segundo dispositivo de memoria y los agujeros de paso, tales como, por ejemplo, las entradas del tercer dispositivo de memoria. Como se discutió previamente, la conectividad desde un dispositivo de memoria hasta un siguiente dispositivo de la pila forma caminos respectivos a través de los dispositivos de memoria.

En cualquiera de las realizaciones, los uno o más caminos a través de la pila dan soporte al transporte de datos a través de la pila. Algunos de los caminos se pueden utilizar con fines de control. Por ejemplo, uno o más caminos a través de los dispositivos de memoria pueden ser usados para transmitir señales de control o datos de control a través de y para los dispositivos de memoria en la pila para permitir que un controlador respectivo controle los dispositivos de memoria.

Las señales de control para controlar el funcionamiento de uno o más dispositivos de memoria respectivos en la pila pueden ser generados por un controlador u otro dispositivo de memoria en la pila.

El sistema de almacenamiento de memoria incluyendo la disposición de configuración de las patillas de superficie y los agujeros de paso incluye un controlador. El controlador está acoplado eléctricamente a la pila para acceder a

datos almacenados en la pila. El controlador está acoplado eléctricamente a un primer dispositivo de memoria en la pila tal como, por ejemplo, el primer dispositivo de memoria. El controlador está configurado para acceder a los datos del primer dispositivo de memoria en base a un flujo de datos a lo largo del camino desde el primer dispositivo de memoria a través de por lo menos el segundo dispositivo de memoria y/u otros dispositivos de memoria en la pila hasta el controlador. Una conexión entre un último dispositivo de memoria en la pila al controlador permite que al controlador recibir datos desde los dispositivos de memoria en la pila en base a un flujo de datos a lo largo de los uno o más caminos.

- El acoplamiento entre el controlador y el primer dispositivo de memoria en la pila permite al controlador transmitir datos a través de los dispositivos de memoria y por lo tanto almacenar datos en los dispositivos de memoria. El acoplamiento entre el último dispositivo de memoria en la pila al controlador permite al controlador recuperar los datos almacenados en los respectivos dispositivos de memoria. Sin embargo, en esta última realización, incluye la conectividad de agujeros de paso a conexiones de patillas de superficie.

- Para permitir la entrega de datos al controlador, tenga en cuenta que las realizaciones en este documento también pueden incluir conectividad eléctrica tal como por ejemplo, enlaces de alambre entre patillas de superficie (tales como por ejemplo, salidas) en un plano del segundo dispositivo de memoria (o un último dispositivo de memoria en la pila) a las entradas asociadas con el controlador.

- De una manera como se discutió anteriormente, cada dispositivo de memoria en la pila puede ser ajustado a un modo de paso directo o a un modo de acceso a memoria.

- En una realización, cada uno de los dispositivos de memoria en la pila es de forma plana y tiene caras respectivas superior e inferior. Un primer dispositivo de memoria y un dispositivo de memoria subsiguiente se apilan el uno encima del otro, de forma que una cara inferior respectiva del segundo dispositivo de memoria está fijada a una cara superior del primer dispositivo de memoria. La cara superior del primer dispositivo de memoria y la cara superior del segunda dispositivo de memoria están orientadas en una misma dirección a lo largo de la pila. En base a la alineación correcta de los dispositivos de memoria en la pila, las salidas que se encuentran en la parte superior del primer dispositivo de memoria están alineadas verticalmente sobre las entradas correspondientes situadas en la cara superior del segundo dispositivo de memoria. En otras palabras, los dispositivos de memoria pueden estar alineados de forma que las patillas de superficie (salidas) de un dispositivo de memoria en la pila se alinean directamente con agujeros de paso (entradas) de un dispositivo de memoria siguiente en la pila.

- En otras realizaciones adicionales en este documento, un chip semiconductor incluye una disposición de configuración que incluye múltiples entradas y múltiples salidas para la transmisión de datos a través del chip semiconductor. El chip semiconductor también incluye pares entrada-salida en donde las entradas en la disposición de configuración están emparejadas en diagonal con las múltiples salidas en la disposición de configuración. El chip semiconductor incluye un camino de circuito de entrada-salida respectivo entre cada uno de los pares de entrada-salida.

- Los caminos de circuito a través del chip semiconductor pueden dar soporte a diferentes funciones, tales como, por ejemplo, el transporte de datos o señales de control a través del chip semiconductor y, por lo tanto, de la pila de almacenamiento de memoria.

- El diseño de la configuración del chip semiconductor puede incluir la ordenación de las múltiples entradas y múltiples salidas. Cada uno de los respectivos caminos de circuito entre los pares de entrada-salida en la disposición incluye una entrada y una salida correspondientes. La salida correspondiente de un par de entrada-salida está en diagonal a través de la entrada en el diseño del chip semiconductor. En una realización, la salida correspondiente en la disposición está desplazada 180 grados con respecto a la entrada en la disposición.

- En otras realizaciones adicionales, un chip semiconductor incluye una disposición de configuración que incluye múltiples entradas y múltiples salidas para la transmisión de datos a través del chip semiconductor. Los pares de entrada-salida de la disposición se basan en emparejar cada entrada con una correspondiente de las múltiples salidas. Un camino de circuito de entrada-salida correspondiente entre cada una de las parejas de entrada-salida está orientada de forma que cruza otros caminos de circuito respectivos de entrada y salida en el chip semiconductor. En otras palabras, de acuerdo con una realización, una disposición de configuración de entrada/salida del chip semiconductor puede ser elegida de tal manera que algunos o todos los ejes asociados con las combinaciones de entrada-salida se crucen entre sí.

55

- 60 El diseño de la disposición de configuración del chip semiconductor puede incluir una columna de entradas y una columna de salidas. Las columnas pueden ser paralelas entre sí y estar dispuestas a lo largo o en la proximidad de los bordes respectivos del chip semiconductor. En cumplimiento de dicha realización, los pares de entrada-salida incluyen caminos de circuito entre una entrada en una columna y una salida en otra columna. En otras realizaciones, cada una de las columnas incluye dos entradas y salidas.

- Tal y como se discutió previamente, el chip semiconductor incluye pares de entrada-salida puede incluir una

memoria para almacenar datos. Cada uno de los respectivos caminos de circuito de entrada-salida permite el acceso a una parte correspondiente de la memoria.

En un ejemplo de realización, la disposición de configuración puede incluir una ordenación de las múltiples entradas y múltiples salidas en las proximidades de un perímetro del chip semiconductor. Cada uno de los respectivos caminos de circuito entre los pares de entrada-salida incluye una entrada en la proximidad del perímetro del chip semiconductor, así como una salida correspondiente en la proximidad del perímetro del chip semiconductor. La salida correspondiente de un camino de circuito respectivo puede residir en una posición a sustancialmente 180 grados de diferencia respecto de la entrada, de forma similar a la configuración de un reloj tradicional en el que el número 4 está situado frente al número 10, el número 5 se encuentra frente al número 11, y así sucesivamente. Sin embargo, como se mencionó anteriormente, las entradas/salidas del chip semiconductor pueden formar una o más columnas en lugar de formar un círculo.

5

10

15

20

25

30

35

40

45

50

55

En otras realizaciones adicionales, la pila de almacenamiento de memoria incluye un primer dispositivo de memoria y un segundo dispositivo de memoria. Tanto el primer dispositivo de memoria como el segundo dispositivo de memoria tienen una misma disposición de configuración de entrada/salida. El primer dispositivo de memoria está desplazado (para producir un paso) con respecto al segundo dispositivo de memoria para exponer salidas sobre una superficie plana del primer dispositivo de memoria para conectarlo eléctricamente a las entradas en una superficie plana del segundo dispositivo de memoria. Cada dispositivo de memoria adicional añadido a la pila puede estar desplazado en la misma dirección para producir un tipo de escalera de apilamiento.

La conectividad entre las salidas de un dispositivo de memoria a la entrada de otro dispositivo de memoria crea caminos. Tal y como se mencionó anteriormente, los caminos facilitan una conexión en serie a través del primer dispositivo de memoria y el segundo dispositivo de memoria y dan soporte a funcionalidades tales como, por ejemplo, el transporte de datos. Los datos pueden ser comandos, información para su almacenamiento en un dispositivo de memoria respectivo, información que se recupera de un dispositivo de memoria respectivo, etc.

La conectividad entre un dispositivo de memoria y otro dispositivo de memoria en la pila de almacenamiento de memoria puede incluir un enlace conductor. La conexión conductora puede ser un enlace de cable entre una salida del primer dispositivo de memoria y una entrada del segundo dispositivo de memoria.

En una realización, la disposición de configuración de entrada/salida de cada dispositivo de memoria en la pila de almacenamiento de memoria incluye una secuencia de múltiples entradas y múltiples salidas a lo largo de uno o más bordes de un dispositivo de memoria respectivo.

Una entrada y de salida correspondiente en un dispositivo de memoria pueden estar situados uno junto al otro en la disposición de configuración de entrada/salida del chip semiconductor, tal y como se discute más recientemente. La salida de un dispositivo de memoria dado puede estar conectada eléctricamente a una entrada en un siguiente dispositivo de memoria sucesivo en la pila de almacenamiento de memoria para formar un camino para transmitir datos a través de la pila. La localización de una entrada y una salida correspondiente de un dispositivo de memoria al lado del otro reduce la longitud de un enlace conductor requerida para conectar una salida de un dispositivo de memoria a una entrada correspondiente de otro dispositivo de memoria en la pila de almacenamiento de memoria.

A modo de ejemplo no limitativo, la pila de almacenamiento de memoria puede incluir dispositivos de memoria adicionales tales como, por ejemplo, un tercer dispositivo de memoria que tiene la misma disposición de configuración de entrada/salida que el primer dispositivo de memoria y el segundo dispositivo de memoria. De una manera similar que el segundo dispositivo de memoria está desplazado con respecto al primer dispositivo de memoria, el tercer dispositivo de memoria puede estar desplazado con respecto al segundo dispositivo de memoria (en la misma dirección que el segundo dispositivo de memoria está desplazado con respecto al primer dispositivo de memoria) en la pila para exponer salidas del segundo dispositivo de memoria para conectar eléctricamente a las entradas del tercer dispositivo de memoria.

La adición de cada dispositivo a la pila de almacenamiento de memoria y la conexión correspondiente extienden la conexión en serie a través de cada dispositivo de memoria en la pila como primer dispositivo de memoria, segundo dispositivo de memoria, tercer dispositivo de memoria, etc.

Estas y otras realizaciones se discutirán en más detalle más adelante en esta memoria descriptiva con referencia a las figuras correspondientes.

Como se discutió anteriormente, las técnicas de la presente memoria son muy adecuadas para su uso en el apilamiento de dispositivos y sistemas tales como los que dan soporte al uso de tecnología flash, memorias de semiconductor eléctricamente borrables, memorias no volátiles, etc. Sin embargo, cabe señalar que las realizaciones en este documento no están limitadas a su utilización en tales aplicaciones y que las técnicas discutidas en este documento son también muy adecuadas para otras aplicaciones.

Además, aunque cada una de las diferentes características, técnicas, configuraciones, etc., en este documento,

pueden ser discutidos en diferentes lugares de esta descripción, se pretende en general que cada uno de los conceptos se pueda ejecutar de forma independiente de los otro o en combinación entre ellos cuando sea factible. En consecuencia, pueden realizarse y verse, al menos algunas realizaciones de ejemplo de la invención, de muchas maneras diferentes.

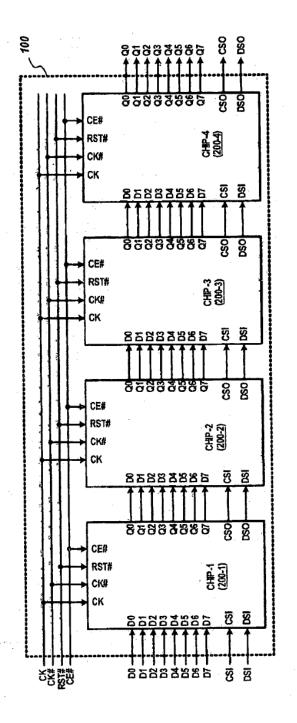

Ahora, más particularmente, la Figura 1 es un diagrama de ejemplo que ilustra un sistema de memoria 100 de acuerdo con las realizaciones en este documento.

5

20

25

30

35

50

55

60

65

Como se muestra, el sistema de almacenamiento de memoria 100 incluye cuatro chips de memoria 200 (por ejemplo, el chip de memoria 200-1, el chip de memoria200-2, el chip de memoria 200-3 y el chip de memoria200-4) conectados en serie. Tenga en cuenta que el sistema de almacenamiento de memoria 100 puede incluir cualquier número adecuado de chips de memoria y que el sistema de almacenamiento de memoria 100 incluye cuatro chips de memoria sólo a modo de ejemplo no limitativo.

15 Cada uno de los chips de memoria 200 comprende puertos serie de entrada (D0-7, CSI y DSI), puertos de salida en serie (Q0-7, CSO y DSO) y puertos de entrada comunes paralelos (CK, CK#, # RST y CE#).

Como se muestra en la Figura 1, a través de conexiones en paralelo, las señales de entrada (CK, CK#, RST# y CE#) suelen ir unidas a los respectivos puertos de entrada de los cuatro chips de memoria 200-1, 200-2, 200-3 y 200-4. Es decir, la señal CK alimenta la entrada CK respectiva de cada chip de memoria 200, la señal CK# alimenta la entrada respectiva CK de cada chip de memoria 200, y así sucesivamente.

En una realización, la señal CK representa una señal de reloj que conmuta entre los estados lógicos alto y bajo. La señal CK# conmuta también entre los estados lógicos alto y bajo, 180 grados fuera de fase con respecto a la señal CK. Por ejemplo, cuando la señal CK está en un nivel lógico alto, la señal CK# está en un nivel lógico bajo. Cuando la señal CK\* está en un nivel lógico bajo, la señal CK# es un nivel lógico alto.

Tenga en cuenta que las señales a lo largo de un borde izquierdo (por ejemplo, la señal CK, CK#, RST#, CE#, D0, D1,..., D7, CSI, DSI) de sistema de almacenamiento de memoria 100 pueden ser entradas de una fuente tal como, por ejemplo, un controlador de memoria. Las señales a lo largo de un borde derecho (por ejemplo, la señal Q0, Q1, Q2,..., Q7, OSC, DSO) del sistema de almacenamiento de memoria 100 pueden ser salidas de vuelta al controlador de memoria o pueden ser salidas conectadas a las entradas de otra sistema sucesivo de almacenamiento de memoria 100. En ciertas realizaciones, tenga en cuenta que un sistema de almacenamiento más grande puede incluir varios sistemas de almacenamiento, en donde uno o más controladores múltiples permiten el acceso a los datos almacenados en los respectivos chips de memoria.

Cada chip puede incluir potencia, conexión a tierra y otra conectividad para un funcionamiento apropiado.

Los chips 200 del sistema de almacenamiento de memoria 100 pueden conectarse en serie. Por ejemplo, las señales de entrada serie externas (mostradas como señales D0-D7, CSI, y DSI a la izquierda del chip de memoria 200-1) para el sistema de almacenamiento de memoria 100 están acoplados a los puertos de entrada en serie (D0-D7, CSI y DSI) del primer chip de memoria 200-1, tal y como se muestra. Además, los puertos de salida en serie (Q0-Q7, OSC y DSO) del primer chip de memoria 200-1 están acoplados a los puertos de entrada en serie (D0-D7, CSI y DSI) del segundo chip de memoria 200-2. Del mismo modo, los puertos de salida en serie (Q0-Q7, CSO y DSO) del segundo chip de memoria 200-2 están acoplados a los puertos de entrada en serie (D0-D7, CSI y DSI) del tercer chip de memoria 200-3. Además, los puertos de salida en serie (Q0-Q7, OSC y DSO) del tercer chip de memoria 200-4. Por último, los puertos de salida en serie (Q0-Q7, OSC y DSO) del cuarto chip de memoria 200-4 están acoplados a las señales de salida en serie (Q0-7, OSC y DSO) del sistema de almacenamiento de memoria 100.

Más detalles de los chips de memoria 200 y las interconexiones entre los chips de memoria 200 (y otros componentes de un sistema asociado) se proporcionan en un número de las anteriormente referenciadas, de propiedad común, solicitudes de patente como se indicó anteriormente, sin embargo, se entenderá que, en al menos algunos ejemplos, los chips de memoria 200 pueden ser cualquier tipo adecuado de chips semiconductores. A modo de un ejemplo no limitativo de los chips de memoria 200 pueden ser NAND de memoria flash, memoria Flash NOR, EEPROM, MRAM, PCM, ReRAM, FeRAM, SRAM, DRAM y PSRAM, etc.

Tenga en cuenta que el uso de chips no de memoria o de circuitos integrados también se contempla de acuerdo con al menos algunas realizaciones en este documento. Por ejemplo, los principios que se describen en este documento pueden ser extendidos para proporcionar conectividad con respecto al tipo de circuitos no de memoria, así como los circuitos basados en memoria mostrados en la Figura 1.

Como se mencionó anteriormente, tenga en cuenta de nuevo que a pesar de que se muestran cuatro chips de memoria 200 en el ejemplo ilustrado, el número de chips en el interior del sistema de almacenamiento de memoria 100 puede ser cualquier número que sea mayor que uno y en algunos ejemplos adicionales puede haber uno o más chips controladores de memoria funcionando como receptor, que puede proporcionar una configuración SiP

(Sistema Empaquetado).

10

30

35

40

45

La Figura 2 es un diagrama de ejemplo de 3 dimensiones de una disposición de configuración de las entradas y salidas en la proximidad de los bordes de un chip respectivo 200 de acuerdo con las realizaciones en este documento. El ejemplo de chip 200 como se muestra en la Figura 2 puede incluir la funcionalidad apropiada asociada con cada uno de los cuatro chips de memoria 200 en la Figura 1. Las patillas que se muestran en el chip de memoria 200, que puede ser un chip semiconductor, son patillas de superficie que representan las respectivas entradas/salidas, tal y como está etiquetadas. Las patillas se conectan eléctricamente a los circuitos internos de memoria, circuitos de control, circuitos de almacenamiento en búfer, etc., asociados con el chip 200. Como se ha discutido en esta memoria descriptiva, las patillas también proporcionan conectividad a circuitería externa. En consecuencia, las patillas del chip 200 proporcionan una manera de conectar los circuitos internos del chip 200 a otra circuitería externa.

A modo de un ejemplo no limitativo, el diseño de la configuración del chip semiconductor 200 puede incluir una columna incluyendo entradas y una columna incluyendo salidas. Las columnas pueden ser paralelas entre sí y estar dispuestas a lo largo o en la proximidad de los bordes respectivos del chip semiconductor.

En otras realizaciones, el chip incluye columnas de entrada/salidas en cualquiera o en todos los bordes del chip 200.

Cada entrada en una columna está emparejada con una salida correspondiente en la columna opuesta. Por ejemplo, la entrada D0 se empareja con la salida Q0 del chip 200; la entrada D1 se empareja con la salida Q1 del chip 200, la entrada D2 se empareja con la salida Q2 del chip 200; la entrada D3 se empareja con la salida Q3 del chip 200, la entrada D4 se empareja con salida Q4 del chip 200, la entrada CSI se empareja con la salida CSO del chip 200, la entrada D5I se empareja con la salida D5O del chip 200, la entrada D4 está conectada a la salida Q4 del chip 200, la entrada D5 está emparejada con la salida Q5 del chip 200, la entrada D6 se empareja con la salida Q6 del chip 200, la entrada D7 está emparejada con salida Q7 del chip 200.

En el desarrollo de dicha realización, las combinaciones de entrada y salida pueden incluir caminos de circuito en el chip 200 entre las parejas de entradas y salidas. Obsérvese de nuevo que las ilustraciones de la Figura 2, que muestra las entradas en una columna y las salidas en otra columna del chip 200 son sólo a modo de ejemplo y que cada columna puede incluir tanto entradas como salidas.

El chip semiconductor 200 incluye memoria para almacenar datos. Cada uno de los respectivos caminos de circuito de entrada-salida permite el acceso a una parte correspondiente de la memoria.

En el lado izquierdo del chip 200, las patillas de entrada en serie o las patillas de superficie en el grupo 200A (incluyendo 200A-1, 2-200A, 200A-3,..., 200A-10) y las patillas de entrada en paralelo en el grupo 200C (200C-1, 2-200C, 200C-3,... 200C-6) están situadas en la columna de la izquierda de la disposición de configuración, tal y como se muestra.

Las patillas de entrada de datos, D0 a D3 y D4 a D7 están situadas, respectivamente, en los extremos próximos de la columna de patillas en el lado izquierdo de acuerdo con un orden inicial seleccionado D0, D1, D2, etc., a lo largo del borde de los chips 200, mientras la patilla de entrada de impulsos de comando (CSI) y la entrada de impulsos de datos (DSI) se encuentran en el centro de la columna de la izquierda entre los chips D3 y D4.

Las patillas de entrada en paralelo (200C-1, 2-200C, 200C-3,... 200C-6) permiten introducir diversas señales (CK, CK#, RST# y CE#) de entrada en el chip 200.

En el lado derecho del chip de memoria 200, las patillas de salida en serie 200B (200B-1, 200B-2, 200B-3,..., 200B-50 10) están dispuestas en orden inverso u opuesto con respecto a la ordenación inicial asociada con entradas D0 hasta D7 (es decir, el orden de las patillas de entrada en serie en el lado izquierdo del chip). Por ejemplo, la entrada D0 reside en una parte superior de la columna de la izquierda del chip 200 mientras que la salida correspondiente Q0 reside en una parte inferior de la columna de la derecha del chip 200, por lo tanto la entrada D0 está al otro lado de la salida Q0 en la disposición de configuración del chip 200. La entrada D1 reside en una segunda posición de la columna de la izquierda del chip 200, mientras que la correspondiente salida Q1 reside entra las segunda y última posición en la columna de la derecha del chip 200, por lo que la entrada D1 está al otro lado de la salida Q1 en la disposición de configuración del chip 200. De una manera similar, cada uno de los pares está uno frente al otro en la disposición de configuración del chip 200.

Cada uno de los ejes entre los pares de entradas y salidas correspondientes puede cruzarse entre sí en la disposición de configuración del chip 200. Por ejemplo, el eje entre la entrada Q0 y la salida D0 cruza cada uno de los ejes D1-D2-Q1, Q2, Q3-D3, CSI-OSC, DSI-DSO, D4-Q4, Q5-D5, D6-Q6, Q7-D7, el eje entre la entrada D1 y la salida Q1 atraviesa cada uno de los ejes D0-Q0, D2-Q2, Q3-D3, CSI-CSO, DSI-DSO, D4-Q4, Q5-D5, D6-Q6, Q7-D7, el eje entre la entrada D2 y la salida Q2 atraviesa cada uno de los ejes D0-Q0, Q1, D1-D3-Q3, CSI-CSO, DSI-DSO, D4-Q4, Q5-D5, D6-Q6, Q7-D7, el eje entre la entrada D3 y la salida Q3 atraviesa cada uno de los ejes D0-Q0, Q1 D1, D2-Q2, CSI-CSO, DSI-DSO, D4-Q4, Q5-D5, D6-Q6, Q7-D7, el eje entre la entrada CSI y la salida CSO

atraviesa cada uno de los ejes D0-Q0, Q1, D1-D2-Q2, D3-D3, DSI-DSO, D4-Q4, D4-Q4, Q5-D5, D6-Q6, Q7-D7, y así sucesivamente.

Por lo tanto, de acuerdo con realizaciones en este documento, el chip 200 puede incluir una disposición de entrada/salida en la que un camino de circuito de entrada-salida respectivo entre cada uno de los pares de entrada-salida está orientado de tal forma que cruza otros caminos respectivos de circuito de entrada-salida en el (semiconductor) chip 200.

5

30

35

40

45

50

55

60

65

El chip 200 incluye circuitería correspondiente, tal como un camino de circuito, la memoria correspondiente, la lógica de control, etc., entre cada par. Por ejemplo, el chip 200 incluye un camino de circuito respectivo entre el par de entrada-salida D0 y Q0; el chip 200 incluye un camino de circuito respectivo entre el par de entrada-salida D1 y Q1, el chip 200 incluye un camino de circuito entre el par de entrada-salida D2 y Q2; el chip 200 incluye un camino de circuito entre el par de entrada-salida D3 y Q3, y así sucesivamente.

15 El diseño de pares de entrada-salida se ha elegido de tal manera que la rotación del chip 200 con respecto a otro chip (que tiene la misma disposición de configuración de entrada/salida) provoca la alineación de las salidas de un chip de memoria con las entradas de otro chip de memoria.

Para el ejemplo de disposición de adaptador de conexión ilustrado (por ejemplo, disposición de configuración de entrada/salida), como se mencionó anteriormente, la patilla de salida de datos Q0 (200B-1) del primer chip 200-1 en la Figura 1 se empareja con la patilla de entrada de datos D0 (200A-1) del segundo chip 200-2 de la Figura 1. Del mismo modo, el resto de los datos de entrada y las patillas de salida (D1-7 y Q1-7), las patillas CSI y CSO y las patillas DSI y DSO para cada chip se interconectan en serie con el orden apropiado, como se indica en la Figura 1 cuando se crea una pila respectiva y se muestra más particularmente en las figuras subsiguientes.

Con el fin de lograr la anterior interconectividad en serie entre las salidas correspondientes de un dispositivo de memoria a un dispositivo de memoria sucesivo como se discutió anteriormente, las patillas de salida en serie del chip pueden estar situadas en el lado derecho del chip con posiciones ordenadas de forma inversa respecto a las ubicaciones de las patillas de entrada del lado izquierdo como se ha discutido anteriormente. Por ejemplo, la patilla Q0 se encuentra en la esquina inferior derecha del chip y la patilla Q7 se encuentra en la esquina superior derecha del chip, como se muestra en el ejemplo de la Figura 2.

Como se ilustra en las figuras subsiguientes, la disposición de patillas invertida y reflejada en las respectivas columnas de patillas de entrada/salida del chip 200, tal y como se muestra en la Figura 2, puede proporcionar soluciones de unión por hilo sencilla, más corta y eficaz cuando varios chips se apilan verticalmente y se conectan en serie. Sin embargo, tenga en cuenta que el número de entradas de datos y las patillas de salida no está limitado, por lo que los modos xl I/O, x2, x4, x16 I/O pueden implementarse de acuerdo con realizaciones ejemplares.

También, se entenderá que las realizaciones no están limitadas por el orden de las patillas de entrada y las patillas de salida.

Además, se entenderá que las patillas de entrada en paralelo pueden estar duplicadas en el lado derecho del chip con el fin de proporcionar una señalización más robusta. Además, las patillas de suministro de energía y otras patillas diversas típicamente necesarias no han sido mostradas, a fin de no oscurecer la materia objeto de las realizaciones de ejemplo, tal y como se describe en este documento.

De acuerdo con realizaciones, tal y como se discutió anteriormente, el chip (semiconductor) chip 200 incluye una disposición de configuración que incluye múltiples entradas y múltiples salidas para la transmisión de datos a través del chip semiconductor. En una realización, el chip semiconductor 200 también incluye pares de entrada-salida en el que las entradas en la disposición de configuración están emparejadas diagonalmente con las múltiples salidas en la disposición de configuración. El chip 200 incluye un camino de circuito de entrada-salida respectivo entre cada uno de los pares de entrada-salida. Las ramificaciones de un circuito a través del chip semiconductor pueden soportar diferentes funciones, tales como, por ejemplo, medio de transporte de datos o señales de control a través del chip semiconductor.

La disposición de la configuración del chip semiconductor puede incluir la ordenación de las múltiples entradas y múltiples salidas. Cada uno de los respectivos caminos de circuito entre los pares de entrada-salida en la disposición incluye una entrada y una salida correspondiente. La salida correspondiente está en diagonal a través de la entrada en el diseño.

En una realización, la salida correspondiente en la disposición está desplazada 180 grados con respecto a la entrada en la disposición. Por ejemplo, la salida Q0 del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada D0; salida Q1 del chip 200 se encuentran en diagonal en una posición desplazada 180 grados respecto a la entrada D1; la salida Q2 del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada D2; la salida Q3 del chip 200 se encuentran diagonal en una posición desplazada 180 grados respecto a la entrada D3; la salida OSC del chip 200 se encuentra en diagonal en una

posición desplazada 180 grados respecto a la entrada CSI; ..., y la salida de DSO del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada DSI, y la salida Q4 del chip 200 se encuentra en diagonal desplazada 180 grados respecto a la entrada D4, y la salida Q5 del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada D5; la salida Q6 del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada D6, y la salida Q7 del chip 200 se encuentra en diagonal en una posición desplazada 180 grados respecto a la entrada D7.

La Figura 3 es un diagrama de ejemplo que ilustra varios chips que forman una respectiva pila de almacenamiento de memoria de acuerdo con las realizaciones en este documento.

10

15

20

25

El chip superior 202 se coloca en la parte superior de la parte inferior del chip 201. El chip superior 202 se hace girar 180 grados con respecto a la parte inferior del chip 201 de modo que las salidas en el chip 201 están expuestas para conectarse a las entradas del chip 202. El chip 202 está desplazado con respecto al chip 201 en la pila con el fin de exponer las patillas del chip 201. El desplazamiento permite que las patillas de entrada en serie202A del chip superior 202 se coloque cerca de las patillas de salida en serie 201B de la parte inferior del chip 201.

A modo de un ejemplo no limitativo, la rotación de 180 ° y la posición de desplazamiento del segundo chip 202 permite a las patillas de salida del primer chip 201 estar expuestas y permite un proceso de unión por hilo más fácil entre las dos correspondientes entrada en serie e interconexiones de salida, como Q0 hasta D0, Q1 hasta D1, Q2 hasta Q3, etc.

Continuando con el ejemplo de realización en la Figura 3, el enlace 311 tal como, por ejemplo, una unión por hilo que interconecta la patilla Q7 del chip 201 y la patilla D7 del chip 202 de tal manera que el enlace 311 es de una longitud relativamente corta. Esto reduce la resistencia parásita, la capacitancia y la inductancia asociada con el enlace.

De una manera similar al enlace 311, todas las otras patillas de salida en serie del primer chip 201 se pueden interconectar a las respectivas patillas de entrada en serie del chip 202 en la pila.

30 El chip 201 puede estar asegurado al sustrato 300. En el ejemplo de la realización, las patillas de entrada en paralelo, CE#, CK, VSS, VCC, CK# y RST#, del segundo chip 202 están acopladas a las áreas de unión de metalización conductora o trazas conductoras 300D del sustrato 300 por medio de los enlaces 313, tales como, por ejemplo, los hilos de conexión. Por lo tanto, el sistema de almacenamiento de memoria 100 de acuerdo con realizaciones en este documento puede incluir la conectividad entre el sustrato 300 y la pila de la memoria de los chips 201, 202, etc.

La pila de chips conectados en serie 201 y 202 puede estar unida físicamente al sustrato 300, en donde el sustrato puede comprender, por ejemplo, una placa de circuito impreso (PCB), una tarjeta de memoria, un bastidor de conductores, una unión automatizada de cinta (TAB) u otro tipo de sustrato.

40

Como se mencionó anteriormente, el ejemplo no limitativo en la Figura 2 incluye dos chips de la pila respectiva. Las patillas de salida en serie 202B del segundo chip de memoria 202 se conectan a las patillas correspondientes o trazas 300B del sustrato 300 a través de enlaces tales como, por ejemplo, uniones por hilo.

45 Además, los enlaces 310 conectan las patillas de entrada en serie 201A del primer chip 201 y las áreas de unión de metalización conductoras 300A del sustrato 300.

Las áreas de unión de metalización conductoras adicionales o trazas conductoras 300C y 300D pueden estar situadas en la superficie del sustrato 300. Tales áreas de unión se pueden proporcionar en los lados izquierdo y derecho de la pila con el fin de conectar las señales de entrada comunes y fuentes de alimentación (tales como RST#, CK#, VCC, VSS CK y CE#) a las patillas de unión de entrada en paralelo del primer chip 201 y del segundo chip 202, respectivamente. En otras palabras, debido a que los chips deben girarse con respecto a los otros en la pila, las patillas de unión para las señales RST#, CK#, VCC, VSS CK y CE# sobre el sustrato 300 se pueden duplicar de manera que cada chip en la pila puede estar conectado al sustrato con un enlace relativamente corto.

55

Para resumir las realizaciones de la Figura 3, el sistema de almacenamiento de memoria incluye un apilamiento de un primer dispositivo de memoria, tal como el chip 201 y un segundo dispositivo de memoria, tal como el chip 202. A modo de ejemplo no limitativo, el primer dispositivo de memoria (chip 201) y el segundo dispositivo de memoria (chip 202) tienen una misma disposición de configuración de entrada/salida.

60

65

Como se mencionó anteriormente, para formar la pila, el segundo dispositivo de memoria (chip 202) está fijado al primer dispositivo de memoria (chip 201). Para facilitar la conectividad entre las salidas del primer dispositivo de memoria (chip 201) y las entradas del segundo dispositivo de memoria (chip 202), el segundo dispositivo de memoria (chip 202) está rotacionalmente desplazada con respecto al primer dispositivo de memoria (chip 201) en el apilar para alinear salidas del primer dispositivo de memoria (chip 201) con las entradas correspondientes del segundo dispositivo de memoria. El chip 202 se puede girar alrededor de un eje a lo largo del cual los chips se

apilan unos encima de otros.

El desplazamiento rotacional del segundo dispositivo de memoria (chip 202) con respecto al primer dispositivo de memoria (chip 201) en la pila resulta en la alineación sustancial de una o más salidas del primer dispositivo de memoria (chip 201) con una o más entradas respectivas del segundo dispositivo de memoria (chip 202). La pila de dispositivos de memoria puede incluir caminos que facilitan una o más configuraciones de conexión en serie entre el primer dispositivo de memoria (chip 201) y el segundo dispositivo de memoria (chip 202).

Haciendo referencia de nuevo a la Figura 1, un primer camino lógico a través de una respectiva pila de múltiples dispositivos de memoria incluye una conexión de configuración en serie de la señal de entrada D0 del sistema de almacenamiento de memoria 100 (por ejemplo, una patilla sobre el sustrato 300) a la patilla de entrada asociada con D0 del chip 200-1. El camino lógico en el chip continúa extendiéndose a través de un camino del circuito de la patilla D0 del chip 200-1 a una patilla de salida Q0 del chip 200-1, a través de un enlace físico que conecta la salida Q0 del chip 200-1 en la entrada D0 del chip 200-2, a través de un camino de circuito de la entrada D0 del chip 200-2 a una patilla Q0 de salida del chip 200-2, a través de un enlace físico que conecta la salida Q0 del chip 200-2 a la entrada D0 del chip 200-3, a través de un camino de circuito de la patilla D0 del chip 200-3 a una patilla de salida Q0 del chip 200-3, a través de un enlace físico que conecta la salida Q0 del chip 200-3 a la entrada D0 del chip 200-4, a través de un camino de circuito de la patilla D0 del chip 200-3 a la entrada D0 del chip 200-4, a través de un camino de circuito de la patilla D0 del chip 200-4 a una patilla de salida Q0 de chip 200-4, y así sucesivamente.

20

25

30

15

5

10

Un segundo camino lógico incluye una conexión de configuración en serie D1 de la señal de entrada del sistema de almacenamiento de memoria 100 a la patilla de entrada asociada D1 del chip 200-1. El segundo camino lógico continúa extendiéndose a través de un camino de circuito desde la patilla D1 del chip 200-1 hasta una patilla de salida Q1 del chip 200-1, a través de un enlace físico que conecta la salida Q1 del chip 200-1 a la entrada D1 del chip 200-2, a través de un camino de circuito desde la patilla D1 del chip 200-2 hasta una patilla de salida Q1 del chip 200-3, a través de un enlace físico que conecta la salida Q1 del chip 200-2 a la entrada D1 del chip 200-3, a través de un enlace físico que conecta la salida Q1 del chip 200-3 hasta una patilla de salida Q1 del chip 200-3, a través de un enlace físico que conecta la salida Q1 del chip 200-3 a la entrada D1 del chip 200-4, a través de un camino de circuito desde la patilla D1 del chip 200-4 hasta una patilla de salida Q1 del chip 200-4, y así sucesivamente. De una manera similar, el sistema de almacenamiento de memoria 100 incluye caminos lógicos para cada una de las señales D0..D7, CSI y DS1.

Estas configuraciones de conexión en serie a través de un apilamiento de dispositivos de memoria se discutirán con más detalle a lo largo de esta especificación.

35

40

Haciendo referencia de nuevo a la Figura 3, las realizaciones en este documento son útiles sobre los procedimientos convencionales porque el desplazamiento rotacional de los dispositivos de memoria (por ejemplo, alrededor de 180 grados) para alinear las entradas de un chip a las salidas de un chip sucesivas en la pila permite la creación de una pila de almacenamiento de memoria utilizando dispositivos de memoria que tienen una disposición de configuración común de entrada /salida. Esto alivia la necesidad de dispositivos de memoria de valores que tienen diferentes diseños de configuración de entrada/salida para crear una pila de memoria.

45

El sistema de almacenamiento de memoria de acuerdo con realizaciones en este documento puede incluir un controlador. Tenga en cuenta que un controlador puede estar acoplado a la pila de un número de maneras. Por ejemplo, tanto un controlador como la pila de chips se pueden unir al sustrato 300 tal como, por ejemplo, una placa de circuito impreso. En tal realización, los caminos conductores en el sustrato 300 proporcionan conectividad entre el controlador y la pila de dispositivos de memoria.

50

De acuerdo con otra realización, ha de tenerse en cuenta que la pila de fichas en sí misma puede incluir el controlador. En dicha realización, el controlador puede estar fijado a un dispositivo de memoria en la pila.

55

Como se ilustra en la Figura 3, la pila puede estar fijada al sustrato 300. El sustrato puede configurarse para conectarse a una placa de circuito impreso a través de juntas de soldadura. Por ejemplo, en una realización, el sustrato 300 es un paquete de matriz de malla de bolas y por lo tanto incluye bolas de soldadura para conectar el conjunto de pila a una placa de circuito impreso respectiva.

En otras realizaciones de ejemplo, el sustrato 300 es un paquete del tipo matriz de malla de pines y por lo tanto incluye las patillas de un lado inferior del sustrato 300 para conectar el conjunto de pila de una placa de circuito respectiva.

60

65

Tal y como se discutió previamente, cada chip en la pila puede tener la misma disposición de configuración de entrada/salida. Por lo tanto, un chip puede ser sustituido por otro. Cada chip incluye contactos de entrada y contactos de salida, tales como, por ejemplo, patillas de superficie en un solo plano (por ejemplo, plano superior) del chip de memoria respectivo. Otras realizaciones pueden incluir patillas situadas en ambas caras superior e inferior del chip de memoria.

A modo de ejemplo no limitativo, los dispositivos de memoria o chips en la pila pueden ser de forma plana y tener respectiva partes superior e inferior. La parte superior incluye patillas de superficie de entrada y patillas de superficie de salida que da soporte a la conectividad fuera del chip. Los dispositivos de memoria pueden ser chips semiconductores cortados a partir de uno o más obleas.

5

En un ejemplo de realización, los dispositivos de memoria se apilan los unos encima de otros, donde una parte inferior respectiva frente a un dispositivo de memoria en la pila está fijada a una parte superior frente a otro dispositivo de memoria en la pila de tal manera que la parte superior enfrentada del primer dispositivo de memoria y la parte superior del segundo dispositivo de memoria en una misma dirección a lo largo de la pila.

10

Como se discutió previamente, la pila incluye una o más conexiones de configuración de serie o caminos de acceso en base a las conexiones entre los contactos de entrada/salida. Por ejemplo, los uno o más caminos se pueden crear sobre la base de enlaces conductores entre los contactos de salida, tales como las señales Q0 ...Q7, CSO y DSO de un dispositivo de memoria en la pila con los contactos de entrada correspondientes como D0..D7, CSI, y DSI de un dispositivo de memoria sucesivo en la pila.

15

Los uno o más caminos de acceso están adaptados para soportar transmisión de datos a través de la pila. Un controlador está acoplado eléctricamente a la pila para acceder a datos almacenados en la pila. El controlador está acoplado al primer dispositivo de memoria (chip 201) en la pila. Aunque, en otras realizaciones, el controlador puede residir en cualquier posición en la pila o externa a la pila.

20

El controlador está configurado para acceder a los datos del primer dispositivo de memoria (chip 201) en base a un flujo de datos a lo largo del camino desde el primer dispositivo de memoria (chip 201) a través del segundo dispositivo de memoria (chip 202), así como otros dispositivos de memoria en la pila de nuevo al controlador. Una conexión entre un último dispositivo de memoria en la pila de nuevo al controlador permite que al controlador recibir datos desde los dispositivos de memoria en la pila en base a un flujo de datos a lo largo de los uno o más caminos.

25

El acoplamiento entre el controlador y el primer dispositivo de memoria (chip 201) en la pila permite que al controlador transmitir datos a través de los dispositivos de memoria y por lo tanto almacenar datos en los dispositivos de memoria. El acoplamiento entre el último dispositivo de memoria en la pila de nuevo al controlador permite que al controlador recuperar los datos almacenados en los dispositivos de memoria respectivos.

30

Cada dispositivo de memoria (chip 200) en la pila puede ajustarse a un modo de paso directo o un modo de acceso a memoria. El modo de paso permite a un dispositivo de memoria respectivo (chip 200) en la pila transmitir los datos recibidos en una entrada del dispositivo de memoria respectivo a lo largo de un camino de circuito a una salida del dispositivo de memoria respectivo. Por lo tanto, el controlador puede hacer que los datos pasen a través de uno o más dispositivos de memoria en la pila para su almacenamiento en un dispositivo de memoria de destino en la pila.

35

El modo de acceso a memoria permite i) recibir datos en el camino y almacenar los datos en los circuitos de memoria asociados con un dispositivo de memoria correspondiente en la pila, y ii) recuperar datos de los circuitos de memoria en el dispositivo de memoria respectivo para su transmisión en el camino a una salida del respectivo dispositivo de memoria de vuelta al controlador. Por lo tanto, el controlador puede hacer que los datos se almacenen o recuperen de un dispositivo de memoria en particular en la pila.

40

45

Más detalles de ejemplo de posibles operaciones de acceso (tales como, por ejemplo, almacenar y recuperar datos) asociados con el sistema de almacenamiento de memoria 100 se discuten en, por ejemplo, las siguientes solicitudes de patente de propiedad común: Solicitud PCT No. WO 2007/036047 A1 titulada "MULTIPLE INDEPENDENT SERIAL LINK MEMORY" Solicitud PCT No. WO 2007/036048 A1 titulada "DAISY CHAIN CASCADING DEVICES", y la solicitud PCT No. PCT/CA2008/001756 titulada "SEMICONDUCTOR MEMORY DEVICE SUITABLE FOR INTERCONNECTION IN A RING TOPOLOGY". Las realizaciones en este documento permiten tales operaciones con respecto a una pila de almacenamiento de memoria.

55

50

Cada uno de los uno o más caminos a través de la pila puede incluir segmentos del camino a través de los dispositivos de memoria. Por ejemplo, como se muestra en la Figura 3, un camino de configuración en serie, tales como, por ejemplo, la asociada con la señal D0 incluye un segmento de camino 5 325-1 y un segmento de camino 325-2.

El segmento de camino 325-1 reside en el chip 201 e incluye un camino de circuito respectivo entre la entrada D0 y la salida Q0 del chip 201. El segmento de camino 325-2 reside en el chip 202 e incluye un camino de circuito entre la entrada D0 y la salida Q0 del chip 202.

60

En base al desplazamiento del chip 202 con respecto al chip 201 en el apilamiento, un eje entre la entrada D0 y la salida Q0 del chip 201 en la pila es sustancialmente paralelo a un eje entre la entrada D0 y la salida Q0 de chip 202 en la pila.

65

Además, en base a una orientación de chip 202 con respecto al chip 201 en la pila, una dirección del flujo de datos