# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 440 491

51 Int. Cl.:

**H03M 9/00** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

96 Fecha de presentación y número de la solicitud europea: 02.08.2007 E 07813729 (6)

(97) Fecha y número de publicación de la concesión europea: 20.11.2013 EP 2055008

(54) Título: Codificador serie con doble tasa de trasmisión de datos con leve desalineación de salida

(30) Prioridad:

08.08.2006 US 463129

Fecha de publicación y mención en BOPI de la traducción de la patente: 29.01.2014

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) ATTN: INTERNATIONAL IP ADMINISTRATION 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121, US

(72) Inventor/es:

MUSFELDT, CURTIS D.

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

## **DESCRIPCIÓN**

Codificador serie con doble tasa de trasmisión de datos con leve desalineación de salida

#### Referencia cruzada a solicitudes relacionadas

La presente solicitud reivindica prioridad respecto de la Solicitud No. 11/285,397 titulada "Codificador serie con doble tasa de transmisión de datos" ["Double Data Rate Serial Encoder"] depositada el 23 de noviembre de 2005, que reivindica prioridad respecto de la Solicitud Provisional No. 60/630,853 titulada "Diseño de Núcleo Anfitrión de MDDI" ["MDDI Host Core Design"] depositada el 24 de noviembre de 2004, Solicitud Provisional No. 6/631,549 titulada "Dispositivo Móvil de Interfaz de Cámara Anfitrión de Interfaz Digital de Representación" ["Mobile Display Digital Interface Host Camera Interface Device"] depositada el 30 de noviembre de 2004, Solicitud Provisional No. 60/362,825 titulada "Dispositivo de Cámara Anfitrión de MDDI" ["Camera MDDI Host Device"] depositada el 2 de diciembre de 2004, Solicitud Provisional No. 60/633,701 titulada "Panorámica de MDDI" ["MDDI Overview"] depositada el 2 de diciembre de 2004, Solicitud Provisional No. 60/633,084 titulada "Diseño de Tableta de Núcleo Anfitrión de MDDI" ["MDDI Host Core Pad Design"] depositada el 2 de diciembre de 2004 y Solicitud Provisional No. 60/622,852 titulada "Implementación del Controlador Anfitrión de MDDI" ["Implementation of the MDDI Host Controller"] depositada el 2 de diciembre de 2004.

La presente solicitud está también relacionada con la Patente estadounidense No. 6,760,772 B2, transferida legalmente, titulada "Generación e Implementación de un Protocolo y de una Interfaz de Comunicación para la Transferencia de Datos de Alta Velocidad", publicada el 6 de julio de 2004.

## **Antecedentes**

#### 20 Campo

30

35

40

45

50

La presente invención se refiere, en general, a un codificador serie para enlaces de comunicación serie con tasa de transmisión de datos elevada. Más en concreto, la invención se refiere a un codificador serie de doble tasa de transmisión de datos para enlaces de Interfaz Digital de Representación Móvil (MDDI).

#### **Antecedentes**

En el campo de las tecnologías de interconexión, continúa en auge la demanda de tasas de transmisión de datos en constante aumento, especialmente por lo que se refiere a las presentaciones de vídeo.

La Interfaz Digital de Representación Móvil (MDDI) es un mecanismo de transferencia con un consumo de energía reducido y rentable que hace posible la transferencia de datos a gran velocidad a través de un enlace de comunicación de corto alcance entre un anfitrión y un cliente. La MDDI requiere un mínimo de exactamente cuatro cables más la energía para la transferencia de datos bidireccionales que proporcione un máximo ancho de banda de hasta 3.2 Gbits por segundo.

En una aplicación, la MDDI incrementa la fiabilidad y reduce el consumo de energía en teléfonos de tapa abatible ("clamsel") mediante la reducción significativa del número de cables que discurren a través de una articulación del aparato telefónico para interconectar el controlador en banda base digital con una pantalla de LCD y / o una cámara. Esta reducción de cables permite también que los fabricantes de los aparatos telefónicos reduzcan los costes de desarrollo mediante la simplificación del teléfono de tapa abatible y mediante diseños de aparatos telefónicos de tapa deslizante.

La MDDI es un protocolo de transferencia serie y, en cuanto tal, los datos recibidos en paralelo para la transmisión a través de un enlace de MDDI necesitan ser serializados. La Solicitud de Patente estadounidense No. 11/285,397, titulada "Codificador Serie con Doble Tasa de Transmisión de Datos" ["Double Data Rate Serial Encoder"], depositada el 23 de noviembre de 2005 describe un codificador serie con Doble Tasa de Transmisión de Datos (DDR) de MDDI que incorpora una salida sin perturbaciones de baja frecuencia. El codificador serie de salida sin perturbaciones de baja frecuencia cuenta con la ventaja de un multiplexador sin perturbaciones de baja frecuencia, diseñado con un conocimiento a priori de una secuencia de selección de entrada de código Gray. Este conocimiento a priori de la secuencia de selección de entrada permite una reducción del tamaño del multiplexador y, en consecuencia, del codificador serie con DDR.

Sin embargo, pueden llevarse a cabo mejoras en diversos aspectos del diseño del codificador serie con DDR descrito en la Solicitud estadounidense No. 11/285,397. En un aspecto, se destaca que el multiplexador sin perturbaciones de baja frecuencia utilizado en el codificador serie con DDR descrito en la Solicitud estadounidense No. 11/285,397 sigue siendo de mayor tamaño que un multiplexador que no sea de no perturbaciones de baja frecuencia. En otro aspecto de capas lógicas entre la etapa de registro final y la salida del codificador, un factor que contribuye a una mayor asincronía de salida y a una menor tasa de transmisión de enlaces, puede ser considerablemente reducido.

Por tanto, lo que se necesita es un codificador serie con DDR de MDDI que ofrezca un tamaño, una complejidad y

una desalineación de salida reducidas. Así mismo, se necesita que el codificador serie con DDR de MDDI ofrezca una salida sin perturbaciones de baja intensidad.

#### Breve sumario de la invención

En la presente memoria se proporciona un codificador serie con Doble Tasa de Transmisión de Datos (DDR).

- En un aspecto, el codificador serie con DDR incluye un multiplexador no sin perturbaciones de baja frecuencia y una lógica digital para asegurar una salida del codificador exenta de perturbaciones de baja frecuencia, mediante la utilización de un multiplexador no sin perturbaciones de baja frecuencia, se reduce de manera considerable el tamaño y la complejidad del codificador.

- En otro aspecto, el codificador serie con DDR presenta una sola capa lógica entre la etapa de registro final y la salida del codificador y un número reducido de trayectorias desde la etapa de registro final hasta la salida del codificador, lo que se traduce en una desalineación de salida reducida y en una tasa de transmisión de enlaces incrementada. El número reducido de trayectorias desde la etapa de registro final hasta la salida del codificador simplifica también el análisis de la asimetria de salida.

- Otras formas de realización, características distintivas y ventajas de la presente invención, así como la estructura y operación de las diversas formas de realización de la presente invención se describen con detalle en las líneas que siguen con referencia a los dibujos que se acompañan.

## Breve descripción de los dibujos

20

30

Los dibujos que se acompañan, los cuales se incorporan en la presente memoria y forman parte de la memoria descriptiva, ilustran la presente invención y, junto con la descripción, sirven también para exponer los principios de la invención y para hacer posible que una persona experta en la materia haga uso de la invención.

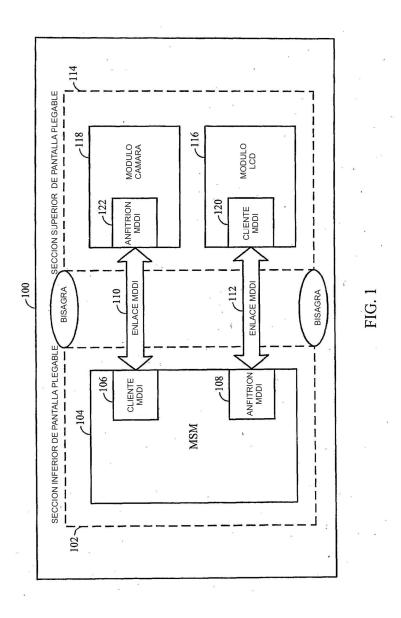

La FIG. 1 es un diagrama de bloques que ilustra un entorno ejemplar que utiliza una interfaz de la Interfaz Digital de Representación Móvil (MDDI).

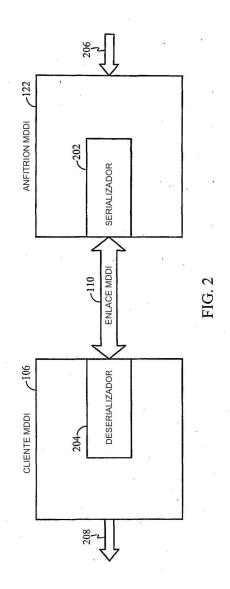

La FIG. 2 es un diagrama de bloques que ilustra una interconexión de enlace de MDDI de acuerdo con una forma de realización del ejemplo de la FIG. 1.

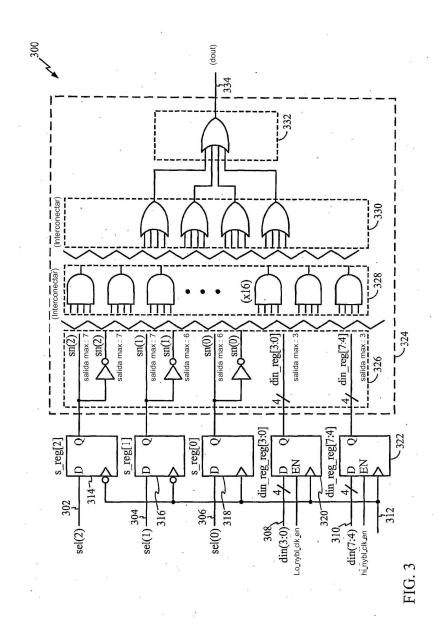

25 La FIG. 3 es un diagrama de circuito que ilustra un codificador serie de MDDI.

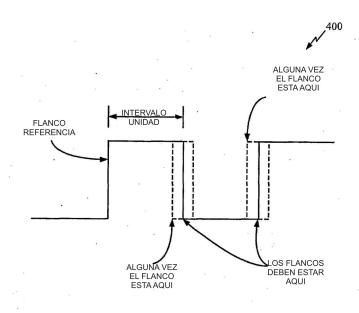

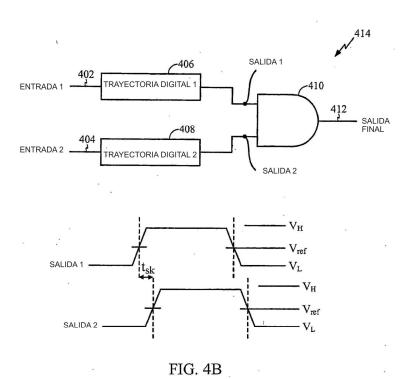

Las FIGs. 4A – B ilustran ejemplos de una desalineación.

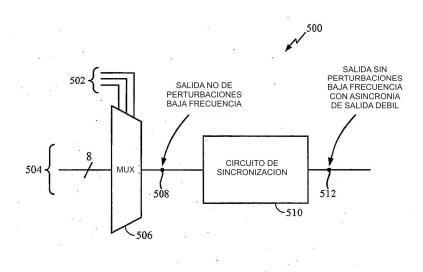

La FIG. 5 es un diagrama de bloques que ilustra un codificador serie de MDDI de acuerdo con una forma de realización de la presente invención.

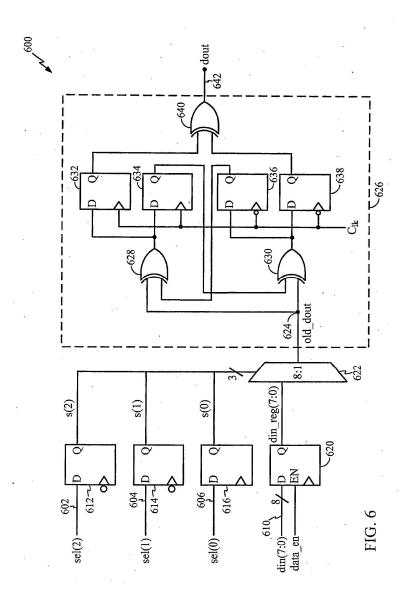

La FIG. 6 es un diagrama de circuito que ilustra un codificador serie de MDDI de acuerdo con otra forma de realización de la presente invención.

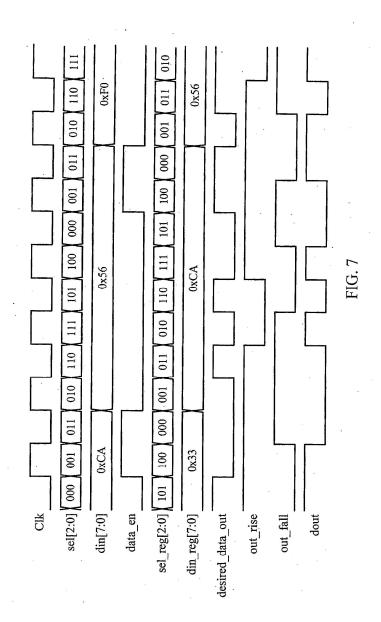

La FIG. 7 es un diagrama de temporización ejemplar que se refiere a unas señales del codificador serie de MDDI de la FIG. 6.

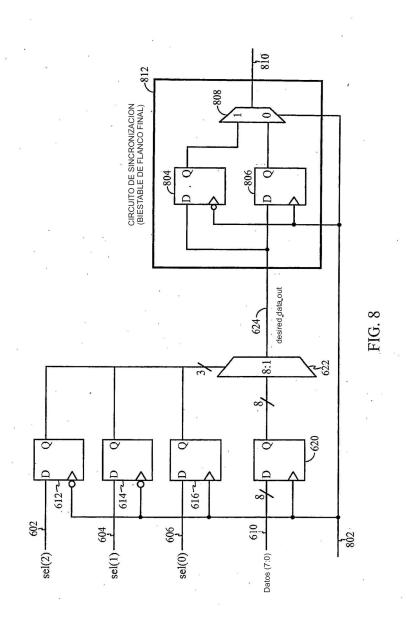

La FIG. 8 es un diagrama de circuito que ilustra un codificador serie de MDDI de acuerdo con una forma de realización adicional de la presente invención.

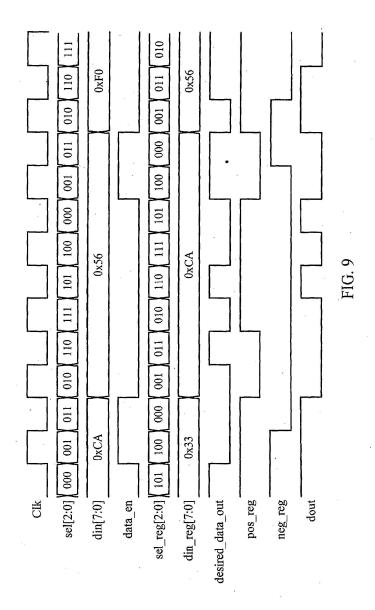

La FIG. 9 es un diagrama de temporización ejemplar que se refiere a las señales del codificador serie de MDDI de la FIG. 8

La presente invención se describirá con referencia a los dibujos que se acompañan. El dibujo en el que un elemento aparece por primera vez se indica típicamente mediante el (los) dígito(s) de más a la izquierda en el correspondiente número de referencia.

## 40 Descripción detallada

La memoria descriptiva divulga una o más formas de realización que incorporan las características distintivas de la presente invención. La(s) forma(s) de realización divulgada(s) simplemente ejemplifican la invención. El alcance de la invención no está limitada a la(s) forma(s) de realización divulgada(s). La invención se define mediante las reivindicaciones adjuntas a ella.

La(s) forma(s) de realización descrita(s), y las referencias en la memoria descriptiva a "una forma de realización", "una forma de realización ejemplar", etc., indican que la(s) forma(s) de realización descrita(s) puede(n) incluir el elemento, estructura o característica concretas. Así mismo, dichas frases no se refieren necesariamente a la misma forma de realización. Así mismo, cuando un elemento, estructura o característica particular se describa en conexión con una forma de realización, se da por supuesto que entra dentro de los conocimientos de una persona experta en

la materia el llevar a efecto dicho elemento, estructura o característica en conexión con otras formas de realización sean o no descritas explícitamente.

Las formas de realización de la invención pueden ser implementadas en hardware, firmware, software, o en cualquier combinación de estos. Las formas de realización de la invención pueden también ser implementadas como instrucciones almacenadas en un medio legible por una máquina, las cuales pueden ser leídas o ejecutadas por uno o más procesadores. Un medio legible por máquina puede incluir cualquier mecanismo para almacenar o transmitir información de una forma legible por una máquina (por ejemplo un dispositivo informático). Por ejemplo, un medio legible por máquina puede incluir una memoria de solo lectura (ROM); una memoria de acceso aleatorio (RAM); unos medios de almacenamiento épticos; unos dispositivos de memoria Flash; formas eléctricas, ópticas, acústicas, u otras formas de señales propagadas (por ejemplo, ondas portadoras, señales de infrarrojo, señales digitales, etc.), y otras. Así mismo, el firmware, el software, las rutinas, las instrucciones pueden ser descritas en la presente memoria llevando a cabo determinadas acciones. Sin embargo, se debe apreciar que dichas descripciones se deben simplemente a razones de comodidad y que dichas acciones de hecho se derivan de dispositivos informáticos, procesadores, controladores, u otros dispositivos que ejecutan el firmware, el software, las rutinas, las instrucciones, etc.

#### Interfaz Digital de Representación Móvil (MDDI)

5

10

15

25

30

35

40

45

50

55

60

La Interfaz Digital de Representación Móvil (MDDI) es un mecanismo de transferencia rentable de reducido consumo de energía que permite la transferencia de datos serie de muy alta velocidad a través de un enlace de comunicación de corto alcance entre un anfitrión y un cliente.

A continuación, se representarán ejemplos de la MDDI con respecto a un módulo de cámara contenido en una pantalla plegable superior de un teléfono móvil. Sin embargo, debe resultar evidente para las personas expertas en la(s) materia(s) relevante(s) que cualquier módulo que incorpore características funcionalmente equivalentes al módulo de cámara puede ser fácilmente sustituido y utilizado en diversas formas de realización de la presente invención.

Así mismo, de acuerdo con formas de realización de la invención, un anfitrión de MDDI puede comprender uno entre varios tipos de dispositivos que puedan contar con el beneficio de la utilización de la presente invención. Por ejemplo, el anfitrión podría ser un ordenador portátil bajo la forma de un ordenador de mano, de falda o dispositivo informático similar. Así mismo, podría ser un Asistente Personal de Datos (PDA), un dispositivo de envío de radiomensajes o uno de los muchos teléfonos inalámbricos o módems. Como alternativa, el anfitrión podría ser un dispositivo de entretenimiento o presentación portátil, como por ejemplo un reproductor DVD o CD portátil, o un dispositivo de reproducción de juegos. Así mismo, el anfitrión puede residir como un dispositivo anfitrión o elemento de control en una diversidad de otros productos comerciales ampliamente utilizados o planeados para los cuales se desea un enlace de comunicaciones a gran velocidad con un cliente. Por ejemplo, un anfitrión podría ser utilizado para transferir datos con tasas de transmisión elevadas desde un dispositivo de registro de vídeo hasta un cliente con base en memoria para una respuesta mejorada, o hasta una pantalla de mayor tamaño de gran resolución para presentaciones. Un electrodoméstico como por ejemplo una nevera que incorpore un inventario de a bordo o un sistema informático y / o unas conexiones Bluetooth con otros dispositivos domésticos, pueden incorporar unas capacidades de representación mejoradas cuando operen en un modo conectado con Internet o Bluetooth, o que presenten unas necesidades de cableado reducidas para representaciones en la puerta (un cliente) y teclados o escáneres (cliente) mientras los sistemas de control o informáticos electrónicos (anfitrión) residen en cualquier otra parte del armario. En general, los expertos en la materia apreciarán que una amplia variedad de dispositivos y aparatos electrónicos modernos pueden beneficiarse del uso de esta interfaz, así como de la capacidad de reconvertir antiquos dispositivos con un transporte de información con una tasa de transmisión de datos más elevada utilizando el números de conductores limitados disponibles en ya sea conectores o cables añadidos recientemente o existentes. Al mismo tiempo, un cliente MDDI puede comprender una diversidad de dispositivos de utilidad para presentar información a un usuario final, o presentar información desde un usuario al anfitrión. Por ejemplo, una micropantalla incorporada en anteojos de protección o gafas, un dispositivo de proyección incorporado en un sombrero o un casco, una pequeña pantalla o incluso un elemento holográfico incorporado en un vehículo, como por ejemplo en una ventana o en un parabrisas, o diversos sistemas de altavoz, cascos o sonido para presentar sonido o música de gran calidad. Otros dispositivos de presentación incluyen proyectores o dispositivos de proyección utilizados para presentar información para reuniones, o para películas e imágenes de televisión. Otros ejemplos incluyen el uso de tabletas táctiles o dispositivos sensibles, dispositivos de entrada de reconocimiento de voz, escáneres de seguridad, etc., que pueden ser necesarios para transferir una cantidad considerable de información desde un usuario del dispositivo o del sistema con escasa "entrada" efectiva distinta de la táctil o sonora procedente del usuario. Así mismo, unas estaciones de acoplamiento para ordenadores y para equipos de coches para armar o equipos para escritorios y soportes para teléfonos inalámbricos pueden actuar como dispositivos de interfaz con los usuarios terminales o con otros dispositivos y equipamientos, y emplear o bien clientes (dispositivos de entrada o salida, como por ejemplo ratones, o anfitriones para ayudar a la transferencia de datos, especialmente cuando están implicadas redes de alta velocidad. Sin embargo, los expertos en la materia advertirán sin dificultad que la presente invención no está limitada a estos dispositivos, existiendo otros muchos dispositivos en el mercado, propuestos para su utilización, que están concebidos para proporcionar a los usuarios finales unas imágenes y sonido de alta calidad, ya sea en términos de almacenamiento y transporte o en términos de presentación en

reproducción. La presente invención es de utilidad para incrementar el volumen total de datos entre diversos elementos o dispositivos para adaptarse a las elevadas tasas de transmisión de datos requeridas para conseguir la experiencia requerida por el usuario.

La FIG. 1 es un diagrama de bloques que ilustra un entorno ejemplar que utiliza una interfaz MDDI. En el ejemplo de la FIG. 1, la MDDI es utilizada para interconectar módulos a través de la articulación de un teléfono de pantalla plegable100. Se debe destacar aquí que determinadas formas de realización de la invención se describirán en el contexto de ejemplos específicos, como por ejemplo las interconexiones MDDI en un teléfono de pantalla plegable, esto se efectúa únicamente con fines de ilustración y no debe ser utilizado para limitar la presente invención a dichas formas de realización. Como comprenderá la persona experta en la(s) materia(s) relevante(s) en base a las enseñanzas contenidas en la presente memoria, las formas de realización de la presente invención pueden ser utilizadas en otros dispositivos incluyendo cualquier dispositivo que pueda contar con la ventaja de incorporar las interconexiones MDDI.

Con referencia a la FIG. 1, una sección inferior de pantalla plegable 102 del teléfono de pantalla plegable 100 incluye chip de banda base de Módem de Estación Móvil (MSM) 104. El MSM 10 es un controlador de banda base digital. Una sección superior de la pantalla plegable 114 del teléfono de pantalla plegable 100 incluye un módulo de Pantalla de Cristal Líquido (LCD) 116 y un módulo de cámara 118.

Todavía con referencia a la FIG. 1, un enlace de MDDI 110 conecta el módulo de cámara 118 al MSM 104. Típicamente un controlador de enlace de MDDI está integrado tanto en el módulo de cámara 118 como en el MSM 104. En el ejemplo de la FIG. 1, un anfitrión de MDDI 122 está integrado en un módulo de cámara 112, mientras que un Cliente de MDDI 106 reside en el lado del MSM del enlace de MDDI 110. Típicamente el anfitrión de MDDI es el controlador maestro del enlace MDDI. En el ejemplo de la FIG. 1, los datos de píxeles procedentes del módulo de cámara 118 son recibidos y formateados en paquetes MDDI por el Anfitrión de MDDI 122 antes de ser transmitidos sobre el enlace de MDDI 110. El cliente de MDDI 106 recibe los paquetes de MDDI y los reconvierte en datos de píxeles del mismo formato que el generado por el módulo de cámara 118. Los datos de píxeles son, a continuación, enviados al bloque apropiado del MSM 104 para su procesamiento.

Con referencia todavía a la FIG. 1, un enlace de MDDI 112 conecta el módulo de LCD 116 al MSM 104. En el ejemplo de la FIG. 1, el enlace de MDDI 112 interconecta un Anfitrión de MDDI 108, integrado en el MSM 104, y un Cliente de MDDI 120 integrado en el módulo de LCD 116. En el ejemplo de la FIG. 1, los datos de representación generados por un controlador de gráficos del MSM 104 son recibidos y formateados en paquetes de MDDI por el Anfitrión de MDDI 108 antes de ser transmitidos sobre el enlace de MDDI 112. El cliente de MDDI 120 recibe los paquetes de MDDI y los reconvierte en datos de representación para su uso por el módulo de LCD 116.

La FIG. 2 es un diagrama de bloques que ilustra la interconexión de enlaces de MDDI 110 de acuerdo con el ejemplo de la FIG. 1. Según lo descrito anteriormente, una de las funciones del enlace MDDI 110 es transferir los datos de píxeles desde el módulo de cámara 118 al MSM 104. De acuerdo con ello, en la forma de realización de la FIG. 2, una interfaz de trama 206 conecta el módulo de cámara 118 al Anfitrión de MDDI 122. La interfaz de trama 206 sirve para transferir los datos de píxeles desde el módulo de cámara 118 al Anfitrión de MDDI 122.

Típicamente, el módulo de cámara 118 recibe los datos de píxeles desde una cámara a través de una interfaz paralela, almacena los datos de píxeles y, a continuación, los transfiere al Anfitrión de MDDI 122 cuando el anfitrión está preparado. El Anfitrión de MDDI 122 encapsula los datos de píxeles recibidos en paquetes de MDDI. Sin embargo, con el fin de que el Anfitrión de MDDI 122 pueda transmitir los datos de píxeles sobre el enlace de MDDI 110, es necesaria una serialización de los paquetes de MDDI.

En la forma de realización de la FIG. 2, un módulo de serialización 202 integrado en el Anfitrión de MDDI 122, sirve para desplazar en serie de salida los paquetes de MDDI sobre el enlace de MDDI 110. En el extremo del MSM del enlace de MDDI 110, un módulo deserializador 204, integrado en el cliente de MDDI 106, reconstruye los paquetes de MDDI a partir de los datos serie recibidos a partir del enlace de MDDI 110. El cliente de MDDI 106 a continuación retira la encapsulación de la MDDI y transfiere los datos de píxeles paralelos a través de una interfaz de trama 208 hasta un bloque apropiado del MSM 104.

#### Codificador Serie de MDDI

5

10

15

20

25

30

35

40

45

50

La FIG. 3 es un diagrama de circuito que ilustra un codificador serie de MDDI 300. El codificador serie de MDDI 300 se describe con mayor detalle en la Solicitud estadounidense No. 11/285,397, titulada "Codificador Serie con Doble Tasa de Codificador de Datos", depositada el 23 de noviembre de 2005. El codificador serie 300 incluye una etapa de registro de datos final, ilustrada utilizando los biestables 320 y 322, una etapa de registro de entrada de selección ilustrada utilizando los biestables 314, 316 y 318, y un conjunto de circuitos de multiplexador sin perturbaciones de baja frecuencia 324.

Los biestables de etapa de registro de datos final 320 y 322 reciben las señales de entrada de datos 308 y 310, respectivamente. En una forma de realización, las señales de entrada de datos 308 y 310 son cada una de 4 bits. De acuerdo con ello, los biestables 320 y 322 son cada uno biestables de 4 bits. En otra forma de realización los biestables 320 y 322 pueden ser sustituidos por cuatro biestables de 2 bits o por ocho biestables de 1 bit. Como se

ilustra en la FIG. 3, los biestables 320 y 322 son biestables D, pero también pueden ser utilizados otros tipos de biestables o registros como debe entender la persona experta en la materia en base a las enseñanzas contenidas en la presente memoria. Los biestables 320 y 322 son controlados por una señal de reloj 312 y actualizan sus salidas en cada flanco de subida de la señal de reloj.

Los biestables de etapa de registro de entrada de selección 314, 316 y 318 reciben unas señales de entrada de selección sel (2) 302, sel (1) 304 y sel (0) 306, respectivamente. Las señales de entrada de selección 302, 304 y 306 son típicamente suministradas por un contador y son utilizadas para seleccionar la entrada del conjunto de circuitos de multiplexador 324. En una forma de realización, las señales de selección 302, 304 y 306 son generadas de acuerdo con una secuencia de código Gray, lo que es conocido *a priori* por el conjunto de circuitos del multiplexador 324, permitiendo con ello una salida de multiplexador sin perturbaciones de baja frecuencia. Los biestables 314, 316 y 318 son biestables D, pero también pueden ser utilizados otros tipos de biestables como debe entender la persona experta en la materia en base a las enseñanzas contenidas en la presente memoria. Los biestables 314, 316 y 318 son también controlados por la señal de reloj 312, actualizando el biestable 318 su salida en los flancos de subida, de la señal de reloj 312 y actualizando los biestables 314 y 316 sus salidas en los flancos de caída de la señal de reloj 312.

El conjunto de circuitos de multiplexador 324 recibe las señales de entrada de datos procedentes de la etapa de registro final y las señales de selección de entrada procedentes del registro de entrada de selección, y genera la salida 334 del codificador serie 300. El conjunto de circuitos de multiplexador 324 genera una señal de codificador sin perturbaciones de baja frecuencia utilizando un conocimiento *a priori* de la secuencia de selección de entrada de código Gray. El conjunto de circuitos de multiplexador 324 incluye cuatro capas de lógica 326, 328, 330 y 332 que separan la etapa de registro de datos final (biestables 320 y 322) y la etapa de registro de entrada de selección (biestables 318, 320 y 322) de la salida del codificador 334. La capa lógica 326 incluye un conjunto de circuitos inversores expuestos sobre determinadas trayectorias desde la etapa de registro de entrada de selección hasta la salida del codificador. La capa lógica 326 está acoplada por medio de una interconexión con la capa lógica 328, la cual incluye una pluralidad de puertas AND. A su vez, la capa lógica 328 está acoplada por medio de una interconexión con la capa lógica 330. La capa lógica 330 incluye una pluralidad de puertas OR, las cuales proporcionan las entradas de la capa lógica 332. La capa lógica 332 incluye una puerta OR que proporciona la salida 334 del codificador serie.

Se debe destacar que las cuatro capas lógicas 326, 328, 330 y 332 de un conjunto de circuitos de multiplexador 324 están basadas en la lógica combinatoria y no son accionadas por señales de reloj. De acuerdo con ello, los retardos en la propagación de las señales sobre las diferentes trayectorias desde la etapa de registro de datos final y / o la etapa de registro de entrada de selección hasta la salida del codificador pueden ser diferentes. Así mismo, los retardos en la programación de las señales podrían variar con la temperatura y / o con las variaciones del proceso producidas en el conjunto de circuitos de codificador, haciendo que sea difícil controlarlas y / o compensarlas.

Típicamente, al producirse unos retardos en las propagación de las señales diferentes desde la trayectoria hasta la salida del codificador, ello se traduce en lo que se denomina como "asincronía de salida", estando la salida del codificador real no sincronizada o distorsionada con respecto a una salida nominal deseada. La desalineación de salida también se traduce en la falta de sincronización de una sola señal que contribuye a la salida del codificador.

Las FIGs. 4A - B ilustran ejemplos de asincronía de señales. La FIG. 4A ilustra la asincronía en una señal ejemplar 400, por medio de la cual pueden producirse flancos de caída y / o subida antes o después de cuando deberían en teoría producirse. La FIG. 4B ilustra la asincronía entre dos señales Salida No. 1 y Salida No. 2. La Salida 1 y Salida 2 resultan de las señales de entrada sincronizadas 402 y 404 que se propagan a través de las trayectorias 406 y 408, respectivamente, del circuito ejemplar 414,, presentando las trayectorias 406 y 408 diferentes retardos de propagación de las señales. La asincronía entre las señales Salida 1 y Salida 2, ilustrada como "t<sub>sk</sub>" en la FIG. 4B, representa la magnitud de la diferencia de tiempo entre las señales Salida 1 y Salida 2, las cuales teóricamente se producirían de manera simultánea. Nótese que la asincronía entre las señales Salida 1 y Salida 2 podría traducirse en una asincronía de salidas en la referencia numeral 412 del circuito ejemplar 414.

En ciertos casos, la asincronía de salida puede provocar una reducción en la tasa de transmisión de enlace de MDDI máxima. Es evidente, por tanto, que la asincronía de salida debería reducirse al mínimo.

#### 50 Codificador Serie de MDDI con Asincronía de Salida Reducida

20

25

55

De acuerdo con la presente invención, la asincronía de salida se reduce minimizando los efectos de los factores que contribuyen a ella. En un aspecto, la asincronía de salida está afectada por la asincronía individual de cada señal (desde la etapa de registro de datos final y / o de la etapa de registro de entrada de selección) que contribuye a la salida del codificador. En otro aspecto, la asincronía de salida es proporcional a las magnitudes de estas asincronías de salida individuales las cuales, a su vez, son proporcionales a sus respectivas trayectorias de señales (como función del número de capas lógicas sucesivas para alcanzar la salida del codificador).

En cuanto tal, la asincronía de salida puede ser reducida minimizando: (1) el número de señales (procedentes de la etapa de registro de datos final y / o de la etapa de registro de entrada de selección) que contribuye a la salida del

codificador, y (2) el número de capas lógicas desde la etapa de registro de entrada final y / o la etapa de registro de entrada de selección hasta la salida del codificador.

La FIG. 5 es un diagrama de bloques que ilustra un codificador serie de MDDI 500 de acuerdo con una forma de realización de la presente invención. El codificador 500 incluye un multiplexador no de perturbaciones de baja frecuencia 506 y un circuito de sincronización 510.

5

10

30

35

40

45

50

55

El multiplexador no de perturbaciones de baja frecuencia 506 recibe la señal de entrada de entradas 504 y las señales de selección de entrada 502 y genera la señal de salida 508. En una forma de realización, la señal de entrada de datos 504 incluye una señal de 8 bits. En otra forma de realización, la señal de entrada de datos 504 incluye dos señales de 4 bits, cuatro señales de 2 bits, u ocho señales de 1 bit. Las señales de selección de entrada 502 controlan el multiplexador 506 para acoplar una de las señales de entrada de datos recibida a la salida del multiplexador. Típicamente, el número N, de las señales de selección de entrada 502 es tal que 2<sup>N</sup> iguala el número de bits de datos de la señal 504. En la FIG. 5, el número de señales de selección de entrada 502 es 3, haciendo que el multiplexador 506 sea un multiplexador de 8:1.

Dado que la salida 508 del multiplexador 506 puede ser de no sin perturbaciones de baja frecuencia, el codificador serie 500 puede ser simplificado de manera considerable. En un aspecto, se permite que los bits de datos de la señal de entrada 504 se conmuten en cualquier momento y no solo cuando están siendo seleccionados para la salida, como en el multiplexador sin perturbaciones de baja frecuencia. En otro aspecto, la secuencia de selección de entrada llevadas a cabo por la señales de selección de entrada 502 ya no necesitan adherirse a una secuencia de código Gray.

De acuerdo con ello, para generar una salida del codificador sin perturbaciones de baja frecuencia se utiliza un circuito 510 para asegurar que cualquier perturbación de baja frecuencia en la salida 508 sea eliminada en la salida del codificador 512. En una forma de realización, el circuito de señalización 510 incluye una etapa de registro de datos final accionada por reloj que hace posible que las señales que contribuyen a la salida del codificador presenten una mínima asincronía entre sí. Así mismo, la etapa de registro de datos final está en un número de capas lógicas muy pequeño alejado de la salida del codificador, reduciendo así mismo la asincronía de salida.

La FIG. 6 es un diagrama de circuito que ilustra un codificador serie de MDDI 600 de acuerdo con otra forma de realización de la presente invención.

El codificador serie 600 incluye una etapa de registro de datos, ilustrada utilizando el biestable 620, una etapa de registro de entrada de selección ilustrada utilizando los biestables 612, 614 y 616, un multiplexador 622 y un circuito de sincronización 626.

El biestable de etapa de registro de datos 620 recibe la señal de entrada de datos 610. En una forma de realización, la señal de entrada de datos 610 incluye una señal de 8 bits. De acuerdo con ello el biestable 620 es un biestable de 8 bits. En otras formas de realización, el biestable 620 puede ser sustituido por dos biestables de 4 bits, cuatro biestables de 2 bits u ocho biestables de 1 bit. Como se ilustra en la FIG. 6, el biestable 620 es un biestable D, pero también pueden ser utilizados otros tipos de biestables o registros como comprenderá el experto en la técnica en base a las enseñanzas contenidas en la presente memoria.

Los biestables de etapa de registro de entrada de selección 612, 614 y 616 reciben las señales de entrada de selección sel (2) 602, Sel (1) 604 y Sel (0) 606, respectivamente. Las señales de entrada de selección 602, 604 y 606 son típicamente proporcionadas por un contador y son utilizadas para seleccionar la entrada del multiplexador 622. Las señales de selección 602, 604 y 606 no necesitan adherirse a ningún tipo de secuencia de selección de entrada, como por ejemplo una secuencia de código Gray, por ejemplo. Los biestables 612, 614 y 616 son biestables D, pero también pueden ser utilizados otros tipos de biestables como comprenderá la persona experta en la materia en base a las enseñanzas contenidas en la presente memoria.

El multiplexador 622 recibe las señales de entrada de datos procedentes de la entrada de registro de datos y las señales de selección de entrada procedentes de la etapa de registro de entrada de selección, y genera la señal de salida 624. En una forma de realización, el multiplexador 622 es un multiplexador 8:1.

El multiplexador 622 es un multiplexador no de sin perturbaciones de baja frecuencia. En otras palabras, las perturbaciones de baja frecuencia pueden producirse en la salida 624 del multiplexador 622. De acuerdo con ello, la salida 624 del multiplexador 622 se proporciona a un circuito de sincronización 626 para asegurar que cualquier perturbación de baja frecuencia en la salida 624 sea eliminada en la salida del codificador 642.

El circuito de sincronización 626 incluye una primera etapa XOR, ilustrada utilizando las puertas XOR 628 y 630, una etapa de registro de datos final, ilustrada utilizando los biestables 632, 634, 636 y 638 y una etapa XOR final, ilustrada utilizando la puerta XOR 640, para generar la salida del codificador 642.

Las primeras puertas de etapa XOR 628 y 630 reciben la señal de salida 624 y las señales de retroalimentación procedentes de los biestables 633 y 634, respectivamente. Las salidas de las puertas XOR 628 y 630 son respectivamente recibidas por los biestables 632, 634 y 636 y 638. Los biestables 632, 634, 636 y 638 son

controlados por una señal de reloj clk, actualizando los biestables 632 y 634 las salidas de los flancos en subida de la señal de reloj y actualizando los biestables 636 y 638 las salidas de los flancos de salida de la señal de reloj.

Los biestables 634 y 636 son biestables de retroalimentación de la etapa de registro de datos final que presenta sus salidas acopladas transversalmente a las puertas XOR 628 y 638 de la primera etapa XOR. En otras formas de realización, las señales de retroalimentación hasta las puertas 628 y 630 XOR son proporcionadas desde las salidas de los biestables 638 y 632, respectivamente, siendo eliminados los biestables 634 y 636 de la etapa de registro de datos final. Un diseño más estable, sin embargo, se obtiene mediante la utilización de los biestables 634 y 636 para proporcionar las señales de retroalimentación a la primera etapa XOR. Esto reduce cualquier encaminamiento adicional de las salidas de los biestables 632 y 638, los cuales a continuación solo necesitan ser introducidos en la etapa XOR final de la etapa de sincronización 626.

La etapa XOR final del circuito de sincronización 626 incluye una sola puerta XOR 640, la cual recibe las salidas de los biestables 632, 638 y la salida del codificador de las salidas 642. La salida del codificador 642 es una salida sin perturbaciones de baja frecuencia con una asincronía de salida débil.

Se destaca que en el codificador serie 600, una sola capa de lógica separa la etapa de registro de datos final de la salida del codificador. De acuerdo con ello, la desalineación individual de las señales que contribuyen a la salida del codificador permanece muy débil. Así mismo, se destaca que solo dos señales procedentes de la etapa de registro de datos final (salidas de los biestables 632 y 638) contribuyen a la salida del descodificador 642, reduciendo también la desalineación de salida. El número reducido de trayectorias desde la etapa de registro final hasta la salida del codificador simplifica también el análisis de la desalineación de salida.

La FIG. 8 es un diagrama de circuito que ilustra un codificador serie de MDDI 800 de acuerdo con una forma de realización adicional de la invención. El codificador serie de MDDI 800 es similar en diversos aspectos al codificador serie de MDDI 800 de la FIG. 6, pero emplea una implementación de circuito de sincronización diferente 812. Se destaca que, en la práctica, el circuito de sincronización es equivalente a un biestable de flanco doble y, de acuerdo con ello, cualquier implementación de un biestable de flanco doble o de un conjunto de circuitos funcionalmente equivalente puede ser utilizado para el circuito de sincronización de acuerdo con formas de realización de la presente invención.

En la FIG. 8, el circuito de sincronización 812 incluye una etapa de registro final, ilustrada utilizando los biestables 804 y 806 y un multiplexador 808. Los biestables 804 y 806 reciben la señal de salida 624 del multiplexador 622 y son controlados por la señal de reloj 802, actualizando el biestable 804 su salida en los flancos de subida, actualizando el biestable 804 su salida en los flancos de subida de la señal de reloj 802 y actualizando el biestable 806 su salida en los flancos de caída de la señal de reloj 802. Las salidas de los biestables 804 y 806 forman a continuación unas entradas al multiplexador 808. El multiplexador 808 es también controlado por la señal de reloj 802. siendo la salida del biestable 804 emitida desde el multiplexador 808 cuando la señal de reloi 802 es elevada v siendo la salida del biestable 806 emitida desde el multiplexador 808 cuando la señal de reloj 802 es débil, para generar la salida del codificador 810. Se destaca que, en la forma de realización 800, la salida del codificador 810 presenta una condición de carrera sobre la señal de reloj 802. Esta condición de carrera es un resultado del flanco de caída o subida de la señal de reloj 802 que provoca que la entrada actualmente seleccionada al multiplexador 808 cambie. La salida del codificador 810 es sin perturbaciones de baja frecuencia solo si un flanco de subida o caída de la señal de reloj 802 ha seleccionado la otra entrada del multiplexador 808 como salida del codificador 810 antes de que la entrada actual cambie. A modo de ejemplo, cuando la señal de reloj 802 es débil, la salida del biestable 806 está siendo emitida desde el multiplexador 808 como salida del codificador 810. En el flanco de subida de la señal de reloj 802, la salida del biestable 806 será actualizada en un nuevo estado mientras que al mismo tiempo la salida del biestable 804 es seleccionada como salida del multiplexador 808 como salida del codificador 810. Para evitar perturbaciones de baja frecuencia en la salida del codificador 810, el retardo procedente de la señal de reloj 802 a través del multiplexador 808 hasta la salida del codificador 810 debe ser inferior al retardo de la señal de reloi 802 a través de los biestables 804 u 810 hasta el multiplexador 808. En tanto en cuanto esta condición de temporización se cumpla, la salida del codificador 810 es una salida sin perturbaciones de baja frecuencia con una asincronía de salida débil.

Se destaca también que en el codificador serie 800, una sola capa de lógica separa la etapa de registros final de la salida del codificador contribuyendo solo dos señales procedentes de la etapa de registro de datos final a la salida del codificador 810, traduciéndose ello en una asincronía de salida reducida y en un análisis de la asincronía de salida simplificado.

#### Diagramas de temporización ejemplares

5

10

30

35

40

45

50

55

La FIG. 7 es un diagrama de temporización ejemplar relacionado con las señales del codificador serie de MDDI 600 de la FIG. 6. En este diagrama ejemplar, las transiciones de las salidas de selección, ilustradas como señal sel [2:0] de la FIG. 7, está de acuerdo con una secuencia de código Gray como típicamente se requiere para los codificadores de MDDI con multiplexador sin perturbaciones de baja frecuencia. De acuerdo con ello, el multiplexador 622 opera de manera idéntica a un multiplexador sin perturbaciones de baja frecuencia, pero sin la exigencia de salida libre de las perturbaciones de baja frecuencia. Nótese que la secuencia de salidas de selección

de la FIG. 7 es una secuencia ejemplar y que también pueden ser utilizadas otras secuencias de salidas de selección.

La salida din [7:0] de la FIG. 7 se corresponde a la señal de entrada de datos 610 de la FIG. 6. Una secuencia ejemplar de la señal DIN [7:0] se proporciona en la FIG. 7.

La señal din\_reg [7:0] se corresponde con la señal din\_reg [7:0] ilustrada en la FIG. 6, y puede ser generada a partir de la señal din [7:0] de acuerdo con la señal data\_en de la FIG. 7. Una secuencia ejemplar de la señal din\_reg [7:0] se proporciona en la FIG. 7.

La señal desired data out se corresponde con la señal 624 de la FIG. 6.

- Las señales out\_rise y out\_fall se corresponde con las salidas de los biestables 632 y 638, respectivamente. Nótese que out\_rise = (desired\_data\_out XOR out\_fall) y que out\_fall = (desired\_data\_out XOR out\_rise). Así mismo, nótese que la señal dout = out\_rise XOR out\_fall. De acuerdo con ello, uno cualquiera de los dos registros de salida finales pueden accionar el valor desired\_data\_out hasta dout mediante el mantenimiento o la inversión de su salida. La señal dout es equivalente a la señal desired data out pero es retardada ½ ciclo de reloj.

- La FIG. 9 es un diagrama de temporización ejemplar relativo a las señales del codificador serie MDDI 800 de la FIG. 8. De modo similar al diagrama de temporización ejemplar de la FIG. 7, las transacciones de la salida de transición ilustradas como sel [2:0] de la FIG. 9, están de acuerdo con una secuencia de código Gray como se requiere típicamente para los descodificadores de MDDI con multiplexador sin perturbaciones de baja frecuencia. Nótese que, sin embargo, la secuencia de entrada de selección ilustradas en la FIG. 9 es solo ejemplar, y que también podrían ser utilizadas otras secuencias de entrada de selección.

- La señal din [7:0] de la FIG. 9 se corresponde con la señal de entrada de datos 610 de la FIG. 8. Una secuencia ejemplar de la señal din [7:0] se proporciona en la FIG. 9.

- La señal din\_reg [7:0] se corresponde con la salida del biestable 620 de la FIG. 8. Una secuencia ejemplar de la señal din\_reg [7:0] se proporciona en la FIG. 9.

- La señal desired data out se corresponde con la señal 624 de la FIG. 8.

- Las señales post\_reg y neg\_reg se corresponden con las salidas de los biestables 804 y 806, respectivamente, de la FIG. 8.

La señal dout se corresponde con el dout de salida del codificador 810 de la FIG. 8. Nótese que dout es equivalente a la señal desired\_data\_out, pero está retrasada por 1 ciclo de reloj, con un retraso de ½ ciclo de reloj debido a los biestables 804 y 806 y un retraso de ½ ciclo de reloj debido al multiplexador 808.

## 30 Conclusión

35

Aunque en las líneas anteriores se han descrito diversas formas de realización de la presente invención se debe entender que han sido ofrecidas solo a modo de ejemplo y no de limitación. Debe resultar evidente para los expertos en la materia relevante que pueden llevarse a cabo diversos cambios de forma y detalle sin apartarse del alcance de la presente invención. Por tanto, la amplitud y el alcance de la presente invención no debe quedar limitada por cualquiera de las formas de realización ejemplares descritas anteriormente, sino que deben quedar definidas únicamente con arreglo a las reivindicaciones que siguen.

#### REIVINDICACIONES

1. Un codificador serie (600, 800) que comprende:

5

10

15

20

25

un medio (620) para almacenar una pluralidad de bits de entrada de datos;

un medio (612; 614; 616) para almacenar una pluralidad de bits de entrada de selección;

un medio (622) para emitir en serie la pluralidad de bits de entrada de datos de acuerdo con una secuencia de selección de entrada generada por la pluralidad de bits de entrada de selección;

un medio (812) para eliminar unas perturbaciones de baja frecuencia de una salida de dicho medio de salida serie, generando con ello una salida de codificador serie sin perturbaciones de baja frecuencia (dout) en el que dicho medio para la eliminación de perturbaciones de baja frecuencia incluye una etapa de registro accionada por reloj caracterizado porque\_la salida de dicho medio de salida serie (624) está acoplada a una entrada de datos de la etapa de registro accionada por reloj (804, 806), y en el que dicha etapa de registro (804; 806) está separada por una sola capa lógica (640, 808) de la salida del codificador serie, determinando de esta manera una desalineación de salida débil del codificador.

2. El codificador serie de la reivindicación 1, en el que

el medio de almacenamiento comprende también un multiplexor (622) que presenta una pluralidad de entradas de datos, una pluralidad de entradas de selección, y una salida;

el medio de almacenamiento comprende también una pluralidad de biestables de entrada de datos (620) acoplada a las entradas de datos del multiplexador;

el medio de almacenamiento comprende también una pluralidad de biestables de entrada de selección (612, 614, 616) acoplada a las entradas de selección del multiplexador; y

el medio de eliminación comprende también un circuito de sincronización (606, 812) acoplado a la salida del multiplexador y que proporciona una salida del codificador serie (642, 810), en el que el circuito de sincronización comprende una etapa de registro de datos final (632, 634, 636, 638 u 804, 806), y la etapa de registro de datos final está separada por una sola capa lógica (640, 808) de la salida del codificador serie, resultando de esta forma una desalineación de salida débil del codificador, en el que la salida del multiplexador (624) está acoplada a una entrada de datos de la etapa de registro de datos final (804, 806), y en el que el circuito de sincronización sustancialmente elimina cualquier perturbación de baja frecuencia de salida de la salida del multiplexador.

- 3. Un codificador de acuerdo con la reivindicación 2, en el que el multiplexador presenta ocho salidas de datos y tres salidas de selección.

- 4. Un codificador de acuerdo con la reivindicación 2, en el que el multiplexador es un multiplexador no de perturbaciones de baja frecuencia.

- 5. Un codificador de acuerdo con la reivindicación 2, en el que los biestables de entrada de datos y los biestables de entrada de selección son biestables D.

- 35 6. Un codificador de acuerdo con la reivindicación 2, en el que las entradas de selección del multiplexador son proporcionadas por un contador de acuerdo con una señal de reloj.

- Un codificador de acuerdo con la reivindicación 6, en el que el multiplexor emite un bit en cada flanco de la señal de reloj.

- 8. Un codificador de acuerdo con la reivindicación 2, en el que la etapa de registro de datos final es accionada por reloj.

- 9. Un codificador de acuerdo con la reivindicación 2, en el que el codificador recibe una entrada de datos paralela y emite en serie la entrada de datos sobre un enlace de comunicación serie.

- Un codificador de acuerdo con la reivindicación 9, en el que el enlace de comunicación serie es un enlace de Interfaz Digital de Representación Móvil (MDDI).

- 45 11. Un codificador de acuerdo con la reivindicación 2, en el que el circuito de sincronización es implementado utilizando cualquier biestable de flanco doble.

- 12. El codificador serie (600, 800) de la reivindicación 1, en el que la etapa de registro de accionamiento por reloj emite dos señales, y en el que la salida del codificador serie se determina seleccionando una de las dos señales, de manera que la salida del codificador serie se determina únicamente por las dos señales

procedentes de dicha etapa de registro, determinando con ello una desalineación de salida débil del codificador.

13. El codificador serie de acuerdo con la reivindicación 12, en el que dicho medio de salida serie emite un bit en cada flanco de una señal de reloj, determinado con ello que el codificador serie sea un codificador de doble tasa de transmisión de datos.

5

FIG. 4A

FIG. 5