# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 444 371

51 Int. Cl.:

G06F 11/267 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 26.02.2007 E 07726502 (3)

(97) Fecha y número de publicación de la concesión europea: 25.12.2013 EP 2002340

(54) Título: Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control

(30) Prioridad:

28.03.2006 DE 102006014267

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **24.02.2014**

(73) Titular/es:

ROBERT BOSCH GMBH (100.0%) POSTFACH 30 02 20 70442 STUTTGART, DE

(72) Inventor/es:

**AUE, AXEL**

74) Agente/Representante:

CARVAJAL Y URQUIJO, Isabel

#### **DESCRIPCIÓN**

Procedimiento para la verificación de al menos una unidad de cálculo integrada en un aparato de control

Estado de la técnica

5

25

30

40

45

50

La presente invención se refiere a un procedimiento para la verificación de al menos una unidad de cálculo incorporada en un aparato de control, en el que el aparato de control está incorporado especialmente en un automóvil.

El aparato técnico de la invención se refiere a la verificación de circuitos integrados, en particular su unidad de cálculo o unidades de cálculo. A continuación se utilizan de forma similar una unidad de cálculo, un mecanismo de cálculo, un dispositivo de cálculo y un núcleo digital y se designan de la misma manera.

Se conoce verificar circuitos integrados o bien su mecanismo de cálculo o mecanismos de cálculo en un estado no montado. A este respecto, estado no motado significa que el circuito integrado o bien el mecanismo de cálculo o los mecanismos de cálculo no están montados o incorporados, en particular todavía no en un aparato de control, en un dispositivo de control o similar. Esta verificación es realizada especialmente por el fabricante de semiconductores del circuito integrado. Ejemplos de tales ensayos son el llamado ensayo-Stuck-At y el ensayo-Path-Delay. Por medio del ensayo Stuck-At se verifica un cortocircuito potencial de una señal después de la tensión de alimentación o masa, por ejemplo en una cadena de escaneo o en una trayectoria de escaneo de la unidad de cálculo correspondiente. Por medio del ensayo-Path-Delay se verifican los tiempos de propagación de las señales por ejemplo a través de las cadenas de escaneo o de las trayectorias de escaneo. Descripciones detalladas del ensayo-Stuck-At y del ensayo-Path-Delay se conocen a partir del documento EP 0548585 A2.

20 Se conoce a partir del documento US 2004/064 757 A1 otro procedimiento para la verificación de un aparato de control.

El procedimiento de acuerdo con la invención para la verificación de una unidad de cálculo incorporada al menos en un aparato de control con las características de la reivindicación 1 presenta frente a los principios de solución conocidos la ventaja de que también se pueden verificar unidades de cálculo en un estado montado o incorporado y en particular también en el aparato de control cerrado. De esta manera es posible de acuerdo con la invención verificar una unidad de cálculo o varias unidades de cálculo de un aparato de control, que está montado, por ejemplo, en un lugar discrecional de un automóvil. En particular, de acuerdo con la invención, en el aparato de control montado se pueden realizar el ensayo-Stuck-At y el ensayo-Path-Delay.

A través del procedimiento de acuerdo con la invención se asegura, por lo tanto, que el aparato de control y en particular sus unidades de cálculo se puedan verificar después de esfuerzo de tensión o después de la utilización de la misma manera (y, por lo tanto, con buena cobertura de ensayo comparativamente similar) como en el fabricante correspondiente de semiconductores. De ello resulta especialmente una capacidad de análisis mejorada de retornos de campo. En particular, se eleva la probabilidad de que un fallo determinado, que podría encontrarse por el fabricante de semiconductores en el estado no montado, no se encentra en el estado montado.

La idea en la que se basa la presente invención consiste esencialmente en preparar un procedimiento con las siguientes etapas para la verificación de al menos una unidad de cálculo incorporada en un aparato de control, presentando el aparato de control una interfaz de aparato de control, al menos dos unidades de cálculo, que presentan, respectivamente, una cadena de escaneo (o bien el comienzo de un circuito, que interconecta las cadenas de escaneo internas), y presenta al menos una unidad de memoria:

- carga de primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación de una primera unidad de cálculo;

- registro en memoria de los primeros datos de ensayo cargados en una segunda unidad de memoria de una segunda unidad de cálculo:

- conmutación de la primera unidad de cálculo aun modo de ensayo, en el que una primera cadena de escaneo de la primera unidad de cálculo es accesible, por medio de la segunda unidad de cálculo;

- lectura de los primeros datos de ensayo desde la segunda unidad de cálculo por medio de la segunda unidad de cálculo;

- desplazamiento de los primeros datos de ensayo leídos a través de la primera cadena de escaneo a la primera unidad de cálculo conmutada al modo de ensayo, por medio de la segunda unidad de cálculo para la preparación de datos de resultados de ensayo para la primera unidad de cálculo;

- verificación de la verosimilitud de los datos de resultados de ensayo acondicionados por medio de la segunda unidad de cálculo para la preparación de un resultado de ensayo para la primera unidad de

cálculo.

5

10

15

20

40

45

De acuerdo con la invención, el procedimiento de acuerdo con la invención presenta, además, las siguientes etapas:

- carga de segundos datos de ensayo para la verificación de la segunda unidad de cálculo, en el que los segundos datos de ensayo son cargados por medio de la interfaz de aparatos de control o los primeros datos de ensayo registrados en la segunda unidad de memoria son cargados como segundos datos de ensayo a través de una interfaz interna del aparato de control;

- registro en memoria de los segundos datos de ensayo cargados en una primera unidad de memoria de la primera unidad de cálculo;

- conmutación de la segunda unidad de cálculo a un modo de ensayo, en el que una segunda cadena de escaneo de la segunda unidad de cálculo es accesible, por medio de la primera unidad de cálculo;

- lectura de los segundos datos de ensayo desde la primera unidad de memoria por medio de la primera unidad de cálculo:

- desplazamiento de los segundos datos de ensayo leídos a través de la segunda cadena de escaneo de la segunda unidad de cálculo conmutada al modo de ensayo por medio de la primera unidad de cálculo para la preparación de datos de resultados de ensayo para la segunda unidad de cálculo; y

- verificación de factibilidad de los datos de resultados de ensayo acondicionados por medio de la primera unidad de cálculo para la preparación de un resultado de ensayo para la segunda unidad de cálculo.

En las reivindicaciones dependientes se encuentran desarrollos y configuraciones ventajosos del procedimiento indicado en la reivindicación 1 para la verificación de al menos una unidad de cálculo incorporada en un aparato de control.

De acuerdo con un desarrollo preferido de la invención, los datos de ensayo leídos desde la segunda unidad de memoria son desplazados por medio de la segunda unidad de cálculo a través de una primera interfaz dedicada, por medio de la cual se acopla la segunda unidad de cálculo con la primera cadena de escaneo, a través de la primera cadena de escaneo.

De acuerdo con otro desarrollo preferido, los segundos datos de ensayo leídos desde la primera unidad de memoria son desplazados por medio de la primera unidad de cálculo a través de una segunda interfaz dedicada, por medio de la cual se acopla la primera unidad de cálculo con la segunda cadena de escaneo, a través de la segunda cadena de escaneo.

De acuerdo con otro desarrollo preferido, el aparato de control está provisto con un generador de pulsos de reloj para el acondicionamiento de un pulso de reloj predeterminable y el desplazamiento de los datos de ensayo leídos en cada caso se realiza a través de la cadena de escaneo respectiva para la realización de un ensayo-Path-Delay utilizando el pulso de reloj acondicionado.

De acuerdo con una configuración preferida de la invención, la primera interfaz dedicada y/o la segunda interfaz dedicada están configuradas, respectivamente, como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

De acuerdo con otra configuración preferida, la interfaz de aparatos de control está configurada como bus-CAN o como Bus-FlexRay o bus-K-Line o Bus-LIN.

De acuerdo con otra configuración preferida, los datos de resultados de ensayo acondicionados en cada caso y/o los resultados de ensayos acondicionados en cada caso son registrados en al menos una unidad de memoria de la primera unidad de cálculo o de la segunda unidad de cálculo y/o son acondicionados por medio de la interfaz de aparatos de control para la exportación.

De acuerdo con otra configuración preferida, el pulso de reloj del generador de pulsos de reloj se ajusta a través de la interfaz de aparatos de control.

De acuerdo con otro desarrollo preferido, la primera unidad de cálculo y la segunda unidad de cálculo están integradas en un único circuito integrado, en el que aquellas trayectorias-Stuck-At del circuito integrado, que no pertenecen a la primera unidad de cálculo o a la segunda unidad de cálculo, son verificadas por medio de la primera unidad de cálculo o de la segunda unidad de cálculo

#### Dibujos

En los dibujos se representan ejemplos de realización de la invención y se describen en detalle en la descripción siguiente. En este caso:

## ES 2 444 371 T3

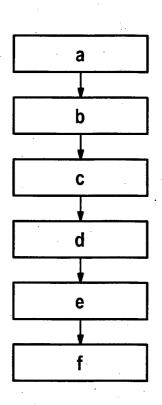

La figura 1 muestra un diagrama de fluj9o esquemático de una primera parte del ejemplo de realización del procedimiento de acuerdo con la invención.

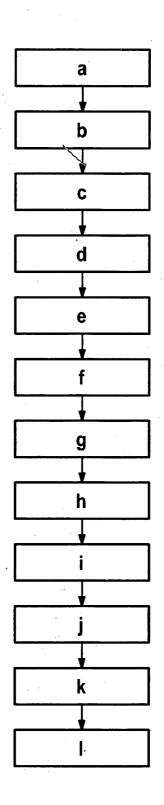

La figura 2 muestra un diagrama de flujo esquemático de una segunda parte del ejemplo de realización del procedimiento de acuerdo con la invención; y

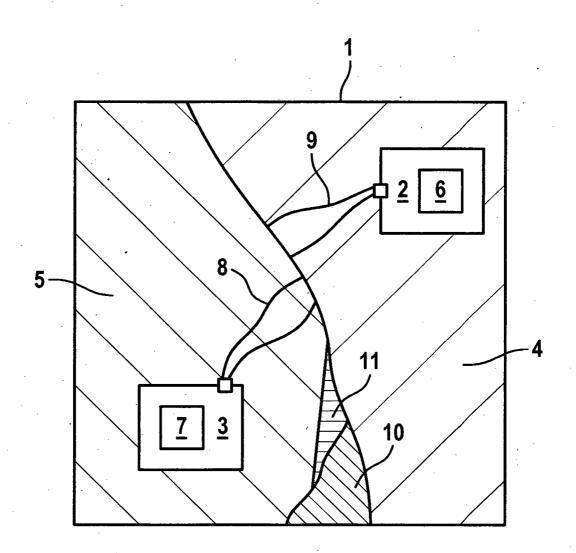

La figura 3 muestra una vista esquemática de un ejemplo de realización de un aparato de control, que es ensayado por medio del procedimiento de acuerdo con la invención.

## Descripción de los ejemplos de realización

En las figuras, los mismos signos de referencia designan componentes iguales o funcionales iguales.

En la figura 1 se representa un diagrama de flujo de una primera parte del ejemplo de realización del procedimiento de acuerdo con la invención. El procedimiento de acuerdo con la invención para la verificación de al menos un microcontrolador incorporado en un aparato de control con las unidades de cálculo 2, 3 presenta las etapas de procedimiento a) a f) indicadas anteriormente. El aparato de control presenta en este caso una interfaz de aparato de control, al menos dos unidades de cálculo 2, 3, que presentan, respectivamente, una cadena de escaneo 4, 5 o bien una zona de una cadena de escaneo 4, 5, y al menos una unidad de memoria 6, 7.

#### 15 Etapa a del procedimiento:

20

35

40

45

50

Se cargan primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación de una primera unidad de cálculo 2. La interfaz de aparatos de control está configurado con preferencia como bus-CAN o Bus-FlexRay o bus-K-Line. Los datos de ensayo representan especialmente vectores de ensayo especialmente modelados, que son generados o bien modelados durante la síntesis del circuito de la unidad de cálculo correspondiente por el fabricante de semiconductores. Con preferencia, los datos de ensayo son proporcionados por el fabricante de semiconductores, por decirlo así, como placas de escaneo.

#### Etapa b del procedimiento:

Los primeros datos de ensayo son registrados o bien depositados en una segunda unidad de memoria 7 de una segunda unidad de cálculo 3.

## 25 Etapa c del procedimiento:

La primera unidad de cálculo 2 es conmutada a un modo de ensayo por medio de la segunda unidad de cálculo 3. En el modo de ensayo, una primera cadena de escaneo 4 o bien una zona de la primera cadena de escaneo 4 de la primera unidad de cálculo 2 es accesible, es decir, que se puede acceder a la primera cadena de escaneo 4, por ejemplo, por medio de la segunda unidad de cálculo 3.

## 30 Etapa d del procedimiento:

Los primeros datos de ensayo son leídos desde la segunda unidad de memoria 7 por medio de la segunda unidad de cálculo 3.

#### Etapa e del procedimiento:

Los primeros datos de ensayo leídos son desplazados a través de la primera cadena de escaneo 4 a la primera unidad de cálculo 2 conmutada el modo de ensayo por medio de la segunda unidad de cálculo 3 para el acondicionamiento de datos de resultados de ensayo para la primera unidad de cálculo 2. Con preferencia, los primeros datos de ensayo leídos desde la segunda unidad de memoria 7 son desplazados por medio de la segunda unidad de cálculo 3 a través de una primera interfaz dedicada 8, por medio de la cual se acopla la segunda unidad de cálculo 3 con la primera cadena de escaneo 4, a través de la primera cadena de escaneo 4. En particular, la primera interfaz dedicada 8 está configurada como registro de corredera o como una interfaz-ASC o una interfaz-SPI.

## Etapa f del procedimiento:

Los datos de resultados de ensayo acondicionados son verificados con respecto a la factibilidad por medio de la segunda unidad de cálculo 3 para el acondicionamiento de un resultado de ensayo para la primera unidad de cálculo 2. En particular, los datos de resultados de ensayo acondicionados son comparados con los datos de resultados de ensayo previsibles. El resultado de ensayo expresa especialmente si existe un error o en particular un error-Stuck-At para la primera cadena de escaneo 4. Con preferencia, los datos de resultados de ensayo acondicionados y/o el resultado de ensayo acondicionado para la primera unidad de cálculo 2 son registrados en una unidad de memoria, en particular en la segunda unidad de memoria 7. De manera alternativa, los datos de resultados de ensayo acondicionados y/o el resultado de ensayo acondicionados para la primera unidad de cálculo 2 son acondicionados

también a través de la interna de aparatos de control para la exportación por medio de un dispositivo de análisis discrecional.

La figura 2 muestra un diagrama de flujo esquemático de una segunda parte del ejemplo de realización del procedimiento de acuerdo con la invención. El ejemplo de realización según la figura 2 presenta las etapas a) a f) del procedimiento del ejemplo de realización según la figura 1 así como las etapas g) a l) del procedimiento descritas a continuación. El ejemplo de realización según la figura 2 acondiciona un procedimiento de ensayo, en el que la primera unidad de cálculo 2 es verificada por medio de la segunda unidad de cálculo 3 y la segunda unidad de cálculo 3 es verificada por medio de la primera unidad de cálculo 2.

Las etapas a) a f) del procedimiento según la figura 2 corresponden a las etapas a) a f) del procedimiento según la figura 1. El ejemplo de realización según la figura 2 se conecta con la etapa g) del procedimiento en la etapa f) del procedimiento del ejemplo de realización según la figura 1.

Etapa g) del procedimiento:

5

15

25

40

45

50

Se cargan dos datos de ensayo para el ensayo de la segunda unidad de cálculo 3, de manera que los segundos datos de ensay9o so cargados por medio de la interfaz de aparatos de control o los primeros datos de ensayo registrados en la segunda unidad de memoria 7 son cargados como segundos datos de ensayo a través de una interfaz interna del aparato de control 1. La interfaz interna está configurada, por ejemplo, como sistema de bus del aparato de control.

Etapa h) del procedimiento:

Los segundos datos de ensayo cargados son registrados o bien depositados en una primera unidad de seguridad 6 de la primera unidad de cálculo 2.

Etapa i) del procedimiento:

La segunda unidad de cálculo 3 es conmutada por medio de la primera unidad de cálculo 2 a un modo de ensayo, en el que una segunda cadena de escaneo 5 de la segunda unidad de cálculo 2 es accesible. En particular, en el modo de ensayo, la segunda unidad de cálculo 2 puede acceder a la segunda cadena de escaneo 5 de la segunda unidad de cálculo 3.

Etapa i) del procedimiento:

Los segundos datos de ensayo son leídos desde la primera unidad de memoria 6 por medio de la segunda unidad de cálculo 2.

Etapa k) del procedimiento:

Los segundos datos de ensayo leídos son desplazados a través de la segunda cadena de escaneo 5 de la segunda unidad de cálculo 3 conmutada al modo de ensayo por medio de la primera unidad de cálculo 2 para el acondicionamiento de datos de resultados de ensayo para la segunda unidad de cálculo 5. Con preferencia, los segundos datos de ensayo leídos desde la primera unidad de cálculo 6 son desplazados por medio de la primera unidad de cálculo 2 a través de una segunda interfaz dedicada 9 a través de la segunda cadena de escaneo 5. La segunda interfaz dedicada 9 acopla la primera unidad de cálculo 2 con la segunda cadena de escaneo 5 y está configurada especialmente como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

Etapa I) del procedimiento:

Los datos de resultados de ensayo acondicionados son verificados con respecto a la factibilidad por medio de la primera unidad de cálculo 2 para el acondicionamiento de un resultado de ensayo para la segunda unidad de cálculo 3. Durante la verificación de la factibilidad se comparan kilos datos de resultados de ensayo acondicionados con datos de resultados de ensayo previsibles, que dependen de los segundos datos de ensayo. Con preferencia, los datos de resultados de ensayos acondicionados y/o el resultado de ensayo acondicionado para la segunda unidad de cálculo 3 son registrados en al menos una unidad de memoria 6, 7 del aparato de control 1, en particular en la primera unidad de memoria 6. De manera alternativa, los datos de resultados de ensayo acondicionados y/o el resultado de ensayo acondicionado para la segunda unidad de cálculo 3 son acondicionados a través de la interfaz de aparatos de control para la exportación por medio de un dispositivo de análisis discrecional.

Con preferencia, tanto en la primera parte del ejemplo de realización según la figura 1 como también en la segunda parte del ejemplo de realización según la figura 2, el aparato de control 1 está provisto con un generador de pulsos de reloj 10 para la preparación de un pulso de reloj predeterminable. Por consiguiente, los datos de ensayo leídos respectivos puede ser desplazados de forma sincronizada a través de la cadena de escaneo 4, 5 respectiva. De esta manera, se posibilita la realización de un ensayo-Path-Delay utilizando el pulso de reloj acondicionado. En el ensayo-Path-Delay se miden especialmente tiempos de retraso durante el desplazamiento a través de unidades

# ES 2 444 371 T3

individuales de la cadena de escaneo o de la trayectoria de escaneo respectiva. Con preferencia, el pulso de reloj del generador de pulsos de reloj 10 se ajusta a través de la interfaz de aparatos de control. A tal fin, se acopla, por ejemplo un dispositivo de análisis a la interfaz de aparatos de control, con la que se ajusta el pulso de reloj del generador de pulsos de reloj 10.

- En particular, de acuerdo con los dos ejemplos de realización según la figura 1 y la figura 2, la primera unidad de cálculo 2 y la segunda unidad de cálculo 3 están integradas en un único circuito integrado, de manera que aquellas trayectorias-Stuck-At o bien cadenas del circuito integrado, que no pertenecen a la primera unidad de cálculo 2 o a la segunda unidad de cálculo 3, son verificadas por medio de la primera unidad de cálculo 2 o de la segunda unidad de cálculo 3.

- 10 La figura 3 muestra una vista esquemática de u ejemplo de realización de un microcontrolador 1, que es verificado por medio del procedimiento de acuerdo con la invención - como se ha descrito anteriormente -. El signo de referencia 1 presenta una primera unidad de cálculo 2 con una primera unidad de memoria 6 y una segunda unidad de cálculo 3 con una segunda unidad de memoria 7. Además, el aparato de control 1 presenta una interfaz de aparatos de control (no mostrada), un primer generador de pulsos de reloj 10 y un segundo generador de pulsos de 15 reloj 11. El primer generador de pulsos de reloj 10 suministra especialmente el pulso de reloj para la realización del ensayo-Path-Delay. El segundo generador de pulsos de reloj 11 sincroniza, por ejemplo, la primera unidad de cálculo 2 y/o la segunda unidad de cálculo 3. Los signos de referencia 4 y 5 identifican la zona de la primera cadena de escaneo 4 sobre la superficie de silicio o bien una zona de la segunda cadena de escaneo 5 sobre la superficie de silicio. Por medio de la primera interfaz dedicada 8, la segunda unidad de cálculo 3 puede acceder a la zona de la 20 primera cadena de escaneo 4. Por medio de la segunda interfaz dedicada 8, la primera unidad de cálculo 2 puede acceder a la zona de la segunda cadena de escaneo 5. En particular, las interfaces dedicadas 8, 9 están configuradas, respectivamente, como un registro de corredera.

- Aunque la presente invención se ha descrito anteriormente con la ayuda de ejemplos de realización preferidos, no está limitada a ellos, sino que se puede modificar de diferentes maneras. Así, por ejemplo, el número de las unidades de cálculo a ensayar de un aparato de control, que son ensayadas por medio del procedimiento de acuerdo con la invención, no están limitadas a dos. Se puede verificar cualquier número discrecional de unidades de cálculo de un aparato de control por medio del procedimiento de acuerdo con la invención. Otra forma de realización es la disposición de los vectores de ensayo en una memoria común. Además, es posible que los datos de ensayo no sean registrados en el silicio, sino que tanto los datos de entrada como también los datos de salida son cargados a través de una interfaz de aparatos de control separada para cada unidad de cálculo (no contenida en los dibujos) y son enviados también de nuevo hacia fuera.

35

#### REIVINDICACIONES

1.- Procedimiento para la verificación de unidades de cálculo (2, 3) incorporadas en un aparato de control, presentando el aparato de control una interfaz de aparato de control, al menos dos unidades de cálculo (2, 3), que presentan, respectivamente, una cadena de escaneo (4, 5) y al menos dos unidades de memoria (6, 7), con las etapas:

5

20

25

30

35

40

45

- a) carga de primeros datos de ensayo por medio de la interfaz de aparatos de control para la verificación de una primera unidad de cálculo (2);

- registro en memoria de los primeros datos de ensayo cargados en una segunda unidad de memoria (7) de una segunda unidad de cálculo (3);

- 10 c) conmutación de la primera unidad de cálculo (2) a un modo de ensayo, en el que una primera cadena de escaneo (4) de la primera unidad de cálculo (2) es accesible, por medio de la segunda unidad de cálculo (3);

- d) lectura de los primeros datos de ensayo desde la segunda unidad de cálculo (7) por medio de la segunda unidad de cálculo (3):

- e) desplazamiento de los primeros datos de ensayo leídos a través de la primera cadena de escaneo (4) a la primera unidad de cálculo (2) conmutada al modo de ensayo, por medio de la segunda unidad de cálculo (3) para la preparación de datos de resultados de ensayo para la primera unidad de cálculo (2);

- f) verificación de la verosimilitud de los datos de resultados de ensayo acondicionados por medio de la segunda unidad de cálculo (3) para la preparación de un resultado de ensayo para la primera unidad de cálculo (2);

- g) carga de segundos datos de ensayo para la verificación de la segunda unidad de cálculo (3), en el que los segundos datos de ensayo son cargados por medio de la interfaz de aparatos de control o los primeros datos de ensayo registrados en la segunda unidad de memoria (7) son cargados como segundos datos de ensayo a través de una interfaz interna del aparato de control (1);

- registro en memoria de los segundos datos de ensayo cargados en una primera unidad de memoria (6) de la primera unidad de cálculo (2);

- i) conmutación de la segunda unidad de cálculo (3) a un modo de ensayo, en el que una segunda cadena de escaneo (5) de la segunda unidad de cálculo (3) es accesible, por medio de la primera unidad de cálculo (2):

- j) lectura de los segundos datos de ensayo desde la primera unidad de memoria (6) por medio de la primera unidad de cálculo (2);

- desplazamiento de los segundos datos de ensayo leídos a través de la segunda cadena de escaneo (5) de la segunda unidad de cálculo (3) conmutada al modo de ensayo por medio de la primera unidad de cálculo (2) para la preparación de datos de resultados de ensayo para la segunda unidad de cálculo (5); y

- verificación de factibilidad de los datos de resultados de ensayo acondicionados por medio de la primera unidad de cálculo (2) para la preparación de un resultado de ensayo para la segunda unidad de cálculo (3).

- 2.- Procedimiento de acuerdo con la reivindicación 1, caracterizado porque los primeros datos de ensayo leídos desde la segunda unidad de memoria (7) son desplazados por medio de la segunda unidad de cálculo (3) a través de una primera interfaz dedicada (8), por medio de la cual se acopla la segunda unidad de cálculo (3) con la primera cadena de escaneo (4), a través de la primera cadena de escaneo (4).

- 3.- Procedimiento de acuerdo con la reivindicación 2, caracterizado porque la primera interfaz dedicada (8) está configurada como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

- 4.- Procedimiento de acuerdo con la reivindicación 2, caracterizado porque los segundos datos de ensayo leídos desde la primera unidad de memoria (6) son desplazados por medio de la primera unidad de cálculo (2) a través de una segunda interfaz dedicada (9), por medio de la cual se acopla la primera unidad de cálculo (2) con la segunda cadena de escaneo (5), a través de la segunda cadena de escaneo (5).

- 5.- Procedimiento de acuerdo con la reivindicación 4, caracterizado porque la primera interfaz dedicada (8) y/o la segunda interfaz dedicada (9) están configuradas, respectivamente, como un registro de corredera o una interfaz-ASC o una interfaz-SPI.

## ES 2 444 371 T3

- 6.- Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque el aparato de control (1) es provisto con un generador de pulsos de reloj (10) para el acondicionamiento de un pulso de reloj predeterminable y el desplazamiento de los datos de ensayo leídos en cada caso se realiza a través de la cadena de escaneo (4, 5) respectiva para la realización de un ensayo-Path-Delay utilizando el pulso de reloj acondicionado.

- 7.- Procedimiento de acuerdo con la reivindicación 6, caracterizado porque el pulso de reloj del generador de pulsos de reloj (10) se ajusta a través de la interfaz del aparato de control.

- 8.- Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque la interfaz de aparatos de control está configurada como bus-CAN o como Bus-FlexRay o bus-K-Line o Bus-LIN.

- 9.- Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque los datos de resultados de ensayo acondicionados en cada caso y/o los resultados de ensayos acondicionados en cada caso son registrados en al menos una unidad de memoria (6, 7) de la primera unidad de cálculo (2) o de la segunda unidad de cálculo (3) y/o son acondicionados por medio de la interfaz de aparatos de control para la exportación.

- 10.- Procedimiento de acuerdo con una o varias de las reivindicaciones 1 a 5, caracterizado porque la primera unidad de cálculo (2) y la segunda unidad de cálculo (3) están integradas en un único circuito integrado, en el que aquellas trayectorias-Stuck-At del circuito integrado, que no pertenecen a la primera unidad de cálculo (2) o a la segunda unidad de cálculo (3), son verificadas por medio de la primera unidad de cálculo (2) o de la segunda unidad de cálculo (3).

FIG. 2

FIG. 1

FIG. 3