# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 449 620

61 Int. Cl.:

H03M 13/11 (2006.01) H03M 13/27 (2006.01) H04L 1/00 (2006.01) H03M 13/29 (2006.01) H03M 13/15 (2006.01)

12 TRADUCCIÓN DE PATENTE EUROPEA

T3

- 96 Fecha de presentación y número de la solicitud europea: 03.03.2010 E 10250372 (9)

97 Fecha y número de publicación de la concesión europea: 22.01.2014 EP 2234274

- (54) Título: Equipo de recepción, método de recepción, programa y sistema de recepción compatibles con DVB-T.2

- (30) Prioridad:

24.03.2009 JP 2009072161

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 20.03.2014

(73) Titular/es:

SONY CORPORATION (100.0%) 1-7-1 Konan, Minato-ku Tokyo, JP

(72) Inventor/es:

YOKOKAWA, TAKASHI y SHINYA, OSAMU

(74) Agente/Representante:

**LEHMANN NOVO, María Isabel**

#### **DESCRIPCIÓN**

Equipo de recepción, método de recepción, programa y sistema de recepción compatibles con DVB-T.2

La presente invención está relacionada con un equipo de recepción, un método de recepción, un programa y un sistema de recepción.

Los sistemas de comunicación, recurriendo a la codificación, llevan a cabo comunicaciones fiables sobre canales de comunicación afectados por el ruido. Por ejemplo, los sistemas inalámbricos como, por ejemplo, redes basadas en satélite están expuestos a numerosas fuentes de ruido debido a factores geográficos y medioambientales. Dichos canales de comunicación representan capacidades fijas que se definen en términos del número de bits por símbolo en una relación señal ruido (SNR) dada y que constituyen un límite superior teórico conocido como límite de Shannon. Como resultado, el diseño de la codificación tiene el objetivo de conseguir tasas próximas al límite de Shannon. Este objetivo está muy relacionado con los sistemas basados en satélite con ancho de banda limitado.

En los últimos años se ha presenciado el desarrollo de técnicas de codificación conocidas como codificación turbo que ayuda a conseguir niveles de rendimiento que se acercan al límite de Shannon. Específicamente, las técnicas desarrolladas incluyen Códigos Convolucionales Concatenados en Paralelo (PCCC) y Códigos Convolucionales Concatenados en Serie (SCCC). Además de estas técnicas de codificación turbo, en la actualidad reciben de nuevo atención los Códigos de Comprobación de Paridad de Baja Densidad (denominados de aquí en adelante codificación LDPC), una técnica de codificación tradicional conocida desde hace mucho tiempo.

15

30

35

45

La codificación LDPC fue propuesta por primera vez por R. G. Gallager en "Low Density Parity Check Codes (Códigos de Comprobación de Paridad de Baja Densidad)", Cambridge, Massachusetts: M. I. T. Press, 1963. Más tarde, la técnica recibió atención una vez más cuando se expuso ilustrativamente por parte de D. J. C. MacKay en "Good error correcting codes based on very sparse matrices (Buenos códigos de corrección de errores basados en matrices de paridad de baja densidad)", enviado a las Actas del IEEE de Teoría de la Información, IT-45, pág. 399-431, 1999 y por parte de M. G. Luby, M. Mitzenmacher, M. A. Shokrollahi y D. A Spielman en "Analysis of low density codes and improved designs using irregular graphs (Análisis de códigos de baja densidad y diseños mejorados utilizando gráficos irregulares) en las Actas del Simposio de la ACM sobre Teoría de la Computación, pág. 249-258, 1998.

Los estudios de los últimos años han aclarado cada vez más que la codificación LDPC, cuando se aumenta su longitud de código, proporciona niveles de rendimiento cercanos al límite de Shannon como la codificación turbo. Debido a que su distancia mínima es proporcional a su longitud de código, la codificación LDPC ofrece una excelente tasa de errores por bloque y produce pocos fenómenos de los denominados suelo de error, que se pueden observar en las características de decodificación mediante secuencias de codificación turbo.

Las ventajas de la codificación LDPC mencionadas más arriba han conducido a la adopción de esta técnica de codificación en el DVB (Difusión de Video Digital)-T.2 (DVB BlueBook (Libro Azul) A122 Rev. 1, codificación y modulación del canal de estructura de trama para un sistema de difusión de televisión terrestre digital de segunda generación (DVB, T2), recuperado el 17 de marzo de 2009 en la página Web de DVB fechado el 1 de septiembre de 2008 <URL: http://www.dvb.org/technology/standards/> (Documento No Patente 1)). Esto es, el DVB-T.2 es el estándar de difusión de TV terrestre digital de segunda generación sometido a estudio (en marzo de 2009) por el ETSI (Instituto Europeo de Estándares de Telecomunicación).

Existe la necesidad de que los receptores compatibles con DVB-T.2 lleven a cabo la decodificación LDPC de PLP (conexiones de capa física) y de L1 (capa 1) utilizando un único decodificador. Sin embargo, los receptores posibles todavía tienen que satisfacer adecuadamente esta necesidad.

Las PLP indican flujos de datos y L1 representa los parámetros de transmisión de la Capa 1 (la capa física) en DVB-T.2. Además de los parámetros de modulación y demodulación, L1 incluye la posición y tamaño de cada PLP y el sistema de corrección de errores que se utiliza. En el caso de múltiples PLP (denominado de aquí en adelante como multiPLP), las posiciones y tamaños de las PLP varían de una trama T2 a otra. Esto quiere decir que a menos que se tome L1, mediante un proceso de desentrelazado de frecuencia no se puede extraer cualquier PLP deseada. En DVB-T.2, la trama T2 es la unidad de transmisión de datos en la capa física. Así pues, la trama T2 está compuesta de símbolos P1 y P2 así como símbolos de datos que incluyen una PLP. La L1 se incluye en un símbolo P2 de cada trama T2. En el Documento No Patente 1 citado más arriba se divulgan de forma ilustrativa detalles de L1.

50 El documento ORGANIZACIÓN DE DVB: "T2\_0447\_DVB-T2\_Implementation\_Guide-lines\_0\_7\_2.doc", DVB, DIGITAL VIDEO BROADCASTING (DIFUSIÓN DE VÍDEO DIGITAL), C/O EBU – 17A ANCIENNE ROUTE – CH-1218 GRAND SACONNEX, GINEBRA – SUIZA, 4 de septiembre de 2008, páginas 1-167, está relacionado con las directrices de implementación para un sistema de difusión de televisión terrestre digital de segunda generación (dvb-t2)

55 El presente modo de realización se ha elaborado considerando las circunstancias citadas más arriba y proporciona

un equipo de recepción, un método de recepción, un programa y un sistema de recepción para permitir que un receptor compatible con DVB-T.2 realice una decodificación LDPC de PLP y L1 utilizando un único decodificador.

En las reivindicaciones adjuntas se definen algunos aspectos de la invención.

5

10

15

40

45

50

55

En la realización de la presente divulgación y de acuerdo con un ejemplo de la misma, se proporciona un equipo de recepción que incluye: un dispositivo de decodificación LDPC configurado de modo que cuando se transmite de forma multiplexada una señal de datos codificada con LDPC, significando LDPC Comprobación de Paridad de Baja Densidad, y una señal de control de transmisión codificada con LDPC, el dispositivo de decodificación LDPC puede decodificar tanto la señal de datos como la señal de control de transmisión; y un dispositivo de almacenamiento configurado para estar situado en el flujo de subida del dispositivo de decodificación LDPC y para almacenar al menos la señal de control de transmisión al recibir la señal de datos y la señal de control de transmisión. El equipo de recepción incluye, además, un dispositivo de control configurado para controlar que el dispositivo de decodificación LDPC decodifica la señal de datos mientras que la señal de control de transmisión está siendo acumulada en el dispositivo de almacenamiento y para interrumpir la decodificación actual con el fin de controlar que el dispositivo de decodificación LDPC decodifica la señal de control de transmisión cuando la señal de control de transmisión se ha acumulado en el dispositivo de almacenamiento.

Preferiblemente, la señal de control de transmisión y la señal de datos pueden haber experimentado un proceso de entrelazado de frecuencias; y el dispositivo de almacenamiento puede almacenar la señal de datos y la señal de control de transmisión al recibir ambas y puede llevar a cabo sobre la señal de datos y la señal de control de transmisión un proceso de desentrelazado de frecuencias correspondiente al proceso de entrelazado de frecuencias.

Preferiblemente, el equipo de recepción puede cumplir con el Estándar T2 de Difusión de Video Digital conocido como DVB-T.2; y la señal de control de transmisión puede ser una L1 incluida en un símbolo P2 especificado en el DVB-T.2.

De acuerdo con otros ejemplos de la presente divulgación, se proporcionan un método y un programa de recepción correspondientes al equipo de recepción que incorpora la invención tal como se ha descrito más arriba.

25 En los casos en los que se proporcionan tal como se ha descrito más arriba el equipo de recepción, el método de recepción y el programa de los presentes ejemplos, el equipo de recepción incluye: un dispositivo de decodificación LDPC (Comprobación de Paridad de Baia Densidad) configurado de modo que cuando se transmite de forma multiplexada una señal de datos codificada con LDPC y una señal de control de transmisión codificada con LDPC, el dispositivo de decodificación LDPC puede decodificar tanto la señal de datos como la señal de control de 30 transmisión; y un dispositivo de almacenamiento configurado para estar situado en el flujo de subida del dispositivo de decodificación LDPC y para almacenar al menos la señal de control de transmisión al recibir la señal de datos y la señal de control de transmisión. A continuación, el método o programa de recepción realizan el control para que el dispositivo de decodificación LDPC decodifique la señal de datos mientras que la señal de control de transmisión está siendo acumulada en el dispositivo de almacenamiento. El método o programa de recepción realizan, además, el control para interrumpir la decodificación actual para permitir que el dispositivo de decodificación LDPC 35 decodifique la señal de control de transmisión cuando la señal de control de transmisión ha sido ha acumulada en el dispositivo de almacenamiento.

De acuerdo con otro ejemplo de la presente divulgación, se proporciona un sistema de recepción que incluye: un dispositivo de adquisición configurado para obtener una señal de datos codificada con LDPC, significando LDPC Comprobación de Paridad de Baja Densidad, y una señal de control de transmisión codificada con LDPC cuando estas señales se transmiten de forma multiplexada sobre un canal predeterminado; y un dispositivo de decodificación de canal configurado para llevar a cabo un proceso de decodificación de canal sobre las señales obtenidas por el dispositivo de adquisición sobre el canal, incluyendo el proceso de decodificación de canal al menos un proceso de corrección de errores que se pueden haber producido en el canal, transmitiendo además el dispositivo de decodificación de canal las señales procesadas de este modo. El sistema de recepción incluye, además, o bien un dispositivo de procesamiento para decodificar fuentes de información configurado para llevar a cabo un proceso de decodificación de fuentes de información sobre las señales procedentes del dispositivo de decodificación de canal, o bien un dispositivo de grabación configurado para grabar en un medio de grabación las señales procedentes del dispositivo de decodificación de canal. El dispositivo de decodificación de canal incluye: un dispositivo de decodificación LDPC configurado para decodificar la señal de datos y la señal de control de transmisión; un dispositivo de almacenamiento configurado para estar situado en el flujo de subida del dispositivo de decodificación LDPC y para almacenar al menos la señal de control de transmisión al recibir la señal de datos y la señal de control de transmisión; y un dispositivo de control configurado para controlar que el dispositivo de decodificación LDPC decodifica la señal de datos mientras la señal de control de transmisión está siendo acumulada en el dispositivo de almacenamiento y para interrumpir la decodificación actual con el fin de controlar que el dispositivo de decodificación LDPC decodifica la señal de control de transmisión cuando la señal de control de transmisión ha sido acumulada en el dispositivo de almacenamiento.

En los casos en los que el sistema de recepción del presente ejemplo se proporciona tal como se ha descrito más arriba, el sistema incluye: un dispositivo de adquisición configurado para obtener una señal de datos codificada con LDPC (Comprobación de Paridad de Baja Densidad) y una señal de control de transmisión codificada con LDPC cuando estas señales se transmiten de forma multiplexada sobre un canal predeterminado; y un dispositivo de decodificación de canal configurado para llevar a cabo un proceso de decodificación de canal sobre las señales obtenidas por el dispositivo de adquisición sobre el canal, incluyendo el proceso de decodificación de canal al menos un proceso de corrección de errores que se pueden haber producido en el canal, transmitiendo además el dispositivo de decodificación de canal las señales procesadas de este modo. El sistema incluye, además, o bien un dispositivo de procesamiento para decodificar fuentes de información configurado para llevar a cabo un proceso de decodificación de fuentes de información sobre las señales procedentes del dispositivo de decodificación de canal, o bien un dispositivo de grabación configurado para grabar en un medio de grabación las señales procedentes del dispositivo de decodificación de canal. El dispositivo de decodificación de canal incluye un dispositivo de decodificación LDPC configurado para decodificar la señal de datos y la señal de control de transmisión y un dispositivo de almacenamiento configurado para estar situado en el flujo de subida del dispositivo de decodificación LDPC y para almacenar al menos la señal de control de transmisión al recibir la señal de datos y la señal de control de transmisión. El dispositivo de decodificación de canal se dispone para controlar que el dispositivo de decodificación LDPC decodifica la señal de datos mientras que la señal de control de transmisión está siendo acumulada en el dispositivo de almacenamiento. El dispositivo de decodificación de canal se dispone, además, para controlar que se interrumpe la decodificación actual con el fin de permitir que el dispositivo de decodificación LDPC decodifica la señal de control de transmisión cuando la señal de control de transmisión se ha acumulado en el dispositivo de almacenamiento.

De acuerdo con los presentes ejemplos tal como se han descrito más arriba, el receptor compatible con DVB-T.2 se prepara para llevar a cabo la decodificación LDPC de las PLP y L1 utilizando un único decodificador.

Preferiblemente, la divulgación está relacionada con un equipo de recepción, un método de recepción, un programa y un sistema de recepción para permitir que un receptor compatible con DVB-T.2 lleve a cabo la decodificación LDPC de las PLP y L1 utilizando un único decodificador.

En las reivindicaciones adjuntas se definen varios aspectos y características respectivos de la invención.

A continuación se describirán algunos modos de realización de la invención haciendo referencia a los dibujos adjuntos, a lo largo de los cuales las mismas partes se denominarán mediante las mismas referencias y en los que:

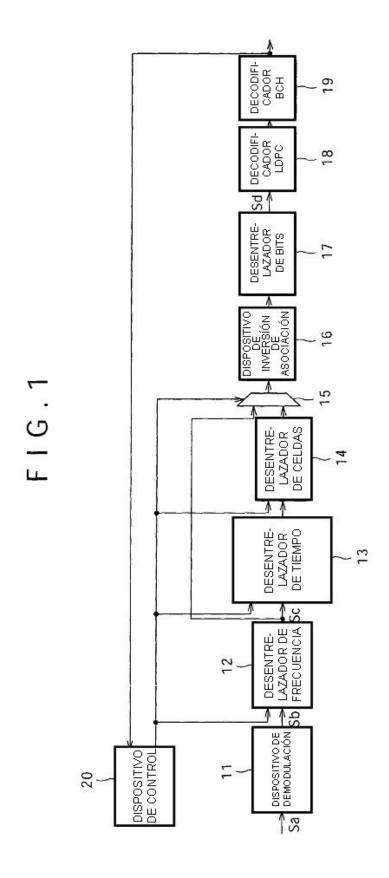

- 30 la Fig. 1 es una vista esquemática que muestra una estructura típica de un equipo de recepción siguiendo un modo de realización de la presente invención;

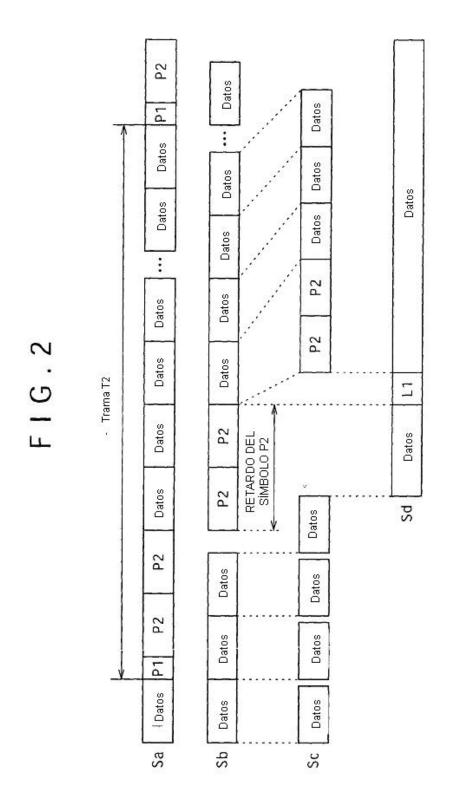

- la Fig. 2 es una vista esquemática explicativa de una planificación de funcionamiento típico de un equipo de recepción cuya estructura se muestra en la Fig. 1;

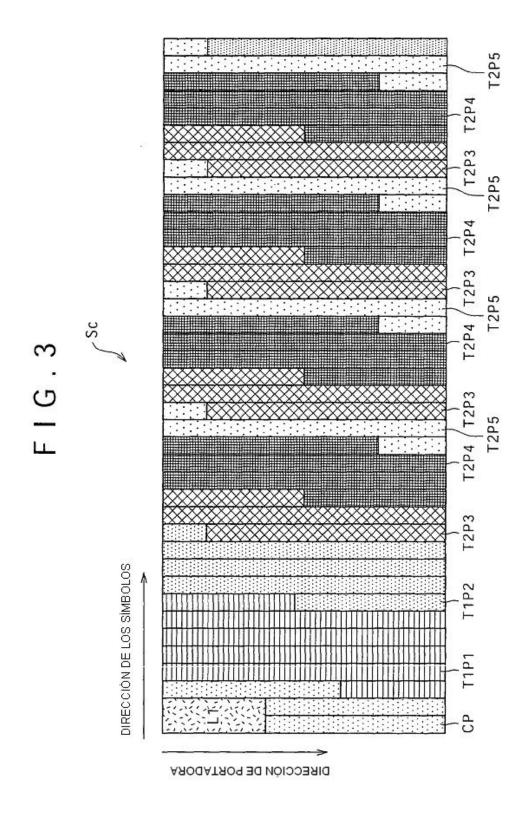

- la Fig. 3 es una vista esquemática que muestra una estructura típica de una señal de salida procedente de un desentrelazador de frecuencias en el modo multiPLP;

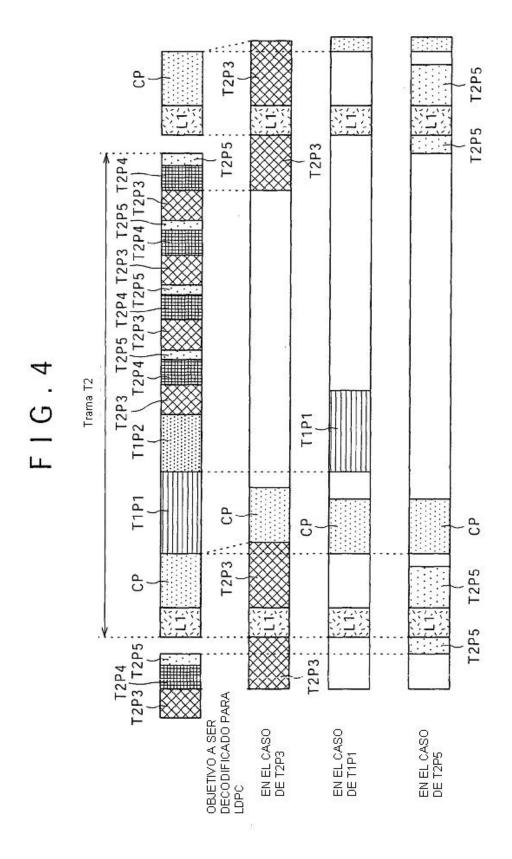

- la Fig. 4 es una vista esquemática que muestra una planificación típica de funcionamiento de decodificación LDPC en el modo multiPLP, ilustrando la vista cómo se planifica la decodificación en unidades de PLP;

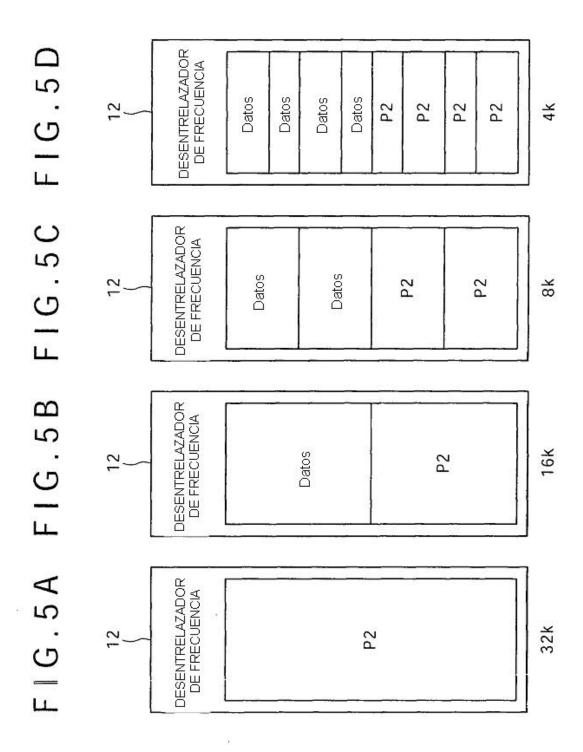

- las Fig. 5A, 5B, 5C y 5D son vistas aclaratorias de cómo se utiliza típicamente el desentrelazado de frecuencias del equipo de recepción de la Fig. 1;

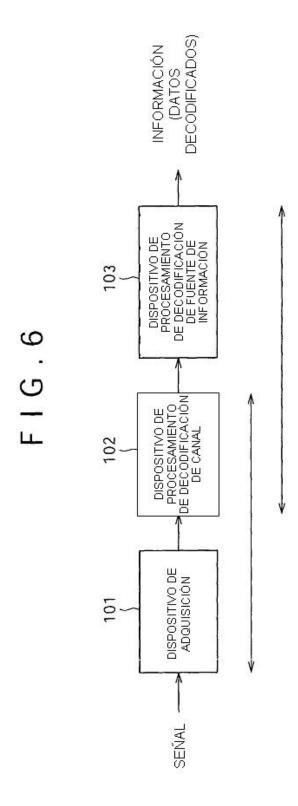

- 40 la Fig. 6 es un diagrama de bloques que muestra un primer ejemplo de estructura de un sistema de recepción aplicable al equipo de recepción de la Fig. 1;

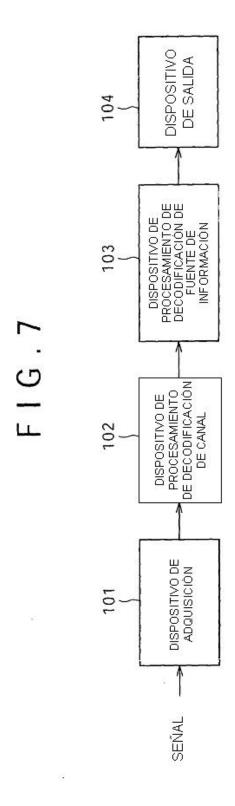

- la Fig. 7 es un diagrama de bloques que muestra un segundo ejemplo de estructura del sistema de recepción aplicable al equipo de recepción de la Fig. 1;

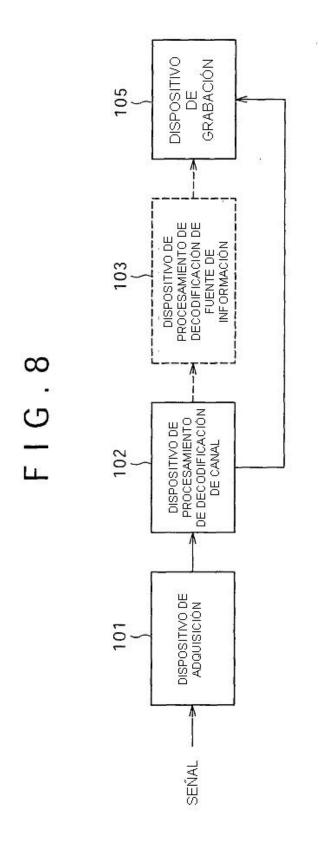

- la Fig. 8 es un diagrama de bloques que muestra un tercer ejemplo de estructura del sistema de recepción aplicable 45 al equipo de recepción de la Fig. 1; y

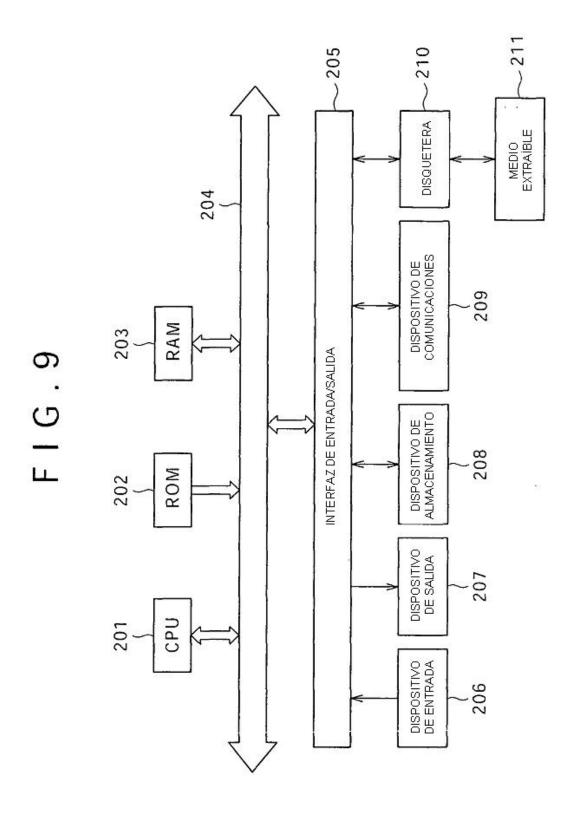

- la Fig. 9 es un diagrama de bloques que muestra una estructura hardware típica del equipo de recepción que refleja la presente invención.

- [Estructura del equipo de recepción que cumple con el DVB-T.2]

10

15

- La Fig. 1 muestra esquemáticamente una estructura típica de un equipo de recepción llevado a la práctica como un modo de realización preferido de la presente invención.

- En la difusión digital bajo el DVB-T.2, los códigos LDPC se convierten en símbolos de modulación ortogonal

(modulación digital) como, por ejemplo, QPSK (Modulación por Desplazamiento de Fase Cuaternaria), y estos símbolos se asocian a puntos de constelación antes de ser transmitidos. De forma ilustrativa, el equipo de recepción de la Fig. 1 adopta OFDM (Multiplexación por División de Frecuencia Ortogonal) como sistema de modulación para difusión digital.

- El equipo de recepción de la Fig. 1 funciona como un equipo de difusión digital que se ajusta al DVB-T.2. El equipo de recepción compatible con DVB-T.2 está estructurado para incluir un dispositivo 11 de demodulación, un desentrelazador 12 de frecuencia, un desentrelazador 13 de tiempo, un desentrelazador 14 de celda, un dispositivo 15 de conmutación, un dispositivo 16 de inversión de asociación, un desentrelazador 17 de bits, un decodificador 18 de LDPC, un decodificador 19 de BCH, y un dispositivo 20 de control.

- El equipo de recepción de la Fig. 1 recibe las ondas de difusión procedentes de una estación de difusión, que no se muestra. Dentro del equipo de recepción, un sintonizador o similar transforma las ondas de difusión recibidas en una señal Sa de IF (Frecuencia Intermedia), que no se muestra, reenviando la señal Sa de IF al dispositivo 11 de demodulación. Esto es, la señal Sa de IF se convierte en una señal de entrada para el dispositivo 11 de demodulación. El dispositivo 11 de demodulación demodula ortogonalmente la señal Sa de entrada en una señal OFDM de banda base que se envía como señal Sb de salida y se inyecta al desentrelazador 12 de frecuencia.

La señal Sb de salida del dispositivo 11 de demodulación se convierte en la señal de entrada del desentrelazador 12 de frecuencia. A su vez, el desentrelazador 12 de frecuencia lleva a cabo un proceso de desentrelazado de frecuencia sobre la señal Sb de entrada. Esto es, el desentrelazador 12 de frecuencia está diseñado para desentrelazar lo que se ha entrelazado de forma integrada en símbolos OFDM. El proceso de desentrelazado se lleva a cabo en unidades de celdas (en este ejemplo en unidades de portadoras OFDM).

20

35

40

45

50

55

Más específicamente, la señal Sb de entrada es una señal que se denomina señal OFDM del dominio de la frecuencia que ha sido sometida al cálculo de la FFT (Transformada Rápida de Fourier). En el proceso de desentrelazado de frecuencia, se utiliza un patrón pseudoaleatorio para conmutar posiciones de portadora en la señal Sb de entrada que es una señal OFDM del dominio de la frecuencia.

Tal como se ha mencionado más arriba, una trama T2 de acuerdo con el DVB-T.2 incluye símbolos P1 y P2 y símbolos de datos. De estos símbolos, el símbolo P1 se elimina al salir del dispositivo 11 de demodulación. De este modo la señal OFDM del dominio de la frecuencia constituida por símbolos P2 y datos se suministra al desentrelazador 12 de frecuencia como la señal de entrada Sb. Como resultado, el desentrelazador 12 de frecuencia produce una señal Sc de salida en forma de símbolos P2 desentrelazados en frecuencia (denominados de aquí en adelante simplemente como símbolos P2 cuando sea apropiado) y símbolos de datos desentrelazados en frecuencia (denominados de aquí en adelante simplemente símbolos de datos cuando sea apropiado).

Con este modo de realización, la señal de salida Sc del desentrelazador 12 de frecuencia se retrasa al menos un símbolo P2 con respecto a la señal de entrada Sb con el fin de permitir la decodificación LDPC de los códigos LDPC de la PLP y de la L1. En otras palabras, desde un punto de vista de la decodificación LDPC se considera que el desentrelazador 12 de frecuencia dispone de la función denominada almacenamiento intermedio. La función de almacenamiento intermedio se discutirá en detalle más adelante haciendo referencia a la Fig. 4 y a otros dibujos.

De los elementos de la señal Sc de salida procedente del desentrelazador 12 de frecuencia, el elemento de señal correspondiente a la PLP se inyecta al desentrelazador 13 de tiempo. Del resto de elementos de la señal Sc de salida, el elemento de señal correspondiente a la L1 (incluido en el símbolo P2) se reenvía al dispositivo 15 de conmutación.

La señal de salida del desentrelazador 12 de frecuencia y de entrada al desentrelazador 13 de tiempo ha sido sometida un proceso de entrelazado de bloques (proceso de entrelazado de tiempo) realizado a través de una pluralidad de códigos LDPC en el lado transmisor. Este proceso se lleva a cabo en unidades de celdas (en unidades de constelaciones en este ejemplo). De este modo, el desentrelazador 13 de tiempo lleva a cabo un proceso de desentrelazado correspondiente al proceso de entrelazado de tiempo sobre la señal de entrada y alimenta al desentrelazador 14 de celda con la señal resultante del proceso de desentrelazado.

La señal de salida del desentrelazador 13 de tiempo y de entrada del desentrelazador 14 de celda ha sido sometida un proceso de entrelazado (proceso de entrelazado de celdas) incorporado en los códigos LDPC en el lado transmisor. Este proceso se lleva a cabo en unidades de celdas (en unidades de constelaciones en este ejemplo). De este modo, el desentrelazador 14 de celda lleva a cabo un proceso de desentrelazado correspondiente al proceso de entrelazado de celda sobre la señal de entrada y alimenta al dispositivo 15 de conmutación con la señal resultante del proceso de desentrelazado.

En el modo descrito más arriba, se proporciona a la entrada del dispositivo 15 de conmutación una señal de control de transmisión correspondiente a la salida L1 procedente del desentrelazador 12 de frecuencia (la señal de control se denominará de aquí en adelante simplemente L1 cuando sea apropiado) y una señal de datos correspondiente a la salida PLP procedente del desentrelazador 14 de celda (la señal de datos se denominará de aquí en adelante

simplemente los datos cuando sea apropiado). Bajo el control del dispositivo 20 de control, el dispositivo 15 de conmutación selecciona como sus datos de salida o bien L1 o los datos.

Más específicamente, con este modo de realización en un estado normal bajo el control del dispositivo 20 de control, el dispositivo 15 de conmutación genera la entrada de datos que proceden del desentrelazador 14 de celda. Cuando L1 es enviada desde del desentrelazador 12 de frecuencia, el dispositivo 15 de conmutación bajo el control del dispositivo 20 de control genera L1 mediante el manejo de interrupciones. Esto es, cuando L1 es enviada desde el desentrelazador 12 de frecuencia, el dispositivo 20 de control interrumpe las operaciones del desentrelazador 13 de tiempo y del desentrelazador 14 de celda y permite que L1 llegue al decodificador 18 de LDPC a través del dispositivo 16 de inversión de asociación y del desentrelazador 17 de bits de modo que el decodificador 18 de LDPC somete L1 a la decodificación LDPC.

El dispositivo 16 de inversión de asociación convierte los datos de salida procedentes del dispositivo 15 de conmutación en datos codificados mediante LDPC en unidades de bits con signo y envía los datos convertidos al desentrelazador 17 de bits.

Los datos enviados desde el dispositivo 16 de inversión de asociación e inyectados al desentrelazador 17 de bits han sido sometidos un proceso de entrelazado de bits en unidades de bits con signo LDPC en el lado transmisor. De este modo el desentrelazador 17 de bits lleva a cabo un proceso de desentrelazado de bits sobre los datos de entrada para obtener un código LDPC con su bit de signo revertido a la posición que tenía antes del proceso de entrelazado de bits. La señal construida mediante dichos códigos LDPC se inyecta al decodificador 18 de LDPC como una señal Sd de salida del desentrelazador 17 de bits.

- Esto es, la señal Sd de salida procedente del desentrelazador 17 de bits se convierte en la señal de entrada del decodificador 18 de LDPC. El decodificador 18 de LDPC lleva a cabo a continuación un proceso de decodificación LDPC sobre la señal Sd de entrada utilizando una matriz de comprobación de la conversión generada a partir de la matriz de comprobación utilizada en el proceso de codificación LDPC en el lado transmisor. Los datos resultantes del proceso de decodificación LDPC alimentan al decodificador 19 de BCH.

- Los datos enviados desde el decodificador 18 de LDPC e inyectados al decodificador 19 de BCH han sido sometidos a un proceso de codificación BCH (Bose-Chaudhuri-Hocquenghem) como proceso de corrección de errores en el lado transmisor. De este modo, el decodificador 19 de BCH decodifica los datos codificados mediante BCH y envía al exterior los datos obtenidos en el proceso de decodificación.

- El dispositivo 20 de control controla las operaciones de los componentes comprendiendo desde el desentrelazador 12 de frecuencia al dispositivo 15 de conmutación típicamente basado en los datos de salida procedentes del decodificador 19 de BCH. De forma ilustrativa, el dispositivo 20 de control controla una serie de operaciones hasta la decodificación LDPC de acuerdo con la planificación de operaciones explicada más abajo.

[Planificación de operaciones del equipo de recepción adaptado al DVB-T.2]

10

45

50

La Fig. 2 es una vista esquemática que explica una planificación de operaciones típica del equipo de recepción cuya estructura se ilustra en la Fig. 1.

En la Fig. 2 se muestran diagramas de tiempo en unidades de símbolos con respecto a, de arriba abajo, la señal Sa de entrada hacia el dispositivo 11 de demodulación, la señal Sb de salida procedente del dispositivo 11 de demodulación, la señal Sc de salida procedente del desentrelazador 12 de frecuencia, y la señal Sd de salida (sometida a la decodificación LDPC) hacia el decodificador 18 de LDPC.

40 Con el propósito de simplificar e ilustrar, se supone que la señal Sd de salida en la Fig. 2 es una señal existente cuando no hay retardo en el desentrelazador 14 de celda, el dispositivo 16 de inversión de asociación y el desentrelazador 17 de bits.

Cada una de las tramas T2 (indicadas en la Fig. 2 como "trama T2") formadas por un símbolo P1 ("P1" en la Fig. 2), dos símbolos P2 ("P2" en la Fig. 2), y una pluralidad de símbolos de datos ("Datos" en la Fig. 2) son inyectadas sucesivamente al dispositivo 11 de demodulación como señal Sa de entrada.

A continuación, se elimina el símbolo P1 de la señal Sa de entrada y se retarda con la cantidad correspondiente a dos símbolos P2 para convertirse en la señal Sb que es enviada desde el dispositivo 11 de demodulación al desentrelazador 12 de frecuencia.

El desentrelazador 12 de frecuencia retarda la señal Sb de entrada la cantidad correspondiente a dos símbolos P2 para obtener la señal Sc, y envía la señal Sc resultante como la señal de salida.

La velocidad a la que la señal Sc de salida procedente del desentrelazador 12 de frecuencia se transmite al desentrelazador 13 de tiempo es mayor que la velocidad a la que la señal Sb de entrada se inyecta al desentrelazador 12 de frecuencia. Por esta razón, la magnitud del retardo de la señal Sc de salida procedente del

desentrelazador 12 de frecuencia con respecto a la señal Sb de entrada al desentrelazador 12 de frecuencia es equivalente a un símbolo en la última medición de tiempo de la trama T2.

De los elementos de la señal Sc de salida procedente del desentrelazador 12 de frecuencia, se proporcionan los datos PLP al desentrelazador 13 de tiempo y L1 (incluido en cada símbolo P2) se inyecta al dispositivo 15 de conmutación. Como resultado, el objetivo a decodificar por parte del decodificador 18 de LDPC es la señal Sd que se muestra en la Fig. 2. Esto es, cuando los símbolos de datos se han acumulado en el desentrelazador 13 de tiempo, se empieza a decodificar mediante LDPC el código LDPC de la PLP correspondiente (indicada como "Datos" en la señal Sd de la Fig. 2). Cuando L1 sale del desentrelazador 12 de frecuencia, se produce una interrupción y se lleva a cabo la decodificación LDPC de la L1. Esto es, el decodificador 18 de LDPC realiza la decodificación LDPC de la L1 en algún punto intermedio de la decodificación LDPC de los datos.

[Operación de decodificación LDPC en el modo multiPLP]

A continuación se describe la operación de decodificación LDPC en el modo multiPLP.

La Fig. 3 muestra de forma esquemática una estructura típica de la señal Sc de salida procedente del desentrelazador 12 de frecuencia en el modo multiPLP.

15 En la Fig. 3 cada columna representa un símbolo.

10

25

30

35

40

45

La señal Sc de salida en la Fig. 3 está compuesta por una L1 y una pluralidad de PLP.

En el ejemplo de la Fig. 3 existen las siguientes PLP: una PLP común (de aquí en adelante denominada CP), una PLP(1) de Tipo 1 (de aquí en adelante denominada T1P1) y una PLP(2) de Tipo 1 (de aquí en adelante denominada T1P2).

En el mismo ejemplo también existen otras PLP: una PLP(3) de Tipo 2 (de aquí en adelante denominada T2P3), una PLP(4) de Tipo 2 (de aquí en adelante denominada T2P4), y una PLP(5) de Tipo 2 (de aquí en adelante denominada T2P5). En la Fig. 3 se muestra cada una de las T2P3, T2P4 y T2P5 divididas en cuatro porciones.

En el modo multiPLP, a partir de dichas PLP múltiples se extraen las PLP deseadas (hasta dos PLP) y se decodifican mediante LDPC. Se debe observar que CP se decodifica siempre mediante LDPC. De este modo, además de la CP, también es objeto de decodificación LDPC una PLP deseada de entre las siguientes: T1P1, T1P2, T2P3, T2P4 y T2P5.

La Fig. 4 muestra de forma esquemática una planificación de operación típica de una decodificación LDPC en modo multiPLP, ilustrando la vista cómo se planifica la decodificación, típicamente, en unidades de PLP.

En la parte superior de la Fig. 4 se muestra un diagrama de tiempo de lo que se lee procedente del desentrelazador 12 de frecuencia en unidades de PLP.

En segundo lugar desde la parte superior de la Fig. 4 se encuentra un diagrama de tiempo aplicable cuando la CP y la T2P3 se someten a decodificación LDPC. En este caso, durante la decodificación LDPC de T2P3 de la trama T2 anterior, se produce una interrupción y se decodifica mediante LDPC la L1 de la trama T2 actual (mostrada en la parte superior de la Fig. 4). Cuando finaliza la decodificación LDPC de la L1, se reanuda la decodificación LDPC de la T2P3. Al final de la decodificación LDPC de la T2P3, se reanuda la decodificación LDPC de la CP en la trama T2 actual.

En tercer lugar desde la parte superior de la Fig. 4 se encuentra un diagrama de tiempo aplicable cuando la CP y la T1P1 se someten a decodificación LDPC. En este caso, se decodifican mediante LDPC sucesivamente la L1, la CP y la T1P1 de la trama T2 actual. Esto es, durante la decodificación LDPC de una PLP no tiene lugar ninguna interrupción para la decodificación LDPC de la L1.

En cuarto lugar desde la parte superior de la Fig. 4, esto es, en la parte inferior de la Fig. 4, se encuentra un diagrama de tiempo aplicable cuando la CP y la T2P5 se someten a decodificación LDPC. En este caso, durante la decodificación LDPC de la T2P5 en la trama T2 anterior, se produce una interrupción y se decodifica mediante LDPC la L1 de la trama T2 actual (mostrada en la parte superior de la Fig. 4). Cuando termina la decodificación LDPC de la L1, se reanuda la decodificación LDPC de la T2P5. Al final de la decodificación LDPC de la T2P5, se reanuda la decodificación LDPC de la CP en la trama T2 actual.

[Cómo utilizar el desentrelazador de frecuencia]

Más abajo se describe cómo se utiliza típicamente el desentrelazador 12 de frecuencia.

Tal como se ha expuesto más arriba, en cada símbolo P2 se incluye la L1. De este modo, antes de que se produzca la decodificación LDPC de la L1, el desentrelazador 12 de frecuencia necesita acumular todos los símbolos P2.

Durante la decodificación LDPC de la L1, el desentrelazador 12 de frecuencia también necesita acumular los símbolos de datos procedentes del dispositivo 11 de demodulación.

El desentrelazador 12 de frecuencia tiene que tener un tamaño lo suficientemente grande como para poder procesar una FFT de 32k puntos. Cuando se adopta una FFT de 16k, 8k, 4k, 2k ó 1k puntos, el desentrelazador 12 de frecuencia puede aceptar datos equivalentes a 2, 4, 8, 16 ó 32 símbolos en tamaño.

5

15

25

40

45

50

Bajo el DVB-T.2, en el caso de 32k ó 16k puntos el número de símbolos P2 es uno. En el caso de 8k puntos el número de símbolos P2 es el doble; en el caso de 4k puntos el número de símbolos P2 se multiplica por cuatro; y así sucesivamente.

Esto es, el desentrelazador 12 de frecuencia da cabida a tantos símbolos de datos como el número de símbolos P2 en el caso de 16k puntos o menos.

En el caso de 32k puntos, se utilizan alternativamente los patrones de entrelazado colocados entre sí en secuencia. Esto significa que la decodificación LDPC de la L1 tiene que terminarse y la lectura de los datos tiene que iniciarse antes de iniciar la escritura del siguiente símbolo.

En el caso de 16k puntos o menos, se utiliza un único patrón de entrelazado. Esto significa que la lectura de un dominio dado tiene que completarse antes del inicio de la escritura de dicho dominio.

Como se entiende a partir de lo que se ha expuesto más arriba, la función de almacenamiento intermedio del desentrelazador 12 de frecuencia funciona tal y como se muestra en las Fig. 5A a 5D.

Las Fig. 5A a 5D son vistas aclaratorias de la función de almacenamiento intermedio del desentrelazador 12 de frecuencia.

20 En el caso de 32k puntos, el desentrelazador 12 de frecuencia puede alojar datos equivalentes a un símbolo tal como se muestra en la Fig. 5A. En este caso, en el desentrelazador 12 de frecuencia se puede mantener un símbolo P2.

En el caso de 16k puntos, el desentrelazador 12 de frecuencia puede alojar datos equivalentes a dos símbolos tal como se muestra en la Fig. 5B. En este caso, en el desentrelazador 12 de frecuencia se pueden mantener un símbolo P2 y un símbolo de datos.

En el caso de 8k puntos, el desentrelazador 12 de frecuencia puede alojar datos equivalentes a cuatro símbolos tal como se muestra en la Fig. 5C. En este caso, en el desentrelazador 12 de frecuencia se pueden mantener dos símbolos P2 y dos símbolos de datos.

En el caso de 4k puntos, el desentrelazador 12 de frecuencia puede alojar datos equivalentes a ocho símbolos tal como se muestra en la Fig. 5D. En este caso, en el desentrelazador 12 de frecuencia se pueden mantener cuatro símbolos P2 y cuatro símbolos de datos.

En el caso de 2k ó 1k puntos, que no se muestra, el desentrelazador 12 de frecuencia puede alojar tantos símbolos de datos como símbolos P2.

[Recapitulación de la descripción anterior del equipo de recepción que materializa la presente invención]

Para recapitular lo que se ha descrito más arriba, el equipo de recepción de la Fig. 1 es un dispositivo de demodulación compatible con el DVB-T.2 que utiliza mediante tiempo compartido un único dispositivo de decodificación LDPC para la decodificación LDPC de L1 y PLP.

Desde un punto de vista de decodificación LDPC, el desentrelazador 12 de frecuencia posee la funcionalidad de almacenamiento intermedio. Esto es, en los casos que no son de 32k puntos, el desentrelazador 12 de frecuencia se utiliza como una memoria intermedia correspondiente a una pluralidad de símbolos. En tales casos, el desentrelazador 12 de frecuencia aloja no únicamente símbolos P2, sino también tantos símbolos de datos como sea posible. Esto puede ahorrar tiempo hasta la terminación de la decodificación LDPC de la L1.

El desentrelazador 13 de tiempo tiene que leer los datos procedentes del desentrelazador 12 de frecuencia tan pronto como la escritura de datos de este último haya terminado. Al mismo tiempo, la decodificación LDPC de L1 tiene que iniciarse tan pronto como sea posible de modo que se haya completado la decodificación antes de que los símbolos P2 escritos al desentrelazador 12 de frecuencia sean sobrescritos con los símbolos siguientes. Por esta razón, el dispositivo 20 de control ejerce el control de interrupción con el objeto de detener la decodificación LDPC de una PLP.

Más específicamente, el dispositivo 20 de control interrumpe las operaciones del desentrelazador 13 de tiempo y del desentrelazador 14 de celda para el control de interrupción. La detención de la decodificación LDPC de la PLP en

algún punto intermedio debido al control de interrupción destruye los datos que están siendo procesados. Esto obliga a que el dispositivo 20 de control lleve a cabo, de nuevo, un control de lectura mediante el desentrelazador 13 de tiempo y el desentrelazador 14 de celda una vez completada la decodificación LDPC de la L1.

En el modo multiPLP, la decodificación LDPC se realiza de acuerdo con la planificación mostrada en la Fig. 2 o en la Fig. 4. Esto es, el dispositivo 16 de inversión de asociación, el desentrelazador 17 de bits, el decodificador 18 de LDPC y el decodificador 19 de BCH se comparten en el tiempo con el fin de llevar a cabo la decodificación LDPC de la L1, las PLP comunes (CP en las Fig. 3 y 4) y las PLP de datos (T1P1, T1P2, T2P3, T2P4, T2P5). Como resultado, un dispositivo de decodificación LDPC puede sustituir hasta un máximo de tres dispositivos de decodificación LDPC que se necesitaban tradicionalmente.

10 [Estructura del sistema de recepción]

5

15

20

25

30

35

45

La Fig. 6 es un diagrama de bloques que muestra un primer ejemplo de estructura del sistema de recepción aplicable al equipo de recepción de la Fig. 1.

En la Fig. 6, el sistema de recepción está constituido por un dispositivo 101 de adquisición, un dispositivo 102 de procesamiento de decodificación de canal, y un dispositivo 103 de procesamiento de decodificación de fuente de información.

El dispositivo 101 de adquisición obtiene una señal que incluye al menos códigos LDPC obtenidos mediante datos objetivos codificados con LDPC como, por ejemplo, datos de vídeo y audio de programas de difusión. De forma ilustrativa, el dispositivo 101 de adquisición obtiene la señal de canales como, por ejemplo, difusiones terrestres digitales, difusiones de satélite digitales, redes de CATV (Televisión por Cable), y otras redes que incluyen Internet, que no se muestra, y proporciona la señal obtenida al dispositivo 102 de procesamiento de decodificación de canal.

Cuando la señal obtenida por el dispositivo 101 de adquisición se ha emitido, por ejemplo, a través de estaciones de difusión que utilizan ondas terrestres, ondas por satélite o redes de CATV, el dispositivo 101 de adquisición está constituido, típicamente, por un sintonizador externo (STB) o similar. Cuando la señal obtenida por el dispositivo 101 de adquisición es emitida en multidifusión por parte de servidores web en forma de IPTV (Televisión sobre el Protocolo de Internet), el dispositivo 101 de adquisición está constituido, por ejemplo, por una interfaz (I/F) de red como, por ejemplo, una tarjeta (NIC) de interfaz de red.

El dispositivo 102 de procesamiento de decodificación de canal lleva a cabo un procesamiento de decodificación de canal que incluye al menos un proceso de corrección de errores que se pueden haber producido en los canales en la señal obtenida por parte del dispositivo 101 de adquisición procedente de los canales. El dispositivo 102 de procesamiento de decodificación de canal reenvía la señal procesada de este modo al dispositivo 103 de procesamiento de decodificación de fuente de información.

La señal obtenida a partir del dispositivo 101 de adquisición ha sido sometida al menos a una codificación con corrección de errores con el objetivo de corregir cualquier error que se pueda haber producido en los canales. De este modo el dispositivo 102 de procesamiento de decodificación de canal realiza sobre la señal obtenida un procesamiento de decodificación de canal como, por ejemplo, decodificación de corrección de errores.

Las técnicas de codificación de corrección de errores típicas incluyen la codificación LDPC y la codificación Reed-Solomon. Con este modo de realización, se asume que al menos se realiza la codificación LDPC.

El procesamiento de decodificación de canal puede incluir la demodulación de señales moduladas.

Sobre la señal que se ha sometido al procesamiento de decodificación de canal, el dispositivo 103 de procesamiento de decodificación de fuente de información lleva a cabo el procesamiento de decodificación de fuente de información que incluye al menos un proceso de descompresión de información comprimida.

La señal obtenida por el dispositivo 101 de adquisición procedente de los canales puede haber sido sometida a una codificación con compresión para reducir la cantidad requerida de datos de vídeo y audio. En ese caso, el dispositivo 103 de procesamiento de decodificación de fuente de información lleva a cabo un procesamiento de decodificación de fuente de información comprimida sobre la señal que ha sido sometida al procesamiento de decodificación de canal.

Si la señal obtenida por el dispositivo 101 de adquisición procedente de los canales no ha sido sometida a una codificación con compresión, entonces el dispositivo 103 de procesamiento de decodificación de fuente de información no descomprime la información comprimida.

Las técnicas de descompresión típicas incluyen la decodificación MPEG (Grupo de Expertos de Imágenes en Movimiento). El procesamiento de decodificación de canal también puede incluir, además de la descompresión, descodificación de los datos.

En el sistema de recepción estructurado tal como se ha descrito más arriba, el dispositivo 101 de adquisición obtiene la señal constituida típicamente por datos de vídeo y audio que ha sido sometida a una codificación con compresión como, por ejemplo, codificación MPEG así como una codificación con corrección de errores como, por ejemplo, una codificación LDPC. La señal obtenida de este modo es enviada al dispositivo 102 de procesamiento de decodificación de canal.

5

10

35

El dispositivo 102 de procesamiento de decodificación de canal lleva a cabo como procesamiento de decodificación de canal los mismos procesos que los realizados por los componentes que comprenden desde el dispositivo 11 de demodulación al decodificador 19 de BCH sobre la señal procedente del dispositivo 101 de adquisición. La señal resultante del procesamiento de decodificación de canal es enviada al dispositivo 103 de procesamiento de decodificación de fuente de información.

El dispositivo 103 de procesamiento de decodificación de fuente de información lleva a cabo un procesamiento de decodificación de fuente de información como, por ejemplo, una decodificación MPEG sobre la señal procedente del dispositivo 102 de procesamiento de decodificación de canal. A continuación se envían las imágenes y/o sonidos resultantes del procesamiento de decodificación de fuente de información.

15 El sistema de recepción de la Fig. 6 descrito más arriba se puede aplicar, por ejemplo, a sintonizadores de TV o similares para recibir emisiones de TV digital.

El dispositivo 101 de adquisición, el dispositivo 102 de procesamiento de decodificación de canal y el dispositivo 103 de procesamiento de decodificación de fuente de información pueden estar organizados, cada uno de ellos, como un dispositivo independiente (hardware como, por ejemplo, IC (circuitos integrados)) o un módulo software.

Se puede establecer como un dispositivo independiente un conjunto de al menos dos dispositivos de entre el dispositivo 101 de adquisición, el dispositivo 102 de procesamiento de decodificación de canal y el dispositivo 103 de procesamiento de decodificación de fuente de información. Uno de dichos conjuntos puede estar compuesto, por ejemplo, por el dispositivo 101 de adquisición y por el dispositivo 102 de procesamiento de decodificación de canal. Otro conjunto puede estar formado por el dispositivo 102 de procesamiento de decodificación de canal y el dispositivo 103 de procesamiento de decodificación, el dispositivo 102 de procesamiento de decodificación de canal y el dispositivo 103 de procesamiento de decodificación de fuente de información.

La Fig. 7 es un diagrama de bloques que muestra un segundo ejemplo de estructura del sistema de recepción aplicable al equipo de recepción de la Fig. 1.

30 En la Fig. 7 los componentes cuyos equivalentes se encuentran en la Fig. 6 se designan mediante números de referencia equivalentes y cuando sea adecuado se omitirán sus descripciones.

El sistema de recepción de la Fig. 7 tiene en común con el de la Fig. 6 que el sistema incluye el dispositivo 101 de adquisición, el dispositivo 102 de procesamiento de decodificación de canal y el dispositivo 103 de procesamiento de decodificación de fuente de información. Lo que hace que el sistema de recepción de la Fig. 7 sea distinto del de la Fig. 6 es que el sistema incluye un nuevo dispositivo 104 de salida añadido.

El dispositivo 104 de salida puede estar constituido por un dispositivo de visualización para mostrar las imágenes y/o por altavoces para emitir los sonidos. Así pues, el dispositivo 104 de salida sirve para producir imágenes y sonidos derivados de la señal de salida procedente del dispositivo 103 de procesamiento de decodificación de fuente de información. Esto es, el dispositivo 104 de salida muestra imágenes y/o emite sonidos.

40 El sistema de recepción de la Fig. 7 descrito más arriba se puede aplicar, por ejemplo, a aparatos de TV para recibir emisiones de TV digital o receptores de radio o equivalentes para recibir emisiones de radio.

Se debe observar que si la señal obtenida por el dispositivo 101 de adquisición no ha sido sometida a codificación con compresión, entonces la señal de salida del dispositivo 102 de procesamiento de decodificación de canal es enviada directamente al dispositivo 104 de salida.

La Fig. 8 es un diagrama de bloques que muestra un tercer ejemplo de estructura del sistema de recepción aplicable al equipo de recepción de la Fig. 1.

En la Fig. 8, los componentes cuyos equivalentes se encuentran en la Fig. 6 se designan mediante números de referencia equivalentes y cuando resulte apropiado se omitirán sus descripciones.

El sistema de recepción de la Fig. 8 tiene en común con el de la Fig. 6 que el sistema incluye el dispositivo 101 de adquisición y el dispositivo 102 de procesamiento de decodificación de canal.

Lo que hace que el sistema de recepción de la Fig. 8 sea diferente del de la Fig. 6 es que el sistema no está equipado con el dispositivo 103 de procesamiento de decodificación de fuente de información e incluye un nuevo

dispositivo 105 de grabación.

10

25

30

50

El dispositivo 105 de grabación graba (es decir, almacena) la señal de salida procedente del dispositivo 102 de procesamiento de decodificación de canal (como, por ejemplo, paquetes TS en el formato MPEG) en un medio de grabación (almacenamiento) como, por ejemplo, discos ópticos, discos duros (discos magnéticos) o memorias flash.

5 El sistema de recepción de la Fig. 8 descrito más arriba se puede aplicar, por ejemplo, a equipos de grabación o similares para grabar emisiones de TV.

En la Fig. 8, el sistema de recepción se puede estructurar para incluir el dispositivo 103 de procesamiento de decodificación de fuente de información de modo que la señal que ha sido sometida al procesamiento de decodificación de fuente de información, esto es, decodificación de imágenes y sonidos, puede ser registrada por parte del dispositivo 105 de grabación.

[Aplicación del presente modo de realización a programas]

El conjunto de los procesos descritos más arriba pueden ser ejecutados bien mediante hardware o bien mediante software.

En dichos casos, al menos parte del sistema de recepción que incluye el equipo de recepción descrito más arriba puede estar constituido, por ejemplo, en forma de un ordenador que se muestra en la Fig. 9.

En la Fig. 9, una CPU (unidad central de procesamiento) 201 realiza varios procesos de acuerdo con los programas cargados en una ROM (memoria de sólo lectura) 202 o de acuerdo con los programas cargados en una RAM (memoria de acceso aleatorio) 203 desde un dispositivo 208 de almacenamiento. La RAM 203 también puede contener los datos requeridos por la CPU 201 para ejecutar los distintos procesos.

20 La CPU 201, la ROM 202, y la RAM 203, están interconectadas mediante un bus 204. Al bus 204 también se encuentra conectada una interfaz 205 de entrada/salida.

La interfaz 205 de entrada/salida está conectada con un dispositivo 206 de entrada compuesto típicamente por un teclado y un ratón y un dispositivo 207 de salida constituido, por ejemplo, por una unidad de visualización. La interfaz 205 de entrada/salida está conectada, además, con un dispositivo 209 de comunicación formado típicamente por un modem o un adaptador de terminal. El dispositivo 209 de comunicación controla las comunicaciones con otros dispositivos (que no se muestran) a través de redes que incluyen Internet.

Según sea necesario, también se encuentra conectado un disco 210 a la interfaz 205 de entrada/salida. En el disco 210 se puede cargar un elemento de medios extraíbles 211 como, por ejemplo, discos magnéticos, discos ópticos, discos magnetoópticos o memorias de semiconductor. En el dispositivo 208 de almacenamiento se instalan según sea necesario los programas de ordenador recuperados del medio extraíble cargado.

Cuando los procesos descritos más arriba se realizan mediante software, los programas que constituyen el software pueden bien encontrarse incorporados de antemano en el hardware dedicado del ordenador para su utilización o bien instalarse desde una red o un medio de grabación en un ordenador personal de propósito general o equipamiento similar capaz de ejecutar las distintas funciones de acuerdo con los programas instalados.

Tal como se muestra en la Fig. 9, el medio de almacenamiento que contiene los programas en él se ofrece a los usuarios no únicamente como medios extraíbles (medios de paquetes) 211 independiente de sus ordenadores y formados por discos magnéticos (incluyendo discos flexibles) que incluyen el programa, discos ópticos (incluyendo CD-ROM (memoria de disco compacto de solo lectura) y DVD (disco digital versátil)), discos magnetoópticos (incluyendo MD (mini-discos)), o memorias de semiconductor; sino también en forma de la ROM 202 o el disco duro contenido en el dispositivo 208 de almacenamiento, conteniendo cada uno de ellos los programas e incorporados en los ordenadores de antemano.

En esta especificación, los pasos que describen los programas almacenados en los medios de grabación representan no solo los procesos que se van a realizar en la secuencia descrita (esto es, basándose en una serie temporal) sino que también se pueden ejecutar procesos en paralelo o de forma individual y no cronológicamente.

Hasta el momento como los modos de realización de la invención descritos más arriba se implementan, al menos en parte, utilizando un equipo de procesamiento de datos controlado por software, se apreciará que un programa de ordenador que proporcione dicho control software y una transmisión, almacenamiento u otro medio mediante el cual se proporcione dicho programa de ordenador se consideran aspectos de la presente invención.

En esta especificación, el término "sistema" se refiere a una configuración completa formada por una pluralidad de dispositivos componentes y elementos de procesamiento.

Aquellos experimentados en la técnica deben entender que se pueden realizar varias modificaciones,

combinaciones, subcombinaciones o alteraciones en función de los requisitos de diseño y otros factores en la medida que se encuentren dentro del alcance de las reivindicaciones adjuntas.

#### **REIVINDICACIONES**

1. Un equipo de recepción que cumple con el Estándar T.2 de Difusión de Vídeo Digital conocido como DVB-T.2, estando configurado el equipo para llevar a cabo una decodificación con Comprobación de Paridad de Baja Densidad (LDPC) de conexiones de capa física (PLP) que representan flujos de datos, y de capa 1 (L1) que representan parámetros de transmisión de la capa física, comprendiendo el equipo:

un dispositivo (18) de decodificación LDPC configurado de tal modo que cuando se transmiten de modo multiplexado una señal de datos codificada con LDPC y una señal de control de transmisión codificada con LDPC, dicho dispositivo de decodificación LDPC puede decodificar tanto la señal de datos como la señal de control de transmisión en modo de tiempo compartido:

un dispositivo de almacenamiento configurado para colocarse en el flujo de subida de dicho dispositivo de decodificación LDPC y para mantener al menos dicha señal de control de transmisión al recibir dicha señal de datos y dicha señal de control de transmisión; y

un dispositivo de control configurado para controlar que dicho dispositivo de decodificación LDPC decodifica dicha señal de datos mientras que dicha señal de control de transmisión está siendo acumulada en dicho dispositivo de almacenamiento y para interrumpir la decodificación de la señal de datos correspondiente a una trama anterior con el fin de controlar que dicho dispositivo de decodificación LDPC comience a decodificar dicha señal de control de transmisión de una trama actual cuando dicha señal de control de transmisión se ha acumulado en dicho dispositivo de almacenamiento.

en donde:

dicha señal de datos es una PLP y dicha señal de control de transmisión es una L1 incluida en un símbolo P2 especificado por dicho DVB-T.2;

dicha señal de control de transmisión y dicha señal de datos han sido sometidas a un proceso de entrelazamiento de frecuencia:

dicho dispositivo de almacenamiento se puede utilizar para almacenar dicha señal de datos y dicha señal de control de transmisión al recibir las mismas y para llevar a cabo un proceso de desentrelazado de frecuencia correspondiente a dicho proceso de entrelazado de frecuencia sobre dicha señal de datos y dicha señal de control de transmisión;

el dispositivo de decodificación está configurado para reanudar la decodificación de la señal de datos después de haber terminado la decodificación LDPC de la señal de control de transmisión de la trama actual.

2. Un método de recepción para utilizar con un equipo de recepción que cumpla con el Estándar T.2 de Difusión de Vídeo Digital conocido como DVB-T.2, estando configurado el equipo para llevar a cabo una decodificación con Comprobación de Paridad de Baja Densidad (LDPC) de conexiones de capa física (PLP) que representan flujos de datos, y de capa 1 (L1) que representan parámetros de transmisión de la capa física, y comprendiendo el equipo:

un dispositivo de decodificación LDPC configurado de tal modo que cuando se transmiten de modo multiplexado una señal de datos codificada con LDPC y una señal de control de transmisión codificada con LDPC, dicho dispositivo de decodificación LDPC puede decodificar tanto la señal de datos como la señal de control de transmisión en modo de tiempo compartido;

un dispositivo de almacenamiento configurado para colocarse en el flujo de subida de dicho dispositivo de decodificación LDPC y para almacenar al menos dicha señal de control de transmisión al recibir dicha señal de datos y dicha señal de control de transmisión,

comprendiendo dicho método de recepción los pasos de:

controlar dicho dispositivo de decodificación LDPC para decodificar dicha señal de datos mientras que dicha señal de control de transmisión está siendo acumulada en dicho dispositivo de almacenamiento; e

interrumpir la decodificación de la señal de datos correspondiente a una trama anterior con el fin de controlar que dicho dispositivo de decodificación LDPC comience a decodificar dicha señal de control de transmisión de una trama actual cuando dicha señal de control de transmisión se ha acumulado en dicho dispositivo de almacenamiento; y

reanudar la decodificación de la señal de datos después de haber terminado la decodificación LDPC de la señal de control de transmisión de la trama actual.

13

20

5

10

15

25

35

40

45

en donde:

dicha señal de datos es una PLP y dicha señal de control de transmisión es una L1 incluida en un símbolo P2 especificado por dicho DVB-T.2;

dicha señal de control de transmisión y dicha señal de datos han sido sometidas a un proceso de entrelazado de frecuencia;

el método comprende almacenar dicha señal de datos y dicha señal de control de transmisión cuando se reciban las mismas y llevar a cabo un proceso de desentrelazado de frecuencia correspondiente a dicho proceso de entrelazado de frecuencia sobre dicha señal de datos y dicha señal de control de transmisión.

3. Un programa para un ordenador que controla un equipo de recepción que cumple con el Estándar T.2 de Difusión de Vídeo Digital conocido como DVB-T.2, estando configurado el equipo para llevar a cabo una decodificación con Comprobación de Paridad de Baja Densidad (LDPC) de conexiones de capa física (PLP) que representan flujos de datos, y de capa 1 (L1) que representan parámetros de transmisión de la capa física, y comprendiendo el equipo:

un dispositivo (18) de decodificación LDPC configurado de tal modo que cuando se transmiten de modo multiplexado una señal de datos codificada con LDPC y una señal de control de transmisión codificada con LDPC, dicho dispositivo de decodificación LDPC puede decodificar tanto la señal de datos como la señal de control de transmisión en modo de tiempo compartido; y

un dispositivo de almacenamiento configurado para colocarse en el flujo de subida de dicho dispositivo de decodificación LDPC y para almacenar al menos dicha señal de control de transmisión al recibir dicha señal de datos y dicha señal de control de transmisión, provocando dicho ordenador la ejecución de un proceso de control que comprende los pasos de:

controlar dicho dispositivo de decodificación LDPC para decodificar dicha señal de datos mientras que dicha señal de control de transmisión está siendo acumulada en dicho dispositivo de aloiamiento: e

interrumpir la decodificación de la señal de datos correspondiente a una trama anterior con el fin de controlar que dicho dispositivo de decodificación LDPC comience a decodificar dicha señal de control de transmisión de una trama actual cuando dicha señal de control de transmisión se ha acumulado en dicho dispositivo de almacenamiento; y

reanudar la decodificación de la señal de datos después de haber terminado la decodificación LDPC de la señal de control de transmisión de la trama actual.

en donde:

dicha señal de datos es una PLP y dicha señal de control de transmisión es una L1 incluida en un símbolo P2 especificado por dicho DVB-T.2;

dicha señal de control de transmisión y dicha señal de datos han sido sometidas a un proceso de entrelazado de frecuencia;

el proceso de control comprende almacenar dicha señal de datos y dicha señal de control de transmisión cuando se reciban las mismas y realizar un proceso de desentrelazado de frecuencia correspondiente a dicho proceso de entrelazado de frecuencia sobre dicha señal de datos y dicha señal de control de transmisión;

4. Un sistema de recepción que cumple con el Estándar T.2 de Difusión de Vídeo Digital conocido como DVB-T.2, estando configurado el equipo para llevar a cabo una decodificación con Comprobación de Paridad de Baja Densidad (LDPC) de conexiones de capa física (PLP) que representan flujos de datos, y de capa 1 (L1) que representan parámetros de transmisión de la capa física, comprendiendo el sistema:

un dispositivo (101) de adquisición configurado para adquirir una señal de datos codificada con LDPC y una señal de control de transmisión codificada con LDPC cuando estas señales se transmiten de modo multiplexado sobre un canal predeterminado;

un dispositivo (102) de decodificación de canal configurado para realizar un proceso de decodificación de canal sobre las señales obtenidas por dicho dispositivo de adquisición sobre dicho canal, incluyendo al menos dicho proceso de decodificación de canal un proceso para corregir los errores que se pueden haber producido sobre dicho canal, generando además dicho dispositivo de decodificación de canal las señales procesadas de este modo; y

o bien un dispositivo (103) de procesamiento de decodificación de fuente de información configurado para llevar a cabo un proceso de decodificación de fuente de información sobre las señales enviadas desde dicho

14

35

40

45

50

5

10

15

20

25

dispositivo de decodificación de canal, o bien un dispositivo (105) de grabación configurado para grabar en un medio de grabación las señales enviadas desde dicho dispositivo de decodificación de canal;

en donde dicho dispositivo de decodificación de canal comprende:

un decodificador (18) de LDPC configurado para decodificar tanto la señal de datos como la señal de control de transmisión en un modo de tiempo compartido;

un dispositivo de almacenamiento configurado para colocarse en el flujo de subida de dicho dispositivo de decodificación LDPC y para almacenar al menos dicha señal de control de transmisión al recibir dicha señal de datos y dicha señal de control de transmisión; y

un dispositivo (20) de control configurado para controlar que dicho dispositivo de decodificación LDPC decodifica dicha señal de datos mientras que dicha señal de control de transmisión está siendo acumulada en dicho dispositivo de almacenamiento y para interrumpir la decodificación de la señal de datos correspondiente a una trama anterior con el fin de controlar que dicho dispositivo de decodificación LDPC comience a decodificar dicha señal de control de transmisión de una trama actual cuando dicha señal de control de transmisión se ha acumulado en dicho dispositivo de almacenamiento,

en donde:

5

10

15

20

25

dicha señal de datos es una PLP y dicha señal de control de transmisión es una L1 incluida en un símbolo P2 especificado por dicho DVB-T.2;

dicha señal de control de transmisión y dicha señal de datos han sido sometidas a un proceso de entrelazado de frecuencia;

dicho dispositivo de almacenamiento se puede utilizar para almacenar dicha señal de datos y dicha señal de control de transmisión cuando se reciban las mismas y para llevar a cabo un proceso de desentrelazado de frecuencia correspondiente a dicho proceso de entrelazado de frecuencia sobre dicha señal de datos y dicha señal de control de transmisión; y

el dispositivo de decodificación está configurado para reanudar la decodificación de la señal de datos después de haber terminado la decodificación LDPC de la señal de control de transmisión de la trama actual.