# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 458 101

51 Int. Cl.:

**B41J 2/175** (2006.01) **G06F 13/42** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 30.03.2010 E 10158354 (0)

(97) Fecha y número de publicación de la concesión europea: 22.01.2014 EP 2237161

- 54 Título: Dispositivo de memoria, placa de circuito, receptáculo de líquido, procedimiento para aceptar de un circuito anfitrión datos para escribir en una sección de memoria de datos, y sistema que incluye un dispositivo de memoria eléctricamente conectable a un circuito anfitrión

- (30) Prioridad:

01.04.2009 JP 2009088591 16.02.2010 JP 2010030856

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 29.04.2014

(73) Titular/es:

SEIKO EPSON CORPORATION (100.0%) 4-1 NISHI-SHINJUKU 2-CHOME SHINJUKU-KU, TOKYO 163-0811, JP

(72) Inventor/es:

**ASAUCHI, NOBORU**

74 Agente/Representante:

**FÚSTER OLAGUIBEL, Gustavo Nicolás**

## **DESCRIPCIÓN**

Dispositivo de memoria, placa de circuito, receptáculo de líquido, procedimiento para aceptar de un circuito anfitrión datos para escribir en una sección de memoria de datos, y sistema que incluye un dispositivo de memoria eléctricamente conectable a un circuito anfitrión

La presente invención se refiere a un dispositivo de memoria, a una placa de circuito dotada de un dispositivo de memoria, a un receptáculo de líquido, a un procedimiento para aceptar de un circuito anfitrión datos para escribir en una sección de memoria de datos, y a un sistema que incluye un dispositivo de memoria eléctricamente conectable a un circuito anfitrión.

La presente solicitud reivindica la prioridad basándose en las solicitudes de patente japonesas Nº 2009-088591 presentada el 1 de abril de 2009, y Nº 2010-030856 presentada el 16 de febrero de 2010, a las que se hace referencia para mayor información.

## Descripción de la técnica relacionada

5

10

15

20

25

30

35

40

45

50

60

Una impresora de inyección de tinta, que es un ejemplo de un dispositivo de inyección de líquido, típicamente tiene uno o más receptáculos de tinta o depósitos de tinta instalados que son receptáculos de líquido extraíbles. Algunos receptáculos de tinta están provistos de dispositivos de memoria. El dispositivo de memoria almacena información de varios tipos, por ejemplo, el nivel de tinta restante o el color de la tinta en el receptáculo de tinta. Una unidad de control provista en la impresora se comunica con el dispositivo de memoria del receptáculo de tinta.

Se hace referencia al documento US 2007/250659 A1 y a los documentos JP-A 2002-370383, JP-A 2004-299405, JP-A 2001-146030, JP-A 6-226989, y JP-A 2003-112431.

El documento US 2007/0250659 A1 describe interfaces eléctricas, esquemas de direccionamiento, y protocolos de comando que permiten comunicaciones con módulos de memoria en dispositivos informáticos tales como dispositivos de impresión y de imagen. Se puede asignar una dirección a los módulos de memoria a través de una serie de tensiones discretas. Puede asignarse una dirección a uno, varios, o todos los módulos de memoria con un único comando, que puede ser un comando de contador incremental, un comando de escritura, un campo de bits expulsables o un comando criptográfico. Los comandos pueden ser transmitidos utilizando un esquema de difusión o un esquema de transacción dividida. El estado de los módulos de memoria puede determinarse muestreando una única señal que puede estar en un nivel de tensión baja alta o intermedia.

Sin embargo, en las técnicas convencionales, no se ha considerado suficientemente el problema de la fiabilidad de la comunicación entre la unidad de control provistos en la impresora y los dispositivos de memoria provistos en los receptáculos de tinta. Por ejemplo, existe el riesgo de que, por motivos como un contacto defectuoso entre las porciones de contacto eléctrico de la impresora y un receptáculo de tinta, pueda producirse una comunicación defectuosa entre la unidad de control provista en la impresora y el dispositivo de memoria del receptáculo de tinta. Si la operación de la unidad de control de impresión continuase sin resolver el problema de la comunicación, existe un riesgo de que se creen problemas como errores en los contenidos de memoria del dispositivo de memoria. Este problema no se limita a los dispositivos de memoria provistos en los receptáculos de tinta, sino que es más bien un problema común a todos los dispositivos de memoria que se conectan eléctricamente a un circuito anfitrión.

Un objeto de la presente invención es proporcionar una tecnología para mejorar la fiabilidad de la comunicación con un circuito anfitrión en un dispositivo de memoria que está eléctricamente conectado al circuito anfitrión.

De acuerdo con un primer aspecto de la invención, se proporciona un dispositivo de memoria de acuerdo con la reivindicación 1.

De acuerdo con un segundo aspecto de la invención, se proporciona un procedimiento para recibir datos de acuerdo con la reivindicación 12.

De acuerdo con un tercer aspecto de la invención, se proporciona un sistema de acuerdo con la reivindicación 13.

A continuación se describe un dispositivo de memoria eléctricamente conectable a un circuito anfitrión. El dispositivo de memoria incluye: una sección de memoria de datos no volátil; una sección de recepción de datos que recibe, del circuito anfitrión, datos que incluyen primeros datos para ser escritos en la sección de memoria de datos y segundos datos generados a partir de los primeros datos; una sección de determinación que determina la consistencia de los datos recibidos por la sección de recepción de datos; y una sección de transmisión de datos que transmite un resultado de la determinación al circuito anfitrión. La sección de determinación determina si los primeros datos y los segundos datos son consistentes unos con otros.

De acuerdo con el dispositivo de memoria, debido a que después de determinar la consistencia de los primeros datos y los segundos datos el resultado de la determinación se transmite al circuito anfitrión, el circuito anfitrión

puede comunicarse con el dispositivo de memoria mientras verifica si hay errores de comunicación. Como resultado, se mejora la fiabilidad de la comunicación entre el circuito anfitrión y el dispositivo de memoria.

5

10

15

20

25

30

40

45

60

Como también se describe más adelante en este documento, los segundos datos son datos invertidos de los primeros datos. Durante una operación de escritura desde el circuito anfitrión al dispositivo de memoria, la sección de recepción de datos recibe en serie desde el circuito anfitrión: datos de identificación que especifican un único dispositivo de memoria de entre una pluralidad de dispositivos de memoria; datos de identificación invertidos; datos de comando de escritura; datos de comando de escritura invertidos; y un primer conjunto de primeros datos y segundos datos de un tamaño prescrito; y a partir de ahí recibe en incrementos de un conjunto único un segundo y subsiguientes conjuntos de primeros datos y segundos datos del tamaño descrito, donde (i) desde el momento en que comienza la recepción de los datos de identificación hasta el momento en que se completa la recepción del primer conjunto de primeros datos y segundos datos, el circuito de transmisión de datos no transmite el resultado de la determinación mediante la sección de determinación al circuito anfitrión, y el circuito de transmisión de datos transmite el resultado de la determinación mediante la sección de determinación al circuito anfitrión después de que se complete la recepción del primer conjunto de primeros datos y segundos datos; y (ii) para el segundo y subsiguientes conjuntos de primeros datos y segundos datos del tamaño prescrito, el circuito de transmisión de datos transmite el resultado de la determinación mediante la sección de determinación al circuito anfitrión cada vez que se completa la recepción de un conjunto de primeros datos y segundos datos. De acuerdo con esta disposición, cada vez que se recibe un conjunto de primeros datos y segundos datos de tamaño prescrito, el dispositivo de memoria transmite el resultado de la determinación de consistencia para el mismo al circuito anfitrión, y en consecuencia se mejora la fiabilidad de la comunicación entre el circuito anfitrión y el dispositivo de memoria. También, en la parte inicial del proceso de escritura, una vez se inicia la recepción de los datos de identificación, un resultado de la determinación no se transmite al circuito anfitrión hasta que se completa la recepción del primer conjunto de primeros datos y segundos datos, de modo que se reduce el número de veces que se envían los resultados de la determinación desde el dispositivo de memoria hacia el circuito anfitrión, y el proceso de escritura se lleva a cabo de una manera globalmente más eficiente.

En una variante, los primeros datos y los segundos datos incluyen cada uno de ellos un bit de paridad, y la sección de determinación genera un resultado de determinación afirmativo si los primeros y segundos datos tienen una relación mutuamente invertida, y también los primeros y segundos datos carecen de errores de paridad. De acuerdo con esta disposición, la fiabilidad de la comunicación entre el circuito anfitrión y el dispositivo de memoria se mejora aún más.

En otra variante, los primeros y segundos datos tienen un tamaño de datos idéntico. Con esta disposición, se lleva a cabo una determinación de consistencia más precisa por parte del circuito anfitrión.

En una variante más, el dispositivo de memoria puede además incluir una sección de control de lectura/escritura que escribe los primeros datos en la sección de memoria de datos si el resultado de la determinación es afirmativo, y no escribe los primeros datos en la sección de memoria de datos si el resultado de la determinación es negativo. Con esta disposición, en caso de un error de comunicación, los primeros datos no se escribirán en la sección de memoria de datos, evitando así la actualización errónea de la sección de memoria de datos.

En otra variante, los primeros datos y los segundos datos son cada uno señales de n bits donde n es un entero igual o mayor que 1, y los segundos datos son datos invertidos que invierten cada bit de los primeros datos. Con esta disposición, si debido a un error de comunicación la señal recibida por el dispositivo de memoria es una señal en la que los primeros datos y los segundos datos tienen todos ellos el mismo valor, por ejemplo, se detecta de una manera fiable el error de comunicación.

En otra variante, la sección de recepción de datos recibe en serie los primeros datos y los segundos datos en sincronismo con una señal de reloj suministrada desde el circuito anfitrión, y la sección de transmisión de datos transmite el resultado de la determinación al circuito anfitrión en sincronismo con la señal de reloj en un ciclo de la señal de reloj inmediatamente posterior a un ciclo anterior de la señal de reloj utilizado para recibir un bit de datos final de los primeros datos y los segundos datos. Con esta disposición, el circuito anfitrión reconoce el resultado de la determinación inmediatamente después de que se reciban los primeros datos y los segundos datos. Así, en caso de que el resultado de la determinación sea negativo, medidas como el reenvío de los datos se llevan a cabo rápidamente.

En otra variante más, la sección de determinación hace que el resultado de la determinación sea afirmativo si una salida OR exclusiva de un valor m-ésimo de los primeros datos y un valor m-ésimo de los segundos datos es verdadera para todos los n bits, donde m es un entero de tal modo que 1 <= m <= n, y la sección de determinación hace que el resultado de la determinación sea negativo si la salida OR exclusiva es falsa para uno cualquiera de los n bits. Con esta disposición, la existencia de un error de comunicación se determina fácilmente a través de una operación OR exclusiva.

En otra variante, el entero n es un número par, y la sección de recepción de datos recibe, en sincronismo con una señal de reloj, los n/2 bits superiores de los primeros datos, los n/2 superiores de los segundos datos, los n/2 bits

inferiores de los primeros datos, y los n/2 bits inferiores de los segundos datos, en ese orden, y la sección de transmisión de datos transmite el resultado de la determinación en un ciclo de la señal de reloj inmediatamente después de un ciclo anterior de la señal de reloj utilizado para recibir el bit más bajo de los n/2 bits inferiores de los segundos datos. Con esta disposición, un resultado de la determinación se transmite cada vez que se reciben datos de 2n bits. En consecuencia, como la comunicación tiene lugar a la vez que se identifica la existencia de errores de comunicación en unidades de 2n bits, se mejora la fiabilidad de la comunicación.

En otra variante más, el circuito anfitrión y el dispositivo de memoria se deben conectar eléctricamente a través de terminales del lado del circuito que están eléctricamente conectados al circuito anfitrión, y terminales del lado del dispositivo de memoria que están eléctricamente conectados al dispositivo de memoria. Con esta disposición, se detecta la aparición de errores de comunicación provocados por contacto defectuoso entre los terminales del lado del dispositivo de memoria y los terminales del lado del circuito y, en consecuencia, mejora la fiabilidad de la comunicación entre el circuito anfitrión y el dispositivo de memoria.

La presente invención puede implementarse de diferentes modos, por ejemplo, una placa de circuito conectable a un dispositivo de inyección de líquido; un receptáculo de líquido conectable a un dispositivo de inyección de líquido; un receptáculo de líquido instalable en un dispositivo de inyección de líquido; un procedimiento para aceptar de un circuito anfitrión datos para su escritura a una sección de memoria de datos; un sistema que incluye un circuito anfitrión y un dispositivo de memoria instalable de manera desmontable en el circuito anfitrión; un sistema de inyección de líquido; un programa de ordenador para llevar a cabo las funciones de tales procedimientos o dispositivos; o un medio de grabación que tiene tal programa de ordenador grabado en el mismo.

## Breve descripción de las figuras

5

10

35

40

50

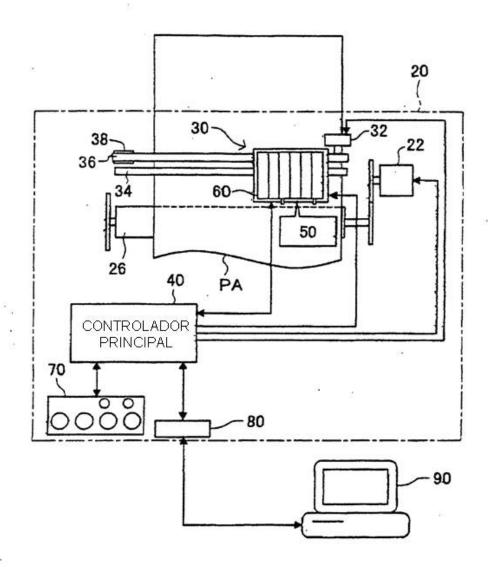

La fig. 1 ilustra una configuración simplificada de un sistema de impresión;

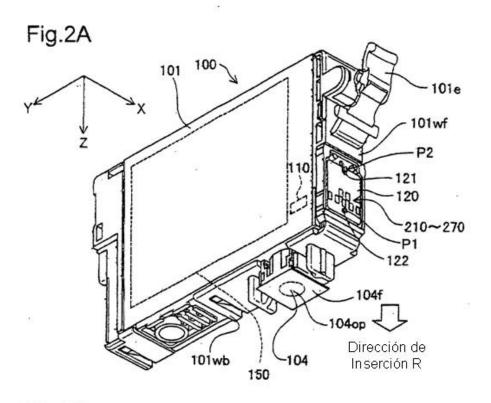

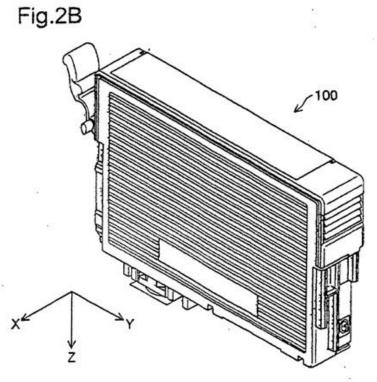

las figs. 2A y 2B son vistas en perspectiva que representan una configuración de un cartucho de tinta de acuerdo con la realización:

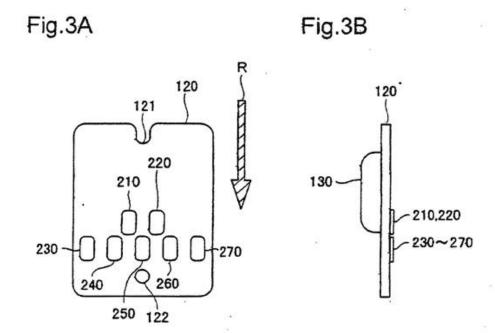

- 30 las figs. 3A y 3B representan una configuración de una placa de acuerdo con la realización;

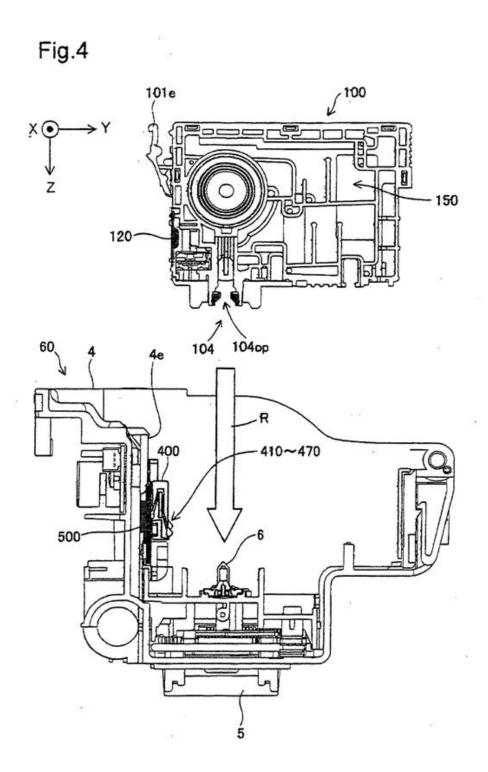

- la fig. 4 ilustra una configuración de una unidad de cabezal de impresión;

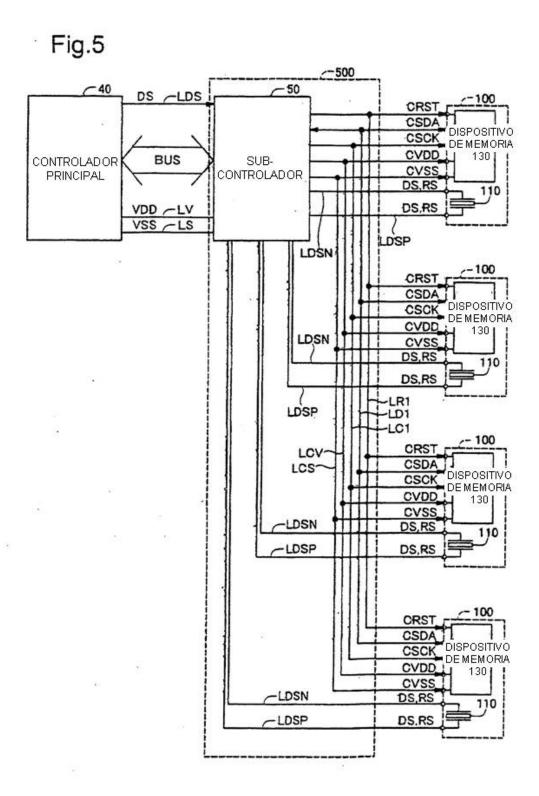

- la fig. 5 es una primera ilustración que representa una configuración eléctrica de una impresora;

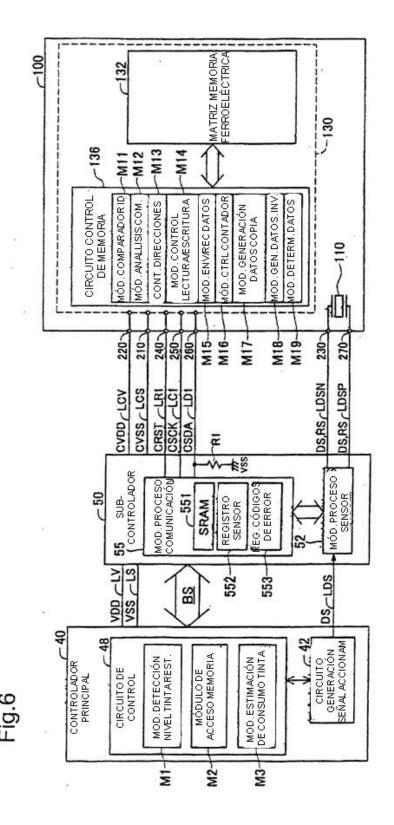

- la fig. 6 es una segunda ilustración que representa una configuración eléctrica de una impresora;

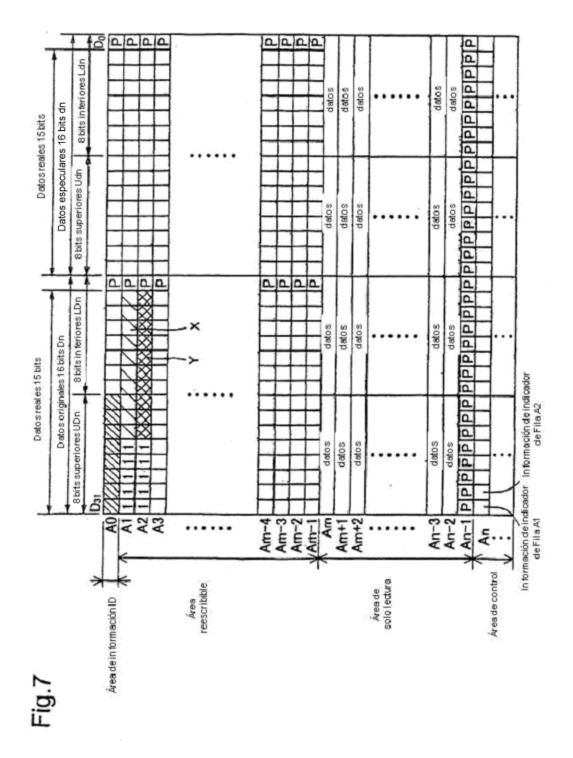

- la fig. 7 representa esquemáticamente un mapa de memoria de áreas de memoria proporcionadas por una matriz de memoria ferroeléctrica de un dispositivo de memoria;

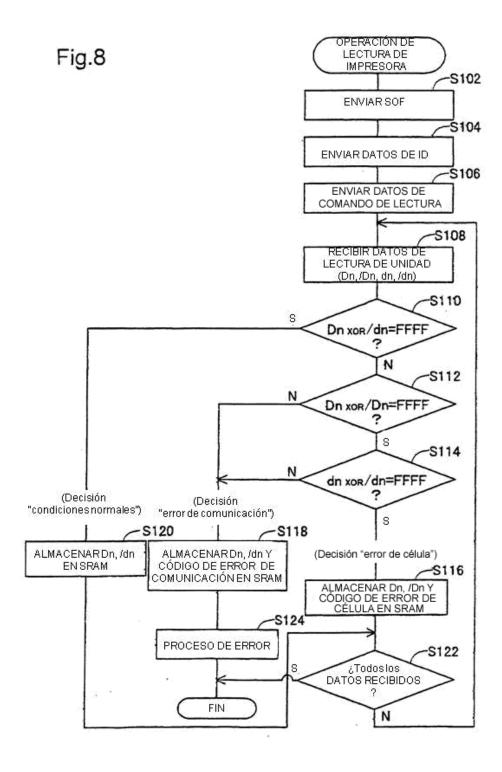

- la fig. 8 es un diagrama de flujo que representa una rutina de procesamiento de una operación de lectura desde un dispositivo de memoria de la impresora;

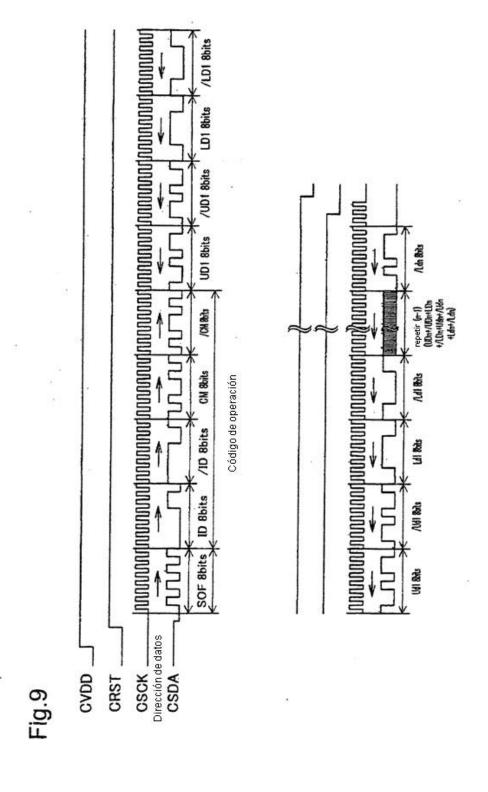

- la fig. 9 es un gráfico de temporización que representa esquemáticamente las señales intercambiadas entre un módulo de proceso de comunicación y un circuito de control de memoria durante una operación de lectura desde un dispositivo de memoria:

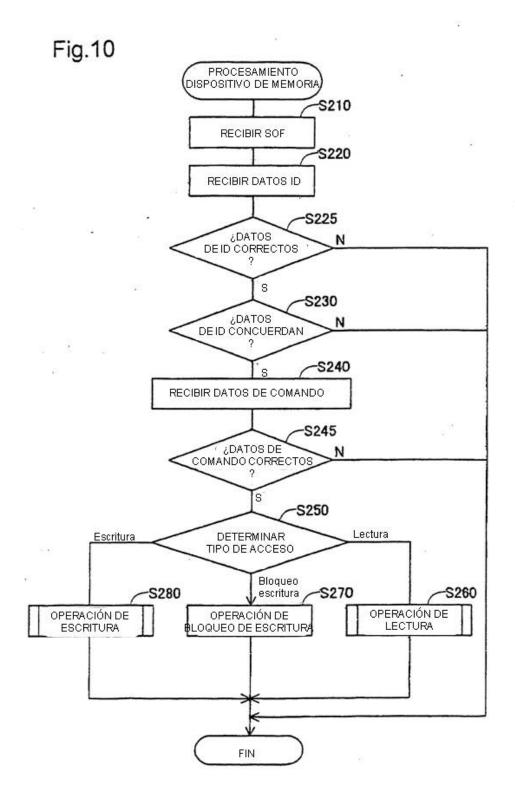

- la fig. 10 es un diagrama de flujo que representa esquemáticamente una rutina de procesamiento de una operación de lectura desde un dispositivo de memoria de la memoria;

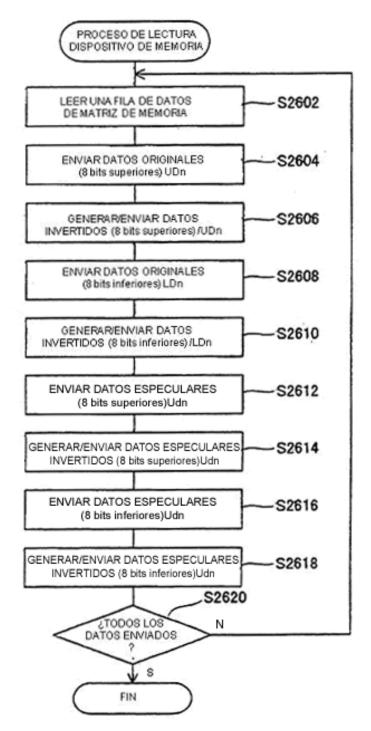

- la fig. 11 es un diagrama de flujo que representa la rutina de procesamiento de una operación de lectura que tiene lugar en el dispositivo de memoria;

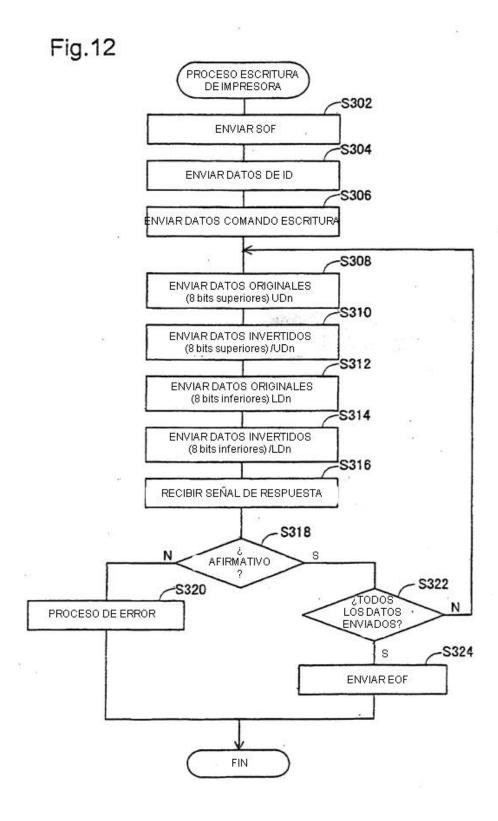

- la fig. 12 es un diagrama de flujo que representa la rutina de procesamiento de una operación de escritura a un dispositivo de memoria que tiene lugar en la impresora;

- la fig. 13 representa esquemáticamente un mapa de memoria reconocido en la impresora durante una operación de escritura a un dispositivo de memoria;

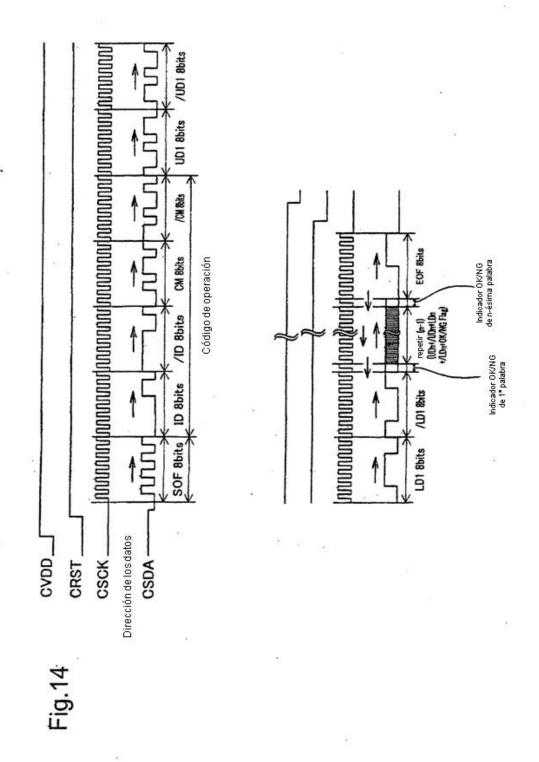

- la fig. 14 es un gráfico de temporización que representa esquemáticamente señales intercambiadas entre un módulo de proceso de comunicación y un circuito de control de memoria durante una operación de escritura a un dispositivo de memoria;

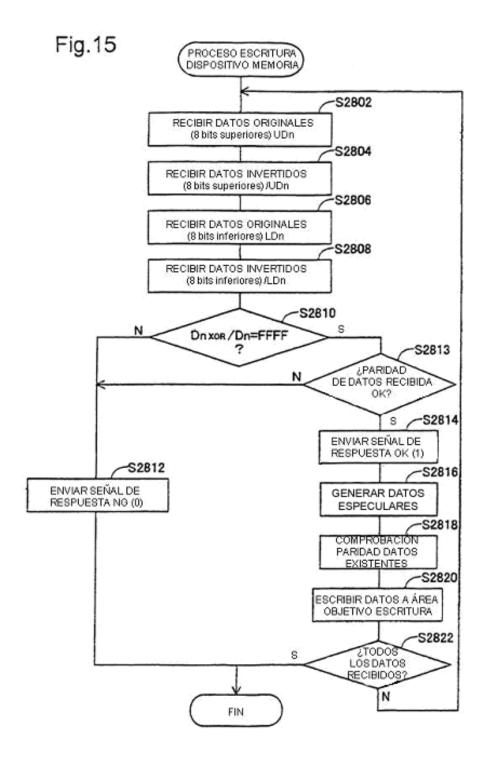

- la fig. 15 es un diagrama de flujo que representa la rutina de procesamiento de una operación de escritura en un dispositivo de memoria;

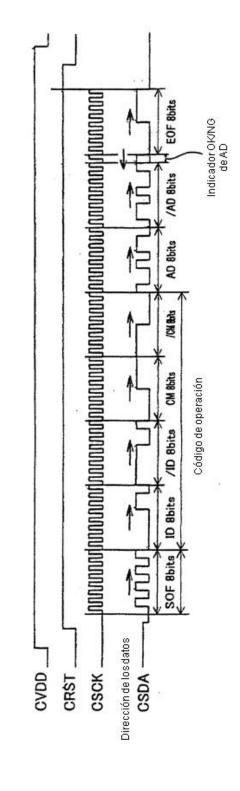

la fig. 16 es un gráfico de temporización que representa esquemáticamente señales intercambiadas entre un módulo de proceso de comunicación y un circuito de control de memoria durante una operación de bloqueo de escritura de un dispositivo de memoria; y

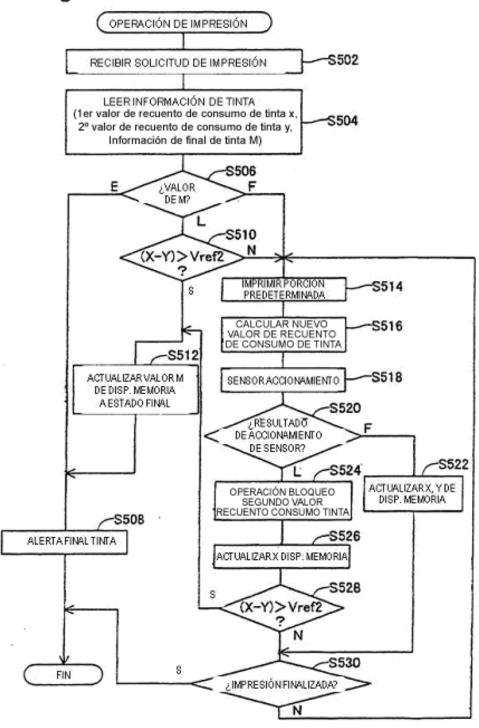

5 la fig. 17 es un diagrama de flujo que representa las etapas del proceso en una operación de impresión.

## Descripción de la realización preferida

#### A. Realización:

10

15

20

25

30

35

40

65

#### Configuración del sistema de impresión

La fig. 1 es una ilustración que representa una configuración simplificada de un sistema de impresión. El sistema de impresión incluye una impresora 20 provista como el dispositivo de impresión, y un ordenador 90. La impresora 20 está conectada al ordenador 90 a través de un conector 80.

La impresora 20 está dotada de un mecanismo de alimentación de sub-escaneo, un mecanismo de alimentación de escaneo principal, un mecanismo de accionamiento de cabezal, y un controlador principal 40. El mecanismo de alimentación de sub-escaneo tiene un motor de alimentación de papel 22 y un rodillo 26, y transporta papel PA en la dirección de sub-escaneo transmitiendo una rotación del motor de alimentación de papel al rodillo. El mecanismo de alimentación de escaneo principal incluye un motor de carro 32, una polea 38, una correa de accionamiento 36 estirada entre el motor de carro y la polea, y un carril de deslizamiento 34 dispuesto paralelo al eje del rodillo 26. El carril de deslizamiento 34 retiene de manera deslizante un carro 30 que está fijado a la correa de accionamiento 36. La rotación del motor de carro 32 se transmite al carro 30 a través de la correa de accionamiento 36, tras lo cual el carro 30 experimenta un movimiento alternativo en la dirección axial del rodillo 26 (la dirección de escaneo principal) a lo largo del carril de deslizamiento 34. El mecanismo de accionamiento de cabezal incluye una unidad de cabezal de impresión 60 instalada en el carro 30, y está diseñado para accionar un cabezal de impresión e inyectar tinta sobre el papel PA. El controlador principal 40 controla los mecanismos anteriores y lleva a cabo las operaciones de impresión. El controlador principal 40, por ejemplo, recibe un trabajo de impresión de un usuario a través del ordenador 90, y controla los mecanismos anteriores para llevar a cabo la impresión basándose en el contenido del trabajo de impresión recibido. Como se analizará más adelante, una pluralidad de cartuchos de tinta son instalables de manera desmontable en la unidad de cabezal de impresión 60. Específicamente, los cartuchos de tinta para suministrar tinta al cabezal de impresión están dispuestos en la unidad de cabezal de impresión 60 de tal modo que se pueden montar y desmontar a través de una operación de usuario. La impresora 20 también tiene una porción de consola 70 que permite el uso para llevar a cabo varios ajustes de impresora, comprobar el estado de la impresora,

La configuración de la impresora, junto con la configuración de un cartucho de tinta (receptáculo de líquido), se analizará más adelante con referencia a las figs. 2A, 2B, 3A, 3B, y 4. Las figs. 2A y 2B son vistas en perspectiva que representan una configuración de un cartucho de tinta de acuerdo con la realización. Las figs. 3A y 3B son dibujos que representan una configuración de una placa de circuito impreso (en adelante se denomina simplemente placa de circuito) de acuerdo con la invención. La fig. 4 es un dibujo que ilustra una configuración de la unidad de cabezal de impresión 60.

- El cartucho de tinta 100 tiene un cuerpo principal 101 para contener la tinta, una placa de circuito 120, y un sensor 110. En la cara de la base del cuerpo principal 101 está provisto un puerto de suministro de tinta 104 que, con el cartucho instalado en la unidad de cabezal de impresión 60, suministra tinta a la unidad de cabezal de impresión 60. Una cámara de tinta 150 para contener la tinta está formada en el cuerpo principal 101. El puerto de suministro de tinta 101 se comunica con la cámara de tinta 150. La abertura 104op del puerto de suministro de tinta 104 está sellada por medio de una lámina 104f. Al instalar el cartucho de tinta 100 en la unidad de cabezal de tinta 60 (fig. 4), la lámina 104f es perforada y una aguja de suministro de tinta 6 se inserta a través del puerto de suministro de tinta 104 (fig. 4). La tinta contenida en la cámara de tinta 150 es suministrada a la impresora 20 a través de la aguja de suministro de tinta 6.

- El sensor 110 se fija al interior del cuerpo principal 101. Como se analizará más adelante, el sensor 110 incluye un elemento piezoeléctrico compuesto por un cuerpo piezoeléctrico intercalado entre dos electrodos opuestos, y se utiliza para detectar el nivel de tinta restante. El cuerpo principal 101 incluye una pared frontal 101wf (la pared que queda en la dirección -Y) y una pared de base 101wb (la pared que queda en la dirección +Z). La pared frontal 101wf intersecta (en la presente realización, según un ángulo sustancialmente recto) la pared de base 101wb. La placa de circuito 120 está fijada a la pared frontal 101wf. La superficie exterior de la placa de circuito 120 está provista de terminales 210 a 270.

Están formados dos salientes P1, P2 en la pared frontal 101wf. Estos salientes P1, P2 sobresalen hacia fuera en la dirección -Y. Un orificio 122 y una muesca 121 adaptados para recibir respectivamente estos salientes P1, P2 están formados en la placa de circuito 120 (fig. 3A). El orificio 122 está formado en el centro del borde de la placa de circuito 120 en el lado del puerto de suministro de tinta 104 (el borde en la dirección +Z) de la misma, mientras que

la muesca 121 está formada en el centro del borde de la placa de circuito 120 en el lado opuesto con relación al puerto de suministro de tinta 104 (el borde en la dirección -Z). Con la placa de circuito 120 montada sobre la pared frontal 101wf, los salientes P1, P2 pasan respectivamente a través del orificio 122 y la muesca 121. Durante la producción del cartucho de tinta 100, después de que la placa de circuito 120 se haya montado en la pared frontal 101wf, las puntas de estos salientes P1, P2 se colapsan. La placa de circuito 120 se fija de ese modo a la pared frontal 101wf.

5

10

15

20

25

35

40

45

Adicionalmente, está provisto un saliente de acoplamiento 101e en la pared frontal 101wf. Se evita que el cartucho de tinta 100 se separe inadvertidamente del soporte 4 mediante el acoplamiento del saliente de acoplamiento 101e y una abertura de acoplamiento 4e de un soporte 4 (fig. 4).

La configuración de la unidad de cabezal de impresión 60, así como la instalación del cartucho de tinta 100 en la unidad de cabezal de impresión 60, se analiza con referencia a la fig. 4. Como se representa en la fig. 4, la unidad de cabezal de impresión 60 incluye un soporte 4, un mecanismo de conexión 400, un cabezal de impresión 5, y una placa de sub-control 500. En la placa de sub-control 500 hay montado un circuito de carro 50 y un grupo de terminales para la conexión respectiva a través del mecanismo de conexión 400 a los terminales individuales 210 a 270 de la placa de circuito 120 del cartucho de tinta 100. El soporte 4 está diseñado para recibir la instalación de varios cartuchos de tinta 100, y está situado encima del cabezal de impresión 5. El mecanismo de conexión 400 tiene terminales de conexión eléctricamente conductores 410 a 470 provistos para cada uno de los terminales de la placa de circuito 120 y adaptados para proporcionar conexiones eléctricas entre los terminales de la placa de circuito 120 y el cartucho de tinta 100, que se analizará más adelante, y los terminales dispuestos en la placa de sub-control 500. Las agujas de suministro de tinta 6 anteriormente mencionadas para suministrar tinta desde los cartuchos de tinta 100 al cabezal de impresión 5 están situadas en el cabezal de impresión 5. El cabezal de impresión 5 incluye varias boquillas y varios elementos piezoeléctricos, y está adaptado para inyectar pequeñas gotas de tinta desde las boquillas en respuesta a una tensión aplicada a los elementos piezoeléctricos, produciendo así puntos sobre el papel PA. El circuito de carro 50 es un circuito diseñado para llevar a cabo el control en relación con los cartuchos de tinta 100 en conjunto con el controlador principal 40, y en este documento se denomina también como subcontrolador.

30 El cartucho de tinta 100 se instala en el soporte 4 insertándolo en la dirección hacia adelante del eje Z (la dirección de inserción R) en la fig. 4. El cartucho de tinta 100 se instala así de manera desmontable en la impresora 20. La placa de circuito 120 que está montada sobre el cartucho de tinta 100 se instala en, o se desinstala de, la impresora 20 en conjunto con la instalación o desinstalación del cartucho de tinta 100 por parte del usuario. Cuando se instala el cartucho de tinta 100 en la impresora 20, la placa de circuito 120 se acopla eléctricamente con la impresora 20.

La descripción de la placa de circuito 120 continúa, volviendo a las figs. 3A y 3B. La flecha R de la fig. 3A indica la dirección de inserción del cartucho de tinta 100 que se ha mencionado anteriormente. Como se muestra en la fig. 3B, la placa de circuito 120 está provista de un dispositivo de memoria 130 en su cara posterior, es decir, la cara en el lado posterior de la cara que se conecta con la impresora 20; y está provista de un grupo de terminales compuesto por siete terminales en su cara frontal, es decir, la cara que se conecta con la impresora 20. En la presente realización, el dispositivo de memoria 130 es un dispositivo de memoria de semiconductor que incluye una matriz de células de memoria ferroeléctrica. Esta matriz de células de memoria, que corresponde a la sección de memoria de datos de la presente invención, almacena datos de diferentes tipos en relación con el cartucho de tinta 100 o con la tinta, como el consumo de tinta, color de la tinta, etc. Los datos de consumo de tinta indican, para la tinta contenida en el cartucho de tinta en cuestión, la cantidad total acumulada de tinta consumida en el transcurso de la impresión y en la limpieza del cabezal. Los datos pueden representar la cantidad de tinta per se, o representar la tinta consumida como un porcentaje de una cantidad de referencia que es equivalente a la cantidad de tinta contenida inicialmente en el cartucho de tinta.

Los terminales del lado frontal de la placa de circuito 120 están formados con una forma generalmente rectangular y están situados para formar dos filas aproximadamente ortogonales con relación a la dirección de inserción R. De estas dos filas, la fila situada hacia la dirección de inserción R (el lado del borde distal según la dirección de inserción cuando está insertado), es decir, el lado inferior en la fig. 3A, se denomina fila inferior; y la fila situada hacia el lado opuesto desde la dirección de inserción R, es decir, el lado superior en la fig. 3A, se denomina fila superior.

Aquí, el término "inferior" se utiliza por motivos de conveniencia de la descripción en cuanto a las figs. 3A y 3B. Los terminales que forman la fila superior y los terminales que forman la fila inferior están configurados de acuerdo con una disposición denominada escalonada mediante un posicionamiento diferente uno de otro, de modo que los centros de los terminales no están alineados en la dirección de inserción R.

Los terminales que están ordenados para formar la fila superior son, en orden desde la izquierda en la fig. 3A, un terminal de tierra 210 y un terminal de alimentación 220. Los terminales que están ordenados para formar la fila inferior son, en orden desde la izquierda en la fig. 3A, un primer terminal de accionamiento de sensor 230, un terminal de reinicio 240, un terminal de reloj 250, un terminal de datos 260, y un segundo terminal de accionamiento de sensor 270. Los cinco terminales situados cerca del centro en la dirección lateral, es decir, el terminal de tierra 210, el terminal de alimentación 220, el terminal de reinicio 240, el terminal de reloj 250, y el terminal de datos 260, están respectivamente conectados al dispositivo de memoria 130 a través de capas de patrón de circuito (no

mostradas) provistas en las caras frontal y posterior de la placa de circuito 120, y orificios pasantes situados en la placa de circuito 120. Los dos terminales situados en los extremos de la fila inferior, es decir, el primer terminal de accionamiento de sensor 230 y el segundo terminal de accionamiento de sensor 270, están respectivamente conectados a uno y otro de los electrodos del elemento piezoeléctrico incluido en el sensor 110.

Con esta placa de circuito 120, los cinco terminales que se conectan al dispositivo de memoria 130 y los dos terminales que se conectan al sensor 110 están situados próximos entre sí. Por tanto, en el mecanismo de conexión 400 también en el lado de la impresora 20, los terminales 410, 420 y 440 a 460 de conexión que corresponden a los cinco terminales conectados al dispositivo de memoria 130 y los terminales de conexión 430, 470 que corresponden a los dos terminales conectados al sensor 110 están igualmente situados próximos entre sí.

Con el cartucho de tinta 100 fijado en el soporte 4, los terminales de la placa de circuito 120 se conectan eléctricamente a través del contacto con los terminales de conexión 410 a 470 del mecanismo de conexión 400. Además, los terminales de conexión 410 a 470 del mecanismo de conexión 400 se conectan eléctricamente a través del contacto con el grupo de terminales de la placa de sub-control 500; y el grupo de terminales en la placa de sub-control 500 están en conexión eléctrica con el sub-controlador (circuito de carro 50). Por tanto, cuando el cartucho de tinta 100 se fija en el soporte 4, los terminales 210 a 270 de la placa de circuito 120 están en conexión eléctrica con el sub-controlador 50.

## Configuración eléctrica de la impresora

5

10

15

20

25

30

35

40

45

50

55

60

65

Las figs. 5 y 6 son ilustraciones que representan la configuración eléctrica de la impresora. La ilustración de la fig. 5 está centrada en la totalidad del circuito de control principal 40, el sub-controlador 50, y todos los cartuchos de tinta 100 instalables en la impresora. La fig. 6 representa las características funcionales del circuito de control principal 40 y las características funcionales del sub-controlador 50, que se muestran junto con un único cartucho de tinta 100. El sub-controlador 50 de la presente realización corresponde al circuito anfitrión de la presente invención. En la presente realización, el sub-controlador 50 provisto como circuito anfitrión suministra energía al dispositivo de memoria 130 provisto como sección de memoria de datos, y transmite comandos que indican varios tipos de acceso al dispositivo de memoria 130 para escribir datos en el dispositivo de memoria 130 o leer datos del dispositivo de memoria 130 (se describirá más adelante).

Al dispositivo de memoria 130 de cada cartucho de tinta 100 se le asigna un número ID de 8 bits (información de identificación) diferente de todos los demás. Debido a que, como se muestra en la fig. 5, los dispositivos de memoria 130 de los cartuchos de tinta están conectados en paralelo a las líneas que salen del sub-controlador 50 (es decir, están conectadas como un bus al sub-controlador 50), si se va a llevar a cabo una operación tal como una operación de lectura/escritura por parte del sub-controlador 50 en el dispositivo de memoria 130 de un cartucho de tinta 100 particular, es necesario que el cartucho de tinta particular sea identificado desde el controlador 40 principal y el sub-controlador 50. El número ID se utiliza con este propósito. Este número ID es utilizado por el sub-controlador 50 para especificar un dispositivo de memoria 130 (cartucho de tinta 100) al que se va a acceder.

Las líneas que conectan eléctricamente el sub-controlador 50 con cada cartucho de tinta 100 incluyen las líneas que conectan el sub-controlador 50 con el grupo de terminales de la placa de sub-control 500; los terminales de conexión 410 a 470 del mecanismo de conexión 400; el grupo de terminales en el lado frontal de la placa de circuito 120; y las líneas que conducen desde el grupo de terminales de la placa de circuito 120 al dispositivo de memoria 130 y al sensor 110. Las líneas que conectan eléctricamente el sub-controlador 50 con cada cartucho de tinta 100 incluyen una línea de señal de reinicio LR1, una línea de señal de reloj LC1, una línea de señal de datos LD1, una primera línea de tierra LCS, una primera línea de alimentación LCV, una primera línea de señal de accionamiento de sensor LDSN, y una segunda línea de señal de accionamiento de sensor LDSP.

La línea de señal de reinicio LR1 entre el sub-controlador 50 y el dispositivo de memoria 130 es una línea conductora para enviar una señal de reinicio CRST desde el sub-controlador 50 al dispositivo de memoria 130. La señal de reinicio es una señal mediante la cual el sub-controlador 50 puede poner el circuito de control de memoria 136 (que se analizará más adelante) de un dispositivo de memoria 130 en el estado inicializado, o en un estado de espera en el que puede aceptar acceso. Cuando el sub-controlador 50 presenta una señal de reinicio de bajo nivel a un circuito de control de memoria 136. el circuito de control de memoria 136 entra en el estado inicializado. La línea de señal de reloj LC1 entre el sub-controlador 50 y el dispositivo de memoria 130 es una línea conductora para enviar una señal de reloj CSCK desde el sub-controlador 50 al dispositivo de memoria 130. La línea de señal de datos LD1 entre el sub-controlador 50 y el dispositivo de memoria 130 es una línea conductora para enviar señales de datos CSDA que son intercambiadas entre el sub-controlador 50 al dispositivo de memoria 130. Como se muestra en la fig. 6, en el sub-controlador 50, la línea de señal de datos LD1 está conectada al potencial de tierra CVSS (0 V) a través de una resistencia a masa R1. Como resultado, el potencial de la línea de señal de datos LD1 se mantiene en un nivel bajo, en particular cuando no se están intercambiando señales de datos entre el subcontrolador 50 y el dispositivo de memoria 130. Para conseguir la sincronización entre el sub-controlador 50 y el dispositivo de memoria 130, se transmiten señales de datos y se reciben en sincronización con la señal de reloj mencionada anteriormente. Por ejemplo, el intercambio puede tener lugar de modo que las señales se transmitan o reciban a la vez que se utiliza una subida o bajada de la señal de reloj como temporización de datos válida. Cada

una de estas tres líneas, LR1, LC1, LD1 es una línea que tiene un único final en el sub-controlador 50, y finales ramificados correspondientes en número al número de cartuchos de tinta 100, en el cartucho de tinta 100. Es decir, con relación a las tres líneas LR1, LC1, LD1, la pluralidad de dispositivos de memoria 130 están conectados mediante un bus al sub-controlador 50. La señal de reinicio CRST, la señal de datos CSDA, y la señal de reloj CSCK son todas ellas señales binarias que tienen bien un nivel alto (en la presente realización, un potencial CVDD de 3,3 V) o un nivel bajo (en la presente realización, un potencial CVSS de 0 V). En el presente documento, una señal de nivel alto también está representada por el valor "0".

La primera línea de tierra LCS es una línea conductora para proporcionar potencial de tierra CVSS al dispositivo de memoria 130, y está eléctricamente conectada al primer dispositivo de memoria 130 a través del terminal de tierra 210 de la placa de circuito 120. La primera línea de tierra LCS es una línea que tiene un único final en el subcontrolador 50, y finales ramificados, correspondientes en número al número de cartuchos de tinta 100, en el cartucho de tinta 100. El potencial de tierra CVSS está conectado al potencial de tierra VSS (= potencial CVSS) suministrado al sub-controlador 50 por el controlador principal 40 a través de una segunda línea de tierra LS, y se establece en un nivel bajo (0 V).

La primera línea de señal de accionamiento de sensor LDSN y la segunda línea de señal de accionamiento de sensor LDSP son líneas conductoras adaptadas para aplicar una tensión de accionamiento al elemento piezoeléctrico del sensor 110, y después de dejar de aplicar la tensión de accionamiento, transmitir al subcontrolador 50 una tensión producida por el efecto piezoeléctrico del elemento piezoeléctrico. La primera línea de señal de accionamiento de sensor LDSP son una pluralidad de líneas que están provistas respectivamente de manera independiente para cada cartucho de tinta 100, y cada una de ellas está eléctricamente conectada en un primer extremo al sub-controlador 50 así como eléctricamente conectada en el otro extremo al primer terminal de accionamiento de sensor 230 y al segundo terminal de accionamiento de sensor 270 de la placa de circuito 120, respectivamente. La primera línea de señal de accionamiento de sensor LDSN está eléctricamente conectada a través del primer terminal de accionamiento de sensor LDSP está eléctricamente conectada a través del segundo terminal de accionamiento de sensor LDSP está eléctricamente conectada a través del segundo terminal de accionamiento de sensor 270 al otro electrodo del elemento piezoeléctrico del sensor 110.

La primera línea de alimentación LCV es a línea conductora para proporcionar la tensión de alimentación de energía CVDD, que representa la tensión de operación del dispositivo de memoria 130, al dispositivo de memoria 130; y está conectada al dispositivo de memoria 130 a través del terminal de alimentación de energía220 de la placa de circuito 120. La primera línea de alimentación LCV es una línea que tiene un único final en el sub-controlador 50, y finales ramificados, correspondientes en número al número de cartuchos de tinta 100, en el cartucho de tinta 100. La tensión de alimentación de energía de nivel alto CVDD utilizada para accionar el dispositivo de memoria 130 utiliza un potencial de aproximadamente 3,3 V frente al potencial de tierra de nivel bajo CVSS (0 V). Por supuesto, dependiendo de factores como la generación de procesador del dispositivo de memoria 130, el nivel de potencial de la tensión de alimentación de energía CVDD puede ser un potencial diferente, como por ejemplo 1,5 o 2,0 V.

En controlador principal 40 y el sub-controlador 5 están eléctricamente conectados por medio de varias líneas. Estas varias líneas incluyen un bus BS, una segunda línea de alimentación de energía LV, una segunda línea de tierra S, y una tercera línea de señal de accionamiento de sensor LDS. El bus BS se utiliza para comunicaciones de datos entre el controlador principal 40 y el sub-controlador 50. La segunda línea de alimentación de energía LV y la segunda línea de tierra LS son líneas conductoras para proporcionar al controlador principal 40 y al sub-controlador 50 respectivamente tensión de alimentación de energía VDD y potencial de tierra VSS. La tensión de alimentación de energía VDD utiliza un potencial del mismo nivel que la tensión de alimentación de energía CVDD proporcionada al dispositivo de memoria 130 mencionado anteriormente, por ejemplo de aproximadamente 3,3 V frente al potencial de tierra VSS y CVSS (0 V). Por supuesto, dependiendo de factores como la generación de procesador de la sección de lógica IC del sub-controlador 50, el nivel de potencial de la tensión de alimentación de energía VDD puede ser un potencial diferente, como 1,5 o 2,0 V por ejemplo. La tercera línea de señal de accionamiento de sensor LDS es una línea conductora para proporcionar una señal de accionamiento de sensor DS (que se describe más adelante) que se aplica en última instancia a cada sensor 110, desde el controlador principal 40 al sub-controlador 50.

El controlador principal 40 está provisto de un circuito de control 48, un circuito de generación de señal de accionamiento 42, y una ROM, RAM, EEPROM o similar (no mostrada). Hay varios programas para controlar la impresora 20 almacenados en la ROM.

El circuito de control 48 es una CPU (Unidad de Procesamiento Central), y lleva a cabo el control de la impresora 20 como un todo conjuntamente con la ROM, RAM, EEPROM u otra memoria. El circuito de control 48 está provisto de los bloques funcionales de un módulo de detección de nivel de tinta restante M1, un módulo de acceso a memoria M2, y un módulo de estimación de consumo de tinta M3.

El módulo de detección de nivel de tinta restante M1 controla el sub-controlador y el circuito de generación de señal

8

60

20

25

30

35

40

45

50

55

65

de accionamiento 42, acciona el sensor 110 del cartucho de tinta 100, y decide si la tinta en el cartucho de tinta 100 es igual que un valor prescrito o mayor. A través del sub-controlador 50, el módulo de acceso a memoria M2 accede al dispositivo de memoria 130 del cartucho de tinta 100 y bien lee la información almacenada en el dispositivo de memoria 130. El módulo de estimación de consumo de tinta M3 está diseñado para contar los puntos que se inyectan sobre el papel impreso en conjunto con condiciones de las operaciones de impresión de la impresora 20; y a partir de este valor de recuento y de la cantidad de tinta consumida por cada punto, estima la cantidad de tinta consumida por las operaciones de impresión. La cantidad de tinta consumida en las operaciones de limpieza de cabezales también se estima. Basándose en estas estimaciones, se lleva un recuento del valor acumulativo estimado para el consumo de tinta consumido del cartucho de tinta desde que el cartucho de tinta 100 se instaló por primera vez en la impresora 20.

10

15

20

25

30

35

40

45

50

55

60

65

La EEPROM del controlador principal 40 almacena datos que representan una señal de accionamiento de sensor DS para accionar el sensor. De acuerdo con una instrucción del módulo de detección de nivel de tinta restante M1 del circuito de control 48, el circuito de generación de señal de accionamiento 42 lee de la EEPROM datos que representan una forma de onda para la señal de accionamiento de sensor DS, y genera una señal de accionamiento de sensor DS que tiene la forma de onda deseada. La señal de accionamiento de sensor DS incluye un potencial que es mayor que la tensión de suministro de energía CVDD (en la presente realización, 3,3 V); en la presente realización, por ejemplo, incluye un potencial máximo de aproximadamente 36 V. Específicamente, la señal de accionamiento de sensor DS es una señal de pulsos trapezoidales que tienen una tensión máxima de 36 V.

En la presente realización, el circuito de generación de señal de accionamiento 42 puede además generar una señal de accionamiento de cabezal para su presentación al cabezal de impresión 5. Específicamente, en la presente realización, durante la determinación de la cantidad de tinta restante, el circuito de control 48 indica al circuito de generación de señal de accionamiento 42 que genere una señal de accionamiento de sensor, y durante las operaciones de impresión indica al circuito de generación de señal de accionamiento 42 que genere una señal de accionamiento de cabezal.

En cuanto a la configuración de hardware, el sub-controlador está provisto de un ASIC (CI de Aplicación Específica). El ASIC tiene un módulo de proceso de comunicación 55 y un módulo de proceso de sensor 52 como características funcionales.

El módulo de proceso de comunicación 55 lleva a cabo procesos de comunicación con el dispositivo de memoria 130 de cada uno de los cartuchos de tinta 100 a través de la línea de señal de reinicio LR1, la línea de señal de datos LD1, y la línea de señal de reloj LC1. El módulo de proceso de comunicación 55 también lleva a cabo procesos de comunicación con el controlador principal 40 a través del bus BS. Detectando los potenciales en los terminales prescritos del grupo de terminales de la placa de circuito 120, el módulo de proceso de comunicación 55 es capaz de detectar si la placa de circuito 120 de un cartucho de tinta 100 está eléctricamente conectada a la impresora 20, es decir, si el cartucho de tinta 100 está instalado en la impresora 20. El módulo de proceso de comunicación 55 notifica entonces al controlador principal 40 que ha detectado los cartuchos de tinta 100 instalados. A través de este proceso el controlador principal 40 puede determinar si los cartuchos de tinta 100 están montados en la sección de montaje de cartucho.

Si el controlador principal 40 determina que las placas de circuito 120 están eléctricamente conectadas y que los cartuchos de tinta 100 están instalados en la impresora 20, entonces accede a los dispositivos de memoria 130 de los cartuchos de tinta 100 instalados según una temporización prescrita, a través del módulo de proceso de comunicación 55.

El módulo de proceso de comunicación 55 es un circuito que incluye un circuito lógico compuesto por un ASIC o similar, y que es accionado por la tensión de alimentación de energía VDD (en la presente realización, 3,3 V). En la presente realización, el ASIC está compuesto por un bloque de área de célula de memoria (SRAM 551) y un área de lógica, estando provista el área de lógica de un registro de sensor 552 y un registro de código de error 553. La SRAM 551 es una memoria utilizada para quardar datos temporalmente durante las operaciones del módulo de proceso de comunicación 55, es decir, para quardar temporalmente datos recibidos del controlador principal 40, o datos recibidos de los sensores 110 o de los dispositivos de memoria 130, por ejemplo. Después de encender la impresora 20, en la SRAM 551 se asigna un espacio de memoria suficiente para almacenar datos que corresponden a los datos originales y que corresponden a datos especulares invertidos de los datos originales en el dispositivo de memoria 130 de cada cartucho de tinta 100 (se analiza más adelante); y los datos que se leen de los dispositivos de memoria se almacenan después en este espacio de memoria asignado. Específicamente, en el espacio de memoria en la SRAM 551 hay asignada un área de memoria suficiente para almacenar los datos originales de 16 bits y los datos especulares invertidos de los datos originales de 16 bits, en el mismo número de filas que la matriz de células de memoria de cada dispositivo de memoria 130. Entonces, los datos originales que se leen de la matriz de memoria de cada dispositivo de memoria, junto con los datos especulares invertidos de los mismos, se almacenan en el área de memoria asignada. Los valores que se leen al área de memoria se actualizan posteriormente en conjunto con las operaciones de impresión (en conjunto con la transmisión de datos de escritura desde el controlador principal 40 y la lectura de datos desde los dispositivos de memoria). Los errores de comunicación y los errores de célula de memoria, que se analizan más adelante, que se producen en relación con las filas en el área de memoria

reescribible de cada dispositivo de memoria 130 son escritos en el registro de códigos de error 553.

5

10

20

25

30

35

40

45

50

55

60

65

El registro de sensor 552 es un registro utilizado por el módulo de proceso de sensor 52 para escribir resultados de procesos de escritura de procesos de sensor. Está provisto un módulo de proceso de sensor 552 para cada cartucho de tinta, y se utiliza para grabar los resultados de la determinación del nivel de tinta restante, como se analiza más adelante.

El módulo de proceso de sensor 52 ejecuta un proceso de determinación de nivel de tinta restante utilizando el sensor (proceso de sensor), que se analiza más adelante. El módulo de proceso de sensor 52 incluye un interruptor de conmutación. El interruptor de conmutación se utiliza para presentar una señal de accionamiento de sensor DS suministrada por el circuito de generación de señal de accionamiento 42, al sensor 110 de un único cartucho de tinta 100 que constituye el objetivo del proceso de sensor, llevándose esto a cabo a través bien de la primera línea de señal de accionamiento de sensor LDSN, o bien la segunda línea de señal de accionamiento de sensor LDSP.

A continuación, se describe la configuración eléctrica de los cartuchos de tinta 100. Cada cartucho de tinta 100 tiene como sus elementos eléctricos un dispositivo de memoria 130 y un sensor 110.

El dispositivo de memoria 130 no está diseñado para aceptar la entrada externa de datos de dirección que especifican la dirección de una localización de acceso. El dispositivo de memoria 130 no acepta la entrada directa de datos de dirección; sin embargo, se puede controlar para especificar las células de memoria a las que se accede, en respuesta a una señal de reloj y datos de comando suministrados externamente. El dispositivo de memoria 130 incluye una matriz de células de memoria ferroeléctrica 132 provistas como la sección de memoria de datos; y un circuito de control de memoria 136. Como se indica a través de círculos blancos sobre las líneas discontinuas que representan el dispositivo de memoria 130 en la fig. 6, el dispositivo de memoria 130 está provisto de un terminal de tierra para la conexión eléctrica al terminal de tierra 210 de la placa de circuito 120, un terminal de alimentación para la conexión eléctrica al terminal de reinicio 240, y un terminal de reloj para la conexión eléctrica al terminal de reloj 250.

La matriz de células de memoria ferroeléctrica 132 es una matriz de células de memoria de semiconductor no volátiles que utiliza elementos de memoria ferroeléctricos y proporciona un área de memoria que tiene una característica de re-escritura de datos.

El circuito de control de memoria 136 está diseñado para controlar las operaciones de lectura y escritura en la matriz de células de memoria ferroeléctrica 132 en respuesta a los datos de comando del sub-controlador 50. El circuito de control de memoria 136 analiza datos de identificación y datos de comando enviados desde el sub-controlador. También, durante una operación de escritura, basándose en los datos de contenido de escritura recibidos del sub-controlador 50, el circuito de control de memoria 136 genera datos de escritura y los escribe en la matriz de células de memoria ferroeléctrica 132. O, durante una operación de lectura, basándose en los datos leídos de la matriz de células de memoria ferroeléctrica 132, el circuito de control de memoria 136 genera datos para la transmisión al sub-controlador 50. Esto se analizará con detalle más adelante.

El circuito de control de memoria 136 está dotado de un módulo comparador de ID M11, un módulo de análisis de comandos M12, un contador de direcciones M13, un módulo de control de lectura/escritura M14, un módulo de envío/recepción de datos M15, un módulo de control de contadores M16, un módulo de generación de datos de copia M17, un módulo de generación de datos invertidos M18, y un módulo de determinación de datos M19. El módulo comparador de ID M11 está diseñado para comparar datos de ID que se suministran desde el subcontrolador 50, y el número ID que está asignado a su propio dispositivo de memoria; y para decidir luego si el objetivo del acceso es el propio dispositivo de memoria. El número ID del dispositivo de memoria está almacenado en las células de memoria que están conectadas a la línea de palabra que se selecciona basándose en la salida del contador de direcciones M13 cuando el acceso desde el sub-controlador 50 se inicia posteriormente a la inicialización del dispositivo de memoria 130. Este número ID se utiliza para distinguir un dispositivo de memoria 130 que constituye el objetivo de acceso desde el sub-controlador 50, de entre los múltiples dispositivos de memoria 130 que están conectados mediante bus al sub-controlador 50. Este número ID puede elegirse de acuerdo con el color de la tinta contenida en el cartucho de tinta 100, por ejemplo. El módulo de análisis de comandos M12 está diseñado para analizar datos de Inicio de Trama (SOF, Start of Frame), datos de Final de Trama (EOF, End of Frame), y datos de comando enviados desde el sub-controlador 50, y para decidir el inicio del acceso y final del acceso desde el subcontrolador 50, así como el tipo de acceso (lectura, escritura, etc.). Cuando se introduce una señal de reinicio de bajo nivel CRST en el dispositivo de memoria 130 de modo que se inicialice el dispositivo de memoria 130, el contador de direcciones M13 reinicia el valor del contador. Durante el reinicio, el valor del contador se ajusta a un valor que selecciona la línea de palabra incluyendo las células de memoria en las que se almacena el número ID. A continuación, basándose en el control del módulo de control de contador M16, se cuenta secuencialmente un número prescrito de pulsos de reloj de entre los pulsos de reloj introducidos en el dispositivo de memoria 130. Cuando se accede a una célula de memoria a través del control por el módulo de control de lectura/escritura M14, el valor de contador del contador de direcciones M13 se emite desde el contador de direcciones M13 a un decodificador de direcciones de la matriz de células de memoria, no mostrado. En consecuencia, se selecciona una fila prescrita (línea de palabra) de la matriz de células de memoria 132 en correspondencia con el valor del contador.

5

10

15

20

25

30

35

40

45

50

55

60

65

En la presente realización, se selecciona una "fila" por parte del decodificador de direcciones basándose en el valor del contador emitido por el contador de direcciones M13. De acuerdo con el contenido de los datos de comando (indicativos del tipo de acceso) que fue analizado por el módulo de análisis de comandos M12, el módulo de control de lectura/escritura M14 lleva a cabo una operación de escritura por lotes sobre una única fila y una operación de lectura por lotes desde una única fila de la matriz de memoria ferroeléctrica 132 que está conectada a la línea de palabra seleccionada por el contador de direcciones M13. El módulo de control de lectura/escritura M14 está provisto de un registro, no mostrado, y es capaz de almacenar temporalmente datos originales, datos invertidos, y dados especulares, que se analizan más adelante con mayor detalle. El módulo de envío/recepción de datos M15 en sincronía con la señal de reloj CSCK recibe una señal de datos CSDA enviada desde el sub-controlador 50 a través de la línea de señal de datos LD1, o en sincronía con la señal de reloj CSCK envía una señal de datos CSDA a través de la línea de señal de datos LD1. Específicamente, el módulo de envío/recepción de datos M15 establece la dirección de envío/recepción de datos de las señales de datos CSDA intercambiadas entre el dispositivo de memoria 130 y el sub-controlador 50. Después de la inicialización, cuando se inicia el acceso al dispositivo de memoria 130 por el sub-controlador, la dirección de envío/recepción del módulo de envío/recepción de datos M15 se establece en la dirección en la que el dispositivo de memoria 130 recibe señales de datos CSDA enviadas desde el subcontrolador 50, de modo que los datos enviados desde la matriz de células de memoria 132 no es enviada desde el dispositivo de memoria 130 al sub-controlador 50. El módulo de generación de datos de copia M17 está adaptado para copiar datos originales (se analiza más adelante) para generar datos especulares (se analiza más adelante) de igual tamaño que los datos originales. El módulo de generación de datos invertidos M18 está adaptado para invertir el valor de cada bit de los datos originales para generar datos invertidos (se analiza más adelante) de igual tamaño que los datos originales. El módulo de determinación de datos M19 está diseñado para llevar a cabo una comprobación de paridad y una operación OR exclusiva de los datos originales y los datos especulares, analizados más adelante, para determinar la consistencia de los datos. El módulo de control de contadores M16 está dotado de un contador de reloj. Después de que el acceso al dispositivo de memoria 130 por parte del sub-controlador 50 se inicie después de que se inicialice el dispositivo de memoria 130, el módulo de control de contadores M16 cuenta el número de pulsos de reloj de la señal de reloj CSCK introducida en el dispositivo de memoria 130. Después de alcanzarse un valor de contador prescrito, basándose en el resultado del análisis de comandos por el módulo de análisis de comandos M12, el módulo de control de contadores M16 emite una señal de control al contador de direcciones M13 para provocar que el contador de direcciones M13 bien aumente o bien disminuya el valor del contador. El módulo de envío/recepción de datos M15 de la presente realización corresponde a la sección de recepción de datos y a la sección de transmisión de datos de la presente invención.

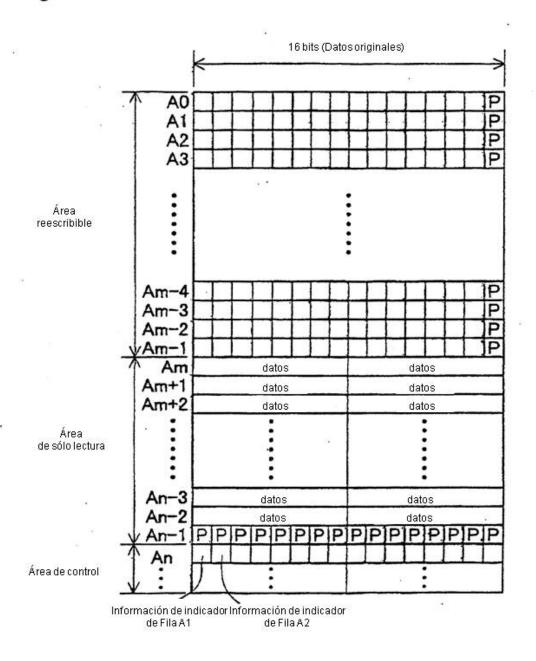

La fig. 7 es un dibuio que representa esquemáticamente un mapa de memoria de la matriz de memoria ferroeléctrica 132 del dispositivo de memoria 130. En la fig. 7, el mapa de memoria de la matriz de memoria ferroeléctrica 132 está compuesto por múltiples filas, donde cada fila tiene 32 células. A la matriz de células de memoria 132 se accede secuencialmente, por orden de fila seleccionada por el valor indicado por el contador de direcciones. En el mapa de memoria representado en la fig. 7, el orden de acceso secuencial es desde el lado superior al inferior, en unidades de filas. Aquí, por conveniencia, en cualquier fila dada, las células de memoria más hacia el lado izquierdo (el lado D31) se denominan células de orden superior. Para filas diferentes, una fila de orden superior que una fila particular significa una fila en el lado superior (una fila que tiene un número de fila menor) que la fila particular de la fig. 7; y una fila de orden inferior que una fila particular significa una fila en el lado inferior (una fila que tiene un número de fila mayor) que la fila particular de la fig. 7. Como se muestra en el mapa, la matriz de células de memoria 132 tiene un área de información de identificación, un área reescribible, un área de sólo lectura, y un área de control. El área de información de identificación tiene el área de memoria de 32 bits de la Fila A0, y se utiliza para almacenar el número ID mencionado anteriormente. El área reescribible tiene un área de memoria de (m-1) filas, donde m es un número natural, desde la Fila A1 a la Fila Am-1 en la fig. 7. El área reescribible es un área a la que se accede con el propósito de reescribir datos por el sub-controlador 50 de la impresora 20. El área de sólo lectura tiene un área de memoria de (n-m) filas desde las Filas Am hasta An-1. Al área de sólo lectura se accede con el propósito exclusivo de leer datos por parte del sub-controlador de la impresora 20. Se proporciona el área de control como un área de orden inferior del área de sólo lectura. El área de control es un área de memoria para almacenar información de indicador de incremento e información de indicador de bloqueo de escritura, que se analizarán más adelante. Cada fila única de las áreas de almacenamiento del mapa de memoria de la matriz de células de memoria 132 tiene una capacidad de almacenamiento de 32 bits. Una única fila corresponde a una fila seleccionada por el contador de direcciones M13 (es decir, una línea de palabra). Dentro de una única fila, los 16 bits superiores representan un área de datos para almacenar datos originales. Aquí, datos originales hace referencia a datos que son la fuente para los datos invertidos y los datos especulares, que se analizarán más adelante. En el presente documento, el área de datos para almacenar los datos originales se denomina el área de datos originales. Dentro de una única fila, los 16 bits inferiores representan un área de datos para almacenar datos especulares que son una copia de los datos originales que están almacenados en los 16 bits superiores. En este documento, el área de datos para almacenar los datos especulares se denomina área de datos especulares. En la fig. 7, la mitad izquierda representa el área de datos originales, y la mitad derecha representa el área de datos especulares. Dicho del modo opuesto, en la fig. 7 los datos que se almacenan en el área de datos originales en la mitad izquierda son los datos originales, y los datos que se almacenan en el área de datos especulares en el lado derecho son los datos especulares. Bajo circunstancias normales, es decir, en ausencia de ningún error de escritura o células defectuosas en una fila dada, los datos originales y los datos especulares de cada fila tienen contenido idéntico.

En el área de información de identificación y en el área reescribible, los 15 bits superiores del área de datos originales de cada fila se utilizan para almacenar datos reales; mientras que el último bit (el bit decimosexto) se utiliza para almacenar datos de paridad P que están asociados a los datos reales. En la presente realización, los datos reales son datos utilizados por el controlador principal 40 de la impresora 20 para controlar varios aspectos del funcionamiento de la impresora 20 (por ejemplo, operaciones de impresión, control de la interfaz de usuario). En la presente realización, los datos reales incluyen, por ejemplo, datos que representan el nivel de tinta restante, la fecha y hora en que el cartucho de tinte fue puesto por primera vez en servicio, etc. Los 15 bits superiores del área de datos especulares se utilizan para almacenar datos especulares de los datos reales de los datos originales, mientras que el último bit (el bit decimosexto) se utiliza para almacenar datos especulares de los datos de paridad P que están asociados a los datos reales de los datos originales. Los datos de paridad P consisten en un bit redundante que se establece en un valor que puede ser bien "1" o "0", de tal manera que el número de bits de valor "1" en los 16 bits de datos que consisten en los 15 bits superiores y el dato P de paridad siempre es un número impar. El dato P de paridad puede por el contrario ajustarse bien a "1" o a "0" de tal modo que el número de bits de valor "1" en los datos de 16 bits que consisten en los 15 bits superiores y el bit de paridad P es siempre un número par. Los datos de paridad P no deberían interpretarse como limitantes, y podrían utilizarse en su lugar cualquiera de los varios tipos de datos redundantes que proporcionan una redundancia de los datos reales.

5

10

15

20

25

30

35

40

45

50

55

60

65

De las (n-m) filas del área de sólo lectura, todas las filas excepto la última fila An-1 se utilizan para almacenamiento de datos reales, mientras que la última fila se utiliza para el almacenamiento de datos de paridad. Específicamente, para cada una de las unidades prescritas de datos reales (por ejemplo, unidades de 8 bits o de 16 bits) de las filas excepto la última fila, se asignan datos de paridad de 1 bit a un bit de la última fila. En la fig. 7, las células nombradas como "P" representan las áreas de memoria de 1 bit para almacenar datos de paridad P.

Como se apreciará a partir de la discusión anterior, en el área de información de identificación y en el área reescribible, los datos originales consisten en datos reales y datos de paridad. En el área de sólo lectura, en áreas diferentes de la última fila, los datos originales son datos reales per se. En el área de sólo lectura, en la última fila, los datos originales son datos de paridad.

El área reescribible almacena varios tipos de información, por ejemplo, información acerca del nivel de tinta restante o información acerca del historial de uso para el cartucho de tinta 100. El número ID (información de identificación, que se elige para cada tipo (color) de cartucho de tinta 100, se almacena en los 8 bits empezando desde la célula delantera en la primera fila delantera (el área de información de identificación de Fila A0) que es seleccionada por el valor inicial del contador de direcciones M13 inmediatamente después que se inicie el acceso al dispositivo de memoria 130. En la fig. 7, el área que almacena el número ID está indicada por un sombreado fino. El resto de células de la Fila A0, es decir, exceptuando las células de bit de paridad de los datos originales y las células que almacenan el número ID, constituyen áreas vacías y almacenan datos fijos que pueden adoptar el valor 0 o 1. Por ejemplo, cuando el número de cartuchos de tinta 100 instalados en la impresora 20 es n, el número ID puede adoptar n tipos de valores que difieren de acuerdo con el tipo de cartucho de tinta 100. La primera fila del área reescribible (Fila A1) almacena un primer valor de recuento de consumo de tinta X (por ejemplo, en 10 bits), y la segunda fila (Fila A2) almacena un segundo valor de recuento de consumo de tinta Y (por ejemplo, en 10 bits). El primer valor de recuento de consumo de tinta X representa información de 10 bits por ejemplo, y es almacenado en las células de los 10 bits inferiores entre los 15 bits exceptuando la célula de información de paridad de la Fila A1. Los 5 bits restantes de la fila A1 constituyen un área vacía que almacena datos fijos, y se envían datos desde la impresora 20 de modo que siempre se almacena "1" en los mismos. En la fig. 7, el área que almacena el primer valor de recuento de consumo de tinta X aparece indicada mediante un sombreado grueso. El segundo valor de recuento de consumo de tinta Y representa información de 10 bits por ejemplo, y se almacena en las células de los 10 bits inferiores de entre los 15 bits exceptuando la célula de información de paridad de la Fila A2. Los 5 bits restantes de la Fila A2 constituyen un área vacía, y se envían datos desde la impresora 20 de modo que siempre se almacena "1" en los mismos. En la fig. 7, el área que almacena el segundo valor de recuento de consumo de tinta Y aparece indicado por medio de un sombreado cruzado. El primer valor de recuento de consumo de tinta X y el segundo valor de recuento de consumo de tinta Y son valores que representan el consumo total de tinta acumulativo para cada cartucho de tinta 100, obtenido basándose en el consumo de tinta estimado por el módulo de estimación de consumo de tinta M3 de la impresora 20. También se almacena información de final de tinta M en una fila prescrita del área reescribible. La información de final de tinta M pueden ser datos de 2 bits que pueden adoptar uno de entre tres estados "01", "11" o "01", por ejemplo. "01" representa un estado en el que el sensor 110 del cartucho de tinta 100 no ha detectado que el nivel de tinta restante es igual o menor que un primer valor umbral Vref1 (al que en adelante también se denomina como el estado lleno), es decir, que el nivel de tinta restante es mayor que el primer valor umbral Vref1. "10" representa un nivel de tinta restante igual o menor que el primer valor umbral Vref1 y mayor que el nivel de final de tinta (al que en adelante también se denomina como el estado bajo; es decir, primer valor umbral Vref1 > nivel de final de tinta. El hecho de que el nivel de tinta restante sea igual o menor que el primer valor umbral Vref1 es detectado por el sensor 110 del cartucho de tinta 100 en cuestión. "11" representa un nivel de tinta restante en o por debajo del nivel de final de tinta (al que en adelante también se denomina como estado final). El nivel de final de tinta es un nivel de tinta restante en el que, si la impresora 20 continua imprimiendo ininterrumpidamente, aparece el riesgo de que entre aire en la unidad de cabezal de impresión 60 debido al agotamiento de la tinta, por lo que es imperativo sustituir el cartucho de tinta 100. Por ejemplo, el primer valor umbral Vref1 puede establecerse en aproximadamente 1,5 gramos, y el nivel de final de tinta puede establecerse en un

nivel de tinta restante de aproximadamente 0,8 gramos. Los procesos relativos al primer valor de recuento de consumo de tinta X, el segundo valor de recuento de consumo de tinta Y, y la información de final de tinta M se analizarán más adelante.

El área de sólo lectura almacena, por ejemplo, información del fabricante que indica el fabricante del cartucho de tinta 100, la fecha de fabricación del cartucho de tinta, la capacidad del cartucho de tinta 100, el tipo de cartucho de tinta, etc. El área de control almacena información de indicador de incremento e información de bloqueo de escritura.

Está provisto un bit de información de indicador de incremento para cada fila del mapa de memoria. Una fila cuya información de indicador de incremento se establece en "1" representa un área en la que se permite que la fila sea sobrescrita sólo con un valor numérico mayor que el valor numérico ya almacenado en la fila (sobreescritura incremental), pero no se permite que la fila sea sobrescrita con un valor numérico más pequeño que el valor numérico ya almacenado en la fila (sobreescritura decremental). Una fila cuya información de indicador de incremento asociada está establecida en "0" puede ser sobreescrita libremente. La decisión acerca de si permitir sólo sobreescrituras incrementales o permitir sobreescritura libre es tomada por el módulo de control de lectura/escritura M14 del circuito de control de memoria 136, con referencia a la información de indicador de incremento. Específicamente, para la Fila A1 y la Fila A2 que almacenan el primer valor de recuento de consumo de tinta X y el segundo valor de recuento de consumo de tinta Y mencionados anteriormente, la correspondiente información de indicador de incremento se establece en "1". El motivo es que es difícil de imaginar que la actualización del primer valor de recuento de consumo de tinta X y el segundo valor de recuento de consumo de tinta Y por la impresora 20 tuviera lugar de un modo diferente que en la dirección del aumento. Esto puede reducir la probabilidad de errores de escritura en la Fila A1 y la Fila A2. A partir de ahora en el presente documento, a las áreas de memoria para las cuales, como la Fila Á1 y la Fila A2, la correspondiente información de indicador de incremento se establece en "1" también se denominan como áreas de incremento. Sobreescribir en una fila puede ser permitido en los casos en los que la sobreescritura de datos es una sobreescritura incremental realizada en unidades de datos originales de 16 bits en lugar de en unidades de fila. Cuando el nivel de tinta restante, en lugar del consumo de tinta, se guarda en una fila de la memoria, esta fila puede ser controlada por un valor de indicador que indica si se permite sólo sobreescritura decremental o si se permite sobreescritura libre.

30 Está provisto un bit de información de indicador de bloqueo de escritura para cada fila en el área de información de identificación, el área reescribible, y el área de sólo lectura. Una fila cuya información de indicador de bloqueo de escritura está establecida en "1" representa un área que no se permite reescribir mediante acceso externo. Una fila cuya información de indicador de bloqueo de escritura está establecida en "0" representa un área que se permite rescribir mediante acceso externo. La decisión acerca de si permitir sobreescritura es tomada por el módulo de 35 control de lectura/escritura M14 del circuito de control de memoria 136, con referencia a la información de indicador de bloqueo de escritura. Para el área reescribible, es decir, las Filas A1 a Am-1, la información de indicador de bloqueo de escritura se establece en "0" en la fábrica antes de su envío, para permitir el borrado y/o la rescritura de datos por el módulo de proceso de comunicación 55 de la impresora 20. Por otro lado, para el área de información de identificación, es decir, la Fila A0, y para el área de sólo lectura, es decir, las Filas Am a An-1, la información de 40 indicador de bloqueo de escritura se establece en "1" en la fábrica antes de su envío, para prohibir el borrado y/o la rescritura de datos por el módulo de proceso de comunicación 55 de la impresora 20. Tales áreas de memoria para las cuales la información de indicador de bloqueo de escritura se establece en "1" son también denominadas como áreas con escritura bloqueada.

45 El sensor 110, que no se representa con detalle en los dibujos, está dotado de una cavidad (porción de resonancia) que define parte del canal de fluio de tinta cerca de la sección de suministro de tinta: una placa oscilante que forma parte de la pared de la cavidad; y un elemento piezoeléctrico dispuesto sobre la placa oscilante. El módulo de proceso de sensor 52 de la impresora 20 puede aplicar una señal de accionamiento de sensor DS al elemento piezoeléctrico a través de los terminales de accionamiento de sensor 230, 270, e inducir de ese modo la oscilación 50 de la placa oscilante a través del elemento piezoeléctrico. Entonces, recibiendo del elemento piezoeléctrico una señal de respuesta RS que tiene la frecuencia de la vibración residual de la placa oscilante, el módulo de proceso de sensor 52 puede detectar si hay presencia o ausencia de tinta en la cavidad. Específicamente, si la tinta contenida en el cuerpo principal 101 se consume de modo que el estado del interior de la cavidad cambia desde un estado lleno de tinta a un estado lleno de aire, la frecuencia de la vibración residual de la placa oscilante cambia. Este 55 cambio de frecuencia se refleja en un cambio de frecuencia de la señal de respuesta RS. Midiendo la frecuencia de la señal de respuesta RS, el módulo de proceso de sensor 52 puede detectar si hay presencia o ausencia de tinta en la cavidad. La detección de que hay "ausencia" de tinta en la cavidad significa que el nivel de tinta restante contenido en el cuerpo principal 101 es igual o menor que el primer valor umbral Vref1 (esto corresponde a la cantidad de tinta restante corriente abajo de la cavidad). Detectar que hay "presencia" de tinta en la cavidad significa 60 que el nivel de tinta restante contenida en el cuerpo principal 101 es mayor que el primer nivel umbral Vref1.

# Operación de lectura del dispositivo de memoria

10

15

20

25

65

La fig. 8 es un diagrama de flujo que representa una rutina de procesamiento de una operación de lectura del dispositivo de memoria 130, ejecutada por el sub-controlador 50 de la impresora 20. La fig. 9 es un diagrama de temporización que representa esquemáticamente señales intercambiadas entre el módulo de proceso de

comunicación 55 de la impresora 20 y el circuito de control de memoria 136 del dispositivo de memoria 130 durante una operación de lectura desde el dispositivo de memoria 130. En la fig. 9, se representa un ejemplo de una tensión de alimentación de energía CVDD, una señal de reinicio CRST, una señal de reloj CSCK, y una señal de datos CSDA. La tensión de alimentación de energía CVDD es una señal que aparece en la primera línea de alimentación de energía LCV que conecta el sub-controlador 50 y el dispositivo de memoria 130, y es suministrada al dispositivo de memoria 130 por el sub-controlador 50. La señal de reinicio CRST es una señal que aparece en la línea de señal de reinicio LR1 que conecta el sub-controlador 50 y el dispositivo de memoria 130, y es suministrada al dispositivo de memoria 130 por el sub-controlador 50. La señal de reloj CSCK es una señal que aparece en la línea de señal de reloj LC1 que conecta el sub-controlador 50 y el dispositivo de memoria 130, y es suministrada al dispositivo de memoria 130 por el sub-controlador 50. La señal de datos CSDA es una señal que aparece en la línea de señal de datos LD1 que conecta el sub-controlador 50 y el dispositivo de memoria 130. En la fig. 9, también se indica la dirección de los datos de la señal de datos CSDA. Las flechas que apuntan hacia la derecha representan la dirección en la que el sub-controlador 50 está en el lado de envío y el dispositivo de memoria 130 está en el lado de recepción. Las flechas que apuntan hacia la izquierda representan la dirección en la que el sub-controlador 50 está en el lado de recepción y el dispositivo de memoria 130 está en el lado de envío. En la presente realización, el dispositivo de memoria 130 envía y recibe datos de manera síncrona con la subida de la señal de reloj CSCK que le presenta el sub-controlador 50. El envío y recepción de datos tiene lugar cuando la señal de reloi CSCK sube y el nivel de la señal de datos en el terminal de datos del dispositivo de memoria 130 tiene un valor válido para el envío o recepción de datos. La fig. 10 es un diagrama de flujo que representa esquemáticamente la rutina de procesamiento de una operación ejecutada por el circuito de control de memoria 136 en el lado de memoria.

10

15

20

25

30

35

65

El controlador principal 40 de la impresora 20, a través del bus BS, envía al sub-controlador 50 un comando de Lectura que ordena que se lleve a cabo una operación de lectura del dispositivo de memoria 130 del cartucho de tinta 100. El módulo de proceso de comunicación 55 suministra la tensión de alimentación de energía CVDD a cada uno de los cartuchos de tinta 100 a través de la primera línea de alimentación de energía LCV. Específicamente, se suministra una tensión de operación al dispositivo de memoria 130 de cada uno de los cartuchos de tinta 100, poniendo así el dispositivo de memoria 130 en el estado operativo. Después de suministrar la tensión de alimentación de energía CVDD, se suministra una señal de reinicio de bajo nivel para inicializar los dispositivos de memoria 130. Como la señal de reinicio permanece en un nivel bajo desde el momento en que terminó el acceso anterior, está en un nivel bajo incluso antes de que se suministre la tensión de alimentación de energía al dispositivo de memoria 130. Cuando el módulo de proceso de comunicación 55 del sub-controlador recibe el comando de Lectura, comienza la operación de lectura representada en el diagrama de la fig. 8.