(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 492 680**

(51) Int. Cl.:

**G01R 19/00** (2006.01)

**H03F 1/32** (2006.01)

**H03F 3/24** (2006.01)

**H03F 1/02** (2006.01)

**H03F 3/19** (2006.01)

**H03F 3/21** (2006.01)

**H03F 3/217** (2006.01)

**H03F 3/72** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: **12.03.2007 E 11181888 (6)**

(97) Fecha y número de publicación de la concesión europea: **14.05.2014 EP 2405277**

---

(54) Título: **Sistemas y procedimientos de transmisión, modulación y amplificación de potencia de RF**

(30) Prioridad:

**24.04.2006 US 794121 P**

**05.05.2006 US 797653 P**

**09.05.2006 US 798705 P**

**24.08.2006 US 508970**

**24.08.2006 US 509031**

**24.08.2006 US 508989**

(45) Fecha de publicación y mención en BOPÍ de la traducción de la patente:

**10.09.2014**

(73) Titular/es:

**PARKERVISION, INC. (100.0%)**

7915 Baymeadows Way

Jacksonville, FL 32256, US

(72) Inventor/es:

**SORRELLS, DAVID F.;**

**RAWLINS, GREGORY S. y**

**RAWLINS, MICHAEL W.**

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

**ES 2 492 680 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Sistemas y procedimientos de transmisión, modulación y amplificación de potencia de RF

La presente invención se refiere, en general, a la transmisión, modulación y amplificación de potencia de RF. Más en particular, la invención se refiere a procedimientos y sistemas para una amplificación de potencia mejorada.

5    **Técnica anterior**

En los amplificadores de potencia, típicamente existe una relación compleja entre la linealidad y la eficiencia energética.

10    La linealidad se determina mediante el intervalo de operación de un amplificador de potencia sobre una curva característica que relaciona su entrada con las variables de salida - cuanto más lineal es el intervalo de operación, se dice que el amplificador de potencia es más lineal. La linealidad es una característica deseada de un amplificador de potencia. En un aspecto, por ejemplo, se desea que un amplificador de potencia amplifique de manera uniforme unas señales de amplitud y / o fase y / o frecuencia variables. Por consiguiente, la linealidad es un importante factor determinante de la calidad de señal de salida de un amplificador de potencia.

15    La eficiencia energética puede calcularse usando la relación de la potencia total entregada a una carga dividida por la potencia total suministrada al amplificador. Para un amplificador ideal, la eficiencia energética es de un 100 %. Típicamente, los amplificadores de potencia se dividen en unas clases que determinan la eficiencia energética teórica máxima del amplificador. La eficiencia energética es, claramente, una característica deseada de un amplificador de potencia, en particular, en los sistemas de comunicación inalámbrica en los que el consumo de energía se ve dominado de forma significativa por el amplificador de potencia.

20    Desafortunadamente, el compromiso tradicional entre la linealidad y la eficiencia en los amplificadores de potencia es tal que, cuanto más lineal es un amplificador de potencia, menos eficiente es la potencia. Por ejemplo, el amplificador más lineal se polariza para el funcionamiento de clase A, que es la clase menos eficiente de amplificadores. Por otro lado, los amplificadores de clase más alta, tal como la clase B, C, D, E, etc., son de una eficiencia energética mayor, pero son considerablemente no lineales, lo que puede dar como resultado unas señales de salida espectralmente distorsionadas.

25    El compromiso que se ha descrito en lo que antecede se ve subrayado por las señales de comunicación inalámbrica típicas. Las señales de comunicación inalámbrica, tales como, por ejemplo, OFDM, CDMA y W - CDMA, se caracterizan en general por sus relaciones de potencia de pico a promedio. Cuanto mayor sea la relación de pico a promedio de la señal, más distorsión no lineal se producirá cuando se empleen unos amplificadores no lineales. El documento US2004/0185805 divulga un transmisor de potencia de LIMC.

30    Se han propuesto técnicas de amplificación por desfase para los diseños de amplificador de RF. En diversos aspectos, no obstante, las técnicas por desfase existentes son deficientes en cuanto a satisfacer los requisitos de amplificación de señales complejas, en particular tal como se define, por ejemplo, por las normas de comunicación inalámbrica.

35    En un aspecto, las técnicas por desfase existentes emplean un elemento de aislamiento y / o uno de combinación cuando se combinan unas constituyentes de envolvente constante de una señal de salida deseada. Por ejemplo, habitualmente es el caso que un circuito combinador de potencia se use para combinar las señales de constituyente. Este enfoque de combinación, no obstante, típicamente da como resultado un deterioro de la potencia de señal de salida debido la pérdida de inserción y al limitado ancho de banda y, de forma correspondiente, una disminución en cuanto a la eficiencia energética.

40    En otro aspecto, el tamaño típicamente grande de los elementos de combinación impide tener los mismos en los diseños de amplificador monolíticos.

45    Lo que se necesita, por lo tanto, son unos procedimientos y sistemas de amplificación de potencia que solucionen las deficiencias de las técnicas de amplificación de potencia existentes a la vez que se maximiza la eficiencia energética y se minimiza la distorsión no lineal. Además, son necesarios unos procedimientos y sistemas de amplificación de potencia que puedan implementarse sin las limitaciones de las técnicas, y la circuitería de combinación de potencia, tradicionales.

**Breve sumario**

50    En el presente documento se divultan unas realizaciones para la amplificación de potencia de combinación de vectores.

En una realización, una pluralidad de señales de envolvente sustancialmente constante se amplifican de forma individual, a continuación se combinan para formar una señal de envolvente compleja variable en el tiempo deseada. Las características de fase y / o de frecuencia de una o más de las señales se controlan para proporcionar las características de fase, de frecuencia y / o de amplitud deseadas de la señal de envolvente compleja variable en el

tiempo deseada.

En otra realización, una señal de envolvente compleja variable en el tiempo se descompone en una pluralidad de señales de constituyente de envolvente sustancialmente constante. Las señales de constituyente se amplifican y, a continuación, se recombinan para construir una versión amplificada de la señal de envolvente variable en el tiempo original.

Las realizaciones de la presente invención pueden ponerse en práctica con unas señales portadoras moduladas y con una información de banda de base y unas señales de reloj. Las realizaciones de la presente invención también consiguen una conversión elevadora en frecuencia. Por consiguiente, las realizaciones de la presente invención representan soluciones integradas para una conversión elevadora en frecuencia, amplificación y modulación.

- 5 Las realizaciones de la presente invención pueden implementarse con controles analógicos y / o digitales. Las realizaciones de la presente invención pueden implementarse con componentes analógicos o con una combinación de componentes analógicos y de componentes digitales. En la última realización, puede implementarse un procesamiento de señales digitales en un procesador de banda de base existente para unos ahorros de costes añadidos.

- 10 Las realizaciones de la presente invención pueden implementarse con controles analógicos y / o digitales. Las realizaciones de la presente invención pueden implementarse con componentes analógicos o con una combinación de componentes analógicos y de componentes digitales. En la última realización, puede implementarse un procesamiento de señales digitales en un procesador de banda de base existente para unos ahorros de costes añadidos.

- 15 En la descripción que sigue se expondrán características y ventajas adicionales de las realizaciones de la presente invención. Todavía más características y ventajas serán evidentes para un experto en la materia, en base a la descripción que se expone en el presente documento, o pueden aprenderse mediante la práctica de las realizaciones de la presente invención. Las ventajas de las realizaciones de la presente invención se realizarán y se conseguirán mediante los procedimientos y la estructura que se señalan, en particular, en la descripción escrita y en las reivindicaciones del presente documento, así como en los dibujos adjuntos.

- 20

Ha de entenderse que tanto el sumario precedente como la siguiente descripción detallada son ejemplares y explicativos y se pretende que proporcionen una explicación adicional de las realizaciones de la presente invención tal como se reivindica.

#### **Breve descripción de las figuras**

- 25 Las realizaciones de la presente invención se describirán con referencia a los dibujos adjuntos, en los que unos números de referencia semejantes indican, en general, unos elementos idénticos o funcionalmente similares. Asimismo, en general, el dígito o dígitos más a la izquierda de los números de referencia identifican los dibujos en los que se introducen en primer lugar los elementos asociados.

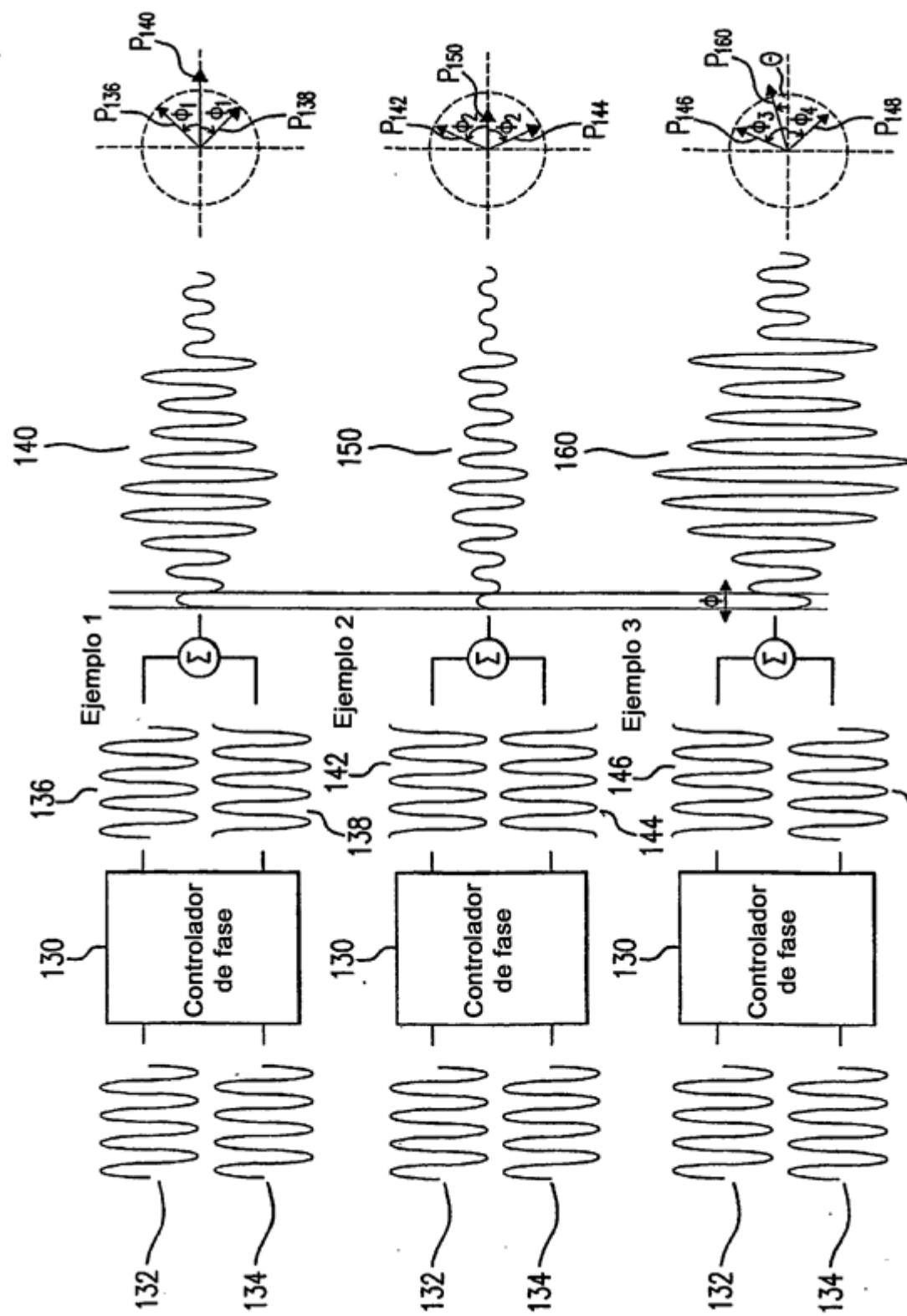

- 30 La figura 1A es un ejemplo que ilustra la generación de una señal de envolvente compleja variable en el tiempo ejemplar.

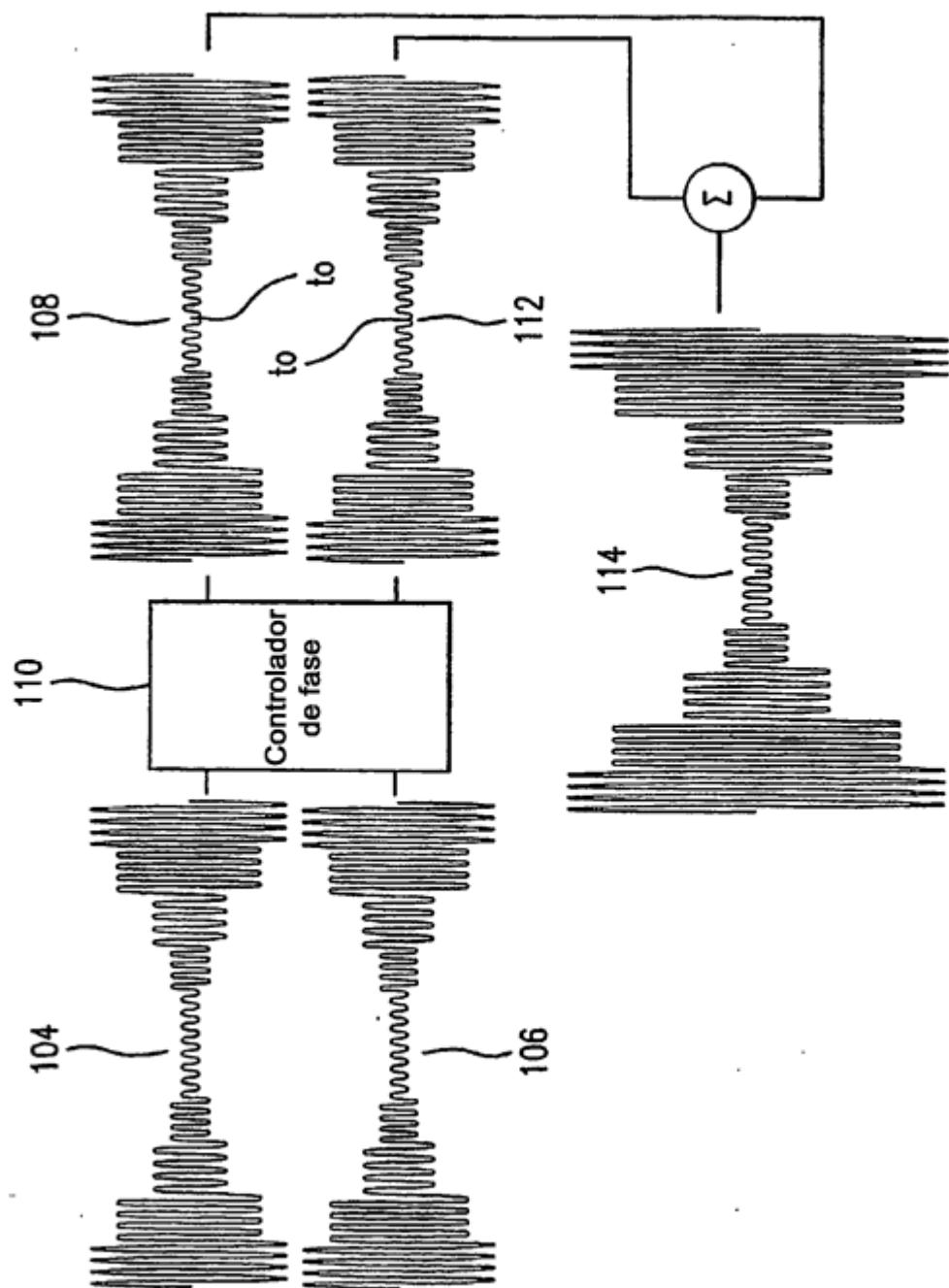

- La figura 1B es otro ejemplo que ilustra la generación de una señal de envolvente compleja variable en el tiempo ejemplar.

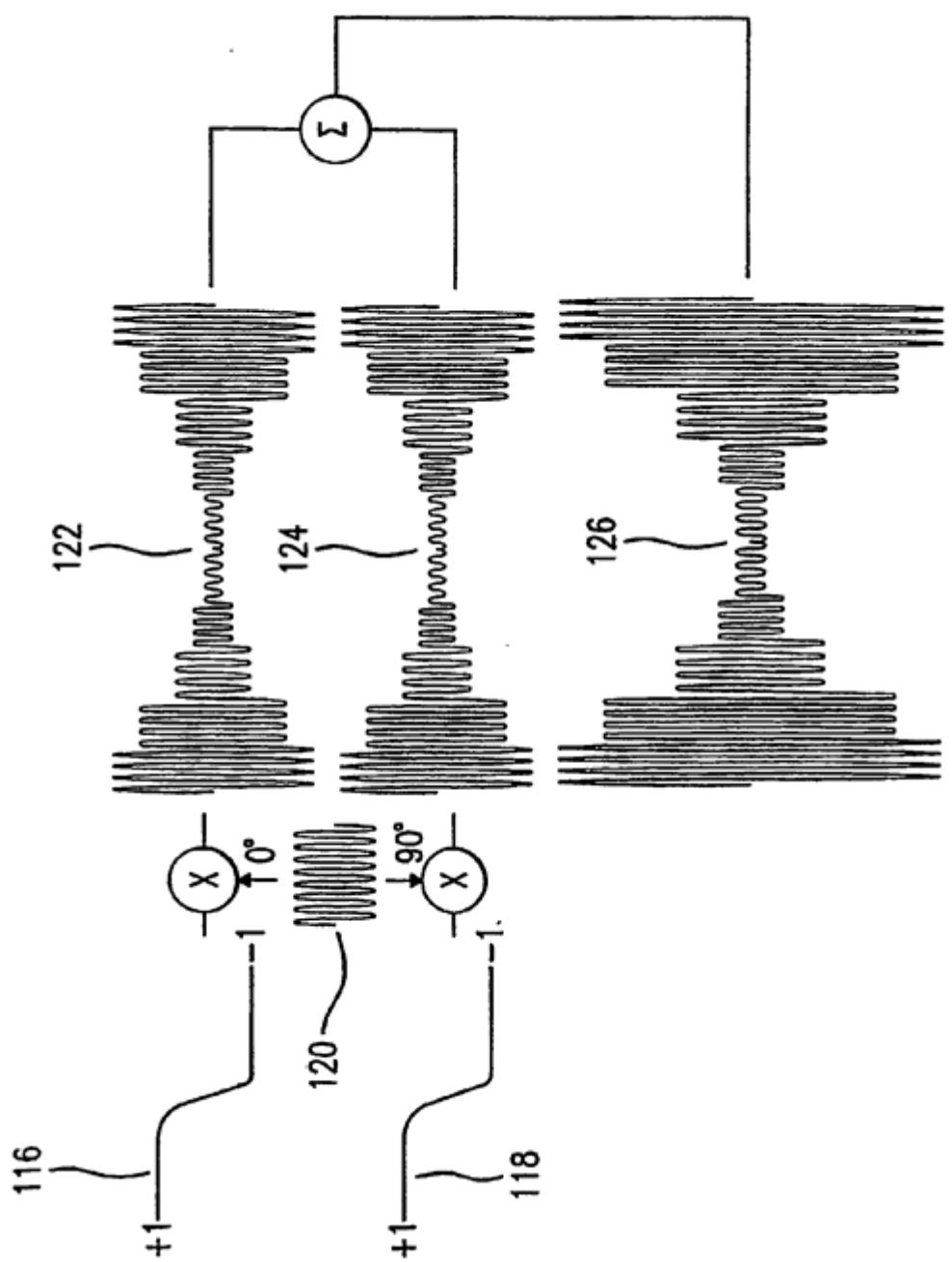

- La figura 1C es un ejemplo que ilustra la generación de una señal de envolvente compleja variable en el tiempo ejemplar a partir de la suma de dos o más señales de envolvente constante.

- 35 La figura 1D ilustra la amplificación de potencia de una señal de envolvente compleja variable en el tiempo a modo de ejemplo.

- La figura 1E es un diagrama de bloques que ilustra una amplificación de potencia vectorial a modo de ejemplo.

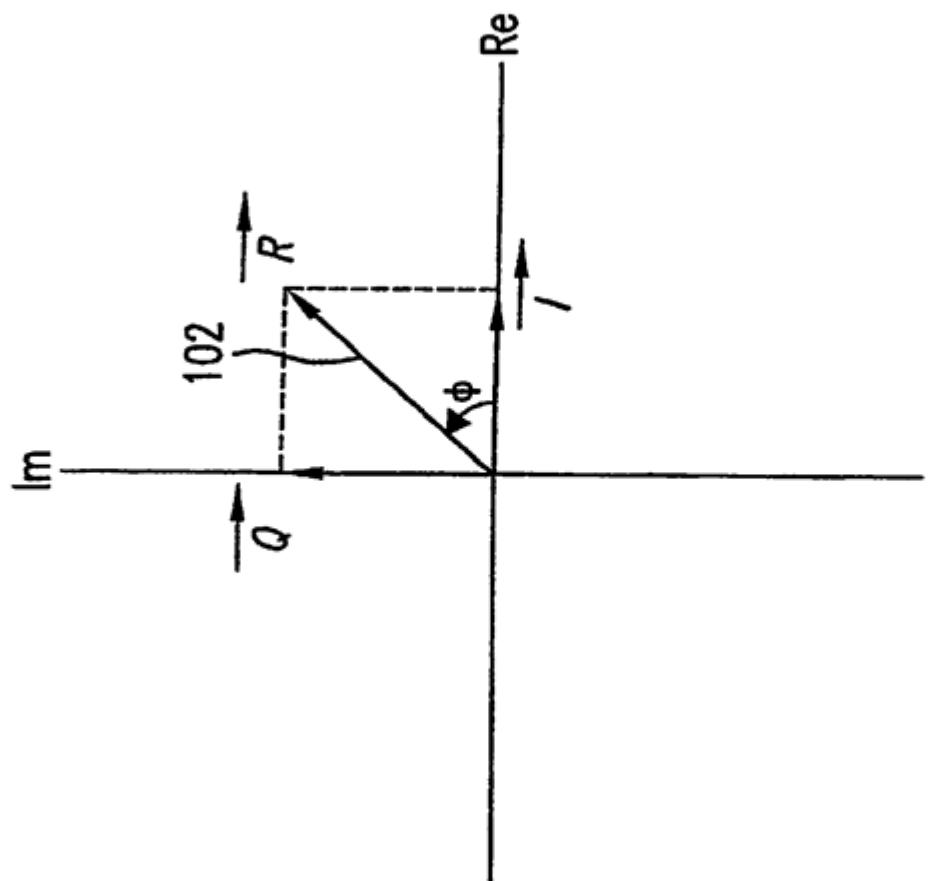

- La figura 1 ilustra una representación fasorial de una señal.

- 40 La figura 2 ilustra una representación fasorial de una señal de envolvente compleja variable en el tiempo.

- Las figuras 3A - 3C ilustran una modulación a modo de ejemplo para generar una señal de envolvente compleja variable en el tiempo.

- La figura 3D es un ejemplo que ilustra una descomposición de envolvente constante de una señal de envolvente variable en el tiempo.

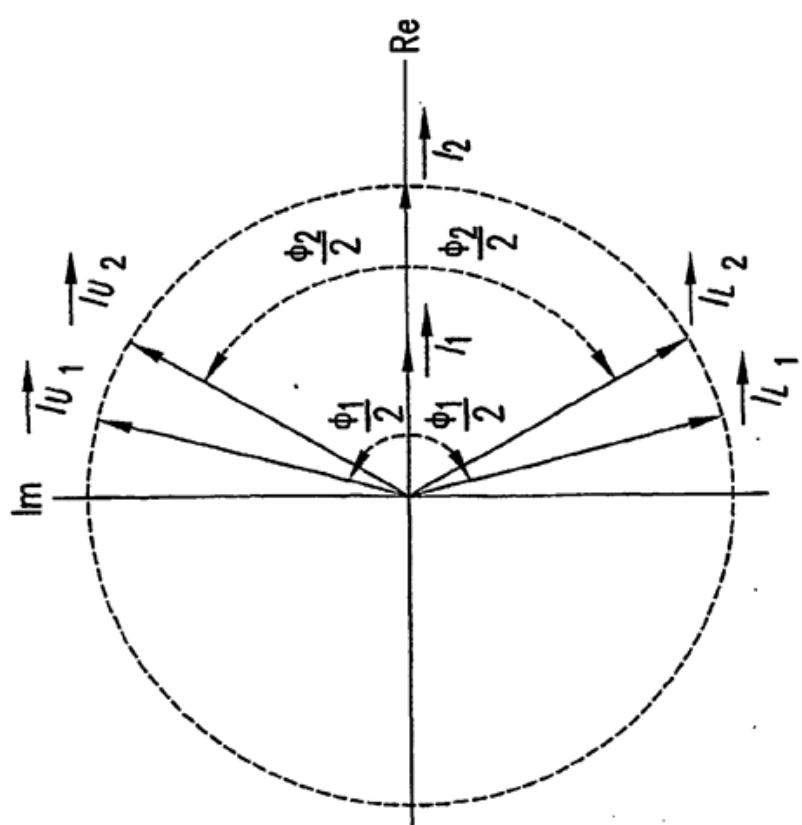

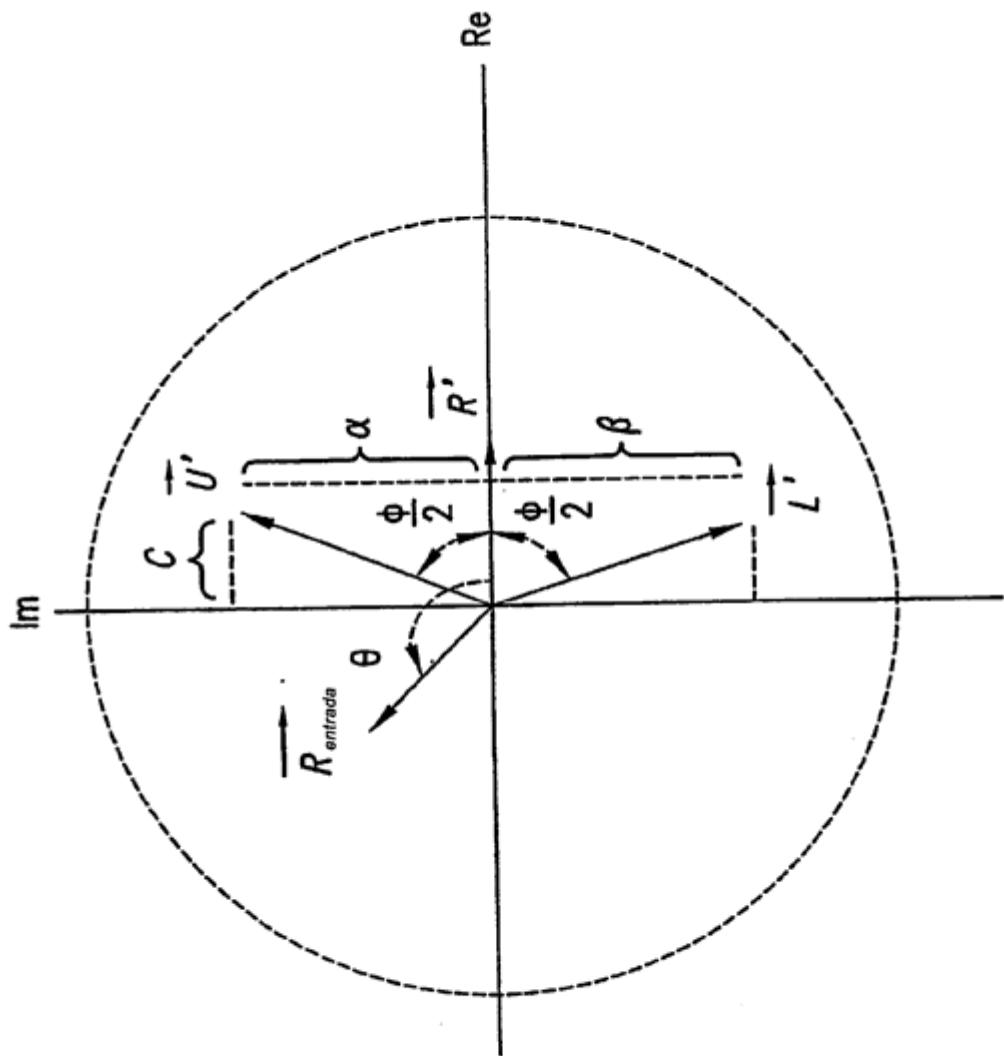

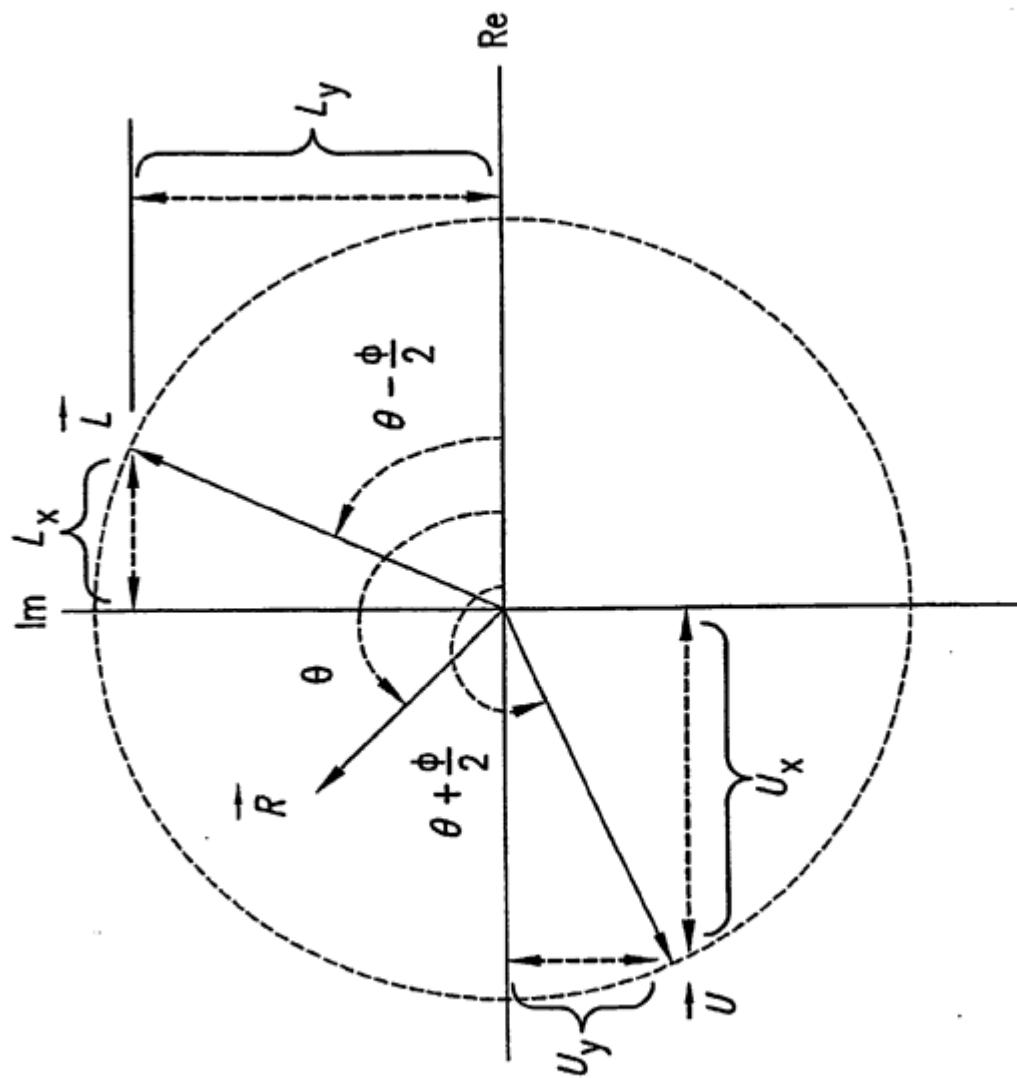

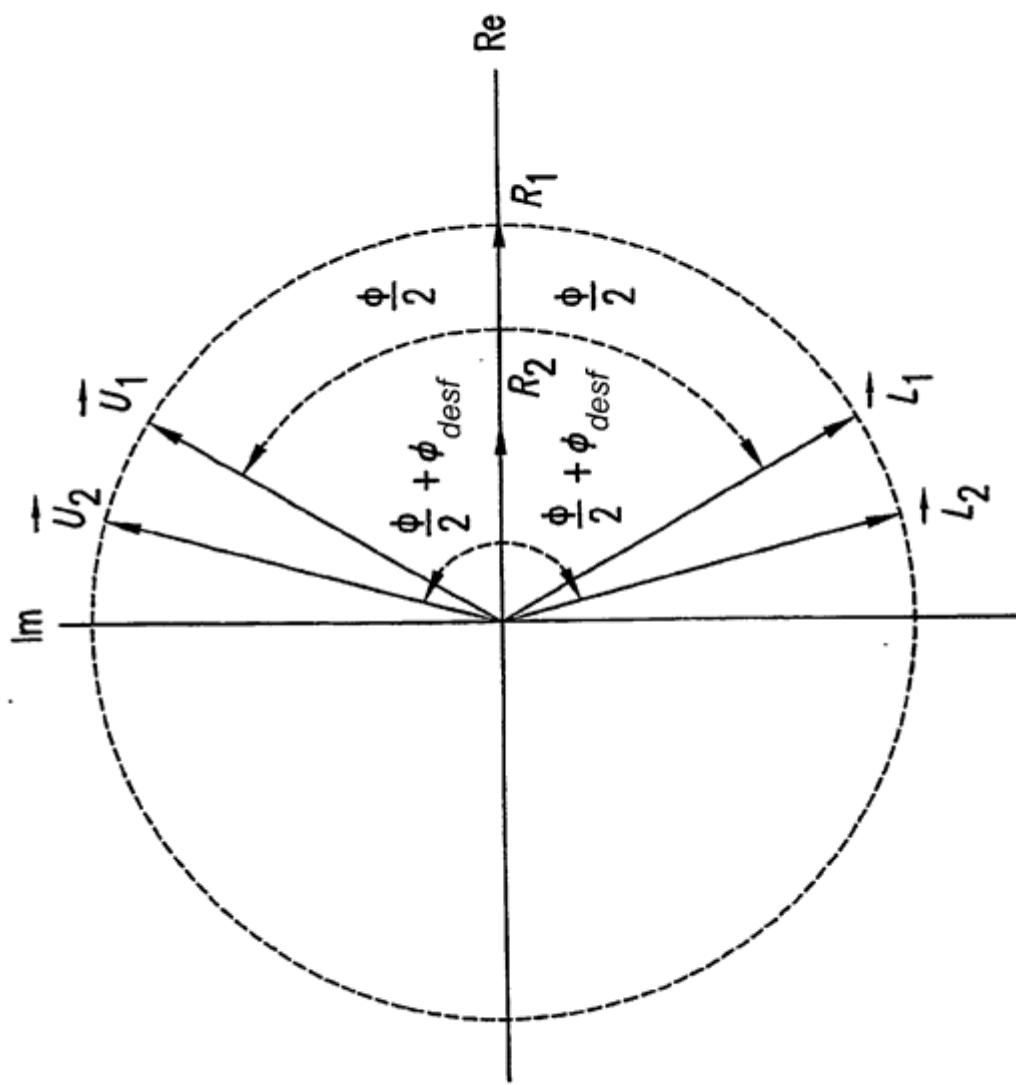

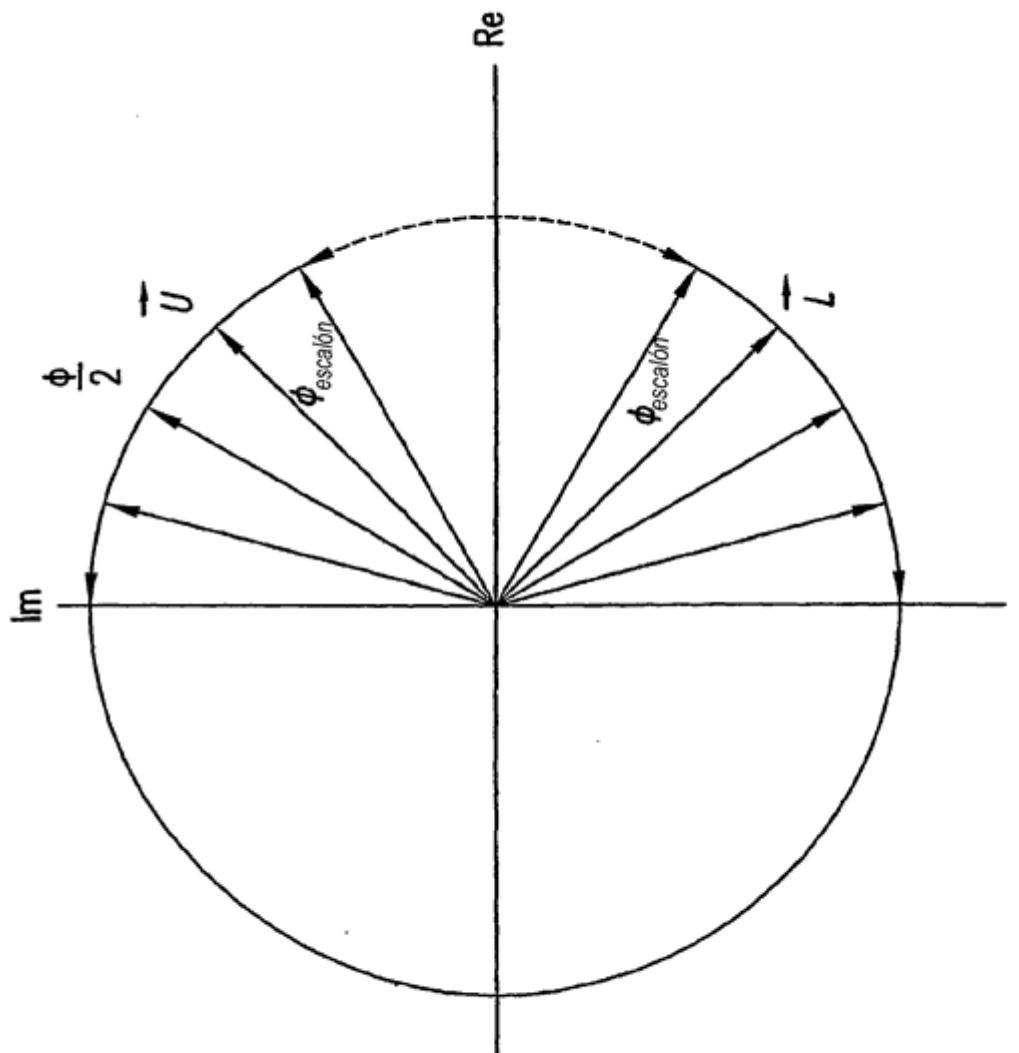

- 45 La figura 4 es un diagrama fasorial que ilustra un procedimiento de Amplificación de Potencia Vectorial (VPA) de 4 Ramas Cartesiana ejemplar.

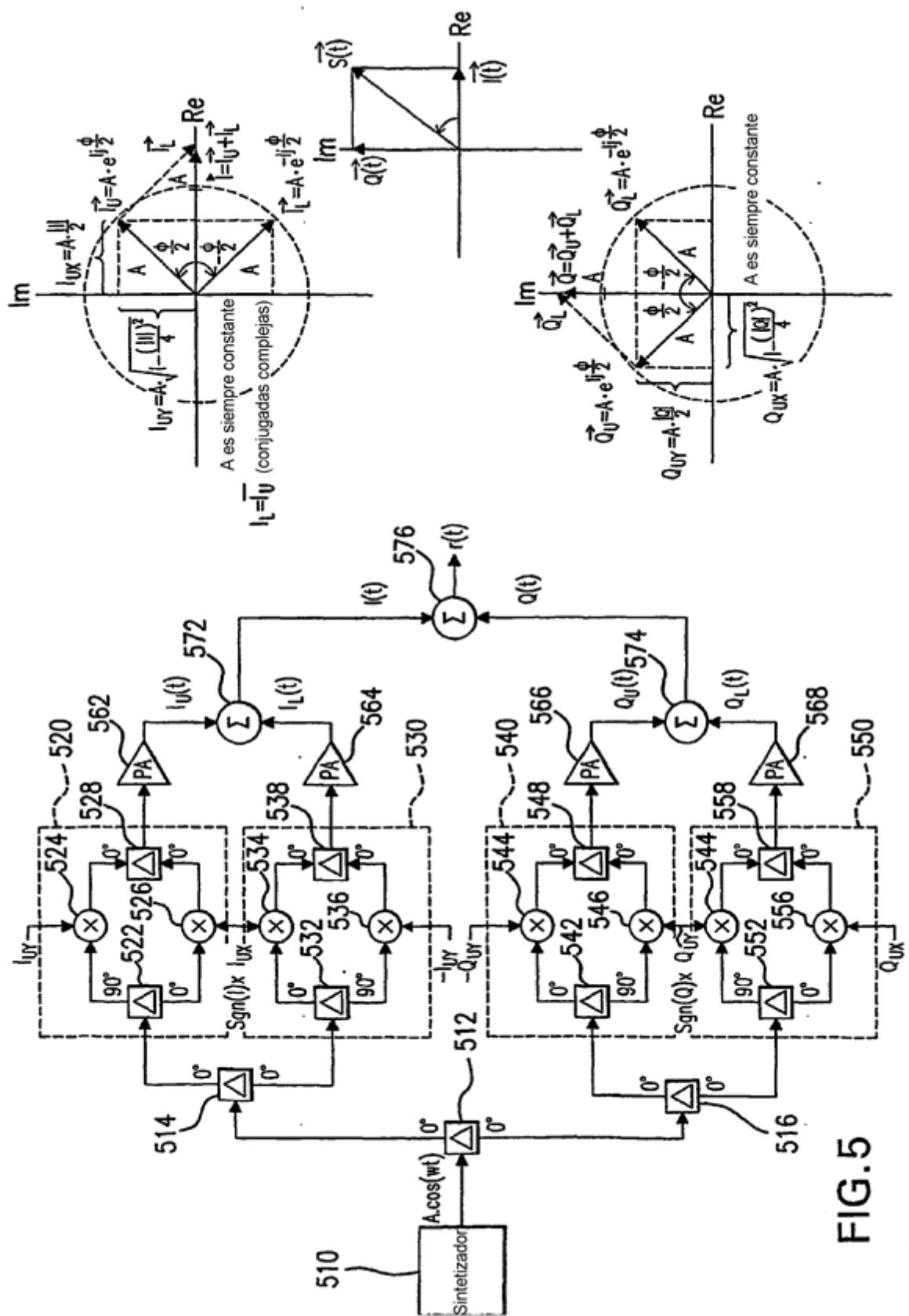

- La figura 5 es un diagrama de bloques que ilustra un procedimiento de VPA de 4 Ramas Cartesiana ejemplar.

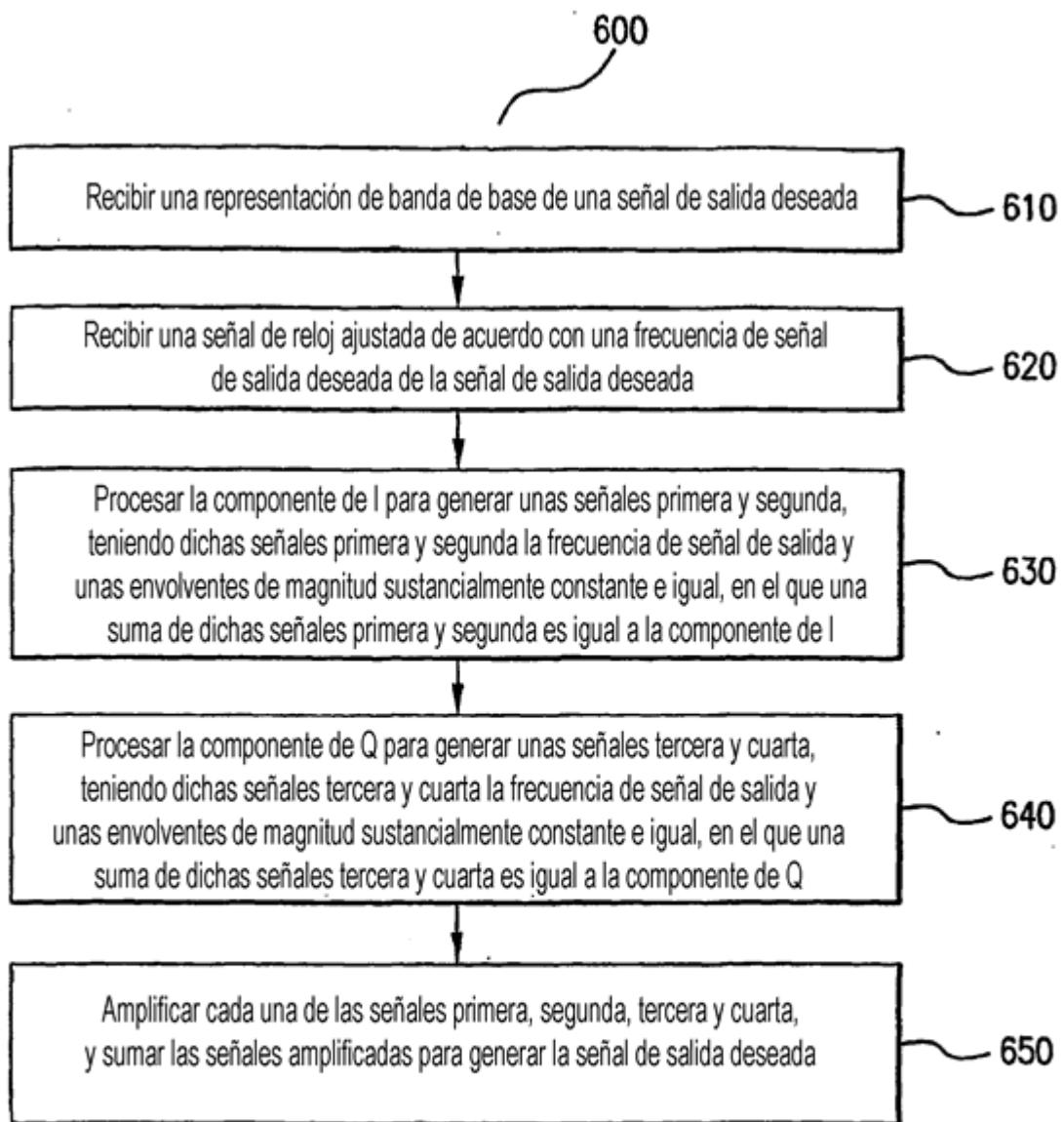

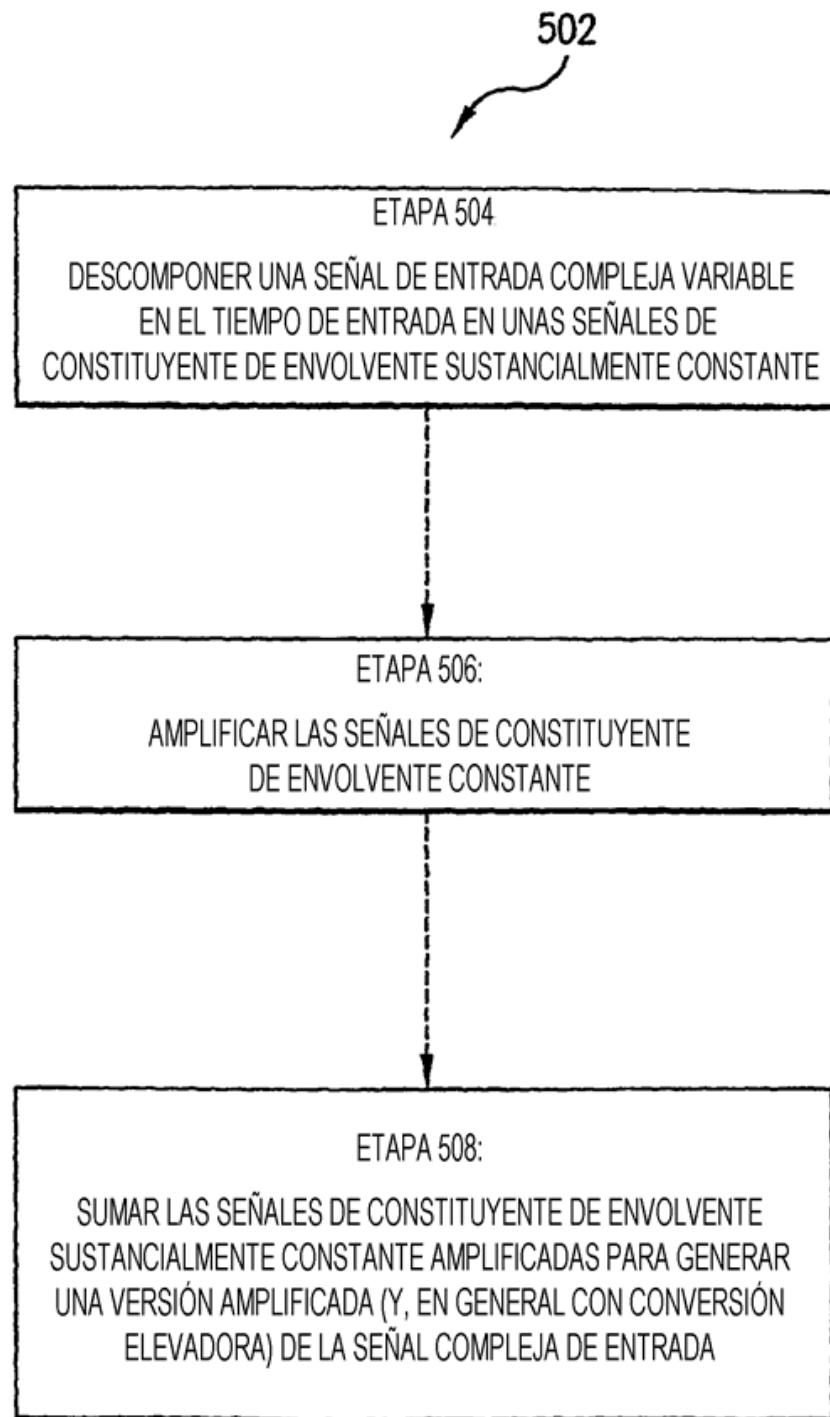

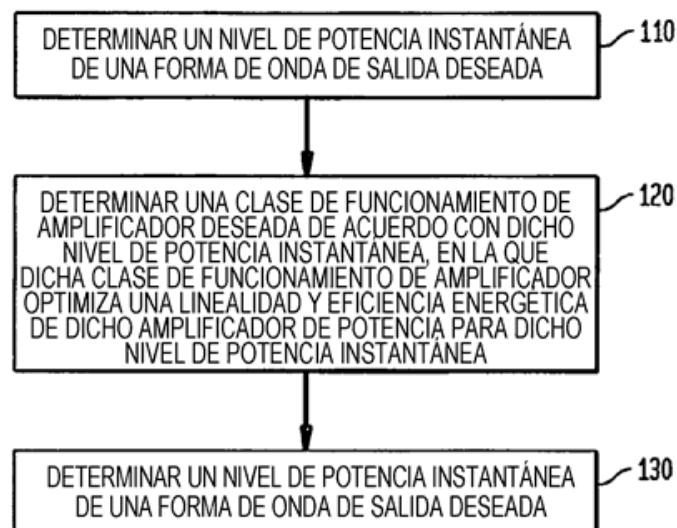

- La figura 6 es un diagrama de flujo de proceso para la amplificación de potencia de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

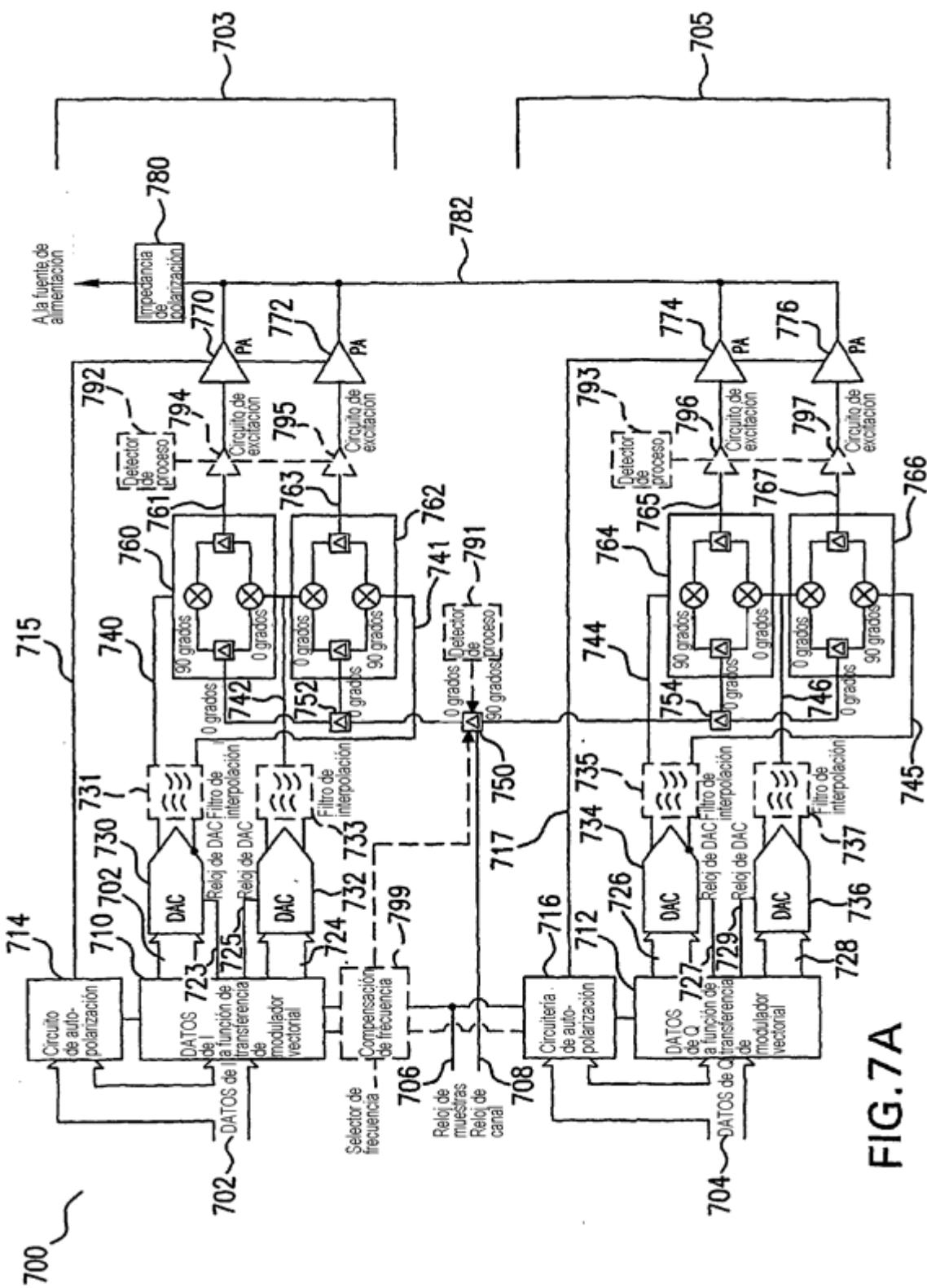

- 50 La figura 7A es un diagrama de bloques que ilustra una realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 4 Ramas Cartesiana.

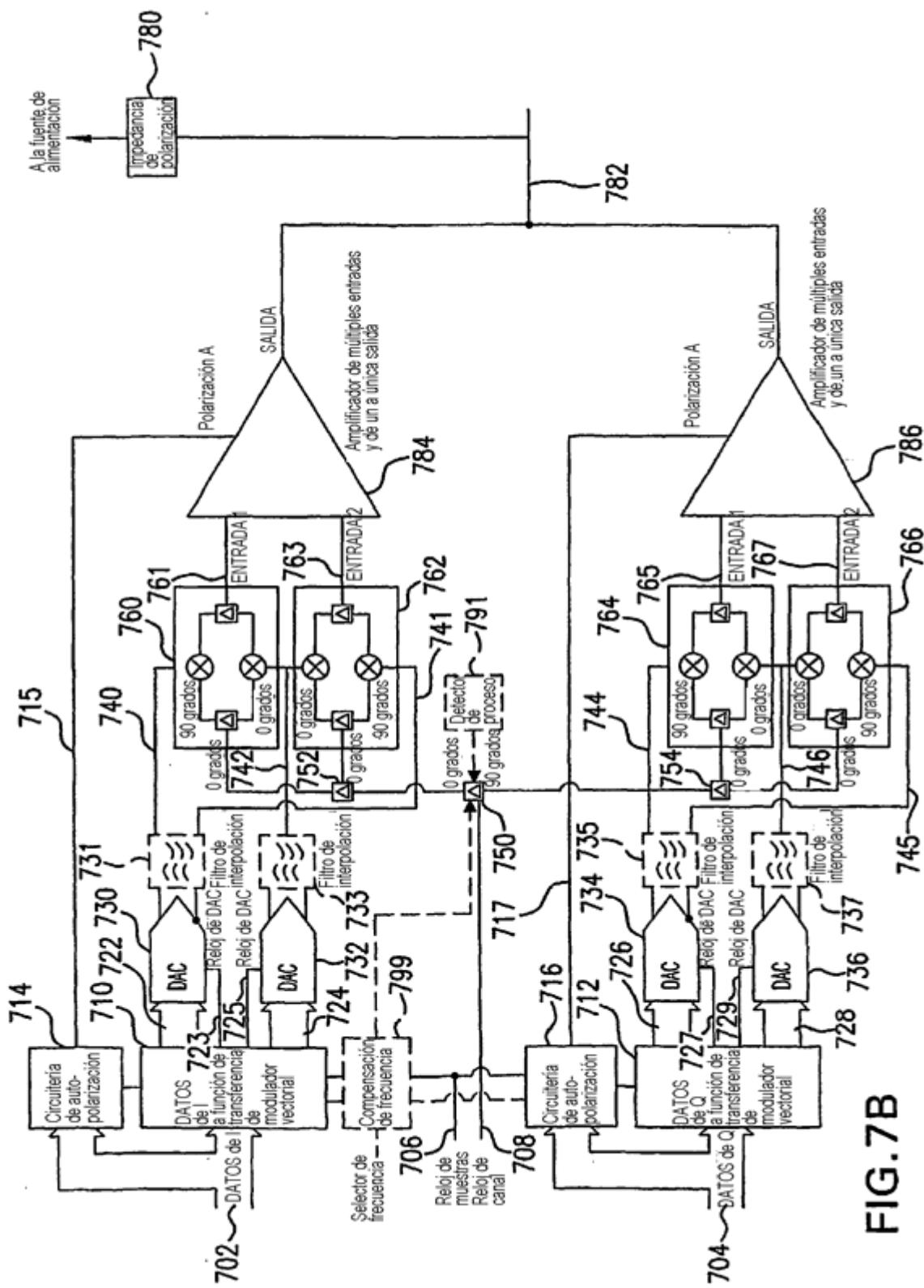

- La figura 7B es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 4 Ramas Cartesiana.

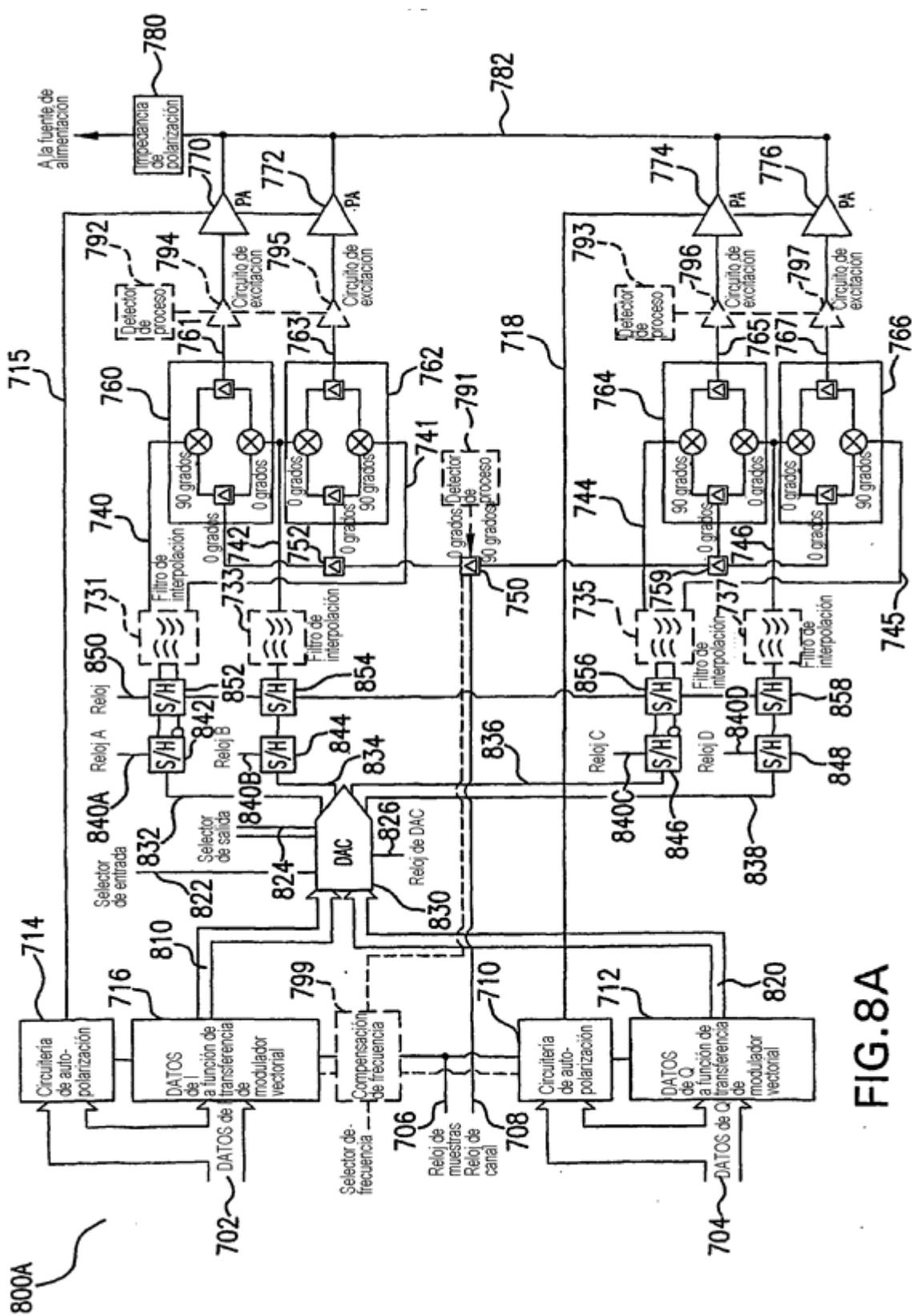

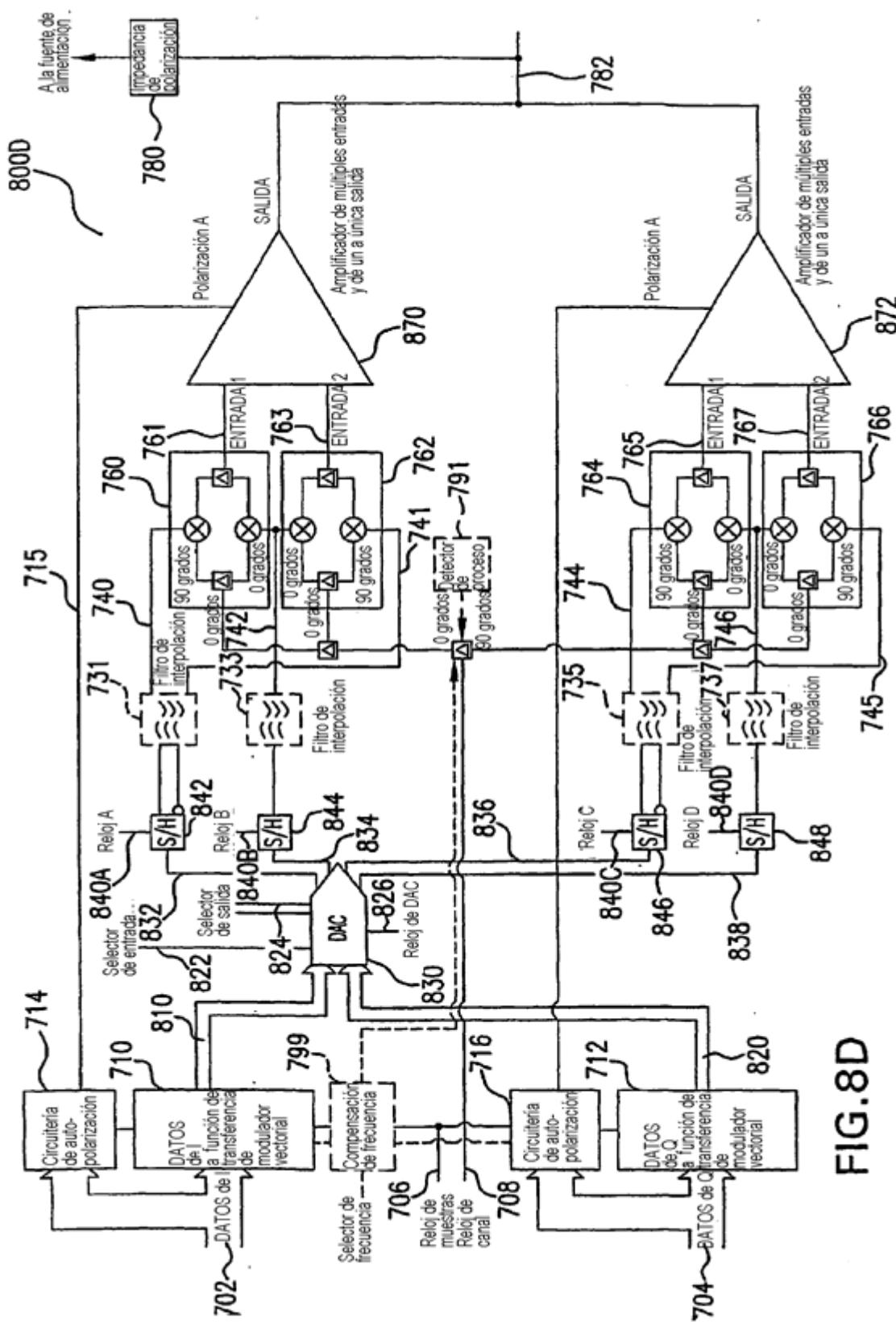

- La figura 8A es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

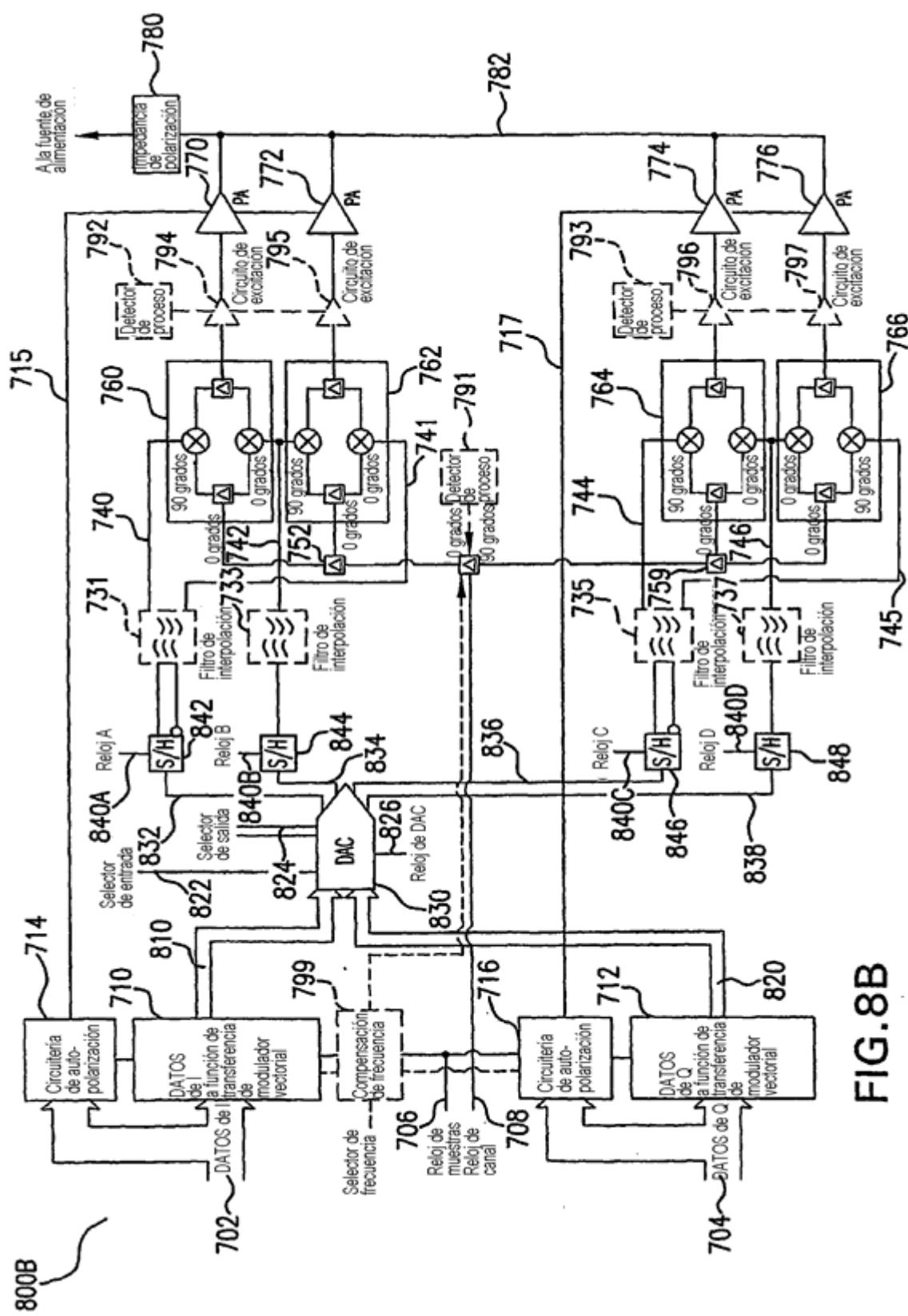

- 55 La figura 8B es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

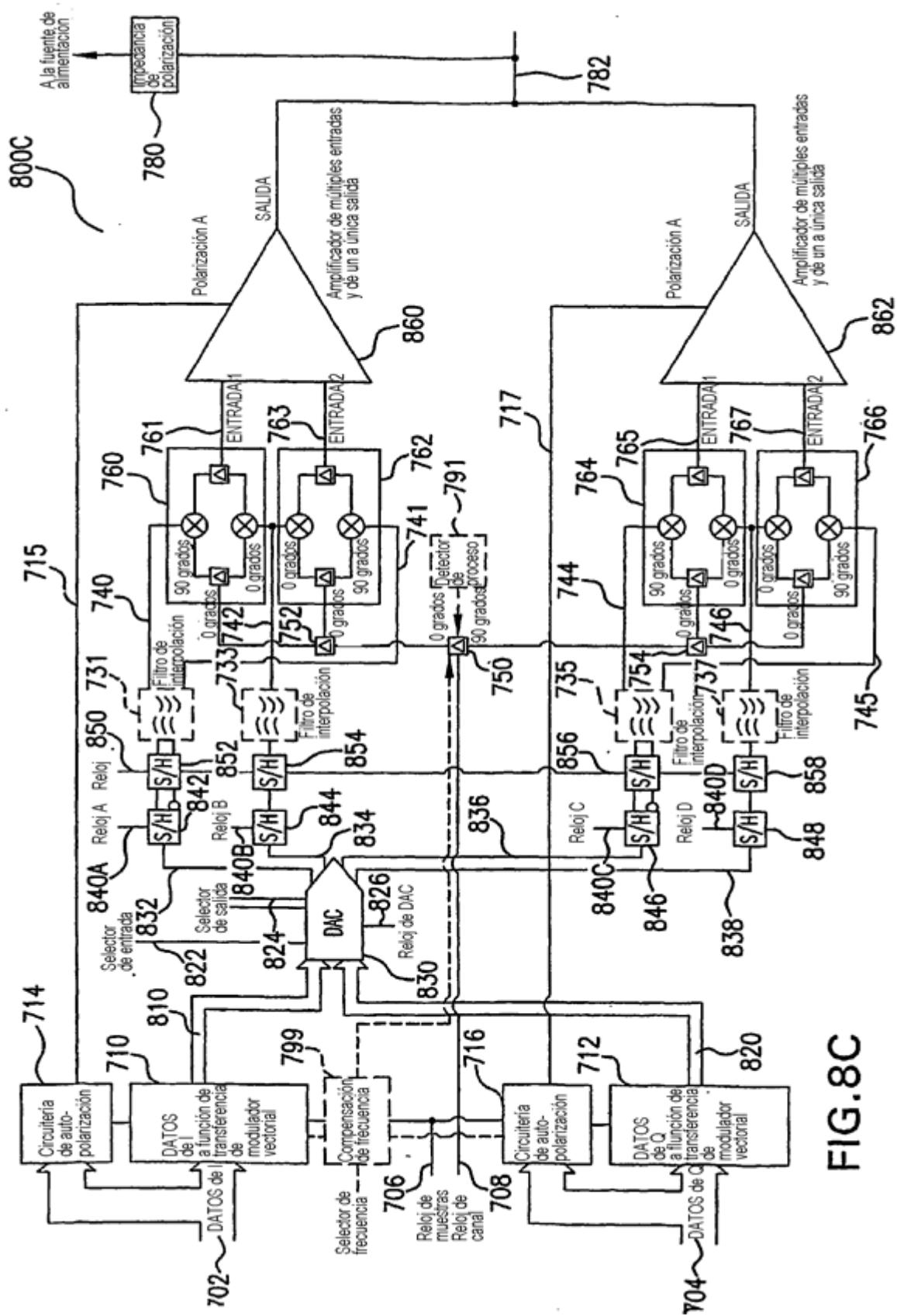

- La figura 8C es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

- La figura 8D es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial de

- acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

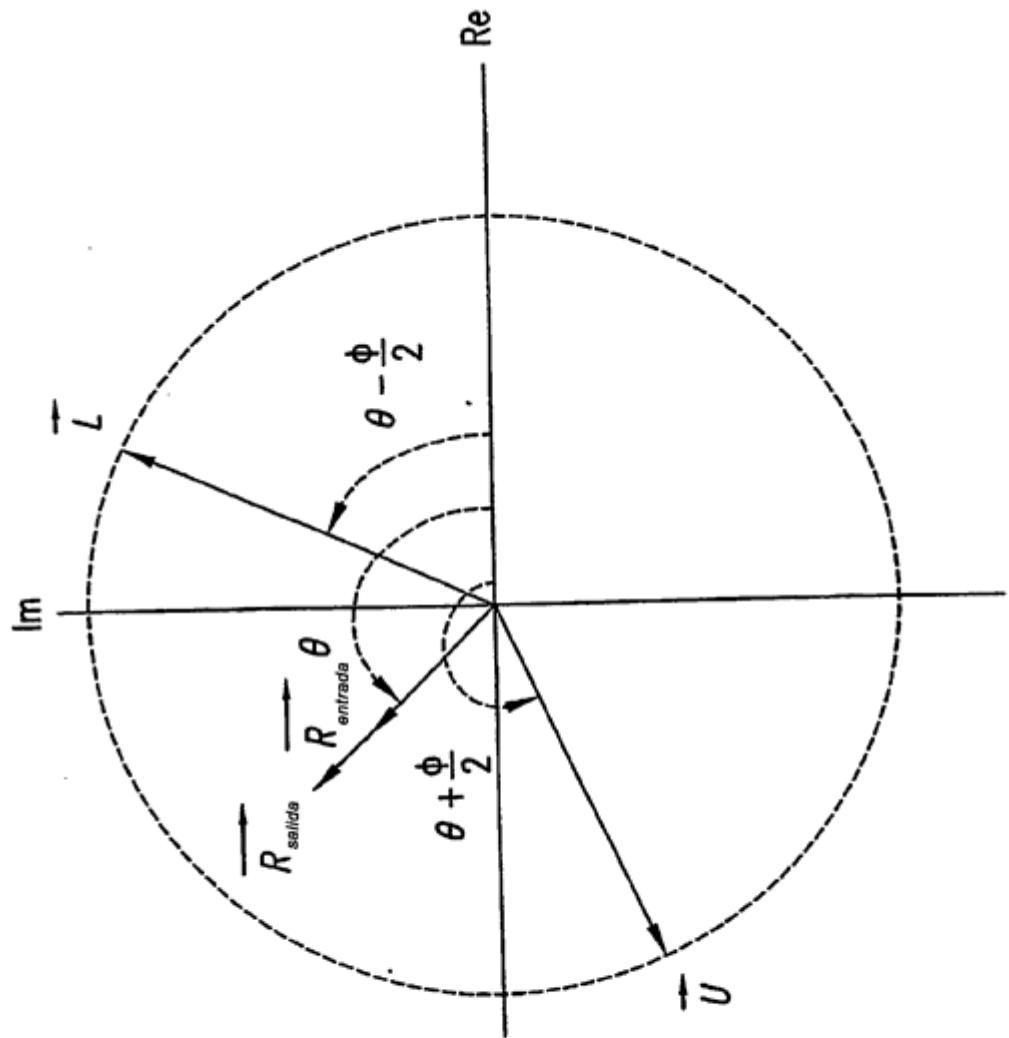

- Las figuras 9A - 9B son unos diagramas fasoriales que ilustran un procedimiento de Amplificación de Potencia Vectorial (VPA) de 2 Ramas Cartesiana - Polar - Cartesiana - Polar (CPCP) ejemplar.

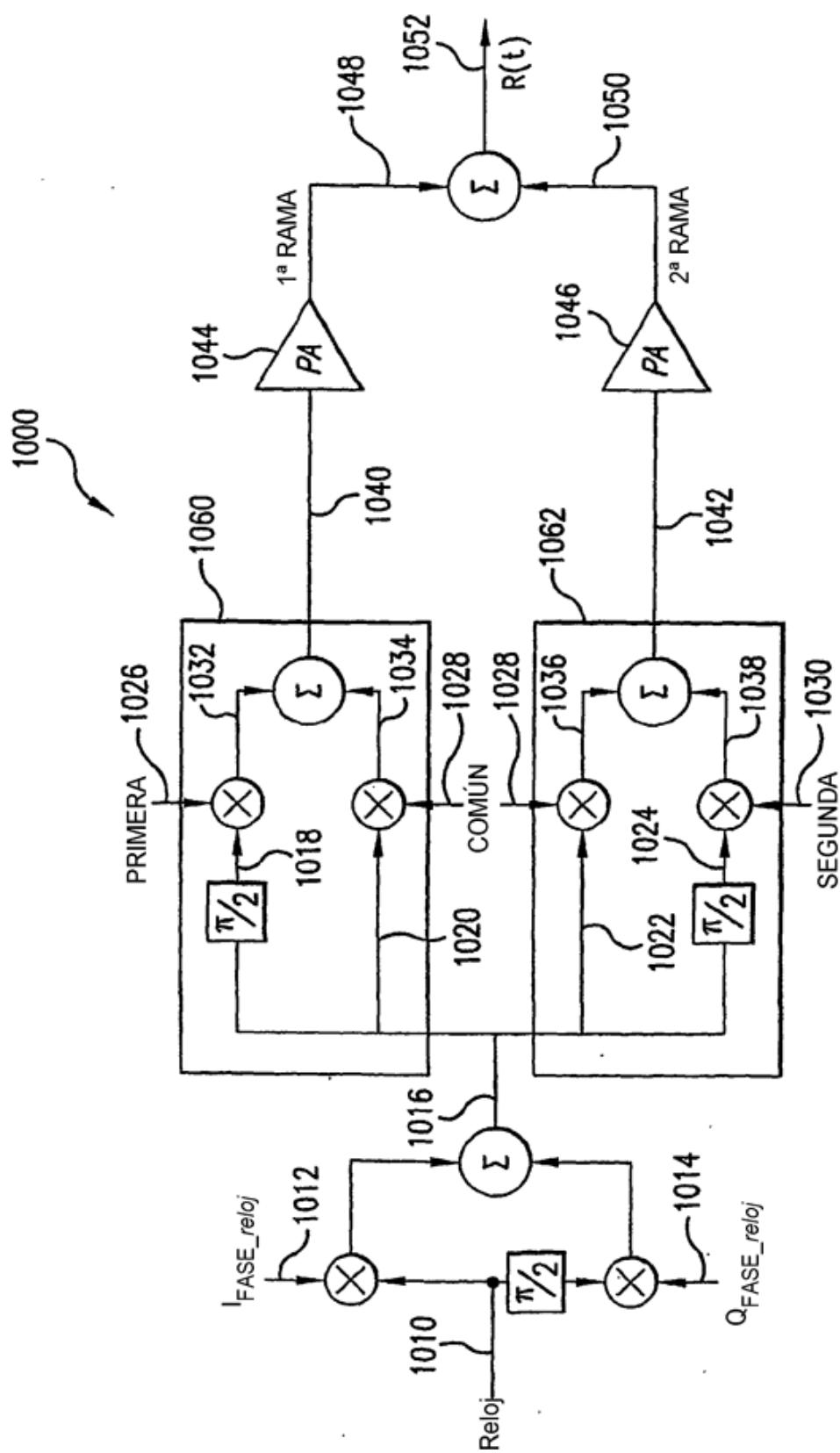

- 5 La figura 10 es un diagrama de bloques que ilustra un procedimiento de VPA de 2 Ramas CPCP ejemplar.

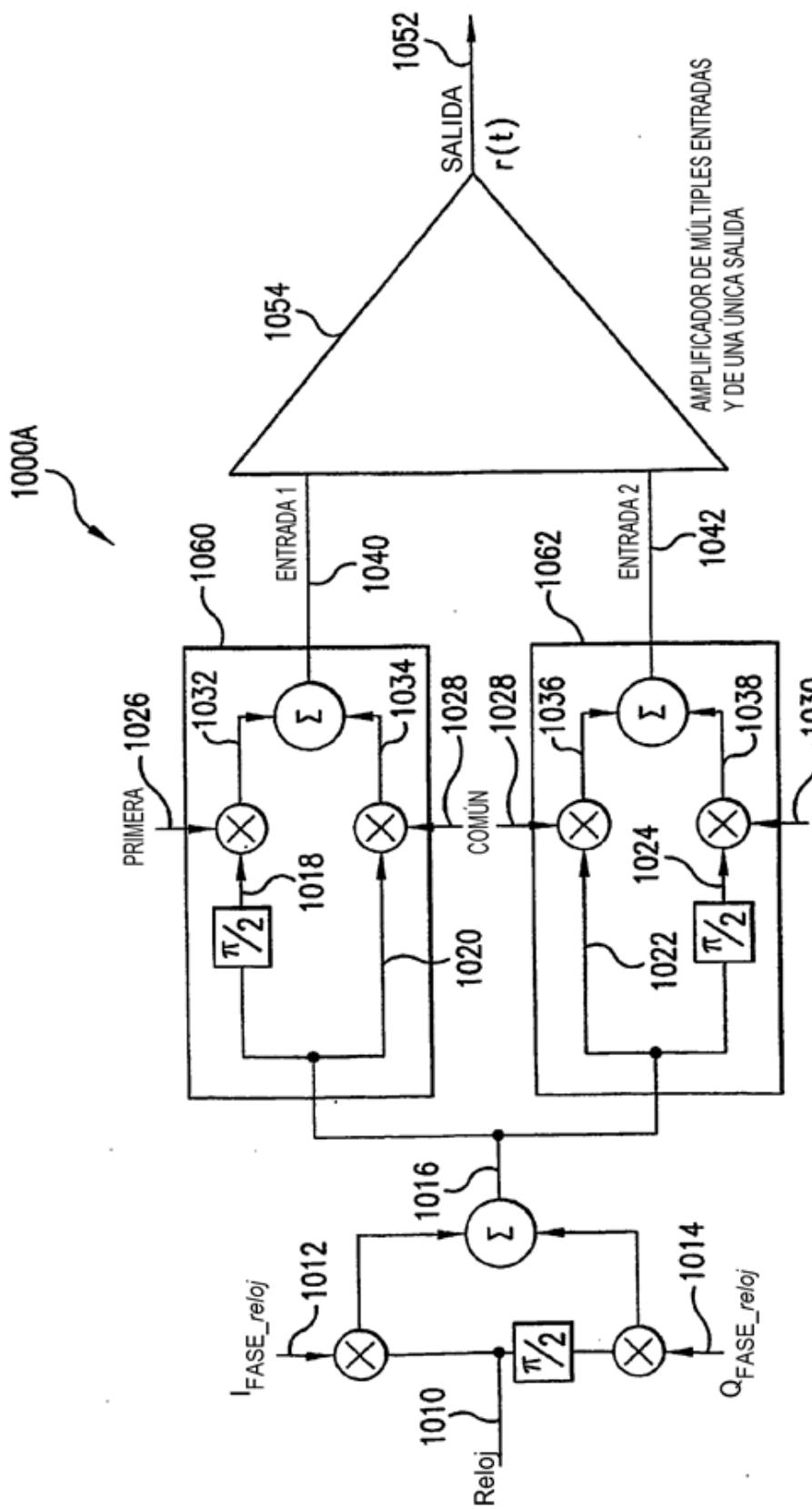

- La figura 10A es un diagrama de bloques que ilustra otro procedimiento de VPA de 2 Ramas CPCP ejemplar.

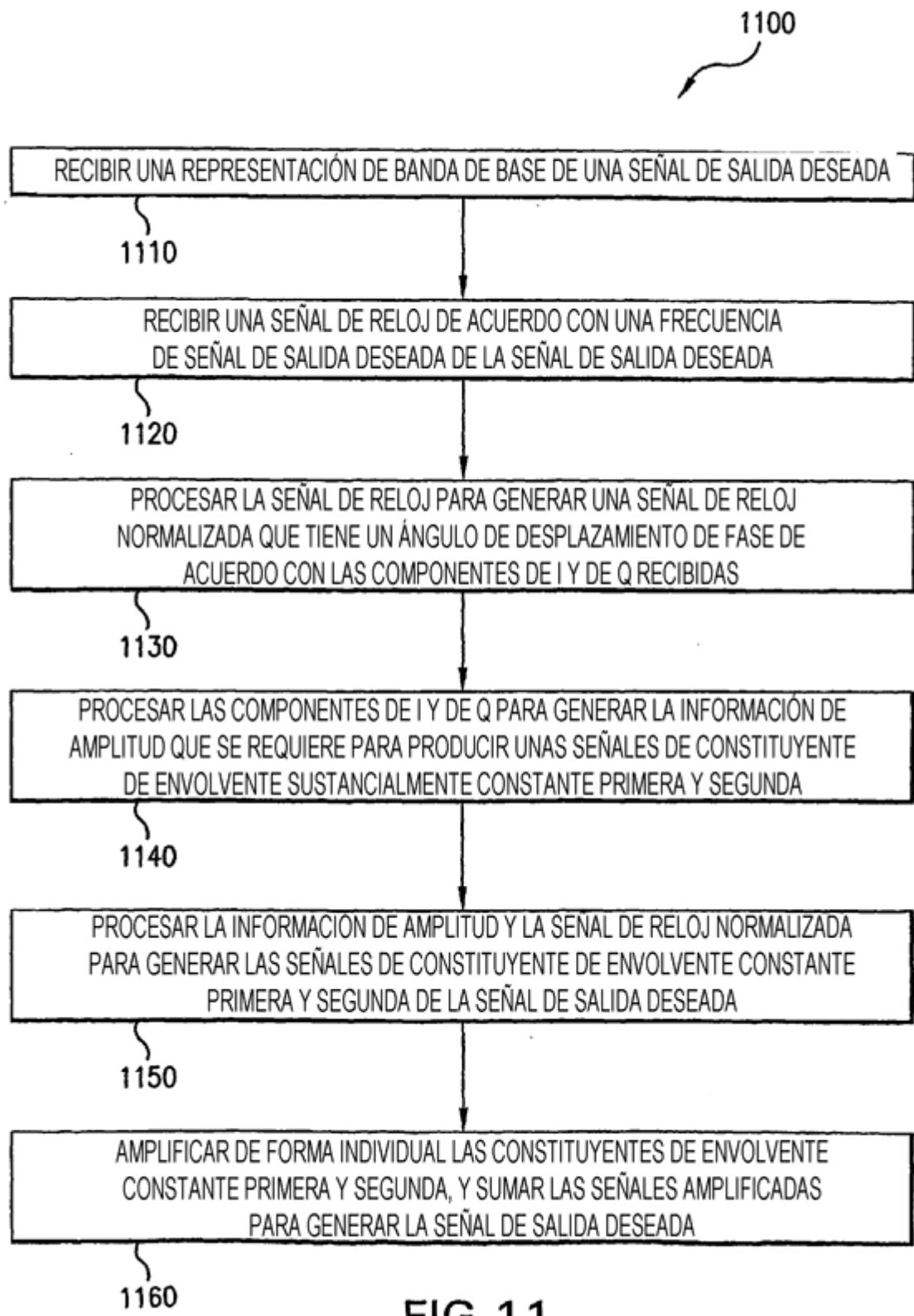

- La figura 11 es un diagrama de flujo de proceso para la amplificación de potencia de acuerdo con un procedimiento de VPA de 2 Ramas CPCP ejemplar.

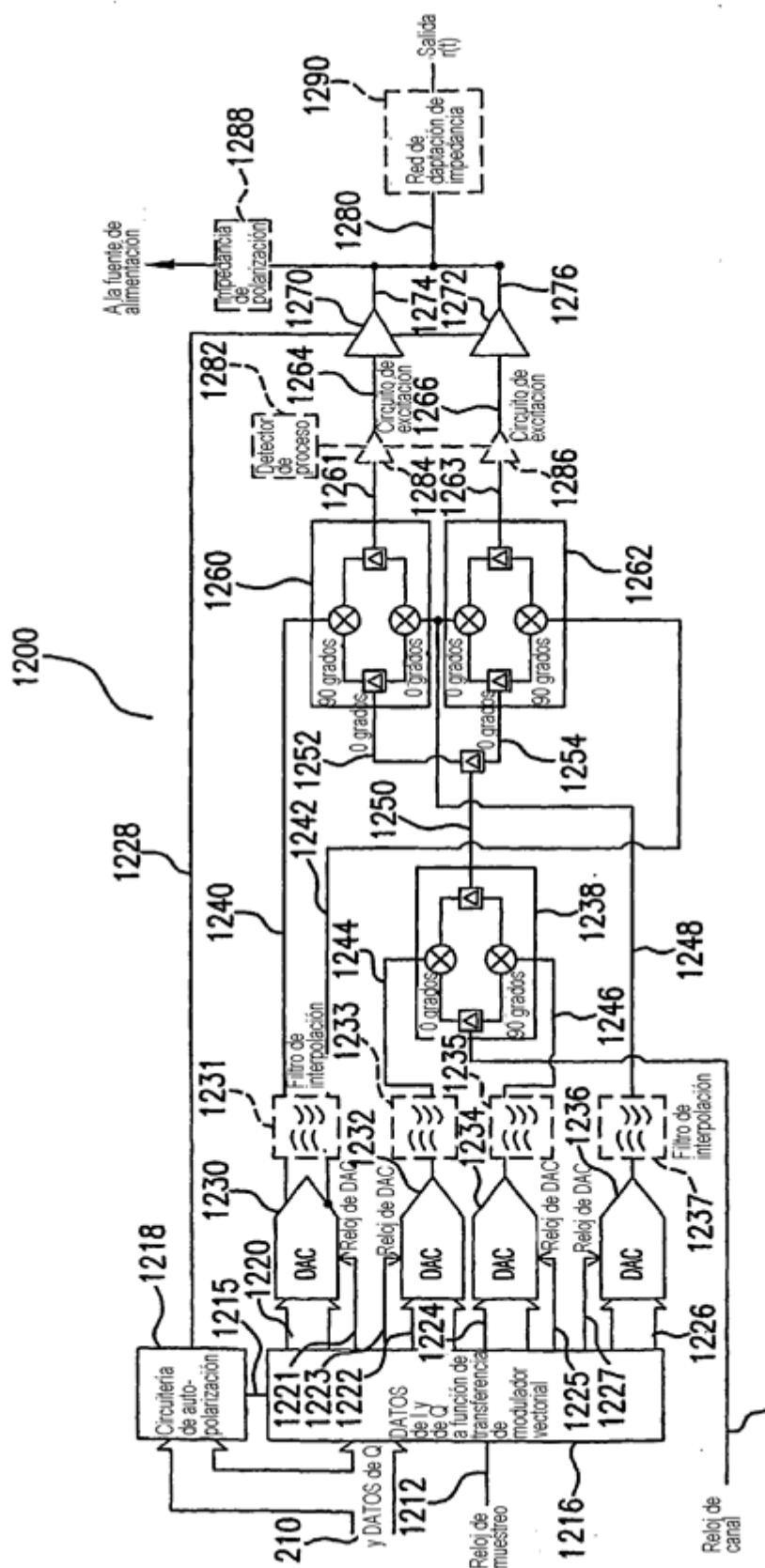

- 10 La figura 12 es un diagrama de bloques que ilustra una realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas CPCP.

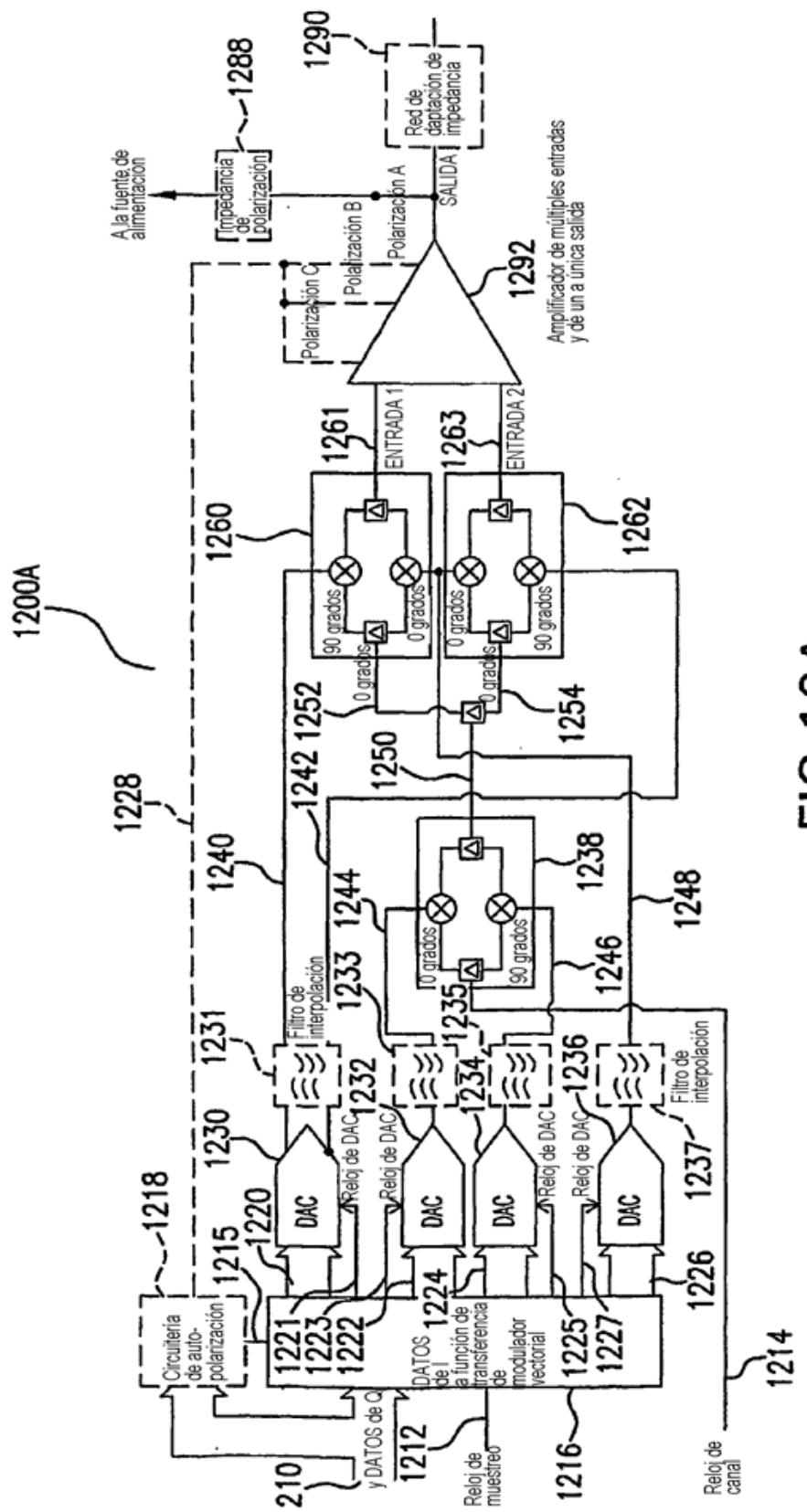

- La figura 12A es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas CPCP.

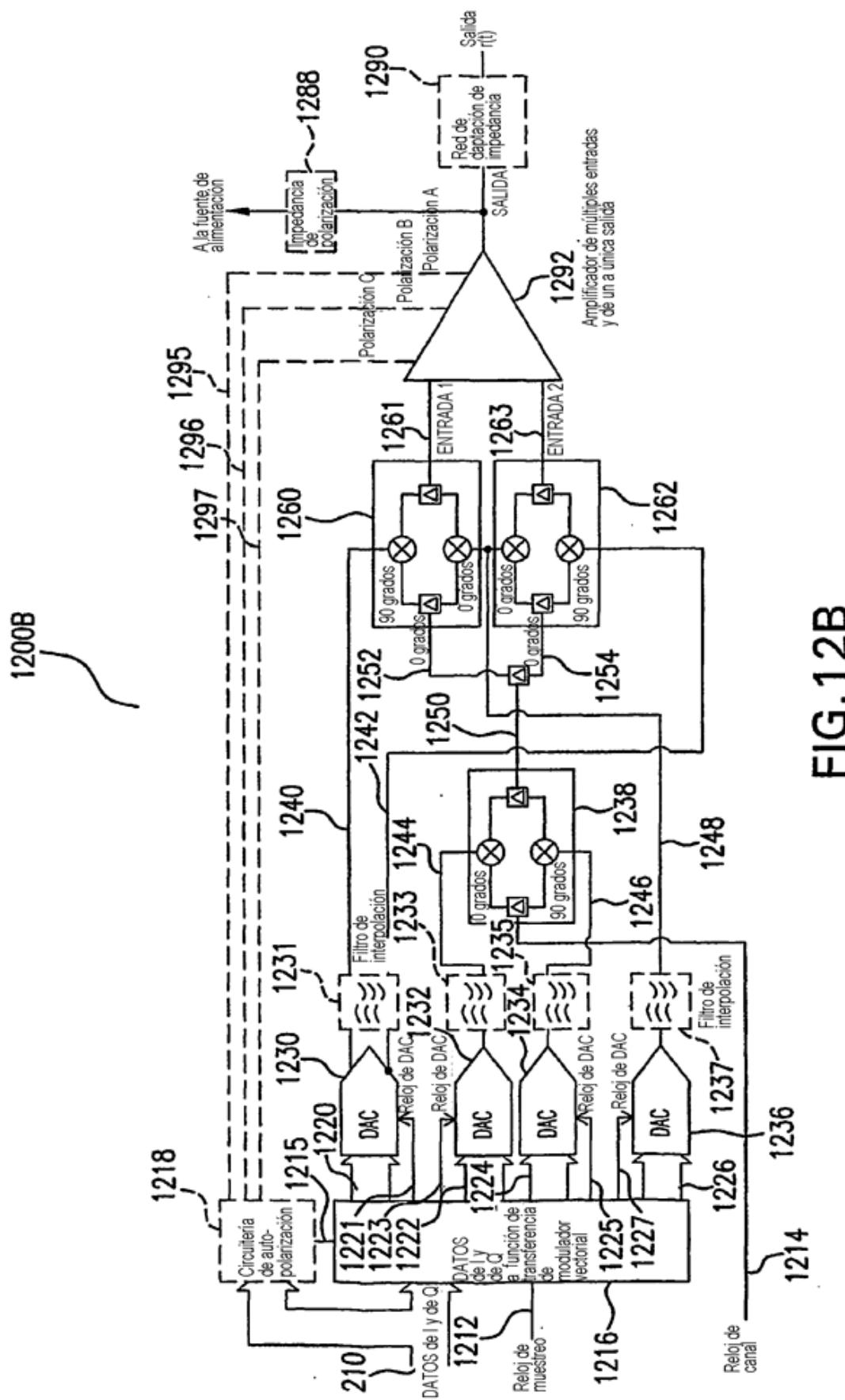

- La figura 12B es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas CPCP.

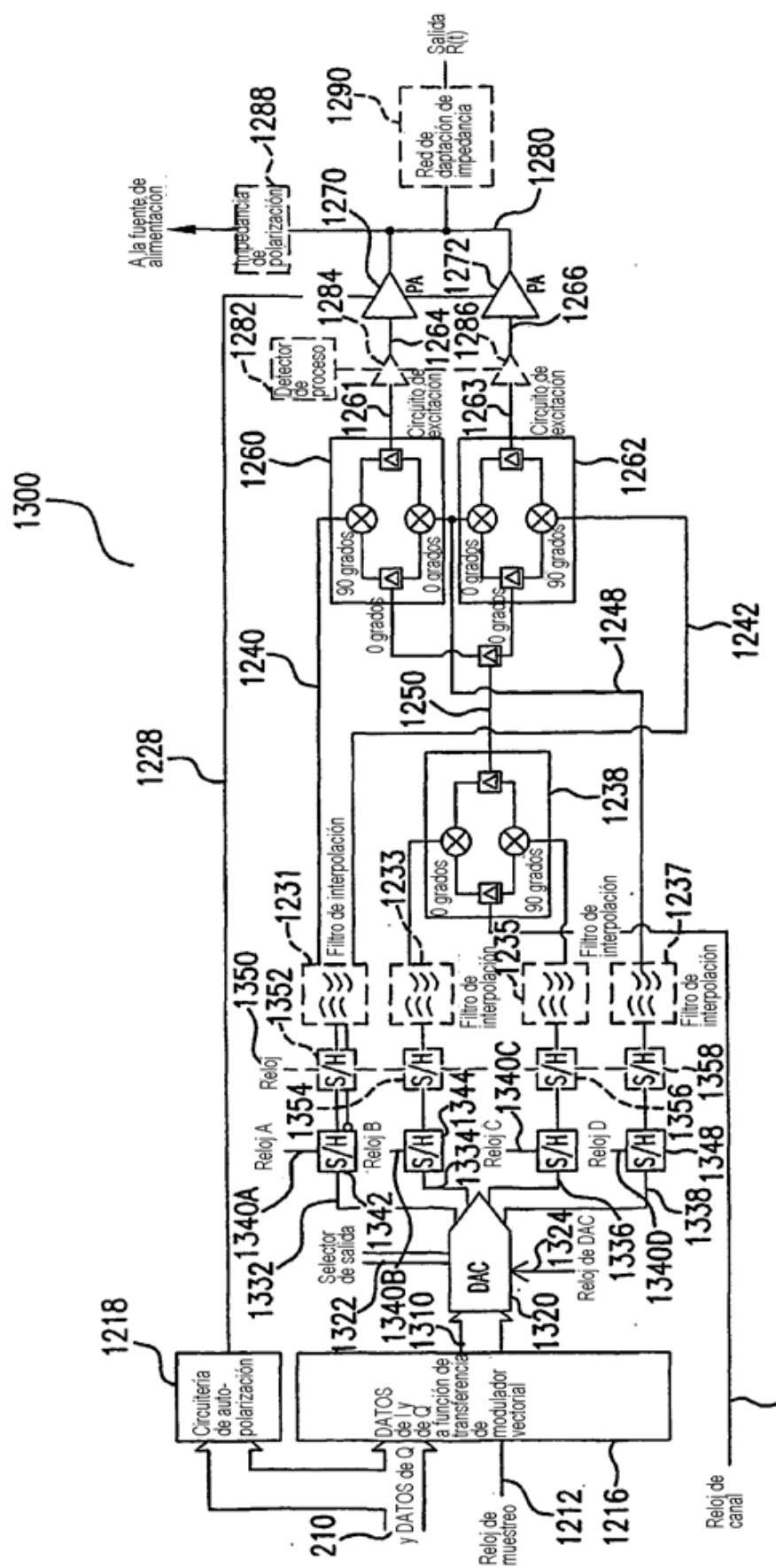

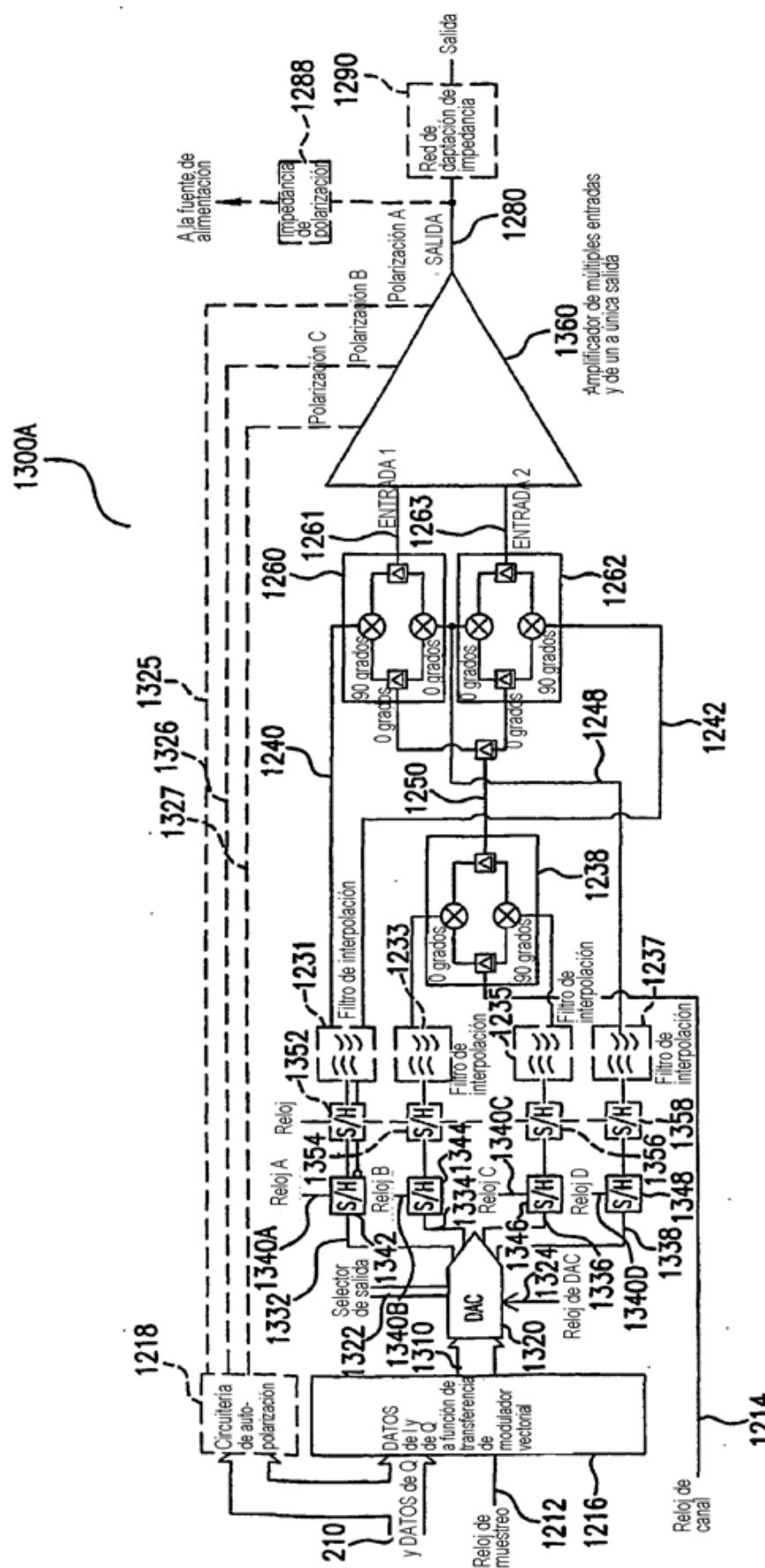

- 15 La figura 13 es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas CPCP.

- La figura 13A es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas CPCP.

- La figura 14 es un diagrama fasorial que ilustra un procedimiento de Amplificación de Potencia Vectorial (VPA) de 2 Ramas Cartesiana Directa ejemplar.

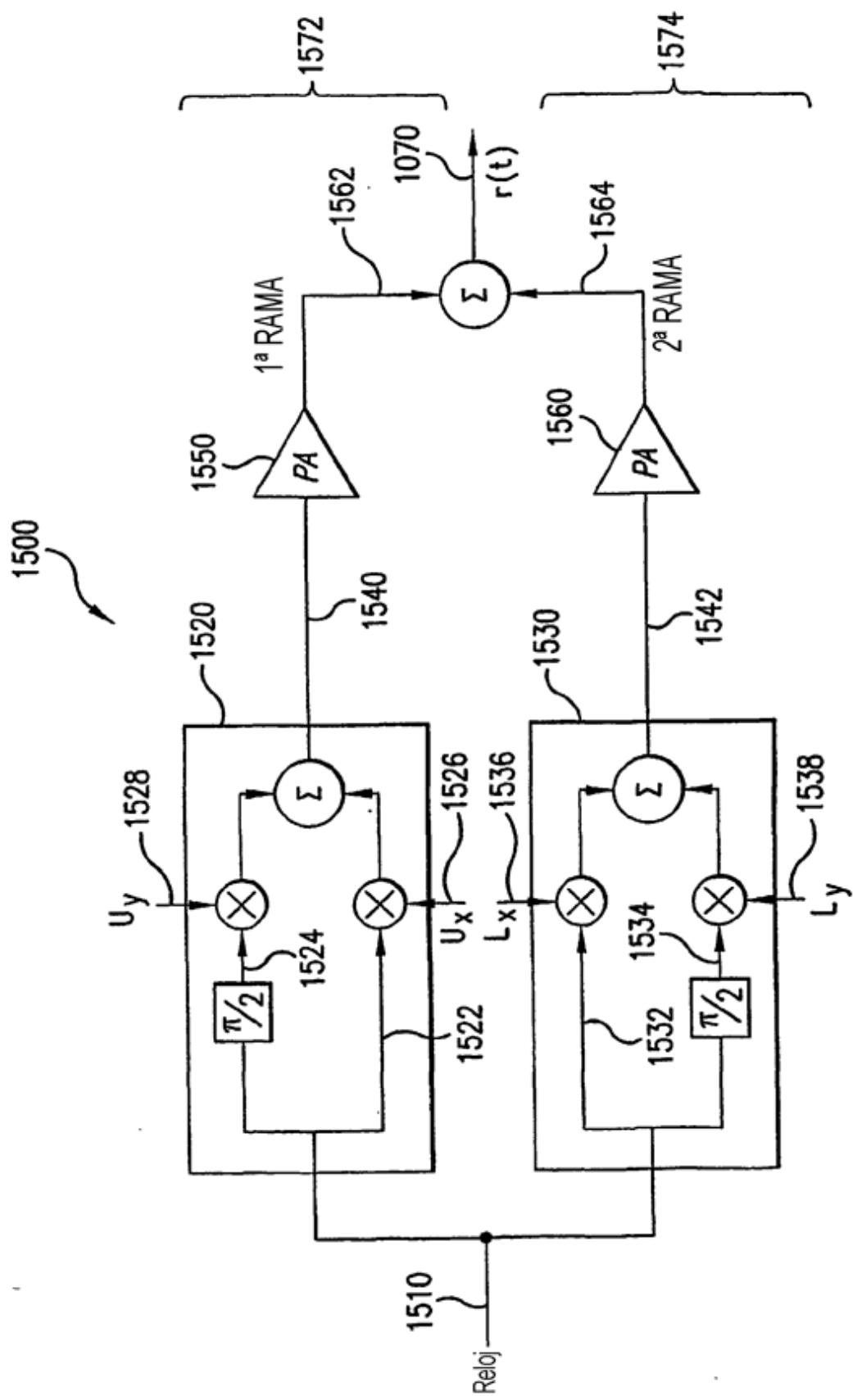

- 20 La figura 15 es un diagrama de bloques que ilustra una realización ejemplar del procedimiento de VPA de 2 Ramas Cartesiana Directa.

- La figura 15A es un diagrama de bloques que ilustra otro procedimiento de VPA de 2 Ramas Cartesiana Directa ejemplar.

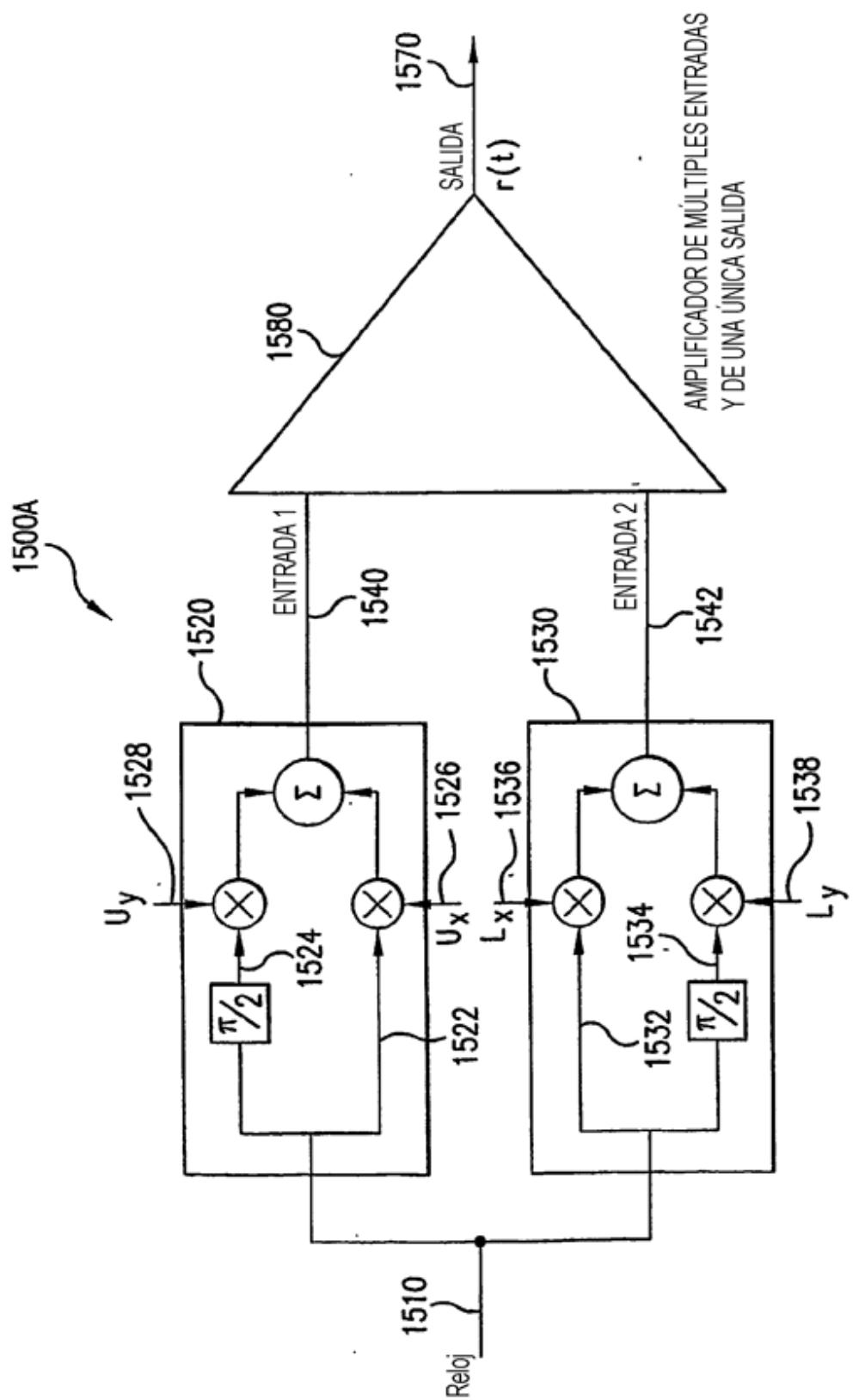

- 25 La figura 16 es un diagrama de flujo de proceso para la amplificación de potencia de acuerdo con un procedimiento de VPA de 2 Ramas Cartesiana Directa ejemplar.

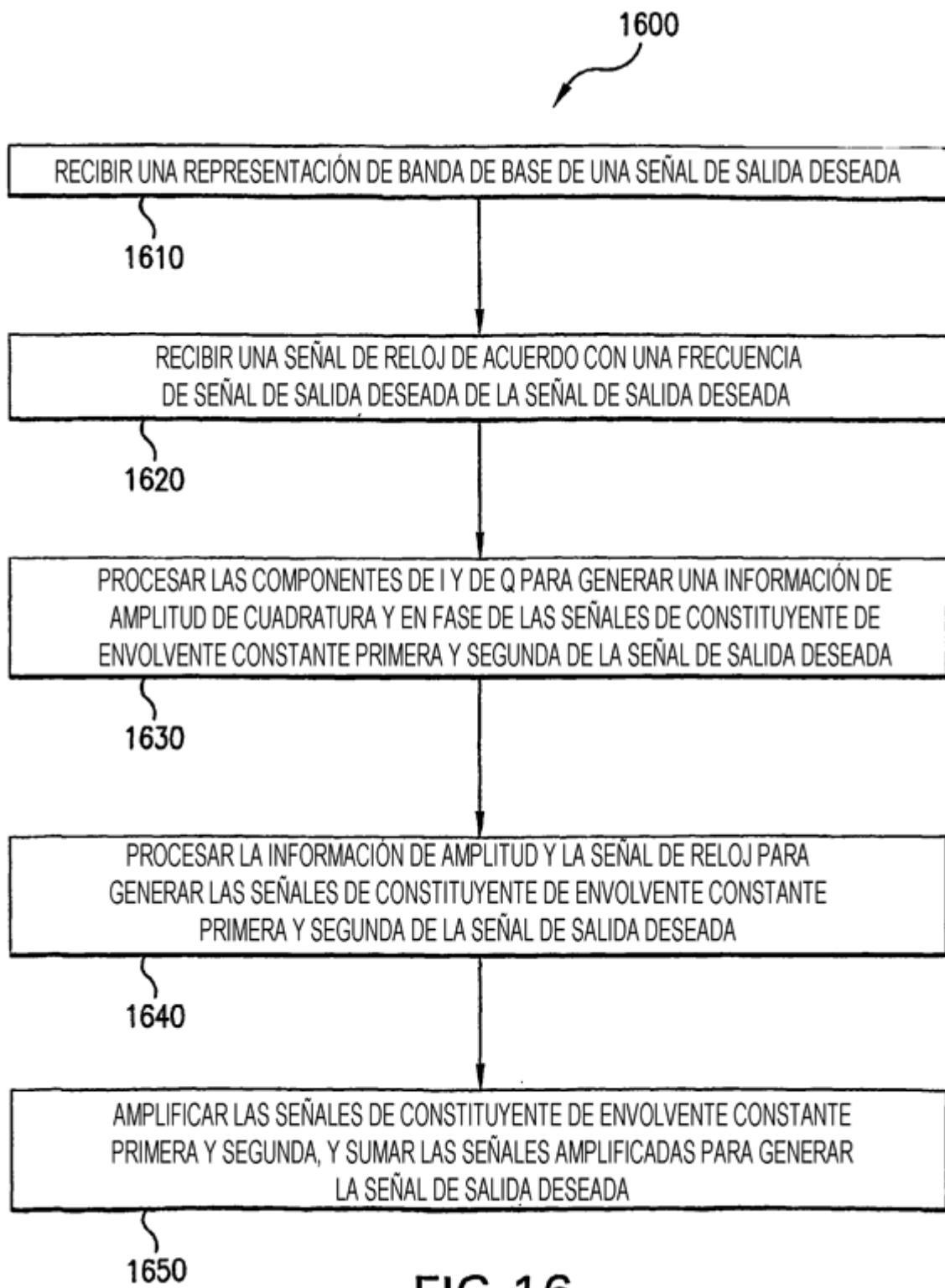

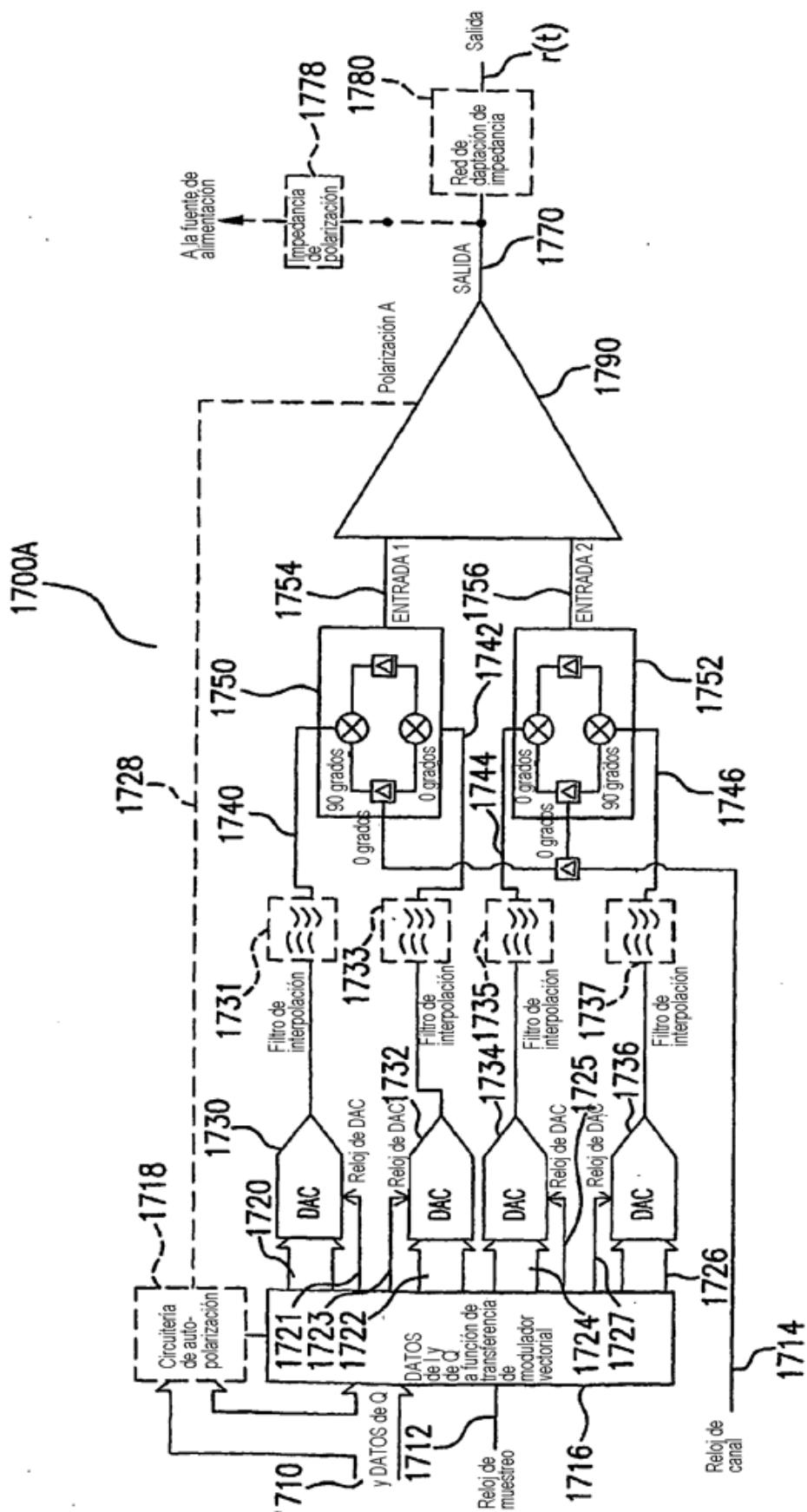

- La figura 17 es un diagrama de bloques que ilustra una realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas Cartesiana Directa.

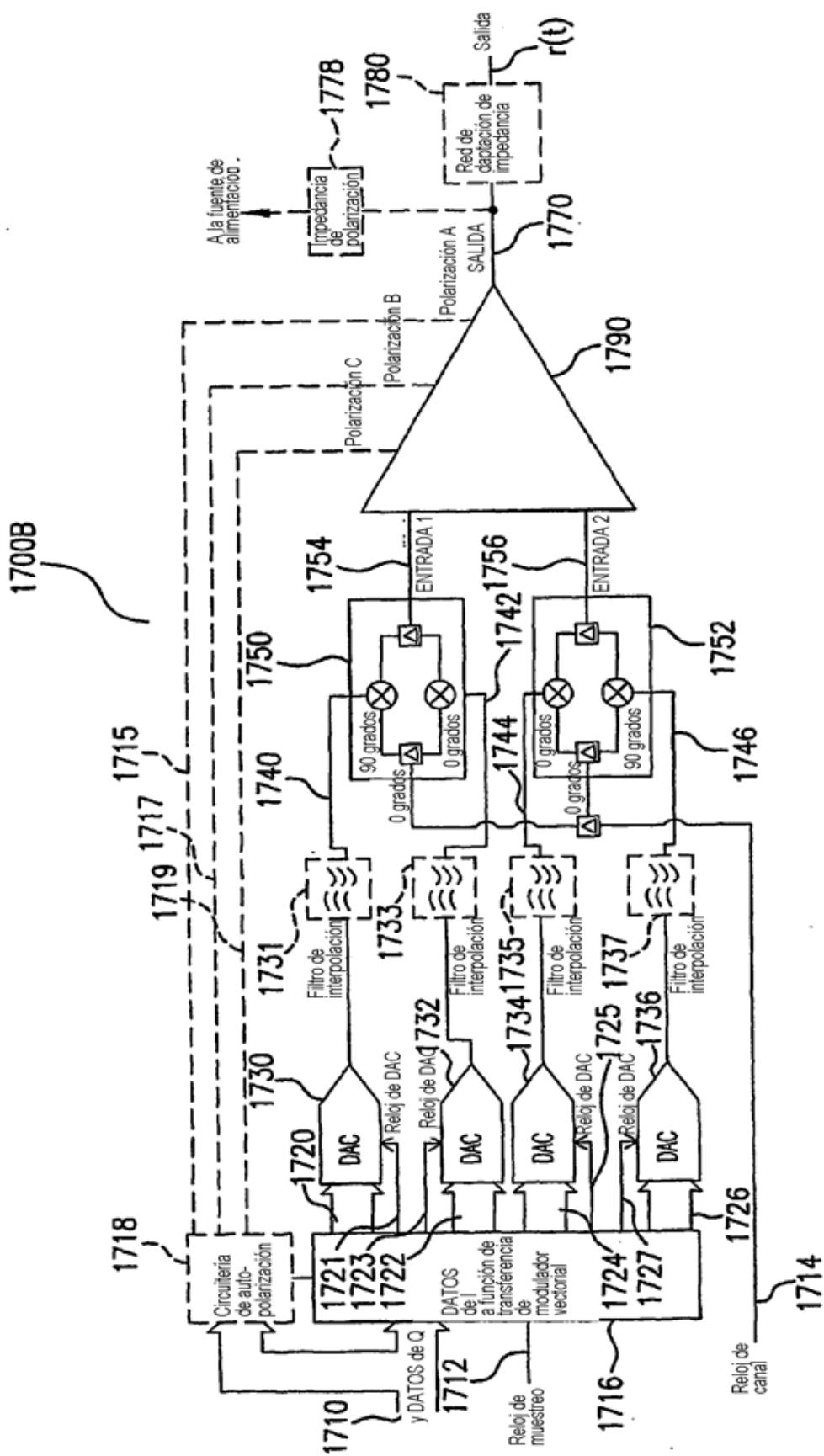

- La figura 17A es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas Cartesiana Directa.

- 30 La figura 17B es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas Cartesiana Directa.

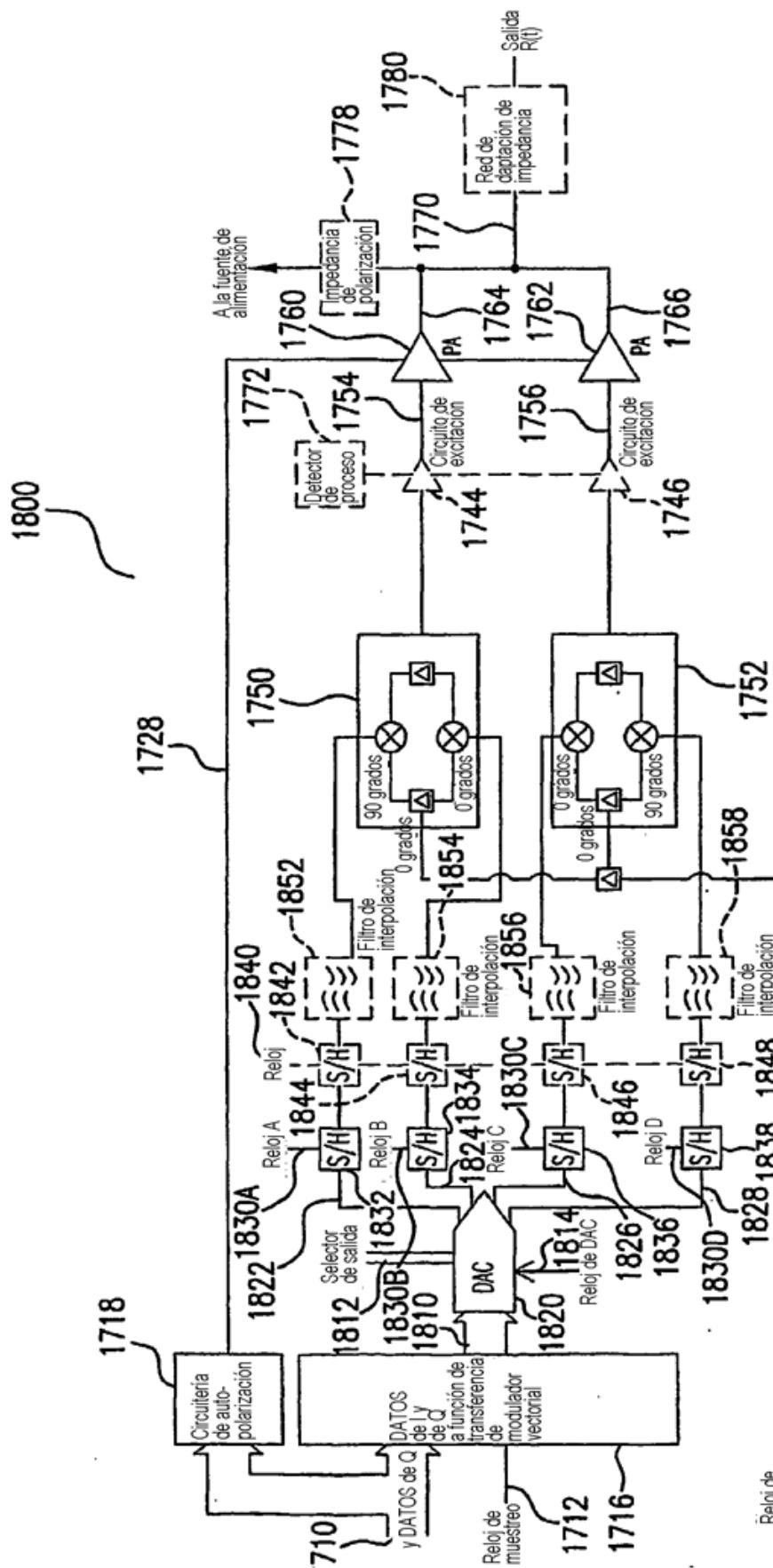

- La figura 18 es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas Cartesiana Directa.

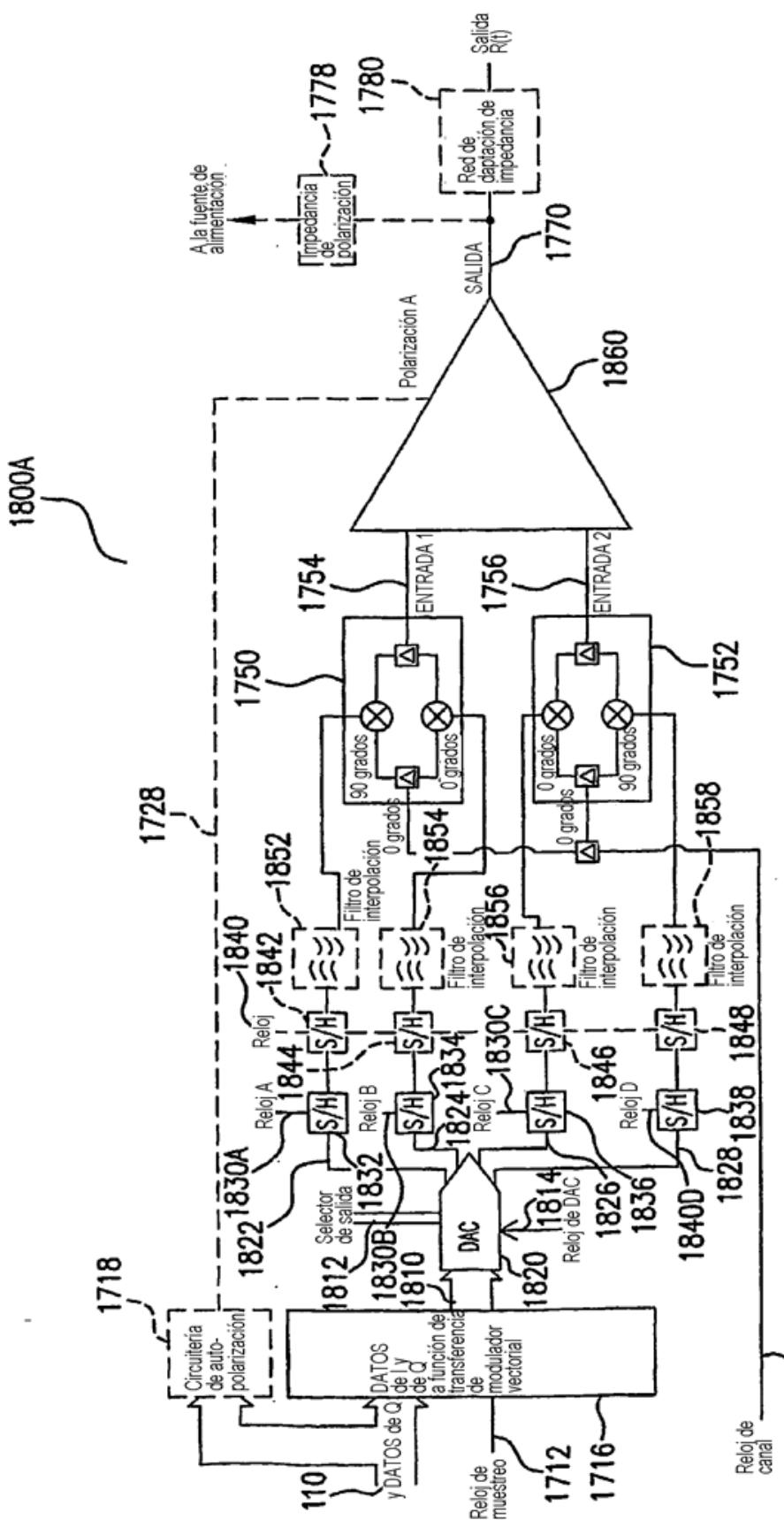

- 35 La figura 18A es un diagrama de bloques que ilustra otra realización de un amplificador de potencia vectorial para implementar un procedimiento de VPA de 2 Ramas Cartesiana Directa.

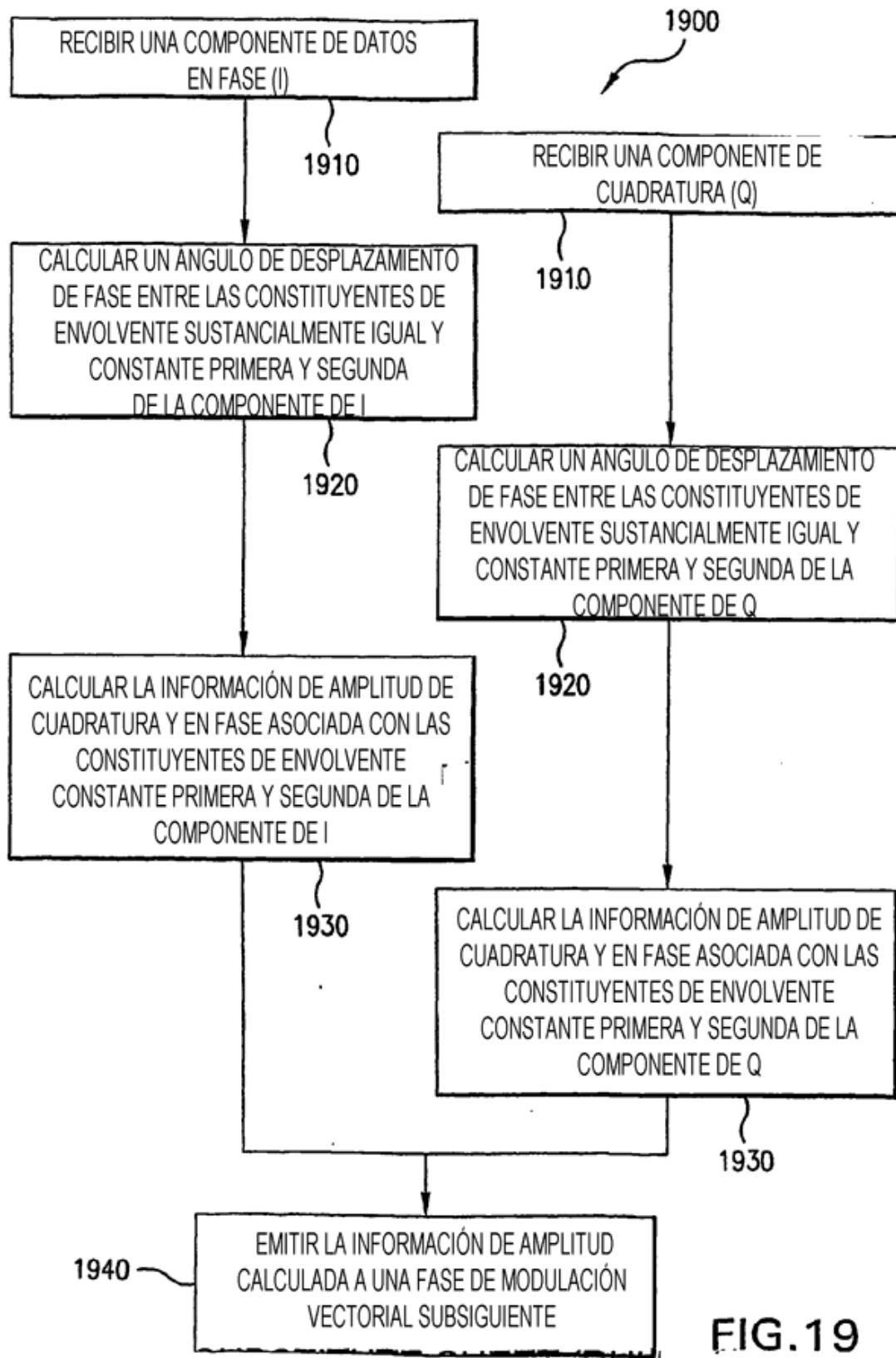

- La figura 19 es un diagrama de flujo de proceso que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

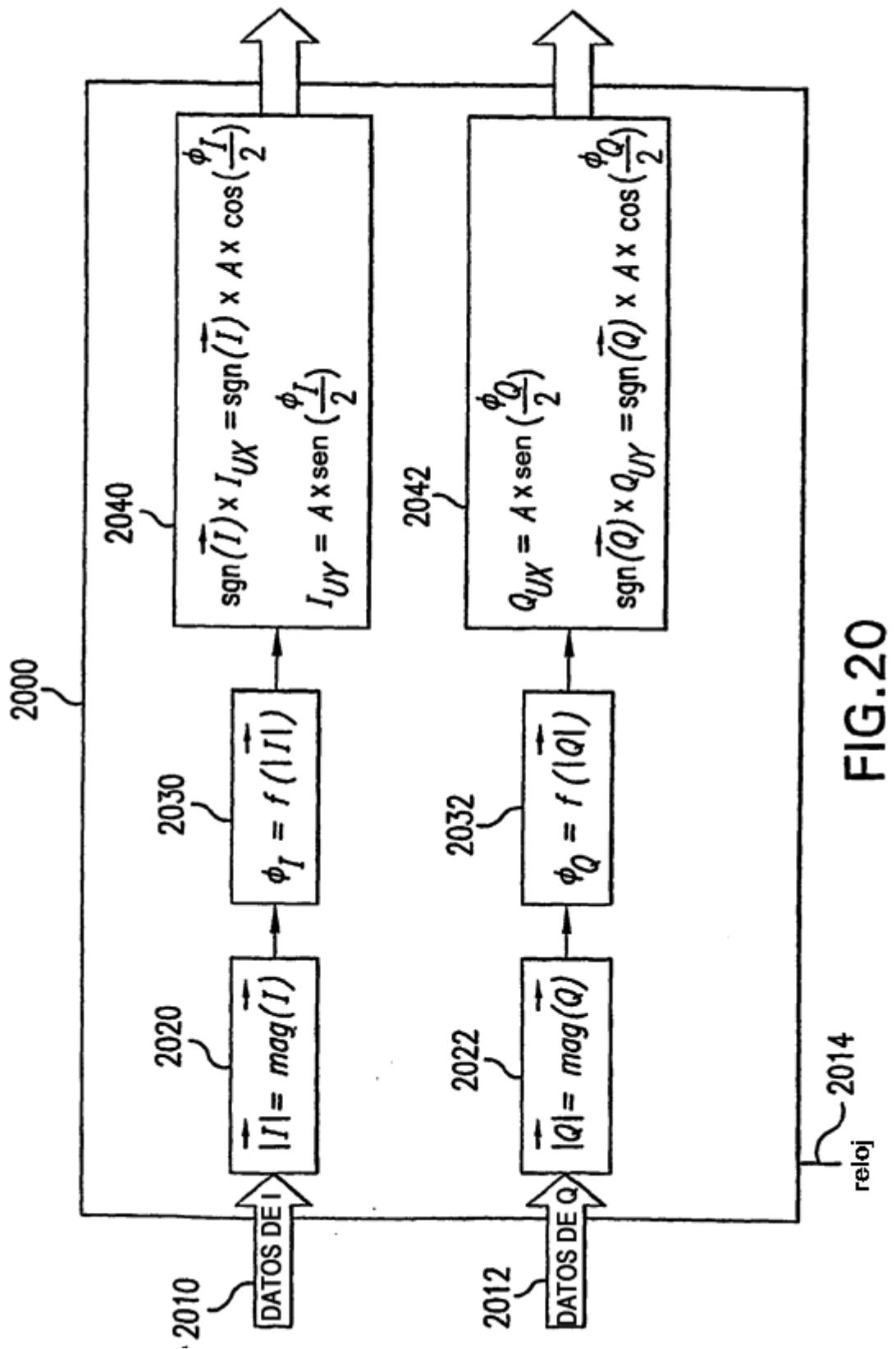

- La figura 20 es un diagrama de bloques que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 4 Ramas Cartesiana.

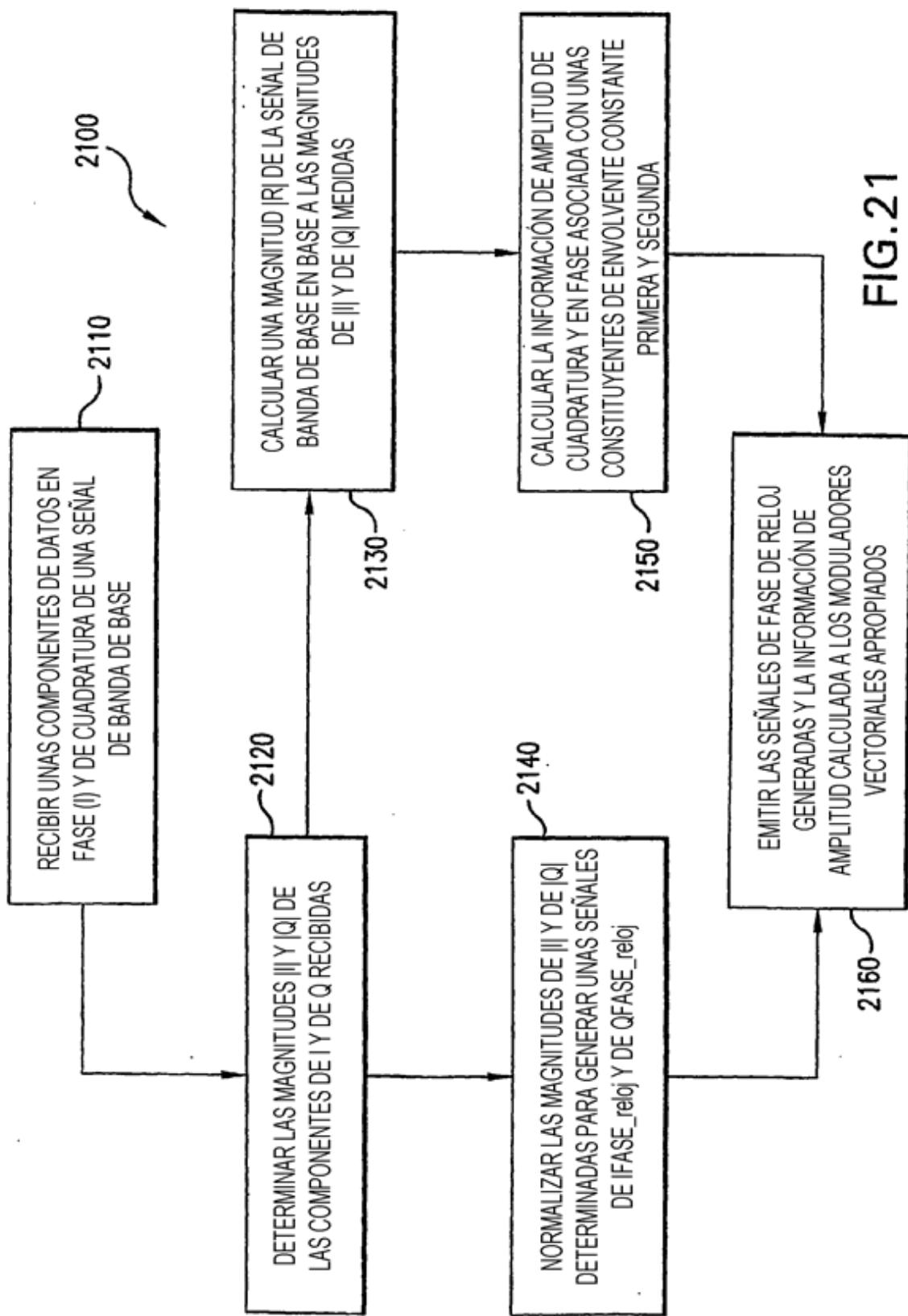

- 40 La figura 21 es un diagrama de flujo de proceso que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 2 Ramas CPCP.

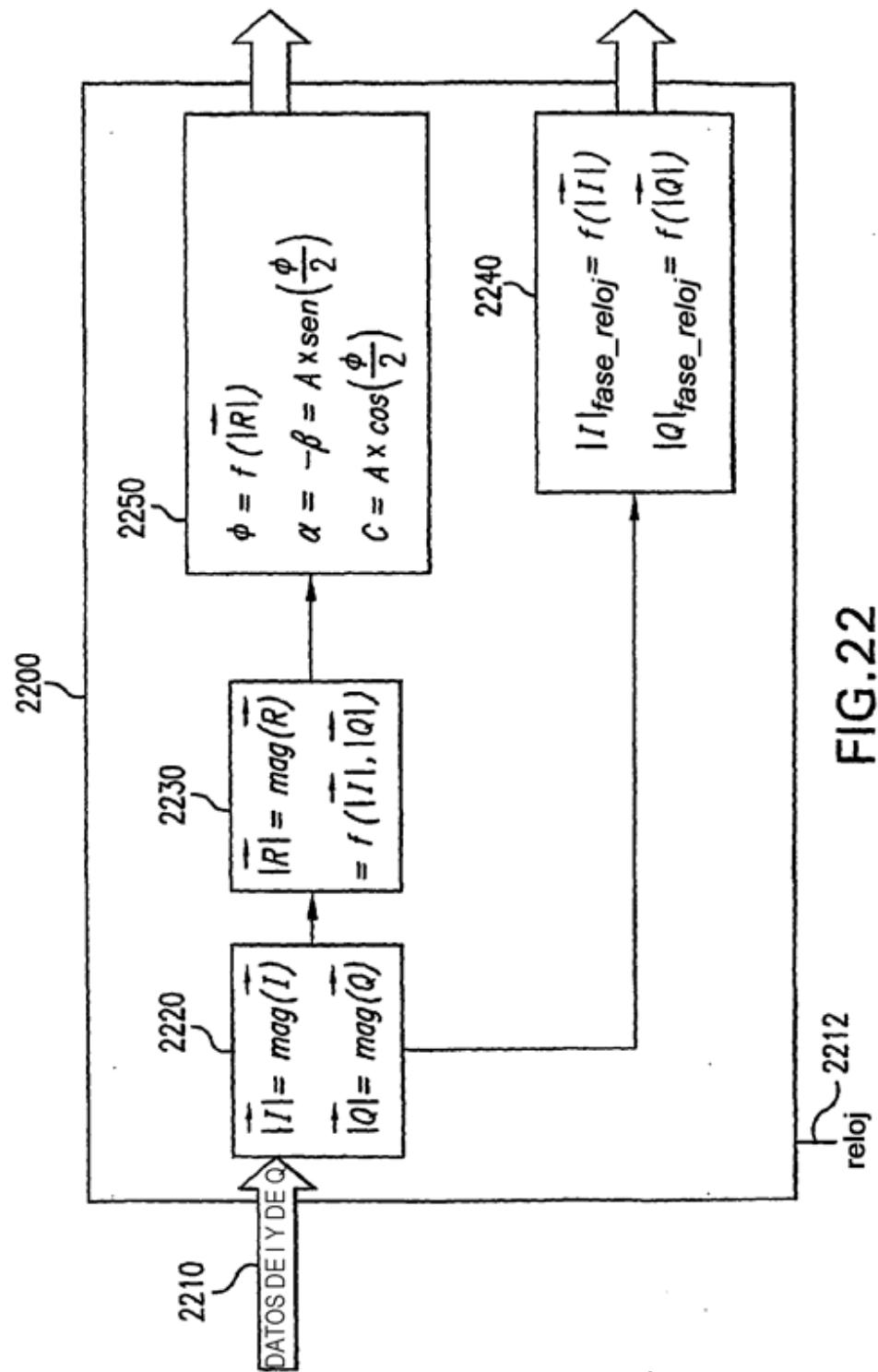

- La figura 22 es un diagrama de bloques que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 2 Ramas CPCP.

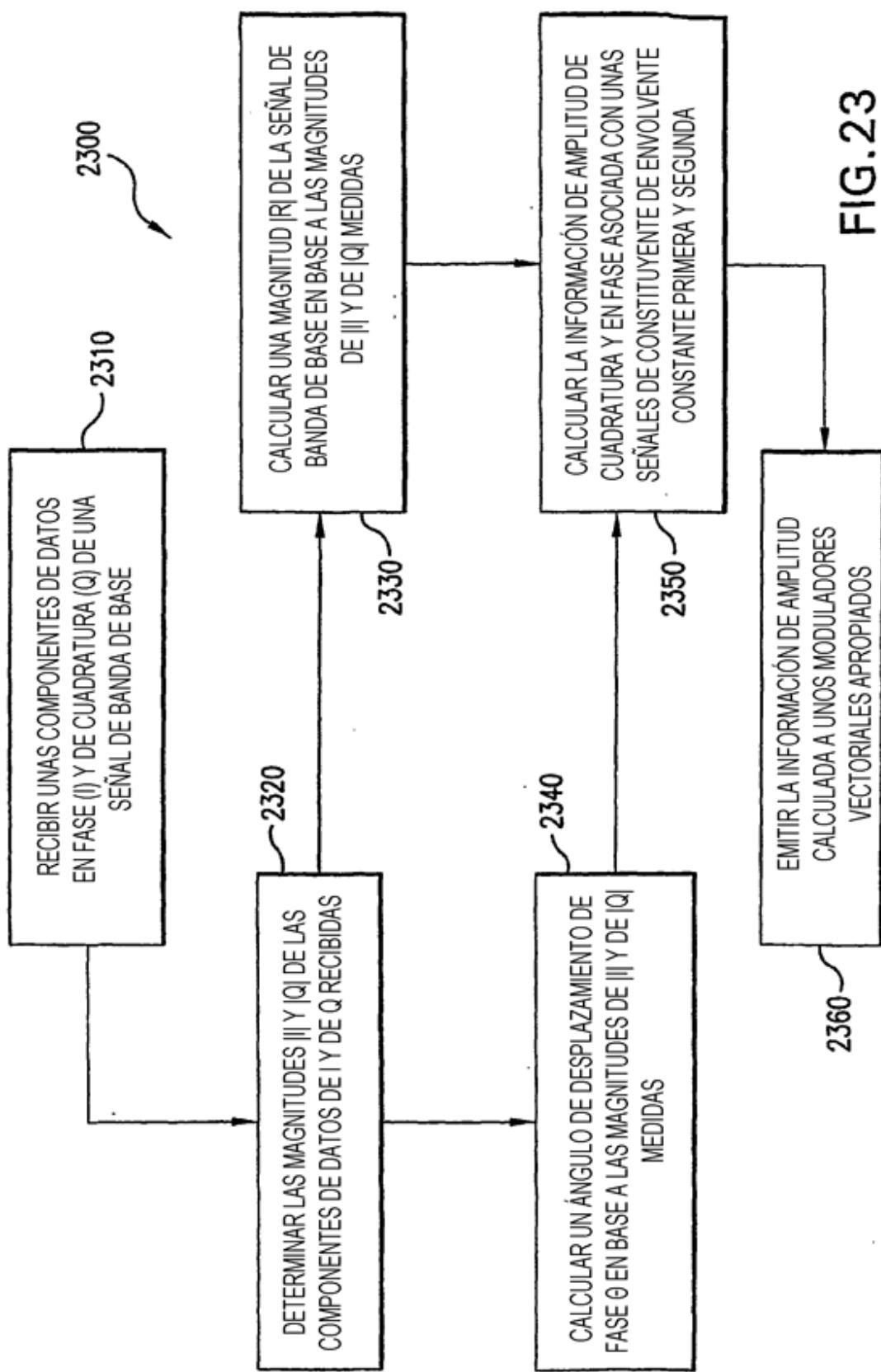

- 45 La figura 23 es un diagrama de flujo de proceso que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 2 Ramas Cartesiana Directa.

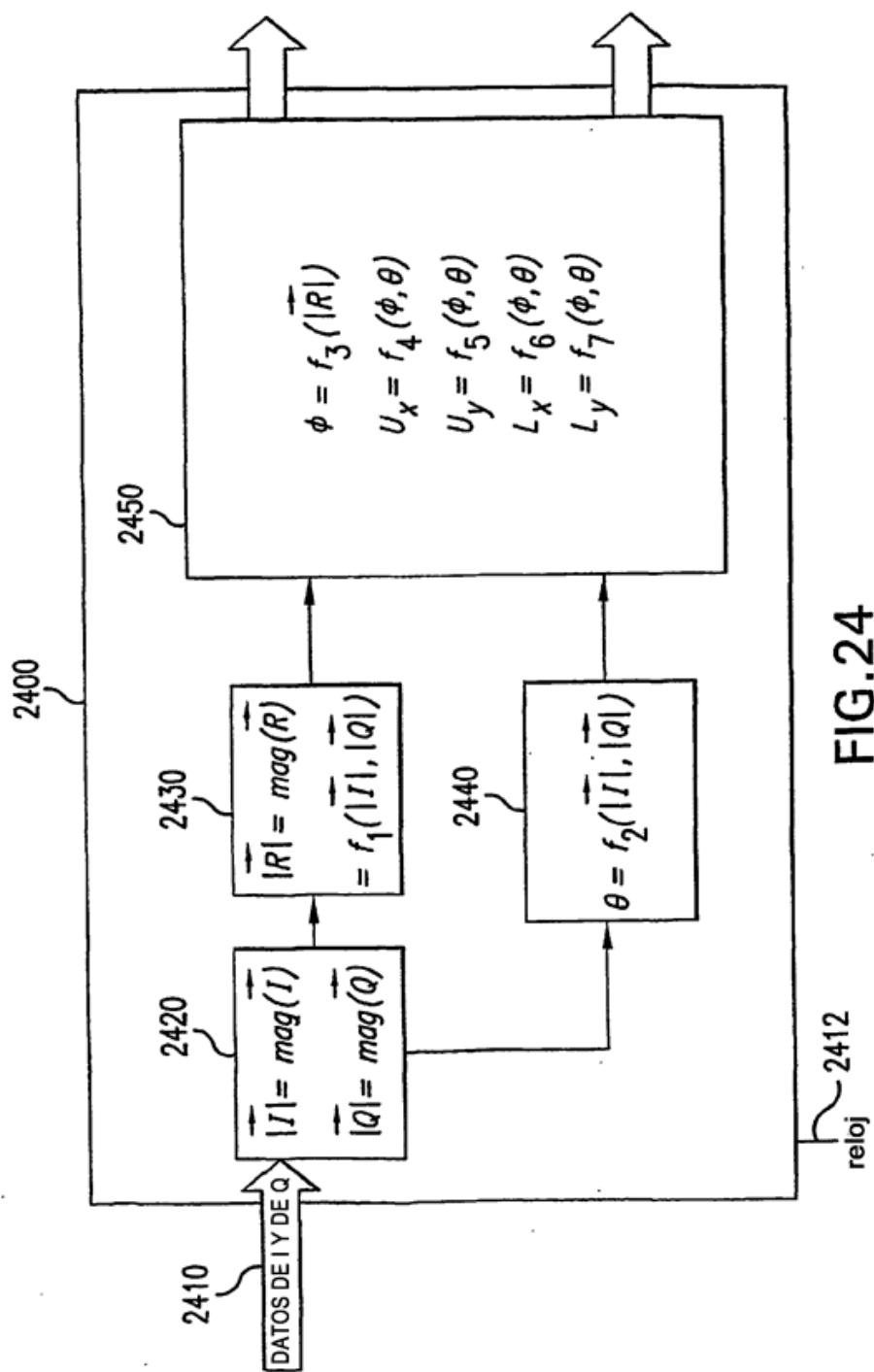

- La figura 24 es un diagrama de bloques que ilustra una función de transferencia de I y de Q ejemplar de acuerdo con un procedimiento de VPA de 2 Ramas Cartesiana Directa.

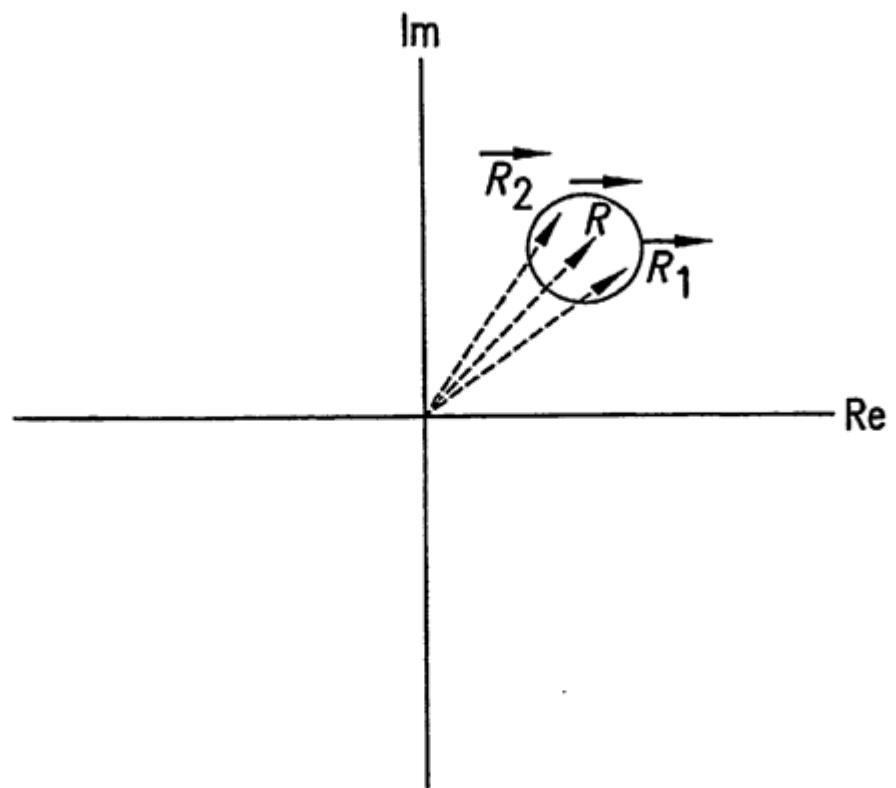

- La figura 25 es un diagrama fasorial que ilustra el efecto de la distorsión de forma de onda sobre una representación de un fasor de señal.

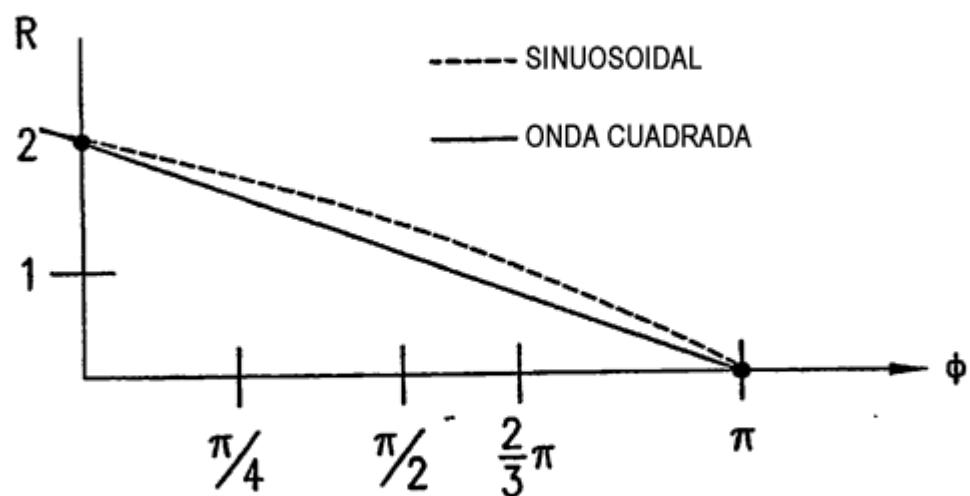

- 50 La figura 26 ilustra unas funciones de transformada de magnitud en fase.

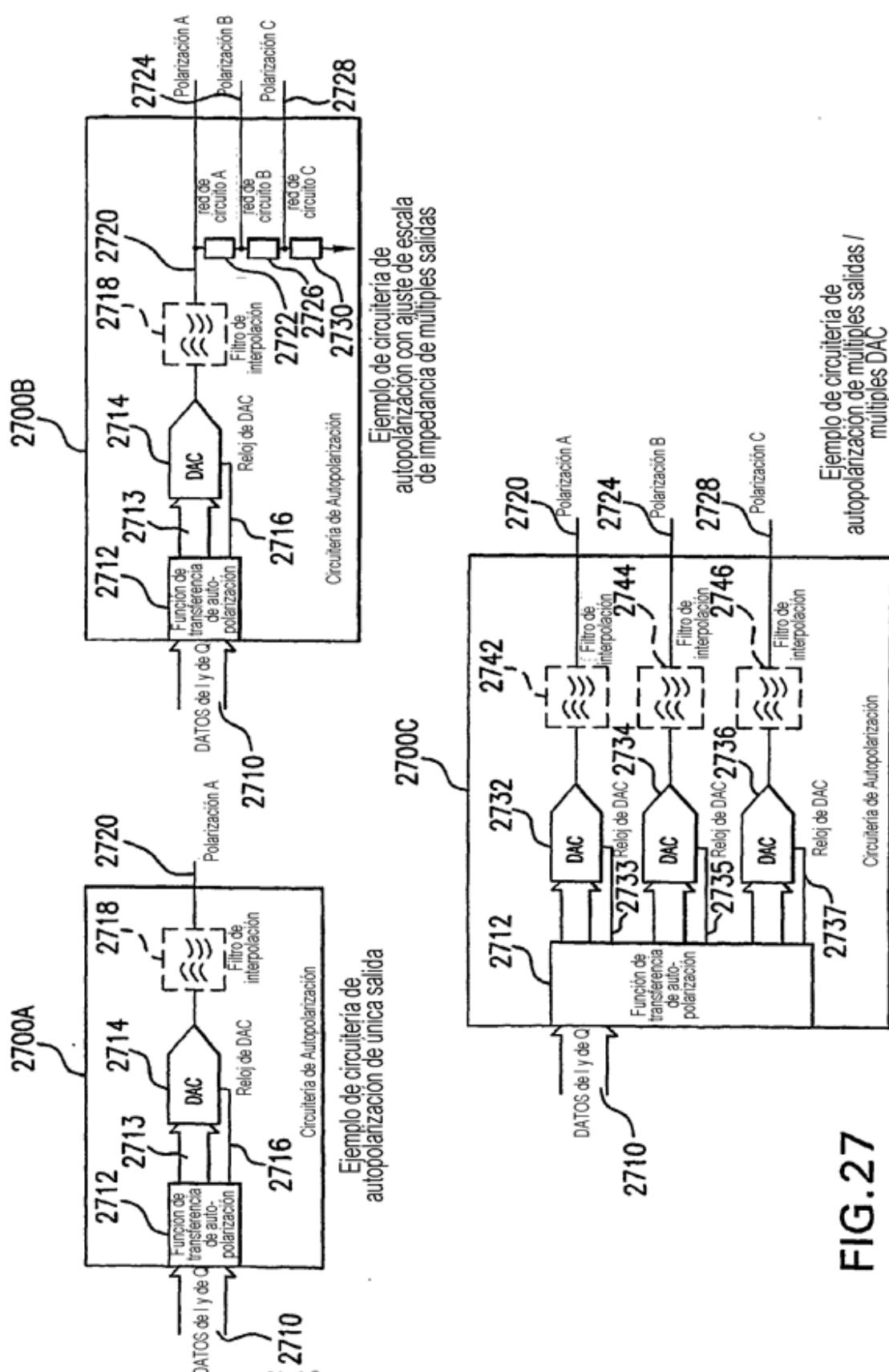

- La figura 27 ilustra unas realizaciones ejemplares de una circuitería de polarización de acuerdo con las realizaciones de la presente invención.

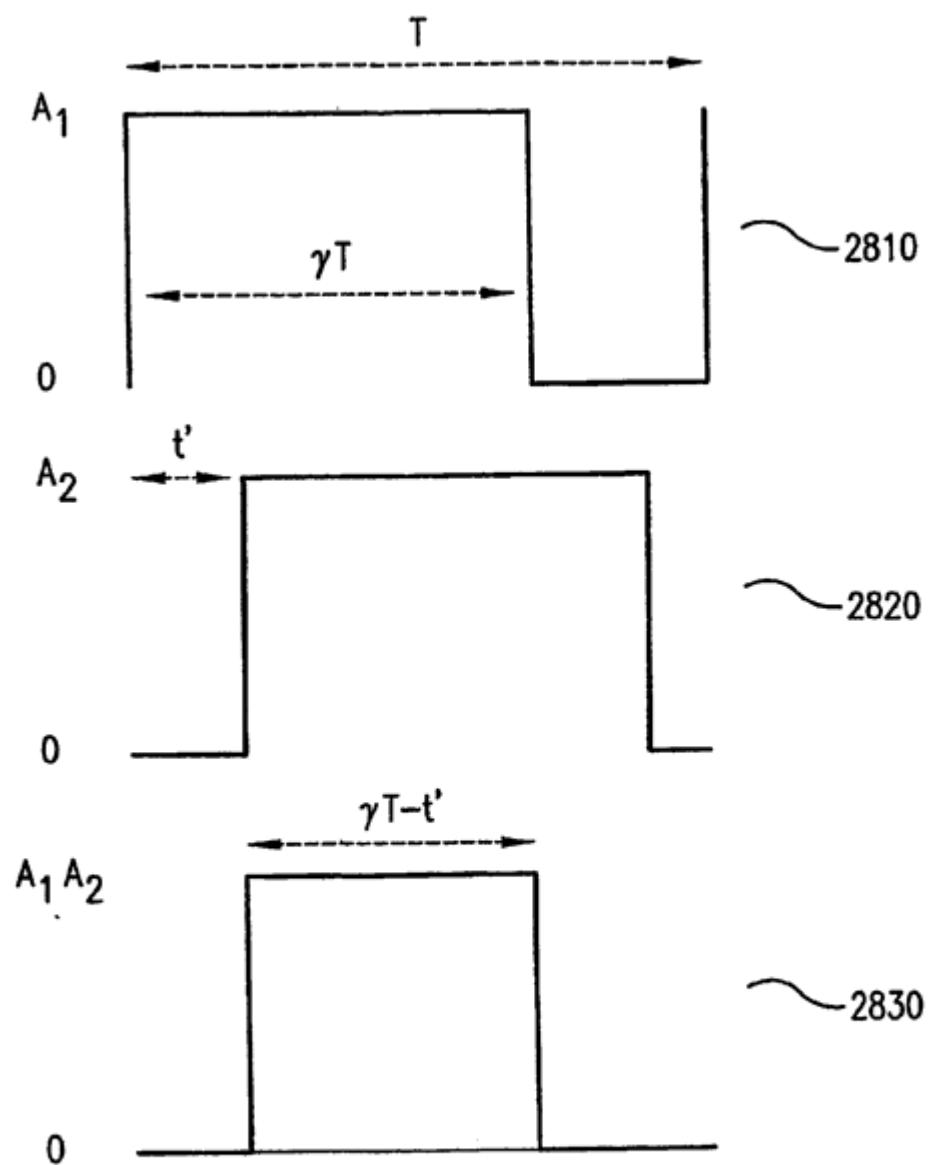

- La figura 28 ilustra un procedimiento ejemplar de combinación de unas señales de envolvente constante.

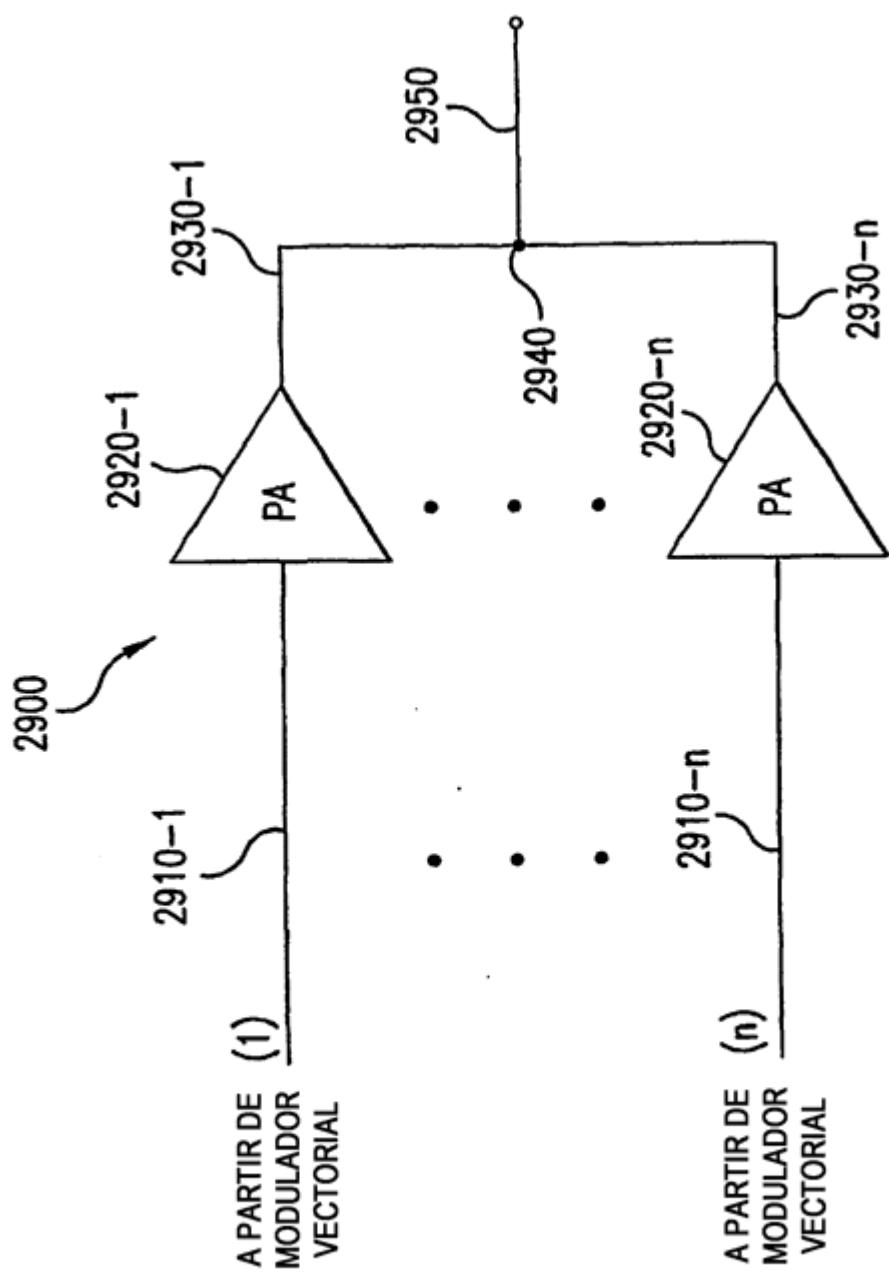

- La figura 29 ilustra una fase de salida de amplificador de potencia vectorial ejemplar.

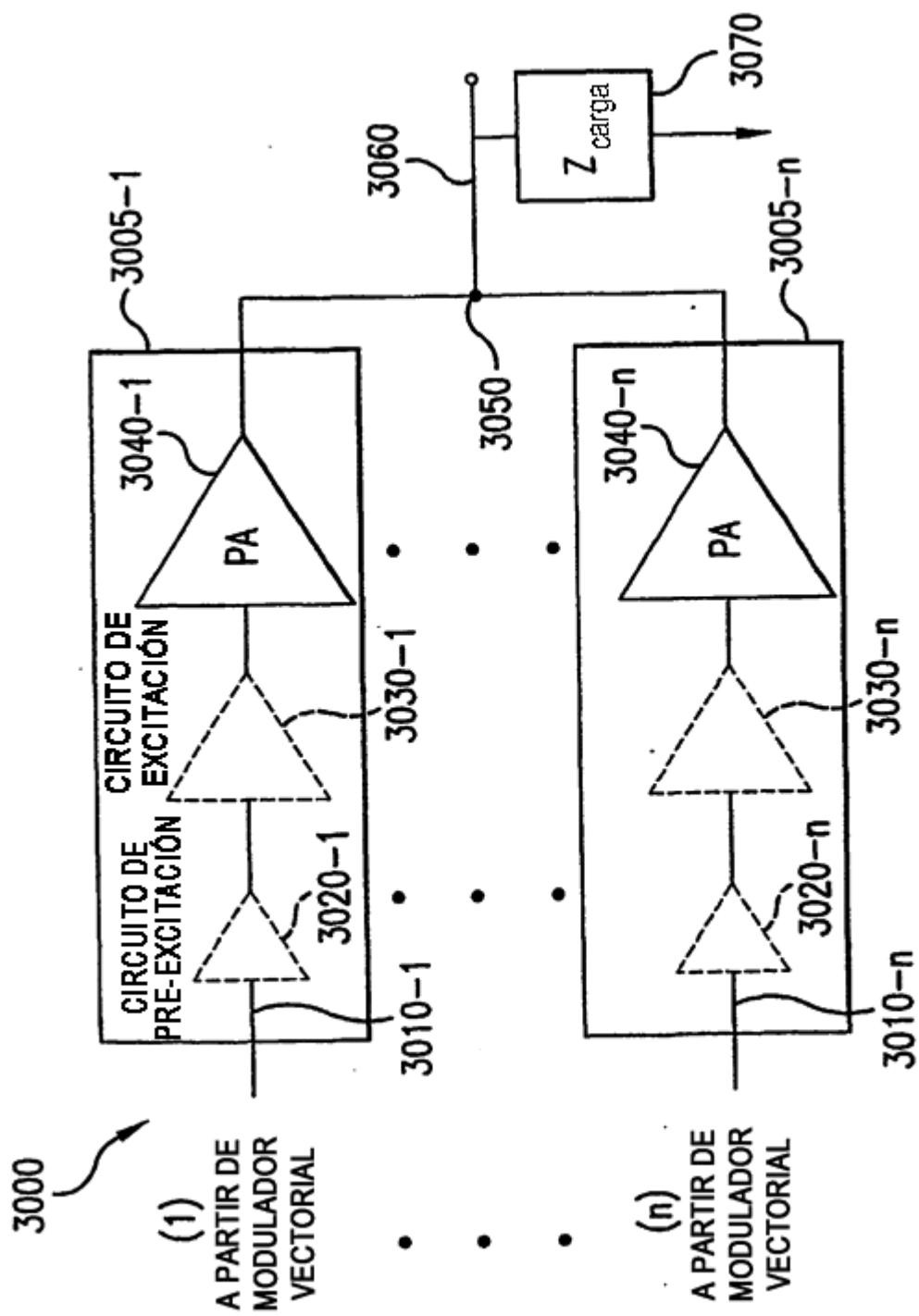

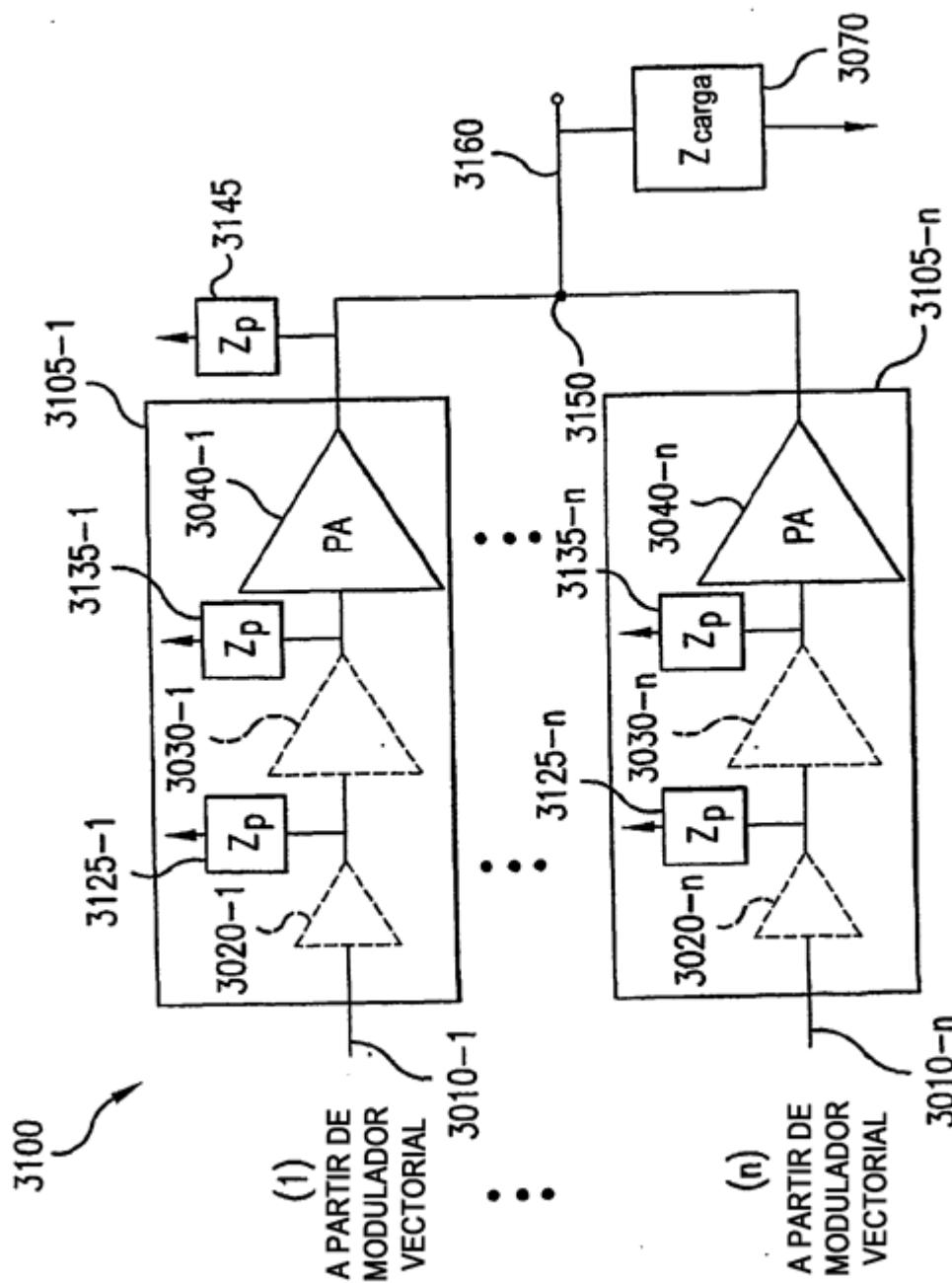

- 55 La figura 30 es un diagrama de bloques ejemplar de una fase de salida de amplificador de potencia (PA).

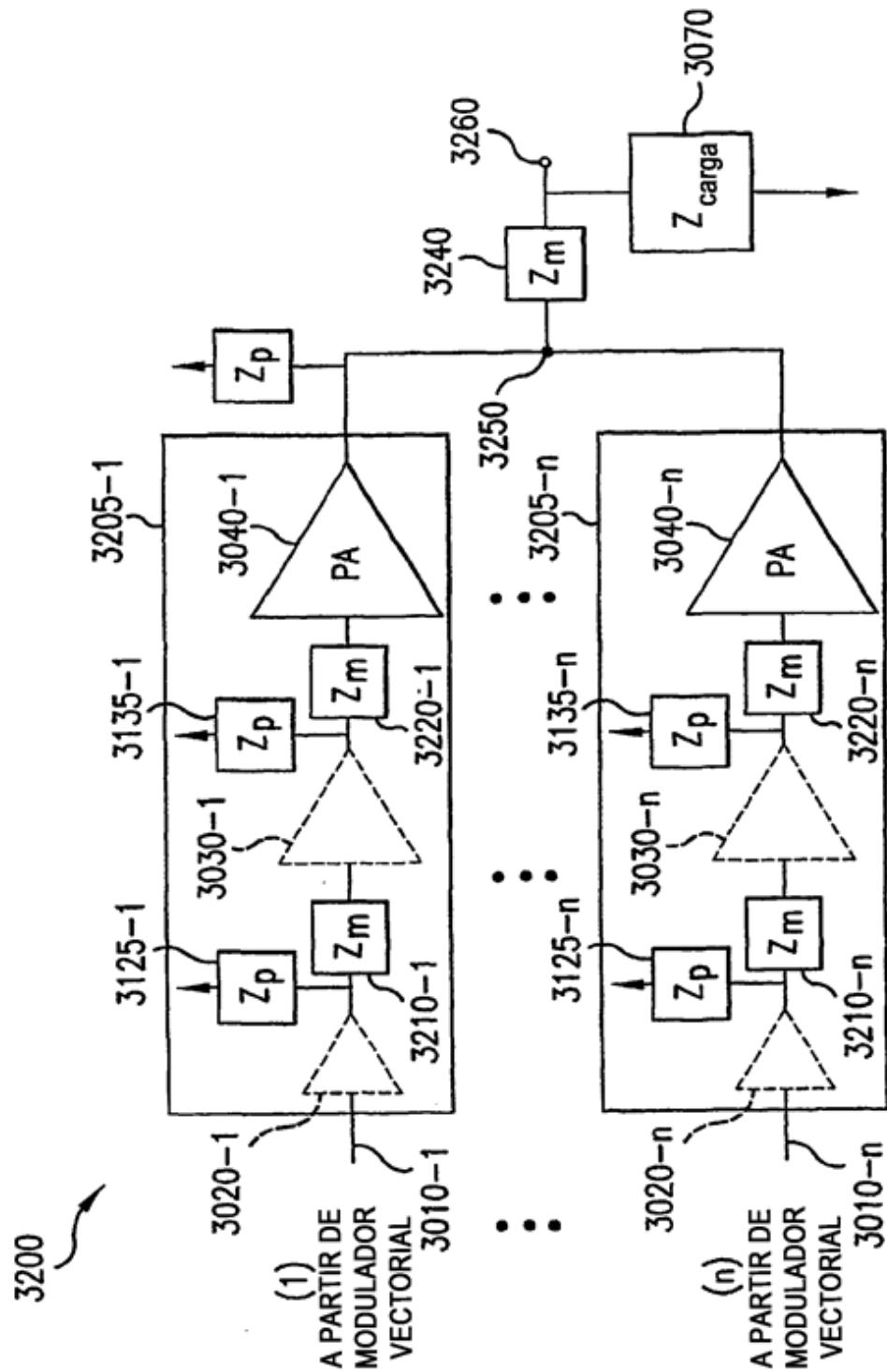

- La figura 31 es un diagrama de bloques de otra fase de salida de amplificador de potencia (PA) ejemplar.

- La figura 32 es un diagrama de bloques de otra fase de salida de amplificador de potencia (PA) ejemplar.

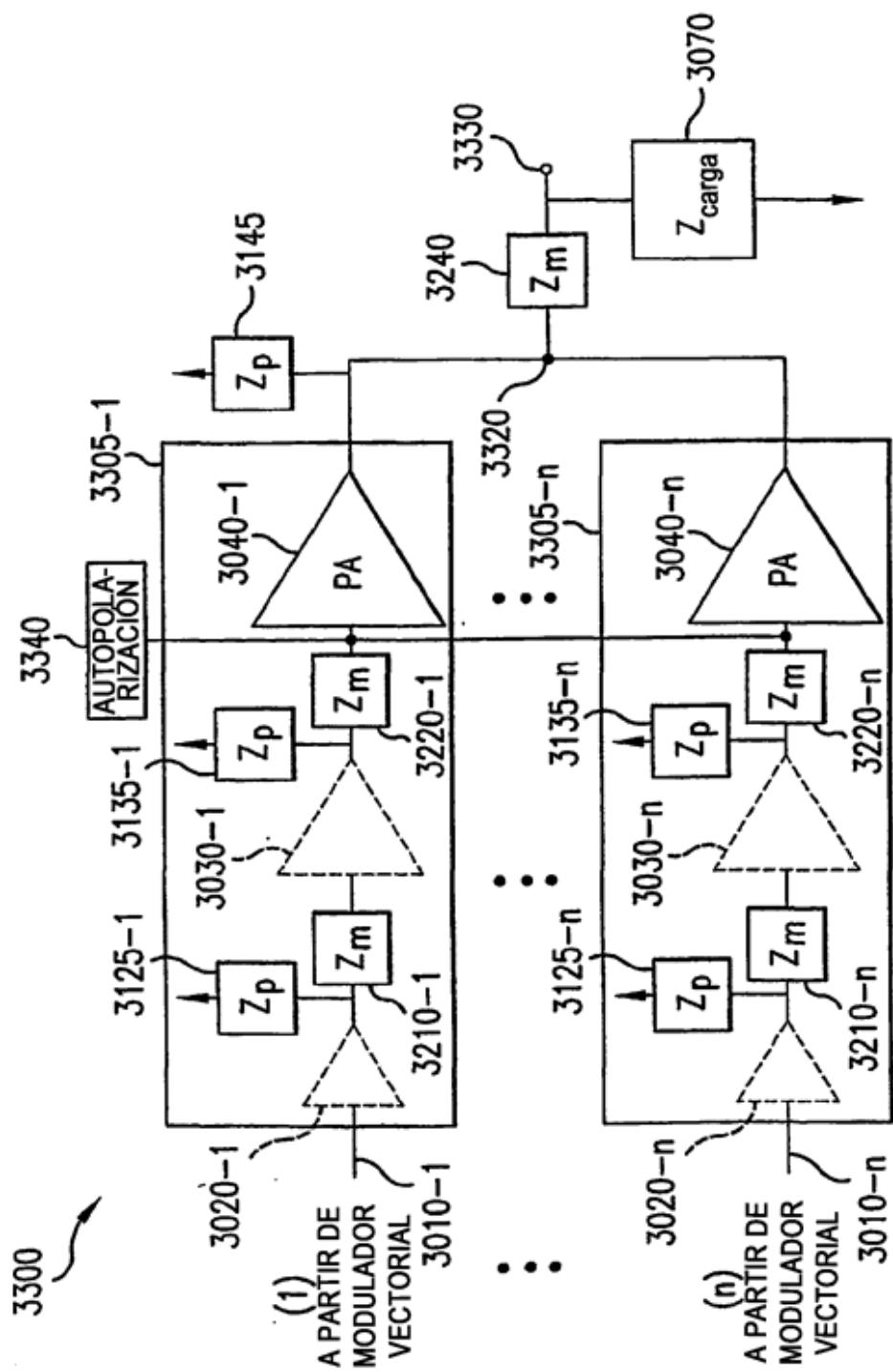

- La figura 33 es un diagrama de bloques de otra realización de fase de salida de amplificador de potencia (PA) de acuerdo con la presente invención.

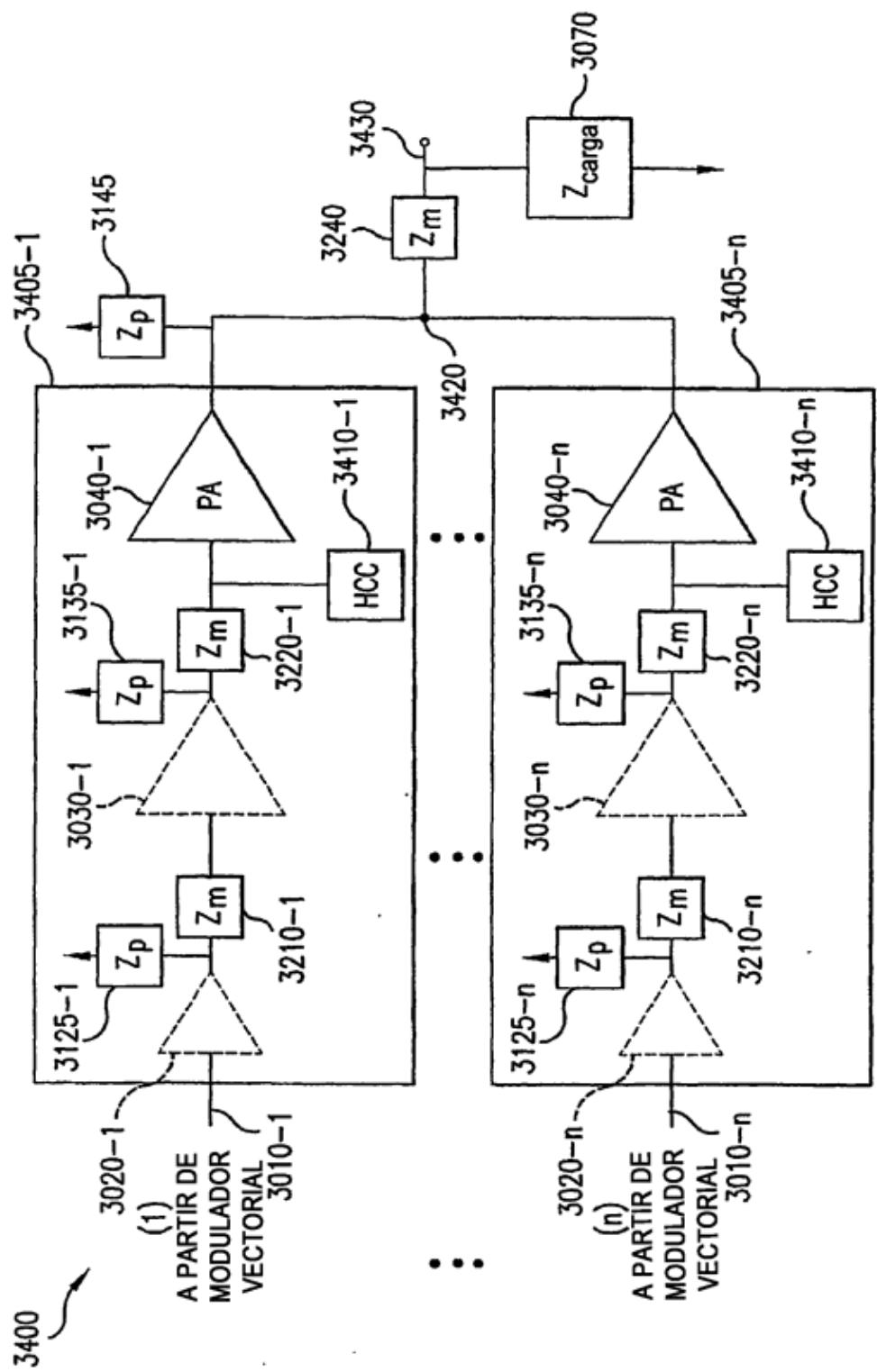

- 60 La figura 34 es un diagrama de bloques de otra fase de salida de amplificador de potencia (PA) ejemplar.

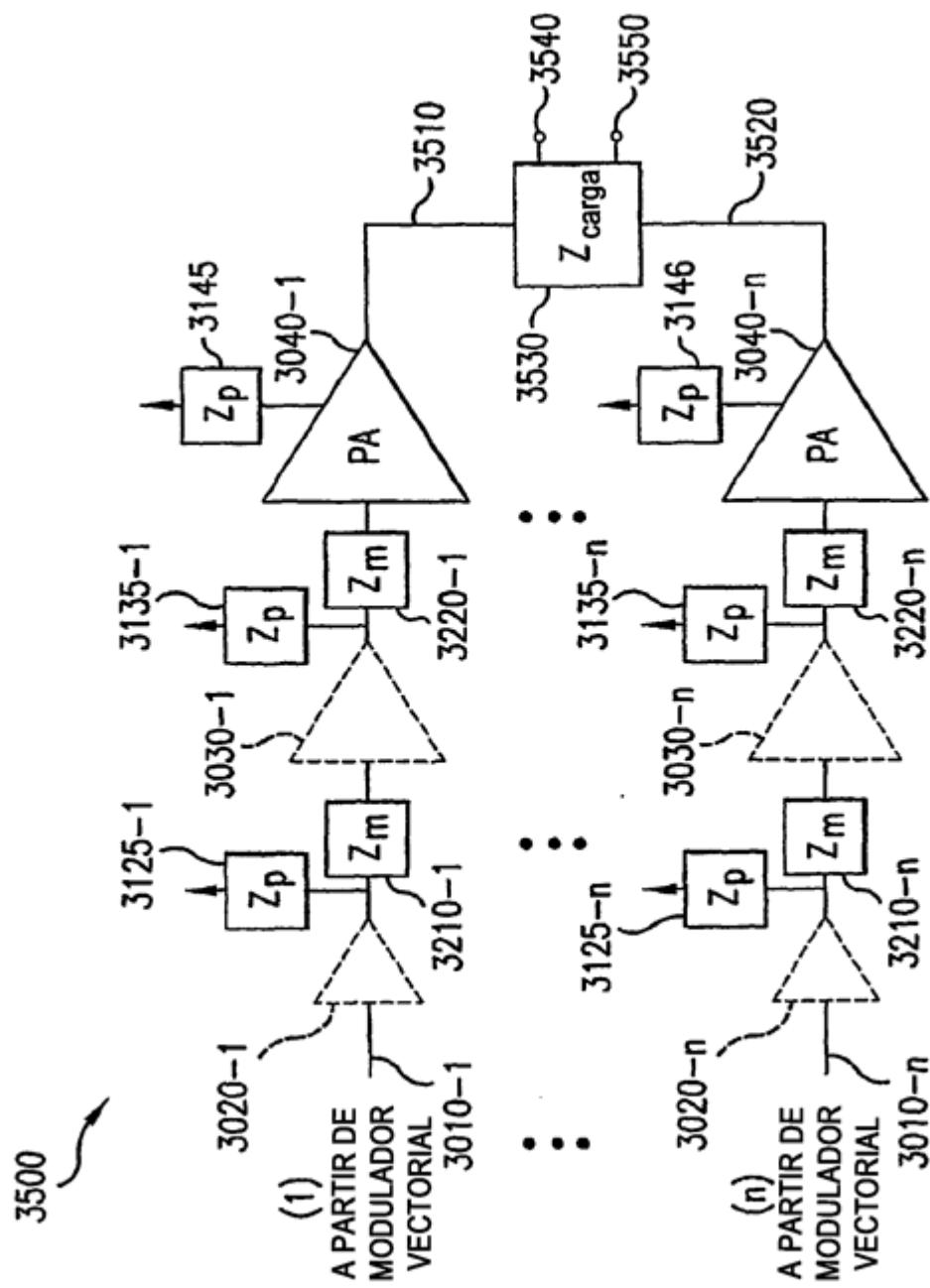

- La figura 35 es un diagrama de bloques de otra fase de salida de amplificador de potencia (PA) ejemplar.

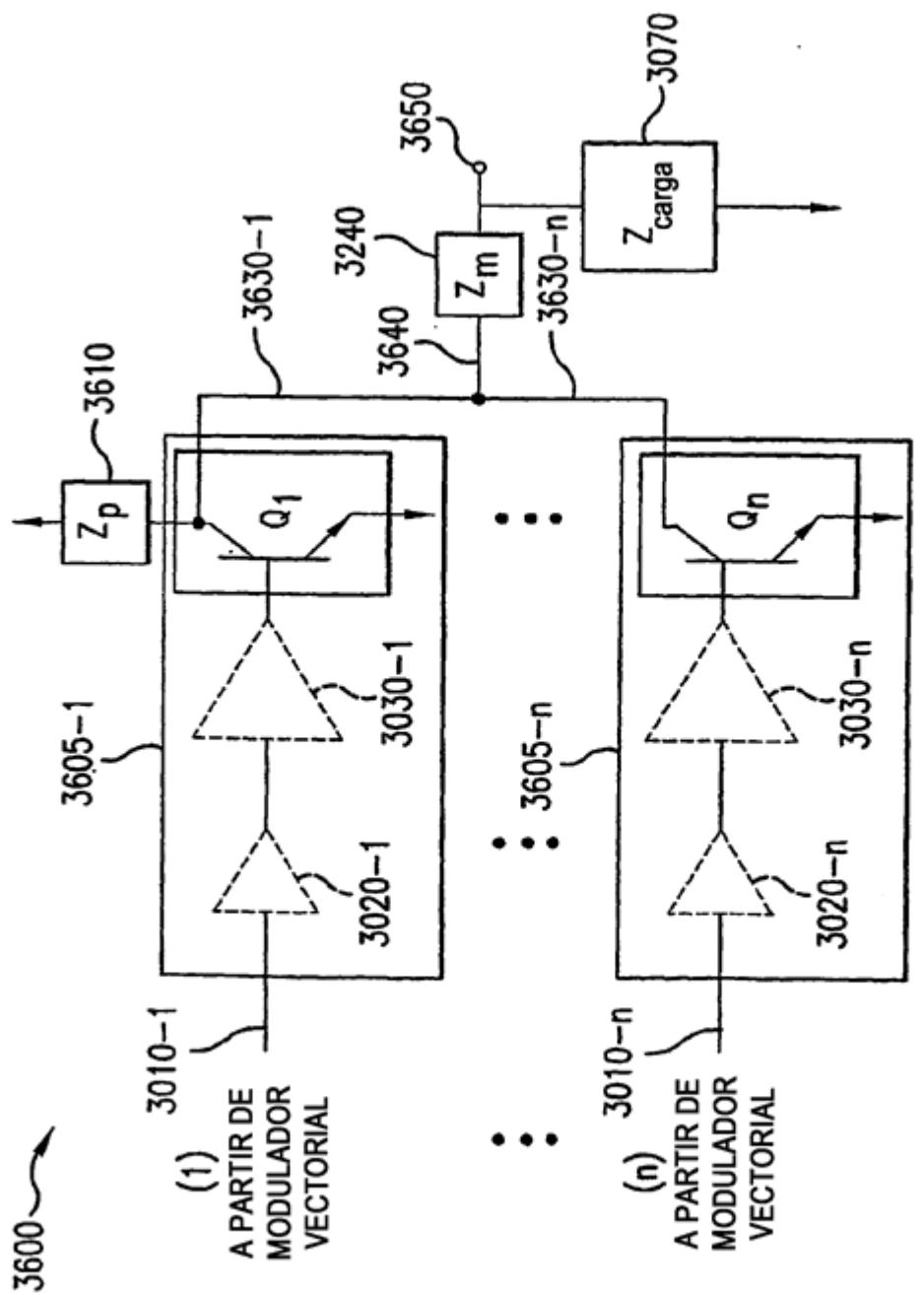

- La figura 36 es un diagrama de bloques de otra fase de salida de amplificador de potencia (PA) ejemplar.

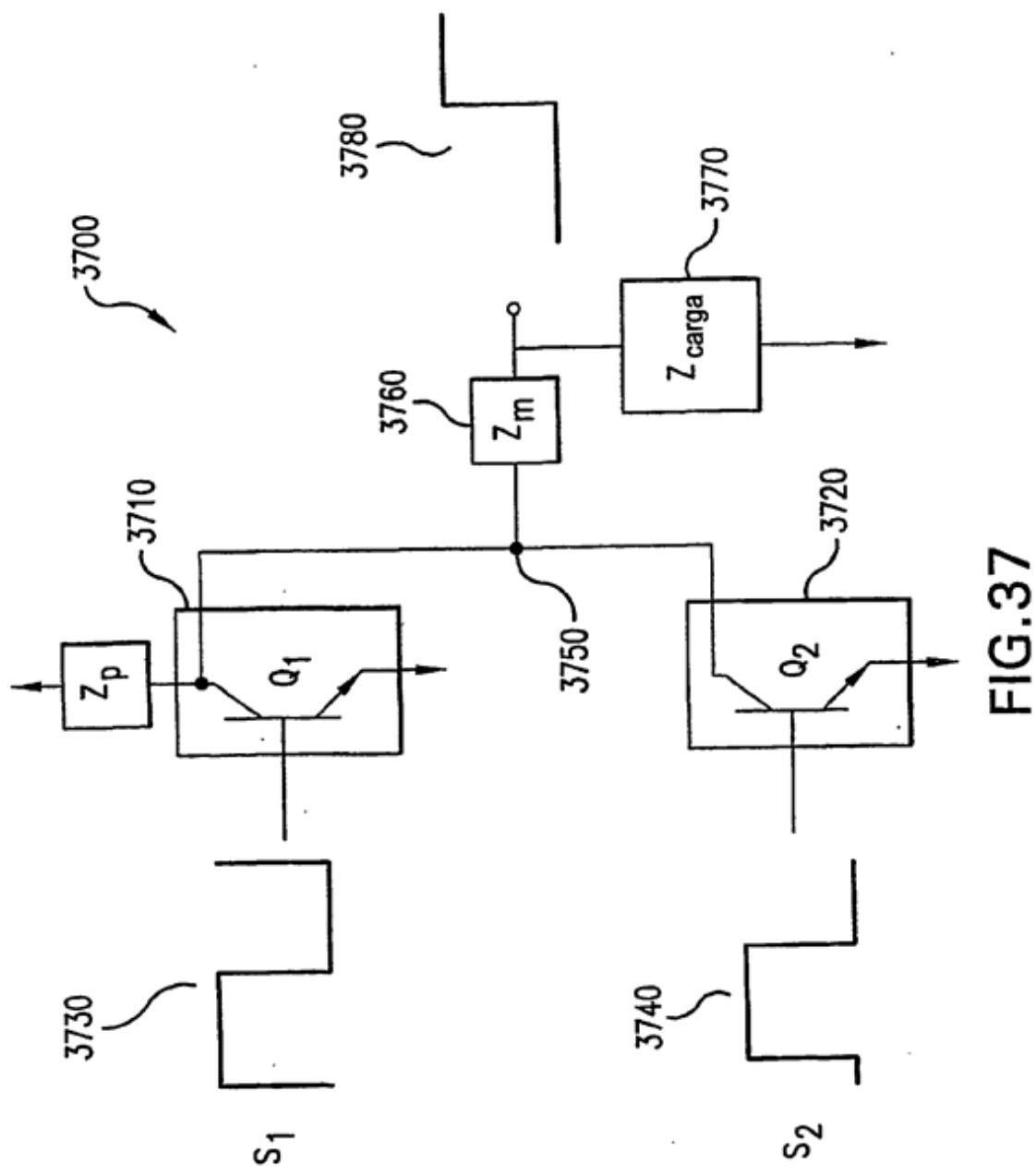

- La figura 37 ilustra una señal de salida a modo de ejemplo.

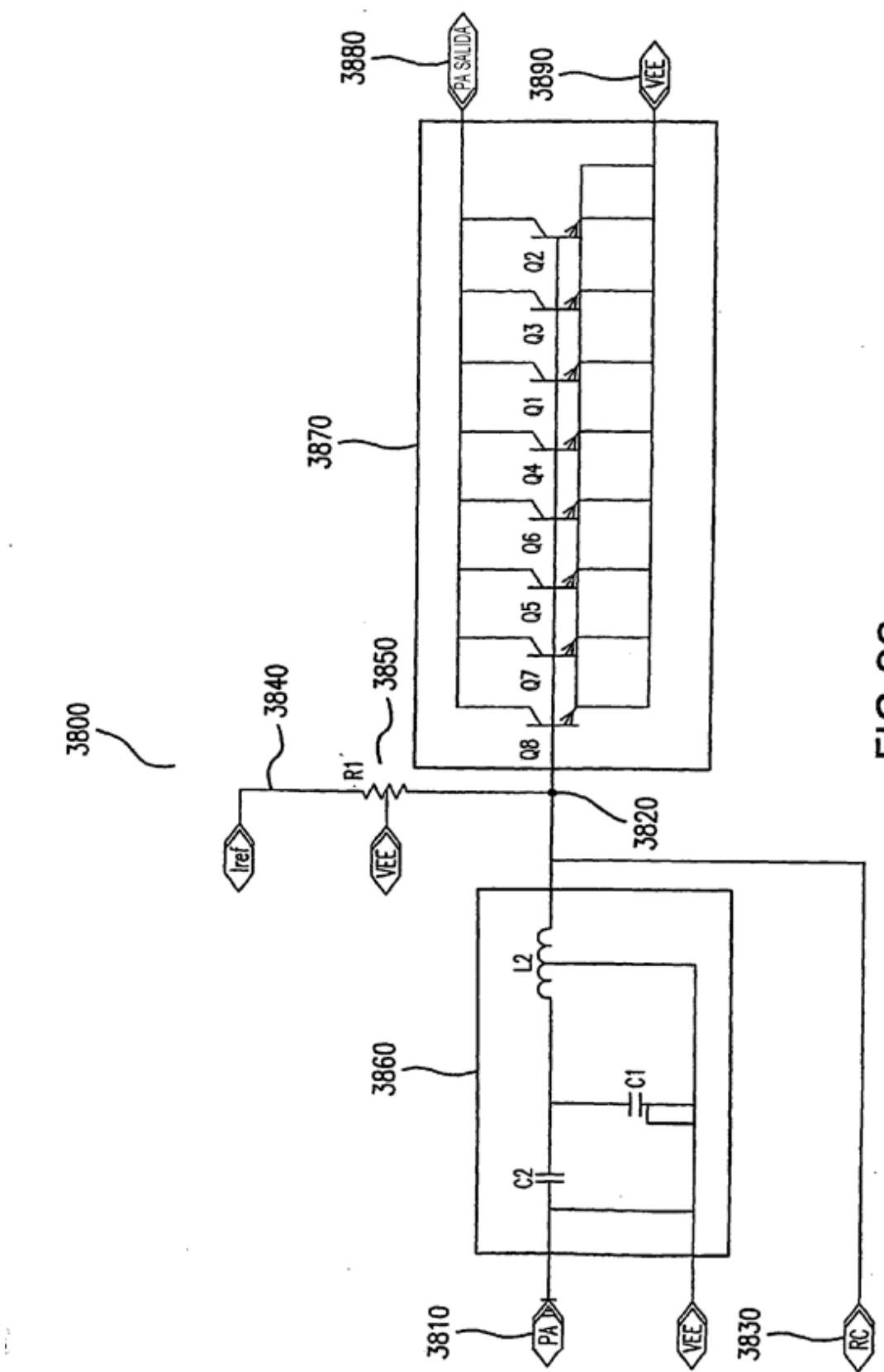

- La figura 38 ilustra una realización de PA ejemplar.

- 65 La figura 39 ilustra una señal de salida de PA de envolvente compleja variable en el tiempo a modo de ejemplo y una señal de envolvente correspondiente.

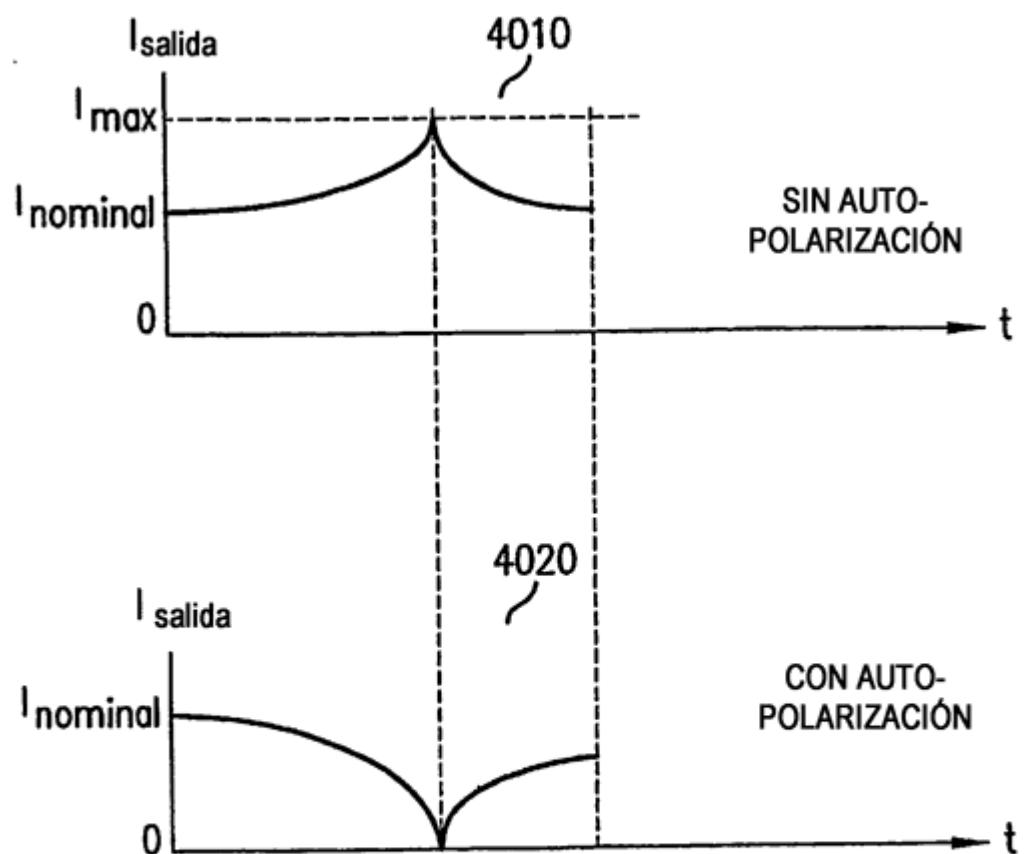

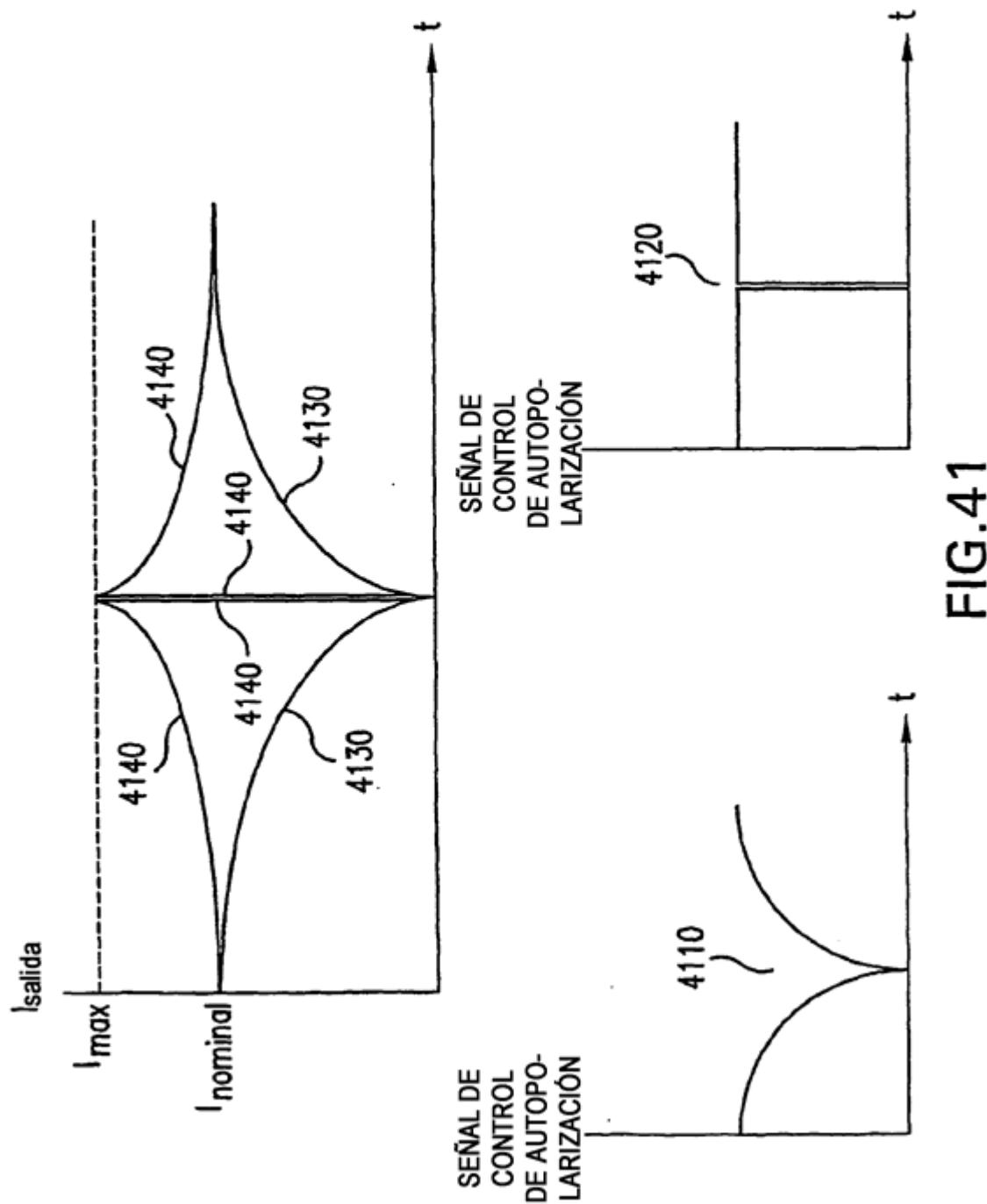

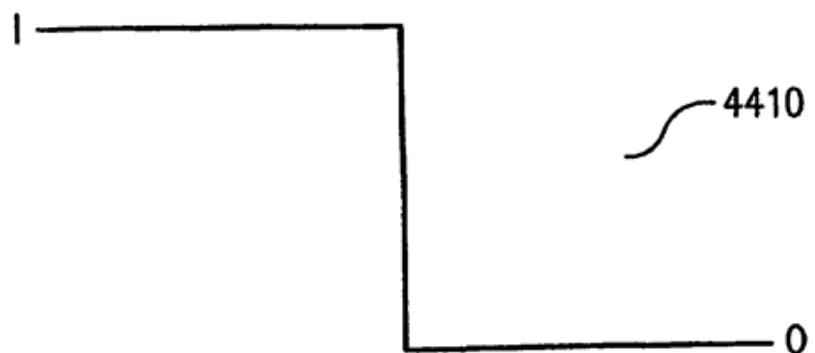

- La figura 40 ilustra unos diagramas de sincronismo a modo de ejemplo de una intensidad de fase de salida de PA.

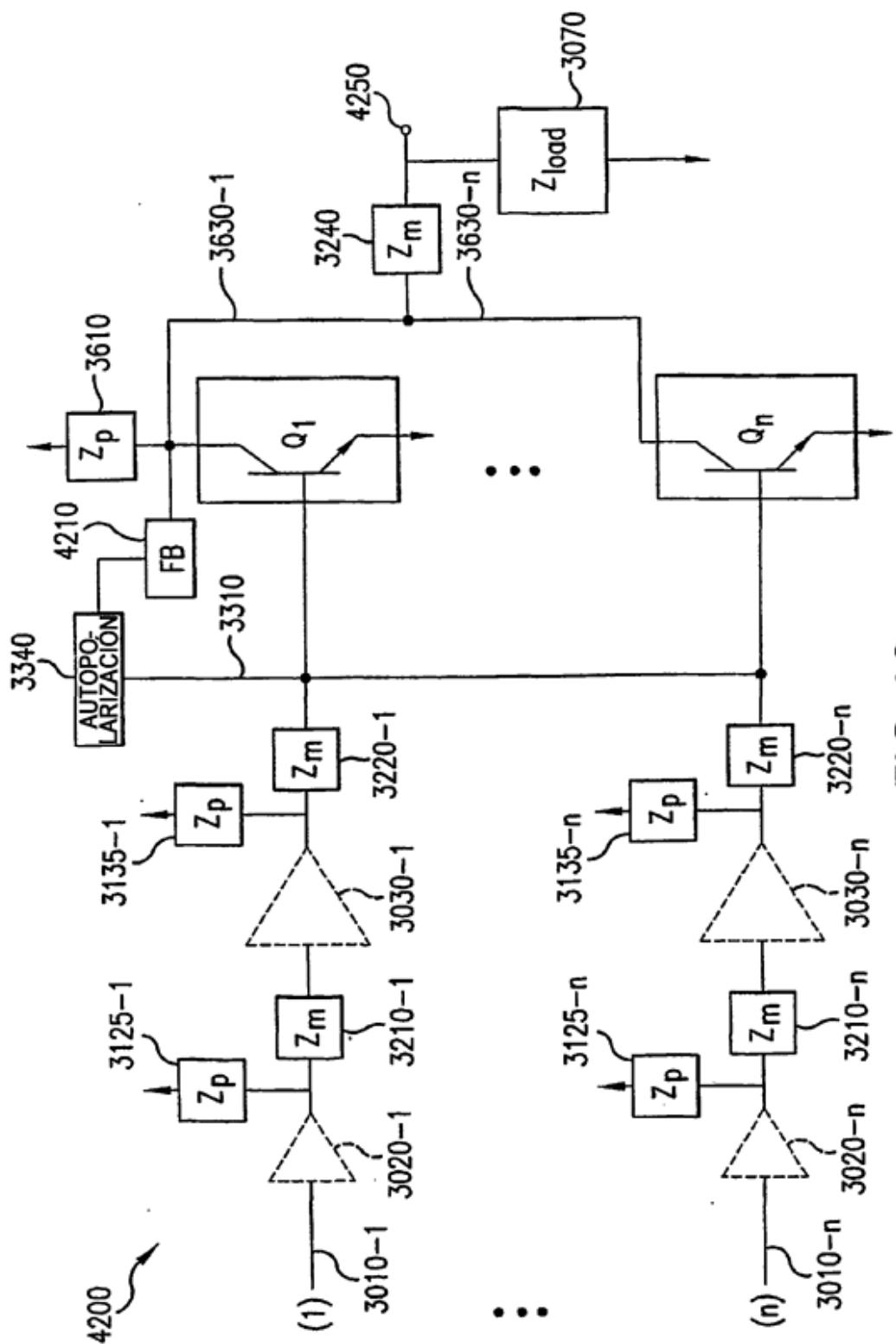

- 5 La figura 41 ilustra unas funciones de control de intensidad de fase de salida ejemplares.

- La figura 42 es un diagrama de bloques de otra realización de fase de salida de amplificador de potencia (PA).

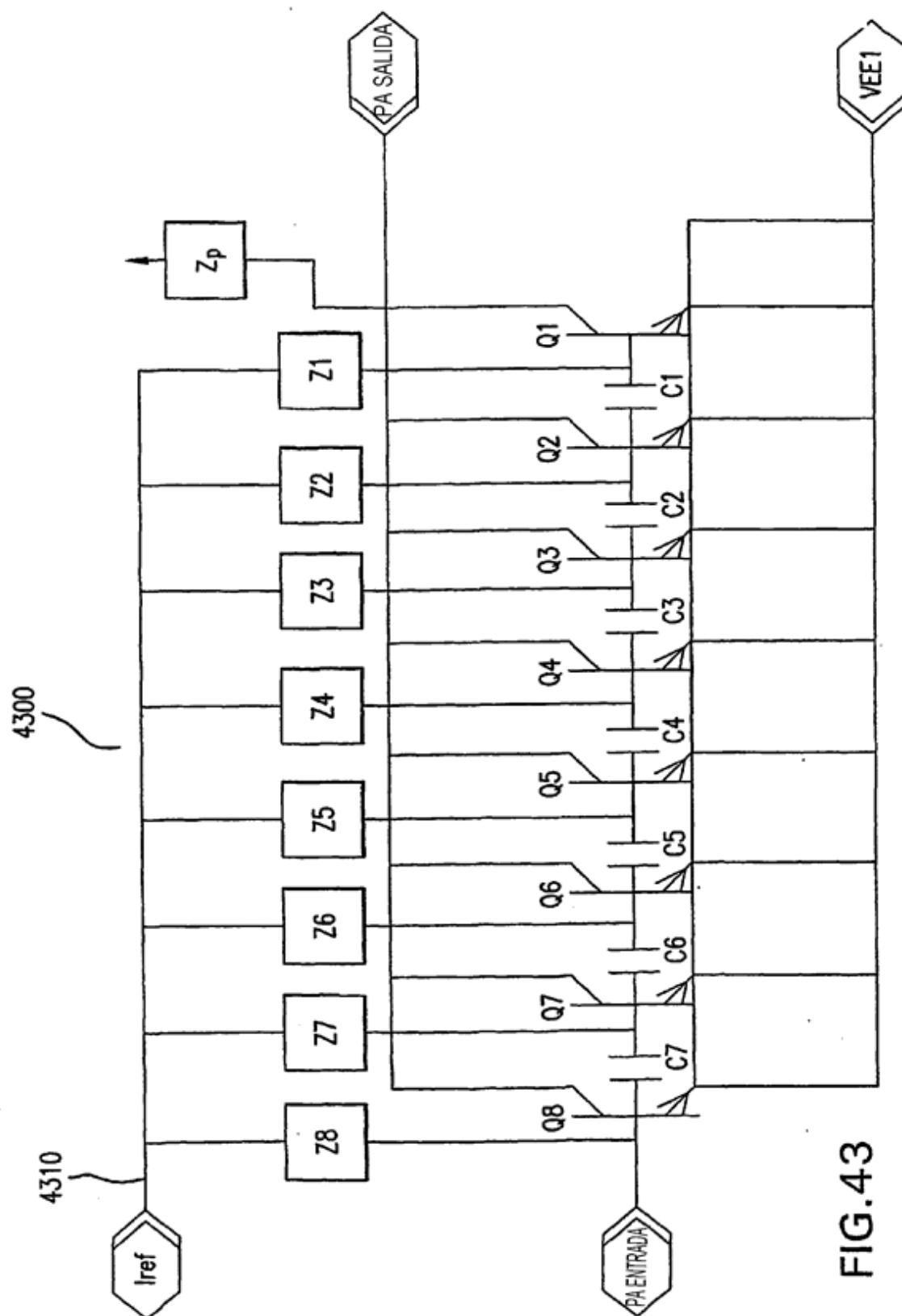

- La figura 43 ilustra una realización de fase de PA.

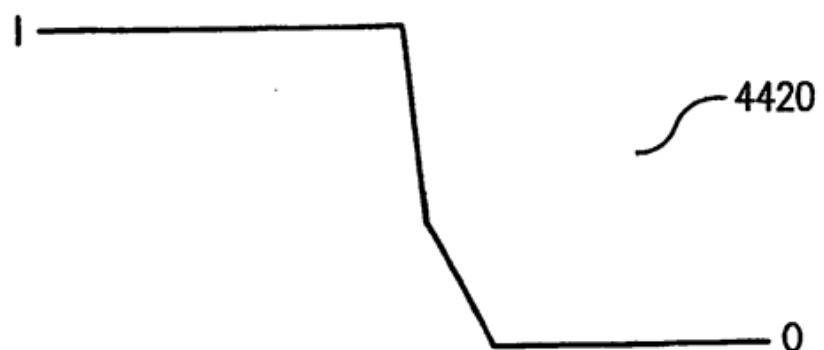

- La figura 44 ilustra una señal de salida de PA con forma ondulada ejemplar.

- La figura 45 ilustra un procedimiento de control de potencia ejemplar.

- La figura 46 ilustra otro procedimiento de control de potencia ejemplar.

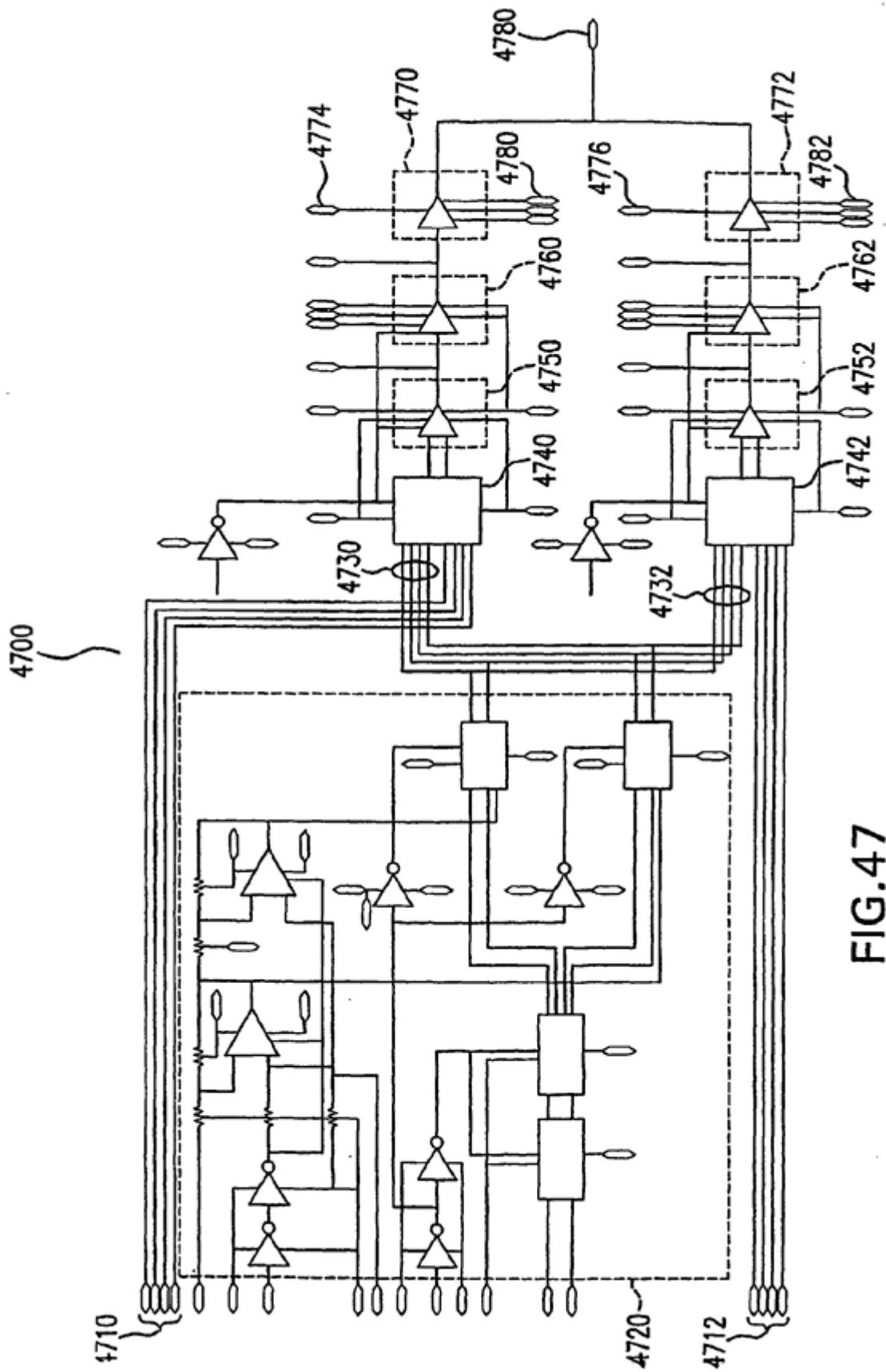

- 10 La figura 47 ilustra un amplificador de potencia vectorial ejemplar.

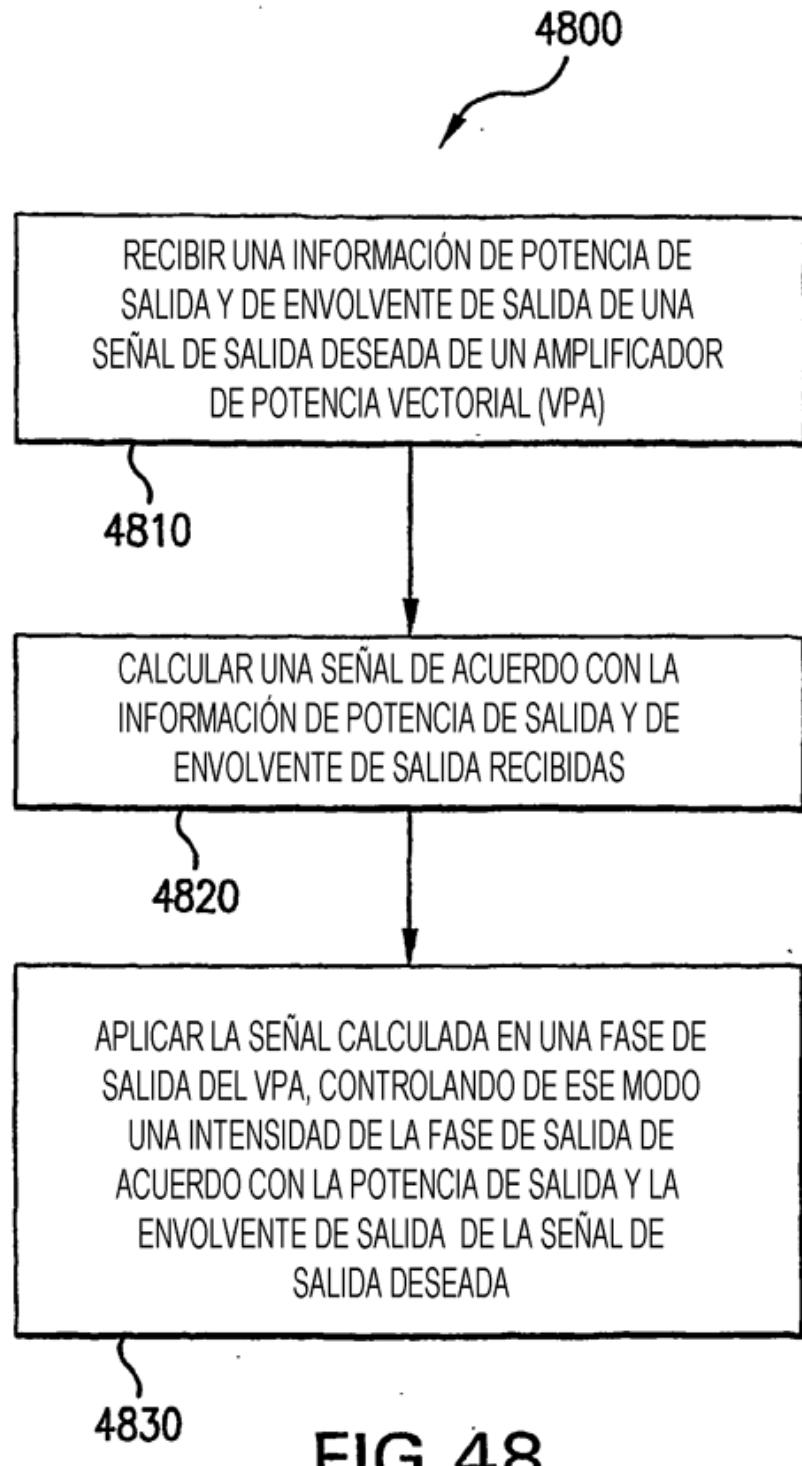

- La figura 48 es un diagrama de flujo de proceso ejemplar para implementar una conformación de intensidad de fase de salida.

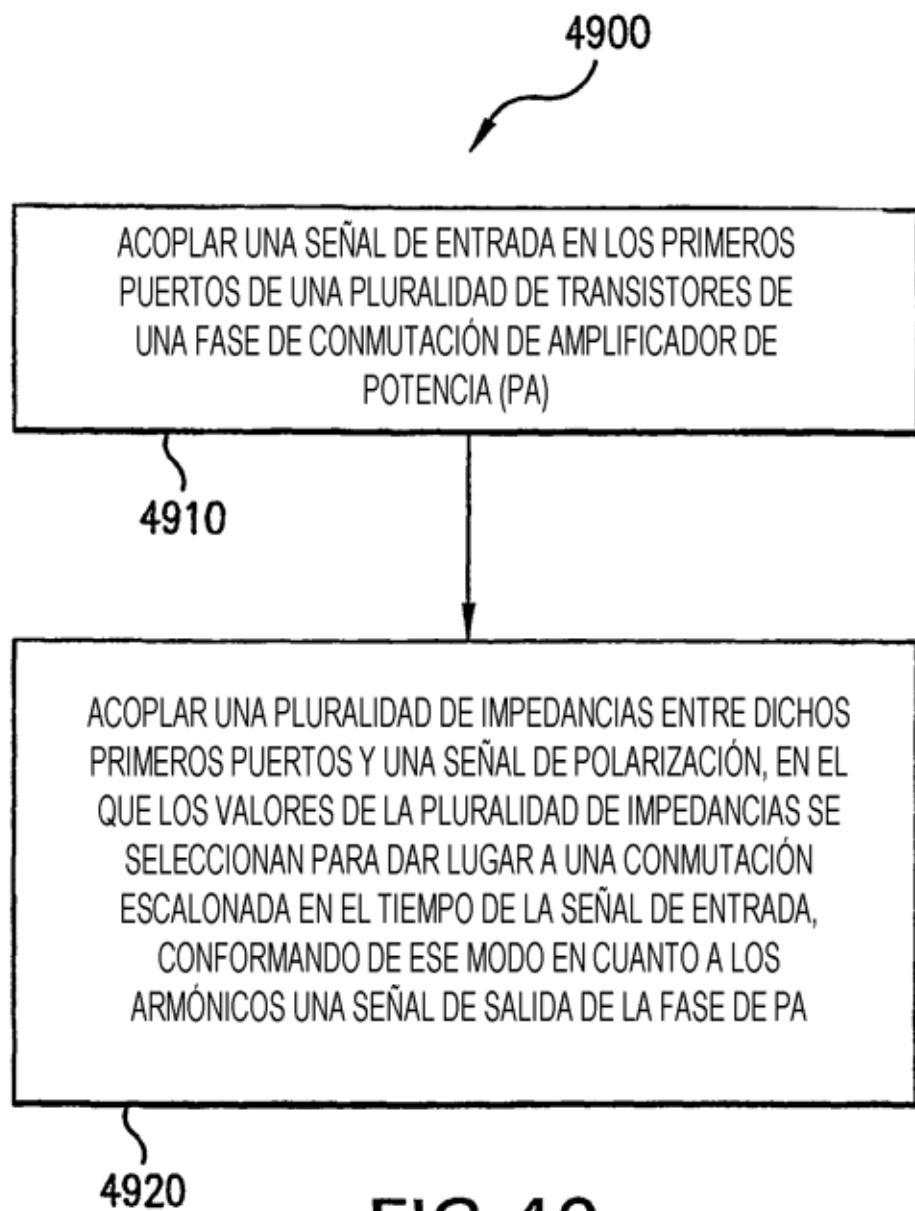

- La figura 49 es un diagrama de flujo de proceso ejemplar para implementar un control de armónicos.

- La figura 50 es un diagrama de flujo de proceso ejemplar para la amplificación de potencia.

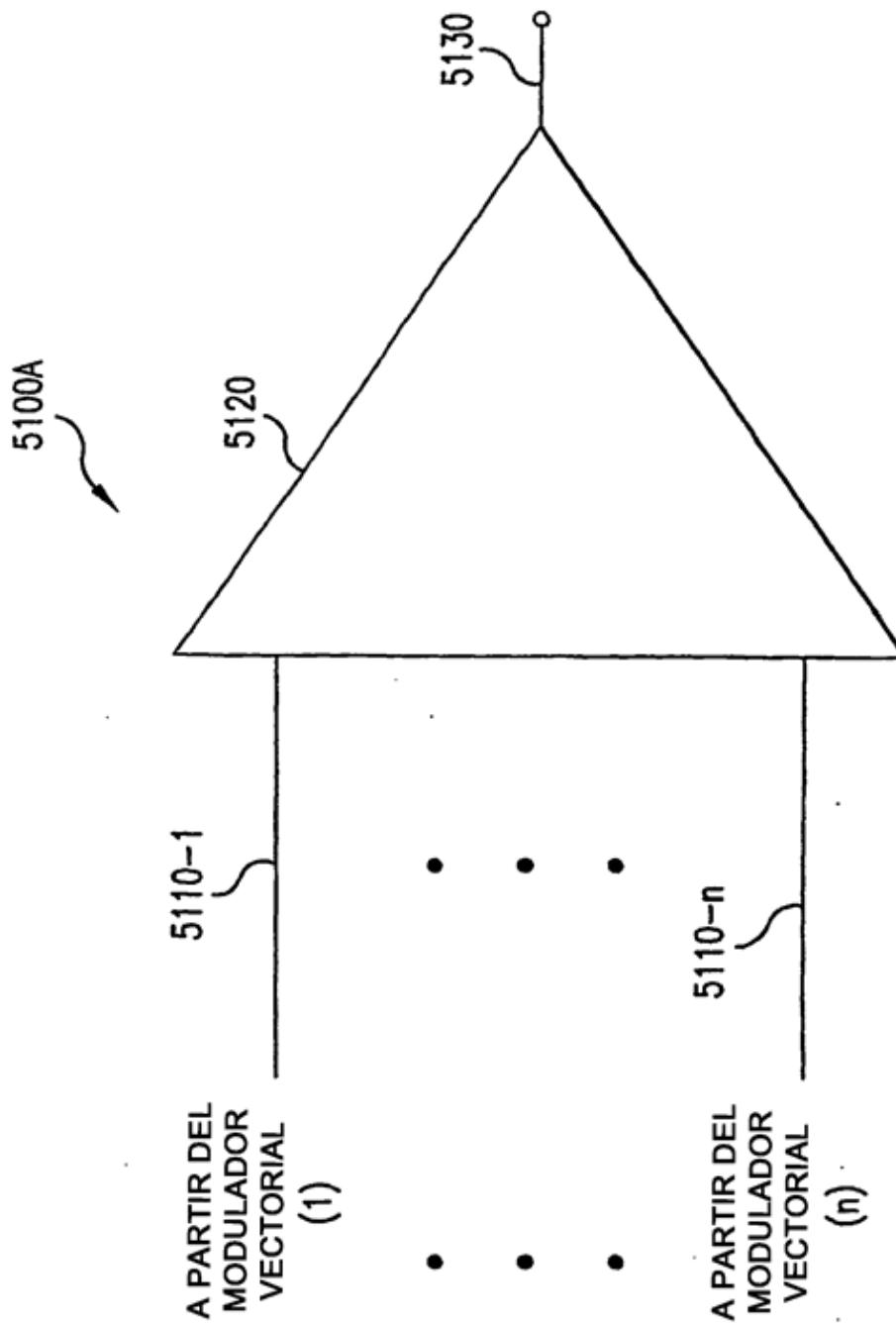

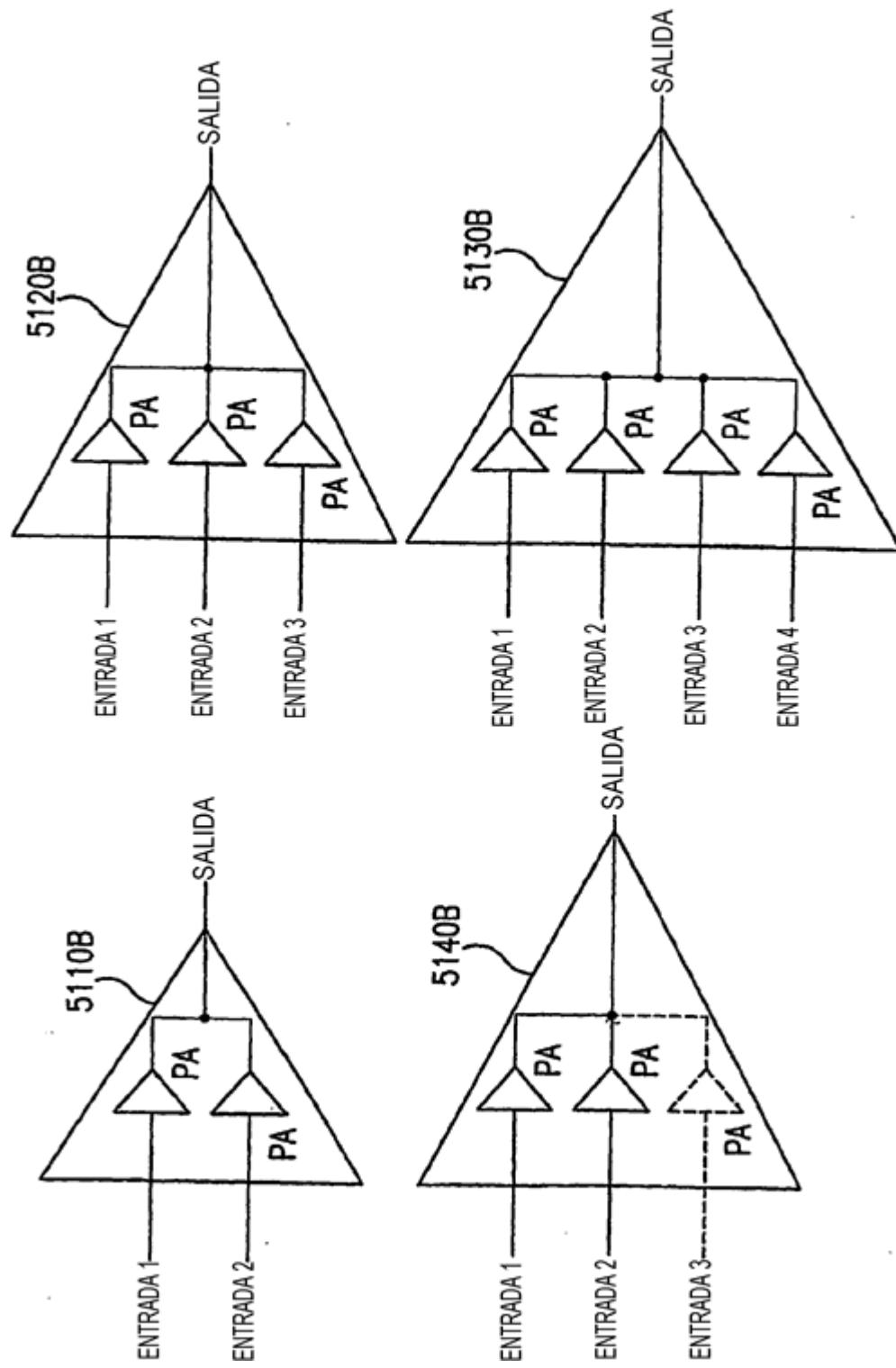

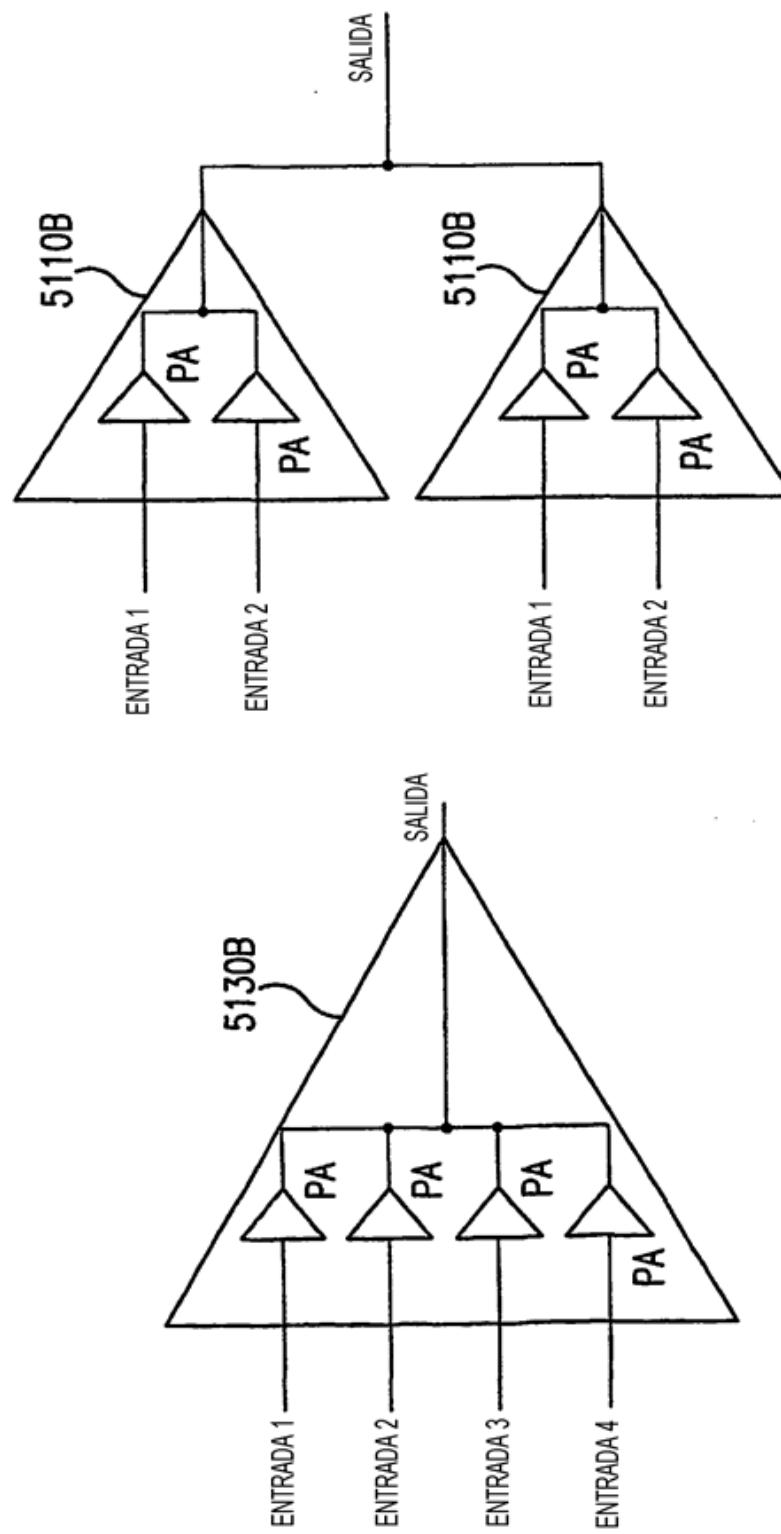

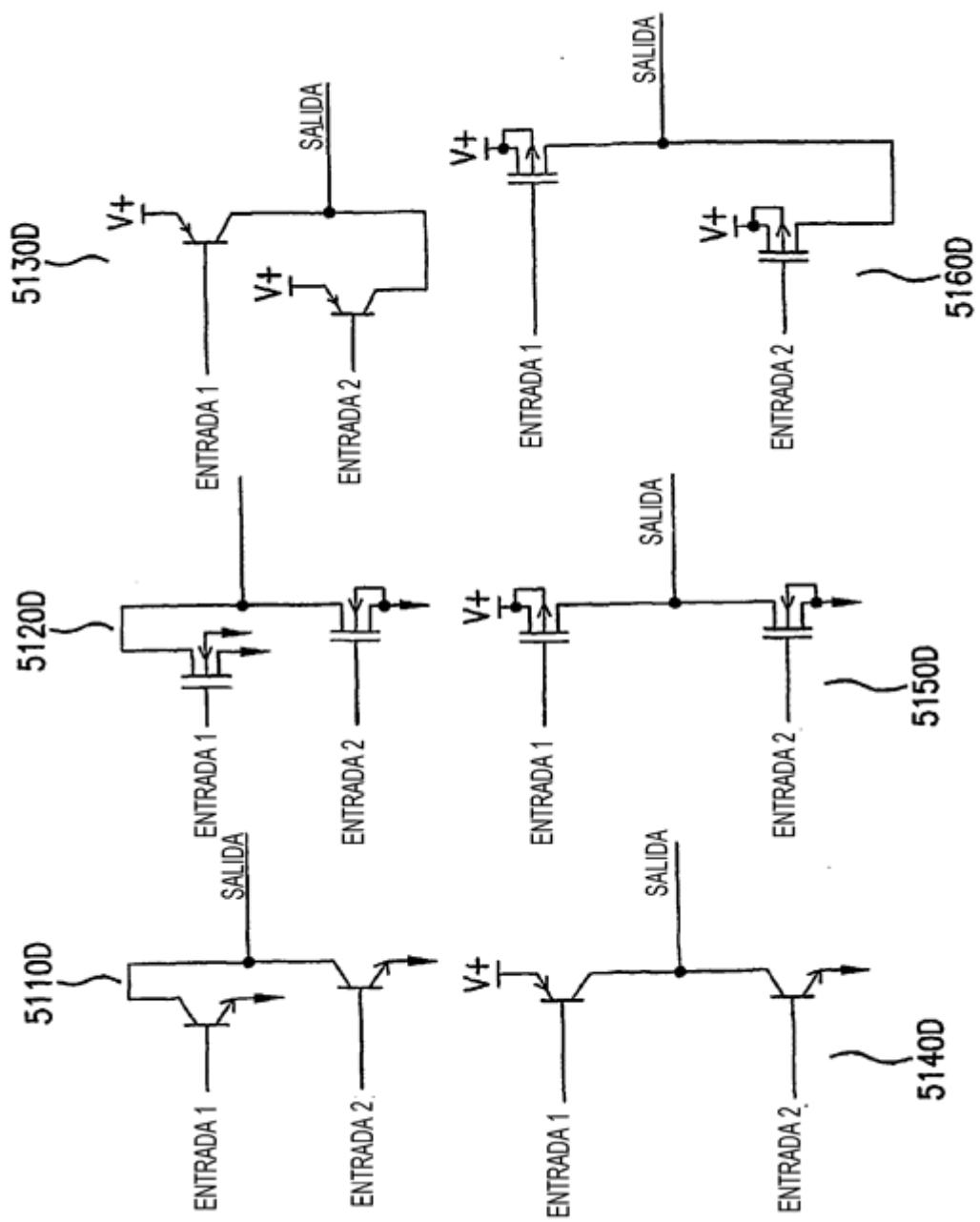

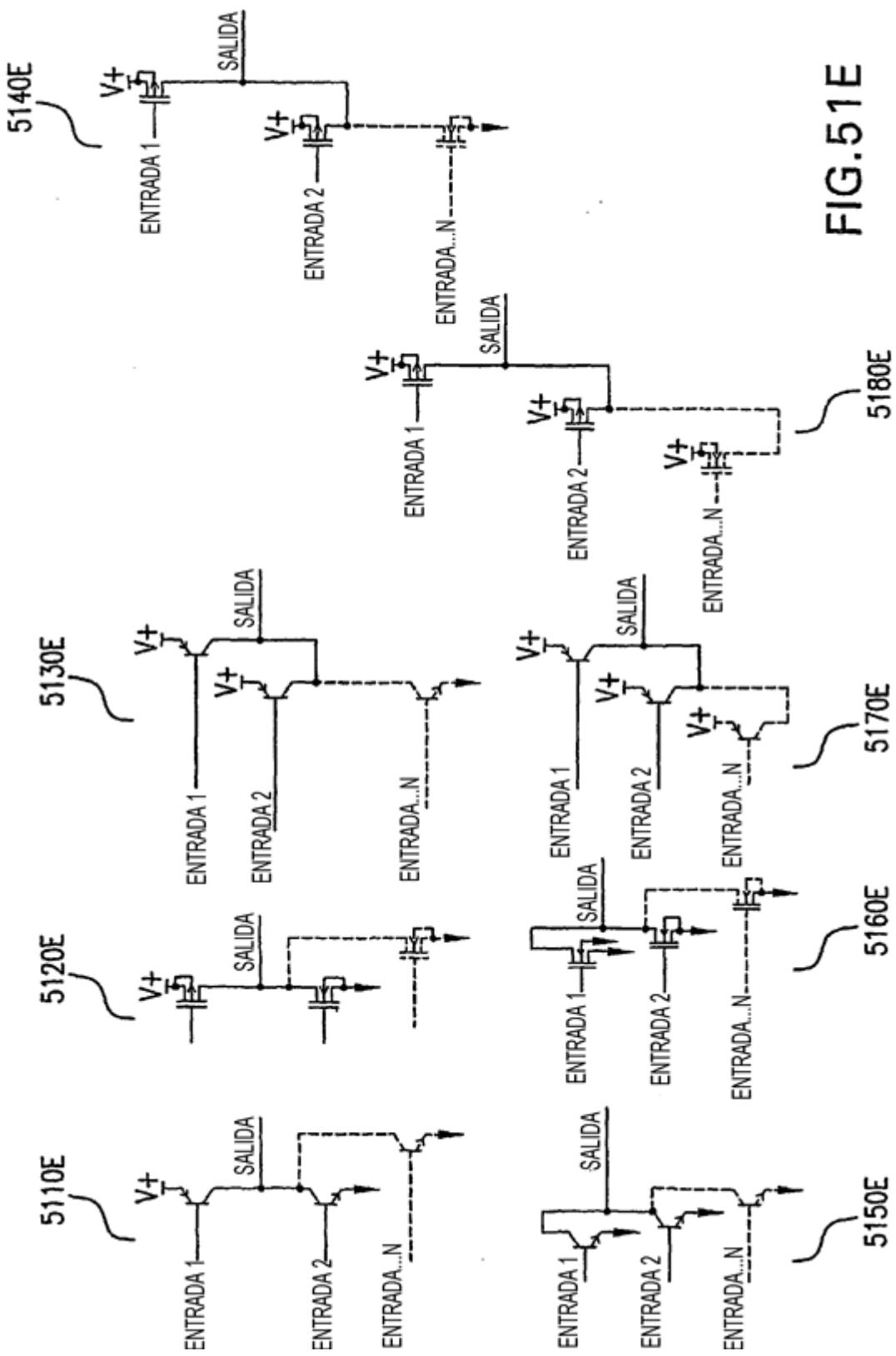

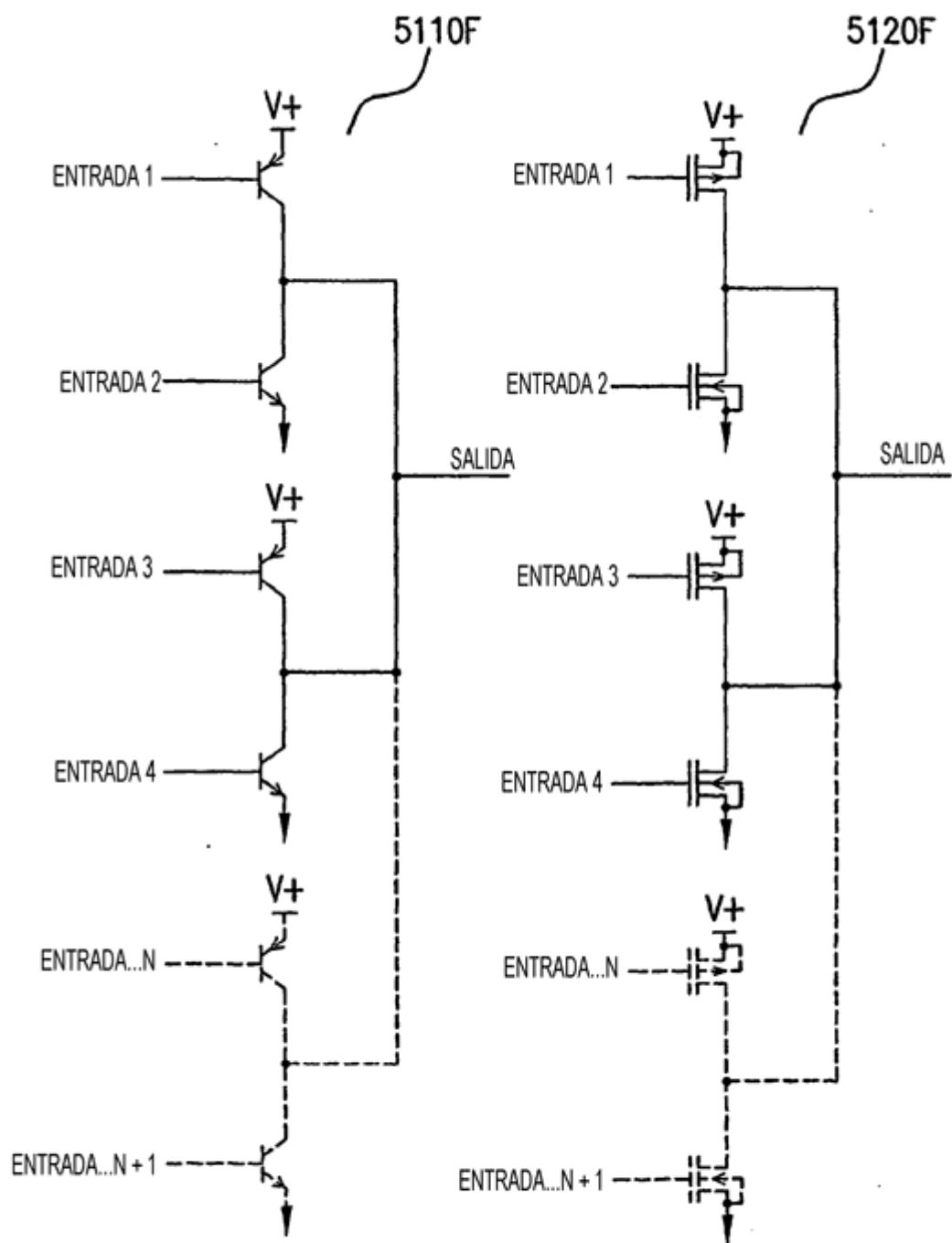

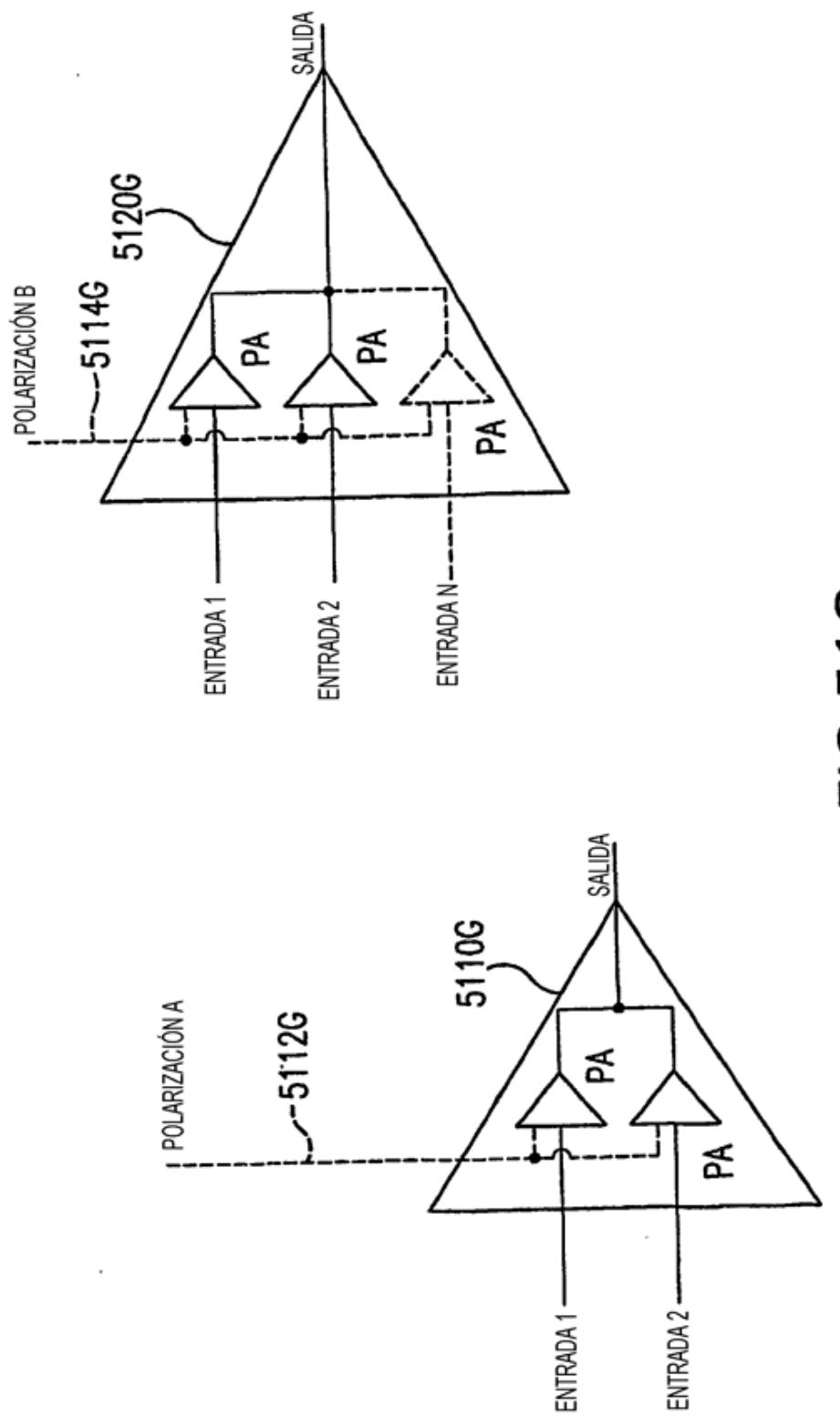

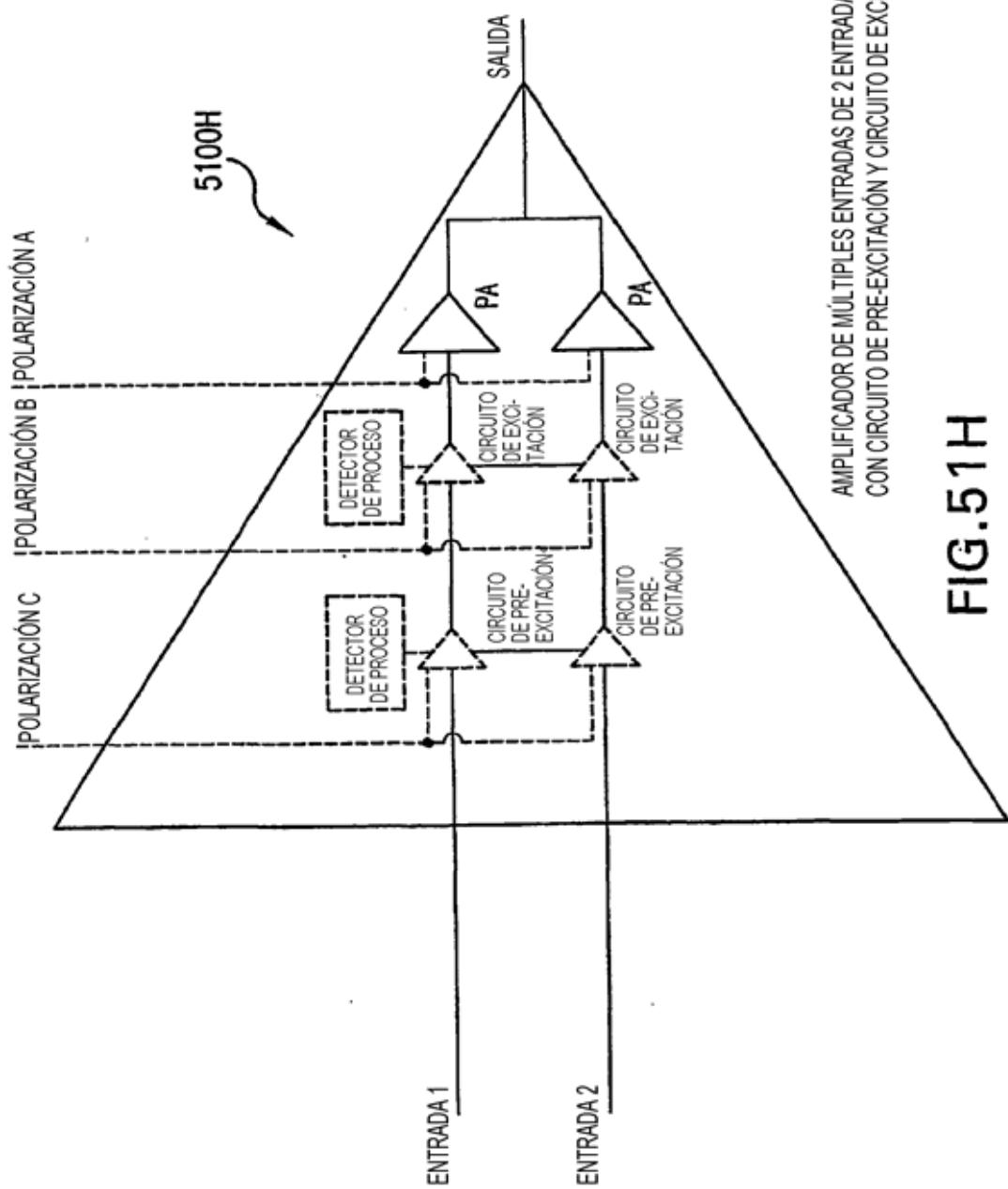

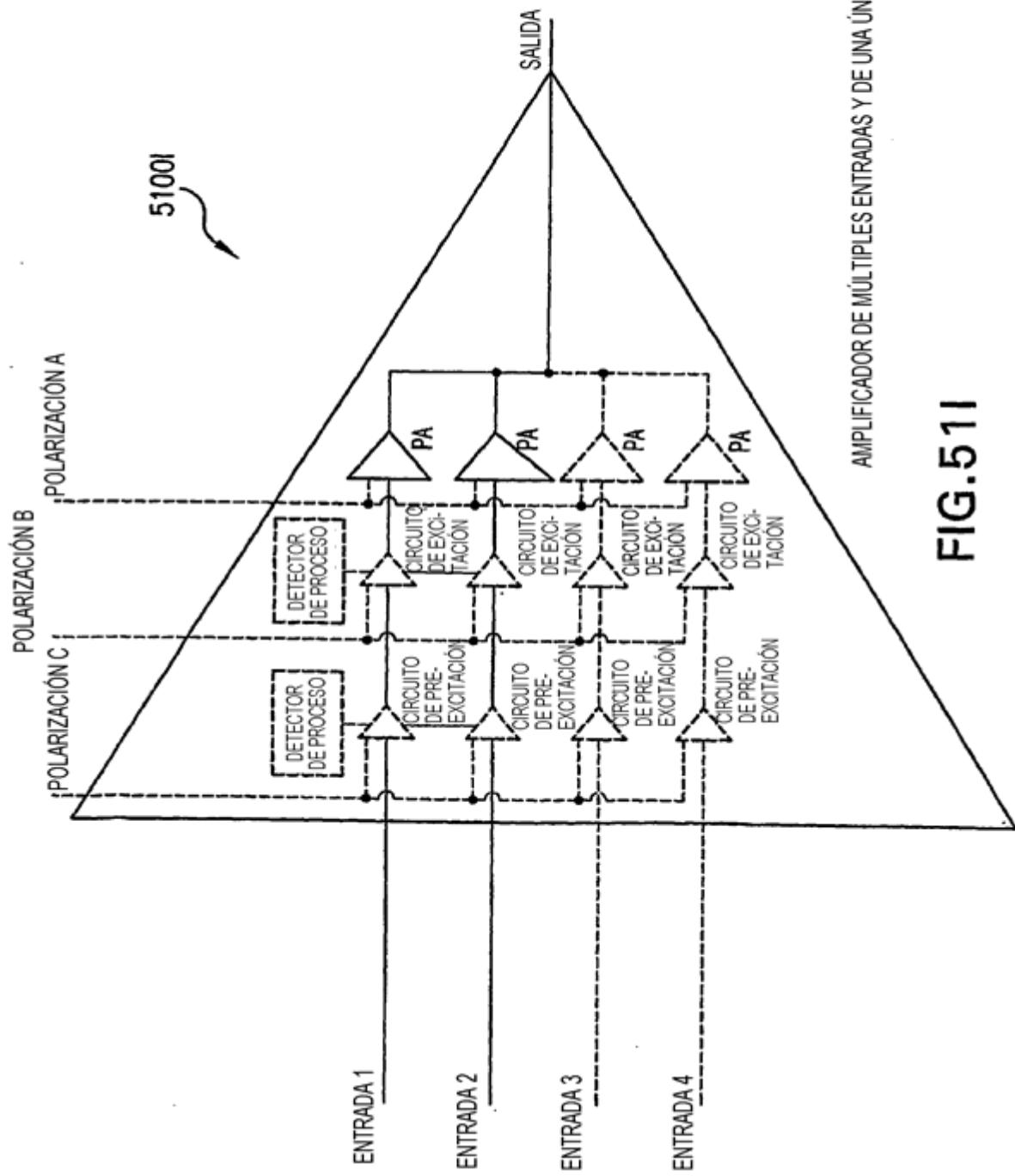

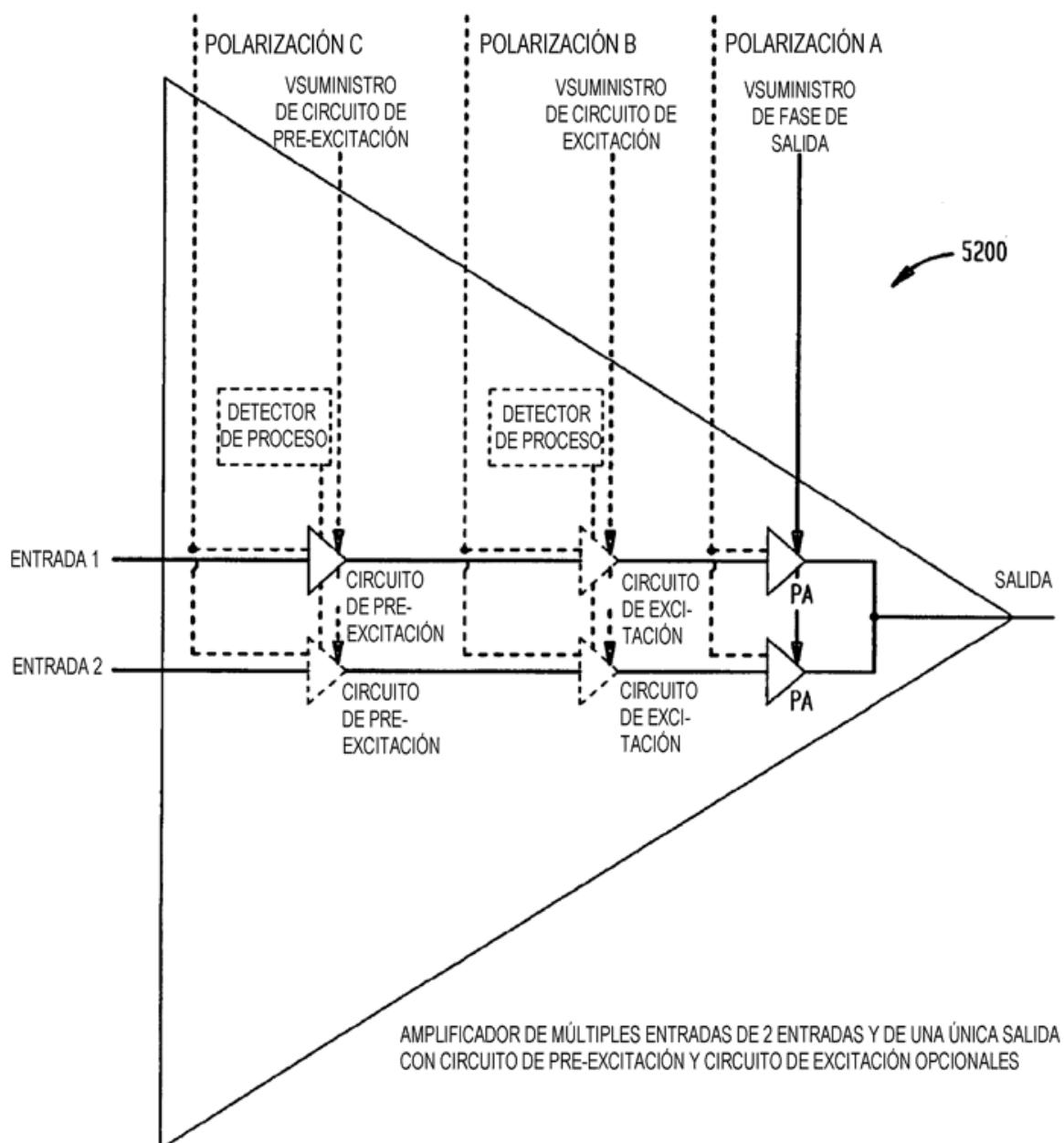

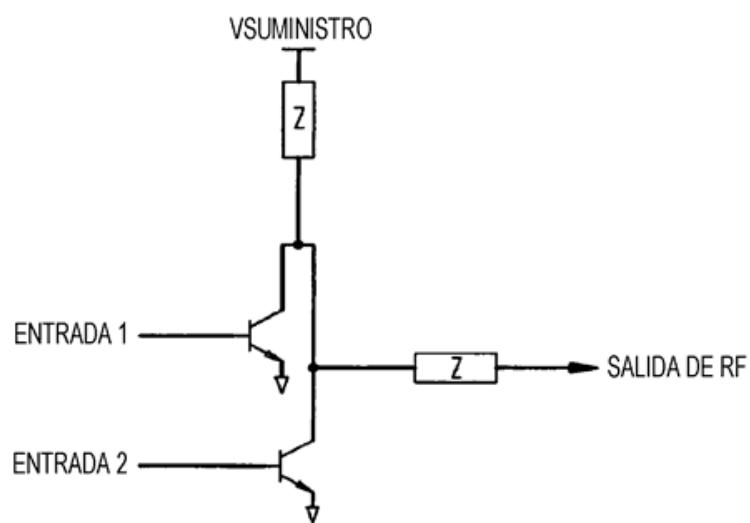

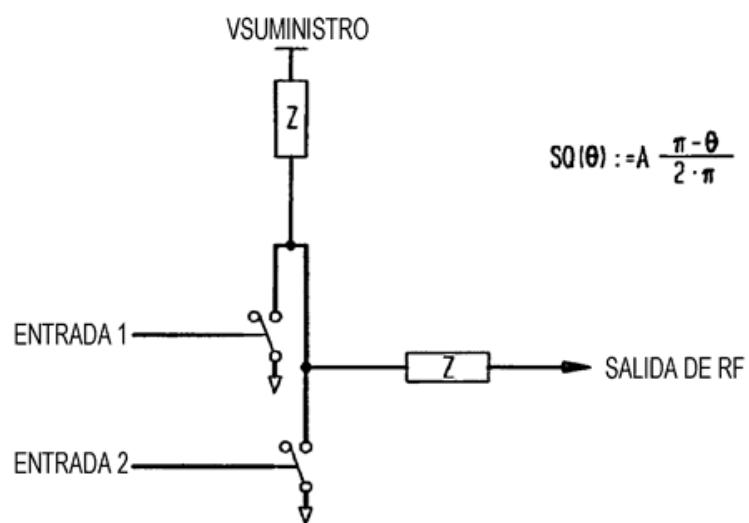

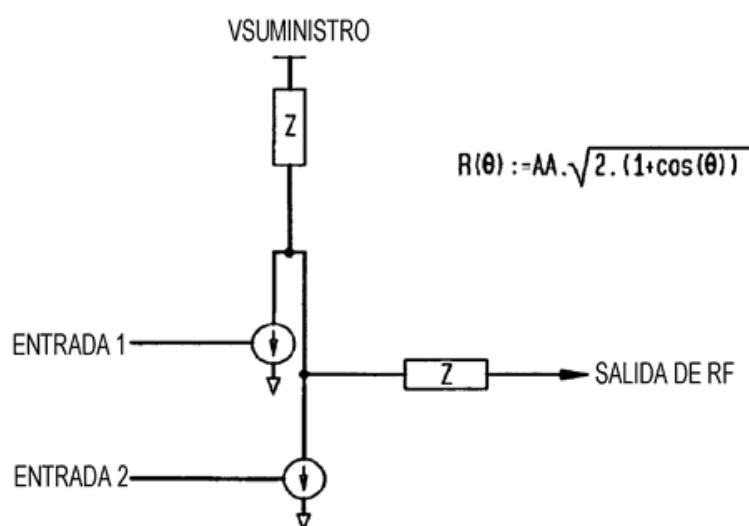

- 15 Las figuras 51A - I ilustran unas realizaciones de fase de salida de múltiples entradas y de una única salida (MISO).

- La figura 52 ilustra una realización de amplificador de MISO.

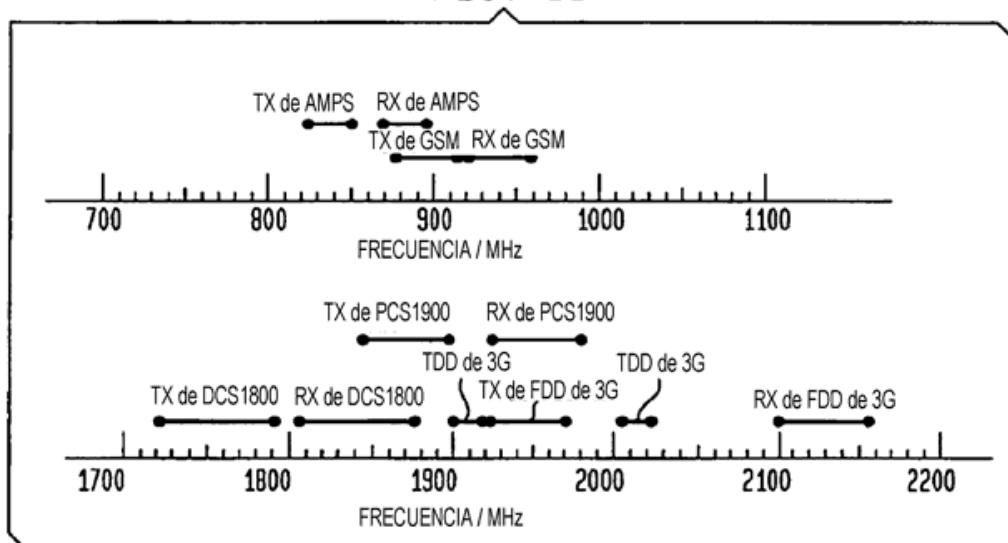

- La figura 53 ilustra una asignación de banda de frecuencia ejemplar en bandas de espectro inferior y superior para diversas normas de comunicación.

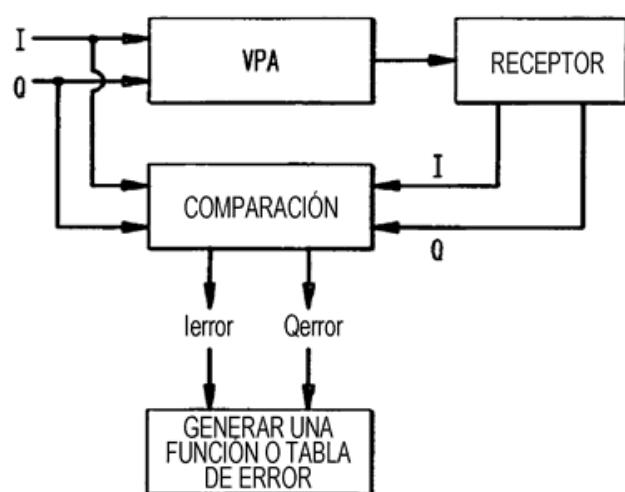

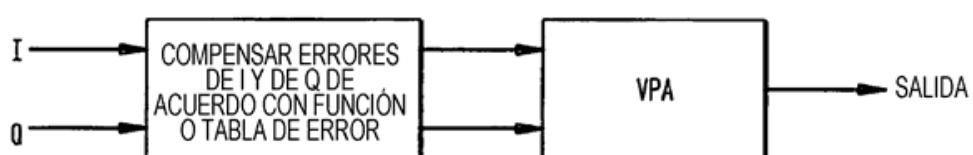

- 20 Las figuras 54A - B ilustran unas técnicas de alimentación en avance ejemplares para compensar los errores.

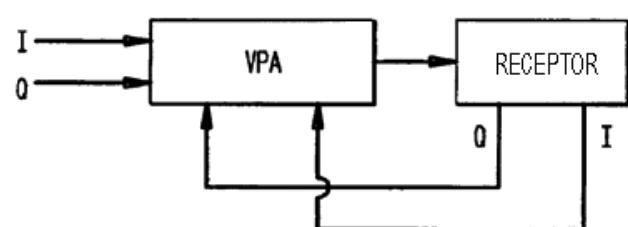

- La figura 55 ilustra una técnica de corrección de errores de realimentación basada en receptor ejemplar.

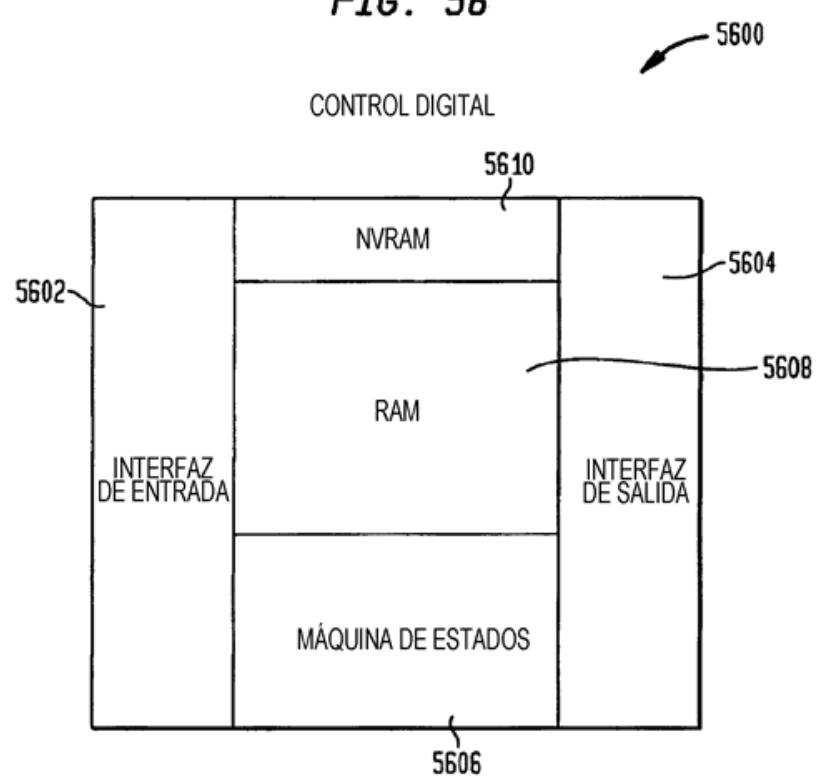

- La figura 56 ilustra un módulo de control digital ejemplar.

- La figura 57 ilustra otro módulo de control digital ejemplar.

- La figura 58 ilustra otra realización de módulo de control digital.

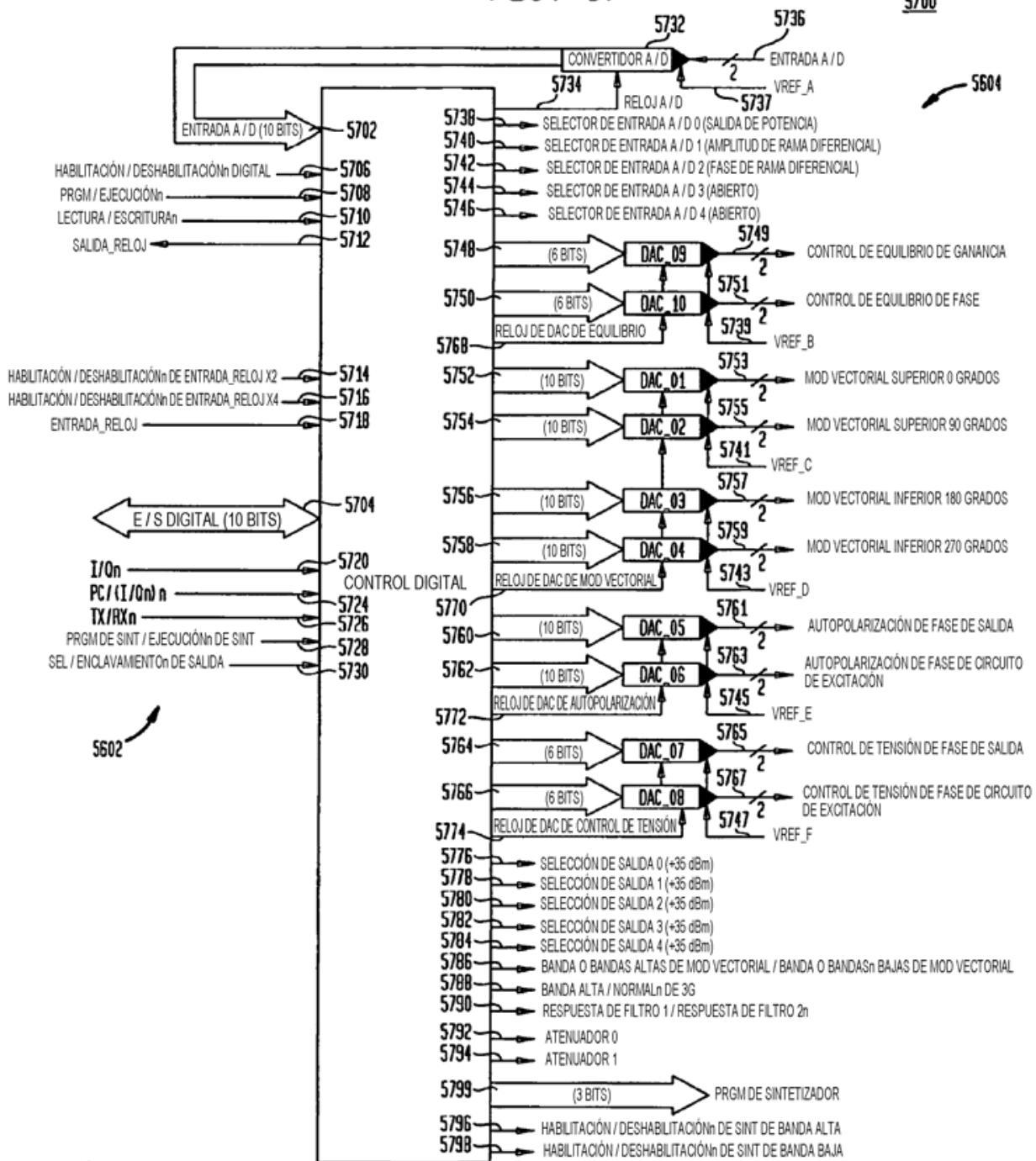

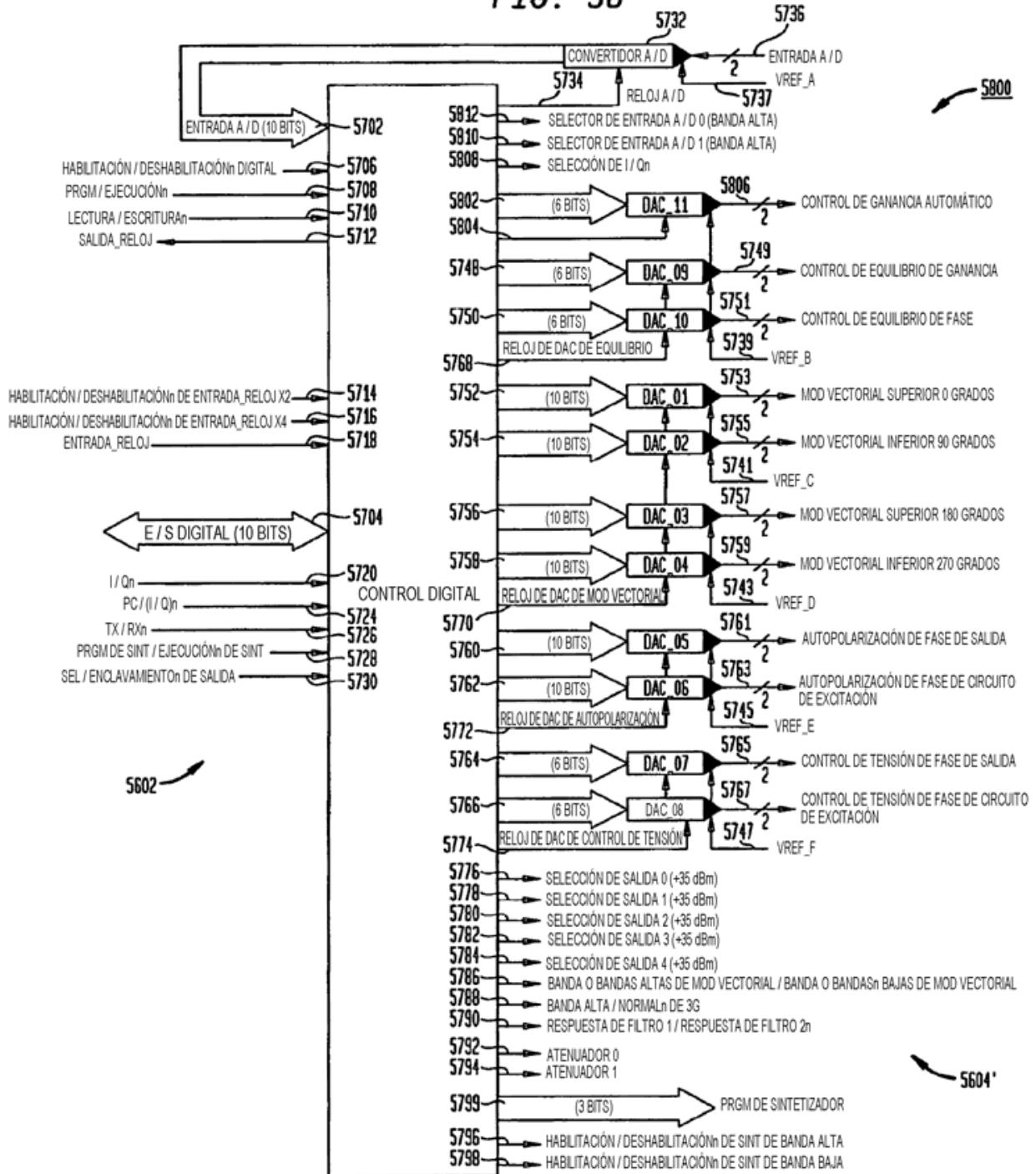

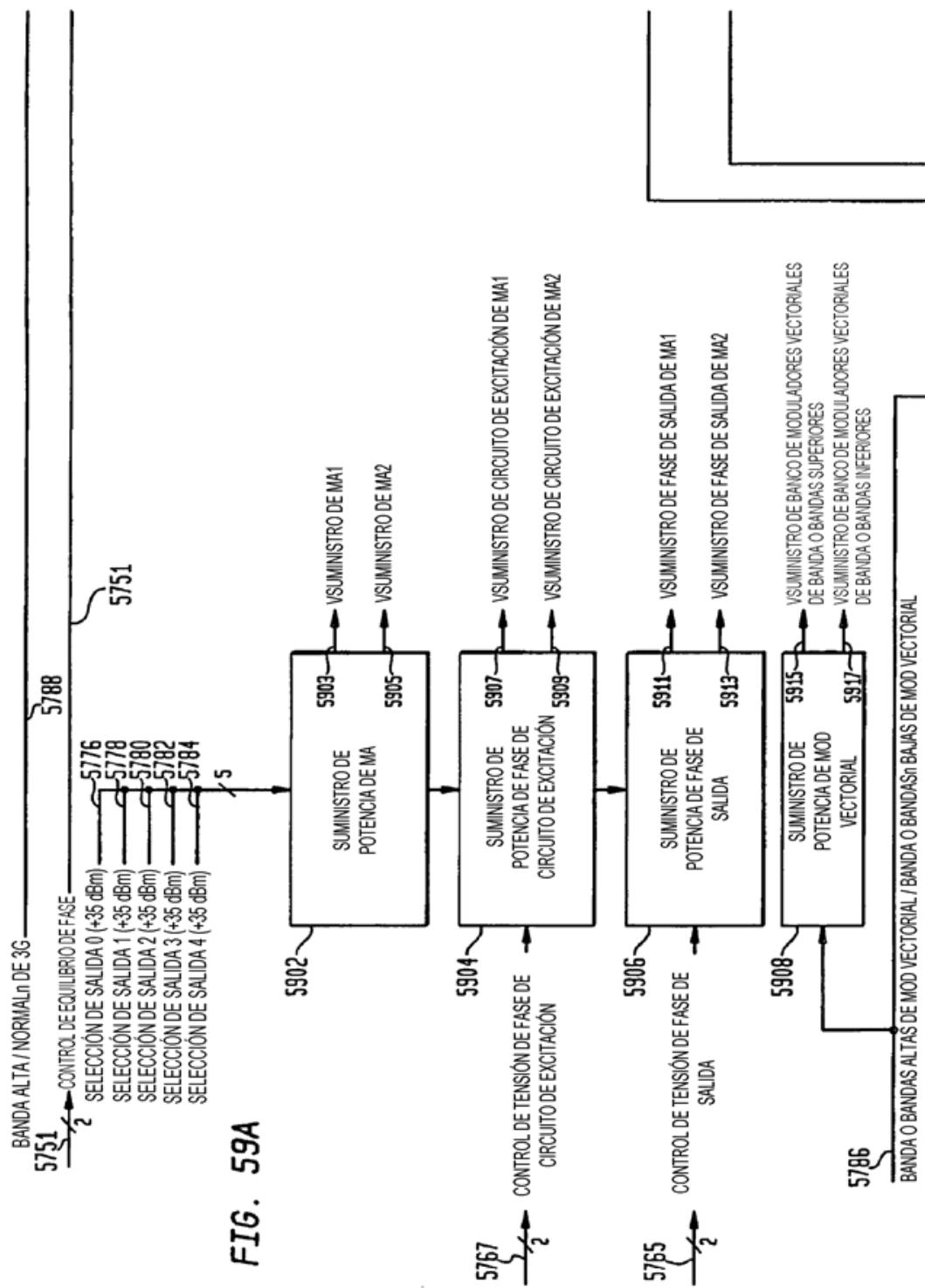

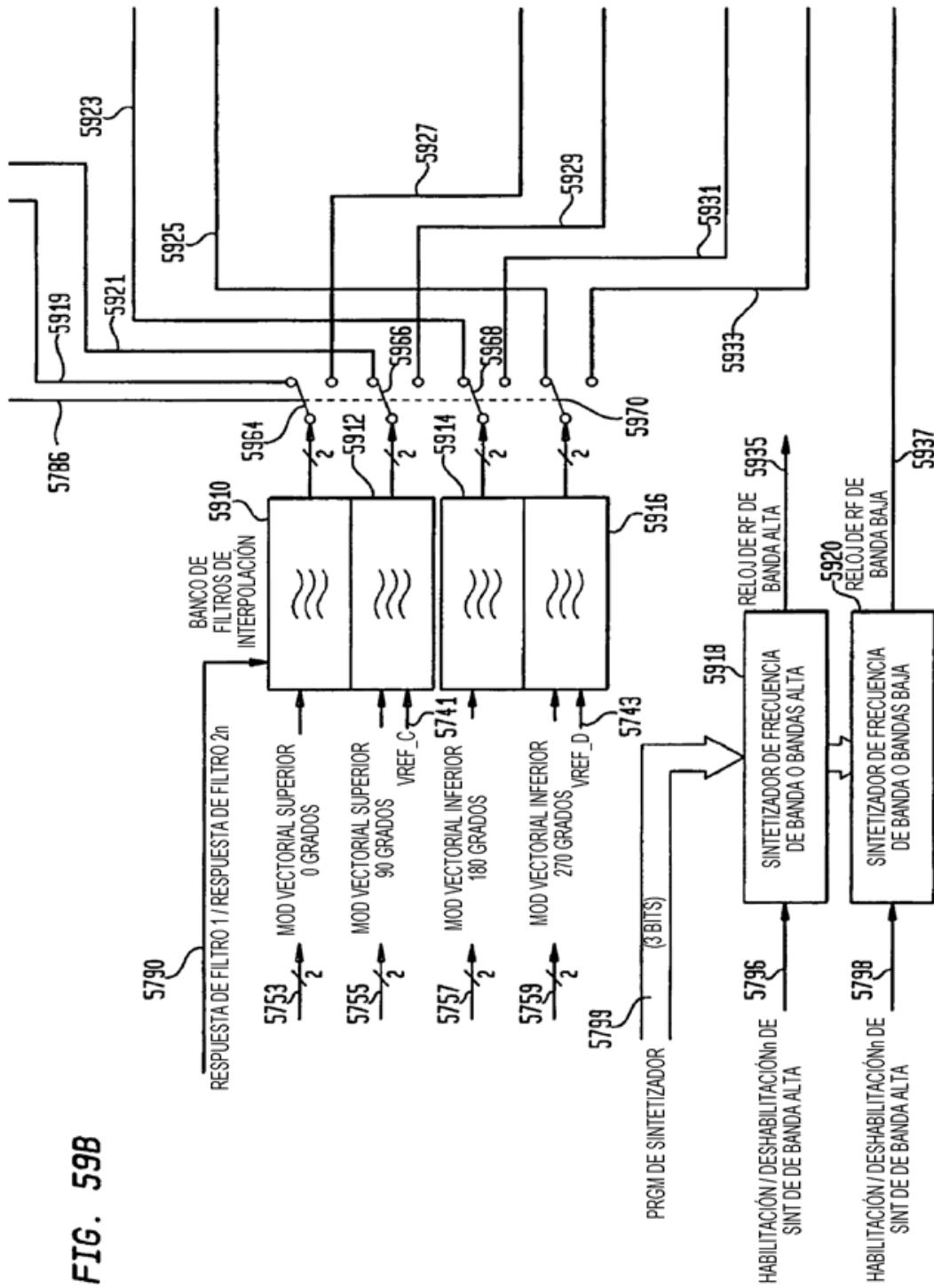

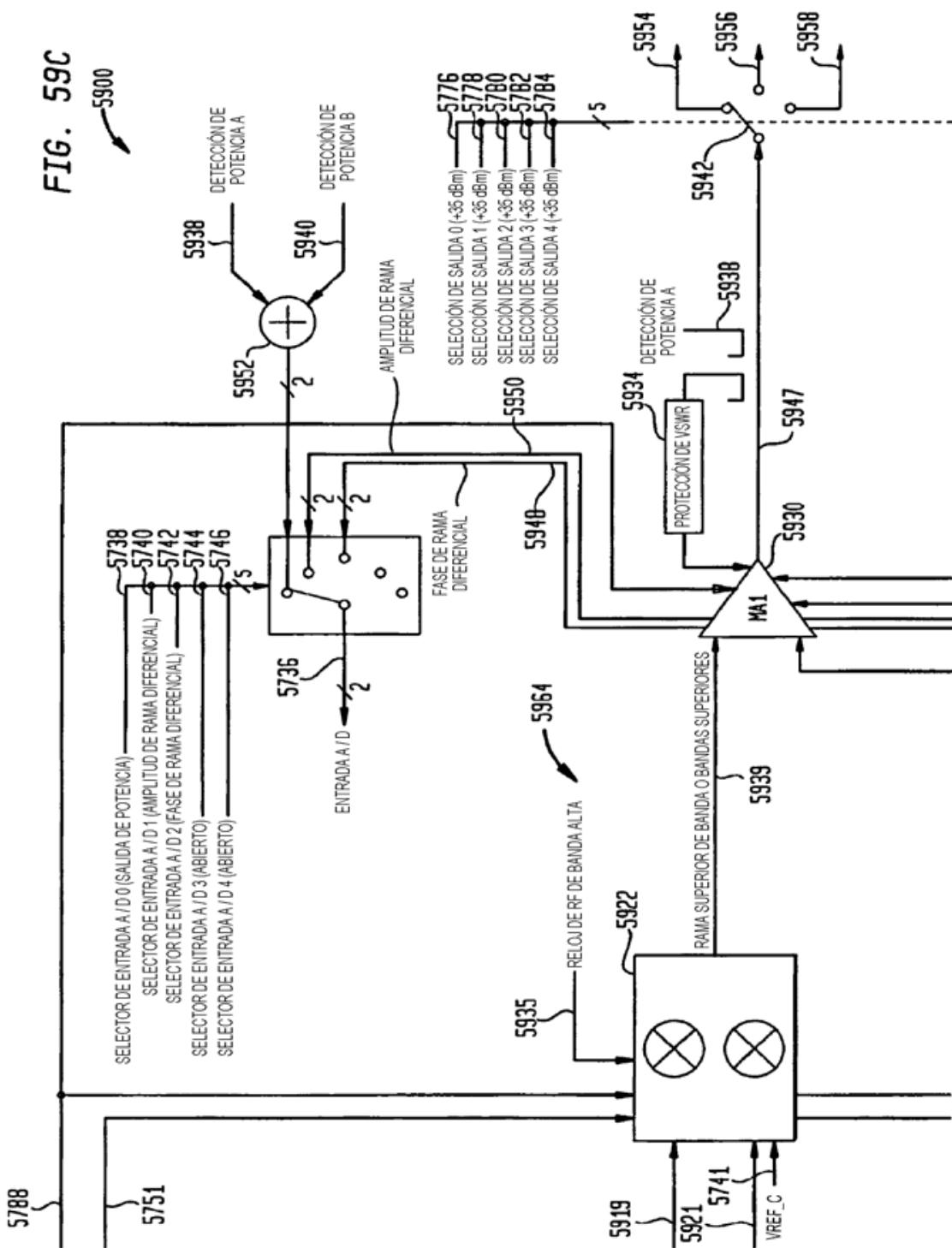

- 25 Las figuras 59A - D ilustran un núcleo analógico de VPA ejemplar.

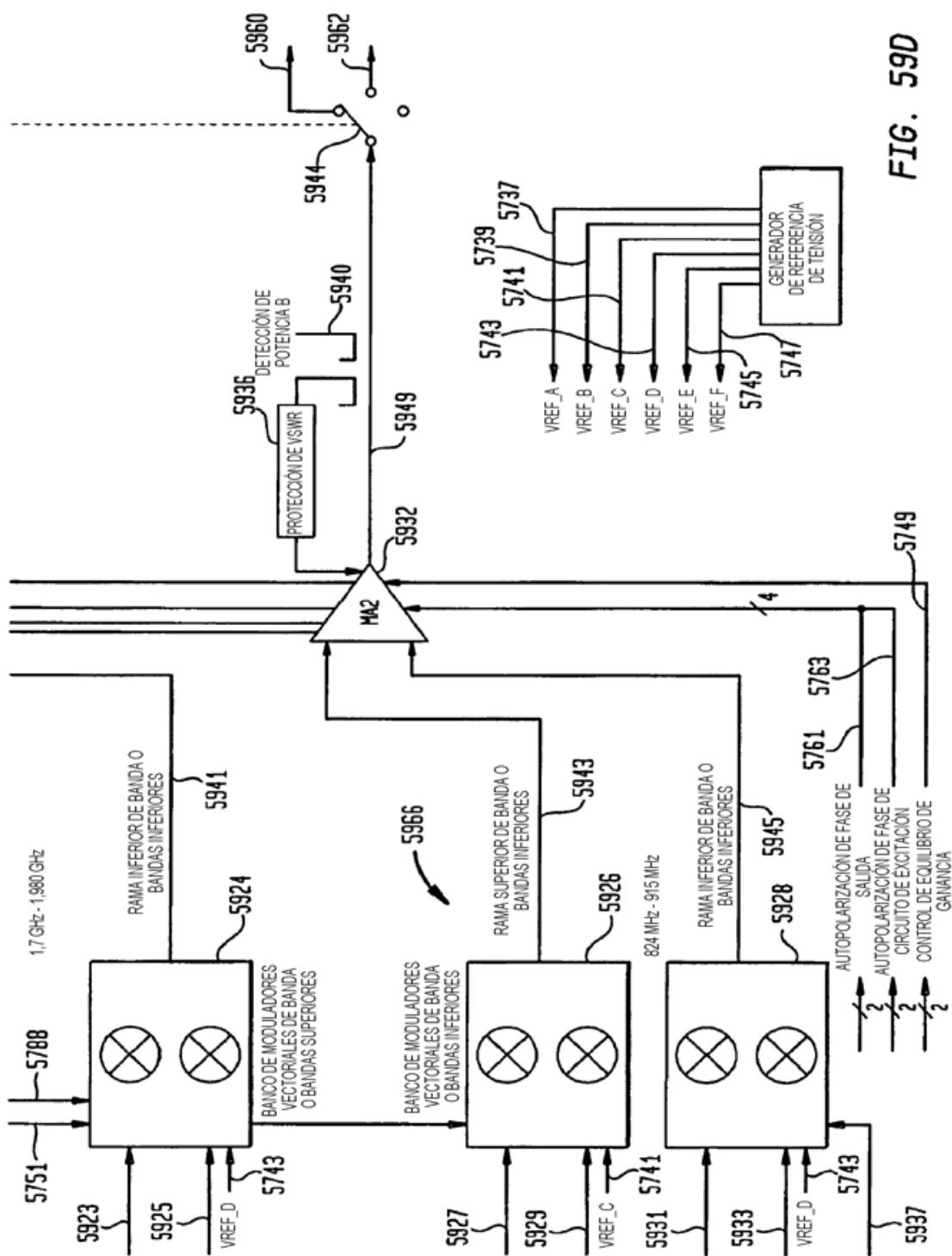

- La figura 60 ilustra una fase de salida ejemplar de acuerdo con el núcleo analógico de VPA de las figuras 59A - D.

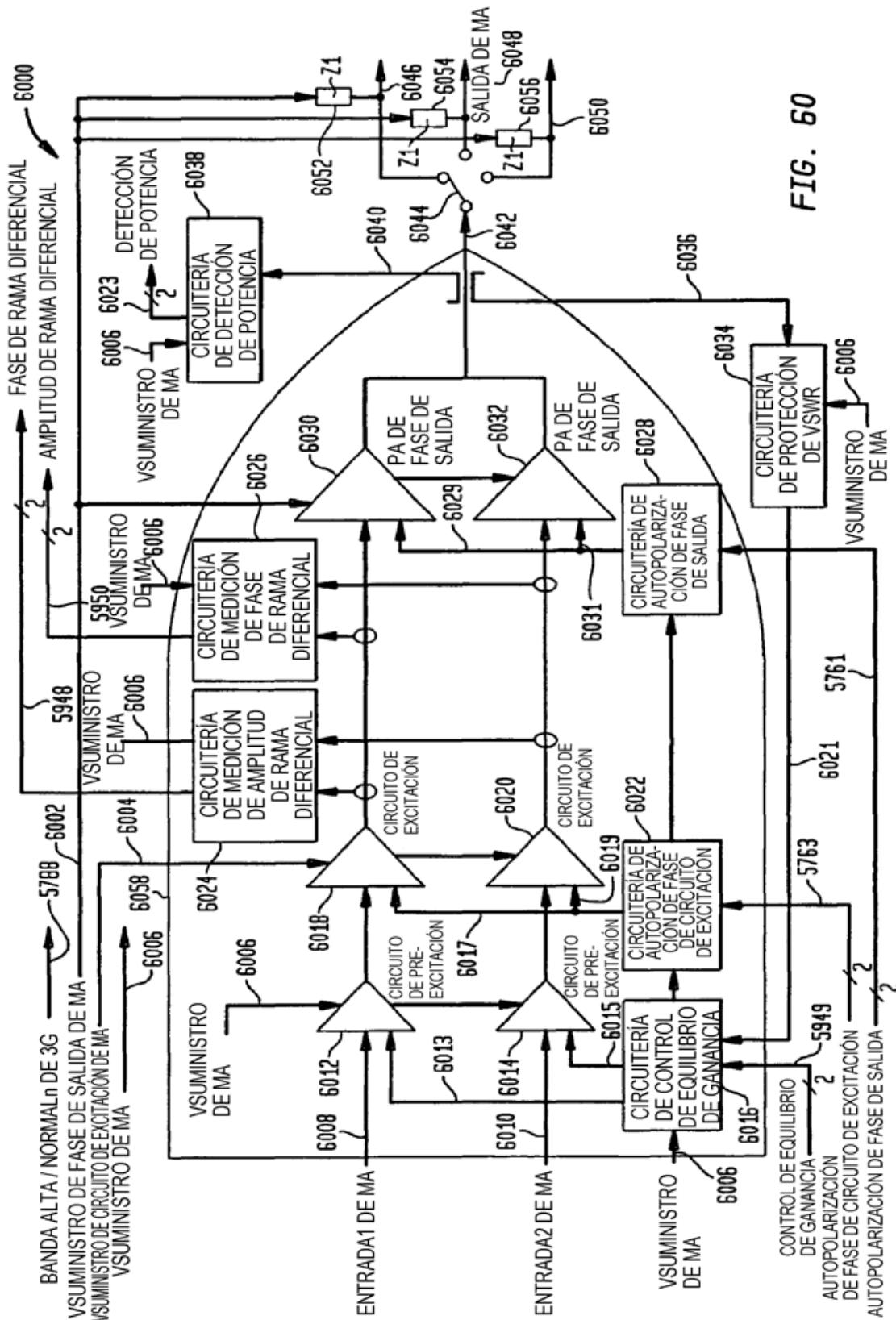

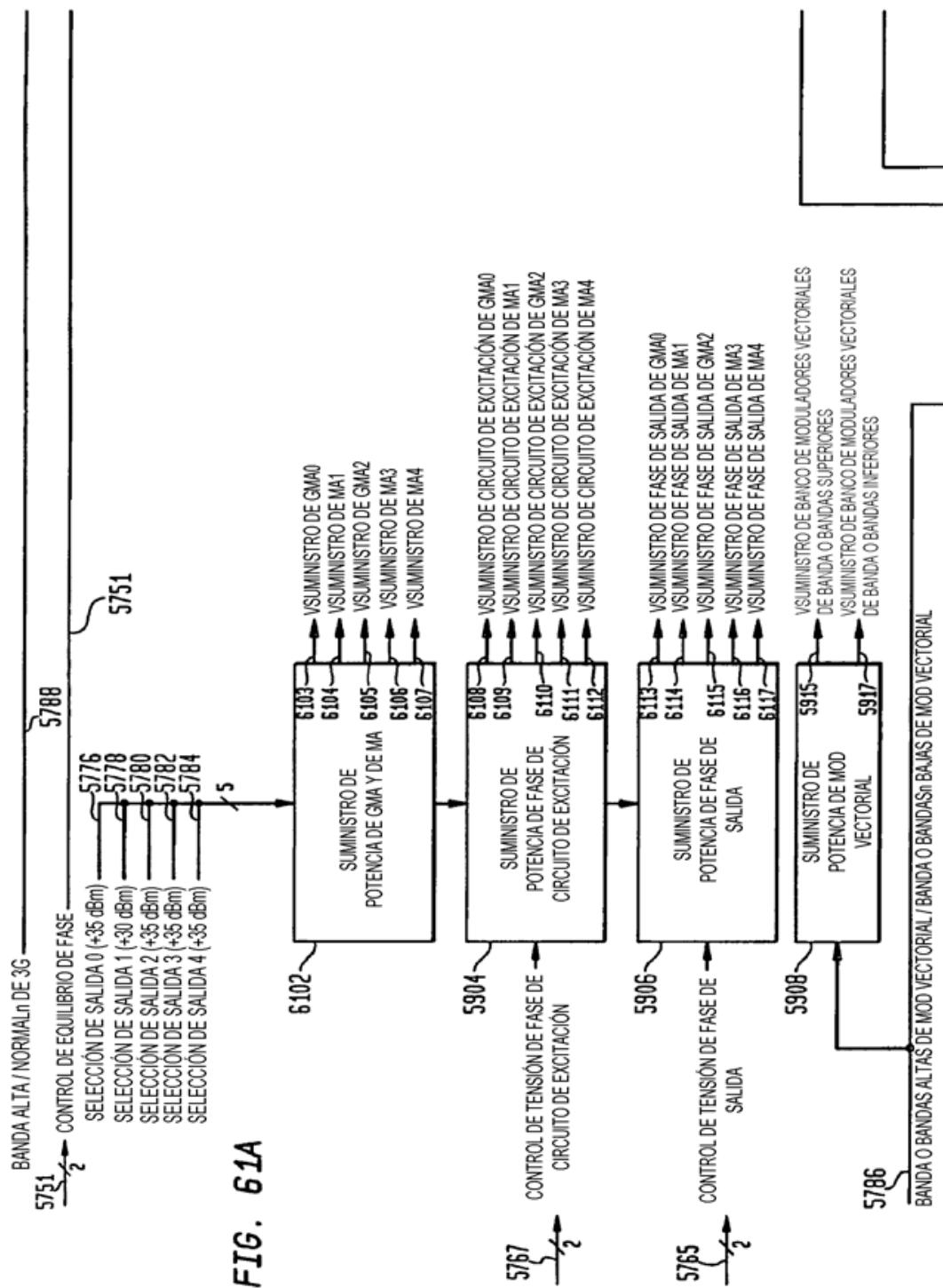

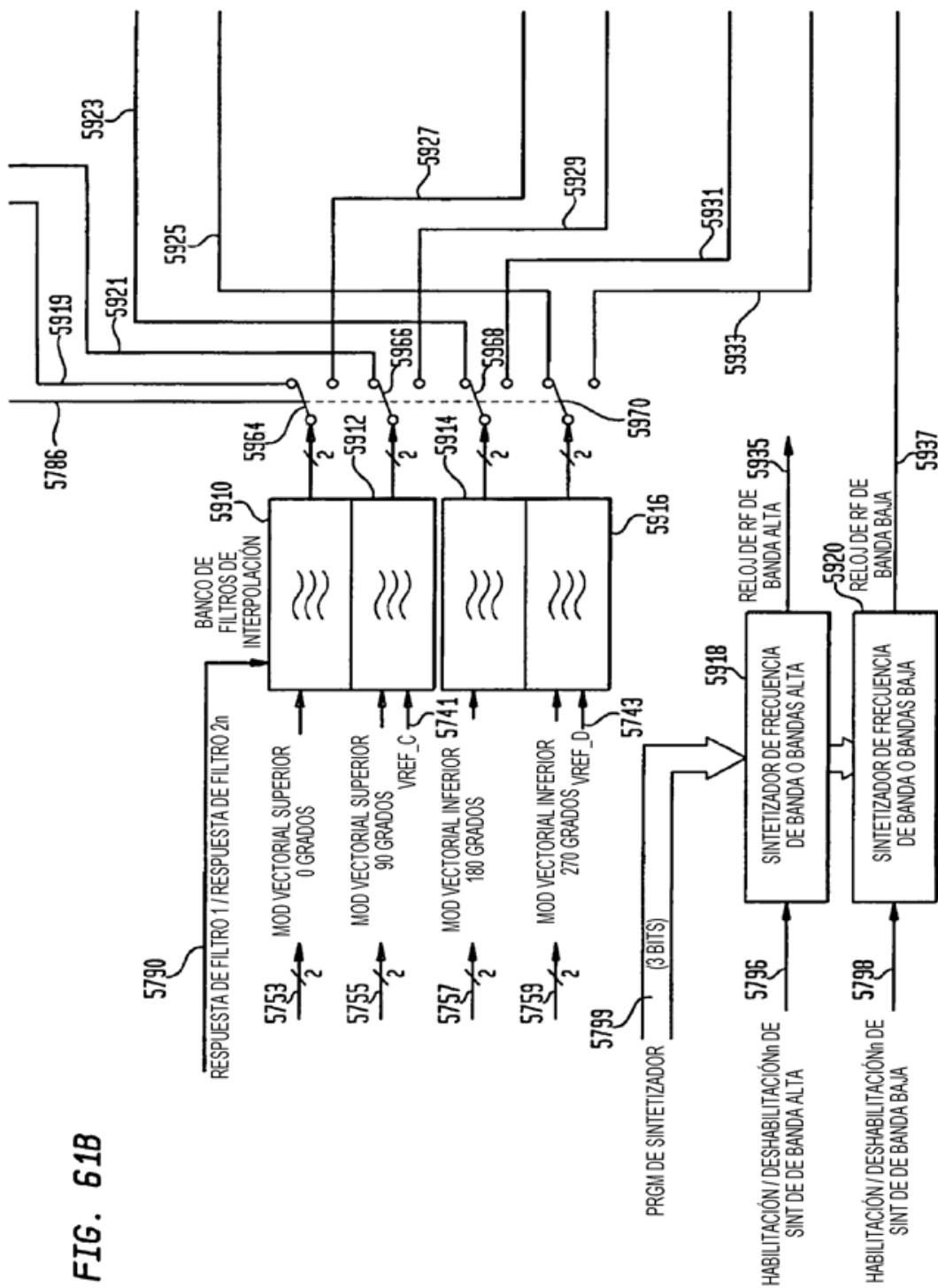

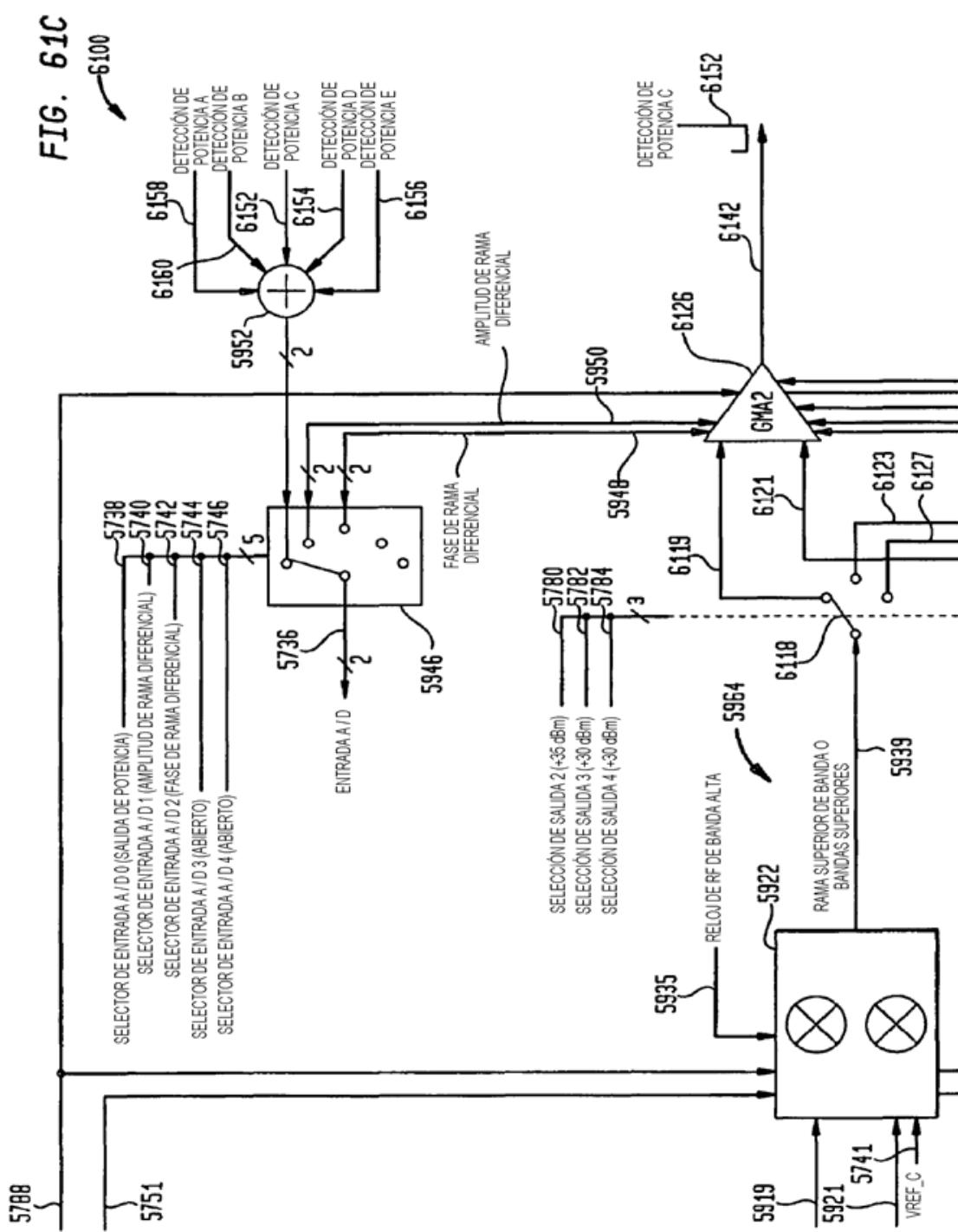

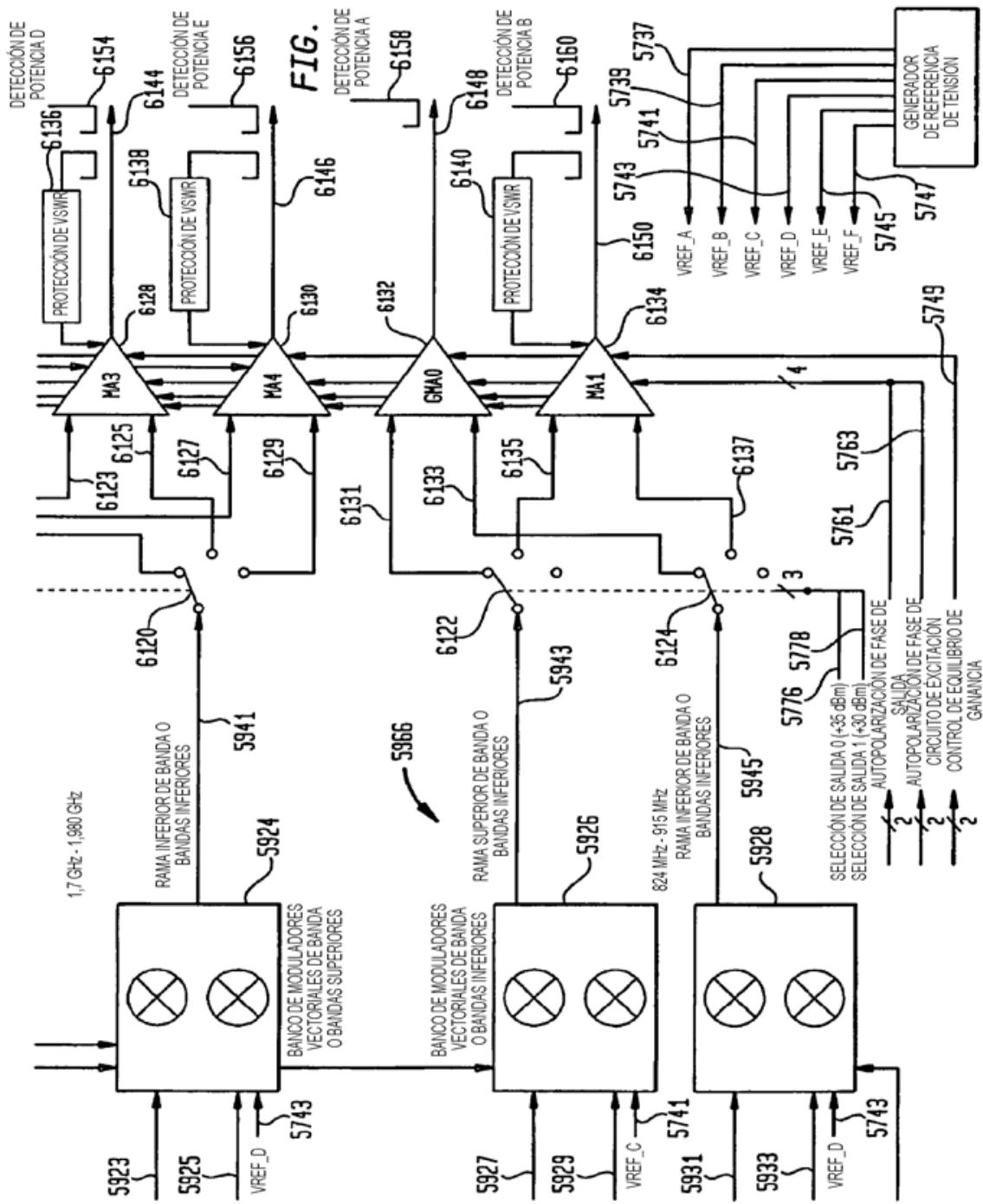

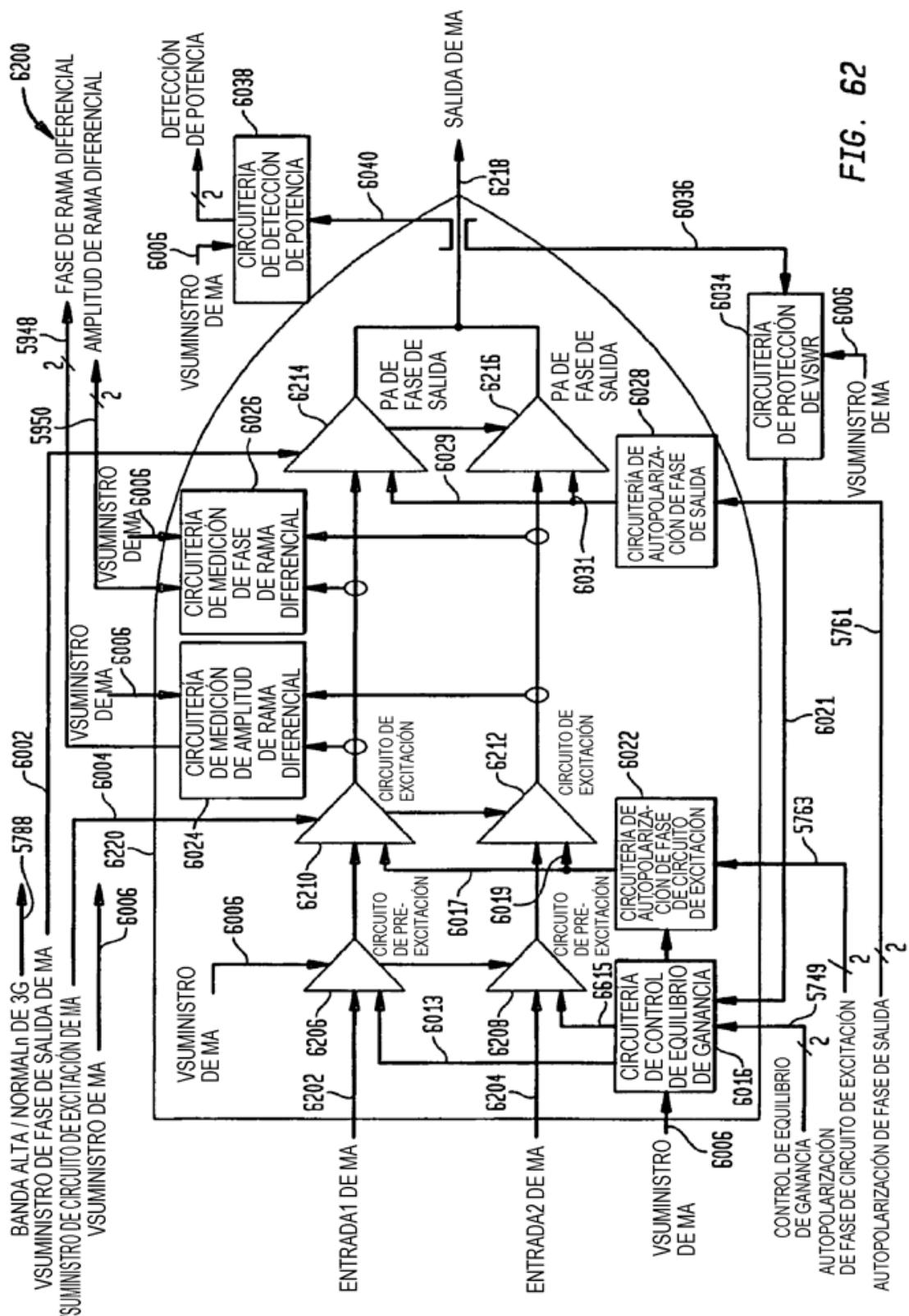

- Las figuras 61A - D ilustran otro núcleo analógico de VPA ejemplar.

- La figura 62 ilustra una fase de salida ejemplar de acuerdo con el núcleo analógico de VPA de las figuras 61A - D.

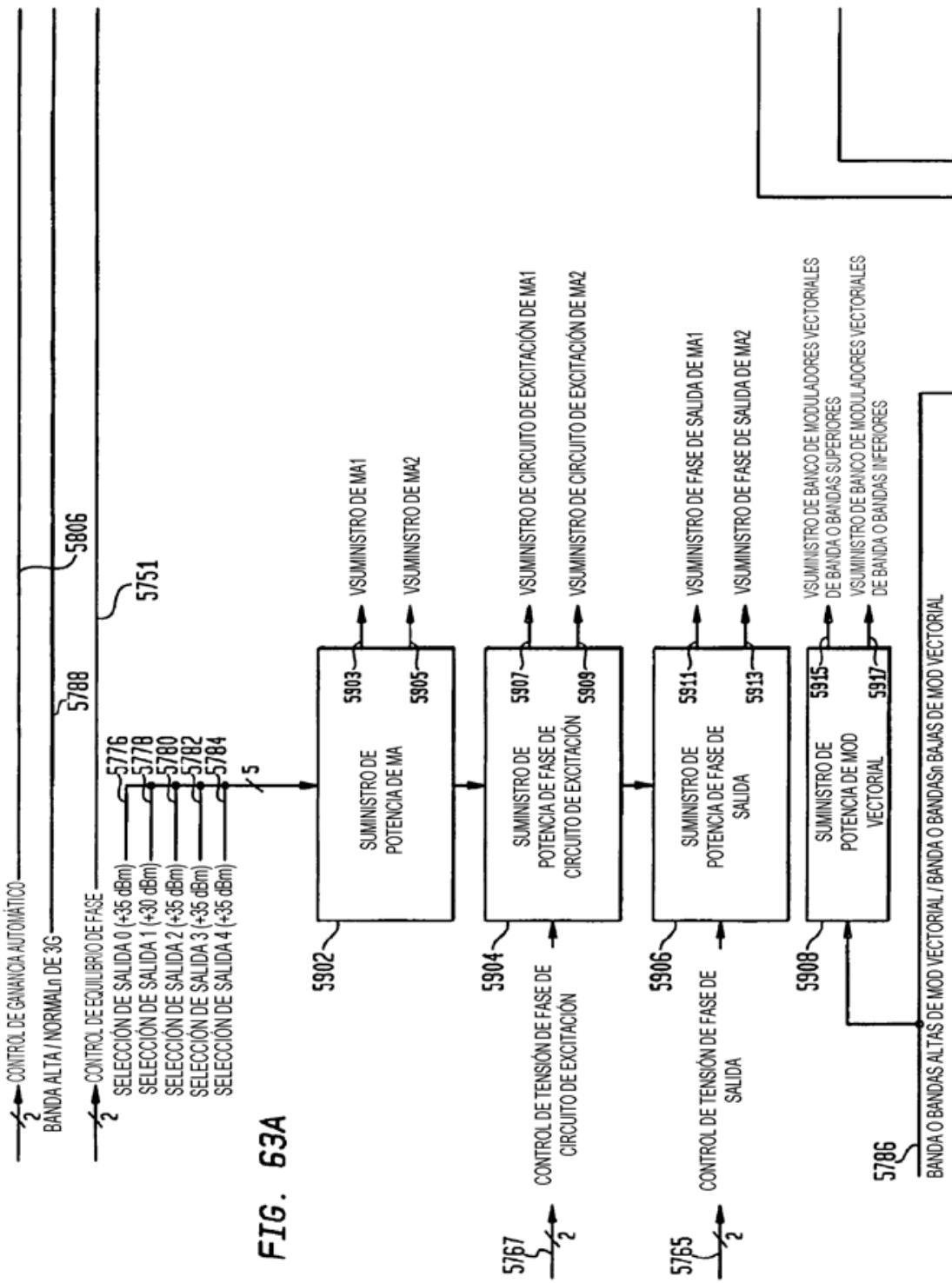

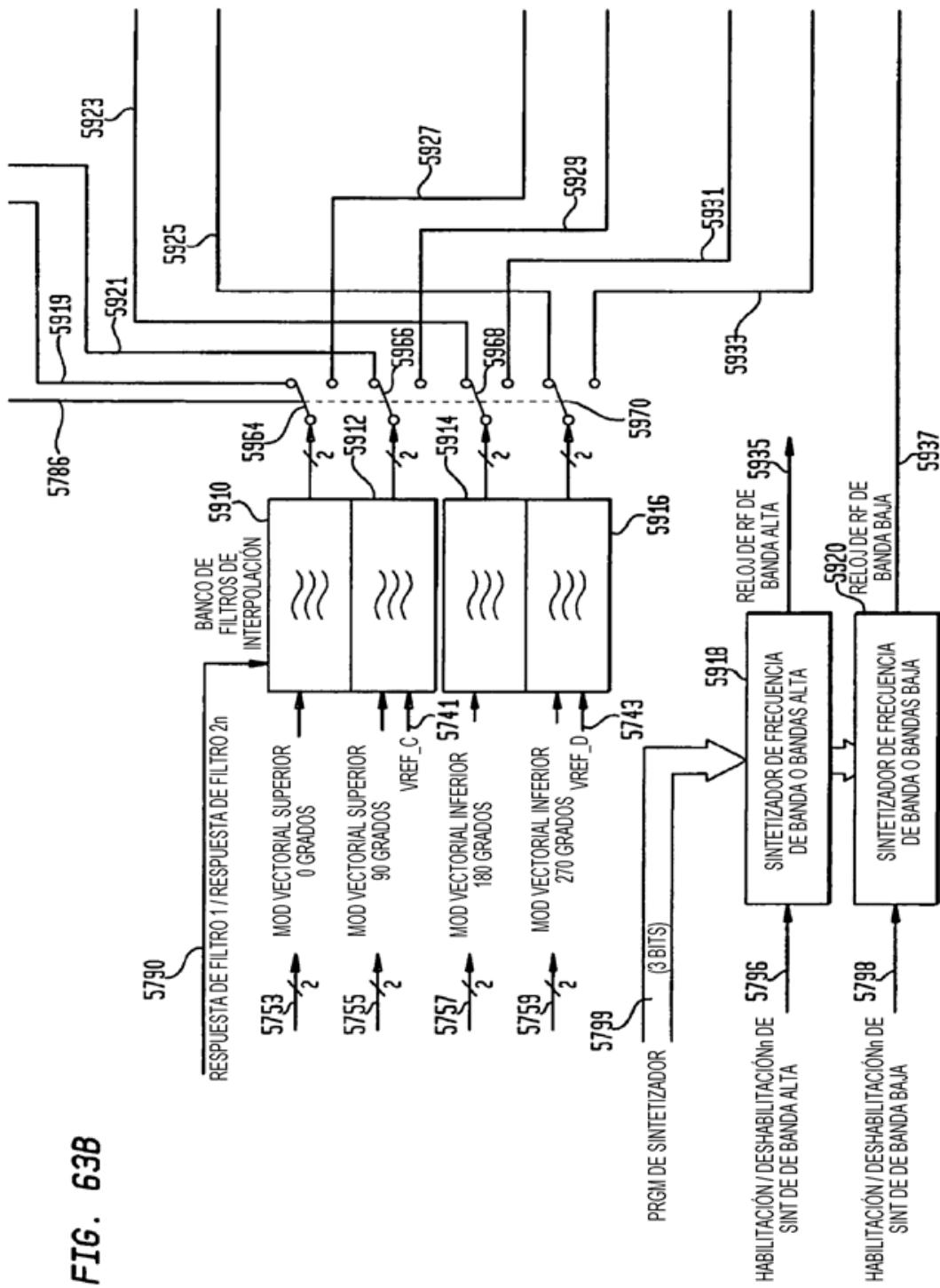

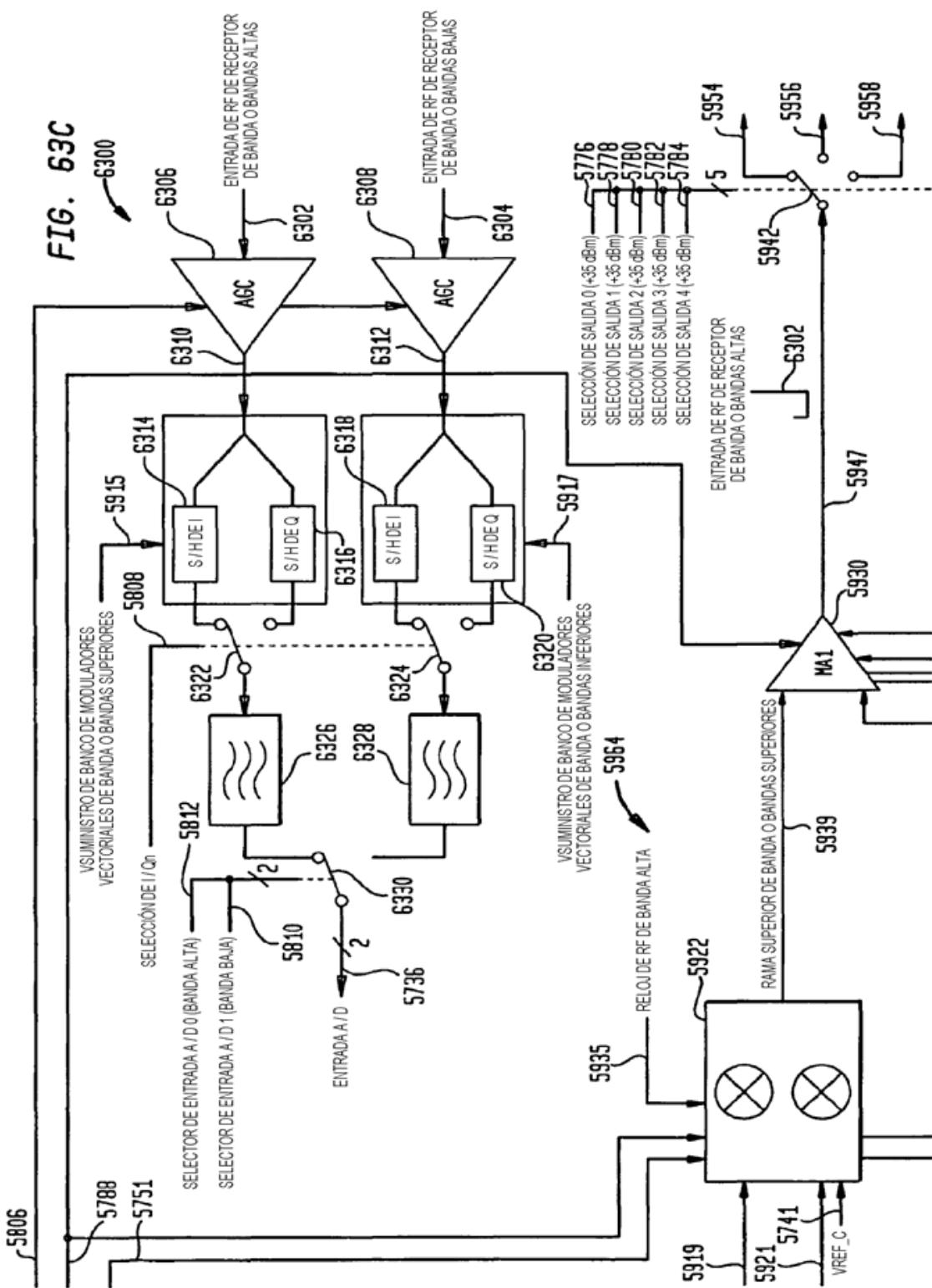

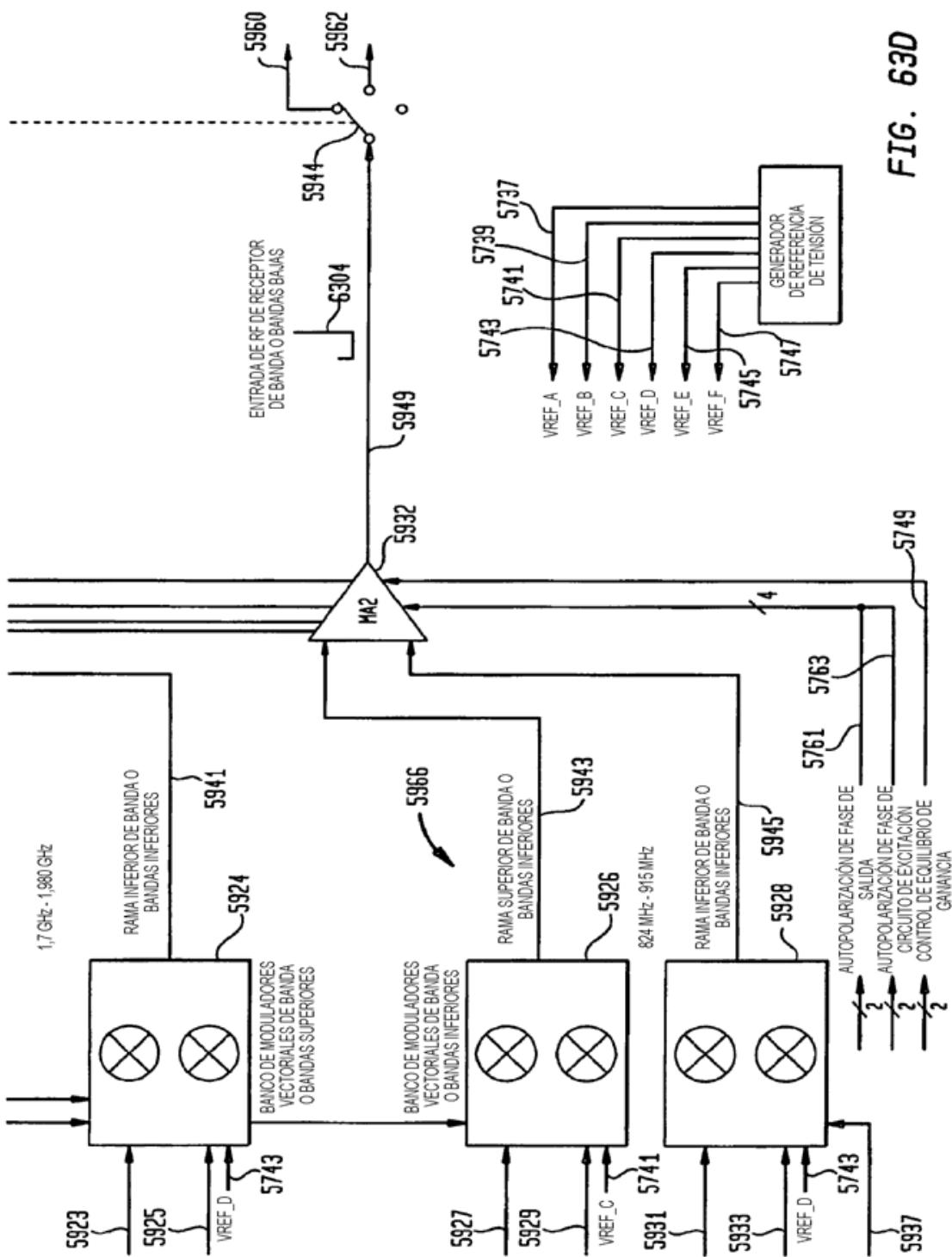

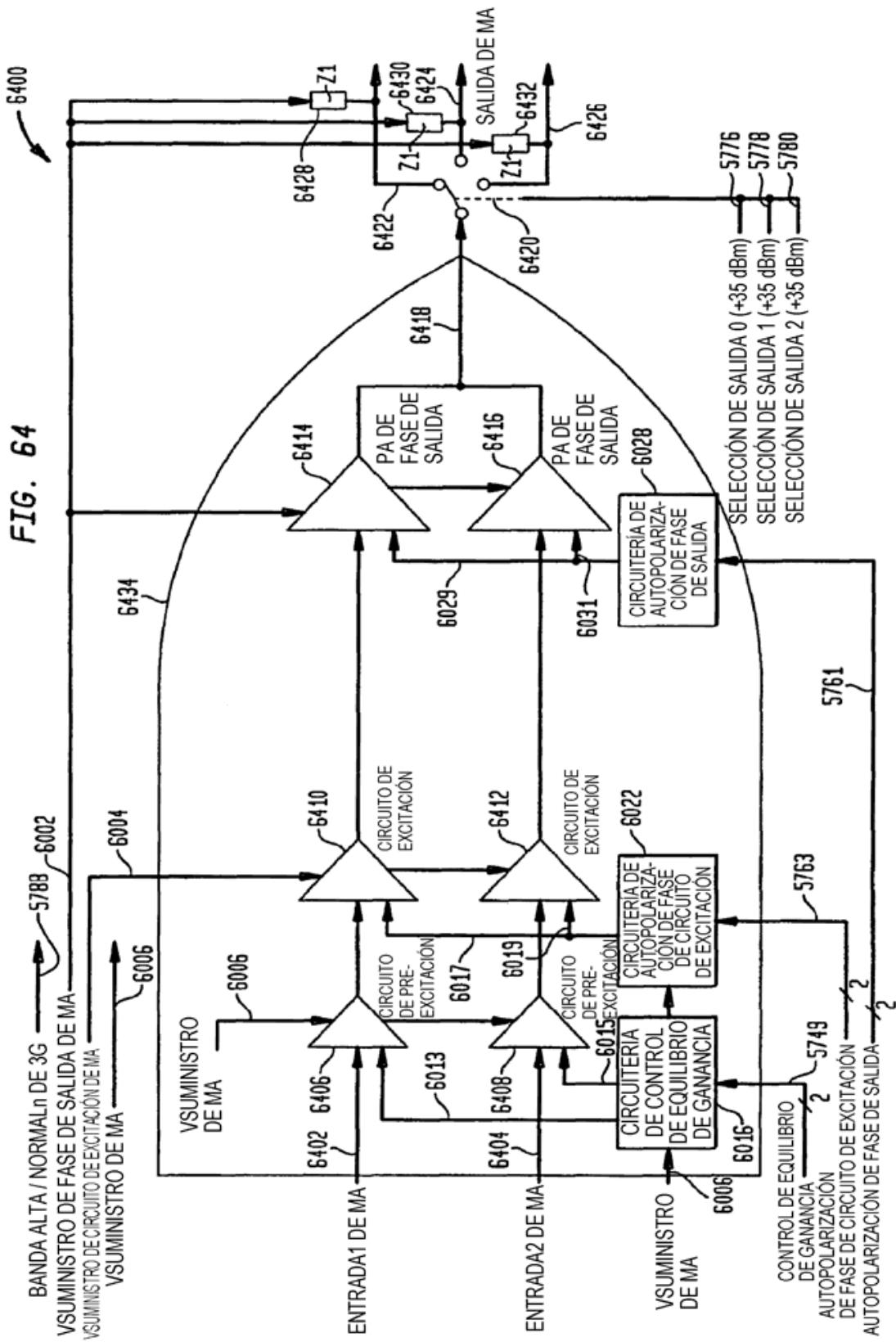

- 30 Las figuras 63A - D ilustran otro núcleo analógico de VPA ejemplar.

- La figura 64 ilustra una fase de salida ejemplar - de acuerdo con el núcleo analógico de VPA de las figuras 63A - D.

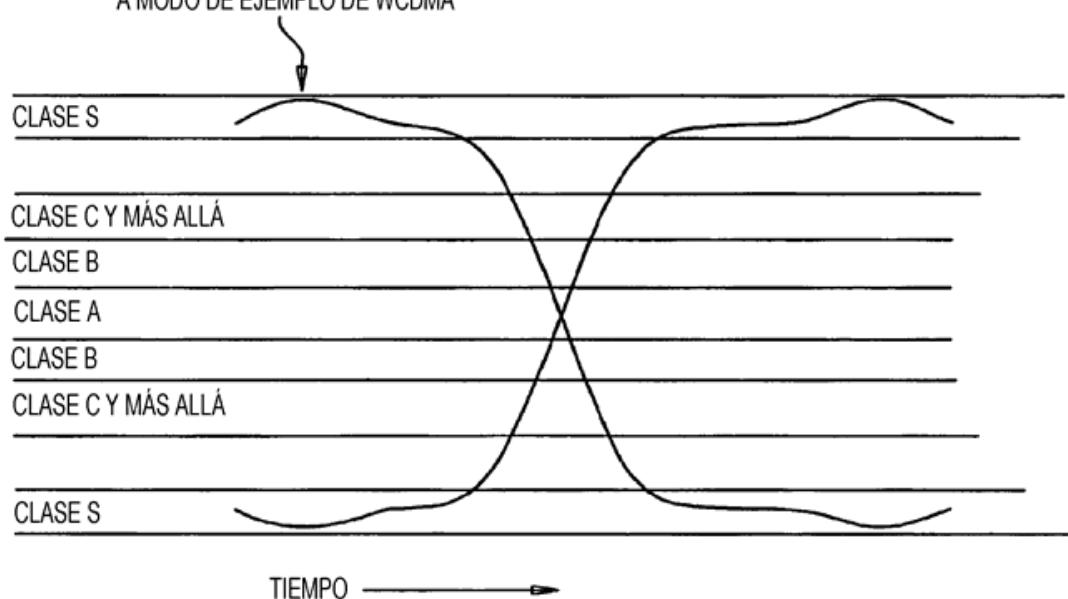

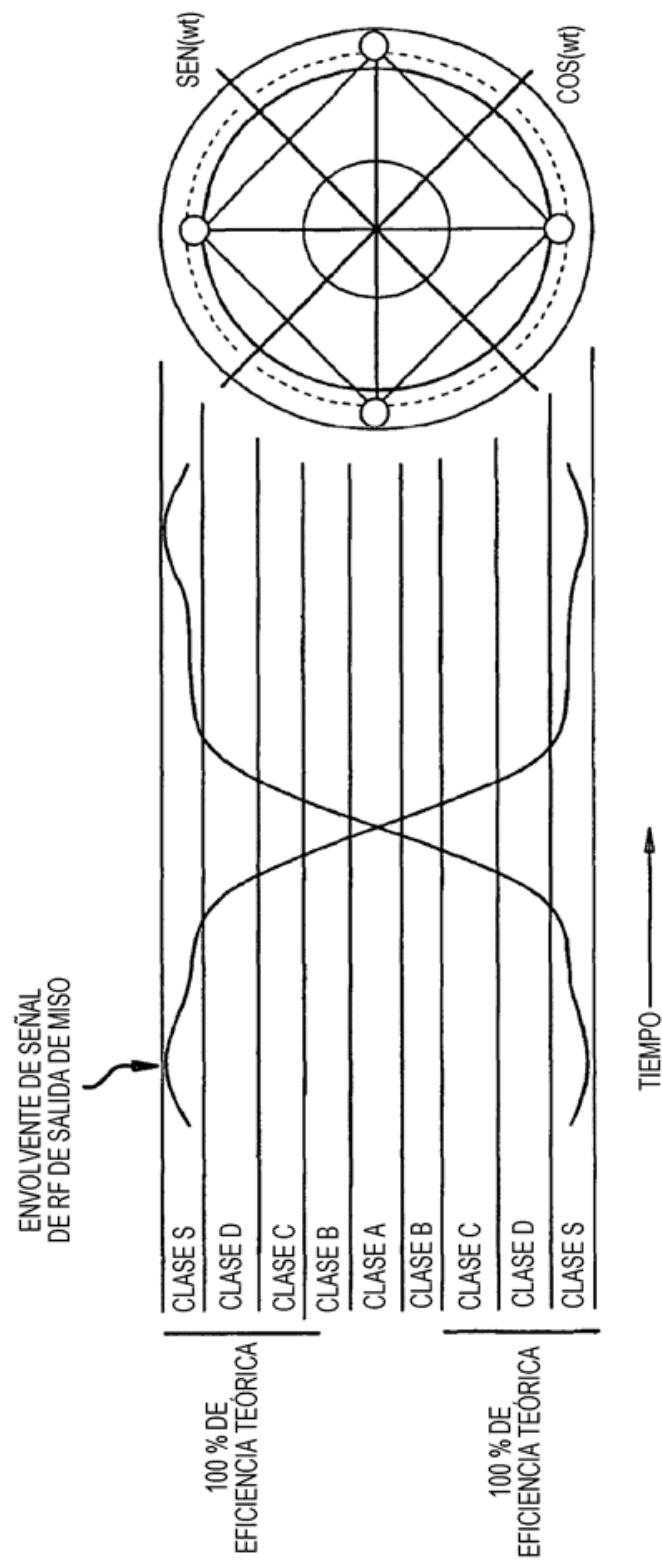

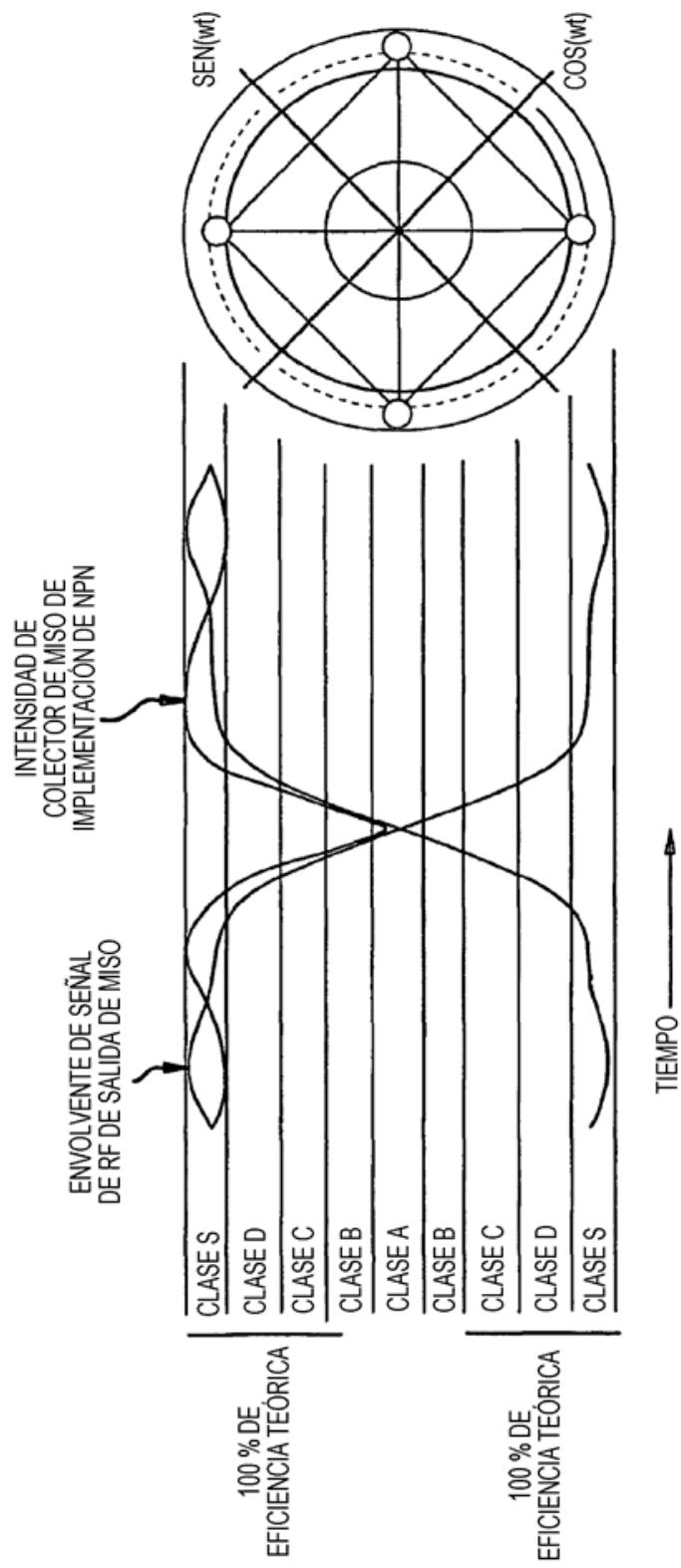

- La figura 65 ilustra el control de clase de amplificador en tiempo real usando una forma de onda ejemplar, de acuerdo con una realización de la presente invención.

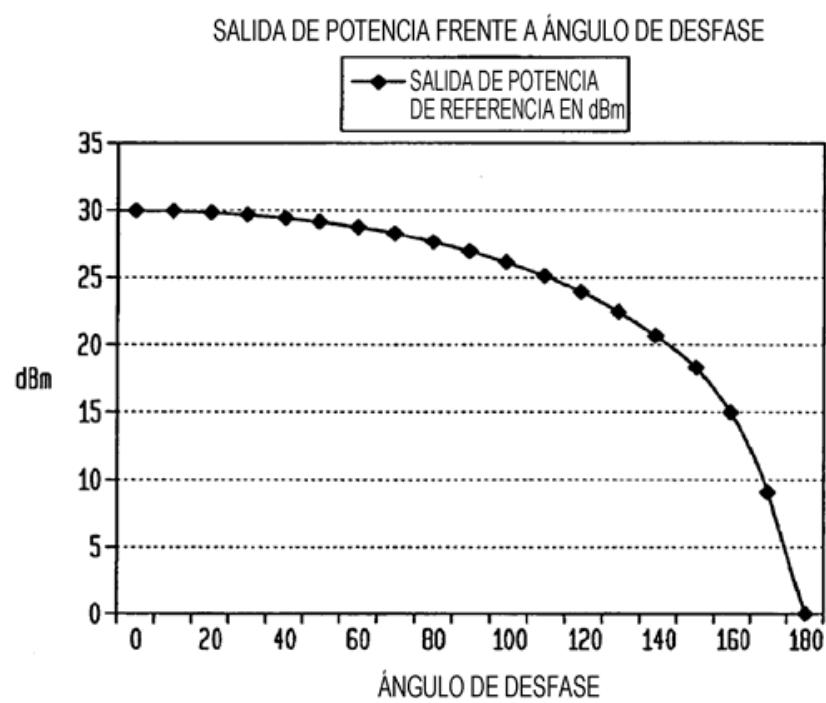

- 35 La figura 66 es una representación gráfica a modo de ejemplo de la potencia de salida frente al ángulo de desfase.

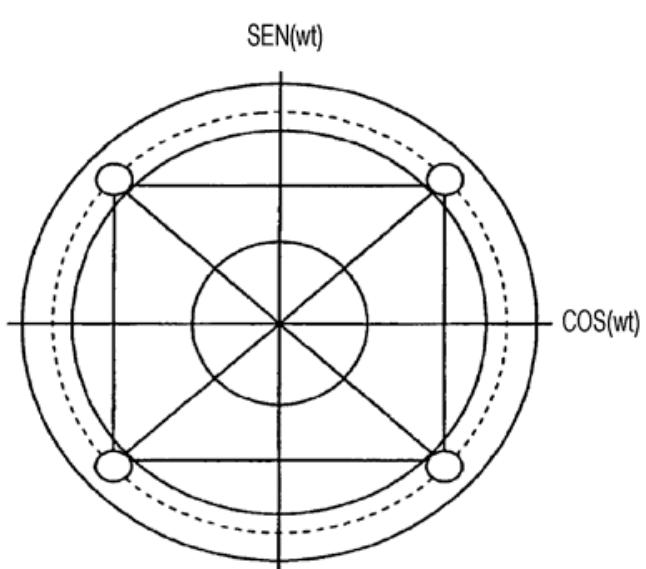

- La figura 67 ilustra unos mecanismos de control de potencia ejemplares usando una forma de onda de QPSK ejemplar, de acuerdo con una realización de la presente invención.

- 40 La figura 68 ilustra el control de clase de amplificador en tiempo real usando una forma de onda ejemplar, de acuerdo con una realización de la presente invención.

- La figura 69 ilustra el control de clase de amplificador en tiempo real usando una forma de onda ejemplar, de acuerdo con una realización de la presente invención.

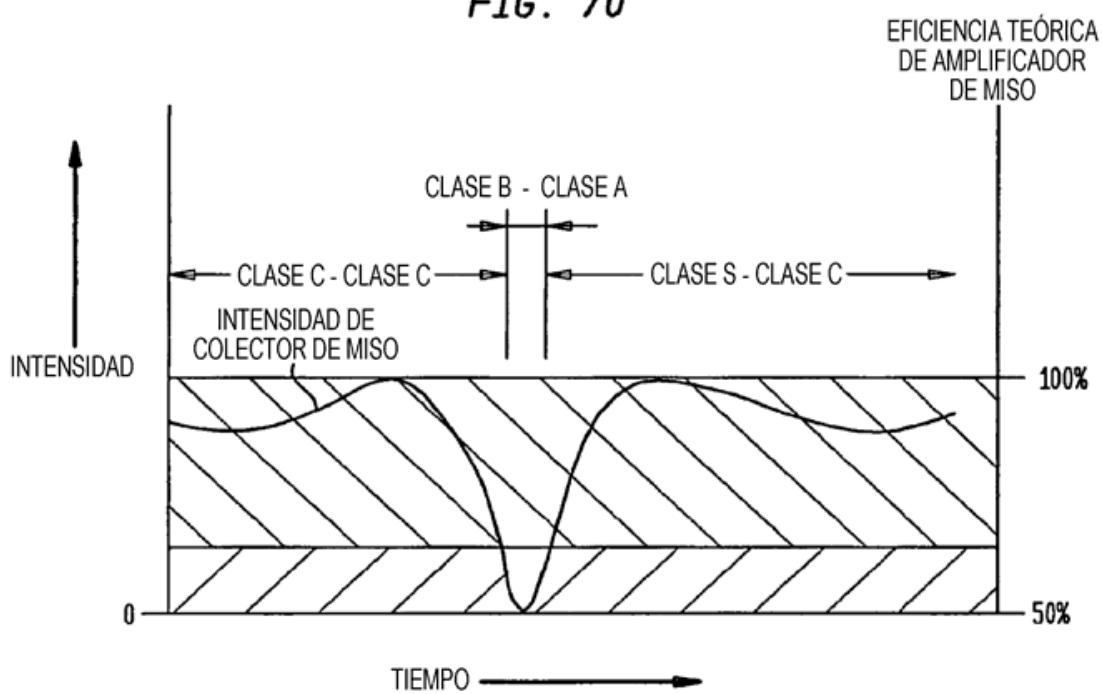

- 45 La figura 70 ilustra una representación gráfica ejemplar de la eficiencia teórica de fase de salida de VPA frente a la intensidad de fase de salida de VPA, de acuerdo con una realización de la presente invención.

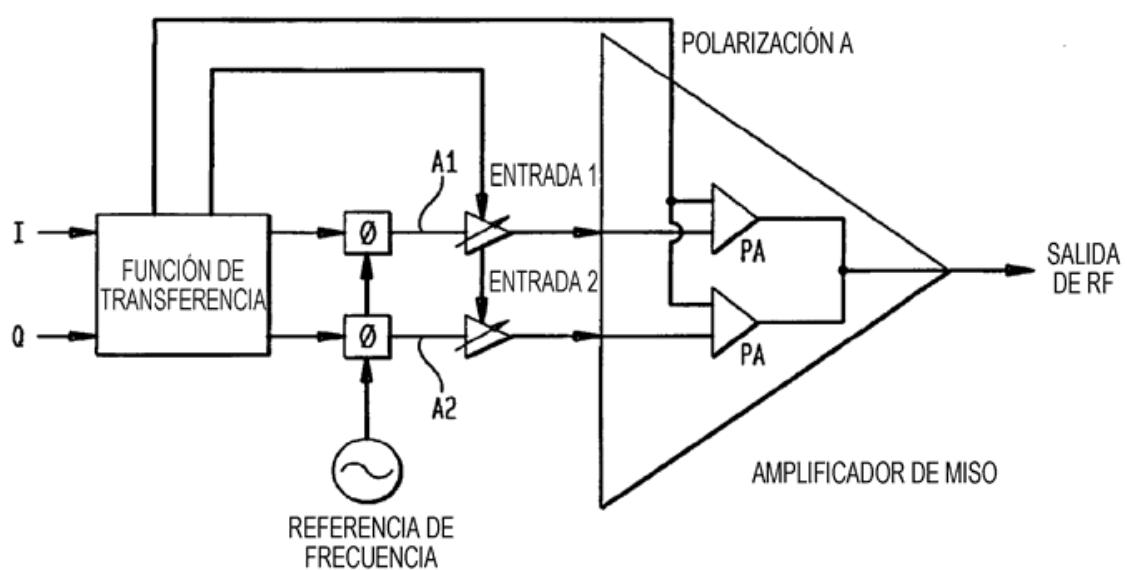

- La figura 71 ilustra un VPA ejemplar de acuerdo con una realización de la presente invención.

- La figura 72 es un diagrama de flujo de proceso que ilustra un procedimiento para el control de clase de amplificador en tiempo real en un amplificador de potencia, de acuerdo con una realización de la presente invención.

- 50 La figura 73 ilustra una fase de salida de VPA a modo de ejemplo.

- La figura 74 ilustra un circuito equivalente para el funcionamiento de clase S de amplificador de la fase de salida de VPA de la figura 73.

- La figura 75 ilustra un circuito equivalente para el funcionamiento de clase A de amplificador de la fase de salida de VPA de la figura 73.

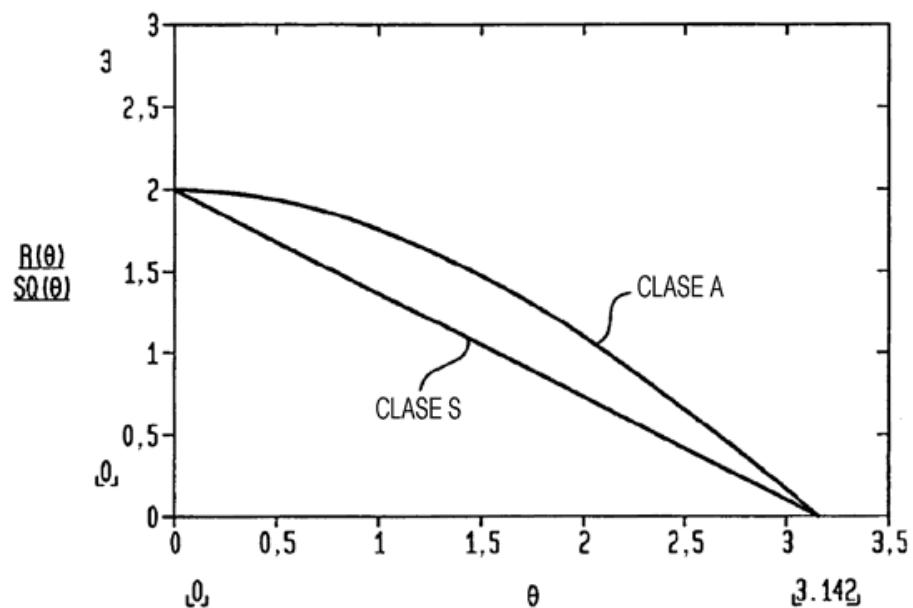

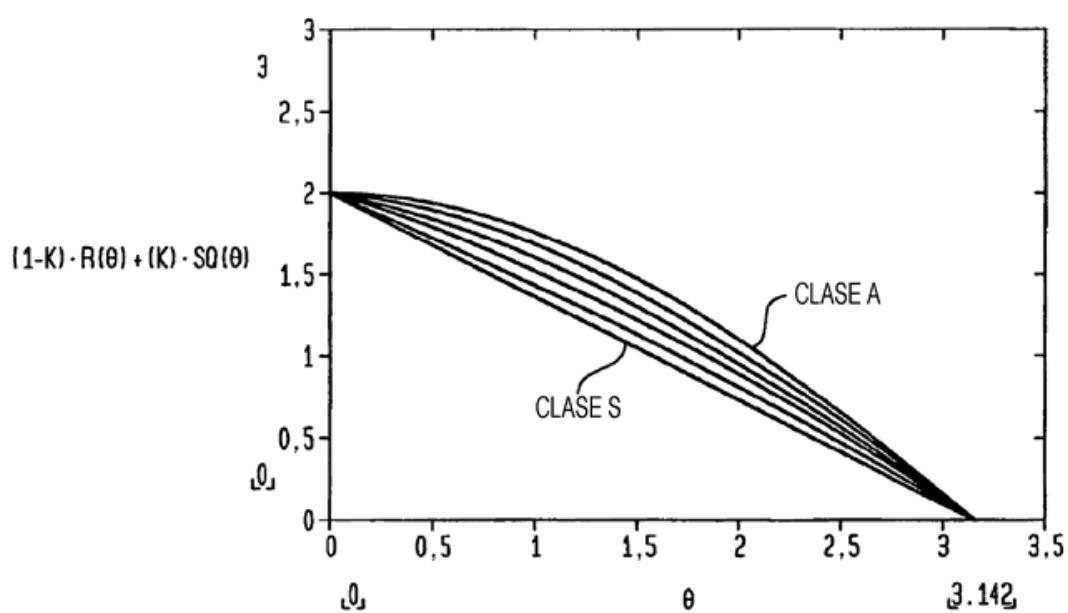

- 55 La figura 76 es una representación gráfica que ilustra unas funciones de transformada de magnitud en desplazamiento de fase ejemplares para el funcionamiento de clase A y de clase S de amplificador de la fase de salida de VPA de la figura 73.

- La figura 77 es una representación gráfica que ilustra un espectro de funciones de transformada de magnitud en desplazamiento de fase que se corresponden con una gama de clases de funcionamiento de amplificador de la fase de salida de VPA de la figura 73.

- 60 La figura 78 ilustra una deducción matemática de la transformada de magnitud en desplazamiento de fase en presencia de errores de amplitud y de fase de rama.

Las realizaciones de la presente invención se describirán con referencia a los dibujos adjuntos. El dibujo en el que un elemento aparece por primera vez se indica típicamente mediante el dígito o dígitos más a la izquierda en el número de referencia correspondiente.

**Descripción detallada**

**Índice de Contenidos**

1. Introducción

- 1.1. Generación a modo de ejemplo de Señales de Entrada de Envolvente Compleja Variable en el Tiempo

- 5 1.2. Generación a modo de ejemplo de Señales de Envolvente Compleja Variable en el Tiempo a partir de Señales de Envolvente Constante

- 1.3. Visión de Conjunto de Amplificación de Potencia Vectorial

2. Visión de Conjunto Matemática General

- 2.1. Representación de Señal Fasorial

- 10 2.2. Señales de Envolvente Compleja Variable en el Tiempo

- 2.3. Descomposición de Envolvente Constante de Señales de Envolvente Variable en el Tiempo

3. Procedimientos y Sistemas de Amplificación de Potencia Vectorial (VPA)

- 3.1. Amplificador de Potencia Vectorial de 4 Ramas Cartesiana

- 3.2. Amplificador de Potencia Vectorial de 2 Ramas Cartesiana - Polar - Cartesiana - Polar (CPCP)

- 15 3.3. Amplificador de Potencia Vectorial de 2 Ramas Cartesiana Directa

- 3.4. Funciones de Transferencia de Datos de I y de Q a Modulador Vectorial

- 3.4.1. Función de Transferencia de VPA de 4 Ramas Cartesiana

- 3.4.2. Función de Transferencia de VPA de 2 Ramas CPCP

- 3.4.3. Función de Transferencia de VPA de 2 Ramas Cartesiana Directa

- 20 3.4.4. Magnitud para Transformada en Desplazamiento de Fase

- 3.4.4.1. Magnitud para Transformada en Desplazamiento de Fase para Señales Sinusoidales

- 3.4.4.2. Magnitud para Transformada en Desplazamiento de Fase para Señales de Onda Cuadrada

- 3.4.5. Compensación de Distorsión de Forma de Onda

- 3.5. Fase de Salida

- 25 3.5.1. Realizaciones de fase de salida

- 3.5.2. Conformación de Intensidad de Fase de Salida

- 3.5.3. Protección de Fase de Salida

- 3.6. Control de Armónicos

- 3.7. Control de Potencia

- 30 3.8. Realización de Amplificador de Potencia Vectorial ejemplar

4. Realizaciones e Implementaciones Adicionales Ejemplares

- 4.1. Visión de Conjunto

- 4.1.1. Control de Potencia de Salida y Eficiencia Energética

- 4.1.2. Compensación y / o Corrección de Errores

- 35 4.1.3. Funcionamiento de Múltiples Bandas y de Múltiples Modos

- 4.2. Módulo de Control Digital

- 4.3. Núcleo Analógico de VPA

- 4.3.1. Implementación A de Núcleo Analógico de VPA

- 4.3.2. Implementación B de Núcleo Analógico de VPA

- 4.3.3. Implementación C de Núcleo Analógico de VPA

- 5. Control de Clase de Amplificador en Tiempo Real de Fase de Salida de VPA

- 5      6. Sumario

- 7. Conclusiones

### **1. Introducción**

En el presente documento se divultan procedimientos, aparatos y sistemas para la amplificación de potencia de combinación de vectores.

10 La amplificación de potencia de combinación de vectores es un enfoque para optimizar la linealidad y la eficiencia energética de forma simultánea. En términos generales, y haciendo referencia al diagrama de flujo 502 en la figura 50, en la etapa 504 una señal de entrada de envolvente compleja variable en el tiempo, con una amplitud y una fase variables, se descompone en unas señales de constituyente de envolvente constante. En la etapa 506, las señales de constituyente de envolvente constante se amplifican y, a continuación, se suman en la etapa 508 para generar una versión amplificada de la señal de envolvente compleja de entrada. Debido a que las señales de envolvente sustancialmente constante pueden amplificarse con una preocupación mínima por la distorsión no lineal, el resultado de la suma de las señales de envolvente constante experimenta una distorsión no lineal mínima a la vez que proporciona una eficiencia óptima.

20 Por consiguiente, la amplificación de potencia de combinación de vectores permite que se usen unos amplificadores de potencia no lineales para amplificar de forma eficiente señales complejas a la vez que se mantienen unos niveles de distorsión no lineal mínimos.

Para fines de conveniencia, y no de limitación, a veces se hace referencia en el presente documento a los procedimientos y sistemas de las realizaciones de la presente invención como procedimientos y sistemas de amplificación de potencia vectorial (VPA).

25 En lo que sigue se proporciona una descripción de alto nivel de procedimientos y sistemas de VPA. Para fines de claridad, en lo que sigue se definen, en primer lugar, determinadas expresiones. Las definiciones que se describen en esta sección se proporcionan solo para fines de conveniencia, y no son limitantes. El significado de estas expresiones será evidente para los expertos en la materia o materias en base a la totalidad de las enseñanzas que se proporcionan en el presente documento. Estas expresiones pueden analizarse a través de la totalidad de la memoria descriptiva con detalle adicional.

30 La expresión envolvente de señal, cuando usa en el presente documento, hace referencia a un límite de amplitud dentro del cual una señal está contenida a medida que esta fluctúa en el dominio del tiempo. Las señales moduladas en cuadratura pueden describirse mediante  $r(t) = i(t) \cdot \cos(\omega \cdot t) + q(t) \cdot \sin(\omega \cdot t)$  en la que  $i(t)$  y  $q(t)$  representan unas

35 señales de cuadratura y en fase con la envolvente de señal  $e(t)$ , que es igual a  $e(t) = \sqrt{i(t)^2 + q(t)^2}$  y el ángulo de fase asociado con  $r(t)$  está relacionado con  $\arctan(q(t) / i(t))$ .

40 La expresión señal de envolvente constante, cuando se usa en el presente documento, hace referencia a unas señales de cuadratura y en fase en las que  $e(t) = \sqrt{i(t)^2 + q(t)^2}$ , con  $e(t)$  teniendo un valor relativa o sustancialmente constante.

45 La expresión señal de envolvente variable en el tiempo, cuando usa en el presente documento, hace referencia a una señal que tiene una envolvente de señal variable en el tiempo. Una señal de envolvente variable en el tiempo puede describirse en términos de las señales de cuadratura y en fase como  $e(t) = \sqrt{i(t)^2 + q(t)^2}$ , con  $e(t)$  teniendo un valor variable en el tiempo.

La expresión desplazamiento en fase, cuando se usa en el presente documento, hace referencia a retardar o a adelantar la componente de fase de una señal de envolvente constante o variable en el tiempo en relación con una fase de referencia.

#### **1.1) Generación a modo de ejemplo de Señales de Entrada Variable en el Tiempo de Envolvente Compleja**

Las figuras 1A y 1B son unos ejemplos que ilustran la generación de señales de entrada complejas de fase y de envolvente variables en el tiempo. En la figura 1A, las señales de portadora de envolvente variable en el tiempo 104

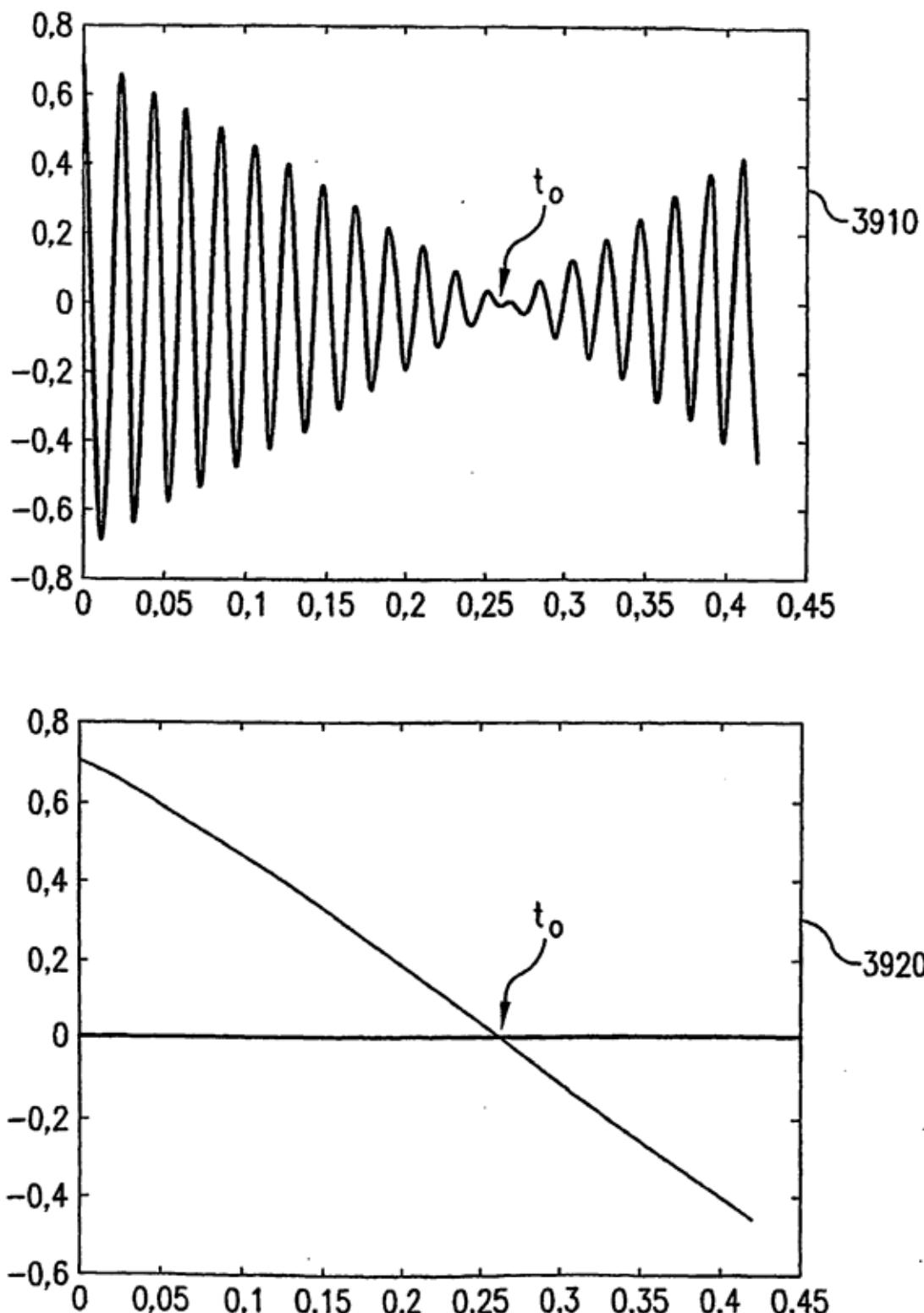

5 y 106 se introducen en el controlador de fase 110. El controlador de fase 110 manipula las componentes de fase de las señales 104 y 106. Dicho de otra forma, el controlador de fase 110 puede desplazar en fase las señales 104 y 106. Las señales 108 y 112 resultantes, por consiguiente, pueden desplazarse en fase en relación con las señales 104 y 106. En el ejemplo de la figura 1A, el controlador de fase 110 da lugar a una inversión de fase (desplazamiento de fase de 180 grados) en las señales 104 y 106 en el instante de tiempo  $t_0$ , tal como puede verse a partir de las señales 108 y 112. Las señales 108 y 112 representan unas señales de portadora complejas variables en el tiempo. Las señales 108 y 112 tienen tanto unas envelopantes como unas componentes de fase variables en el tiempo. Cuando se suman, las señales 108 y 112 dan como resultado la señal 114. La señal 114 también representa una señal compleja variable en el tiempo. La señal 114 puede ser una señal de entrada a modo de ejemplo en las 10 realizaciones de VPA de la presente invención (por ejemplo, una entrada a modo de ejemplo en la etapa 504 de la figura 50).

15 Las señales complejas variables en el tiempo también pueden generarse tal como se ilustra en la figura 1B. En la figura 1B, las señales 116 y 118 representan unas señales de banda de base. Por ejemplo, las señales 116 y 118 pueden ser unas componentes de banda de base en fase (I) y de cuadratura (Q) de una señal. En el ejemplo de la figura 1B, las señales 116 y 118 experimentan un paso por cero a medida que estas realizan una transición de +1 a -1. Las señales 116 y 118 se multiplican por la señal 120 o la señal 120 desplazada en fase 90 grados. La señal 116 se multiplica por una versión desplazada 0 grados de la señal 120. La señal 118 se multiplica por una versión desplazada 90 grados de la señal 120. Las señales 122 y 124 resultantes representan unas señales de portadora complejas variables en el tiempo. Se hace notar que las señales 122 y 124 tienen unas envelopantes que varían de acuerdo con las amplitudes variables en el tiempo de las señales 116 y 118. Además, ambas de las señales 122 y 124 experimentan unas inversiones de fase en los pasos por cero de las señales 116 y 118. Las señales 122 y 124 se suman para dar como resultado la señal 126. La señal 126 representa una señal compleja variable en el tiempo. La señal 126 puede representar una señal de entrada a modo de ejemplo en las realizaciones de VPA de la 20 presente invención. Adicionalmente, las señales 116 y 118 pueden representar unas señales de entrada a modo de ejemplo en las realizaciones de VPA de la presente invención.

25

### **1.2) Generación a modo de ejemplo de Señales de Envoltoría Compleja Variable en el Tiempo a partir de Señales de Envoltoría Constante**

30 La descripción en esta sección se refiere, en general, al funcionamiento de la etapa 508 en la figura 50. La figura 1C ilustra tres ejemplos para la generación de señales complejas variables en el tiempo a partir de la suma de dos o más señales de envoltoría sustancialmente constante. Un experto en la materia apreciará, no obstante, en base a las enseñanzas que se proporcionan en el presente documento, que los conceptos que se ilustran en los ejemplos de la figura 1C pueden extenderse de forma similar al caso de más de dos señales de envoltoría constante.

35 En el ejemplo 1 de la figura 1C, las señales de envoltoría constante 132 y 134 se introducen en el controlador de fase 130. El controlador de fase 130 manipula las componentes de fase de las señales 132 y 134 para generar las señales 136 y 138, respectivamente. Las señales 136 y 138 representan unas señales de envoltoría sustancialmente constante, y se suman para generar la señal 140. La representación fasorial en la figura 1C, asociada con el ejemplo 1, ilustra las señales 136 y 138 como los fasores  $P_{136}$  y  $P_{138}$ , respectivamente. La señal 140 se ilustra como el fasor  $P_{140}$ . En el ejemplo 1,  $P_{136}$  y  $P_{138}$  se desplazan en fase de forma simétrica un ángulo  $\phi_1$  en relación con una señal de referencia que se supone que está alineada con el eje real de la representación fasorial. 40 De forma correspondiente, las señales en el dominio del tiempo 136 y 138 se desplazan en fase en unas cantidades iguales pero en sentidos opuestos en relación con la señal de referencia. Por consiguiente,  $P_{140}$ , que es la suma de  $P_{136}$  y  $P_{138}$ , se encuentra en fase con la señal de referencia.

45 En el ejemplo 2 de la figura 1C, las señales de envoltoría sustancialmente constante 132 y 134 se introducen en el controlador de fase 130. El controlador de fase 130 manipula las componentes de fase de las señales 132 y 134 para generar las señales 142 y 144, respectivamente. Las señales 142 y 144 son unas señales de envoltoría sustancialmente constante, y se suman para generar la señal 150. La representación fasorial asociada con el ejemplo 2 ilustra las señales 142 y 144 como los fasores  $P_{142}$  y  $P_{144}$ , respectivamente. La señal 150 se ilustra como el fasor  $P_{150}$ . En el ejemplo 2,  $P_{142}$  y  $P_{144}$  se desplazan en fase de forma simétrica en relación con una señal de referencia. Por consiguiente, de forma similar a  $P_{140}$ ,  $P_{150}$  también se encuentra en fase con la señal de referencia.  $P_{142}$  y  $P_{144}$ , no obstante, se desplazan en fase un ángulo mediante lo cual  $\phi_2 \neq \phi_1$  en relación con la señal de referencia.  $P_{150}$ , como resultado, tiene una magnitud diferente de  $P_{140}$  del ejemplo 1. En la representación en el dominio del tiempo, se observa que las señales 140 y 150 se encuentran en fase pero tienen diferentes amplitudes una en relación con otra.

55 En el ejemplo 3 de la figura 1C, las señales de envoltoría sustancialmente constante 132 y 134 se introducen en el controlador de fase 130. El controlador de fase 130 manipula las componentes de fase de las señales 132 y 134 para generar las señales 146 y 148, respectivamente. Las señales 146 y 148 son unas señales de envoltoría sustancialmente constante, y se suman para generar la señal 160. La representación fasorial asociada con el ejemplo 3 ilustra las señales 146 y 148 como los fasores  $P_{146}$  y  $P_{148}$ , respectivamente. La señal 160 se ilustra como el fasor  $P_{160}$ . En el ejemplo 3,  $P_{146}$  se desplaza en fase un ángulo  $\phi_3$  en relación con la señal de referencia.  $P_{148}$  se desplaza en fase un ángulo  $\phi_4$  en relación con la señal de referencia.  $\phi_3$  y  $\phi_4$  pueden o pueden no ser iguales. Por consiguiente,  $P_{160}$ , que es la suma de  $P_{146}$  y  $P_{148}$ , ya no se encuentra por más tiempo en fase con la señal de

referencia.  $P_{160}$  se desplaza en fase un ángulo  $\Theta$  en relación con la señal de referencia. De forma similar,  $P_{160}$  se desplaza en fase  $\Theta$  en relación con  $P_{140}$  y  $P_{150}$  de los ejemplos 1 y 2.  $P_{160}$  también puede variar en cuanto a su amplitud en relación con  $P_{140}$  tal como se ilustra en el ejemplo 3.

En resumen, los ejemplos de la figura 1C muestran que una señal de amplitud variable en el tiempo puede obtenerse mediante la suma de dos o más señales de envolvente sustancialmente constante (ejemplo 1). Además, la señal variable en el tiempo puede tener unos cambios de amplitud, pero no cambios de fase, impartidos sobre la misma mediante el desplazamiento por igual en sentidos opuestos de las dos o más señales de envolvente sustancialmente constante (ejemplo 2). Al desplazar por igual en el mismo sentido los dos o más constituyentes de envolvente constante de la señal, pueden impartirse unos cambios de fase, pero no cambios de amplitud, sobre la señal variable en el tiempo. Cualquier señal de fase y de amplitud variable en el tiempo puede generarse usando dos o más señales de envolvente sustancialmente constante (ejemplo 3).

Se hace notar que las señales en los ejemplos de la figura 1C se muestran como unas formas de onda sinusoidales solo para fines de ilustración. Un experto en la materia apreciará, en base a las enseñanzas en el presente documento, que también pueden haberse usado otros tipos de formas de onda. También debería observarse que los ejemplos de la figura 1C se proporcionan en el presente documento solo para fines de ilustración, y pueden o pueden no corresponderse con una realización particular de la presente invención.

### 1.3) Visión de Conjunto de Amplificación de Potencia Vectorial

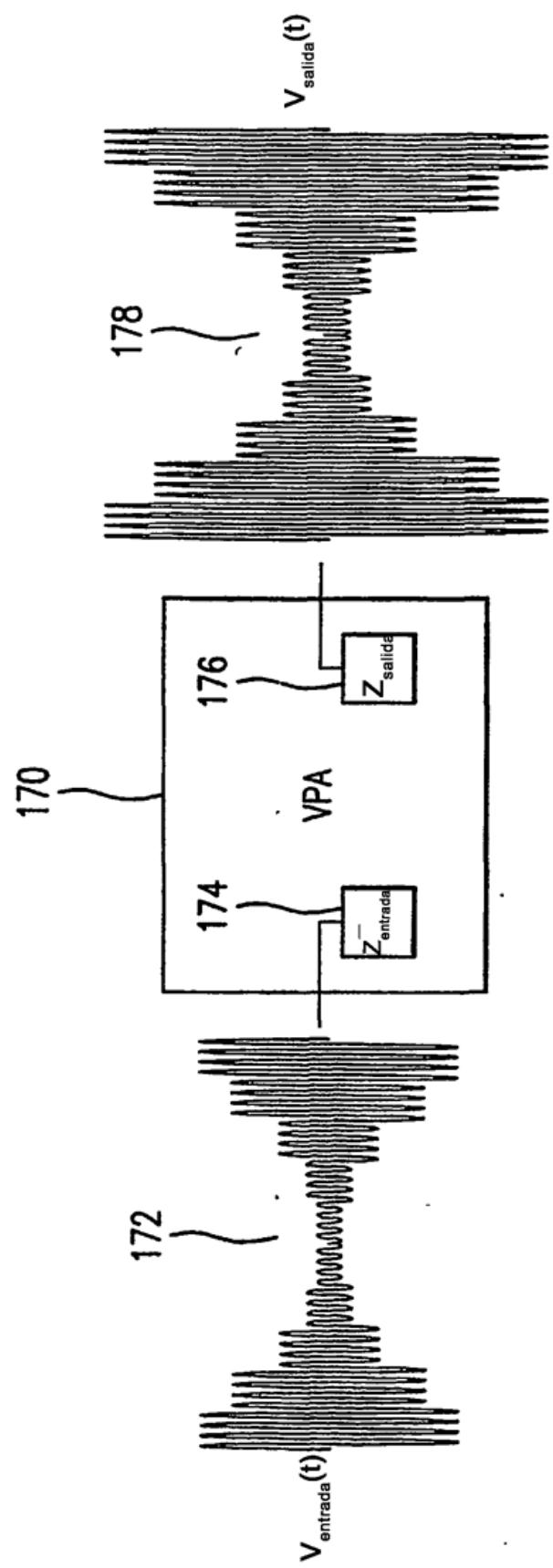

En lo que sigue se proporciona una visión de conjunto de alto nivel de la amplificación de potencia vectorial. La figura 1D ilustra la amplificación de potencia de una señal de entrada compleja variable en el tiempo ejemplar 172. Las señales 114 y 126 tal como se ilustra en las figuras 1A y 1B pueden ser ejemplos de la señal 172. Además, la señal 172 puede generarse mediante o estar compuesta por dos o más señales de constituyente tal como 104 y 106 (figura 1A), 108 y 112 (figura 1A), 116 y 118 (figura 1B) y 122 y 124 (figura 1B).

En el ejemplo de la figura 1D, el VPA 170 representa un sistema de VPA ejemplar. El VPA 170 amplifica la señal 172 para generar la señal de salida amplificada 178. La señal de salida 178 se amplifica de forma eficiente con una distorsión mínima.

En el ejemplo de la figura 1D, las señales 172 y 178 representan las señales de tensión  $V_{\text{entrada}}(t)$  y  $V_{\text{out}}(t)$ , respectivamente. En cualquier instante de tiempo, en el ejemplo de la figura 1D,  $V_{\text{in}}(t)$  y  $V_{\text{out}}(t)$  están relacionadas de tal modo que  $V_{\text{out}}(t) = K V_{\text{entrada}}(t-t')$ , en la que  $K$  es un factor de escala y  $t'$  representa un retardo de tiempo que

puede estar presente en el sistema de VPA. Para la implicación de potencia,  $\frac{V_{\text{salida}}^2(t)}{Z_{\text{salida}}} > \frac{V_{\text{entrada}}^2(t)}{Z_{\text{entrada}}}$ , en la que la señal

30 de salida 178 es una versión amplificada en potencia de la señal de entrada 172.

La amplificación de potencia lineal (o sustancialmente lineal) de señales complejas variables en el tiempo, tal como se ilustra en la figura 1D, se consigue tal como se muestra en la figura 1E.

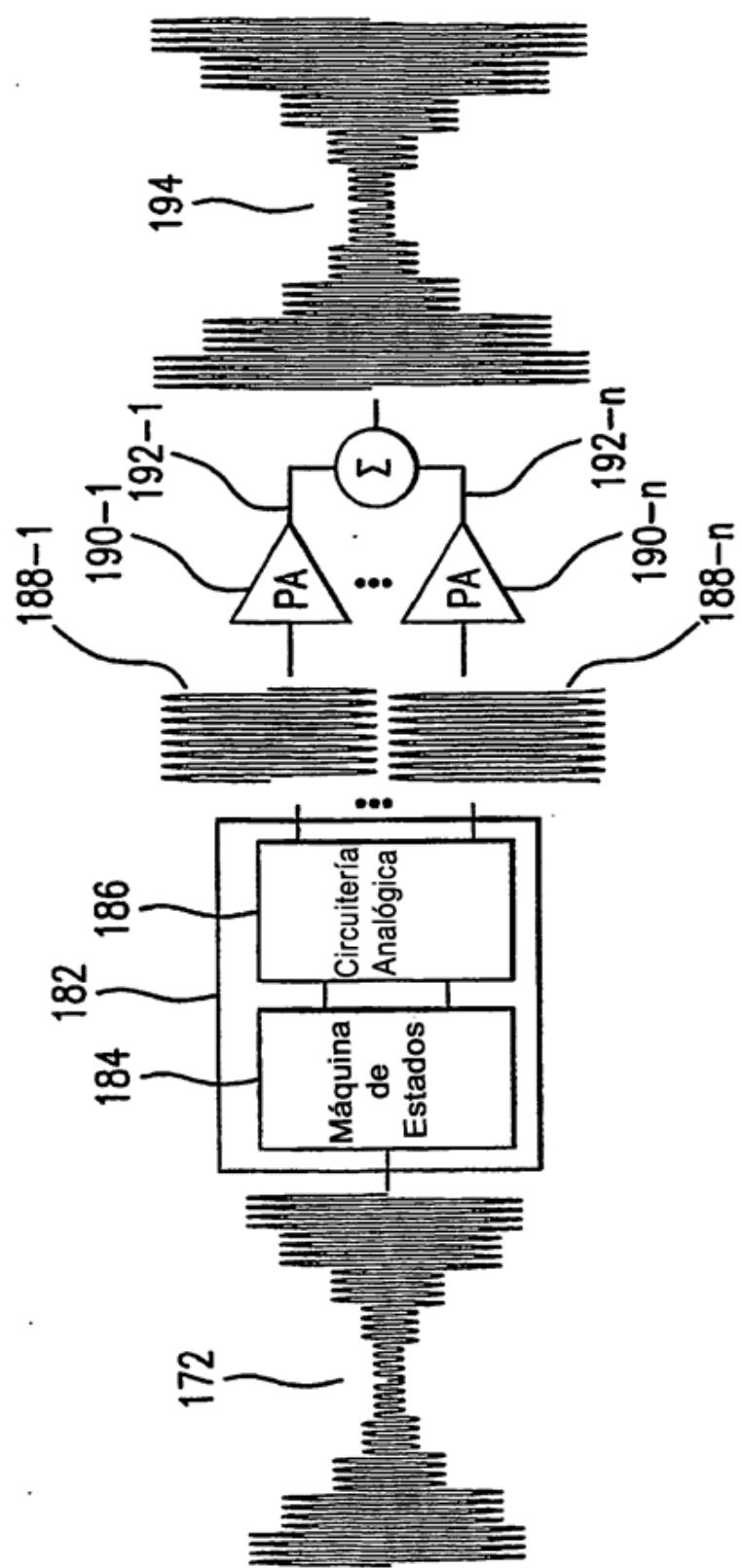

La figura 1E es un diagrama de bloques a modo de ejemplo que ilustra de forma conceptual una amplificación de potencia vectorial. En la figura 1E, la señal de entrada 172 representa una señal compleja variable en el tiempo. Por ejemplo, la señal de entrada 172 puede generarse tal como se ilustra en las figuras 1A y 1B. La señal 172 puede ser una señal digital o una analógica. Además, la señal 172 puede ser una banda de base o una señal basada en portadora.

Haciendo referencia a la figura 1E, la señal de entrada 172 o equivalentes de la misma se introducen en el VPA 182. En la figura 1E, el VPA 182 incluye una máquina de estados 184 y la circuitería analógica 186. La máquina de estados 184 puede incluir componentes analógicos y / o digitales. La circuitería analógica 186 incluye componentes analógicos. El VPA 182 procesa la señal de entrada 172 para generar dos o más señales 188 - {1, ..., n}, tal como se ilustra en la figura 1E. Como se describe con respecto a las señales 136, 138, 142, 144 y 146, 148, en la figura 1C, las señales 188 - {1, ..., n} pueden o pueden no desplazarse en fase una en relación con otra a través de diferentes períodos de tiempo. Además, el VPA 182 genera unas señales 188 - {1, ..., n} de tal modo que una suma de las señales 188 - {1, ..., n} da como resultado la señal 194 que puede ser una versión amplificada de la señal 172.

Haciendo de nuevo referencia a la figura 1E, las señales 188 - {1, ..., n} son unas señales de envolvente sustancialmente constante. Por consiguiente, la descripción en el párrafo anterior se corresponde con la etapa 504 en la figura 50.

50 En el ejemplo de la figura 1E, que se corresponde, en general, con la etapa 506 en la figura 50, cada una de las señales de envolvente constante 188 - {1, ..., n} se amplifica de forma independiente mediante un amplificador de potencia (PA) 190 - {1, ..., n} correspondiente para generar las señales amplificadas 192 - {1, ..., n}. Los PA 190 - {1, ..., n} amplifican sustancialmente por igual las señales de envolvente constante 188 - {1, ..., n} respectivas. Las señales amplificadas 192 - {1, ..., n} son unas señales de envolvente sustancialmente constante, y en la etapa 508

se suman para generar la señal de salida 194. Se hace notar que la señal de salida 194 puede ser una versión amplificada de forma lineal (o de forma sustancialmente lineal) de la señal de entrada 172. La señal de salida 194 también puede ser una versión con conversión elevadora en frecuencia de la señal de entrada 172, tal como se describe en el presente documento.

5 **2. Visión de Conjunto Matemática General**

**2.1) Representación de Señal Fasorial**

La figura 1 ilustra una representación fasorial  $\vec{R}$  102 de una señal  $r(t)$ . Una representación fasorial de una señal es explícitamente representativa de la magnitud de la envolvente de la señal y del desplazamiento de fase de la señal en relación con una señal de referencia. En el presente documento, para fines de conveniencia, y no de limitación, la señal de referencia se define como alineada con el eje real ( $\text{Re}$ ) del espacio ortogonal de la representación fasorial. La divulgación no se limita, no obstante, al presente ejemplo. La información de frecuencia de la señal está implícita en la representación, y está dada por la frecuencia de la señal de referencia. Por ejemplo, haciendo referencia a la figura 1, y suponiendo que el eje real se corresponde con una señal de referencia de  $\cos(\omega t)$ , el fasor  $\vec{R}$  se traduciría en la función  $r(t) = R(t) \cos(\omega t + \phi(t))$ , en la que  $\vec{R}$  es la magnitud de  $\vec{R}$ .

15 Haciendo de nuevo referencia a la figura 1, se hace notar que el fasor  $\vec{R}$  puede descomponerse en un fasor de parte real  $\vec{I}$  y un fasor de parte imaginaria  $\vec{Q}$ . Se dice que  $\vec{I}$  y  $\vec{Q}$  son las componentes fasoriales de cuadratura y en fase de  $\vec{R}$  con respecto a la señal de referencia. Se observa además que las señales que se corresponden con  $\vec{I}$  y  $\vec{Q}$  están relacionadas con  $r(t)$  como  $I(t) = R(t) \cdot \cos(\phi(t))$  y  $Q(t) = R(t) \cdot \sin(\phi(t))$ , respectivamente. En el dominio del tiempo, la señal  $r(t)$  también puede escribirse en términos de sus componentes de cuadratura y en fase tal como sigue:

$$\begin{aligned} r(t) &= I(t) \cdot \cos(\omega t) + Q(t) \cdot \sin(\omega t) = \\ &= R(t) \cdot \cos(\phi(t)) \cdot \cos(\omega t) + R(t) \cdot \sin(\phi(t)) \cdot \sin(\omega t) \end{aligned} \quad (1)$$

Obsérvese que, en el ejemplo de la figura 1,  $R(t)$  se ilustra en un instante de tiempo particular.

**2.2) Señales de Envoltura Compleja Variable en el Tiempo**

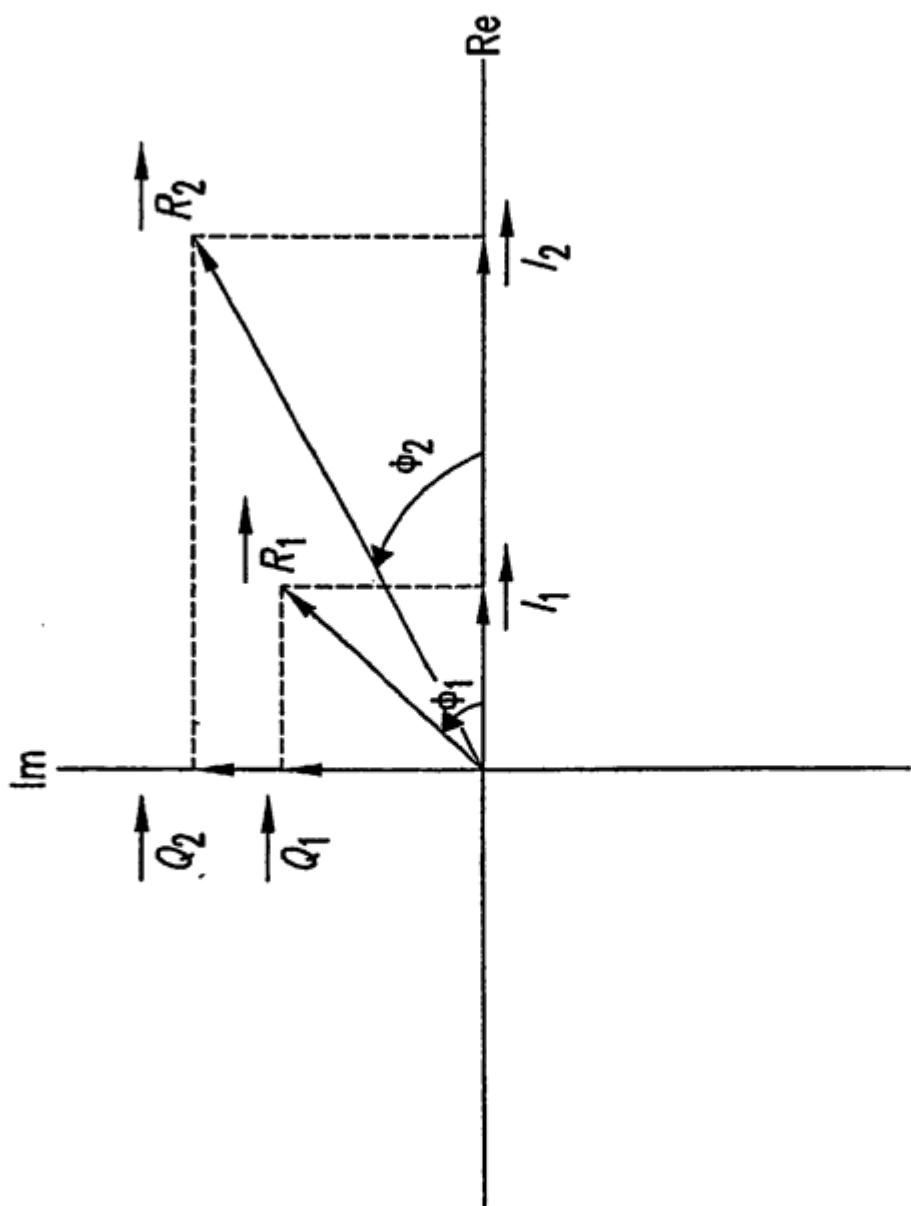

25 La figura 2 ilustra una representación fasorial de una señal  $r(t)$  en dos instantes diferentes de tiempo  $t_1$  y  $t_2$ . Se hace notar que tanto la magnitud del fasor, que representa la magnitud de la envolvente de la señal, como su desplazamiento de fase relativo, varían del instante  $t_1$  al instante  $t_2$ . En la figura 2, esto se ilustra mediante la magnitud variable de los fasores  $\vec{R}_1$  y  $\vec{R}_2$  y sus ángulos de desplazamiento de fase  $\phi_1$  y  $\phi_2$  correspondientes. La señal  $r(t)$ , por consiguiente, es una señal de envolvente compleja variable en el tiempo.

30 Se hace notar además, a partir de la figura 2, que las componentes fasoriales real e imaginaria de la señal  $r(t)$  también son variables en el tiempo en cuanto a su amplitud. Por consiguiente, sus señales en el dominio del tiempo correspondientes también tienen unas envolventes variables en el tiempo.

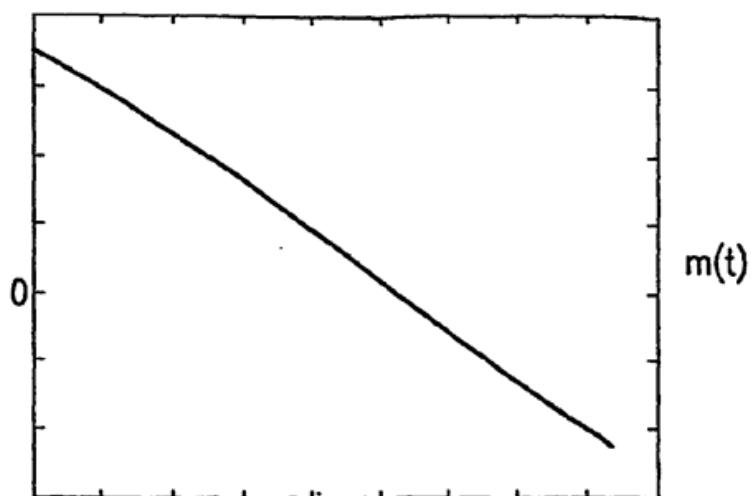

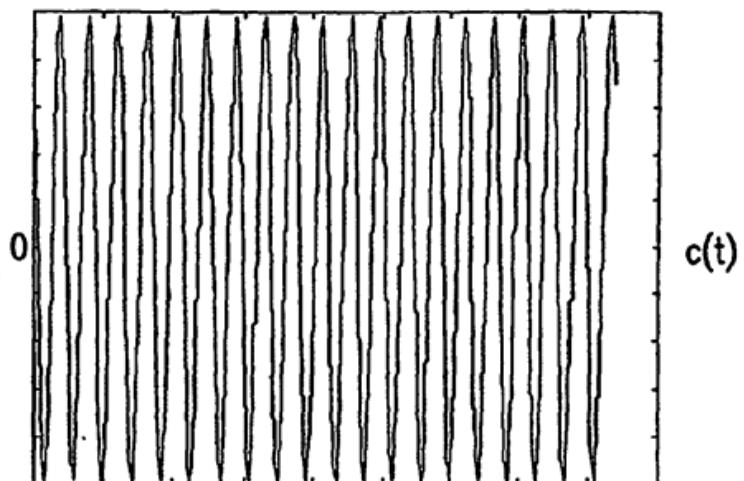

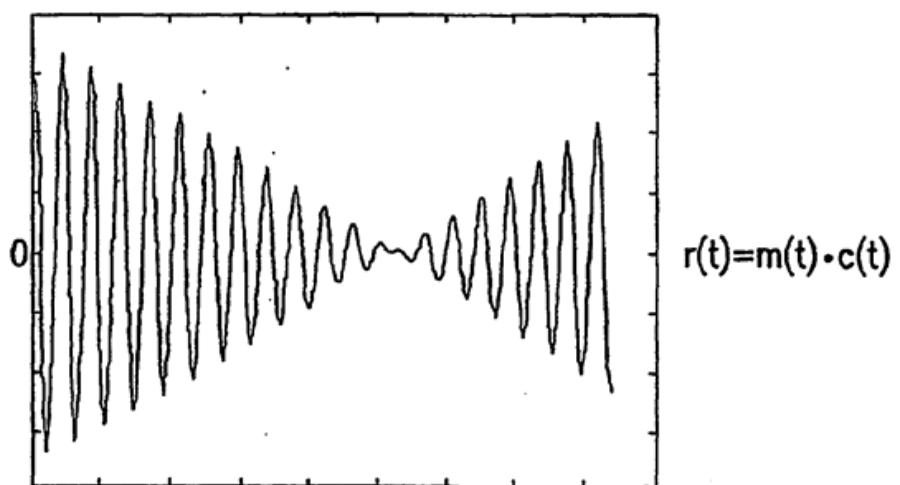

Las figuras 3A - 3C ilustran una modulación a modo de ejemplo para generar una señal de envolvente compleja variable en el tiempo. La figura 3A ilustra una vista de una señal  $m(t)$ . La figura 3B ilustra una vista de una porción de una señal portadora  $c(t)$ . La figura 3C ilustra una señal  $r(t)$  que resulta de la multiplicación de las señales  $m(t)$  y  $c(t)$ .

35 En el ejemplo de la figura 3A, la señal  $m(t)$  es una señal de magnitud variable en el tiempo. Además,  $m(t)$  experimenta un paso por cero. La señal portadora  $c(t)$ , en el ejemplo de la figura 3B, oscila a alguna frecuencia de portadora, típicamente más alta que la de la señal  $m(t)$ .

40 A partir de la figura 3C, puede observarse que la señal resultante  $r(t)$  tiene una envolvente variable en el tiempo. Además, se observa, a partir de la figura 3C, que  $r(t)$  experimenta una inversión en fase en el instante en el que la señal de modulación  $m(t)$  pasa por cero. Teniendo tanto la fase como la envolvente no constantes, se dice que  $r(t)$  es una señal de envolvente compleja variable en el tiempo.

**2.3) Descomposición de Envoltura Constante de Señales de Envoltura Variable en el Tiempo**

45 Cualquier fasor de fase y de amplitud variables en el tiempo puede obtenerse mediante la suma de dos o más fasores de magnitud constante que tienen unos desplazamientos de fase especificados de forma apropiada en relación con un fasor de referencia.

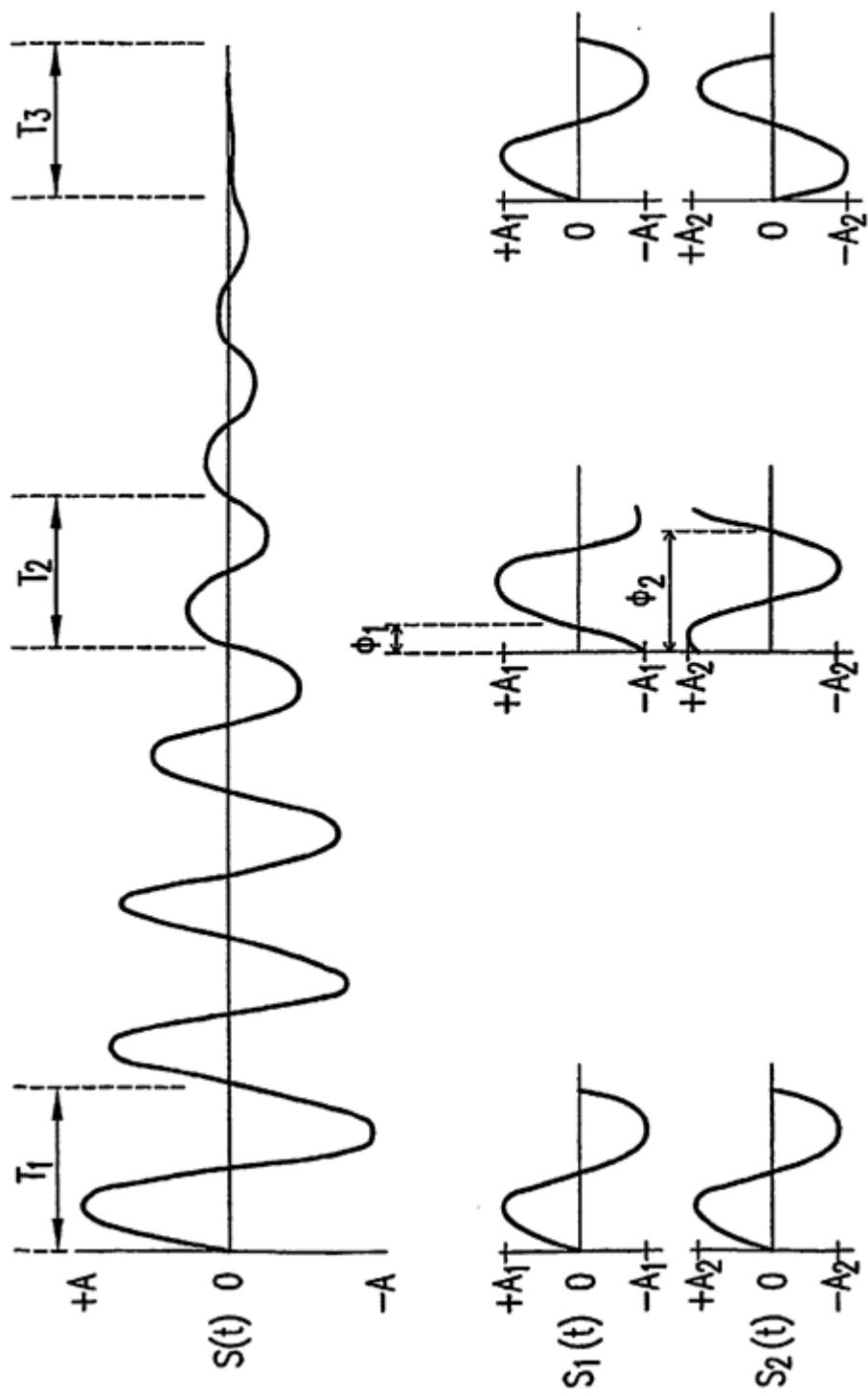

La figura 3D ilustra una vista de una señal de fase y de envolvente variables en el tiempo a modo de ejemplo  $S(t)$ . Para facilidad de ilustración, se supone que la señal  $S(t)$  es una señal sinusoidal que tiene una magnitud de envolvente máxima  $A$ . La figura 3D muestra además un ejemplo de cómo la señal  $S(t)$  puede obtenerse, en cualquier instante de tiempo, mediante la suma de dos señales de envolvente constante  $S_1(t)$  y  $S_2(t)$ . En general,  $S_1(t) = A_1 \sin(\omega t + \phi_1(t))$  y  $S_2(t) = A_2 \sin(\omega t + \phi_2(t))$ .

Para fines de ilustración, en la figura 3D se proporcionan tres vistas que ilustran cómo mediante el desplazamiento en fase de forma apropiada de las señales  $S_1(t)$  y  $S_2(t)$  en relación con  $S(t)$ , las señales  $S_1(t)$  y  $S_2(t)$  pueden sumarse de tal modo que  $S(t) = K(S_1(t) + S_2(t))$  en la que  $K$  es una constante. Dicho de otra forma, la señal  $S(t)$  puede descomponerse, en cualquier instante de tiempo, en dos o más señales. A partir de la figura 3D, a través del periodo  $T_1$ , tanto  $S_1(t)$  como  $S_2(t)$  se encuentran en fase en relación con la señal  $S(t)$  y, por lo tanto, totalizan la magnitud de envolvente máxima  $A$  de la señal  $S(t)$ . A través del periodo  $T_3$ , no obstante, las señales  $S_1(t)$  y  $S_2(t)$  se encuentran desfasadas 180 grados una en relación con otra y, por lo tanto, totalizan una magnitud de envolvente mínima de la señal  $S(t)$ .

El ejemplo de la figura 3D ilustra el caso de las señales sinusoidales. Un experto en la materia, no obstante, entenderá que cualquier envolvente variable en el tiempo, que modula una señal portadora que puede representarse mediante una serie de Fourier o una transformada de Fourier, puede descomponerse, de forma similar, en dos o más señales de envolvente sustancialmente constante. Por lo tanto, mediante el control de la fase de una pluralidad de señales de envolvente sustancialmente constante, puede generarse cualquier señal de envolvente compleja variable en el tiempo.

### 20 **3. Procedimientos y Sistemas de Amplificación de Potencia Vectorial**

Los procedimientos y sistemas de amplificación de potencia vectorial ejemplares pueden basarse en la capacidad de descomponer cualquier señal de envolvente variable en el tiempo en dos o más señales de constituyente de envolvente sustancialmente constante o de recibir o generar tales señales de constituyente, amplificar las señales de constituyente y, a continuación, sumar las señales amplificadas para generar una versión amplificada de la señal de envolvente compleja variable en el tiempo.

En las secciones 3.1 - 3.3, se proporcionan unas realizaciones de amplificación de potencia vectorial (VPA) de la presente invención, incluyendo unas realizaciones de 4 ramas y de 2 ramas. En la descripción, cada realización de VPA se presenta en primer lugar de forma conceptual usando un cálculo matemático de los conceptos subyacentes de la realización. Una realización de un procedimiento de funcionamiento de la realización de VPA se presenta a continuación, seguida por varias realizaciones de nivel de sistema de la realización de VPA.

La sección 3.4 presenta varias realizaciones de módulos de control de acuerdo con las realizaciones de la presente invención. Los módulos de control de acuerdo con las realizaciones de la presente invención pueden usarse para posibilitar determinadas realizaciones de VPA de la presente invención. En algunas realizaciones, los módulos de control son intermediarios entre una fase de entrada de la realización de VPA y una fase de modulación vectorial subsiguiente de la realización de VPA.

La sección 3.5 describe unas realizaciones de fase de salida de VPA de acuerdo con las realizaciones de la presente invención. Las realizaciones de fase de salida están dirigidas a generar la señal de salida de una realización de VPA.

40 La sección 3.6 está dirigida al control de armónicos de acuerdo con las realizaciones de la presente invención. El control de armónicos puede implementarse en determinadas realizaciones de la presente invención para manipular la potencia real e imaginaria en los armónicos de la realización de VPA, aumentando de este modo la potencia presente en la frecuencia fundamental en la salida.

45 La sección 3.7 está dirigida al control de potencia de acuerdo con las realizaciones de la presente invención. El control de potencia puede implementarse en determinadas realizaciones de la presente invención con el fin de satisfacer los requisitos de nivel de potencia de las aplicaciones en las que las realizaciones de VPA de la presente invención pueden emplearse.

#### **3.1) Amplificador de Potencia Vectorial de 4 Ramas Cartesiana**

50 De acuerdo con un ejemplo de la presente invención que se denomina, en el presente documento, VPA de 4 Ramas Cartesiana para facilidad de ilustración y no como limitación, una señal de envolvente compleja variable en el tiempo se descompone en 4 señales de constituyente de envolvente sustancialmente constante. Las señales de constituyente se amplifican por igual o sustancialmente por igual de forma individual y, a continuación, se suman para construir una versión amplificada de la señal de envolvente compleja variable en el tiempo original.

55 Se hace notar que 4 ramas se emplean en el presente ejemplo para fines de ilustración, y no de limitación. El alcance de la divulgación cubre el uso de otros números de ramas, y la implementación de tales variaciones será evidente para los expertos en la materia en base a las enseñanzas que están contenidas en el presente documento.

En un ejemplo, una señal de envolvente compleja variable en el tiempo se descompone en primer lugar en sus componentes vectoriales de cuadratura y en fase. En una representación fasorial, las componentes vectoriales de cuadratura y en fase se corresponden con los fasores de parte real y de parte imaginaria de la señal, respectivamente.

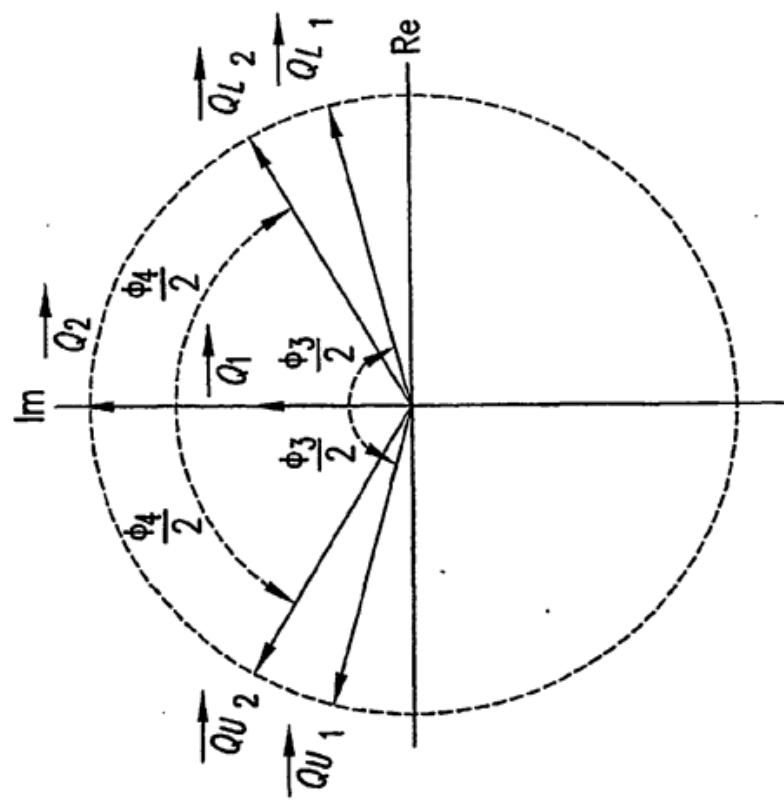

- 5 Como se ha descrito en lo que antecede, las magnitudes de las componentes vectoriales de cuadratura y en fase de una señal varían de forma proporcional a la magnitud de la señal y, por lo tanto, son de envolvente no constante cuando la señal es una señal de envolvente variable en el tiempo. Por consiguiente, el ejemplo de VPA de 4 Ramas descompone adicionalmente cada una de las componentes vectoriales de cuadratura y en fase de la señal en cuatro componentes de envolvente sustancialmente constante, dos para las componentes de señal en fase y dos para las de cuadratura. Este concepto se ilustra en la figura 4 usando una representación de señal fasorial.

En el ejemplo de la figura 4, los fasores  $\vec{I}_1$  e  $\vec{I}_2$  se corresponden con los fasores de parte real de una señal de envolvente compleja variable en el tiempo ejemplar en dos instantes de tiempo  $t_1$  y  $t_2$ , respectivamente. Se observa que los fasores  $\vec{I}_1$  e  $\vec{I}_2$  tienen diferentes magnitudes.

- 10 Haciendo de nuevo referencia a la figura 4, en el instante  $t_1$ , el fasor  $\vec{I}_1$  puede obtenerse mediante la suma de los fasores superior e inferior  $\vec{I}_{U_1}$  e  $\vec{I}_{L_1}$ . De forma similar, en el instante  $t_2$ , el fasor  $\vec{I}_2$  puede obtenerse mediante la suma de los fasores superior e inferior  $\vec{I}_{U_2}$  e  $\vec{I}_{L_2}$ . Se hace notar que los fasores  $\vec{I}_{U_1}$  e  $\vec{I}_{U_2}$  tienen una magnitud igual o sustancialmente igual. De forma similar, los fasores  $\vec{I}_{L_1}$  e  $\vec{I}_{L_2}$  tienen una magnitud sustancialmente igual. Por consiguiente, el fasor de parte real de la señal de envolvente variable en el tiempo puede obtenerse en cualquier instante de tiempo mediante la suma de por lo menos dos componentes de envolvente sustancialmente constante.

- 15 Los desplazamientos de fase de los fasores  $\vec{I}_{U_1}$  e  $\vec{I}_{L_1}$  en relación con  $\vec{I}_1$ , así como los desplazamientos de fase de los fasores  $\vec{I}_{U_2}$  e  $\vec{I}_{L_2}$  en relación con  $\vec{I}_2$ , se ajustan de acuerdo con la magnitud deseada de los fasores  $\vec{I}_1$  e  $\vec{I}_2$ , respectivamente. En un caso, cuando los fasores superior e inferior se seleccionan para que tengan una magnitud igual, los fasores superior e inferior se desplazan de forma simétrica en fase en relación con el fasor. Esto 20 se ilustra en el ejemplo de la figura 4, y se corresponde con  $\vec{I}_{U_1}$ ,  $\vec{I}_{L_1}$ ,  $\vec{I}_{U_2}$  e  $\vec{I}_{L_2}$  y teniendo todos una magnitud igual. En un segundo caso, el desplazamiento de fase de los fasores superior e inferior se desplazan, de forma sustancialmente simétrica, en fase en relación con el fasor. En base a la descripción en el presente documento, cualquier experto en la materia entenderá que la magnitud y el desplazamiento de fase de los fasores superior e inferior no tienen que ser exactamente iguales en cuanto a su valor

- 25 30 A modo de ejemplo, puede verificarse además que, para el caso que se ilustra en la figura 4, los desplazamientos de fase relativos, que se ilustran como  $\frac{\phi_1}{2}$  y  $\frac{\phi_2}{2}$  en la figura 4, están relacionados con las magnitudes de los fasores normalizados  $\vec{I}_1$  e  $\vec{I}_2$  tal como sigue:

$$\frac{\phi_1}{2} = \cot^{-1} \left( \frac{I_1}{2\sqrt{1 - \frac{I_1^2}{4}}} \right); \text{ y} \quad (2)$$

$$\frac{\phi_2}{2} = \cot^{-1} \left( \frac{I_2}{2\sqrt{1 - \frac{I_2^2}{4}}} \right), \quad (3)$$

- en las que  $\vec{I}_1$  e  $\vec{I}_2$  representan las magnitudes normalizadas de los fasores  $\vec{I}_1$  e  $\vec{I}_2$ , respectivamente, y en las que los dominios de  $I_1$  e  $I_2$  se restringen de forma apropiada de acuerdo con el dominio a través del cual la ecuación (2) y la (3) son válidas. Se hace notar que las ecuaciones (2) y (3) son una representación para relacionar los desplazamientos de fase relativos con las magnitudes normalizadas. Otras soluciones, representaciones equivalentes, y / o representaciones simplificadas de las ecuaciones (2) y (3) también pueden emplearse. También pueden usarse tablas de consulta que relacionan los desplazamientos de fase relativos con las magnitudes normalizadas.

- El concepto que se ha descrito en lo que antecede puede aplicarse de forma similar al fasor imaginario o la parte de componente de cuadratura de una señal  $r(t)$  tal como se ilustra en la figura 4. Por consiguiente, en cualquier instante de tiempo  $t$ , la parte de fasor  $\vec{Q}$  de la señal  $r(t)$  puede obtenerse mediante la suma de las componentes fasoriales superior e inferior  $\vec{Q}_U$  y  $\vec{Q}_L$  de una magnitud sustancialmente igual y constante. En este ejemplo,  $\vec{Q}_U$  y  $\vec{Q}_L$  se desplazan de forma simétrica en fase en relación con  $\vec{Q}$  un ángulo ajustado de acuerdo con la magnitud de  $Q$  en el instante  $t$ . Las relaciones de  $\vec{Q}_U$  y  $\vec{Q}_L$  con el fasor deseado  $\vec{Q}$  se relacionan tal como se define en las ecuaciones 2 y 3 mediante la sustitución por  $Q_1$  y  $Q_2$  de  $I_1$  e  $I_2$ , respectivamente.

A partir del análisis anterior se deduce que, en una representación fasorial, cualquier fasor  $\vec{R}$  de una magnitud y una fase variables puede construirse mediante la suma de cuatro componentes fasoriales de magnitud sustancialmente constante:

$$\begin{aligned} \vec{R} &= \vec{I}_U + \vec{I}_L + \vec{Q}_U + \vec{Q}_L; \\ \vec{I}_U + \vec{I}_L &= \vec{I}; \\ \vec{Q}_U + \vec{Q}_L &= \vec{Q}; \\ I_U &= I_L = \text{constante}; \\ Q_U &= Q_L = \text{constante}; \end{aligned} \quad (4)$$

- en los que  $I_U$ ,  $I_L$ ,  $Q_U$ , y  $Q_L$  representan las magnitudes de los fasores  $\vec{I}_U$ ,  $\vec{I}_L$ ,  $\vec{Q}_U$  y  $\vec{Q}_L$ , respectivamente.

De forma correspondiente, en el dominio del tiempo, una señal sinusoidal de envolvente compleja variable en el tiempo  $r(t) = R(t) \cos(\omega t + \phi)$  se construye mediante la suma de cuatro señales de envolvente constante tal como sigue:

$$\begin{aligned}

r(t) &= I_U(t) + I_L(t) + Q_U(t) + Q_L(t); \\

I_U(t) &= \text{sgn}(\vec{I}) \times I_U \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) + I_U \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t); \\

I_L(t) &= \text{sgn}(\vec{I}) \times I_L \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) - I_L \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t); \quad (5) \\

Q_U(t) &= -\text{sgn}(\vec{Q}) \times Q_U \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) + Q_U \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t); \\

Q_L(t) &= -\text{sgn}(\vec{Q}) \times Q_L \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) - Q_L \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t).

\end{aligned}$$

en las que  $\text{sgn}(\vec{I}) = \pm 1$  dependiendo de si  $\vec{I}$  se encuentra en fase o desfasada  $180^\circ$  grados con el eje real positivo.

De forma similar,  $\text{sgn}(\vec{Q}) = \pm 1$  dependiendo de si  $\vec{Q}$  se encuentra en fase o desfasada  $180^\circ$  grados con el eje imaginario.  $\frac{\phi_I}{2}$  se corresponde con el desplazamiento de fase de  $\vec{I}_U$  e  $\vec{I}_L$  en relación con el eje real. De forma

5 similar,  $\frac{\phi_Q}{2}$  se corresponde con el desplazamiento de fase de  $\vec{Q}_U$  y  $\vec{Q}_L$  en relación con el eje imaginario.  $\frac{\phi_I}{2}$  y

$\frac{\phi_Q}{2}$  pueden calcularse usando las ecuaciones dadas en (2) y (3).

Las ecuaciones (5) pueden simplificarse adicionalmente como:

$$\begin{aligned}

r(t) &= I_U(t) + I_L(t) + Q_U(t) + Q_L(t); \\

I_U(t) &= \text{sgn}(\vec{I}) \times I_{UX} \times \cos(\omega t) + I_{UY} \times \sin(\omega t); \\

I_L(t) &= \text{sgn}(\vec{I}) \times I_{UX} \times \cos(\omega t) - I_{UY} \times \sin(\omega t); \quad (6) \\

Q_U(t) &= -Q_{UX} \times \cos(\omega t) + \text{sgn}(\vec{Q}) \times Q_{UY} \times \sin(\omega t); \\

Q_L(t) &= Q_{UY} \times \cos(\omega t) - \text{sgn}(\vec{Q}) \times Q_{UX} \times \sin(\omega t).

\end{aligned}$$

en las que  $I_{UX} = I_U \times \cos\left(\frac{\phi_I}{2}\right) = I_L \times \cos\left(\frac{\phi_I}{2}\right)$ ,  $I_{UY} = I_U \times \sin\left(\frac{\phi_I}{2}\right) = I_L \times \sin\left(\frac{\phi_I}{2}\right)$ ,

10  $Q_{UX} = Q_U \times \sin\left(\frac{\phi_Q}{2}\right) = Q_L \times \sin\left(\frac{\phi_Q}{2}\right)$ , y  $Q_{UY} = Q_U \times \cos\left(\frac{\phi_Q}{2}\right) = Q_L \times \cos\left(\frac{\phi_Q}{2}\right)$ .

15 Puede entenderse por un experto en la materia que, mientras que las representaciones en el dominio del tiempo en las ecuaciones (5) y (6) se han proporcionado para el caso de una forma de onda sinusoidal, representaciones equivalentes pueden desarrollarse para las formas de onda no sinusoidales usando unas funciones base apropiadas. Además, tal como entendería un experto en la materia en base a las enseñanzas en el presente documento, la descomposición bidimensional que se ha descrito en lo que antecede en unas señales de envolvente sustancialmente constante pueden extenderse de forma apropiada para dar una descomposición multidimensional.

La figura 5 es un diagrama de bloques a modo de ejemplo de la VPA de 4 Ramas Cartesiana. Una señal de salida  $r(t)$  de un nivel de potencia, y de unas características de frecuencia, deseadas se genera a partir de las

componentes de cuadratura y en fase de banda de base de acuerdo con la VPA de 4 Ramas Cartesiana ejemplar.

En el ejemplo de la figura 5, un generador de frecuencias tal como un sintetizador 510 genera una señal de referencia  $A^* \cos(\omega t)$  511 que tiene la misma frecuencia que la de la señal de salida  $r(t)$  578. Puede entenderse por un experto en la materia que la elección de la señal de referencia se hace de acuerdo con la señal de salida deseada. Por ejemplo, si la frecuencia deseada de la señal de salida deseada es 2,4 GHz, entonces la frecuencia de la señal de referencia se ajusta para ser 2,4 GHz. De esta forma, puede conseguirse una conversión elevadora en frecuencia.

Haciendo referencia a la figura 5, uno o más divisores de fase se usan para generar las señales 521, 531, 541 y 551 en base a la señal de referencia 511. En el ejemplo de la figura 5, esto se hace usando los divisores de fase 512, 514 y 516 y mediante la aplicación de unos desplazamientos de fase de  $0^\circ$  en cada uno de los divisores de fase. Un experto en la materia apreciará, no obstante, que pueden usarse varias técnicas para generar las señales 521, 531, 541 y 551 de la señal de referencia 511. Por ejemplo, un divisor de fase de 1:4 puede usarse para generar las cuatro réplicas 521, 531, 541 y 551 en una única etapa o en el ejemplo de la figura 5, la señal 511 puede acoplarse directamente a las señales 521, 531, 541, 551. Dependiendo del ejemplo, una diversidad de desplazamientos de fase también pueden aplicarse para dar como resultado las señales deseadas 521, 531, 541 y 551.

Haciendo de nuevo referencia a la figura 5, cada una de las señales 521, 531, 541 y 551 se proporciona a un modulador vectorial 520, 530, 540 y 550 correspondiente, respectivamente. Los moduladores vectoriales 520, 530, 540 y 550, en conjunción con sus señales de entrada apropiadas, generan cuatro constituyentes de envolvente constante de la señal  $r(t)$  de acuerdo con las ecuaciones que se proporcionan en (6). En el ejemplo de la figura 5, los moduladores vectoriales 520 y 530 generan las componentes de  $I_U(t)$  y de  $I_L(t)$ , respectivamente, de la señal  $r(t)$ . De forma similar, los moduladores vectoriales 540 y 550 generan las componentes de  $Q_U(t)$  y de  $Q_L(t)$ , respectivamente, de la señal  $r(t)$ .

La implementación real de cada uno de los moduladores vectoriales 520, 530, 540 y 550 puede variar. Se entenderá por un experto en la materia, por ejemplo, que existen varias técnicas para generar las constituyentes de envolvente constante de acuerdo con las ecuaciones en (6).

En el ejemplo de la figura 5, cada uno de los moduladores vectoriales 520, 530, 540, 550 incluye un divisor de fase de entrada 522, 532, 542, 552 para desplazar en fase las señales 521, 531, 541, 551. Por consiguiente, los divisores de fase de entrada 522, 532, 542, 552 se usan para generar unas componentes en fase y de cuadratura o sus señales de entrada respectivas.

En cada modulador vectorial 520, 530, 540, 550, las componentes de cuadratura y en fase se multiplican con la información de amplitud. En la figura 5, por ejemplo, el multiplicador 524 multiplica la componente de cuadratura de la señal 521 con la información de amplitud de cuadratura  $I_{UY}$  de  $I_U(t)$ . En paralelo, el multiplicador 526 multiplica la señal de réplica en fase con la información de amplitud en fase  $\text{sgn}(I) \times I_{UX}$  de  $I_U(t)$ .

Para generar las señales de constituyente de envolvente constante de  $I_U(t)$  525 y 527 se suman usando el divisor de fase 528 o técnicas de suma alternativas. La señal resultante 529 se corresponde con la componente de  $I_U(t)$  de la señal  $r(t)$ .

De una forma similar a como se ha descrito en lo que antecede, los moduladores vectoriales 530, 540 y 550, respectivamente, generan las componentes de  $I_L(t)$ , de  $Q_U(t)$  y de  $Q_L(t)$  de la señal  $r(t)$ .  $I_L(t)$ ,  $Q_U(t)$  y  $Q_L(t)$ , respectivamente, se corresponden con las señales 539, 549 y 559 en la figura 5.

Además, tal como se ha descrito en lo que antecede, las señales 529, 539, 549 y 559 se caracterizan por tener unas envolventes sustancialmente iguales y constantes. Por consiguiente, cuando las señales 529, 539, 549 y 559 se introducen en los amplificadores de potencia (PA) 562, 564, 566 y 568 correspondientes, las señales amplificadas 563, 565, 567 y 569 correspondientes son unas señales de envolvente sustancialmente constante.

Los amplificadores de potencia 562, 564, 566 y 568 amplifican cada una de las señales 529, 539, 549, 559, respectivamente. En un ejemplo, una amplificación de potencia sustancialmente igual se aplica a cada una de las señales 529, 539, 549 y 559. En un ejemplo, el nivel de amplificación de potencia de los PA 562, 564, 566 y 568 se ajusta de acuerdo con el nivel de potencia deseado de la señal de salida  $r(t)$ .

Haciendo de nuevo referencia a la figura 5, las señales amplificadas 563 y 565 se suman usando el sumador 572 para generar una versión amplificada 573 de la componentes en fase  $\overset{\rightarrow}{I}(t)$  de la señal  $r(t)$ . De forma similar, las señales amplificadas 567 y 569 se suman usando el sumador 574 para generar una versión amplificada 575 de la componente de cuadratura  $\overset{\rightarrow}{Q}(t)$  de la señal  $r(t)$ .

Las señales 573 y 575 se suman usando el sumador 576, tal como se muestra en la figura 5, correspondiéndose la señal resultante con la señal de salida deseada  $r(t)$ .

Se hace notar que, en el ejemplo de la figura 5, los sumadores 572, 574 y 576 se están usando solo para fines de ilustración. Pueden usarse varias técnicas para sumar las señales amplificadas 563, 565, 567 y 569. Por ejemplo, la totalidad de las señales amplificadas 563, 565, 567 y 569 pueden sumarse en una etapa para dar como resultado la señal 578. De hecho, de acuerdo con varios ejemplos de VPA, es suficiente con que la suma se haga después de la amplificación. Determinados ejemplos de VPA, tal como se describirá adicionalmente en lo que sigue, usan técnicas de suma con unas pérdidas mínimas tal como un acoplamiento directo a través de hilo. Como alternativa, determinados ejemplos de VPA usan técnicas de combinación de potencia convencionales. En otros ejemplos, tal como se describirá adicionalmente en lo que sigue, los amplificadores de potencia 562, 564, 566 y 568 pueden implementarse como un amplificador de potencia de múltiples entradas y de una única salida.

10 El funcionamiento de la VPA de 4 Ramas Cartesiana ejemplar se describirá adicionalmente a continuación con referencia al diagrama de flujo de proceso de la figura 6. El procedimiento comienza en la etapa 610, que incluye recibir la representación de banda de base de la señal de salida deseada. Esto comporta recibir las componentes en fase (I) y de cuadratura (Q) de la señal de salida deseada. En otro ejemplo, esto comporta recibir la magnitud y la fase de la señal de salida deseada. En el ejemplo de VPA de 4 Ramas Cartesiana, las I y Q son unas componentes 15 de banda de base. En otro ejemplo, las I y Q son unas componentes de RF y se les aplica una conversión reductora a la banda de base.

La etapa 620 incluye recibir una señal de reloj ajustada de acuerdo con una frecuencia de señal de salida deseada de la señal de salida deseada. En el ejemplo de la figura 5, la etapa 620 se consigue mediante la recepción de la señal de referencia 511.

20 La etapa 630 incluye el procesamiento de la componente de I para generar unas señales primera y segunda que tienen la frecuencia de señal de salida. Las señales primera y segunda tienen unas envolventes de magnitud sustancialmente constante e igual y una suma igual a la componente de I. Las señales primera y segunda se corresponden con las constituyentes de envolvente constante de  $I_U(t)$  y de  $I_L(t)$  que se han descrito en lo que antecede. En el ejemplo de la figura 5, la etapa 630 se consigue mediante los moduladores vectoriales 520 y 530, en 25 conjunción con sus señales de entrada apropiadas.

La etapa 640 incluye el procesamiento de la componente de Q para generar unas señales tercera y cuarta que tienen la frecuencia de señal de salida. Las señales tercera y cuarta tienen unas envolventes de magnitud sustancialmente constante e igual y una suma igual a la componente de Q. Las señales tercera y cuarta se corresponden con las constituyentes de envolvente constante de  $Q_U(t)$  y de  $Q_L(t)$  que se han descrito en lo que antecede. En el ejemplo de la figura 5, la etapa 630 se consigue mediante los moduladores vectoriales 540 y 550, en 30 conjunción con sus señales de entrada apropiadas.

35 La etapa 650 incluye amplificar de forma individual cada una de las señales primera, segunda, tercera y cuarta, y sumar las señales amplificadas para generar la señal de salida deseada. En un ejemplo, la amplificación de las señales primera, segunda, tercera y cuarta es sustancialmente igual y conforme a un nivel de potencia deseado de la señal de salida deseada. En el ejemplo de la figura 5, la etapa 650 se consigue mediante los amplificadores de 40 potencia 562, 564, 566 y 568 que amplifican las señales 529, 539, 549 y 559 respectivas, y mediante los sumadores 572, 574 y 576 que suman las señales amplificadas 563, 565, 567 y 569 para generar la señal de salida 578.

La figura 7A es un diagrama de bloques que ilustra una realización ejemplar de un amplificador de potencia vectorial 700 que implementa el diagrama de flujo de proceso 600 de la figura 6. En el ejemplo de la figura 7A, los 45 componentes opcionales se ilustran con unas líneas discontinuas. En otras realizaciones, pueden ser opcionales unos componentes adicionales.

El amplificador de potencia vectorial 700 incluye una rama en fase (I) 703 y una rama de cuadratura (Q) 705. Cada una de las ramas de I y de Q comprende además una primera rama y una segunda rama.

45 La señal de información en fase (I) 702 se recibe mediante un módulo de función de transferencia de datos de I 710. En una realización, la señal de información de I 702 incluye una señal de banda de base digital. En una realización, el módulo de función de transferencia de datos de I 710 muestrea la señal de información de I 702 de acuerdo con un reloj de muestreo 706. En otra realización, la señal de información de I 702 incluye una señal de banda de base analógica, que se convierte a digital usando un convertidor de analógico a digital (ADC) (que no se muestra en la figura 7A) antes de introducirse en el módulo de función de transferencia de datos de I 710. En otra realización, la señal de información de I 702 incluye una señal de banda de base analógica que se introduce de forma analógica en el módulo de función de transferencia de datos de I 710, que también incluye circuitería analógica. En otra realización, la señal de información de I 702 incluye una señal de RF a la que se le aplica una conversión reductora a la banda de base antes de introducirse en el módulo de función de transferencia de datos de I 710 usando cualquiera de las realizaciones que se han descrito en lo que antecede.

55 El módulo de función de transferencia de datos de I 710 procesa la señal de información de I 702, y determina la información de amplitud de cuadratura y en fase de por lo menos dos señales de constituyente de envolvente constante de la señal de información de I 702. Como se ha descrito en lo que antecede con referencia a la figura 5, la información de amplitud de modulador vectorial de cuadratura y en fase se corresponde con  $\text{sgn}(I) \times I_{UX}$  e  $I_{UY}$ ,

respectivamente. El funcionamiento del módulo de función de transferencia de datos de I 710 se describe adicionalmente en lo que sigue en la sección 3.4.

El módulo de función de transferencia de datos de I 710 emite las señales de información 722 y 724 que se usan para controlar las componentes de amplitud de cuadratura y en fase de los moduladores vectoriales 760 y 762. En una realización, las señales 722 y 724 son señales digitales. Por consiguiente, cada una de las señales 722 y 724 se suministra, respectivamente, a un convertidor de digital a analógico (DAC) 730 y 732 correspondiente. La resolución y la tasa de muestreo de los DAC 730 y 732 se selecciona para conseguir la componente de I deseada de la señal de salida 782. Los DAC 730 y 732 se controlan por las señales de reloj de DAC 723 y 725, respectivamente. Las señales de reloj de DAC 723 y 725 pueden calcularse a partir de una misma señal de reloj o pueden ser independientes.

En otra realización, las señales 722 y 724 son unas señales analógicas, y los DAC 730 y 732 no se requieren.

En la realización exemplar de la figura 7A, los DAC 730 y 732 convierten las señales de información digital 722 y 724 en las señales analógicas correspondientes, e introducen estas señales analógicas en los filtros de interpolación opcionales 731 y 733, respectivamente. Los filtros de interpolación 731 y 733, que también sirven como filtros antisolape, conforman las salidas de los DAC para producir la forma de onda de salida deseada. Los filtros de interpolación 731 y 733 generan las señales 740 y 742, respectivamente. La señal 741 representa la inversa de la señal 740. Las señales 740 - 742 se introducen en los moduladores vectoriales 760 y 762.

Los moduladores vectoriales 760 y 762 multiplican las señales 740 - 742 con unas señales de reloj desplazadas en fase de la forma apropiada para generar unas constituyentes de envolvente constante de la señal de información de I 702. Las señales de reloj se calculan a partir de una señal de reloj de canal 708 que tiene una tasa de acuerdo con una frecuencia de señal de salida deseada. Una pluralidad de divisores de fase, tal como 750 y 752, por ejemplo, y los fasores asociados con los multiplicadores de modulador vectorial, pueden usarse para generar las señales de reloj desplazadas en fase de la forma apropiada.

En la realización de la figura 7A, por ejemplo, el modulador vectorial 760 modula una señal de reloj de canal desplazada 90° con la señal de información de amplitud de cuadratura 740. En paralelo, el modulador vectorial 760 modula una señal de reloj de canal en fase con la señal de información de amplitud en fase 742. El modulador vectorial 760 combina las dos señales moduladas para generar una primera constituyente de envolvente constante modulada 761 de la señal de información de I 702. De forma similar, el modulador vectorial 762 genera una segunda constituyente de envolvente constante modulada 763 de la señal de información de I 702, usando las señales 741 y 742. Las señales 761 y 763 se corresponden, respectivamente, con las componentes de envolvente constante de  $I_U(t)$  y de  $I_L(t)$  que se describen con referencia a la figura 5.

En paralelo y de una forma similar, la rama de Q del amplificador de potencia vectorial 700 genera por lo menos dos señales de constituyente de envolvente constante de la señal de información de cuadratura (Q) 704.

En la realización de la figura 7A, por ejemplo, el modulador vectorial 764 genera una primera constituyente de envolvente constante 765 de la señal de información de Q 704, usando las señales 744 y 746. De forma similar, el modulador vectorial 766 genera una segunda constituyente de envolvente constante 767 de la señal de información de Q 704, usando las señales 745 y 746.

Como se ha descrito en lo que antecede con respecto a la figura 5, las señales de constituyente 761, 763, 765 y 767 tienen unas envolventes sustancialmente iguales y constantes. En la realización exemplar de la figura 7A, las señales 761, 763, 765 y 767 se introducen, respectivamente, en los amplificadores de potencia (PA) 770, 772, 774 y 776 correspondientes. Los PA 770, 772, 774 y 776 pueden ser unos amplificadores de potencia lineales o no lineales. En una realización, los PA 770, 772, 774 y 776 incluyen unos amplificadores de potencia con comutación.