# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 496 446

61 Int. Cl.:

G11C 11/16 (2006.01) G11C 5/08 (2006.01) G11C 5/02 (2006.01) H01L 27/02 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 10.10.2011 E 11773945 (8)

(97) Fecha y número de publicación de la concesión europea: 09.07.2014 EP 2625689

- (54) Título: Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme

- (30) Prioridad:

#### 08.10.2010 US 901074

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 19.09.2014

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) 5775 Morehouse Drive San Diego, CA 92121, US

(72) Inventor/es:

LEE, KANGHO; KIM, TAE HYUN; LI, XIA; KIM, JUNG PILL y KANG, SEUNG H.

(74) Agente/Representante:

CARPINTERO LÓPEZ, Mario

#### **DESCRIPCIÓN**

Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme

#### Campo técnico

La presente divulgación se refiere, en general, al campo de las memorias de acceso aleatorio magnéticas (MRAM). Más en concreto, la presente divulgación se refiere a unos procedimientos y a unos aparatos para fabricar dispositivos de MRAM.

#### **Antecedentes**

5

10

15

20

25

30

35

40

45

50

55

A diferencia de las técnicas de chip de memoria de acceso aleatorio (RAM) convencionales, en la RAM magnética (MRAM) los datos no son almacenados como carga eléctrica sino que, en su lugar, son almacenados por polarización magnética de los elementos de almacenamiento. Los elementos de almacenamiento están formados a partir de dos capas ferromagnéticas separadas por una capa de tunelización. Una de las dos capas presenta al menos una polarización magnética de espiga (o capa fija) fijada a una polaridad concreta. La polaridad magnética de la otra capa magnética (o capa libre) es alterada para representar o bien un "1" (por ejemplo, antiparalela a la capa fija) o bien un "0" (por ejemplo, paralela a la capa fija). Un dispositivo de este tipo que incorpora una capa fija, una capa de tunelización y una capa sobre es una unión túnel magnética (MTJ). La resistencia eléctrica de la MTJ depende de la polaridad magnética de la capa libre en comparación con la polaridad magnética de la capa fija. Un dispositivo de memoria, como por ejemplo una MRAM está construida a partir de una matriz de MTJs dirigibles individualmente.

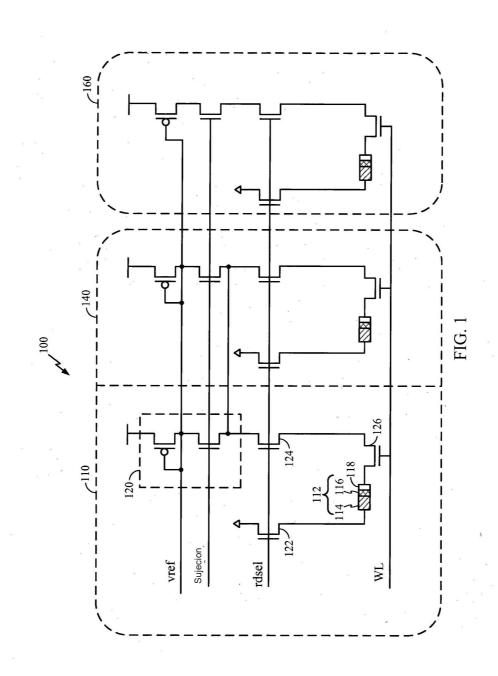

La FIGURA 1 es un circuito esquemático que ilustra una porción de una memoria de acceso aleatorio magnética (MRAM) convencional. Una MRMA 100 está dividida en una pluralidad de células binarias 110, 140, 160. Durante la lectura de la célula binaria 160, la resistencia de la célula binaria 160 es comparada con la célula binaria 110 paralela de referencia y con la célula binaria 140 antiparalela de referencia. La resistencia de las células binarias 110, 140, 160 se mide aplicando una tensión primaria y determinando una cantidad de corriente que fluye a través de las células binaras 110, 140, 160. Por ejemplo, en la célula binaria 110, una tensión primaria 120 es aplicada a una unión túnel magnética (MTJ) 112 mediante unos transistores 122, 124 de selección de lectura y un transistor 126 de selección de línea de palabra. La MTJ 112 incluye una capa 114 fija, una capa 116 de tunelización y una capa 118 libre. Cuando la capa 118 libre y la capa 114 fija incorporan magnetizaciones alineadas sustancialmente en paralelo, la resistencia de la MTJ 112 y con ello de la célula binaria 110, es baja. Cuando la capa 118 libre y la capa 114 fija incorporan magnetizaciones alineadas sustancialmente antiparalelas, la resistencia de la MTJ 112 y con ello de la célula binaria 110, es alta.

Las células binarias de una memoria de acceso aleatorio magnética pueden estar dispuestas en una o más matrices que incluyan un patrón de elementos de memoria (por ejemplo, una MTJ en el caso de la MRAM). Con el fin de obtener unas matrices de memoria de alto rendimiento, es fundamental controlar estrictamente el tamaño de los elementos de memoria. Las técnicas de diseño anteriores para implementar matrices de memoria a gran escala han resultado lastradas por el efecto de macrocarga que es inherente al procedimiento de ataque al ácido. Por ejemplo, la tasa de ataque al ácido de los elementos de memoria puede ser mayor en el borde de las matrices en comparación con el centro de las matrices porque la densidad de los patrones es menor en el borde. Como resultado de ello, el tamaño de una MTJ en el borde de un bloque de matriz unitario puede diferir sustancialmente del tamaño de una MTJ cerca del centro del bloque de la matriz. Esto puede provocar la reducción de los rendimientos de producción.

La estructuración de un gran número de células de memoria de tamaño uniforme en una matriz de memoria a gran escala, como por ejemplo una matriz de MRAM puede proporcionar una densidad de patrones uniformes en un área relativamente amplia y puede incrementar los rendimientos obtenidos. El efecto de macrocarga se puede reducir disponiendo unas matrices a gran escala de células de memoria de tamaño uniforme para que un gran número de células de memoria se aloje en áreas de densidad de patrones uniformes después del ataque al ácido. Sin embargo, diversos condicionamientos y problemas de diseño han lastrado el desarrollo de matrices de MRAM a gran escala con una densidad de patrones uniforme.

Los procedimientos anteriormente propuestos para proporcionar matrices de MRAM a gran escala no han proporcionado el emplazamiento de unas líneas o conjuntos de circuitos de distribución de señales dentro de las matrices de memoria. Las líneas de distribución de señales como por ejemplo una banda de línea de palabra (WL) y son necesarias en diseños prácticos, por ejemplo para proporcionar circuitos de señales de baja resistencia a células binarias situadas dentro de una pluralidad de submatrices de células binarias. Se puede utilizar un conjunto de circuitos de intensificación simple de las señales en lugar de la banda metálica. Así mismo, se pueden colocar ligaduras de sustratos periódicamente dentro de las matrices de memoria para proporcionar la conexión masiva de los transistores de acceso dispuestos en las células binarias. En general, la anchura de la banda metálica de la WL y de las ligaduras de los sustratos se reducen al mínimo con las normas de diseño aplicables para ahorrar área.

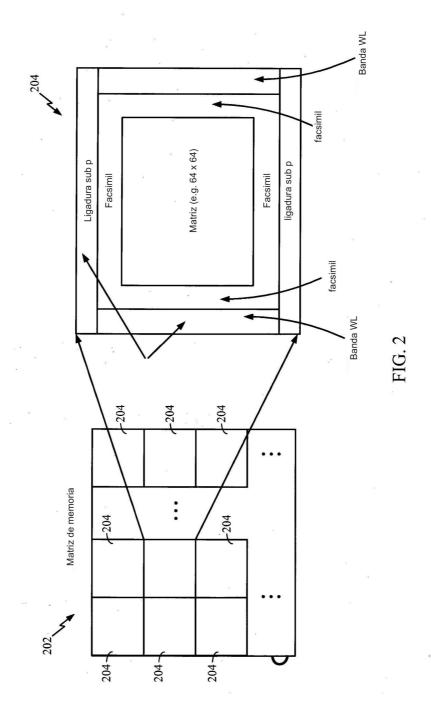

Un procedimiento de provisión del emplazamiento de las líneas de distribución de señales en una matriz de memoria a gran escala se describe con referencia a la FIGURA 2. La matriz 202 de memoria a gran escala se divide en una

pluralidad de submatrices 204 cada una de las cuales incluye un patrón de células binarias de 64 x 64, por ejemplo. Para compensar el efecto de macrocarga en el borde de cada submatriz se puede situar una pluralidad de células binaras ficticias alrededor del perímetro de cada submatriz 204. Estas células binarias ficticias pueden incluir unas células de memoria no funcionales, como por ejemplo unas MTJs flotantes que no estén conectadas al conjunto de circuitos de control de la memoria. Sin embargo, la banda metálica de la línea de palabras y de las ligaduras de sustrato puede ocupar áreas que no incluyan MTJs.

En la FIGURA 2, las líneas o conjunto de circuitos de distribución de señales provocan discontinuidades del patrón que afectan a la densidad global del patrón de la matriz. Debido a que las matrices a gran escala incluyen un gran número de submatrices relativamente pequeñas, este procedimiento genera un gran número de discontinuidades del patrón para acomodar el emplazamiento de las líneas de distribución de señales, como por ejemplo las ligaduras del sustrato o la banda metálica de la WL. Aunque el aumento del número de células ficticias puede mitigar este problema, este sistema no es práctico desde el punto de vista económico porque las múltiples líneas de células ficticias dispuestas en las submatrices incrementarían drásticamente el número total de chips. Por lo tanto, en las matrices de memoria de la práctica, se puede colocar el número mínimo de células de memoria ficticias, y su tamaño puede ser relativamente mayor que el de las células de memoria activas dispuestas dentro de las submatarices 204 para compensar el efecto de carga intenso en los bordes de las submatrices. Sin embargo, este sistema a menudo se traduce en una degradación considerable de la uniformidad del patrón.

La construcción de matrices de memoria a gran escala con una densidad de patrón uniforme a lo largo de ellas ha sido sugerida para reducir el efecto de macrocarga e incrementar los rendimientos de fabricación. Dichas sugerencias no han conseguido dar respuesta a los diversos condicionamientos de diseño y no han suministrado un procedimiento para la colocación de la banda metálica de la WL o de las ligaduras del sustrato, por ejemplo.

El documento US 2005/237791 se refiere a un dispositivo de memoria magnética de gran capacidad en el que el campo magnética para la escritura es casi uniforme para todos los elementos de la memoria. Se lleva a cabo reduciendo la deformación del patrón de la capa protectora que se produce en fotolitografía cuando los patrones de fotomáscara están en íntima proximidad unos respecto de otros.

#### **Breve sumario**

5

10

15

20

25

30

35

40

45

50

55

Aspectos de la presente divulgación incluyen una matriz de memoria a gran escala que incluye un patrón uniforme de elementos de memoria. Submatrices dentro de la matriz de memoria a gran escala están separadas por líneas o conjuntos de circuitos de distribución de señales, como por ejemplo la banda de línea de palabra (WL) y de ligaduras de sustrato. En formas de realización ilustrativas, una ligadura de sustrato puede ser un contacto metálico con un sustrato de la matriz de memoria. Por ejemplo, en un semiconductor - metal - óxido de canal n (NMOS), el sustrato puede ser de tipo p y estar conectado a tierra (Vss). En un MOS de canal p (PMOS), el sustrato (pozo n en el procedimiento MOS complementario) puede ser cualquier tipo n y estar conectado a la fuente de energía (Vdd). La banda de WL puede ser una pila de conducción metálica que conecte, por ejemplo, con las múltiples puertas de la memoria a gran escala.

Las células de la configuración de la unidad para las líneas o conjunto de circuitos de distribución de señales (células de distribución de señales) están conformadas con una anchura o una altura correspondiente a la anchura o a la altura de las células binarias activas dispuestas dentro de las submatrices. Así, las células de distribución de señales ocupan un área que tiene el mismo volumen total que las células binarias activas. Esto permite la colocación de elementos de memoria ficticios en las células de distribución de señales sin distorsionar la uniformidades del patrón a través de las matrices, lo que, a su vez, impide las discontinuidades del patrón de los elementos de memoria a través de la matriz a gran escala. En este caso, no se requieren células binarias ficticias con elementos de memoria ficticios de mayor tamaño, lo que puede conducir a la reducción del tamaño total de la célula binaria.

Dado que la uniformidad del patrón de las MTJs se mantiene a través de las submatrices, no se requieren células binarias ficticias con los elementos de memoria ficticios de gran tamaño. Sin embargo, las células binarias ficticias pueden también ser situadas en submatrices para otros fines, por ejemplo, para proporcionar facsímeles de transistor. En este caso, los elementos de memoria ficticios dispuestos dentro de las células binarias ficticias deben ser los mismos que los elementos de la memoria activos.

Las células ficticias de borde de tamaño similar o mayor que las células de memoria de tamaño estándar pueden ser situadas alrededor del borde de la matriz a gran escala para eliminar el efecto de macrocarga en los bordes.

Un aspecto de la presente divulgación proporciona un aparato que incluye un patrón de células binarias adyacentes de tamaño uniforme en una matriz de memoria y en un conjunto de circuitos de distribución de señales configurados para ofrecer un volumen total del patrón coincidente con un volumen total de una pluralidad de células binarias. En una forma de realización ilustrativa, la anchura del conjunto de circuitos de distribución de señales coincide con un número entero de las anchuras de las células binarias de tamaño uniforme. El aparato incluye una pluralidad de células binarias activas por fuera del volumen total del conjunto de circuitos de distribución de señales. Un elemento de memoria resistivo, como por ejemplo una unión túnel magnética está configurado en cada una de las células binarias activas.

De acuerdo con aspectos de la presente divulgación, el aparato puede incluir una pluralidad de submatrices de las células binarias activas separada de las células binarias ficticias. Al menos una de las submatrices puede estar rodeada por el conjunto de circuitos de distribución de señales. El conjunto de circuitos de distribución de señales está acoplado a los dígitos binarios activos de la pluralidad de submatrices. El conjunto de circuitos de distribución de señales puede incluir una banda metálica de línea de palabra que se extienda en una primera dimensión del patrón y una ligadura de sustrato que se extienda en una segunda dimensión del patrón.

De acuerdo con otro aspecto de la presente divulgación, una pluralidad de células ficticias de borde se extiende alrededor de un perímetro de la matriz de memoria a gran escala. Las células ficticias de borde pueden incluir elementos de memoria de tamaño uniforme o elementos de memoria mayores que los elementos de memoria de tamaño uniforme.

La matriz de memoria a gran escala que incluye unos elementos de memoria del patrón separados de manera uniforme de acuerdo con la presente divulgación, puede estar integrada en una memoria de acceso aleatorio magnética (MRAM). En una forma de realización ilustrativa, la matriz de memoria puede estar integrada, por ejemplo, en un teléfono móvil, un descodificador, un reproductor de música, un reproductor de vídeo, una unidad de esparcimiento, un dispositivo de navegación, un ordenador, una unidad de sistemas de comunicación personal (PCS), una unidad de datos portátil, o una unidad de datos de emplazamiento fijo.

Otro aspecto de la presente divulgación incluye un procedimiento de formación de una matriz de memoria a gran escala. El procedimiento incluye la formación de un patrón de células binarias adyacentes de tamaño uniforme dispuestas en una matriz de memoria y la formación de un conjunto de circuitos de distribución de señales que incorpore un volumen total del patrón que coincida con un volumen total de una pluralidad de células binarias. En una forma de realización ilustrativa, el conjunto de circuitos de distribución de señales está conformado con una anchura que coincide con un número entero de las anchuras de las células binarias de tamaño uniforme.

Otro aspecto de la presente divulgación incluye un procedimiento de formación de una matriz de memoria a gran escala. El procedimiento incluye las etapas de formación de un patrón de células binarias adyacentes de tamaño uniforme dispuestas en una matriz de memoria y la formación de un conjunto de circuitos de distribución de señales que presenta un volumen total del patrón que coincide con un volumen total de una pluralidad de células binarias.

Un aparato de acuerdo con otro aspecto de la presente divulgación incluye unos medios para la formación de un patrón de células binarias adyacentes de tamaño uniforme dispuestas en una matriz de memoria y unos medios de formación de un conjunto de circuitos de distribución de señales que presenta un volumen total del patrón que coincide con un volumen total de una pluralidad de células binarias.

Hasta aquí se ha esbozado, bastante grosso modo, las características distintivas y las ventajas técnicas de la presente divulgación con el fin de que la descripción detallada que sigue pueda ser mejor comprendida. Características distintivas y ventajas adicionales de la divulgación se describirán en las líneas que siguen. Se debe apreciar por parte de los expertos en la materia que la presente divulgación puede ser fácilmente utilizada como base para la modificación o diseño de otras estructuras para desarrollar los mismos fines de la presente divulgación. Se debe entender también por parte de los expertos en la materia que dichas construcciones equivalentes no se apartan de las enseñanzas de la divulgación según se definen en las reivindicaciones adjuntas. Las características novedosas, que se consideran características distintivas de la divulgación, tanto en cuanto a su organización como a su procedimiento operativo, junto con objetos y ventajas adicionales, serán comprendidos de forma más acabada a partir de la descripción subsecuente cuando se conjuguen con las figuras que se acompañan. Se debe entender expresamente, sin embargo, que cada una de las figuras se ofrece únicamente con fines ilustrativos y descriptivos y su finalidad no consiste en ofrecer una definición de los límites de la presente divulgación.

# Breve descripción de los dibujos

Para una comprensión más acabada de la presente divulgación, en las líneas que siguen se hace referencia a la 45 descripción subsecuente tomada en combinación con los dibujos que se acompañan.

> La FIGURA 1 es un circuito esquemático que ilustra una porción de una memoria de acceso aleatorio magnética (MRAM) convencional.

> La FIGURA 2 es un diagrama de bloques que muestra una matriz de memoria MRAM a gran escala de acuerdo con la TÉCNICA ANTERIOR.

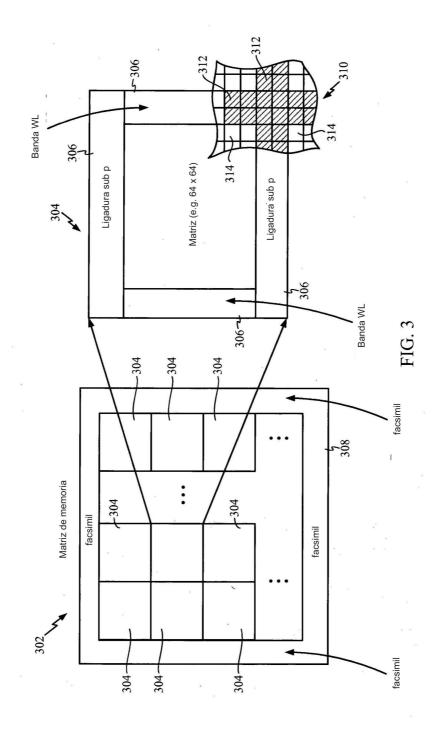

> La FIGURA 3 es un diagrama de bloques que muestra una memoria MRAM a gran escala de acuerdo con un aspecto de la presente divulgación.

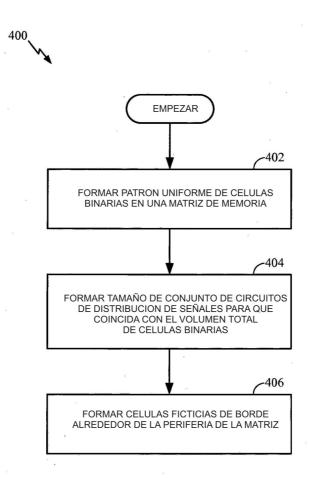

> La FIGURA 4 es un diagrama de flujo que ilustra un procedimiento de formación de la MRAM ejemplar de acuerdo con una forma de realización.

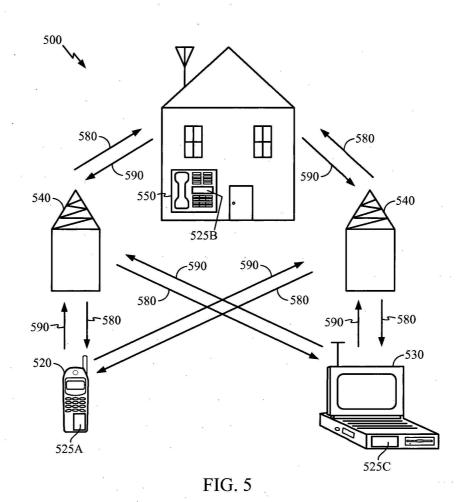

> La FIGURA 5 es un diagrama de bloques que muestra un sistema de comunicación inalámbrica ejemplar en el que una forma de realización de la divulgación puede ser ventajosamente empleada.

55

50

5

10

15

20

25

30

35

40

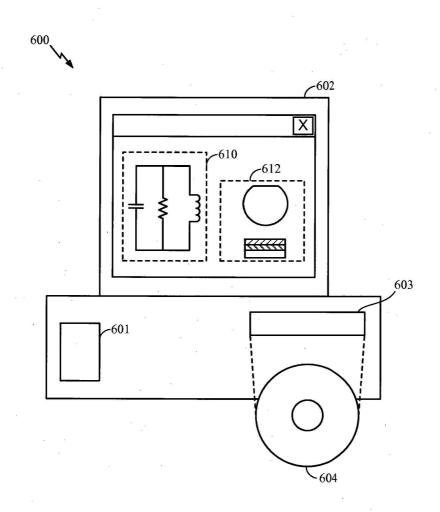

La FIGURA 6 es un diagrama de bloques que ilustra una estación de trabajo de diseño utilizada para un circuito, una configuración y un diseño lógicos de un componente semiconductor de acuerdo con una forma de realización.

#### Descripción detallada

20

25

40

45

50

55

- Aspectos de la presente divulgación se refieren a una matriz de memoria a gran escala que incluye un patrón uniforme de células binarias. Una matriz de memoria a gran escala de acuerdo con un aspecto de la presente divulgación se describe con referencia a la FIGURA 3. La matriz 302 de memoria a gran escala está dividida en una pluralidad de submatrices 304 cada una de las cuales incluye un patrón de células binarias 310. En el ejemplo mostrado en la FIGURA 3, cada submatriz incluye células binarias de 64 x 64, por ejemplo.

- Para conseguir espacio para el conjunto de circuitos de distribución de señales, por ejemplo una banda metálica de línea de palabra y unas ligaduras de sustrato, se sitúa una pluralidad de células binarias ficticias 312 alrededor del perímetro de cada submatriz 304. Las células binarias ficticias 312 pueden incluir células binarias no funcionales, como por ejemplo células binarias con MTJs que no estén conectadas al conjunto de circuitos de control de memoria. Cada una de las submatrices 304 dispuestas dentro de la matriz 302 de memoria a gran escala están por tanto separadas por un área de células ficticias 312 en la cual cada una de las células binarias ficticias 312 presenta la mismas dimensiones que las células binarias activas 314 dispuestas dentro de las submatrices.

De acuerdo con la presente divulgación, el conjunto de circuitos 306 de distribución de señales, como por ejemplo una banda metálica de línea de palabra y unas ligaduras de sustrato están formadas con una anchura o una altura correspondientes a la anchura o a la altura de las células binarias ficticias 312 para que el conjunto de circuitos de distribución de señales ocupe el mismo volumen total que el área de las células binarias ficticias 312. Las células binarias ficticias 312 presentan el mismo tamaño y patrón uniforme que las células binarias activas 314, de forma que el patrón uniforme de las células binarias a través de la matriz 302 a gran escala no resulta interrumpido por el emplazamiento del conjunto de circuitos 306 de distribución de señales. Las células 314 de memoria activas dispuestas en las submatrices 304 a uno o ambos lados del conjunto de circuitos 306 de distribución de señales. En una forma de realización ilustrativa, la banda metálica de línea de palabra está formada sobre una capa metálica inferior, como por ejemplo la capa Metal-2 de unmolde de metal - óxido - semiconductor complementario (CMOS).

Aspectos de la presente divulgación ajustan el tamaño del volumen total del conjunto de circuitos de distribución de señales, incluyendo el volumen total de las ligaduras de sustrato y de la banda metálica de línea de palabra de una matriz de MRAM para acomodar las MTJs ficticias con el mismo tamaño que las MTJs sin romper la uniformidad de patrón de las MTJs. Incrementando la anchura de la banda metálica de línea de palabra desde la anchura de diseño mínima hasta aproximadamente una anchura igual a la de una célula binaria, o a una anchura de células binarias múltiples integrales, no son necesarias células ficticias con MTJs mayores. Ello reduce el área global de la matriz en comparación con diseños de matriz de MRAM anteriores. De modo similar, la altura de las ligaduras del sustrato puede ser incrementada a partir de una anchura de diseño mínimo hasta igualar la altura de una célula binaria o las alturas de múltiples células binarias integrales. Este procedimiento mantiene la uniformidad de patrón de la MTJ a través de una matriz de memoria de gran tamaño (por ejemplo, un banco de 0,25 Mb) y pude reducir el área de una matriz de memoria a gran escala hasta aproximadamente un 3%.

De acuerdo con un aspecto de la presente divulgación, las células ficticias de borde con MTJs ficticias grandes pueden estar situadas alrededor de la matriz 308 de memoria a gran escala, en la que se rompa la uniformidad del patrón de MTJs. Un gran número de células ficticias de borde puede ser situado para asegurar la uniformidad de patrón de las MTJs en los bordes sin incrementar considerablemente el tamaño global de la matriz.

De acuerdo con los diversos aspectos de la presente divulgación, las configuraciones de la unidad para las líneas o conjunto de circuitos de distribución de señales presentan dimensiones que son números enteros de las células binarias activas. Esto sitúa las MTJs ficticias dentro del conjunto de circuitos de distribución de señales sin perturbar la uniformidad de patrón de la memoria a través de las submatrices. Estos elementos de patrón ficticios presentan el mismo tamaño que los elementos de memoria activos.

De acuerdo con aspectos de la presente divulgación, es innecesario situar células binarias ficticias con elementos de memoria ficticios de gran tamaño alrededor de células binarias activas en cada submatriz para compensar el efecto de macrocarga de los bordes. Estas células binarias ficticias no se requieren porque la uniformidad de patrón se mantiene a través de la matriz de memoria de gran tamaño. La eliminación de las inmediaciones de las células binarias activas de estas células binarias ficticias en cada submatriz de acuerdo con la presente divulgación puede conducir a un tamaño de dígito binario más pequeño. Sin embargo, las células binarias ficticias pueden ser situadas con otros fines, como por ejemplo facsímiles de transistor. En este caso, los elementos de memoria ficticios de las células binarias ficticias tienen la misma dimensión que los elementos de memoria activos.

Sin embargo, los elementos de memoria activos situados en los bordes de una matriz de gran memoria resultarán afectados por el efecto de microcarga. Por lo tanto, todavía puede ser necesario colocar elementos de memoria ficticios en los bordes de la matriz de gran tamaño. Las múltiples líneas de los elementos de memoria ficticios

pueden ser situadas sin incrementar sustancialmente el tamaño de dígito binario. El tamaño de estos elementos de memoria ficticios puede ser igual o mayor que el de los elementos de memoria activos.

La FIGURA 4 es un diagrama de flujo que ilustra un procedimiento 400 de formación de una memoria a gran escala de acuerdo con un aspecto de la presente divulgación. El procedimiento 400 incluye la formación de un patrón de células binarias adyacentes de tamaño uniforme en una matriz de memoria en el bloque 402 y la formación de un conjunto de circuitos de distribución de señales con un volumen total dentro del patrón, coincidente con un volumen total de una pluralidad de células binarias dispuestas en el bloque 404. En una forma de realización ilustrativa, el procedimiento 400 puede también incluir la formación de una pluralidad de células ficticias de borde que se extienda alrededor de un perímetro de la matriz de la memoria en el bloque 406.

5

45

50

55

60

La FIGURA 5 es un diagrama de bloques que muestra un sistema 500 de comunicaciones inalámbricas ejemplar, en el que se puede emplear, de modo ventajoso, un elemento de la divulgación. Con fines ilustrativos, la FIGURA 5 muestra tres unidades 520, 530 y 550 distantes y dos estaciones 540 de base. Se advertirá que los sistemas de comunicaciones inalámbricas pueden incorporar muchas más unidades distantes y estaciones de base. Las unidades 520, 530 y 550 distantes incluyen unos dispositivos 525A, 525C y 525B de CI, que incluyen la MRAM divulgada. Se advertirá que otros dispositivos pueden también incluir la MRAM divulgada, como por ejemplo las estaciones de base, los dispositivos de conmutación y el equipamiento de red. La FIGURA 5 muestra unas señales 580 de enlace directo desde la estación 540 de base hasta las unidades 520, 530, y 550 distantes y unas señales 590 de enlace inverso desde las unidades 520, 530 y 550 distantes hasta las estaciones 540 de base.

En la FIGURA 5, la unidad 520 distante se muestra en forma de teléfono móvil, la unidad 530 distante se muestra en forma de ordenador portátil y la unidad 550 distante se muestra en forma de unidad distante de emplazamiento fijo en un sistema de bucle local inalámbrico. Por ejemplo, las unidades distantes pueden ser teléfonos móviles, unidades de sistemas de comunicaciones personales (PCS), portátiles, unidades de datos portátiles, como por ejemplo asistentes personales de datos, dispositivos habilitados para el GPS, dispositivos de navegación, descodificadores, reproductores de música, reproductores de vídeo, unidades de esparcimiento, unidades de datos de emplazamiento fijo, como por ejemplo un equipamiento de medición de lectura, o cualquier otro dispositivo que almacene o recupere datos de instrucciones de ordenador, o cualquier combinación de estos. Aunque la FIGURA 5 ilustra unidades distantes de acuerdo con las enseñanzas de la divulgación, la divulgación no está limitada a estas unidades ejemplares ilustradas. Formas de realización de la divulgación se pueden emplear de forma apropiada en cualquier dispositivo que incluya la MRAM.

La FIGURA 6 es un diagrama de bloques que ilustra una estación de trabajo de diseño utilizada para un circuito una configuración y un diseño lógico de un componente semiconductor, como por ejemplo una MRAM según lo divulgado con anterioridad. Una estación de trabajo 600 de diseño incluye un disco duro 601 que contiene un software de sistema operativo, unos archivos de soporte y un software de diseño, como por ejemplo Cadence o OrCAD. La estación de trabajo 600 de diseño, así mismo, incluye una pantalla para facilitar el diseño de un circuito 610 o de un componente 612 de semiconductor, como por ejemplo un circuito integrado empaquetado que incorpore la MRAM. Un medio 604 de almacenamiento está dispuesto para almacenar de manera tangible el diseño 610 de circuito o el componente 612 de semiconductor. El diseño 610 de circuito o el circuito 612 de semiconductor puede ser almacenado en el medio 604 de almacenamiento en un formato de archivo, como por ejemplo GDSII o GERBER. El medio 604 de almacenamiento puede ser un CD-ROM, un DVD, un disco duro, una memoria flash u otro dispositivo deseado. Así mismo, la estación de trabajo 600 de diseño incluye un aparato 603 de unidad para aceptar la entrada procedente de o la salida de escritura hacia el medio 604 de almacenamiento.

Los datos registrados en el medio 604 de almacenamiento pueden especificar configuraciones de circuitos lógicos, datos de patrones para máscaras fotolitográficas o datos de patrones de máscaras para herramientas de escritura en serie como una litografía de haces de electrones. Los datos pueden, así mismo, incluir datos de verificación lógicos, como por ejemplo diagramas de temporización o circuitos de red asociados con simulaciones lógicas. La provisión de datos al medio 604 de almacenamiento facilita el diseño del diseño 610 de circuito o del componente 612 conductor reduciendo el número de procesos para diseñar obleas de semiconductor.

Para una implementación firmware y / o software, los procedimientos pueden ser implementados con módulos (por ejemplo, procedimientos, funciones, etc.) que lleven a cabo las funciones descritas en la presente memoria. Cualquier medio legible por ordenador que incorpore de modo tangible instrucciones puede ser utilizado para implementar los procedimientos descritos en la presente memoria. Por ejemplo, unos códigos software pueden ser almacenados en la memoria y ejecutados por una unidad de procesador. Una memoria puede ser implementada dentro de la unidad de procesador o por fuera de la unidad de procesador. Según se utiliza en la presente, el término "memoria" se refiere a cualquier tipo de memoria a largo plazo, a corto plazo, volátil, no volátil o de otro tipo y no está limitado a ningún tipo concreto de memoria o pluralidad de memorias o tipo de medios en los cuales esté almacenada.

Si se implementan en firmware y / o software, las funciones pueden ser almacenadas como una o más instrucciones o un código dispuesto sobre un medio legible por ordenador. Ejemplos de estos medios incluyen medios legibles por ordenador modificados por una estructura de datos y unos medios legibles por ordenador modificados por un programa informático. En los medios legibles por ordenador incluyen unos medios de almacenamiento informático o

físicos. Un medio de almacenamiento puede ser cualquier medio disponible al que se pueda acceder por un ordenador. A modo de ejemplo, y no de limitación, dichos medios legibles por ordenador pueden incluir una RAM, una ROM, una EEPROM, un CD-ROM, u otro almacenamiento de disco óptico, almacenamiento de disco magnético, u otros dispositivos de almacenamiento magnéticos, o cualquier otro medio que pueda ser utilizado para almacenar el código de programa deseado bajo la forma de instrucciones o estructuras de datos y al que se pueda acceder por un ordenador; los términos disk (disco magnético) y disc (disco óptico), según se utilizan en la presente memoria, incluyen el disco compacto (CD), disco láser, disco óptico, disco versátil digital (DVD), disco flexible y disco blueray en los que los disks generalmente reproducen datos magnéticamente, mientras que los discs reproducen datos ópticamente con láseres. Combinaciones de los medios expuestos pueden también ser incluidos dentro del alcance de los medios legibles por ordenador.

Además del almacenamiento en el medio legible por ordenador pueden disponerse instrucciones y / o datos en forma de señales en medios de transmisión incluidos en un aparato de comunicaciones. Por ejemplo, un aparato de comunicaciones puede incluir un transceptor que incorpore unas señales indicativas de instrucciones y datos. Las instrucciones y los datos están configurados para hacer que uno o más procesadores implementen las funciones definidas en las reivindicaciones.

Aunque se ha analizado un conjunto de circuito específico, se debe apreciar por los expertos en la materia que no todos los conjuntos de circuitos divulgados son necesarios para llevar a la práctica la divulgación. Además, determinados circuitos sobradamente conocidos no han sido descritos, para mantener el foco sobre la divulgación.

Aunque la presente divulgación y sus ventajas han sido descritas con detalle, se debe entender que pueden llevarse a cabo en la presente memoria, diversos cambios, sustituciones y alteraciones sin apartarse del método de la divulgación según se define mediante las reivindicaciones adjuntas. Por ejemplo los términos relacionales, como por ejemplo "encima" y "debajo" son utilizados con respecto a un sustrato o dispositivo electrónico. Por supuesto si el sustrato o dispositivo electrónico es invertido, encima se convierte en debajo y viceversa. Así mismo, si la orientación es lateral, encima y debajo pueden referirse a los lados de un sustrato y dispositivo electrónico. Así mismo, el alcance de la presente solicitud no pretende quedar limitado a las formas de realización concretas del procedimiento, máquina, manufactura, composición de materia, medios, procedimientos y etapas descritos en la memoria descriptiva. Como apreciará sin dificultad el experto en la materia la divulgación, los procesos, las máquinas, la manufactura o las composiciones de materia, los medios los procedimientos o las etapas existentes en la actualidad o que se desarrollen en el futuro que lleven sustancialmente a cabo la misma función o consigan sustancialmente el mismo resultado que las correspondientes formas de realización descritas en la presente memoria, pueden ser utilizados de acuerdo con la presente divulgación. Por consiguiente, las reivindicaciones adjuntas pretenden incluir dentro de su alcance dichos procesos, máquinas, manufacturas, composiciones de materia, medios, procedimientos o etapas.

#### REIVINDICACIONES

1.- Una matriz (302) de memoria, que comprende:

un patrón de células binarias (314) adyacentes de tamaño uniforme; y

#### caracterizado por comprender:

5

10

35

40

45

- un conjunto de circuitos (306) de distribución de señales configurado para ofrecer un área con un volumen total coincidente con un volumen total de un número entero de las células binarias (314) de tamaño uniforme.

- 2.- La matriz (302) de memoria de la reivindicación 1, en la que las células binarias (314) adyacentes de tamaño uniformen comprenden una pluralidad de células binarias (314) activas situadas fuera del volumen total del conjunto de circuitos (306) de distribución de señales.

- 3.- La matriz (302) de memoria de la reivindicación 2, que comprende:

un elemento de memoria resistivo configurado en cada una de las células binarias (314) activas.

4.- La matriz (302) de memoria de la reivindicación 2, que comprende:

una unión túnel magnética configurada en cada una de las células binarias (314) activas.

- 5.- La matriz (302) de memoria de la reivindicación 2, en la que las células binarias (314) adyacentes de tamaño uniforme comprenden una pluralidad de células binarias ficticias (312) dentro del volumen total del conjunto de circuitos (306) de distribución de señales.

- 6.- La matriz (302) de memoria de la reivindicación 2, en la que el conjunto de circuitos de distribución de señales está acoplado a las células binarias (314) activas.

- 20 7.- La matriz (302) de memoria de la reivindicación 1, en la que el conjunto de circuitos (306) de distribución de señales, comprende:

una banda metálica de línea de palabra que se extiende en una primera dimensión del patrón; o

al menos una ligadura de sustrato que se extiende en una segunda dimensión del patrón.

- 8.- La matriz (302) de memoria de la reivindicación 1, que comprende además una pluralidad de células (314) ficticias de borde que se extiende alrededor de un perímetro de la matriz (302) de memoria.

- 9.- La matriz (302) de memoria de la reivindicación 8, en la que las células ficticias de borde comprenden una pluralidad de células binarias (314) de tamaño uniforme.

- 10.- La matriz (302) de memoria de la reivindicación 8, en la que las células ficticias de borde comprenden unas células ficticias de mayor tamaño que las células binarias (314) de tamaño uniforme.

- 30 11.- La matriz (302) de memoria de la reivindicación 1, integrada en una memoria de acceso aleatorio magnética, MRAM.

- 12.- La matriz (302) de memoria de la reivindicación 1, integrada en al menos un elemento de entre un teléfono móvil, un descodificador, un reproductor de música, un reproductor de vídeo, una unidad de esparcimiento, un dispositivo de navegación, un ordenador, una unidad de sistemas de comunicaciones personales, PCS, portátil, una unidad de datos portátil y una unidad de datos de emplazamiento fijo.

- 13.- Un procedimiento, que comprende:

la formación de un patrón de células binarias (314) adyacentes de tamaño uniforme en una matriz (302) de memoria, y **caracterizado por**

la formación de un conjunto de circuitos (306) de distribución de señales en un área que presenta un volumen total del patrón coincidente con un patrón total de un número entero de las células binarias (314) uniforme.

14.- El procedimiento de la reivindicación 13, que comprende:

la integración de la matriz (302) de memoria en al menos un elemento de entre un teléfono móvil, un descodificador, un reproductor de música, un reproductor de vídeo, una unidad de esparcimiento, un dispositivo de navegación, un ordenador, una unidad de sistemas de comunicaciones personales (PCS) portátil, una unidad de datos portátil y una unidad de datos de emplazamiento fijo.

# 15.- Un aparato, que comprende:

un medio para formar un patrón de células binarias (314) adyacentes de tamaño uniforme en una matriz (302) de memoria; y

# caracterizado por comprender

un medio para formar un conjunto de circuitos (306) de distribución de señales en un área que presenta un volumen total del patrón coincidente con un volumen total de un número entero de las células binarias (314) de tamaño uniforme.

10

5

FIG. 4

FIG. 6