# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 507 075

51 Int. Cl.:

G11C 5/06 (2006.01)

G11C 7/02 (2006.01)

G11C 7/10 (2006.01)

G11C 11/4093 (2006.01)

H04L 25/02 (2006.01)

H03H 7/38 (2006.01)

(12)

#### TRADUCCIÓN DE PATENTE EUROPEA

T3

- Fecha de presentación y número de la solicitud europea: 06.06.2008 E 08757205 (3)

Fecha y número de publicación de la concesión europea: 25.06.2014 EP 2171844

- (54) Título: Control de impedancia dinámica para memorias intermedias de entrada/salida

- (30) Prioridad:

08.06.2007 US 942798 P

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 14.10.2014

(73) Titular/es:

CONVERSANT INTELLECTUAL PROPERTY MANAGEMENT INC. (100.0%) 390 March Road, Suite 100 Ottawa, ON K2K 0G7, CA

(72) Inventor/es:

MILLAR, BRUCE

74 Agente/Representante:

**CURELL AGUILÁ, Mireia**

#### **DESCRIPCIÓN**

Control de impedancia dinámica para memorias intermedias de entrada/salida.

#### 5 Campo de la invención

La invención se refiere al control de impedancia para memorias intermedias de entrada/salida.

#### Antecedentes de la invención

10

15

20

25

30

35

40

45

50

55

60

65

Los Controladores de Memorias para Memorias Dinámicas Síncronas de Acceso Aleatorio (SDRAM) se usan en Ordenadores Personales y en una amplia variedad de productos de electrónica, en general, donde, en el producto, se integran microprocesadores y SDRAM para definir las características de control y la interfaz de usuario del producto. Los Controladores de Memorias de SDRAM permiten que los microprocesadores accedan eficientemente a SDRAM de alta velocidad cuando se ejecutan programas.

A medida que los fabricantes de chips reducen inexorablemente el tamaño característico (feature size) de los procesos que involucran silicio, llevando la tecnología del silicio hacia un rendimiento eléctrico y económico cada vez mejor, surgen importantes problemas de integridad de las señales en la interfase física entre chips en aplicaciones de sistemas, en la medida en la que las velocidades de los relojes y los datos con frecuencia se duplican con cada nueva generación. A velocidades más altas del reloj la integridad de la señal se deteriora, principalmente, debido a efectos de la línea de transmisión en la interconexión entre el chip controlador de memorias y el chip de SDRAM.

Los efectos de la línea de transmisión, que incluyen reflexiones, atenuación, interferencia cruzada y el rebote de masa (ground bounce), juegan todos ellos un papel en el deterioro de la calidad de la señal en la interconexión entre chips. Las reflexiones en la interconexión de un chip con otro, si no se gestionan correctamente, pueden destruir de forma completa la integridad de la señal en cualquier sistema de alta velocidad.

Todas las líneas de transmisión tienen una impedancia característica y una velocidad característica de la señal, que quedan definidas por la geometría de los conductores y la constante dieléctrica del medio aislante que rodea los conductores. Las reflexiones de la señal que se propagan de un lado a otro a través de líneas de transmisión pueden deteriorar la calidad de la señal hasta el punto de no resultar viables si no se controlan. No obstante, en una línea de transmisión no se producen reflexiones de la señal si la impedancia de fuente del circuito que excita un extremo de la línea de transmisión y la impedancia de terminación de circuitos en el otro extremo de la línea coinciden con la impedancia característica de la línea de transmisión. Cuando se usan circuitos de semiconductores, típicamente transistores CMOS (metal óxido semiconductor complementario), para llevar señales fuera del chip sobre pistas de placas de circuito impreso (PCB), que serán recibidas por circuitos de semiconductores en otros chips de la placa de circuito impreso, con frecuencia se producen reflexiones significativas de la señal si los extremos de recepción de las pistas no terminan con alguna impedancia que coincida fuertemente con la impedancia de la línea de transmisión.

Con anterioridad, las señales de alta velocidad se excitaban con memorias intermedias de I/O (Entrada/Salida) que presentaban impedancias de salida que eran muy inferiores a la impedancia característica de la pista de la PCB. Las pistas de la PCB se terminaban usando resistores fijos con valores de resistencia que coincidían con la impedancia característica de la pista. En algunas aplicaciones, se colocaban además resistores fijos en serie con la memoria intermedia de excitación para mejorar la integridad de la señal. La llegada de la SDRAM de DDR (Doble Velocidad de Datos) incentivó la industria de los semiconductores para encontrar formas de incorporar en su interior impedancias de fuente y de terminación con el fin de prescindir de los resistores externos fijos necesarios para igualar las impedancias de las pistas de la PCB en estos nuevos sistemas de memoria. La motivación consiste siempre en disminuir los costes y reducir el consumo de potencia. Se demostró claramente que se puede obtener una buena integridad de la señal en sistemas de Memorias de DDR cuando se dispone de una impedancia de terminación adaptada. Mientras la terminación absorba la señal que se propaga hasta el final de la línea, no se producirán reflexiones. En estos sistemas, la impedancia de fuente de los circuitos que excitan la línea se materializó intencionadamente de manera que fuera inferior a la impedancia característica de las pistas de la PCB con el fin de producir una mayor excursión de la señal con vistas a obtener una mejor inmunidad al ruido.

Se pueden diseñar circuitos de I/O CMOS de manera que se adapten a las impedancias de la línea de transmisión bastante bien en condiciones específicas aunque presentando grandes variaciones de impedancia, que superan frecuentemente la relación 2:1, durante el intervalo completo de Procesos, Voltajes y Temperaturas (PVT) esperado para el circuito. Para contrarrestar la variación de PVT, los diseñadores de circuitos han venido incorporando cierta adaptabilidad para la Excitación Fuera del Chip (Off-Chip Drive) (OCD) y la Terminación En el Dado (On-Die Termination) (ODT).

El documento US 2007/0126467 A1 describe un dispositivo para terminación en el dado y sugiere la provisión de, entre otros, una unidad de control para activar selectivamente una pluralidad de señales *pull-up* y una pluralidad de señales *pull-down* y la provisión de una unidad *pull-up*/*pull-down* para excitar selectivamente una pluralidad de

excitadores de *pull-up* y una pluralidad de excitadores de *pull-down* de acuerdo con las señales *pull-up* y las señales *pull-down* con el fin de dar salida a una resistencia correspondiente del terminal de salida en un modo de funcionamiento de lectura.

- A partir del documento US 2007/0126466 A1 se conoce un dispositivo de semiconductores para ajustar una impedancia de salida de un excitador de salida de datos. Basándose en una comparación de una señal de prueba y una señal de referencia aplicadas en un terminal (en inglés, "pad") de prueba y en mediciones de impedancia, se ajusta una impedancia de un terminal de entrada/salida de datos.

- El documento US 2004/0183565 A1 se refiere a un aparato para su uso en calidad tanto de excitador fuera del chip como de circuito de terminación en el dado del chip. Un circuito de función dual permite excitar una señal desde una línea de señal sobre una línea de transmisión y terminar señales entrantes de la línea de transmisión.

- En la actualidad se están usando varias soluciones para una impedancia de salida programable, especialmente en aplicaciones de Lógica de Transceptores de Alta Velocidad (HSTL) y de DDR. En muchos casos, para el control de la impedancia de salida se dispone de hasta solamente dos configuraciones de excitación. En muchos casos, las impedancias de salida no se ajustan dinámicamente con respecto a una referencia de impedancia.

- Sigue existiendo la necesidad de un circuito combinado más eficiente de excitación y terminación.

#### Sumario

20

35

40

La invención proporciona una solución de acuerdo con las reivindicaciones independientes.

- Según un amplio aspecto, la invención proporciona un circuito combinado de excitación y terminación que comprende: una red de *pull-up* de impedancia variable; una red de *pull-down* de impedancia variable; por lo menos una entrada de control para ajustar una configuración de la red de *pull-up*; por lo menos una entrada de control para ajustar una configuración de la red de *pull-down*; presentando el aparato un modo de funcionamiento de terminación en el cual la red de *pull-up* de impedancia variable está configurada para presentar una impedancia de terminación de red de *pull-up* y la red de *pull-down* de impedancia variable está configurada para presentar una impedancia de terminación de red de *pull-down*, funcionando la red de *pull-up* y la red de *pull-down* en combinación como una terminación dividida; presentando el aparato un modo de funcionamiento de excitación en el cual: para excitar una salida alta, la red de *pull-up* está configurada para generar una impedancia específica cuando se activa; para excitar una salida baja, la red de *pull-down* está configurada para generar una impedancia específica cuando se activa.

- En algunas formas de realización, un aparato comprende: lógica central; una pluralidad de I/O (entradas/salidas), presentando cada una de ellas un terminal respectivo de I/O; para cada I/O, un circuito combinado respectivo de excitación y terminación según se ha resumido anteriormente; funcionando los circuitos combinados de excitación y terminación de manera que generan salidas desde la lógica central y actúan como terminación para entradas externas para la lógica central.

- En algunas formas de realización, las redes de *pull-up* y *pull-down* se conmutan dinámicamente entre dos configuraciones de impedancia cuando cambian entre los modos de excitación y de terminación.

- 45 En algunas formas de realización, el aparato comprende además: para cada I/O, lógica de pre-excitador que comprende lógica AND-OR-AND, que recibe una primera entrada para indicar un nivel alto de excitación, una segunda entrada para indicar un nivel bajo de excitación, y una tercera entrada para indicar terminación, y conmuta entre dos configuraciones de impedancia en consecuencia.

- 50 En algunas formas de realización, el circuito en combinación con una lógica de calibración que calibra las impedancias con respecto a una referencia de impedancia.

- En algunas formas de realización, un aparato comprende: lógica central; una pluralidad de entradas que presentan, cada una de ellas, un terminal de entrada respectivo, y una pluralidad de salidas que presentan, cada una de ellas, un terminal de salida respectivo; para cada terminal de entrada, un circuito combinado respectivo de excitación y terminación, según se ha resumido anteriormente, configurado permanentemente para estar en modo de terminación; para cada terminal de salida, un circuito combinado respectivo de excitación y terminación, según se ha resumido anteriormente, configurado permanentemente para estar en modo de excitación.

- 60 En algunas formas de realización, un aparato comprende: el circuito combinado de excitación y terminación según se ha resumido anteriormente; un controlador que genera las entradas de control en función de si el circuito combinado de excitación y terminación está en un modo de excitación o un modo de terminación.

- En algunas formas de realización, la red de *pull-up* comprende una pluralidad de transistores conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de *pull-up* mediante la activación selectiva de cierto número de la pluralidad de transistores; la red de *pull-down* comprende una pluralidad de

transistores conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de *pull-down* mediante la activación selectiva de cierto número de la pluralidad de transistores.

En algunas formas de realización, un aparato comprende: el circuito combinado de excitación y terminación según se ha resumido anteriormente; una réplica de por lo menos parte del circuito combinado de excitación y terminación para su uso en la ejecución de la calibración.

En algunas formas de realización, el aparato comprende además: un controlador que controla la calibración que se está llevando a cabo en cuatro etapas: 1) calibración de la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto; 2) calibración de la red de *pull-down* para el modo de excitación cuando una salida de datos es un nivel lógico bajo; 3) calibración de la red de *pull-up* para el modo de terminación; y 4) calibración de la red de *pull-down* para el modo de terminación.

10

45

50

55

60

65

En algunas formas de realización, la red de *pull-up* comprende una pluralidad de transistores mosfet de tipo P, y la red de *pull-down* comprende una pluralidad de transistores mosfet de tipo N, comprendiendo además el aparato un controlador que controla la calibración que se está llevando a cabo en cuatro etapas: 1) calibración de la impedancia de salida de dispositivos N para determinar cuántos de los transistores de tipo N habilitar para el modo de excitación cuando una salida de datos es un nivel lógico bajo; 2) calibración de la impedancia de salida de dispositivos P para determinar cuántos de los transistores de tipo P habilitar para el modo de excitación cuando una salida de datos es un nivel lógico alto; 3) calibración de terminación de dispositivos N para determinar cuántos de los transistores de tipo N habilitar para el modo de terminación de dispositivos P para determinar cuántos de los transistores de tipo P habilitar para el modo de terminación.

En algunas formas de realización, la red de *pull-up* y la red de *pull-down* se forman, cada una de ellas, en su totalidad, con transistores de tipo P o transistores de tipo N, comprendiendo además el aparato: un controlador que controla la calibración que se está llevando a cabo en dos etapas: 1) calibración de la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto; y 2) calibración de la red de *pull-up* para el modo de terminación.

30 En algunas formas de realización, la red de *pull-up* comprende una pluralidad de transistores mosfet de tipo N, y la red de *pull-down* comprende una pluralidad de transistores mosfet de tipo N, comprendiendo además el aparato un controlador que controla la calibración que se está llevando a cabo en dos etapas: 1) calibración de la impedancia de salida de dispositivos N para determinar cuántos de los transistores de tipo N habilitar para el modo de excitación cuando una salida de datos es un nivel lógico bajo; 2) calibración de la terminación de dispositivos N para determinar cuántos de los transistores de tipo N habilitar para la terminación.

En algunas formas de realización, el aparato comprende además: interconexiones que trasladan valores de calibración comunes a cada circuito combinado de excitación y terminación.

40 En algunas formas de realización, las interconexiones entregan los valores de calibración usando uno o más códigos unarios.

En algunas formas de realización, la red de *pull-up* comprende transistores de tipo P, y la red de *pull-down* comprende transistores de tipo N, y en donde las interconexiones entregan: un primer valor de calibración que establece cuántos de los transistores de tipo N habilitar para el modo de excitación cuando una salida de datos es un nivel lógico bajo; un segundo valor de calibración que establece cuántos de los transistores de tipo P habilitar para el modo de excitación cuando una salida de datos es un nivel lógico alto; un tercer valor de calibración que establece cuántos de los transistores de tipo N habilitar para el modo de terminación; y un cuarto valor de calibración que establece cuántos de los transistores de tipo P habilitar para el modo de terminación.

En algunas formas de realización, un aparato comprende: una pluralidad de circuitos combinados de excitación y terminación según se ha resumido anteriormente; interconexiones que trasladan valores de calibración comunes a cada circuito combinado de excitación y terminación; para cada circuito combinado de excitación y terminación, un circuito de pre-excitador que aplica selectivamente uno de los valores de calibración en función de si el circuito combinado particular de excitación y terminación está en modo de excitación dando salida a un nivel lógico bajo o dando salida a un nivel lógico alto, o en modo de terminación.

Según una forma de realización, la invención proporciona un circuito combinado de ODT (terminación en el dado) y de OCD (excitación fuera del chip) que comprende transistores de excitación que hacen las veces de transistores de terminación.

Según otra forma de realización, la invención proporciona un circuito de terminación en el chip, que comprende: por lo menos un transistor *pull-up* conectado a por lo menos un transistor *pull-down*; una entrada conectada entre el transistor *pull-up* y el transistor *pull-down*, funcionando el por lo menos un transistor *pull-down* y el por lo menos un transistor *pull-down* para actuar como terminación de la entrada.

En algunas formas de realización, el por lo menos un transistor *pull-up* comprende una primera pluralidad de transistores que se pueden habilitar de manera seleccionable, y el por lo menos un transistor *pull-down* comprende una segunda pluralidad de transistores que se pueden habilitar de manera seleccionable, de modo que el número de la primera y la segunda pluralidades de transistores que se habilitan establece una impedancia de terminación del circuito.

Según otro aspecto amplio, la invención proporciona un método de provisión de excitación y terminación combinadas, comprendiendo el método: en un modo de funcionamiento de terminación, configurar una red de *pull-up* de impedancia variable para tener una impedancia de terminación de la red de *pull-down*, funcionando la red de *pull-up* y la red de *pull-down* en combinación como una terminación dividida; en un modo de funcionamiento de excitación, para excitar una salida alta, configurar la red de *pull-up* para generar una primera impedancia de excitación; en el modo de funcionamiento de excitación, para excitar una salida baja, configurar la red de *pull-down* para generar una segunda impedancia de excitación.

En algunas formas de realización, el método comprende además: seleccionar el modo de funcionamiento entre el modo de terminación y el modo de excitación.

En algunas formas de realización, la configuración de la red de *pull-up* para tener una impedancia de terminación *pull-up* comprende activar selectivamente cierto número de una pluralidad de transistores que forman la red de *pull-up*; la configuración de la red de *pull-down* para tener una impedancia de terminación *pull-down* comprende activar selectivamente cierto número de una pluralidad de transistores que forman la red de *pull-down*.

En algunas formas de realización, el método comprende además: llevar a cabo una calibración para calibrar la impedancia de terminación *pull-up*, la impedancia de terminación *pull-down*, la primera impedancia de excitación y la segunda impedancia de excitación.

En algunas formas de realización, llevar a cabo la calibración comprende: calibrar la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto; calibrar la red de *pull-down* para el modo de excitación cuando una salida de datos es un nivel lógico bajo; calibrar la red de *pull-up* para el modo de terminación; y calibrar la calibración de la red de *pull-down* para el modo de terminación.

En algunas formas de realización, llevar a cabo la calibración comprende: calibrar la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto con el fin de producir un primer resultado de calibración; usar el primer resultado de calibración para calibrar la red de *pull-down* para el modo de excitación cuando una salida de datos es un nivel lógico bajo; calibrar la red de *pull-up* para el modo de terminación con el fin de producir un segundo resultado de calibración; usar el segundo resultado de calibración para calibrar la red de *pull-down* para el modo de terminación.

#### 40 Breve descripción de los dibujos

10

15

30

35

50

A continuación se describirán formas de realización de la invención en referencia a los dibujos adjuntos, en los cuales:

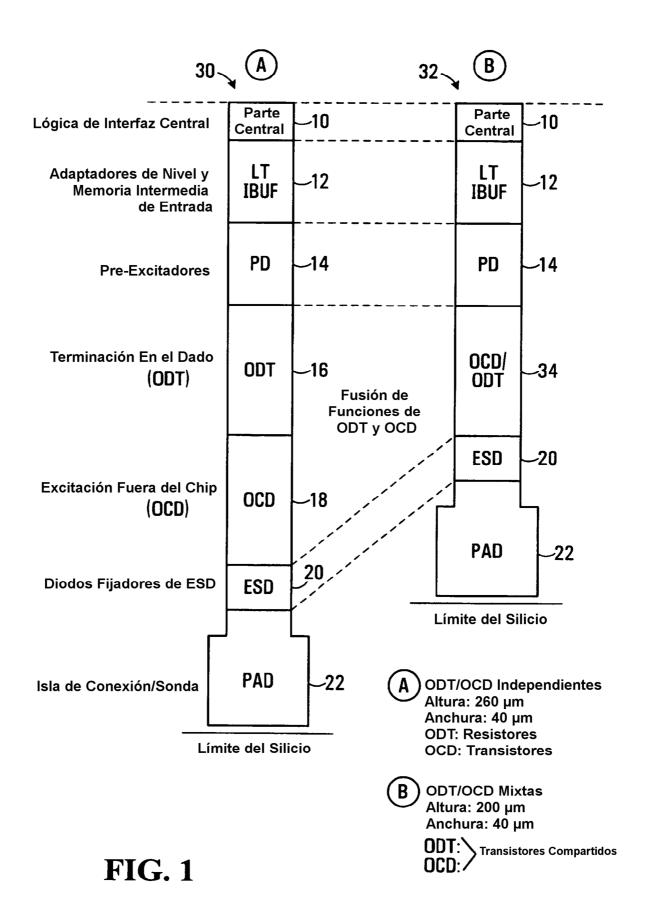

- la Figura 1 es un plano de planta que compara una arquitectura celular convencional con una arquitectura celular proporcionada por una forma de realización de la invención;

- la Figura 2A es un diagrama de bloques de una excitación en el chip/terminación en el dado fusionadas, proporcionadas por una forma de realización de la invención;

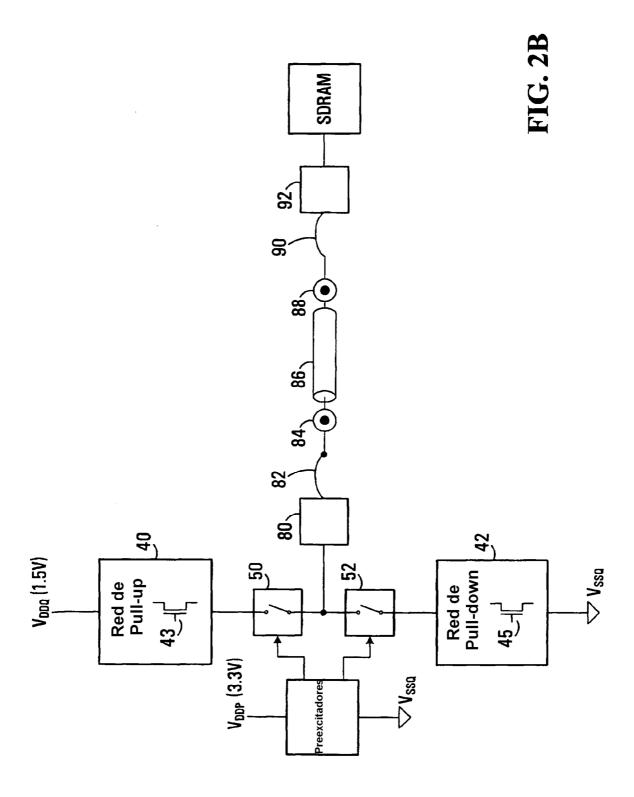

- la Figura 2B es un diagrama de bloques de una excitación en el chip/terminación en el dado fusionadas, proporcionadas por una forma de realización de la invención, adecuadas para aplicaciones de velocidad de datos cuádruple:

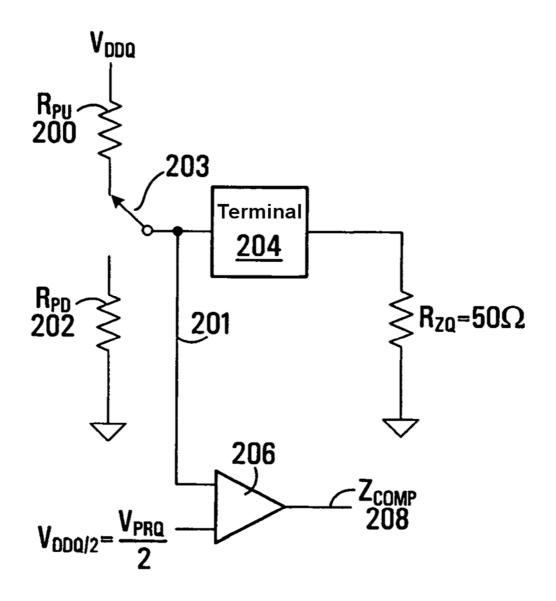

- la Figura 2C es un diagrama de circuito que ilustra cómo puede llevarse a cabo la calibración;

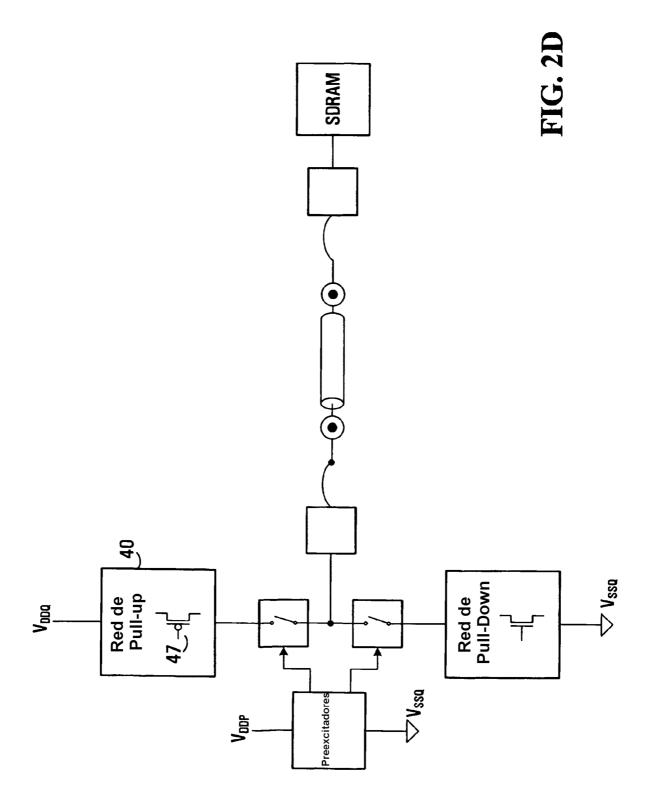

- la Figura 2D es un diagrama de bloques de una excitación en el chip/terminación en el dado fusionadas, proporcionadas por una forma de realización de la invención, adecuadas para aplicaciones de DDR3;

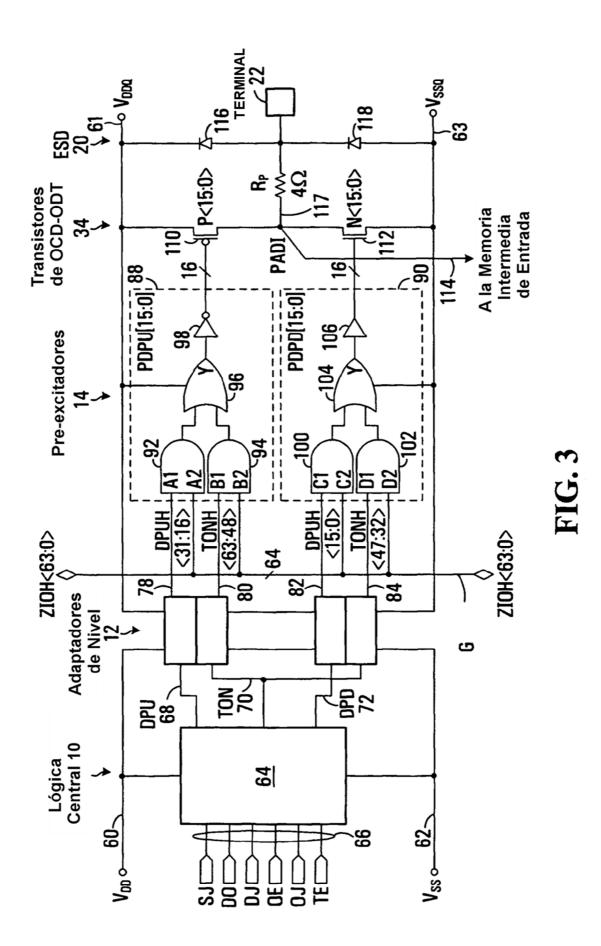

- la Figura 3 es un diagrama de bloques detallado de una arquitectura celular de I/O proporcionada por una forma de realización de la invención;

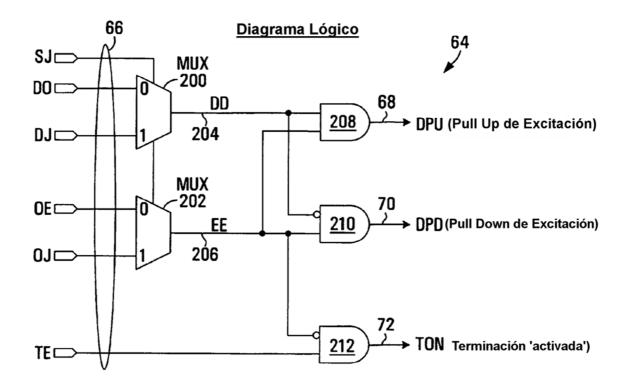

- la Figura 4A es un diagrama lógico de la funcionalidad de la lógica central de la Figura 3;

- 65 la Figura 4B es una tabla de verdad para el diagrama lógico de la Figura 4A;

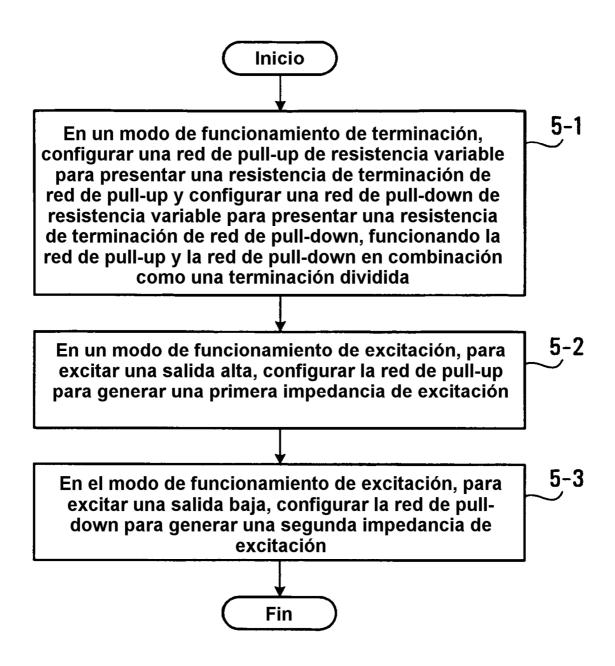

la Figura 5 es un diagrama de flujo de un método para proporcionar excitación y terminación combinadas;

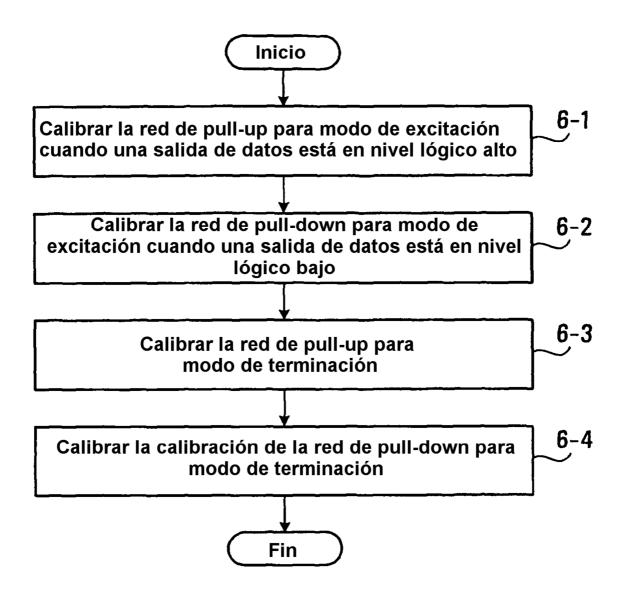

la Figura 6 es un diagrama de flujo de un primer método de calibración del método de la Figura 5; y

la Figura 7 es un diagrama de flujo de un segundo método de calibración del método de la Figura 5.

#### Descripción detallada

5

20

25

30

35

40

45

50

55

60

65

En referencia a continuación a la Figura 1, se muestra un plano de planta de dos arquitecturas celulares diferentes de Entrada/Salida (I/O) de DDR. Indicada de forma general con la referencia 30 se encuentra una arquitectura celular convencional que incluye lógica de interfaz central 10, adaptadores de nivel y una memoria intermedia de entrada 12, pre-excitadores 14, Terminación en el Dado (ODT) 16, Excitación Fuera del Chip (OCD) 18, Diodos Fijadores de Descarga Electrostática (ESD) 20 y un terminal de conexión/sonda 22. Véase por ejemplo la Normativa de la Jedec; DDR2 SDRAM Specification; JESD79-2E (Revisión de la JESD79-2D), abril de 2008.

Indicada en general con la referencia 32 se encuentra una arquitectura celular proporcionada por una forma de realización de la invención en la cual hay nuevamente una parte central 10, adaptadores de nivel y una memoria intermedia de entrada 12, pre-excitadores 14, ESD 20 y un terminal 22. No obstante, en esta forma de realización, la terminación en el dado 16 y la excitación fuera del chip 18 no son componentes independientes; se proporciona por el contrario una Terminación en el Dado/Excitación Fuera del Chip (OCD/ODT) combinadas 34.

Aunque la arquitectura de I/O celular 32 de la Figura 1 se contempla para su uso como I/O de un controlador de memorias que está conectado a un dispositivo de memoria, tal como un dispositivo de memoria SDRAM, la arquitectura de I/O puede encontrar otras aplicaciones, tales como en los propios dispositivos de memoria concretos y en cualquier interconexión de un chip a otro CMOS de alta velocidad, por ejemplo, incluyendo CPU, FPGA, controladores, memorias, etcétera.

Obsérvese que, en la arquitectura convencional 30, se dispone de una ODT y una OCD independientes; en un ejemplo dado de posibles dimensiones específicas de la implementación, la altura total 260 µm y la anchura es 40 µm. La ODT 16 se implementa típicamente usando resistores y la OCD 18 se implementa típicamente usando transistores.

Para la arquitectura celular nueva 32, se dispone de una ODT/OCD fusionada, y el resultado es que, en un ejemplo dado de posibles dimensiones específicas de la implementación, la arquitectura celular tiene una altura total de 200 µm. La ODT y la OCD se implementan usando transistores compartidos.

La Figura 1 es un ejemplo específico de dónde podría implementarse la función de OCD/ODT dentro de una arquitectura celular. De forma más general, el circuito fusionado de OCD/ODT, proporcionado en la presente, se puede usar en cualquier arquitectura celular que requiera tanto terminación como excitación. Todavía en otra forma de realización, el circuito fusionado de OCD/ODT se implementa en células que tienen funciones dedicadas de terminación y excitación, utilizándose instancias independientes del mismo circuito para cada una de ellas, de manera que así se simplifica el diseño y los ensayos.

En referencia a continuación a la Figura 2A, se muestra un diagrama de bloques simple de una ODT/OCD fusionada. Se muestra una red de pull-up de resistencia variable 40 conectada a una red de pull-down de resistencia variable 42 a través, respectivamente, de conmutadores 50, 52. El conmutador 50, cuando está cerrado, conecta la red de pull-up 40 al terminal de I/O 46 y la estructura de ESD (no mostrada). El conmutador 50 tiene una entrada 41 que proporciona un control dinámico de ON/OFF para la red completa de pull-up de ODT/OCD. El conmutador 52, cuando está cerrado, conecta la red de pull-down 42 al terminal de I/O 46 y la estructura de ESD. De manera similar, el conmutador 52 tiene una entrada 43 que proporciona un control dinámico de ON/OFF para la red completa de pull-down de ODT/OCD. El control 41 permite activar y desactivar la red de pull-up para cada una de las funcionalidades de ODT y OCD a una alta velocidad. De manera similar, el control 43 permite activar y desactivar la red de pull-down para cada una de las funcionalidades de ODT y OCD a una alta velocidad. El primer y el segundo controles de ON/OFF 41, 43 activan o desactivan dinámicamente las redes de resistencias pull-up y pull-down para generar salidas o recibir entradas. Típicamente, el terminal 46 se conecta por medio de una pista de PCB a un dispositivo de memoria, tal como una SDRAM (no mostrada). La red de pull-up 40 tiene una entrada de control 48 que proporciona una entrada de control de impedancia para cada una de la ODT y la OCD. La red de pull-down 42 tiene una entrada de control 53 que proporciona un control de impedancia para cada una de la ODT y la ODT. Se muestra también una memoria intermedia de entrada 51. La memoria intermedia de entrada se conecta para recibir una señal desde el terminal 46, y para trasladar el mismo hacia la parte central (no mostrada) por medio de circuitería de receptor (tampoco mostrada). Las dos redes de resistencia variable 40, 42 son principalmente redes de transistores que tienen una resistencia variable. Estas redes de resistencia variable constan de un conjunto de transistores que se pueden activar y desactivar del circuito para variar la resistencia ON del circuito en consecuencia. La resistencia OFF de la red es sustancialmente la correspondiente de un circuito abierto que presenta únicamente corriente de fuga. El primer y el segundo controles de resistencia (48, 53) son controles casi estáticos cuyos estados, una vez establecidos para resistencias calibradas específicas, no es necesario que

cambien nuevamente siempre que las condiciones de funcionamiento para la red de resistencias no provoquen un cambio significativo de la resistencia. Al producirse una re-calibración, los estados de los controles de resistencia se pueden cambiar para lograr la resistencia deseada para las diferentes condiciones de funcionamiento.

- Para funcionar en el modo ODT, el primer y el segundo controles de ON/OFF 41, 43 activan la red de *pull-up* 40 y la red de *pull-down* 42 respectivamente. Adicionalmente, las entradas de control de impedancia 48, 53 se usan para establecer la resistencia de la red de *pull-up* 40 y la red de *pull-down* 42 en los valores calibrados para la terminación. Por medio del terminal 46 se introduce una señal recibida, la misma se pasa a través de la memoria intermedia de entrada 51 y se traslada al resto de circuito (no mostrado). Al activar al mismo tiempo los transistores tanto en la red de *pull-up* como en la red de *pull-down*, el excitador de salida se puede usar para crear el comportamiento de impedancia correspondiente a una red de resistores de terminación dividida. En otras palabras, se pueden usar transistores de salida del controlador para actuar como terminación de una señal de entrada.

- Para funcionar en el modo OCD, cuando se va a dar salida a un nivel lógico alto, las entradas de control 41, 43 activan la red de *pull-up* 40, y desactivan la red de *pull-down* 42. Adicionalmente, el control de impedancia 48 se usa para establecer la resistencia de la red de *pull-up* 40 en el valor calibrado para la red de *pull-up* para la excitación. Cuando se va a dar salida a un nivel lógico bajo, las entradas de control 41, 43 activan la red de *pull-down* 42 y desactivan la red de *pull-up* 40. Adicionalmente, la entrada de control de impedancia 53 se usa para establecer la resistencia de la red de *pull-down* en el valor calibrado para la red de *pull-down* para excitación. Obsérvese que las funciones de OCD y ODT son mutuamente exclusivas.

- La SRAM (memoria estática de acceso aleatorio) de Velocidad de Datos Cuádruple (QDR) es un tipo de SRAM con terminales de entrada y salida independientes. La ODT/OCD fusionada puede seguir encontrando aplicación para conectarse a un dispositivo del tipo mencionado ya que se pueden usar instancias independientes de un diseño 25 celular común de I/O tanto para la entrada como para la salida, simplificando así el diseño. En este caso, una instancia fusionada, dada, de ODT/OCD se configurará permanentemente para que sea o bien ODT o bien OCD. La Figura 2B ilustra un ejemplo específico en el cual una función fusionada de ODT/OCD similar a la de la Figura 1 se usa para un controlador de SRAM de Velocidad de Datos Cuádruple (QDR) en comunicación con una SRAM de QDR a través de un trayecto eléctrico. En el ejemplo ilustrado, el trayecto eléctrico incluye, desde el controlador a la SRAM, un terminal de conexión a chips 80 del controlador, un conductor de encapsulamiento 82 del controlador, una 30 bola 84, una pista de placa de circuito 86, otra bola 88, un conductor de encapsulamiento 90 de la SRAM, y un terminal de conexión a chips 92 de la SRAM. La figura no está dibujada a escala, en la medida en la que típicamente la pista de placa de circuito 86 tiene una longitud significativamente mayor que la totalidad de los otros elementos del trayecto eléctrico. El trayecto eléctrico no se comporta como un nodo de interconexión perfecto, y, consecuentemente, cierta resistencia, inductancia y capacidad parásitas están asociadas al trayecto eléctrico lo cual 35 puede someter señales de alta velocidad a efectos severos en la línea de transmisión. Obsérvese que la circuitería de recepción adicional (por ejemplo, memoria intermedia de recepción, etcétera) no se muestra, aunque estaría presente por lo menos para instancias del circuito que se esté usando para la ODT.

- La impedancia de salida varía inversamente en relación con el número de transistores del excitador de salida de QDR que están activados. En referencia a la Fig. 2B, típicamente habrá por lo menos varios (por ejemplo, 16) transistores NMOS 43 en la red de *pull-up* 40, y también habrá un número similar de transistores NMOS 45 en la red de *pull-down* 42. En algunas implementaciones, a efectos de la calibración únicamente es necesario activar la red de *pull-up* 40 ya que los transistores de las dos redes A y B son del mismo tipo (en este caso NMOS) y se han dimensionado en el diseño para proporcionar impedancias *pull-up* y *pull-down* idénticas en el voltaje de calibración (V<sub>O</sub>=V<sub>DDQ</sub>/2).

50

55

60

65

En referencia a la Figura 2C, se muestra un modelo ejemplificativo de cómo se puede llevar a cabo la calibración en un circuito con redes de pull-up y redes de pull-down formadas con transistores del mismo tipo. A efectos de la calibración se usa una réplica de una celda de I/O. La red de pull-up se representa como R<sub>PU</sub> 200 y la red de pulldown se representa como RPD 202. La conmutación está configurada de tal manera que RPU está siempre conectada, y RPU está siempre desconectada. Esto se muestra en forma de un único conmutador 203, aunque también se puede implementar usando un par de conmutadores equivalentes al conmutador 50, 52 de la Figura 2A y/o usando los transistores que implementan las redes de pull-up y pull-down de resistencia variable, siendo la conexión de R<sub>PU</sub> equivalente al conmutador 50 de la Figura 2A abierto, y el conmutador 52 cerrado. El circuito de réplica se conecta a través de un terminal 204 a un resistor de referencia R<sub>ZQ</sub> que es de 50 ohmios en el ejemplo ilustrado. La salida 201 del circuito de réplica se conecta también a una entrada de un comparador analógico 206. El comparador analógico 206 tiene una segunda entrada 203 conectada a un voltaje de referencia ajustado a V<sub>DDQ</sub>/2 en el ejemplo ilustrado. La salida Z<sub>COMP</sub> 208 del comparador analógico 206 es baja cuando la salida 201 del circuito es menor que el voltaje de referencia 203 y es alta cuando la salida 201 del circuito es mayor que el voltaje de referencia 203. La salida  $Z_{COMP}$  208 es indeterminada cuando la salida  $V_0$  201 es igual al voltaje de referencia 202. Para calibrar la impedancia de salida, R<sub>PU</sub> 200 se hace variar (variando la configuración del circuito, por ejemplo variando el número de transistores que contribuyen a la resistencia) hasta que Z<sub>COMP</sub> 208 conmuta de un "cero" a un "uno". Cuando ocurre esto, el voltaje de salida justo supera el voltaje de referencia, y la configuración del circuito se identifica para su uso en el ajuste de la impedancia de salida de las celdas de I/O concretas. Obsérvese que cuando

la salida  $V_0$  201 está muy próxima a  $V_{DDQ}/2$ , la resistencia *pull-up* está muy próxima en valor a la correspondiente del resistor de calibración  $R_{ZQ}$  debido a que los voltajes iguales en cada resistor tienen la misma corriente.

En algunas formas de realización, el comparador analógico 206 se implementa usando una memoria intermedia de entrada de DDR. Dichas memorias intermedias son comparadores analógicos especializados que se diseñan para velocidad por contraposición a precisión o ganancia. La salida de un comparador analógico de este tipo es digital y está diseñada para conmutar bruscamente de un nivel lógico a otro en función de los valores relativos de sus entradas analógicas.

Por ejemplo, para calibrar la impedancia de salida de manera que coincida con la resistencia de 50Ω en la Figura 2C, el número de transistores activados se puede hacer variar progresivamente mediante el cambio de señales de selección/habilitación aplicadas a puertas de los transistores *pull-up* de la red de *pull-up* de excitadores de referencia hasta que la salida V₀ 201 sea mayor que V<sub>DDQ</sub>/2 aunque lo más próxima posible a esta última. La calibración apropiada para el excitador de salida de QDR se encontrará con este ajuste y, una vez que se ha ajustado el excitador de salida de QDR de referencia, durante el funcionamiento normal se activará el número correcto de transistores de excitadores de salida (X), de todos los excitadores de QDR que comparten los ajustes del excitador de referencia de calibración. Por ejemplo, X de entre 16 transistores de la red de *pull-up* se activarán cuando la línea se excite a un nivel alto, y X de 16 transistores de la red de *pull-down* se activarán cuando la línea se excite a nivel bajo.

20

25

30

35

5

La red de *pull-up* y la red de *pull-down* de la Figura 2B están formadas las dos con transistores de tipo n. Esto es particularmente adecuado para aplicaciones de QDR. Tal como se ha detallado anteriormente, esto permite llevar a cabo una calibración simplificada. De forma más general, en cualquier implementación que presente una red de *pull-up* y una red de *pull-down* formadas con transistores del mismo tipo, únicamente es necesario calibrar una u otra de las redes de *pull-up* y *pull-down* para cada una de ODT y OCD, puesto que el valor de calibración será el mismo para la red de *pull-up* y la red de *pull-down*.

En los ejemplos de las Figuras 2A y 2B, la red de *pull-up* se muestra por separado con respecto al elemento de conmutación que habilita la red de *pull-up*, y la red de *pull-down* se muestra por separado con respecto al elemento de conmutación que habilita la red de *pull-down*. No obstante, en algunas formas de realización, la función de conmutación se implementa mediante los transistores que forman parte de las redes de *pull-up* y de *pull-down*.

En la Figura 2D se ilustra un ejemplo de un excitador de salida para un controlador de DDR3. El excitador de salida de DDR3 es en parte similar al excitador de salida del controlador de QDR mostrado en la Figura 2B; no obstante, la red de *pull-up* 40 está compuesta por transistores PMOS 47 en lugar de transistores NMOS. Debido a esto, es necesario llevar a cabo una calibración de la red de *pull-up* y de la red de *pull-down* por separado, puesto que los transistores PMOS y NMOS pueden tener características de resistencia diferentes. Se dispone también de una memoria intermedia de recepción (no mostrada) para el funcionamiento en modo ODT. Con la DDR3, cada I/O funciona en el modo tanto de entrada como de salida, durante tiempos mutuamente exclusivos.

40

Al activar simultáneamente transistores tanto en la red de *pull-up* como en la red de *pull-down*, el excitador de salida de DDR3 se puede usar para crear el comportamiento de impedancia de una red de resistores de terminación dividida. En otras palabras, los transistores de salida del controlador de DDR3 se pueden usar para actuar como terminación de una señal de entrada.

45

50

55

60

65

A continuación se describirá, en referencia a la Figura 3, una implementación detallada de una arquitectura celular de I/O congruente con la arquitectura celular 32 de la Figura 1. Tal como se describe más adelante, el circuito de la Figura 3 se muestra de manera que incluye entradas de prueba que están destinadas a la realización de pruebas, y entradas normales. Debe entenderse que las entradas de prueba y la circuitería correspondiente se podrían omitir sin afectar al funcionamiento normal del circuito. Los elementos que son comunes a los correspondientes de la Figura 1 se enumeran de manera similar. En particular, el circuito se muestra de manera que incluye lógica central 10, adaptadores de nivel 12, pre-excitadores 14, transistores de OCD/ODT combinadas 34 que incluyen transistores de tipo p pull-up P<15:0> 110 y transistores de tipo n pull-down N<15:0> 112, una ESD 20 compuesta por el diodo fijador de ESD 116 y el diodo fijador de ESD 118 y el terminal 120. Para este ejemplo, se supone que los preexcitadores 14 incluyen 16 pre-excitadores 88 que excitan 16 transistores pull-up 110, y 16 pre-excitadores 90 que excitan 16 transistores pull-down 112, aunque este número es específico de la implementación. Los transistores pullup 110 están conectados a los transistores pull-down 112 en un punto etiquetado como red Interna de TERMINALES (PADI). Se muestra también la resistencia R<sub>p</sub> 117 que conecta la PADI con el terminal 22. El resistor R<sub>p</sub> es un resistor de tipo difusión con una gran área de distribución que se usa para proteger los transistores de salida contra los efectos destructivos de la ESD. El resistor limita las corrientes de ESD que van a los transistores de salida las cuales, si son excesivas, pueden desencadenar el efecto de snap-back en los transistores, dañándolos. Al tener este resistor en su lugar se evita que se produzca el efecto de snap-back. El resistor Rp forma parte de la estructura de ESD 20 de la PAD. La PADI está conectada también por el punto 114 a la memoria intermedia de entrada (no mostrada). El circuito dispone de conexiones para V<sub>DD</sub> 60, V<sub>SS</sub> 62, V<sub>DDQ</sub> 61 y V<sub>SSQ</sub> 63. Estas son los terminales de la línea de alimentación de la celda de I/O. La línea de alimentación es un bus metálico que se usa para distribuir la alimentación a las celdas de I/O dispuestas por la periferia de un chip de silicio. V<sub>DDQ</sub> está conectada a la fuente de

alimentación de I/O que, por ejemplo, se ajusta nominalmente a 2,5 V para DDR1, 1,8V para DDR2 y 1,5V para DDR3.  $V_{\rm SSQ}$  es el retorno de tierra de I/O para la fuente de alimentación de  $V_{\rm DDQ}$ . El terminal de  $V_{\rm DD}$  está conectado a la alimentación de la parte central que, para tecnologías submicrónicas profundas actuales, se ajusta típicamente a voltajes en el intervalo de entre 1,0 y 1,2 Voltios.  $V_{\rm SS}$  es el retorno de tierra de la parte central para la fuente de alimentación de  $V_{\rm DD}$ . Aunque las dos son nominalmente 0,0 Voltios,  $V_{\rm SSQ}$  y  $V_{\rm SS}$  son redes de tierra en el dado independientes. Las dos tierras son independientes para aislar la parte central con respecto al ruido de conmutación de I/O.

- La lógica central 10 incluye un circuito 64 que recibe entradas 66 que constan de SJ, DO, DJ, OE, OJ, TE. La función de estas entradas es la siguiente:

- SJ selecciona entradas normales (DO y OE) cuando está en nivel bajo y selecciona entradas de prueba (DJ y OJ) cuando está en nivel alto;

- DO es la salida de datos normal para el terminal cuando OE = 1. El terminal está en nivel alto cuando DO=1, y el terminal está en nivel bajo cuando DO = 0:

- DJ es la salida de datos de prueba para el terminal cuando OJ = 1. El terminal está en nivel alto cuando DJ = 1 y el terminal está en nivel bajo cuando DJ = 0;

- OE es la habilitación de salida normal. Cuando OE = 1 el Excitador Fuera del Chip (OCD) está habilitado y la Terminación en el Dado (ODT) está deshabilitada. Cuando OE = 0, la OCD está deshabilitada (tri-estado) y la ODT está habilitada si TE = 1;

- OJ es la habilitación de la salida de prueba, y tiene la misma funcionalidad que OE; y

20

- TE es la habilitación de la terminación. Esto permite que los transistores de los excitadores del terminal funcionen como una terminación dividida. Cuando TE = 1, la terminación se activará cuando la OCD sea tri-estado (OE (u OJ) = 1). Será habitualmente de nivel bajo para aplicaciones solamente de excitación y de nivel alto para aplicaciones de I/O de datos.

- Las salidas de la lógica central 64 incluyen DPU 68, TON 70 y DPD 72, que funcionan de la manera siguiente:

- DPU es un control de *pull-up* de excitación. Cuando la misma está en nivel alto, provoca que el transistor *pull-up* de excitación se active. Cuando está en nivel bajo, el transistor *pull-up* de excitación se desactiva;

- DPD es un control de *pull-down* de excitación. Cuando la misma está en nivel alto, provoca que el transistor *pull-down* de excitación se active. Cuando está en nivel bajo, el transistor *pull-down* de excitación de desactiva; y

- 40 TON es un control de activación de la terminación. Cuando está en nivel alto, los transistores tanto *pull-up* como *pull-down* se habilitan para activarse conjuntamente con el fin de formar una terminación dividida cuando OE u OJ pasa a nivel bajo. Cuando está en nivel bajo, la función de terminación se deshabilita completamente y no puede verse influida por los estados de OE u OJ.

- Las tres salidas DPU 68, TON 70, y DPD 72 son entradas a adaptadores de nivel 12 que producen DPUH 78, TONH 80, DPDH 82 y TONH 84 que son las versiones de alto voltaje de DPU 68, TON 70, y DPD 72 usadas para excitar los pre-excitadores de I/O 88, 90.

- Se dispone de un bus de control de impedancia de 64 bits, al que se hace referencia como ZIOH<63:0> que se usa para controlar los transistores *pull-up* 110 y los transistores *pull-down* 112. El bus de control de impedancia ZIOH es un ejemplo específico de cómo podrían implementarse las entradas de control de impedancia de la Figura 2A. Cada pre-excitador recibe bits particulares del bus de control de impedancia, y otros particulares de las salidas adaptadas en nivel DPUH 78, TONH 80, DPDH 82 y TONH 84 según se detalla posteriormente. ZIOH<63:0> incluye lo siguiente:

- 16 bits ZIOH<31:16> para controlar los transistores *pull-up* 110 en el modo de OCD, con un bit por transistor;

- 16 bits ZIOH<63:48:> para controlar los transistores *pull-up* 110 en el modo de ODT, con un bit por transistor;

- 60 16 bits ZIOH<15:10> para controlar los transistores *pull-down* 112 en el modo de OCD, con un bit por transistor; y

- 16 bits ZIOH<47:32> para controlar los transistores pull-down 112 en el modo de ODT, con un bit por transistor.

- Cada pre-excitador 88 incluye una puerta AND 92 y una puerta AND 94 que tienen salidas respectivas conectadas a una puerta OR 96 que tiene una salida alimentada a través de una memoria intermedia de inversión 98 respectiva

cuya salida excita la puerta de uno de los transistores *pull-up* 110. La puerta AND 92 recibe DPUH 78 (A1) y uno de los bits de ZIOH<31:16> (A2). La puerta AND 94 recibe TONH 80 (B1) y uno de los bits de ZIOH<63:48> (B2).

- De manera similar, cada pre-excitador 90 incluye una puerta AND 100 y una puerta AND 102 que tienen salidas respectivas conectadas a una puerta OR 104 que tiene una salida alimentada a través de una memoria intermedia no inversora 106 respectiva cuya salida excita la puerta de uno de los transistores *pull-up* 120. La puerta AND 100 recibe DPDH 82 (C1) y uno de los bits de ZIOH<15:0> (C2). La puerta AND 102 recibe TONH 84 (D1) y uno de los bits de ZIOH<47:32> (D2).

- La lógica AND-OR-AND, incorporada en los pre-excitadores 88, 90, actúa como multiplexores de alta velocidad para el control independiente de impedancias de los excitadores y de terminación. La lógica AND-OR-AND permite activar y desactivar de manera alternada, cuando se está en modo de excitación, un número cualquiera de transistores *pull-up* y *pull-down* y activar y desactivar conjuntamente un número cualquiera de transistores *pull-up* y *pull-down* cuando se está en modo de terminación. La lógica de los pre-excitadores desactiva todos los transistores de OCD/ODT 34 que no son seleccionados por el bus de ZIOH<63:0> 76 y evita que los mismos conmuten. Únicamente los transistores de OCD/ODT seleccionados conmutan a alta velocidad.

- En la Figura 4A se muestra una implementación de ejemplo detallada del circuito 64 de la Figura 3. Como en la Figura 3, hay entradas 66 (que constan de SJ, DO, DJ, OE, OJ, TE) y salidas DPU 68, DPD 70 y TON 72. DO y DJ son entradas a un primer multiplexor 200 que produce una salida DD 204. OE y OJ son entradas a un segundo multiplexor 202 que produce una salida EE 206. DD 204 se conecta a una primera entrada de una puerta AND 208, y a una entrada inversora de la puerta AND 210 cuya salida es DPU 68. EE 206 se conecta a una segunda entrada de la puerta AND 208 y a una segunda entrada de la puerta AND 210 cuya salida es DPD 70. EE 206 se conecta también a una primera entrada inversora de la puerta AND 212. TE se conecta a una segunda entrada de la puerta AND 212 cuya salida es TON 72.

Indicada en general con la referencia 214 en la Figura 4B se encuentra una tabla de verdad para el circuito 64, que muestra cómo se generan DPU, DPD y TON en función de SJ, DO, DJ, OE, OJ y TE.

30 Los pre-excitadores 88, 90 funcionan en función de las DPUH, TONH, TPDH adaptadas en nivel. Se describirá el funcionamiento normal (SJ = 0) por oposición a un funcionamiento de pruebas el cual sería similar.

#### **Modo OCD**

En el funcionamiento en modo OCD, OE estará en nivel alto para habilitar la salida. El estado de TE no es relevante siempre que OE esté en nivel alto. DO será 0 o 1 en cualquier instante dado, reflejando la salida a generar. Si DO es 1 (filas 216, 217), entonces uno respectivo de los transistores *pull-up* 110 es activado por los pre-excitadores 88 para cada "1" en ZIOH<31:16>. De manera similar, si DO es 0 (filas 218, 219), entonces uno respectivo de los transistores *pull-down* 112 se activa para cada "1" en ZIOH<15:0>.

#### **Modo ODT**

40

45

60

El único conjunto de entradas que da como resultado la activación del modo ODT es: OE estará en nivel bajo para deshabilitar la salida y TE = 1 para habilitar ODT (TON = 1). Esta es la fila 220 de la tabla de verdad 214. Si TON es 1, entonces uno respectivo de los transistores *pull-up* 110 es activado por los pre-excitadores 88 para cada "1" en ZIOH<63:48> y uno respectivo de los transistores *pull-down* 112 se activa para cada "1" de ZIOH<47:32>.

#### Calibración

En algunas formas de realización, se proporciona un mecanismo de calibración para identificar números apropiados de transistores a usar para el modo ODT y OCD, y en particular para identificar cuántos transistores *pull-up y/o pull-down* activar para cada uno de estos modos. En algunas formas de realización, la calibración se lleva a cabo dinámicamente durante el funcionamiento del dispositivo de una manera periódica para permitir ajustes bajo condiciones de funcionamiento cambiantes.

En algunas formas de realización, se lleva a cabo una calibración de cuatro fases de la manera siguiente:

- 1) calibración de la impedancia de salida de dispositivos N esto determina cuántos de los transistores de tipo n 112 habilitar para el modo OCD cuando DO es 0;

- 2) calibración de la impedancia de salida de dispositivos P esto determina cuántos de los transistores de tipo p 110 habilitar para el modo OCD cuando DO es 1;

- 3) calibración de terminación de dispositivos N esto determina cuántos de los transistores de tipo n 112 habilitar

65 para ODT; y

4) calibración de terminación de dispositivos P – esto determina cuántos de los transistores de tipo p 110 habilitar para el modo ODT.

De forma más general, la calibración de redes de *pull-up* y la calibración de redes de *pull-down* se puede realizar de una manera similar. Los circuitos descritos se duplican en su mayoría sobre la base de cada pin individual. No obstante, en algunas formas de realización, la calibración no se lleva a cabo sobre la base de cada pin individual. Por el contrario, la calibración se realiza una vez, esperando que se puedan aplicar los mismos resultados de calibración a todos los pines. Esta esperanza es razonable dado que los transistores que se usan para la OCD/ODT combinadas para múltiples pines formarán parte del mismo circuito integrado y, por tanto, tendrán propiedades similares. En algunas formas de realización, se usa una réplica de la OCD/ODT combinadas a efectos de la calibración de la totalidad de las I/O.

10

15

20

25

30

35

40

45

50

55

60

El número de transistores a incluir en la OCD/ODT combinada se puede seleccionar en función de un intervalo deseado de programabilidad, y en función de las características de resistencia/excitación de los transistores. En algunas formas de realización, se usa un conjunto de transistores que proporcionan un intervalo de programabilidad de entre 30 ohmios y 90 ohmios, aunque esto evidentemente es específico de cada implementación.

En algunas formas de realización, un controlador codifica una resistencia usando un código Gray, y este a continuación se convierte en una salida de codificación unaria. Cada palabra de código de una codificación unaria tiene un conjunto único de cero o más 1's seguido por un conjunto único de cero o más 0's para llenar la palabra de código. El uso de una codificación unaria de este tipo garantiza que se habilita un conjunto de transistores consecutivos (pull-up o pull-down). En un ejemplo particular, se usa un código Gray de 4 bits para indicar una de 16 permutaciones posibles, y este se traduce a una codificación unaria de 16 bits que contiene un bit por transistor. Se puede usar un esquema de decodificación de Grey-a-unaria en lugar de un esquema de binaria-a-unaria para evitar que aparezca un error en la salida del excitador mientras se está cambiando el código de la impedancia (ZIOH<63:0>).

Los ejemplos ilustrados se refieren todos ellos a un circuito combinado de OCD/ODT. De forma más general, se proporciona un circuito que ofrece una excitación y terminación combinadas.

La Figura 5 es un diagrama de flujo de un método para proporcionar una excitación y terminación combinadas. El método comienza en la etapa 5-1 con la configuración, en un modo de funcionamiento de terminación, de una red de *pull-up* de resistencia variable para tener una resistencia de terminación de la red de *pull-up* y la configuración de una red de *pull-down* de resistencia variable para tener una resistencia de terminación de la red de *pull-down*, funcionando la red de *pull-up* y la red de *pull-down* en combinación como una terminación dividida. En la etapa 5-2, en un modo de funcionamiento de excitación, para excitar una salida alta, se configura la red de *pull-up* para generar una primera impedancia de excitación. En la etapa 5-3, en el modo de funcionamiento de excitación, para excitar una salida baja, se configura la red de *pull-down* para generar una segunda impedancia de excitación. El orden de la ejecución de las etapas de Figura 5 dependerá evidentemente tanto de la secuencia de excitación con respecto a terminación, como de los datos en los que se aplique la excitación mientras se está en modo de excitación.

La Figura 6 es un diagrama de flujo de un primer método de calibración del método de la Figura 5. El método comienza en la etapa 6-1 con la calibración de la red de *pull-up* para el modo de excitación cuando una salida de datos tiene un nivel lógico alto. El método continúa en la etapa 6-2 con la calibración de la red de *pull-down* para el modo de excitación cuando una salida de datos tiene un nivel lógico bajo. El método continúa en la etapa 6-3 con la calibración de la red de *pull-up* para el modo de terminación. El método continúa en la etapa 6-4 con la calibración de la calibración de la red de *pull-down* para el modo de terminación.

La Figura 7 es un diagrama de flujo de un segundo método de calibración del método de la Figura 5. El método comienza en la etapa 7-1 calibrando la red de *pull-up* para el modo de excitación cuando una salida de datos está en un nivel lógico alto con el fin de producir un primer resultado de calibración. El método continúa en la etapa 7-2 con el uso del primer resultado de calibración para calibrar la red de *pull-down* para el modo de excitación cuando una salida de datos está en un nivel lógico bajo. Esto supone que los transistores usados para la red de *pull-down* y la red de *pull-up* se forman usando el mismo proceso, y, como tal, se puede usar la misma calibración para las dos. El método continúa en la etapa 7-3 con la calibración de la red de *pull-up* para el modo de terminación con el fin de producir un segundo resultado de calibración. El método continúa en la etapa 7-4 con el uso del segundo resultado de calibración para calibrar la red de *pull-down* para el modo de terminación.

Las formas de realización descritas se refieren a redes de *pull-up* de resistencia variable, redes de *pull-down* de resistencia variable, resistencia de terminación, y referencias de resistencia. De forma más general, formas de realización pueden utilizar redes de *pull-up* de impedancia variable, redes de *pull-down* de impedancia variable, impedancia de terminación, y referencias de impedancia.

A la vista de las enseñanzas anteriores son posibles numerosas modificaciones y variantes de la presente invención.

Por lo tanto, debe entenderse que, dentro del alcance de las reivindicaciones adjuntas, la invención puede llevarse a la práctica de otras maneras diferentes a las descritas específicamente en la presente.

#### **REIVINDICACIONES**

- 1. Circuito de excitación y terminación, que comprende:

- 5 una red de *pull-up* de impedancia variable (40) que tiene una primera pluralidad de transistores (43);

- una red de pull-down de impedancia variable (42) que tiene una segunda pluralidad de transistores (45);

- estando configurada cada una de entre la red de *pull-up* (40) y la red de *pull-down* (42) para presentar una impedancia deseada variando el número de transistores activados;

- una primera pluralidad de bits de control de un bus de control de impedancia para establecer una configuración de terminación de la red de *pull-up* (40);

- una segunda pluralidad de bits de control del bus de control de impedancia para establecer una configuración de terminación de la red de *pull-down* (42);

- una tercera pluralidad de bits de control del bus de control de impedancia para establecer una configuración de excitación de la red de *pull-up* (40); y

- una cuarta pluralidad de bits de control del bus de control de impedancia para establecer una configuración de excitación de la red de *pull-down* (42);

- en el que las primera a cuarta pluralidades de bits de control son independientes entre sí;

- presentando el circuito un modo de funcionamiento de terminación en el cual la red de *pull-up* de impedancia variable (40) está configurada para presentar una impedancia de terminación de red de *pull-up* sobre la base de la primera pluralidad de bits de control, y la red de *pull-down* de impedancia variable (42) está configurada para presentar una impedancia de terminación de red de *pull-down* sobre la base de la segunda pluralidad de bits de control, funcionando la red de *pull-up* (40) y la red de *pull-down* (42) en combinación como una terminación dividida:

- presentando el circuito un modo de funcionamiento de excitación, en el cual:

- para excitar una salida alta, la red de *pull-up* (40) está configurada para generar una impedancia específica cuando está activada sobre la base de la tercera pluralidad de bits de control; y

- para excitar una salida baja, la red de *pull-down* (42) está configurada para generar una impedancia específica cuando está activada sobre la base de la cuarta pluralidad de bits de control.

- 2. Aparato, que comprende:

- una lógica central (10);

- 45 una pluralidad de I/O (entradas/salidas), presentando cada una de ellas un terminal respectivo de I/O; y

- para cada I/O, un circuito combinado respectivo de excitación y terminación según la reivindicación 1;

- funcionando los circuitos combinados de excitación y terminación de manera que generen salidas desde la lógica central (10) y actúen a modo de terminación para entradas externas para la lógica central (10).

- 3. Aparato según la reivindicación 2, en el que las redes de *pull-up* y *pull-down* (40, 42) se conmutan dinámicamente entre dos configuraciones de impedancia cuando cambian entre los modos de excitación y de terminación.

- 4. Aparato según cualquiera de las reivindicaciones 2, 3, que comprende además:

- para cada I/O, una lógica de pre-excitador que comprende una lógica AND-OR-AND, que recibe una primera entrada para indicar un nivel alto de excitación, una segunda entrada para indicar un nivel bajo de excitación, y una tercera entrada para indicar terminación, y conmuta en consecuencia entre dos configuraciones de impedancia.

- 5. Circuito según la reivindicación 1 en combinación con una lógica de calibración que calibra las impedancias con respecto a una referencia de impedancia.

- 6. Aparato, que comprende:

65

55

20

25

30

una lógica central (10);

5

25

30

35

40

50

55

una pluralidad de entradas que presentan, cada una de ellas, un terminal de entrada respectivo, y una pluralidad de salidas que presentan, cada una de ellas, un terminal de salida respectivo;

para cada terminal de entrada, un circuito combinado respectivo de excitación y terminación, según cualquiera de las reivindicaciones 1, 5 configurado permanentemente para estar en modo de terminación; y

- para cada terminal de salida, un circuito combinado respectivo de excitación y terminación según la reivindicación 1, configurado permanentemente para estar en modo de excitación.

- 7. Circuito combinado de excitación y terminación según la reivindicación 1, en el que:

- cada una de las pluralidades de bits de control incluye un bit por transistor.

- 8. Circuito combinado de excitación y terminación según cualquiera de las reivindicaciones 1, 5, en el que:

- la red de *pull-up* (40) comprende una pluralidad de transistores (43) conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de *pull-up* mediante la activación selectiva de cierto número de la pluralidad de transistores (43); y

- la red de *pull-down* (42) comprende una pluralidad de transistores (45) conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de *pull-down* (42) mediante la activación selectiva de cierto número de la pluralidad de transistores (45).

- 9. Aparato, que comprende:

- el circuito combinado de excitación y terminación según cualquiera de las reivindicaciones 1, 5, 8; y

una réplica de por lo menos parte del circuito combinado de excitación y terminación para su uso en la ejecución de la calibración.

10. Aparato según la reivindicación 9, que comprende además:

un controlador que controla la calibración que se está llevando a cabo en cuatro etapas:

- 1) calibración de la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto;

- 2) calibración de la red de *pull-down* para el modo de excitación cuando una salida de datos es un nivel lógico bajo;

- 3) calibración de la red de pull-up para el modo de terminación; y

- 4) calibración de la red de *pull-down* para el modo de terminación.

- 11. Aparato según la reivindicación 9, en el que la red de *pull-up* comprende una pluralidad de transistores mosfet de tipo P (110), y la red de *pull-down* comprende una pluralidad de transistores mosfet de N (112), comprendiendo además el aparato un controlador que controla la calibración que se está llevando a cabo en cuatro etapas:

- 1) calibración de la impedancia de salida de dispositivos N para determinar cuántos de los transistores de tipo N (112) hay que habilitar para el modo de excitación cuando una salida de datos es un nivel lógico bajo;

- 2) calibración de la impedancia de salida de dispositivos P para determinar cuántos de los transistores de tipo P (110) hay que habilitar para el modo de excitación cuando una salida de datos es un nivel lógico alto;

- 3) calibración de terminación de dispositivos N para determinar cuántos de los transistores de tipo N (112) hay que habilitar para el modo de terminación; y

- 4) calibración de terminación de dispositivos P para determinar cuántos de los transistores de tipo P (110) hay que habilitar para el modo de terminación.

- 12. Aparato según la reivindicación 9, en el que la red de *pull-up* (40) y la red de *pull-down* (42) se forman, cada una de ellas, en su totalidad, con transistores de tipo P (110) o transistores de tipo N (112), comprendiendo además el aparato:

un controlador que controla la calibración que se está llevando a cabo en dos etapas:

- 1) calibración de la red de *pull-up* para el modo de excitación cuando una salida de datos es un nivel lógico alto; y

- 2) calibración de la red de *pull-up* para el modo de terminación.

5

- 13. Aparato según la reivindicación 1, en el que el número de transistores activados (43, 45) se hace variar progresivamente usando una codificación unaria.

- 14. Aparato según la reivindicación 13, que comprende además el uso de un código gray para codificar el número de transistores activados (43, 45) que se convierte a la codificación unaria.

- 15. Método para proporcionar excitación y terminación combinadas, comprendiendo el método:

- en un modo de funcionamiento de terminación, configurar una red de *pull-up* de impedancia variable (40) para presentar una impedancia de terminación de red de *pull-up* sobre la base de una primera pluralidad de bits de control de un bus de control de impedancia y configurar una red de *pull-down* de impedancia variable (42) para presentar una impedancia de terminación de red de *pull-down* sobre la base de una segunda pluralidad de bits de control del bus de control de impedancia, funcionando la red de *pull-up* (40) y la red de *pull-down* (42) en combinación como una terminación dividida, presentando cada una de entre la red de *pull-up* (40) y la red de *pull-down* (42) una pluralidad de transistores dimensionados para proporcionar impedancias idénticas, y estando cada una de entre la red de *pull-up* (40) y la red de *pull-down* (42) configurada para presentar una impedancia deseada haciendo variar progresivamente el número de transistores activados (43, 45);

- en un modo de funcionamiento de excitación, para excitar una salida alta, configurar la red de *pull-up* (40) para generar una primera impedancia de excitación sobre la base de una tercera pluralidad de bits de control del bus de control de impedancia; y

- en el modo de funcionamiento de excitación, para excitar una salida baja, configurar la red de *pull-down* (42) para generar una segunda impedancia de excitación sobre la base de una cuarta pluralidad de bits de control del bus de control de impedancia;

- en el que las primera a cuarta pluralidades de bits de control son independientes entre sí; y

- en el que cada una de entre la red de *pull-up* y la red de *pull-down* está configurada para presentar una impedancia deseada haciendo variar el número de transistores activados.

FIG. 2C

# Funcionalidad de Lógica Central

## Control de Excitadores/Terminación

FIG. 4A

214

# Tabla de Verdad

|                                     | Entradas |             |             |             |             |       | Salidas     |             |             | Efecto en la PAD                                                             | Modo                        |

|-------------------------------------|----------|-------------|-------------|-------------|-------------|-------|-------------|-------------|-------------|------------------------------------------------------------------------------|-----------------------------|

| 215 → 216 → 218 → 220 → 217 → 219 → | SJ       | DO          | DJ          | OE          | OJ          | TE    | DPU         | DPD         | TON         | Liecto en la 1 Ab                                                            | Wiodo                       |

|                                     | 0        | X<br>0<br>1 | X<br>X<br>X | 0<br>1<br>1 | X<br>X      | 000   | 0<br>0<br>1 | 0<br>1<br>0 | 0           | Flotante<br>Nivel Bajo de Excitador<br>Nivel Alto de Excitador               | Velocidad<br>Alta<br>Normal |

|                                     |          | X<br>0<br>1 | X<br>X<br>X | 0<br>1<br>1 | X<br>X<br>X | 1 1 1 | 0 0 1       | 0<br>1<br>0 | 1<br>0<br>0 | Terminación "ACTIVADA"<br>Nivel Bajo de Excitador<br>Nivel Alto de Excitador |                             |

|                                     | 1        | X<br>X<br>X | X<br>0<br>1 | X<br>X<br>X | 0<br>1<br>1 | 0 0   | 0<br>0<br>1 | 0<br>1<br>0 | 0           | Flotante<br>Nivel Bajo de Excitador<br>Nivel Alto de Excitador               | PRUEBA                      |

|                                     |          | X<br>X<br>X | X<br>0<br>1 | X<br>X<br>X | 0<br>1<br>1 | 1 1   | 0 0 1       | 0<br>1<br>0 | 1<br>0<br>0 | Terminación "ACTIVADA"<br>Nivel Bajo de Excitador<br>Nivel Alto de Excitador |                             |

- En donde, los estados lógicos X, 0 y 1 son: X Entrada "NO IMPORTA"; Salida indeterminada 0 Falso; Cero; Bajo; Función en Estado Inactivo 1 Verdadero; Uno; Alto; Función en Estado Activo

FIG. 4B

FIG. 5

FIG. 6

FIG. 7