# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 507 077

61 Int. Cl.:

H04L 7/027 (2006.01) H04L 7/033 (2006.01) H03L 7/24 (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

- (96) Fecha de presentación y número de la solicitud europea: 04.04.2008 E 08787919 (3)

(97) Fecha y número de publicación de la concesión europea: 09.07.2014 EP 2137874

- (54) Título: Dispositivo de extracción de reloj con retroalimentación digital de fase sin ajuste externo

- (30) Prioridad:

#### 06.04.2007 FR 0702552

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 14.10.2014

73) Titular/es:

CENTRE NATIONAL D'ETUDES SPATIALES (C.N.E.S.) (100.0%) 2, PLACE MAURICE QUENTIN 75039 PARIS CEDEX 01, FR

(72) Inventor/es:

PIGNOL, MICHEL; NEVEU, CLAUDE; DEVAL, YANN; BEGUERET, JEAN-BAPTISTE y MAZOUFFRE, OLIVIER

(74) Agente/Representante:

IZQUIERDO BLANCO, María Alicia

#### Dispositivo de extracción de reloj con retroalimentación digital de fase sin ajuste externo

#### **DESCRIPCIÓN**

25

30

35

40

45

50

55

60

65

- La invención se refiere a un dispositivo de extracción de reloj, y de manera más particular a un dispositivo de extracción de reloj y de datos digitales, a partir de una señal en serie en banda de base, denominada señal recibida, representativa de datos digitales, y codificada con una señal de reloj que presenta un frecuencia de reloj bits fsr que corresponde al menos sustancialmente a una frecuencia nominal fn.

- En numerosas aplicaciones, y en particular en el campo de las muy altas frecuencias (frecuencias nominales fn superiores a 500 MHz, que pueden ser superiores a 10 GHz, que pueden incluso llegar actualmente hasta 40 GHz e incluso superar muy ampliamente estos valores en el futuro) que corresponden a muy altas velocidades (superiores a 500 Mbits/s, que pueden ser superiores a 10 Gbits/s, y que pueden llegar incluso a 40 Gbits/s para los estándares SONET OC-768 y SDH STM-256 y que pueden superar muy ampliamente sus valores en el futuro), se transmite en un canal de transmisión (cuya tecnología de realización puede ser cualquiera: eléctrica, óptica, radiofrecuencia...) de una conexión en serie en banda de base una señal que incorpora unos datos digitales mezclados con una señal de reloj, de tal modo que se evita tener que transmitir estas dos informaciones en dos canales diferentes. Esto permite evitar cualquier emparejamiento delicado de la longitud de los trayectos de las señales. Con dichas señales, al nivel del receptor, es necesario extraer de la señal recibida, de naturaleza analógica, por una parte los valores de los datos digitales y, por otra parte, la señal de reloj correspondiente a estos datos. Para obtener los valores de los datos, se muestrea la señal recibida a partir de la señal de reloj previamente extraída de los datos.

La solución más habitual para realizar dicho dispositivo de extracción de reloj y de datos consiste en utilizar unos circuitos que comprenden al menos un bucle de bloqueo de fase, denominado PLL, que comprende principalmente, en la salida de un circuito que genera impulsos que corresponden a los flancos ascendentes y descendentes de la señal recibida, enviando un comparador de fase una señal de consigna a un oscilador controlado en tensión, denominado VCO, a través de un filtro de bucle. El VCO suministra una señal de reloi interno a un biestable de decisión, que constituye un circuito de muestreo que extrae los datos de la señal recibida. Estos circuitos PLL tradicionales, que utilizan unos osciladores de relajación o unos osciladores de red LC, unos comparadores fase/frecuencia y unos divisores digitales de alta frecuencia, presentan diferentes inconvenientes. Son incompatibles con las conexiones de muy alta velocidad; precisan una referencia de frecuencia externa, precisan una sincronización en el arranque mediante un preámbulo de datos que deben necesariamente estar presentes en la señal recibida, lo que no es aceptable en algunas aplicaciones; presentan una gran complejidad de optimización de funcionamiento y de realización, numerosos parámetros interdependientes y contradictorios que se deben tener en cuenta, en particular en lo que se refiere al circuito comparador fase/frecuencia; tienen un consumo energético muy alto; su realización analógica es muy dependiente de la tecnología de fabricación de los componentes semiconductores que se utilizan... Por consiguiente, la realización de un circuito PLL para realizar una funcionalidad de extracción de reloj precisa la intervención de especialistas de los circuitos analógicos con una gran experiencia y una gran técnica, y, por otra parte, precisa unos tiempos de desarrollo importantes, hay que renovarlos regularmente cada vez que evoluciona la tecnología, lo que, desde el punto de vista de las exigencias actuales de utilización a escala industrial, no es admisible.

Otra solución conocida para realizar la extracción de reloj se basa en el uso de un bucle de bloqueo de retardo, denominado DLL. Sin embargo, estos circuitos precisan un código específico en lo que se refiere a la señal recibida, en particular con un bit de arranque y un bit de parada para formar una transición de referencia en cada palabra (lo que reduce la frecuencia de transmisión máxima accesible para los datos, tradicionalmente del 33 % con unos datos útiles de 8 bits y un código como 8B/12B). Además, los datos recuperados presentan una deriva de fase ("jitter") relativamente importante, que puede conducir a un importante porcentaje de errores de bits. Igualmente, dicho circuito DLL es muy sensible a los ruidos en la señal recibida. Por último, esta técnica implementada con unos componentes digitales es difícilmente compatible con unas velocidades de transmisión extremadamente elevadas.

El documento FR 2838265 ha propuesto una solución que consiste en utilizar un oscilador de inyección, es decir un oscilador bloqueado en inyección en la frecuencia de flancos de la señal recibida en un circuito de bucle abierto. Para ello, el oscilador de inyección es un oscilador de resistencia negativa que utiliza un par acoplado de transistores MOS, y recibe una señal de impulsos de sincronización acompasada a la frecuencia de reloj bits fsr de la señal recibida, emitiéndose esta señal de impulso por un generador de impulsos de sincronización. Este oscilador bloqueado en inyección que presenta una frecuencia de oscilaciones libres fos, tiene la facultad de bloquearse en la señal de impulsos si la frecuencia de esta última está en su intervalo de funcionamiento, denominado intervalo de captura. Este proporciona entonces una señal de reloj cuya frecuencia corresponde exactamente a la frecuencia de reloj bits fsr.

Sin embargo, el problema que se plantea entonces es garantizar también la sincronización en fase de la señal de reloj que proporciona el oscilador, con respecto a la señal recibida. A este respecto, se sabe que el desplazamiento de fase que introduce el oscilador es proporcional a la diferencia entre la frecuencia de la señal en la entrada del oscilador y la frecuencia propia fos de esta última. Como consecuencia, se puede pensar en ajustar el valor de la frecuencia propia del oscilador en función de la frecuencia de reloj bits fsr de la señal recibida al diseñar el circuito.

Pero esta solución sigue siendo imperfecta en la medida en que justamente el valor de esta frecuencia de reloj bits fsr no se conoce con precisión (lo que constituye el problema técnico inicial principal que precisa la presencia de un circuito de extracción de reloj en el receptor). Además, precisaría en cualquier caso un ajuste del circuito para cada aplicación. Aunque dicho ajuste es admisible en el contexto de un prototipo de laboratorio, no es aceptable en la mayoría de las aplicaciones industriales de dicho circuito.

5

10

15

20

25

30

35

40

45

50

55

60

65

El documento FR 2838265 ha propuesto resolver este problema de desplazamiento de fase previendo una lógica de decisión para seleccionar un valor entre diferentes valores suministrados por una multitud de biestables de muestreo desplazados de acuerdo con unos tiempos de desplazamiento distintos con respecto a los impulsos de la señal de reloj de recepción. Resulta que, en la práctica, esta solución no es realmente eficaz en todas las situaciones.

También el documento US 6924705 describe un circuito PLL que comprende un detector digital de fase, una bomba de carga y un filtro de bucle que controla un oscilador controlado en tensión, recibiendo este último la señal de datos en la entrada a través de un duplicador de frecuencia. Además de que no se indica la realización práctica del detector digital de fase, este circuito presenta el inconveniente de no poder realizarse completamente de forma digital, puesto que la bomba de carga y el filtro de bucle son componentes de tipo analógico. Por consiguiente, la realización de un circuito de acuerdo con este documento es estrechamente dependiente en la práctica de la tecnología del semiconductor que se utiliza y no se puede adaptar simple y rápidamente a otra tecnología de semiconductor, sin precisar previamente un nuevo diseño del circuito. Además, este circuito al presentar un reducido intervalo de frecuencias admisibles en la entrada y al no adaptarse automáticamente a la señal recibida, precisa unos ajustes manuales externos de la frecuencia libre del oscilador y de la diferencia de retardos de propagación entre las diferentes líneas, en particular la que permite extraer los datos y la que permite extraer el reloj. Por lo tanto, el circuito que se describe en este documento no puede ser objeto de una utilización a escala industrial en las aplicaciones en las que el periodo de desarrollo se debe minimizar y/o en aquellas en las que es preciso poder migrar con frecuencia de una tecnología de semiconductor a otra y/o en las que la frecuencia de la señal recibida puede variar dentro de un amplio intervalo de valores.

El documento US 5671259 describe un circuito de extracción de reloj que comprende un circuito resonante implementado con unos componentes discretos montados en un circuito impreso y un bucle digital de retroalimentación de fase que comprende un circuito contador que permite conformar una señal de control de ajuste de la frecuencia del circuito resonante. El funcionamiento de dicho circuito resonante no es compatible con una realización en circuito(s) integrado(s) (el factor de calidad de los componentes en esta tecnología es muy insuficiente) y únicamente permite alcanzar unas bajas frecuencias de funcionamiento (del orden de 2 MHz para el ritmo de datos entrantes). Además, con dicho circuito resonante, en ausencia de transición en la señal de datos, la oscilación desaparece al cabo de algunos ciclos, de tal modo que este tipo de circuito no es compatible con las señales de datos que presentan pocas o ninguna transición en determinados periodos. Por otra parte, en este documento, la fase de la señal de entrada puede variar en más o menos un cuarto de bit, esto es una variación absoluta de medio bit sin que reaccione el bucle de retroalimentación de fase, de tal modo que no se detectan los desplazamientos de fase accidentales entre un 0 % y un 50 %. Además, el circuito contador es un contador en 20 bits, utilizándose solo los 8 bits más significativos para el control del circuito resonante. Dicho filtrado extremadamente alto (siendo necesaria una diferencia de 4.096 desplazamientos de fase sucesivos antes de accionar un ajuste) es en la práctica totalmente ineficaz. Sobre todo, no permite de ninguna manera, al contrario de lo que se indica en este documento, resolver los eventuales desplazamientos de fase accidentales presentes en la señal de entrada.

De este modo, a pesar de las intensivas investigaciones realizadas desde hace tiempo en estos circuitos de extracción de reloj, sigue existiendo la necesidad de poder proponer una solución simple, compatible con una utilización en serie a escala industrial en la mayoría de las aplicaciones prácticas actuales de estos circuitos, incluso con unas conexiones de muy alta velocidad -en particular superior a 500 Mbits/s- y/o de muy alta frecuencia -en particular superior a 500 MHz-, cuyo consumo energético es aceptable, y que no precisa ajustes externos ni un diseño específico, ajustándose necesariamente cada circuito fabricado debido a su diseño con independencia de la tecnología de realización utilizada, y que se mantiene perfectamente en fase con las señales de datos de entrada siendo al mismo tiempo compatible con una enorme variedad de dichas señales de datos de entrada, incluso cuando estas últimas presentan unos periodos que presentan pocas transiciones o sin transiciones, o numerosos desplazamientos de fase accidentales.

La invención pretende, por lo tanto, proponer dicha solución. En efecto, los inventores han comprobado que era posible, por medio de una arquitectura específica, proponer por primera vez un dispositivo de extracción de reloj, y de manera más particular un dispositivo de extracción de reloj y de datos, que presenta estas cualidades, y en particular que sea de muy simple realización, "auto regulado" (es decir que no precisa ningún ajuste manual externo) al presentar un amplio intervalo de adquisición y un porcentaje de errores de bits muy bajo siendo al mismo tiempo compatible con una enorme variedad de señales de datos en la entrada.

La invención también pretende proponer un dispositivo de este tipo que sea poco sensible a la variación de calidad de las señales recibidas, y en particular que sea compatible con las señales que pueden presentar una densidad de transiciones variable, y del ruido.

La invención también pretende proponer un dispositivo de este tipo que se pueda realizar casi completamente en forma de componentes digitales, y en particular cuyo bucle de retroalimentación de fase se realice íntegramente en forma de componentes digitales. En efecto, los inventores han determinado que de esto se deriva, por una parte, un intervalo más amplio de frecuencias admisibles para la señal recibida, por otra parte una simplicidad de realización del dispositivo, y en particular una posibilidad de migración de una tecnología de semiconductor a otra de forma simple y rápida. El diseño de cada circuito se puede realizar a partir de bibliotecas de funciones estándar sin que sea necesario desarrollar componentes específicos, al contrario que en los dispositivos anteriores (por ejemplo las compuertas controladas en tensión en un circuito DLL o los componentes analógicos de un circuito PLL).

- En todo el texto, se designa por "componente digital" cualquier componente electrónico que presenta al menos un borne de entrada y/o salida, conduciendo cada borne una señal cuyo estado puede variar entre una multitud discreta de estados, en particular 1 y 0, sin que el valor analógico real de la señal correspondiente influya en el funcionamiento del componente o del circuito en el cual está integrado. Por otra parte, en todo el texto, los términos "entrada" y "salida" de un componente designan un borne de conexión o un conjunto de bornes de conexión que reciben o, respectivamente, emiten una señal única. La señal aplicada en una entrada o emitida por una salida puede, por lo tanto, ser, salvo que se indique otra cosa, tanto una señal en serie como una señal paralela y puede estar formada por un único canal o por varios canales (en particular en el caso de una arquitectura de tipo diferencial).

- La invención se refiere, por lo tanto, a un dispositivo de extracción de reloj a partir de una señal en serie en banda de base, denominada señal recibida, representativa de unos datos digitales y codificada con una señal de reloj que presenta una frecuencia de reloj bits fsr, que comprende:

- un circuito que recibe una señal procedente de la señal recibida y acompasada a la frecuencia de reloj bits fsr, y

que emite, en al menos una salida de reloj, una señal de reloj, denominada señal de reloj de recepción, al menos

sustancialmente sincronizada y en fase con la frecuencia de reloj bits fsr de la señal recibida;

- un bucle de retroalimentación de fase que comprende:

- una primera entrada conectada a una salida de reloj del circuito que emite una señal de reloj de recepción;

- una segunda entrada alimentada con una señal procedente de la señal recibida;

- un detector digital de fase que comprende un detector de adelanto-retardo conectado a la primera y a la segunda entradas y que emite en al menos una salida una señal digital, denominada señal de estados de fase, representativa de un desplazamiento de fase entre la señal de reloj de recepción y la señal recibida, y del sentido de este desplazamiento;

- una salida que emite una señal, denominada señal de control, conectada a una entrada, denominada entrada de control, del circuito que emite una señal de reloj de recepción, adaptada para que el valor de la frecuencia de la señal de reloj de recepción dependa del valor de la señal de control recibida en esta entrada de control;

- un circuito, denominado circuito contador, que presenta una entrada conectada a dicha salida del detector digital de fase, estando dicho circuito contador adaptado para realizar al menos un filtrado por conteo/desconteo digital en las variaciones de los valores relativos de la señal digital emitidos a lo largo del tiempo por el detector de fase, y para emitir una señal de control en forma digital cuyo valor depende del resultado de este (estos) filtrado(s), estando este valor de la señal de control adaptada para imponer un valor de la frecuencia de la señal de reloj de recepción igual a un valor así filtrado de la frecuencia de reloj bits fsr de la señal de reloj de recepción,

# caracterizado por que:

5

25

30

35

40

45

50

55

- el circuito que emite una señal de reloj de recepción es un oscilador bloqueado en inyección con control digital, que comprende una entrada digital de control adaptada para poder recibir la señal de control emitida por el bucle de retroalimentación de fase en forma digital, y para que el valor de la frecuencia propia fos del oscilador dependa del valor de la señal de control recibida en esta entrada de control;

- el circuito contador comprende dos etapas, que son:

- una primera etapa conectada al detector digital de fase y que cuenta/descuenta, a partir de la señal de estados de fase, las variaciones de fase a partir de un valor medio predeterminado, y que emite una señal digital paralela, denominada señal menos significativa, cuyo valor es representativo de una acumulación de variaciones de estados de fase, en un sentido y/o en el otro, a partir del valor medio;

- una segunda etapa conectada a la primera etapa de tal modo que cuenta/descuenta los rebasamientos de la acumulación de variaciones de estados de fase en el mismo sentido más allá de cada valor extremo (es decir por debajo del valor mínimo (nulo) y por encima del valor máximo) de la señal menos significativa, y adaptada para suministrar en una salida digital paralela dicha señal de control cuyo valor corresponde a la acumulación de los rebasamientos en un sentido y/o en el otro.

- La invención también se extiende a un dispositivo de extracción de reloj y de datos digitales que comprende un dispositivo de extracción de reloj de acuerdo con la invención. Un dispositivo de extracción de reloj y de datos digitales de acuerdo con la invención comprende, además, un circuito de muestreo de la señal recibida con la señal

de reloj de recepción, teniendo este circuito de muestreo una primera entrada, denominada entrada de señal, conectada a la entrada de recepción, y una segunda entrada, denominada entrada de reloj, conectada a una salida de reloj del oscilador bloqueado en inyección, estando este circuito de muestreo adaptado para emitir en al menos una salida de datos, unos datos digitales transmitidos por la señal recibida, y se caracteriza por que comprende al menos un circuito desfasador adaptado para introducir una diferencia de fase constante entre la entrada de señal y la entrada de reloj del circuito de muestreo, estando la diferencia de fase total entre estas dos entradas resultante de cada circuito desfasador adaptada para garantizar una alineación de fase de la señal en la entrada de señal y de la señal en la entrada de reloj.

De manera ventajosa y de acuerdo con la invención, la primera etapa está adaptada para reiniciar el valor de la señal menos significativa en el valor medio después de cada rebasamiento en un sentido.

15

20

25

30

35

65

De acuerdo con una primera forma de realización, de manera ventajosa y de acuerdo con la invención, la primera etapa comprende un sumador que presenta una salida paralela que emite la señal menos significativa, y la segunda etapa comprende un circuito detector de retención de la salida del sumador de la primera etapa, y un sumador que recibe la señal de salida de este circuito detector de retención.

De acuerdo con una segunda forma de realización, de manera ventajosa y de acuerdo con la invención, la primera etapa comprende un contador/descontador que presenta una salida superior de retención y una salida inferior de retención, y la segunda etapa comprende un contador/descontador conectado al contador/descontador de la primera etapa para recibir en la entrada los valores de las salidas de retención.

De manera ventajosa y de acuerdo con la invención, el valor medio se registra en un registro permanente conectado a la primera etapa menos significativa.

Por otra parte, de manera ventajosa y de acuerdo con la invención, la segunda etapa comprende un circuito de entrada limitador de variaciones conectado a la salida digital paralela de la segunda etapa para recibir la señal emitida en la salida por esta segunda etapa, estando este circuito de entrada adaptado para impedir una variación de la señal de control por debajo del valor nulo y por encima del valor máximo de la salida digital paralela de la segunda etapa.

De este modo, la doble etapa del circuito contador de un dispositivo de acuerdo con la invención permite realizar un filtrado eficaz de las señales emitidas por el detector de fase, que permite en particular evitar las inestabilidades de la señal de control del oscilador cuando se detectan diferencias de fase alternas en un sentido y en el otro a partir de un valor límite que activa una variación de la señal de control. En efecto, después de cada modificación de la señal de control, al volver a cargarse el valor medio en la primera etapa, es necesaria una acumulación de varias señales de adelanto de fase o de retardo de fase sucesivas para provocar una nueva modificación de la señal de control.

Este filtrado permite evitar tener en cuenta los fenómenos de derivas de fase accidentales no permanentes como los fenómenos de "jitter". En particular, hay que señalar que las series de bits de datos que presentan un desplazamiento de fase en el mismo sentido que comprenden un número de bits de datos que pueden llegar hasta Nm-1, siendo Nm dicho valor medio, no modifican el valor de la señal de estados de fase filtrada. De este modo, el valor de la señal de control solo se modifica a partir del momento en que el circuito acumulador ha contado/descontado un número umbral predeterminado de bits de datos con un desplazamiento de fase en el mismo sentido entre los flancos de la señal de reloj de recepción y los bits de datos correspondientes de la señal recibida. En un dispositivo digital de acuerdo con la invención, se obtiene en realidad un filtrado similar al que se obtiene en un bucle de retroalimentación de fase de tipo analógico.

De manera ventajosa y de acuerdo con la invención, el detector de adelanto-retardo está adaptado para emitir en una primera salida una señal digital representativa de la presencia de un adelanto de fase entre la señal de reloj de recepción y la señal recibida, y en una segunda salida una señal digital representativa de la presencia de un retardo de fase entre la señal de reloj de recepción y la señal recibida.

De manera ventajosa y de acuerdo con la invención, el detector de adelanto-retardo está adaptado para muestrear la señal recibida en los flancos ascendentes y descendentes de la señal de reloj de recepción. De manera más particular y ventajosa, y de acuerdo con la invención, el detector de adelanto-retardo está adaptado para realizar un doble muestreo, uno en fase con los flancos de la señal de reloj de recepción, el otro en cuadratura con los flancos de la señal de reloj de recepción de tal modo que determina el estado intermedio de la señal recibida.

60 En una forma de realización de la invención, la señal más significativa y la entrada de control digital paralela del oscilador bloqueado en inyección comprenden 5 bits.

Hay que señalar que debido a la función de conteo/desconteo, los M bits de datos de una serie de bits de datos con los mismos desplazamientos de fase que activan una modificación de la salida de control no son necesariamente todos sucesivos. Por ejemplo, pueden estar por el contrario separados por unos bits de datos para los cuales no se detecta ningún desplazamiento de fase, e incluso por unos bits de datos que presentan un desplazamiento de fase

en sentido contrario, posteriormente compensados por otros bits de datos subsiguientes. Este segundo tipo de filtrado detecta, por lo tanto, una deriva general de la fase en al menos M bits de datos.

Por otra parte, de manera ventajosa y de acuerdo con la invención, un dispositivo de acuerdo con la invención se caracteriza por que comprende un circuito, en particular un convertido decisional, que presenta al menos una entrada conectada respectivamente a la(s) salida(s) del detector de adelanto-retardo, y que emite en al menos una salida una señal digital, denominada señal de estados de fase filtrada:

- que tiene un primer valor relativo tras la recepción de un número predeterminado N superior a 1 de valores idénticos sucesivos en la entrada, que corresponde a N bits de datos sucesivos de la señal recibida para los cuales el detector de adelanto-retardo ha detectado un desplazamiento de fase en el mismo sentido;

- que tiene un segundo valor relativo tras la recepción de N valores idénticos sucesivos en la entrada, que corresponde a N bits de datos sucesivos de la señal recibida para los cuales el detector de adelanto-retardo ha detectado un desplazamiento de fase en el otro sentido;

- que tiene un tercer valor relativo en los demás casos;

5

10

15

20

25

30

35

40

45

50

55

60

65

de tal modo que el valor relativo de la señal de estados de fase filtrada es representativo de la presencia de un desplazamiento de fase en el mismo sentido, y del sentido de este desplazamiento de fase, para N bits de datos sucesivos de la señal recibida, entre los flancos de la señal de reloj de recepción y los bits de datos correspondientes de la señal recibida.

De manera ventajosa y de acuerdo con la invención, la salida de dicho circuito que emite la señal de estados de fase filtrada está conectada a la entrada del circuito contador. En una forma de realización de la invención, N = 2. No obstante, se puede seleccionar cualquier otro valor, según el nivel de filtrado deseado. En efecto, dicho convertidor decisional tiene como efecto realizar un primer filtrado a partir de valores relativos de los desplazamientos de fase detectados por el detector de fase digital. Este primer filtrado permite asimilar al ruido los desplazamientos de fase accidentales, puesto que solo una serie de N estados idénticos del desplazamiento de fase tendrá un efecto en la salida del convertidor decisional. Tradicionalmente, este primer filtrado permite evitar tener en cuenta los fenómenos de derivas de fase accidentales no permanentes como los fenómenos de "jitter". En particular, hay que señalar que las series de bits de datos que presentan un desplazamiento de fase en el mismo sentido que comprenden un número de bits de datos que puede llegar hasta N-1 no modifican el valor de la señal de estados de fase filtrada.

El primer filtrado permite minimizar el riesgo de una variación de la señal de control de alta frecuencia cuando los datos presentan una deriva de fase accidental ("jitter"). Hay que señalar que en algunas formas de realización de un dispositivo de acuerdo con la invención, no se prevé este primer filtrado, pudiendo considerarse suficiente el filtrado que realiza el circuito contador de doble etapa.

El hecho de realizar el circuito contador por medio de varios sumadores y/o varios contadores en cascada con un dispositivo de recarga de un valor medio, cuando se ha superado dicho valor umbral, de tal modo que el circuito contador retoma el conteo/desconteo a partir de este valor medio, ofrece un segundo filtrado que permite evitar los fenómenos de inestabilidades en alta frecuencia debidos a las variaciones alternas de la señal de estados de fase alrededor de un valor que ha activado una modificación de la señal de control.

Este filtrados digitales entre el detector de fase y la entrada digital de control del oscilador bloqueado en inyección permiten prescindir de cualquier componente específico de filtrado dentro del bucle de retroalimentación de fase.

En una forma de realización ventajosa y de acuerdo con la invención, la entrada digital de control del oscilador bloqueado en inyección está conectado a un circuito que comprende una multitud de conmutadores, estando cada conmutador conectado en serie con al menos un condensador integrado dentro del circuito del oscilador de tal modo que modifica su frecuencia propia. De manera ventajosa y de acuerdo con la invención, cada bit de la entrada digital de control está conectado a uno de los conmutadores.

Además, de manera ventajosa y de acuerdo con la invención, el circuito de extracción de reloj comprende, además, un circuito, denominado generador de impulsos de sincronización, que genera una señal de impulsos de corriente en la frecuencia de flancos de la señal recibida, y adaptado al funcionamiento del oscilador bloqueado en inyección, estando este generador de impulsos de sincronización adaptado para emitir la señal de impulsos de corriente en una salida única conectada únicamente a una entrada de corriente del oscilador bloqueado en inyección. Los impulsos de corriente emitidos por este generador de impulsos de sincronización están adaptados a la entrada del oscilador en inyección de tal modo que garantizan su funcionamiento, es decir el bloqueo del oscilador en la frecuencia de reloj bits fsr.

Por otra parte, se puede utilizar cualquier tipo de oscilador bloqueado en inyección dentro del marco de la invención. Puede tratarse en particular de un oscilador de relajación de tipo RC o con fuente de corriente, de un oscilador astable con compuertas lógicas o emisores acoplados, de un oscilador de anillo, de un oscilador casi senoidal en puente de Wien, desplazamiento de fase o LC, de un oscilador Colpitts, Hartley, Clapp, Pierce o de resistencia negativa con circuito resonante LC, con líneas de transmisión o resonador de tipo cuarzo, resonador con ondas de superficie, con MEMS o piezo-eléctrico integrado.... No obstante, de manera ventajosa y de acuerdo con la

invención, el oscilador bloqueado en inyección es del tipo formado por un circuito resonante LC. Dicho oscilador presenta en particular la ventaja de minimizar la deriva de fase ("jitter") intrínseca. De manera más particular y ventajosa, y de acuerdo con la invención, el oscilador bloqueado en inyección comprende dos ramas que comprenden cada una un transistor con efecto de campo de resistencia negativa, estando los dos transistores acoplados de acuerdo con una topología diferencial. Puede tratarse de un oscilador como el que se describe en el documento FR 2838265.

5

10

15

20

25

30

35

55

De este modo, la invención permite aportar unas ventajas decisivas en el diseño de los dispositivos de extracción de reloj, y de manera más particular de los dispositivos de extracción de reloj y de datos digitales, al permitir una utilización a escala industrial de un circuito cuyo funcionamiento se basa en un oscilador bloqueado en inyección.

En particular, un dispositivo de acuerdo con la invención carece de bomba de carga y de filtro de bucle, y de manera más general de componente analógico en el bucle de retroalimentación de fase. Por lo tanto, en un dispositivo de acuerdo con la invención el bucle de retroalimentación de fase se puede desarrollar con un diseño homogéneo, completamente digital, simple y rápido.

Un dispositivo de acuerdo con la invención también es completamente autónomo, es decir no precisa ningún ajuste externo manual o de otro tipo, ni ninguna calibración. De este modo, de manera ventajosa, un dispositivo de acuerdo con la invención carece de cualquier medio de ajuste manual externo. Además, esta autonomía se obtiene con una gran simplicidad de realización.

Un dispositivo de acuerdo con la invención tampoco precisa la presencia de una referencia de frecuencia externa, a diferencia de un PLL tradicional. Además, unos cuantos bits de datos bastan para garantizar la sincronización en el arranque. Debido a su extrema simplicidad, la arquitectura de un dispositivo de acuerdo con la invención permite su realización con un muy reducido número de componentes elementales con un bajo consumo de energía (por lo tanto, una superficie total reducida y un menor consumo total). Un dispositivo de acuerdo con la invención también puede diseñarse en tecnología digital, en particular en lo que se refiere al bucle de retroalimentación de fase, sin que sea necesaria la intervención de un diseñador con una gran experiencia (al contrario que en los dispositivos anteriores basados en PLL en los cuales resulta difícil en particular realizar un comparador fase/frecuencia que funciona en alta frecuencia). También es posible, con un dispositivo de acuerdo con la invención de diseño simple, alcanzar unas velocidades de transmisión próximas a los límites que ofrece la tecnología de semiconductores. En este caso particular es posible alcanzar unas velocidades de transmisión sustancialmente más elevadas que con unos circuitos anteriores basados en PLL o en DLL. Además, es posible realizar un dispositivo de acuerdo con la invención con una tecnología de semiconductores cualquiera (CMOS, bipolar, SiGe...).

Al contrario que un circuito basado en DLL, un dispositivo de acuerdo con la invención es poco sensible a los ruidos en la señal recibida, y la codificación de los datos presenta una tasa de expansión similar a la de un PLL tradicional, es decir muy inferior al que se precisa para un DLL.

Por otra parte, teniendo en cuenta la simplicidad y la eficacia del bucle de retroalimentación de fase, en un dispositivo de acuerdo con la invención, la frecuencia propia fos del oscilador es siempre igual a la frecuencia de reloj bits fsr de la señal de reloj de recepción, por consiguiente la distancia de fase entre la señal de reloj emitida por el oscilador y la señal recibida es fija. Ahora bien, el conjunto de los demás elementos constitutivos del dispositivo pueden provocar un desplazamiento de fase constante entre las dos entradas del circuito de muestreo, se puede determinar el retardo diferencial de fase estructural constante entre estas dos entradas del circuito de muestreo. Por lo tanto, basta con prever uno (o varios) circuito(s) desfasador(es) para garantizar una alineación de fase entre las dos entradas del circuito de muestreo, sin que sea necesario ningún ajuste exterior, para que el dispositivo de acuerdo con la invención pueda funcionar de forma autónoma y estable con un amplio intervalo de captura. Además, en un dispositivo de acuerdo con la invención, el circuito de muestreo puede estar simplemente compuesto por un simple biestable D.

A este respecto hay que señalar que este (estos) circuito(s) desfasador(es) está(n) previsto(s) como suplemento al eventual circuito desfasador a veces necesariamente previsto en la entrada de un circuito, como un comparador de fase, para compensar los desplazamientos de fase que introducen determinadas arquitecturas de este tipo de circuito. Dicho circuito desfasador necesario para el funcionamiento de un comparador de fase al que alimenta, es funcionalmente diferente al (a los) circuito(s) desfasador(es) de un dispositivo de acuerdo con la invención, cuya función es introducir un desplazamiento de fase suplementario para compensar el desplazamiento de fase total entre las dos entradas del circuito de muestreo.

- De manera ventajosa, un dispositivo de acuerdo con la invención se realiza en forma de al menos un circuito integrado que incorpora al menos el oscilador bloqueado en inyección. Un dispositivo de extracción de reloj y de datos digitales de acuerdo con la invención está adaptado para poder funcionar con una frecuencia de reloj bits fsr superior a 500 MHZ.

- De este modo, la invención permite obtener, por primera vez, un circuito de extracción de reloj, y de manera más particular un circuito de extracción de reloj y de datos digitales, perfectamente autónomo y estable, que puede ser

objeto de una utilización a escala industrial en numerosas aplicaciones.

5

15

35

40

45

50

55

60

65

La invención también se refiere a un dispositivo de extracción de reloj, y de manera más particular a un dispositivo de extracción de reloj y de datos digitales, caracterizado en combinación por todas o parte de las características mencionadas con anterioridad o que se mencionan a continuación.

Se mostrarán otros objetivos, características y ventajas de la invención con la lectura de la siguiente descripción que se da a título no limitativo y que se refiere a las figuras adjuntas, en las que:

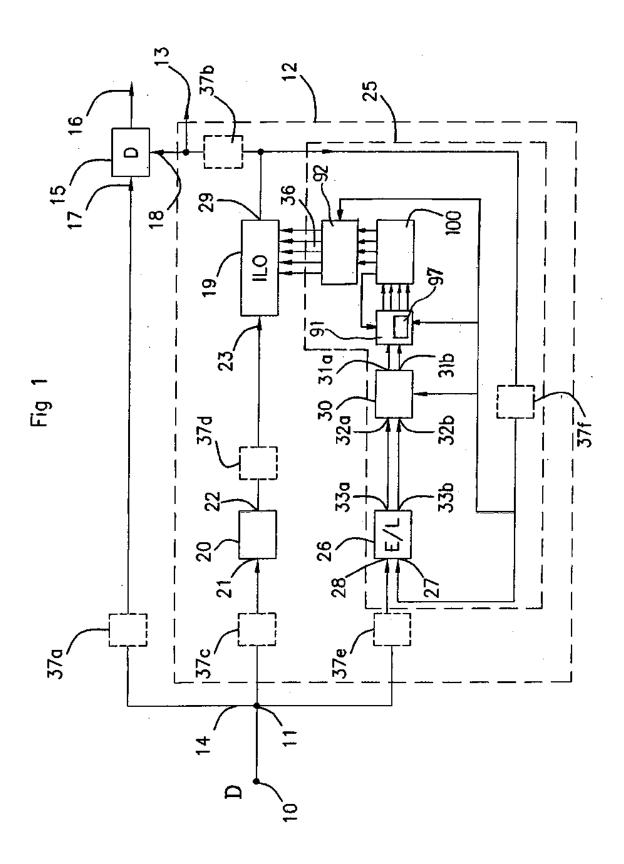

- la figura 1 es un esquema sinóptico funcional general que ilustra un dispositivo de extracción de reloj y de datos digitales de acuerdo con una primera forma de realización de la invención;

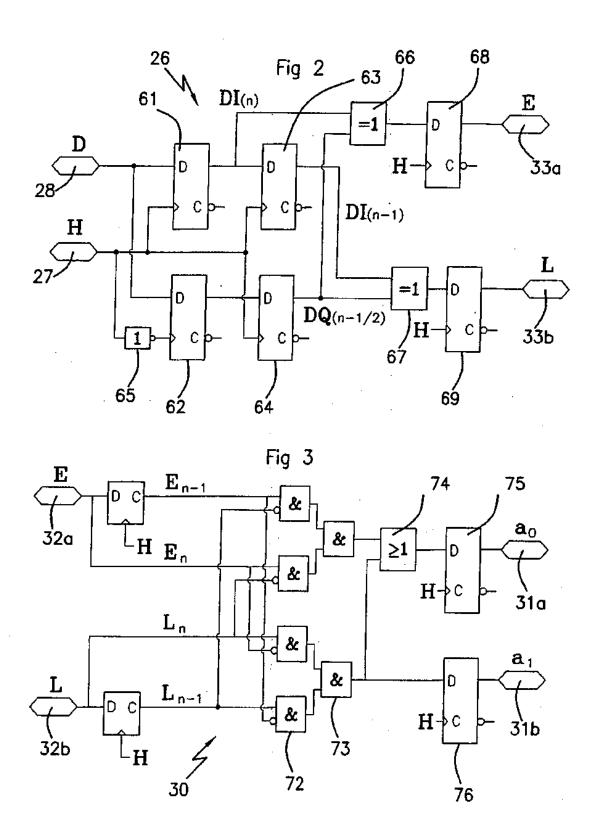

- la figura 2 es un esquema sinóptico funcional de una forma de realización del detector adelanto/retardo del dispositivo de la figura 1;

- la figura 3 es un esquema sinóptico funcional de una forma de realización del convertidor decisional del dispositivo de la figura 1;

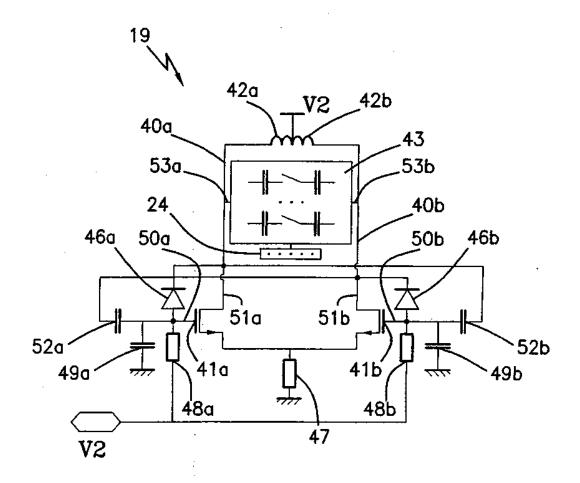

- la figura 4 es un esquema que ilustra una forma de realización de un oscilador bloqueado en inyección que se puede usar en un dispositivo de acuerdo con la invención;

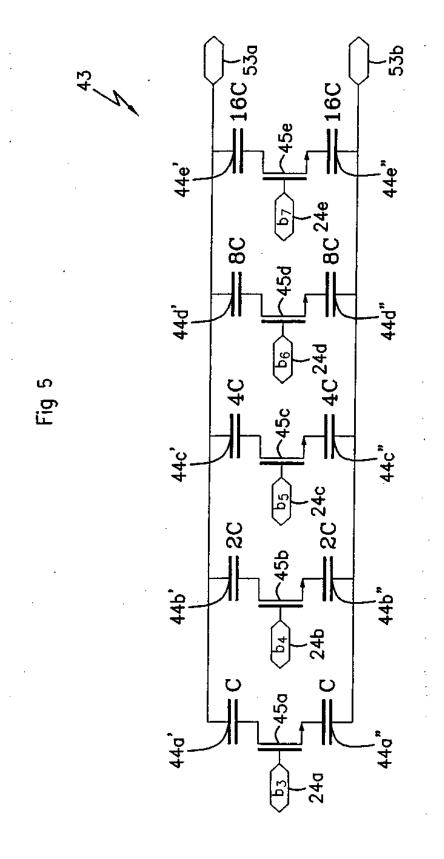

- la figura 5 es un esquema que ilustra un ejemplo de realización de un bloque de capacidades en la entrada digital de control del oscilador de la figura 4;

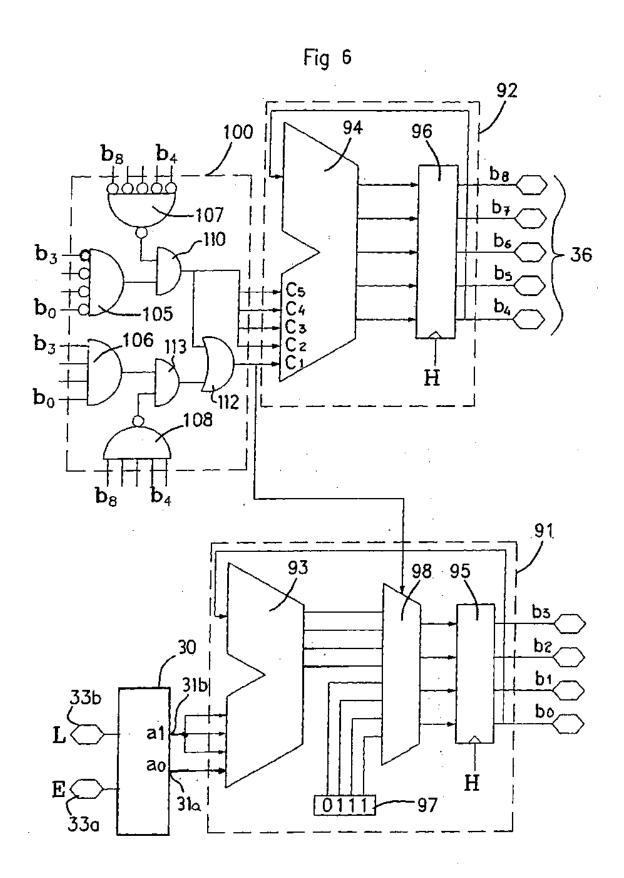

- la figura 6 es un esquema que ilustra una primera forma de realización de un circuito contador de un dispositivo de acuerdo con la invención;

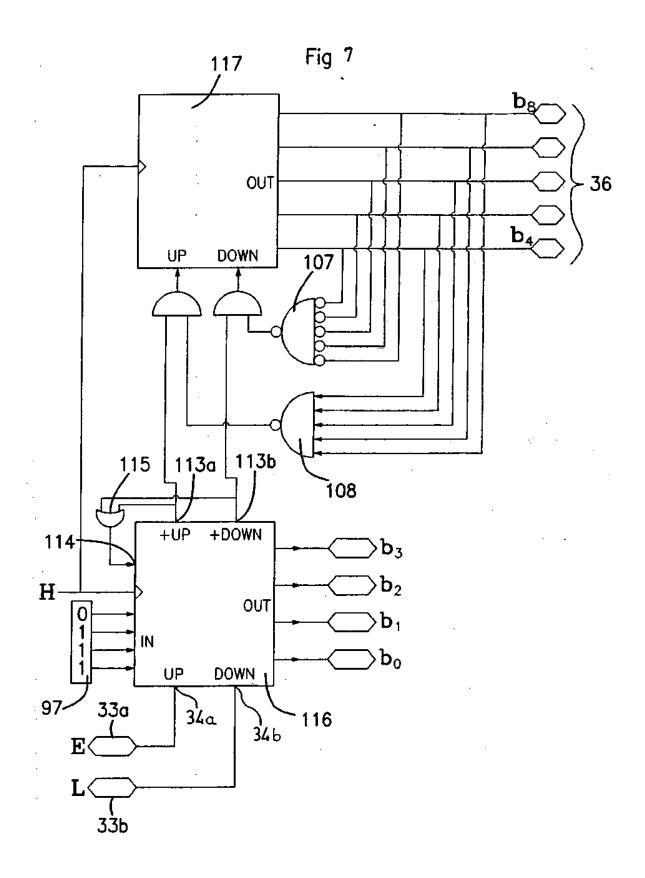

- la figura 7 es un esquema que ilustra una segunda forma de realización de un circuito contador de un dispositivo de acuerdo con la invención.

- Un dispositivo de extracción de reloj y de datos digitales de acuerdo con la invención representado en la figura 1 recibe en una entrada principal, denominada entrada de recepción 10, una señal, denominada señal recibida, que es una señal en serie en banda de base representativa de unos datos digitales D y está codificada con una señal de reloj que presenta una frecuencia de reloj bits fsr. Por lo general, esta señal recibida es una señal codificada del tipo NRZ ("non return to zero") recibida en un canal de transmisión de una conexión en serie en banda de base. Este canal de transmisión puede estar formado por un hilo conductor eléctrico único, o por una fibra óptica única, o por una conexión de radio frecuencia monocanal (señal no diferencial). Sin embargo la invención también se puede aplicar en el caso de una señal recibida del tipo transmitida en diferencial, comprendiendo entonces el canal de transmisión dos líneas que transmiten dos componentes en oposición de fase. La invención también se puede aplicar a otros tipos de codificación de la señal recibida, por ejemplo NRZI ("non return to zero inverted").

- La entrada de recepción 10 está conectada a un nodo de derivación 11 al cual están conectadas dos ramas en paralelo, es decir una primera rama de extracción de reloj 12 de acuerdo con la invención y que genera en una salida de reloj 13 una señal de reloj, denominada señal de reloj de recepción H, sincronizada y en fase con la frecuencia de reloj bits fsr de la señal recibida, y otra segunda rama 14 que comprende un circuito de muestreo 15 de la señal recibida con la señal de reloj de recepción H, estando este circuito de muestreo 15 adaptado para emitir, en una salida de datos 16, unos datos digitales transmitidos por la señal recibida.

- El circuito de extracción de reloj 12 comprende un oscilador bloqueado en inyección 19 alimentado por un generador de impulsos de sincronización 20, presentando este último una entrada 21 conectada al nodo 11 de la entrada de recepción 10. El generador de impulsos de sincronización 20 presenta una salida única 22 (que puede estar formada por dos líneas en el caso de una topología diferencial) conectada únicamente a la entrada de corriente 23 del oscilador bloqueado en inyección 19. La señal de impulsos de corriente suministrada por el generador de impulsos de sincronización 20 está adaptada al funcionamiento del oscilador bloqueado en inyección 19 y está acompasada a la frecuencia de flancos de los datos D de la señal recibida. El conjunto se puede realizar, por ejemplo, como se describe en el documento FR 2838265. En particular, el oscilador bloqueado en inyección19 es entonces del tipo formado por un circuito resonante LC simétrico que define la frecuencia de oscilaciones libres fos de oscilación, y provisto de dos ramas cruzadas que comprenden cada una un transistor de efecto de campo con resistencia negativa, estando de este modo los dos transistores acoplados de acuerdo con una topología diferencial. El oscilador bloqueado en inyección 19 presenta una salida de reloj 29 que emite una señal de reloj sincronizada y en fase con la frecuencia de reloj bits de la señal recibida.

- El circuito de muestreo 15 comprende una primera entrada, denominada entrada de señal 17, conectada mediante la segunda rama 14 a la entrada de recepción 10, y una segunda entrada, denominada entrada de reloj 18, conectada a la salida de reloj del circuito de extracción de reloj 12, es decir a la salida de reloj 29 del oscilador 19. Este circuito de muestreo 15 puede estar formado por un simple biestable D.

- El oscilador bloqueado en inyección 19 comprende, por otra parte, una entrada, denominada entrada de control 24 adaptada para que el valor de la frecuencia propia fos del oscilador dependa del valor de la señal digital de control recibida en esta entrada de control 24. La entrada de control 24 es una entrada paralela digital que, en el ejemplo que se representa, comprende 5 bits 24a, 24b, 24c, 24d, 24e.

El oscilador 19 se puede realizar a partir de cualquier tipo de oscilador siempre que se pueda adaptar para presentar una entrada de control digital 24 como se describe a continuación. Puede tratarse en particular de un oscilador de relajación de tipo RC o con fuente de corriente, de un oscilador astable con compuertas lógicas o emisores acoplados, de un oscilador de anillo, de un oscilador casi senoidal en puente de Wien, desplazamiento de fase o LC, de un oscilador Colpitts, Hartley, Clapp, Pierce o con resistencia negativa con circuito resonante LC, con líneas de transmisión o resonador de tipo cuarzo, resonador con ondas de superficie, con MEMS o piezo-eléctrico integrado...

5

10

15

20

25

30

45

50

55

60

El oscilador 19 se realiza, por ejemplo, como se describe en el documento FR 2838265 y está representado de manera esquemática en la figura 4. Es por tanto del tipo formado por un circuito resonante LC simétrico que define la frecuencia de oscilaciones libres fos, y está provisto de dos ramas cruzadas 40a, 40b que comprende cada una un transistor de efecto de campo 41a, respectivamente 41b con resistencia negativa, estando de este modo los dos transistores 41a, 41b acoplados de acuerdo con una topología diferencial. El par de transistores 41a, 41b se carga por un circuito LC simétrico que define la frecuencia de oscilación a partir de una tensión de referencia de polarización V2 aplicada entre dos inductancias 42a, respectivamente 42b, y de una fuente de corriente 47 cuya salida está en el potencial más bajo y que puede estar simplemente formada por una resistencia en serie conectada a un nodo de unión de las dos fuentes de los transistores 41a, 41b.

Cada transistor 41a, 41b está, por otra parte, polarizado por una tensión de polarización V1 apropiada aplicada en su drenaje 50a, 50b por medio de una resistencia en serie 48a, 48b y por una capacidad paralela 49a, 49b.

Las capacidades paralelas del circuito resonante LC están formadas por un bloque 43 de capacidades asociadas cada una respectivamente a un conmutador 45a, 45b, 45c, 45d, 45e, recibiendo cada conmutador uno de los bits 24a, 24b, 24c, 24d, 24e de la entrada digital paralela 24 de control del oscilador 19. Las capacidades paralelas están asociadas de tal modo que la variación de un incremento (una unidad) de la señal digital recibida en la entrada 24 provoca una variación de un mismo valor Δf de la frecuencia de oscilación fos del oscilador 19. En la forma de realización de la figura 8, cada conmutador 45a, 45b, 45c, 45d, 45e, está interpuesto entre dos condensadores 44a', 44b', 44c', 44d', 44e', y respectivamente 44a'', 44b'', 44d'', 44e'', de mismo valor dispuestos simétricamente en serie con respecto a este conmutador, formando estos dos condensadores dicha capacidad asociada al conmutador. Cada conmutador 45a, 45b, 45c, 45d, 45e, está formada por un transistor de efecto de campo, y los valores de las capacidades son iguales a 2<sup>n</sup> x 2C, siendo n el rango (0, 1, 2, 3, 4) del bit b3, b4, b5, b6, b7 considerado de la señal digital de control aplicada en la entrada digital 24a, 24b, 24c, 24d, 24e, siendo C un valor predeterminado de capacidad, y siendo el valor de capacidad de cada condensador 44a', 44a'', 44b'', 44c'', 44c'', 44d'', 44d'', 44e'' respectivamente igual a C, C, 2C, 2C, 4C, 4C, 8C, 8C, 16C, 16C como se representa en la figura 7.

35 El valor del paso de variación Δf se selecciona lo suficientemente pequeño, de preferencia inferior al 1 % del valor medio de la frecuencia de oscilación fos, en particular del orden de un 0,3 % de este valor medio. Por ejemplo, Δf es del orden de 30 MHz para una frecuencia de oscilación fos del orden de 10 GHz.

La amplitud de oscilación del oscilador 19 se controla por medio de dos diodos 46a, respectivamente 46b montados entre el drenaje 50a, 50b y la compuerta 51a, 51b de cada transistor 41a, 41b correspondiente por medio de una capacidad de filtrado 52a, 52b.

El circuito de extracción de reloj 12 del dispositivo de acuerdo con la invención comprende un bucle de retroalimentación de fase 25 completamente formado por componentes digitales. Este bucle de retroalimentación de fase 25 comprende un detector de adelanto-retardo 26 que presenta dos entradas 27, 28. La primera entrada 27 del detector de adelanto-retardo 26 está conectada a la salida 29 del oscilador 19 de tal modo que recibe la señal de reloj de recepción H generada por el oscilador en esta salida 29. La segunda entrada 28 está conectada al nodo de derivación 11 y, por lo tanto, a la entrada de recepción 10. De este modo, la señal recibida se emite en la segunda entrada 28 del detector de adelanto-retardo 26.

En la figura 2 se representa una forma de realización del detector de adelanto-retardo 26. Este detector adelanto-retardo 26 presenta dos salidas digitales paralelas 33a, 33b en cada una de las cuales emite una señal, denominada señal de estados de fase E, respectivamente L, representativa de la existencia y del sentido de un desplazamiento de fase entre sus dos entradas 27, 28, es decir entre los datos D de la señal recibida y la señal de reloj de recepción H suministrada por el oscilador 19. En particular, las señales E y L emitidas respectivamente en las salidas digitales paralelas 33a, 33b del detector de adelanto-retardo 26 son nulos cuando las señales en sus dos entradas 27, 28 están en fase. La primera salida 33a del detector de adelanto-retardo 26 es una señal digital E de 1 bit que identifica la presencia de un adelanto de fase entre las dos entradas 27, 28. En el ejemplo descrito, esta señal E es igual a 1 cuando se detecta un adelanto de fase, y es igual a 0 cuando las dos entradas 27, 28 están en fase. La segunda salida 33b del detector de adelanto-retardo 26 emite una señal digital L de 1 bit que identifica la presencia de un retardo de fase entre las dos entradas 27, 28. En el ejemplo descrito, esta señal L es igual a 1 cuando se detecta un retardo de fase, y es igual a 0 cuando las dos entradas 27, 28 están en fase.

Se puede utilizar cualquier tipo de detector de adelanto-retardo 26 digital en un dispositivo de acuerdo con la invención. Puede tratarse en particular de una celda de Alexander (véase J. D. H. Alexander "Clock recovery from random binary signals", en Electronics Letters, 30 de octubre de 1975, vol. 11, n°. 22). De este modo, en la forma de

realización que se representa en la figura 2, el detector de adelanto-retardo 26 está formado por una celda de Alexander basada en un doble muestreo de la señal recibida, una primera vez en fase con la señal de reloj de recepción H, una segunda vez en cuadratura con esta señal. De este modo este detector de adelanto-retardo 26 comprende una primera etapa de dos biestables D 61, 62, que reciben la señal recibida y la señal de reloj de recepción H, estando una compuerta de desplazamiento en cuadratura 65 interpuesta en la entrada del segundo biestable D 62 de la primera etapa en su borne que recibe la señal de reloj. El detector 26 comprende una segunda etapa de dos biestables D 63, 64 y dos compuertas O exclusiva 66, 67 para formar las señales representativas del desplazamiento de fase. La salida del primer biestable 61 de la primera etapa proporciona una señal DI(n) representativa del muestreo en fase de un bit n de la señal recibida. La salida del primer biestable 63 de la segunda etapa conectada a continuación del primer biestable 61 de la primera etapa, suministra una señal DI(n-1) representativa del muestreo en fase del bit n-1 que precede inmediatamente a dicho bit n en la señal recibida. La salida del segundo biestable 62 de la primera etapa suministra una señal DQ(n+1/2) representativa del muestreo en cuadratura entre los bits de datos n y n+1. La salida del segundo biestable 64 de la segunda etapa proporciona una señal DQ(n-1/2) representativa del muestreo en cuadratura entre los bits de datos n v n-1. Por otra parte, están previstos dos biestables D 68, 69 para formar un registro de salida que permite sincronizar las señales con el reloj de recepción.

La siguiente tabla 1 es una tabla de verdad de un ejemplo de dicho detector de adelanto-retardo 26:

| 2 | 0 |  |

|---|---|--|

|   |   |  |

5

10

15

# 25

# 30

# 35

40

45

50

55

60

65

|          |          | TABLA  | 1: |   |             |

|----------|----------|--------|----|---|-------------|

| DI (n-1) | DQ (n-½) | DI (n) | Е  | L | Significado |

| 0        | 0        | 0      | 0  | 0 | en fase     |

| 0        | 0        | 1      | 1  | 0 | adelanto    |

| 0        | 1        | 0      | 1  | 1 | imposible   |

| 0        | 1        | 1      | 0  | 1 | retardo     |

| 1        | 0        | 0      | 0  | 1 | retardo     |

| 1        | 0        | 1      | 1  | 1 | imposible   |

| 1        | 1        | 0      | 1  | 0 | adelanto    |

| 1        | 1        | 1      | 0  | 0 | en fase     |

Hay que señalar que el detector digital de fase formado por el detector de adelanto-retardo 26 permite detectar únicamente la existencia de un desplazamiento de fase y su sentido, pero no la amplitud de este desplazamiento de fase.

Las dos salidas 33a, 33b del detector de adelanto-retardo 26 están conectadas respectivamente a dos entradas 32a, 32b de un circuito convertidor decisional 30 del bucle de retroalimentación de fase, cuyo ejemplo de realización se da en la figura 3. Este circuito convertidor decisional 30 permite emitir en una salida digital paralela a dos bornes 31a, 31b una señal digital, denominada señal de estados de fase filtrada, con tres estados en función de los valores que toma la señal de estado de fase, es decir las señales de adelanto E y de retardo L emitidas para cada bit de datos de la señal que recibe el convertidor adelanto-retardo 26.

El convertidor decisional 30 solo modifica el valor de la señal de estados de fase filtrada emitida en su salida digital paralela cuando recibe de forma sucesiva un número predefinido de valores idénticos en sus entradas 32a, 32b, que corresponde a un número predefinido de bits de datos sucesivos de la señal recibida para los cuales el detector de adelanto-retardo 26 ha detectado un desplazamiento de fase en el mismo sentido.

La señal de estados de fase filtrada es, por ejemplo, una señal binaria con signo codificada en dos bits a0 y a1, correspondiendo cada bit a uno de los dos bornes de salida 31a, 31b. Cuando los desplazamientos de fase de los bits de datos sucesivos detectados son en un primer sentido, por ejemplo cuando la señal de reloj de recepción H está adelantada, la señal de estados de fase filtrada es igual a 1, codificada por los valores a0 = 1, y a1 = 0. Cuando los desplazamientos de fase de los bits de datos sucesivos detectados son en el otro sentido, por ejemplo cuando la señal de reloj de recepción H está retrasada, la señal de estados de fase filtrada es igual a -1, codificada por los valores a0 = a1 = 1. Cuando los bits de datos están en fase, la señal de estados de fase filtrada es nula, codificada por los valores a0 = a1 = 0.

Por consiguiente, el convertidor decisional 30 tiene como función realizar un filtrado de las variaciones del desplazamiento de fase detectadas por el detector 26 con el fin de tener en cuenta únicamente los desplazamientos de fase que se reproducen en un número N superior a 1 de bits de datos sucesivos de la señal recibida. El convertidor decisional 30 también tiene como función convertir las señales de estados de fase E y L en señales de estados de fase filtradas a0 y a1.

Este convertidor decisional 30 comprende, en primer lugar, una etapa de dos biestables D 70, 71 que permiten memorizar los estados E(n-1), L(n-1) de cada una de las señales E y, respectivamente L, recibidas en sus entradas 32a, 32b para un bit n-1 con respecto al estado E(n), L(n) de estas señales para un bit n inmediatamente sucesivo. El convertidor decisional 30 comprende, además, dos etapas de compuertas Y 72, 73 y una compuerta O 74 que permite, en el ejemplo representado, detectar los estados de cada una de las señales E y, respectivamente L, recibidas en sus entradas 32a, 32b, que siguen siendo idénticos en dos bits de datos sucesivos. Basta con multiplicar los biestables D de entrada y las compuertas Y para aumentar el número de bits de datos sucesivos que tiene en cuenta el convertidor decisional.

Por otra parte, se prevén dos biestables D 75, 76 para formar un registro de salida que permita sincronizar las señales a0, a1 emitidas en los bornes de salida 31a, 31b del convertidor decisional 30 con el reloj de recepción.

La siguiente tabla 2 es una tabla de verdad de un ejemplo de convertidor decisional 30 para el cual N = 2:

TABLA 2:

5

15

20

25

30

35

40

45

50

55

|      |                    |      |                    |                |                       | TABLA 2:                                       |                                                   |

|------|--------------------|------|--------------------|----------------|-----------------------|------------------------------------------------|---------------------------------------------------|

| E(n) | E <sub>(n-1)</sub> | L(n) | L <sub>(n-1)</sub> | a <sub>1</sub> | <b>a</b> <sub>0</sub> | Valor relativo de la señal de conteo/desconteo | Observaciones                                     |

| 0    | 0                  | 0    | 0                  | 0              | 0                     | +0                                             | -                                                 |

| 1    | 0                  | 0    | 0                  | 0              | 0                     | +0                                             | 1 <sup>er</sup> ciclo en el que E = 1             |

| 1    | 1                  | 0    | 0                  | 0              | 1                     | +1                                             | 2º ciclo sucesivo en el<br>que E = 1              |

| 1    | 1                  | 0    | 0                  | 0              | 1                     | +1                                             | 3 <sup>er</sup> ciclo sucesivo en el<br>que E = 1 |

| 0    | 1                  | 0    | 0                  | 0              | 0                     | +0                                             | 1 <sup>er</sup> ciclo en el que E<br>vuelve a 0   |

| 0    | 0                  | 0    | 0                  | 0              | 0                     | +0                                             |                                                   |

| 0    | 0                  | 1    | 0                  | 0              | 0                     | +0                                             | 1 <sup>er</sup> ciclo en el que L = 1             |

| 0    | 0                  | 1    | 1                  | 1              | 1                     | -1                                             | 2º ciclo sucesivo en el<br>que L = 1              |

| 0    | 0                  | 1    | 1                  | 1              | 1                     | -1                                             | 3 <sup>er</sup> ciclo sucesivo en el<br>que L = 1 |

| 0    | 0                  | 0    | 1                  | 0              | 0                     | +0                                             | 1 <sup>er</sup> ciclo en el que L<br>vuelve a 0   |

| 0    | 0                  | 0    | 0                  | 0              | 0                     | +0                                             |                                                   |

| 0    | 0                  | 0    | 0                  | 0              | 0                     | +0                                             |                                                   |

Los dos bornes de salida 31a, 31b del convertidor decisional 30 están conectados a dos bornes de entrada de un circuito contador de dos etapas 91, 92 del bucle de retroalimentación de fase. Este circuito contador está adaptado para acumular los valores relativos +1, 0, -1 de la señal de estados de fase filtrada. En el ejemplo descrito, el circuito contador presenta una salida paralela 36 de 5 bits en la cual se aplica el resultado de la acumulación.

En la primera forma de realización que se representa en las figuras 1 y 6, el circuito contador comprende dos etapas de sumadores 91, 92, cuya primera etapa de sumador 91 de nivel bajo suministra en la salida unos bits menos significativos, esto es 4 bits menos significativos b0, b1, b2, b3 en el ejemplo representado, y una segunda etapa de sumador 92 de nivel alto que suministra en la salida unos bits de señal de control, esto es 5 bits b4, b5, b6, b7, b8 en el ejemplo representado.

La primera etapa de sumador 91 comprende un circuito sumador 93 que comprende dos entradas digitales paralelas de 4 bits que suministran en una salida digital de 4 bits la suma de las dos entradas. La primera entrada de este circuito sumador 93 se alimenta a partir de la señal de estados de fase E, L mediante las salidas 33a, 33b del detector de adelanto-retardo 26 a través del convertidor decisional 30. La salida 31b del convertidor decisional 30 que emite la señal de estados de fase filtrada a1 está conectada a tres entradas del sumador 93. Si E = 1, el convertidor decisional 30 envía la señal 0001 (correspondiente al valor relativo +1) a la entrada del circuito sumador 93. Si L = 1, el convertidor decisional 30 envía la señal 1111 (correspondiente al valor relativo -1) a la entrada del circuito sumador 93. La salida del circuito sumador 93 está conectada a la entrada de un multiplexor 98 que también

recibe en la entrada un valor registrado en un registro 97 de 4 bits. Este valor es un valor medio, es decir un valor a partir del cual es preciso contar un mismo número de variaciones (no necesariamente inmediatamente sucesivas) en un sentido o en el otro para activar una modificación del valor de la entrada de control del oscilador 19, es decir de la señal en la salida de la segunda etapa de sumador 92. En el ejemplo representado, el registro 97 contiene el valor 0111, de tal modo que la señal de control solo se modificará a partir de la detección de un desequilibrio de 7 u 8 estados en el mismo sentido (u otro número según el valor contenido en el registro 97).

5

10

15

20

25

30

45

50

60

65

La salida del multiplexor 98 es una salida de 4 bits paralelos enviada a un registro 95 acompasado por la señal de reloj de recepción H. Este registro 95 suministra los bits de salida menos significativos b0, b1, b2, b3, que se envían a la segunda entrada del circuito sumador 93 mediante una conexión en bucle.

La segunda etapa de sumador 92 comprende un circuito sumador 94 de 5 bits alimentado por un circuito 100 de cálculo de retención que detecta los valores extremos (inferior nulo y superior) de la salida menos significativa b0, b1, b2, b3. Este circuito 100 de cálculo de retención permite alimentar una entrada de 5 bits del circuito sumador 94 con una señal digital paralela que constituye 5 bits más significativos con respecto a la salida b0, b1, b2, b3 menos significativa de la primera etapa de sumador 91. Para ello, la señal de salida b0, b1, b2, b3 menos significativa se envía a la entrada de dos compuertas 105, 106 del circuito 100 de cálculo de retención. La salida de la compuerta Y 105 es igual a 1 cuando todos los bits b0, b1, b2, b3 son iguales a 0. Esta es igual a 0 cuando uno al menos de los bits b0, b1, b2, b3 es igual a 1. La salida de la compuerta 105 está conectada a la entrada de una compuerta Y 110 cuya salida se aplica en cuatro bits menos significativos c2, c3, c4, c5 de una de las dos entradas del circuito sumador 94 de la segunda etapa 92. La salida de la compuerta 106 es igual a 1 cuando todos los bits b0, b1, b2, b3 son iguales a 1. Esta es igual a 0 cuando uno al menos de los bits b0, b1, b2, b3 es igual a 0. La salida de la compuerta 106 está conectada a la entrada de una compuerta Y 113 cuya salida está conectada a la entrada de una compuerta O 112, formando la salida de esta última el bit c1 menos significativo de la misma entrada del circuito sumador 94 de la segunda etapa 92. Por otra parte, la salida de la compuerta 110 está conectada a la segunda entrada de la compuerta O 112.

Cuando todos los bits b0, b1, b2, b3 son iguales a 0, la salida de la compuerta 105 es igual a 1, y, si la compuerta 110 lo permite, sucede lo mismo con los bits menos significativos c2, c3, c4, c5 de la entrada del circuito sumador 94 así como de una de las entradas de la compuerta 112. Por lo tanto, la salida de la compuerta 112 es igual a 1, y lo mismo sucede con el bit c1 menos significativo de la entrada del circuito sumador 94. Por consiguiente, en esta situación, la entrada c1, c2, c3, c4, c5 del circuito sumador 94 de la segunda etapa es igual a 11111, correspondiente al valor relativo -1 que controla un decremento de una unidad del registro 96.

Del mismo modo, cuando todos los bits b0, b1, b2, b3 son iguales a 1, la salida de la compuerta 106 es igual a 1, y, si la compuerta 113 lo permite, lo mismo sucede con el bit c1 menos significativo de la entrada del circuito sumador 94. Simultáneamente, la salida de la compuerta 105 es igual a 0, y lo mismo sucede con los bits más significativos c2, c3, c4, c5 de la entrada del circuito sumador 94. Por consiguiente, en esta situación, la entrada c1, c2, c3, c4, c5 del circuito sumador 94 de la segunda etapa es igual a 00001, correspondiente al valor relativo +1 que controla un incremento de una unidad del registro 96.

Mientras uno de los bits b0, b1, b2, b3 es igual a 0 y uno de los bits b0, b1, b2, b3 es igual a 1, es decir cuando la salida menos significativa de la primera etapa de sumador 91 tiene un valor que no corresponde a uno de los valores extremos, las salidas de las dos compuertas 105, 106 son las dos iguales a cero, de tal modo que la entrada c1, c2, c3, c4, c5 del circuito sumador 94 de la segunda etapa es igual a 00000, de tal modo que el valor del registro 96 no se modifica.

De este modo, en cuanto se alcanza un valor extremo de la señal de salida b0, b1, b2, b3 menos significativa, por una parte se incrementa o se decrementa el contenido del registro 96, ya que las compuertas 105 o 106 permiten propagar el valor relativo +1 o -1 en la entrada c1, c2, c3, c4, c5 del sumador 94, y, por otra parte, al ser el bit c1 menos significativo de la entrada del circuito sumador 94 igual a 1, este valor +1 o -1 activa la señal de control del multiplexor 98 que fuerza la recarga del registro 95 con el valor contenido en el registro 97.

De este modo, se garantiza que es necesario que se produzca un desplazamiento de fase de 7 u 8 estados en el mismo sentido a partir del valor medio registrado en el registro 97 para que la señal de control emitida en la salida 36a se modifique efectivamente.

El circuito sumador 94 presenta una salida de 5 bits b4, b5, b6, b7, b8 memorizados en un registro 96 sincronizado por la señal de reloj de recepción H, formando la salida de este registro la salida 36 que alimenta la entrada de control 24 del oscilador digital 19.

La salida del registro 96 también se suministra a la segunda entrada del circuito sumador 94 mediante un circuito en bucle. Por otra parte, el circuito 100 de cálculo de retención también permite, si la dinámica del sistema lo precisa, evitar las variaciones intempestivas de la señal en la salida 36 más significativa cuando el valor de esta señal alcanza un valor extremo. Para ello, el circuito 100 de cálculo de retención comprende dos compuertas 107, 108 que reciben los valores de los bits más significativos b4, b5, b6, b7, b8 de la salida 36, y el circuito 100 de cálculo de

retención está adaptado para impedir el incremento de una unidad cuando la señal en los bits b4, b5, b6, b7, b8 es igual a 11111 y el decremento de una unidad cuando la señal en los bits b4, b5, b6, b7, b8 es igual a 00000. Esta función se obtiene mediante las compuertas 110, 113 las cuales reciben en la entrada las salidas de las compuertas 107, respectivamente 108. Cuando los bits b4, b5, b6, b7, b8 toman el valor máximo 11111, la salida de la compuerta 108 es igual a 0, de tal modo que la salida de la compuerta 113 se fuerza a cero; al ser la salida de 105 por otra parte igual a 0, la entrada c1, c2, c3, c4, c5 del circuito sumador 94 sigue siendo igual a 0, impidiendo el incremento de una unidad del registro 96. Del mismo modo, cuando los bits b4, b5, b6, b7, b8 toman el valor mínimo 00000, la salida de la compuerta 107 es igual a 0, de tal modo que la salida de la compuerta 110 se fuerza a 0, así como los bits más significativos c2, c3, c4, c5 de la entrada del circuito sumador 94, la entrada c1 del circuito sumador es por otra parte igual a 0, impidiendo el decremento de una unidad del registro 96.

10

15

20

25

30

35

40

55

60

65

La figura 7 representa una segunda forma de realización similar funcionalmente a la de la figura 6 pero que se realiza sustituyendo los sumadores 93, 94 por unos contadores/descontadores 116, 117. El primer contador 116 recibe las señales E y L de estados de fase en sus entradas de conteo y, respectivamente de desconteo. Este presenta una entrada IN de 4 bits que recibe el valor medio registrado en el registro 97. Su salida OUT suministra la señal de salida b0, b1, b2, b3 menos significativa. También presenta unas salidas de retención 113a superior y, respectivamente, 113b inferior, así como una entrada de control 114 de recarga de su entrada IN. La salida de retención 113a superior se activa cuando la entrada de conteo se incrementa en una unidad y cuando la entrada de desconteo se incrementa en una unidad y cuando la salida OUT está en su valor míximo 1111. Del mismo modo, la salida OUT está en su valor míximo 0000.

Las salidas de retención 113a superior et 113b inferior alimentan las entradas de conteo y de desconteo, respectivamente del segundo contador/descontador 117. Además, una compuerta 115 detecta un estado activo de estas dos salidas de retención 113a superior y 113b inferior e impone una recarga de la entrada IN del primer contador 116 cuando una de estas salidas de retención 113a superior y 113b inferior se activa. De esta forma, el primer contador 116 se reinicia en el valor medio contenido en el registro 97 en cuando la salida b0, b1, b2, b3 menos significativa ha superado uno de sus valores extremos. Por lo tanto, se garantiza también aquí que sea preciso constatar un desplazamiento de fase para al menos 8 o 9 (u otro número según el valor contenido en el registro 97) estados sucesivos a partir de uno de los valores extremos de la salida b0, b1, b2, b3 menos significativa, para modificar el valor de la salida 36a más significativa.

El segundo contador/descontador 117 presenta una salida de 5 bits paralelos que forman la salida 36 que alimenta la entrada de control 24 del oscilador 19. Como en la forma de realización anterior, se prevén unas compuertas 107, 108 que reciben los valores de los bits más significativos b4, b5, b6, b7, b8 de la salida 36, y están adaptadas para impedir el incremento de una unidad cuando la señal en los bits b4, b5, b6, b7, b8 es igual a 11111 y el decremento de una unidad cuando la señal en los bits b4, b5, b6, b7, b8 es igual a 00000.

Hay que señalar que en esta segunda forma de realización, las salidas 33a, 33b del detector de adelanto-retardo están directamente conectadas a la entrada de la primera etapa 116 del circuito contador, suprimiéndose el convertidor decisional 30 de la primera forma de realización. Ni que decir tiene que este convertidor decisional también se puede prever en esta segunda realización y, a la inversa, que se puede suprimir en el marco de la primera forma de realización, según las necesidades.

Hay que señalar que el bucle 25 de retroalimentación de fase de un dispositivo de acuerdo con la invención presenta unas propiedades de auto-adaptación al nivel del ruido de fase de la señal recibida puesto que la ganancia de este bucle de retroalimentación de fase disminuye cuando aumenta la desviación estándar del ruido de fase, lo que implica una reducción de la banda pasante global del filtro.

El filtrado digital realizado mediante el uso de un circuito contador de doble etapa y, llegado el caso, mediante el convertidor decisional 30, permite prescindir del uso de un filtro de bucle analógico.

En un dispositivo de acuerdo con la invención, no es necesario ningún ajuste externo manual en lo que se refiere a la frecuencia propia fos del oscilador 19. Además, sea cual sea la señal recibida, el bucle de retroalimentación de fase 25 permite garantizar que la señal de reloj de recepción H suministrada por el oscilador 19 esté siempre en fase con la señal recibida.

En estas condiciones, en un dispositivo de acuerdo con la invención, los desplazamientos de fase debidos a los retardos de propagación en las diferentes ramas del circuito son todos conocidos y constantes, y por lo tanto se pueden compensar mediante uno (o varios) circuito(s) desfasador(es) 37 situado(s) entre el nodo de derivación 11 y cada una de las entradas 17, 18 del circuito de muestreo 15. Es, en efecto, importante que el circuito de muestreo 15 realice un muestreo de la señal recibida en la zona central del periodo de cada bit de datos de la señal recibida en el que el valor de la tensión correspondiente es el más estable y en el que el margen de ruido es el más grande, con la finalidad de evitar realizar el muestreo en el comienzo o el final del periodo de cada bit en el que la tensión de la señal, que se está estableciendo, se ve sometida a una deriva de fase (tradicionalmente designada "jitter"). En la señal recibida, por lo general con ruido, cada bit se presenta en forma de un "ojo" teniendo en cuenta la deriva de fase ("jitter"). El muestreo debe producirse en el centro del ojo.

Ahora bien, la diferencia entre la frecuencia de reloj bits fsr de los bits recibidos y la frecuencia de oscilación fos del oscilador 19 es nula en un dispositivo de acuerdo con la invención, y al poder introducirse el conjunto de los retardos mediante los demás componentes del circuito, y al estar controlados y conocerse el conjunto de los retardos de propagación en las diferentes ramas del circuito, se puede determinar el retardo diferencial de fase estructural y constante entre los datos contenidos en la señal recibida y la señal de reloj de recepción H que emite el oscilador 19. Este retardo diferencial se compensa mediante el (los) circuito(s) desfasador(es) 37.

Se puede prever un único circuito desfasador 37 en el dispositivo de acuerdo con la invención, en cualquier punto adecuado. En una variante, el desplazamiento de fase entre las dos ramas 12, 14 se puede obtener mediante una multitud de circuitos desfasadores 37 distribuidos en varios puntos de cada rama. En este último caso, la acumulación de los desplazamientos de fase introducidos por cada circuito desfasador 37 es igual al desplazamiento de fase total que se debe realizar entre las dos ramas 12, 14.

En la figura 1 se representan con línea de puntos diferentes ubicaciones posibles en las que se puede prever un circuito desfasador 37. De este modo, se puede prever un circuito desfasador 37a entre el nodo de derivación 11 y la entrada de señal 17 del circuito de muestreo 15; un circuito desfasador 37b entre la salida 29 del oscilador 19 y la entrada de reloj 18 del circuito de muestreo 15; un circuito desfasador 37c entre el nodo de derivación 11 y la entrada 21 del generador de impulsos 20 que alimenta al oscilador 19; un circuito desfasador 37d entre la salida 22 del generador de impulsos 20 y la entrada 23 del oscilador 19; un circuito desfasador 37e entre el nodo de derivación 11 y la segunda entrada 28 del detector de adelanto-retardo 26; un circuito desfasador 37f entre la salida 29 del oscilador 19 y la primera entrada 27 del detector de adelanto-retardo 26. Cada circuito desfasador 37 puede estar formado por una simple línea de retardo.

La arquitectura de un dispositivo de acuerdo con la invención es intrínsecamente muy poco sensible a los eventos transitorios como los cambios de estado de una señal causados por una partícula ionizante una vez que el oscilador 19 está en modo bloqueado. En efecto, la sincronización del oscilador con el ritmo de la señal recibida permite ocultar las perturbaciones de origen externo.

En un dispositivo de acuerdo con la invención, el oscilador bloqueado en inyección está adaptado para que un incremento de la señal digital de control provoque una modificación de la frecuencia propia del oscilador de acuerdo con un paso de valor Δf predeterminado. La elección del número de bits retenidos para formar el bus de la señal de control a partir de la salida paralela del circuito acumulador, y la elección del paso de ajuste Δf dependen de la dinámica requerida para el bucle de retroalimentación de fase 25. Por ejemplo, para una frecuencia propia del oscilador 19 bloqueado en inyección del orden de 10 GHz, con un paso Δf inferior al 1 % -y en particular del orden de 0,3 %-, cada incremento de una unidad de la señal digital de control provoca una variación del orden de 30 MHz de esta frecuencia propia. Por otra parte, en el mismo ejemplo, si la señal de control del oscilador 19 comprende, como en los ejemplos descritos, 5 bits, esta señal permite realizar treinta y dos incrementos, y procura por lo tanto un intervalo de ajuste de la frecuencia propia fos del oscilador 19 bloqueado en inyección del orden del 10 %, es decir del orden de 1 GHz.

La invención puede ser objeto de muy numerosas variantes de realización con respecto a los ejemplos de realización que se representan en las figuras y se han descrito con anterioridad. En particular, los diferentes componentes del dispositivo (detector de adelanto-retardo, convertidor decisional, circuito contador de doble etapa, oscilador, generador de impulsos....) se pueden realizar mediante otras estructuras de circuito, conocidas en sí mismas, y que ofrecen las mismas funciones. Por ejemplo, los circuitos 100, 107, 108 pueden ser objeto de otras implementaciones (con otros tipos de compuertas lógicas u otras combinaciones de compuertas lógicas) diferentes de las dadas a título de ejemplo y que tienen las mismas funciones técnicas.

#### REIVINDICACIONES

- 1. Dispositivo de extracción de reloj a partir de una señal en serie en banda de base, denominada señal recibida, representativa de unos datos digitales y codificada con una señal de reloj que presenta una frecuencia de reloj bits fsr, que comprende:

- un circuito (19) que recibe una señal procedente de la señal recibida y acompasada a la frecuencia de reloj bits fsr, y que emite, en al menos una salida de reloj (29), una señal de reloj, denominada señal de reloj de recepción, al menos sustancialmente sincronizada y en fase con la frecuencia de reloj bits fsr de la señal recibida:

- un bucle de retroalimentación de fase (25) que comprende:

- una primera entrada (27) conectada a una salida de reloj (29) del circuito (19) que emite una señal de reloj de recepción;

- una segunda entrada (28) alimentada con una señal procedente de la señal recibida;

- un detector (26) digital de fase que comprende un detector de adelanto-retardo conectado a la primera y a la segunda entradas (27, 28) y adaptado para emitir, en al menos una salida (33a, 33b), al menos una señal digital, denominada señal de estados de fase, representativa de un desplazamiento de fase entre la señal de reloj de recepción y la señal recibida, y del sentido de este desplazamiento;