# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 516 791

51 Int. Cl.:

**G11C 7/22** (2006.01) **G11C 11/4076** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 29.06.2001 E 10175918 (1)

(97) Fecha y número de publicación de la concesión europea: 16.07.2014 EP 2276033

- (54) Título: Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme

- (30) Prioridad:

07.07.2000 CA 2313954 07.07.2000 US 216679

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 31.10.2014

(73) Titular/es:

CONVERSANT INTELLECTUAL PROPERTY MANAGEMENT INC. (100.0%) 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1, CA

(72) Inventor/es:

**DEMONE, PAUL**

74 Agente/Representante:

**CURELL AGUILÁ, Mireia**

#### **DESCRIPCIÓN**

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme

5 La presente invención se refiere en general a arquitecturas de DRAM de alta velocidad, y específicamente a la temporización de operaciones de lectura, escritura y refresco.

#### Antecedentes de la invención

20

25

30

35

40

45

50

55

60

65

Tradicionalmente, el diseño de productos básicos genéricos de dispositivos de Memoria Dinámica de Acceso Aleatorio (DRAM) se ha centrado más en lograr un coste-por-bit bajo a través de una alta densidad de bits acumulada que en lograr un mayor rendimiento de la memoria. El motivo de esto es que la capacidad de las celdas de una matriz de memoria bidimensional se incrementa cuadráticamente con el escalado, mientras que el área de tara de los amplificadores de detección de líneas de bit, los controladores de líneas de palabra, y los decodificadores de direcciones de fila (o direcciones x) y direcciones de columna (o direcciones y) se incrementa linealmente con el escalado.

Por lo tanto, el hecho de que el diseño haya puesto énfasis en la densidad de las memorias ha dado como resultado el diseño de DRAMs básicas genéricas que tienen submatrices del mayor tamaño posible en la práctica, a pesar de su efecto fuertemente perjudicial sobre el tiempo necesario para llevar a cabo la lectura de celdas, la detección de líneas de bit, la restauración de celdas y la ecualización y precarga de líneas de bit. Como consecuencia, el rendimiento relativamente bajo de arquitecturas de DRAM tradicionales, en comparación con la Memoria Estática de Acceso Aleatorio (SRAM), ha limitado en general su uso a aplicaciones de gran capacidad, alta densidad y sensibles al coste, donde el rendimiento es un factor secundario.

Además, las arquitecturas tradicionales de DRAM minimizan el número de pines de señales en los dispositivos de memoria mediante el multiplexado de líneas de dirección entre los componentes de fila y columna de la dirección. Como consecuencia, el carácter bidimensional de la organización de las matrices de DRAM ha sido siempre una parte inherente de la interfaz entre el control o la lógica de la memoria y los dispositivos de memoria de DRAM.

La llegada de tecnologías de DRAM de interfaz síncrona, tales como la SDRAM, la RAMBUS directa, y la SDRAM de velocidad de datos doble (DDR), ha sustituido las señales de control independiente de filas y columnas de las tecnologías de DRAM de interfaz asíncrona, tales como el modo de paginación rápida (FPM) y la salida de datos extendida (EDO), por órdenes codificadas.

No obstante, la organización tradicional de direccionamiento lógico bidimensional de arquitecturas previas se ha mantenido.

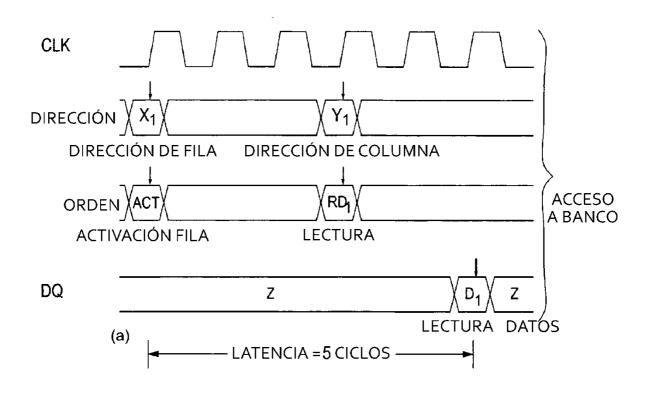

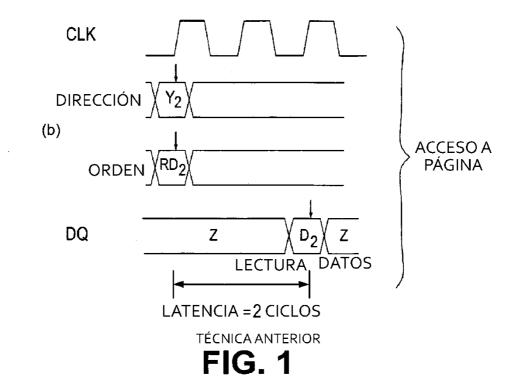

Uno de los primeros intentos de incrementar el rendimiento de la DRAM minimizando el impacto de la latencia y del tiempo de ciclo de las lentas operaciones de acceso a filas debido al uso de grandes matrices de celdas, condujo a la creación de dos clases diferentes de operaciones de memoria, siendo los dos bien conocidas en la industria. Una primera clase comprende accesos a bancos. Un acceso a banco consta de una orden de abrir fila seguida por un acceso a columna. En referencia a la figura 1 a, se ilustra un diagrama de temporización para un acceso a banco. Una segunda clase comprende accesos a página. Un acceso a página consta de un acceso de columna a una fila que se ha dejado abierta por medio de una orden previa de abertura de fila o de acceso de banco. Como consecuencia, los accesos de página son típicamente más rápidos que los accesos de banco. En referencia a la figura 1b, se ilustra un diagrama de temporización para un acceso de página. La eficacia de los accesos de página en la reducción de la latencia media es debida a la localización espacial estadística en los patrones de acceso de memoria de muchas aplicaciones informáticas y de comunicaciones. Es decir, existe una gran probabilidad de que accesos de memoria consecutivos apunten a la misma fila.

Una mejora adicional de la precisión de dicho esquema de clase dual de acceso a memoria es la creación de arquitecturas de DRAM que dividen explícitamente cada dispositivo de memoria en dos o más regiones del mismo tamaño a las que se hace referencia como bancos. La intención de esta mejora arquitectónica es reducir parcialmente la tara de los accesos de fila permitiendo el solapamiento de accesos de memoria en un banco, mientras que el otro banco se ocupa de una operación de abertura o cierre de fila.

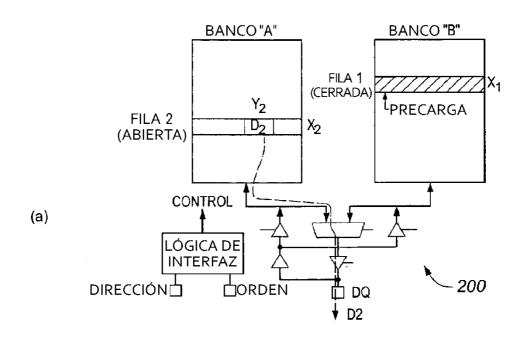

Un sistema que implementa una arquitectura de múltiples bancos es bien conocido en la industria y se ilustra de forma general en la figura 2a por medio del número de referencia 200. En la figura 2b se ilustra un diagrama de temporización para un sistema del tipo mencionado.

Un problema fundamental con todos estos esquemas es la retención del sistema de dos clases de accesos a memoria para compensar parcialmente el lento acceso de fila asociado a las grandes matrices de DRAM. Muchas aplicaciones de tiempo real, tales como los procesadores de señal digital, quedan limitadas por el rendimiento de la memoria en el peor de los casos. Estos sistemas no pueden tolerar diferencias en la temporización de los accesos a memoria en función de los patrones de dirección particulares de accesos consecutivos. Incluso los diseños de

macrobloques de la DRAM embebida con rendimiento optimizado tienden a mantener el paradigma de la clase dual de acceso de las arquitecturas de DRAM básicas genéricas.

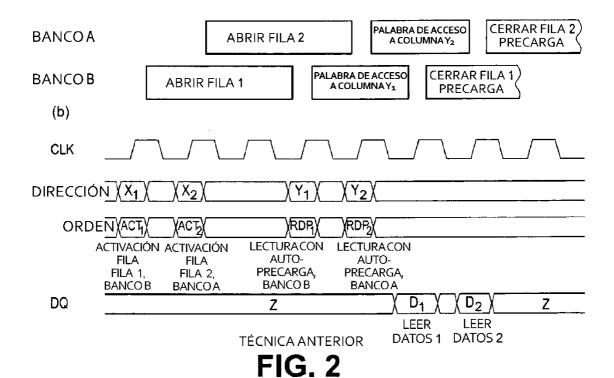

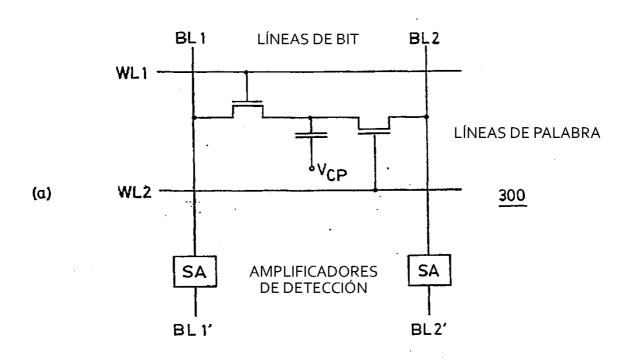

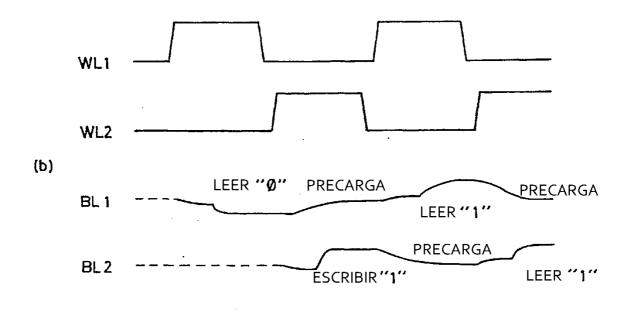

En referencia a la figura 3a, con el número referencia 300 se ilustra de manera general un intento adicional de incrementar el rendimiento de la DRAM con el uso de una arquitectura de puerto dual. La arquitectura con puerto dual es un avance más reciente en la arquitectura de DRAM para lograr un rendimiento mayor. Cada celda de memoria MC está conectada a dos líneas de bit, BL1 y BL2, a través, respectivamente, de transistores de acceso N1 y N2. Esta arquitectura de celdas permite un acceso simultáneo de la celda de memoria MC a través de un transistor de acceso y su línea de bit asociada, por ejemplo N1 y BL1, mientras que BL2, asociada al otro transistor de acceso N2, experimenta una precarga y una ecualización. Como consecuencia, puede producirse un segundo acceso por medio de N2 sin ningún retardo en la línea de bit BL2 de precarga.

Alternando de un lado a otro entre los dos transistores de acceso y sus líneas de bit respectivas, esta arquitectura puede ocultar completamente la tara asociada al cierre de filas y a la precarga y la ecualización de las líneas de bit. No obstante, el principal inconveniente de este sistema es la alta reducción de la densidad de bits dentro de la matriz de DRAM debido al doblamiento del número de transistores de acceso y de líneas de bit por celda de memoria, en comparación con los diseños convencionales de DRAM. Además, un sistema de este tipo usa también una arquitectura de líneas de bit abiertas lo cual no es deseable debido a su susceptibilidad al acoplamiento de ruido desadaptado con respecto a pares de líneas de bit.

El documento US 6072743 da a conocer circuitos para controlar la temporización interna de operaciones de memoria en un dispositivo de DRAM. El documento US 5808959 da a conocer circuitos similares para una memoria de SRAM.

#### 25 Sumario de la invención

5

10

15

20

45

50

La presente invención proporciona un aparato y métodos para acceder a una memoria DRAM que presenta las funcionalidades que se exponen en las reivindicaciones adjuntas.

#### 30 Breve descripción de los dibujos

A continuación se describirán, a título de ejemplo, unas formas de realización de la presente invención, únicamente haciendo referencia a los dibujos siguientes, en los cuales:

35 la figura 1a es un diagrama de temporización para un acceso a bancos de memoria;

la figura 1b es un diagrama de temporización para un acceso a páginas de memoria;

la figura 2a es un diagrama de bloques simplificado que ilustra una arquitectura de una memoria con múltiples bancos (técnica anterior);

la figura 2b es un diagrama de temporización para el sistema ilustrado en la figura 2a;

la figura 3a es un diagrama esquemático de una arquitectura de memoria de puerto dual (técnica anterior);

la figura 3b es un diagrama de temporización que ilustra operaciones de lectura y escritura para la arquitectura de puerto dual ilustrada en la figura 3 a;

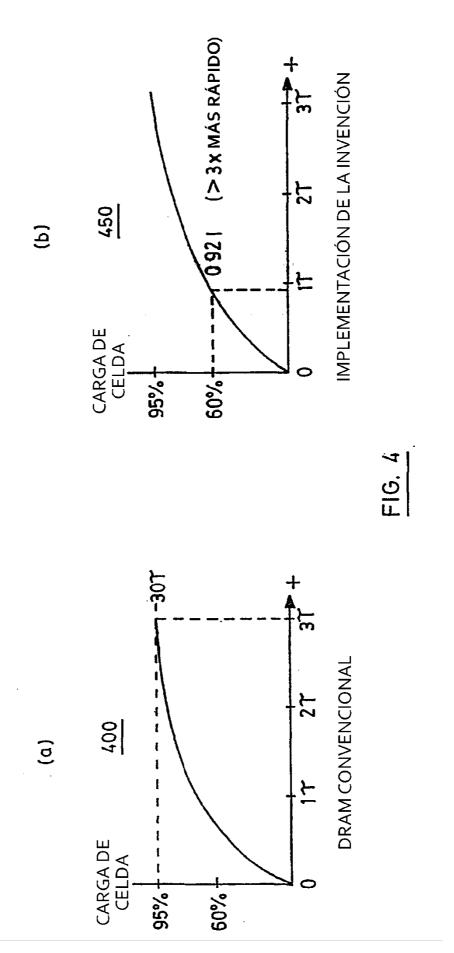

la figura 4 es un gráfico que compara una celda de DRAM convencional (técnica anterior) con una celda de DRAM de acuerdo con una forma de realización de la presente invención;

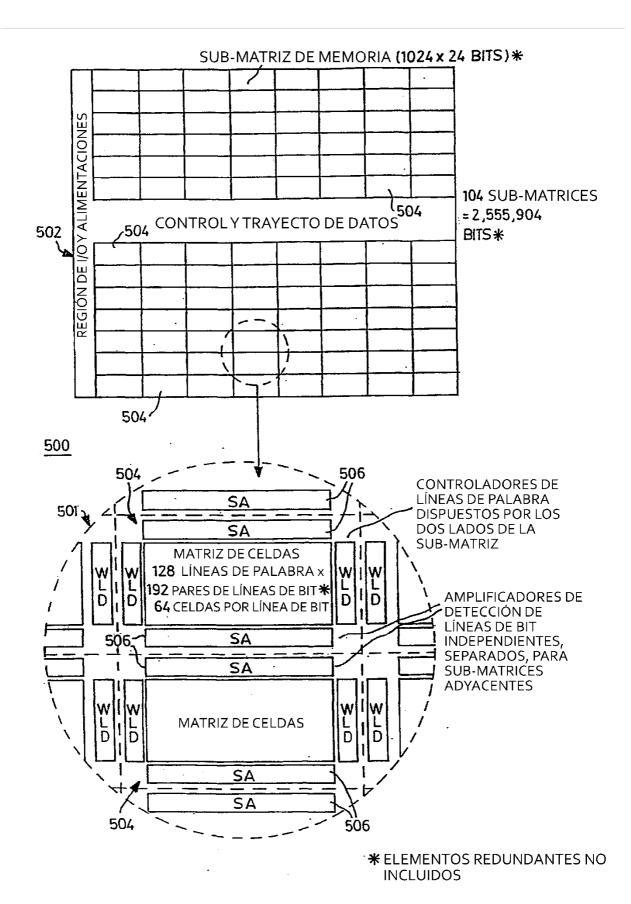

la figura 5 es un diagrama de bloques de una arquitectura de memoria general de acuerdo con una forma de realización de la presente invención;

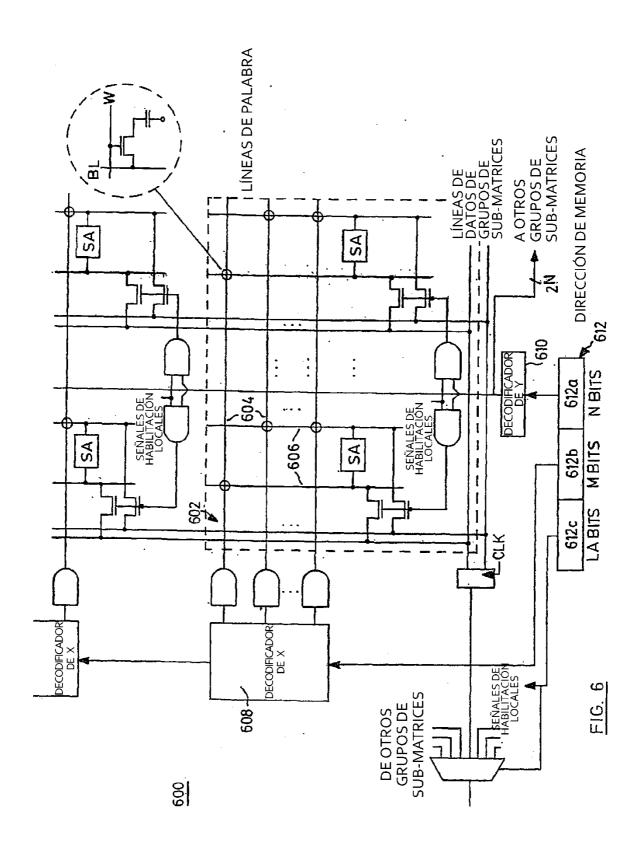

la figura 6 es un esquema conceptual que ilustra los campos de dirección de memoria y su cobertura;

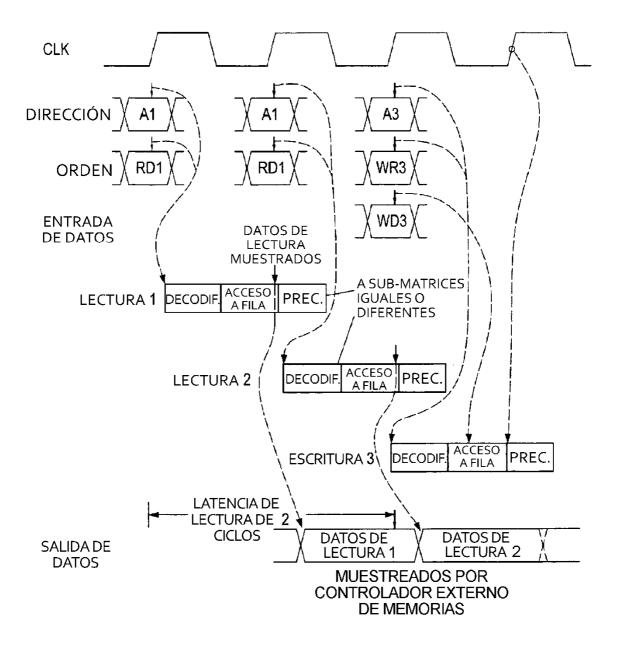

la figura 7 es un diagrama de flujo de temporización y canalización que ilustra el funcionamiento de la arquitectura ilustrada en la figura 6;

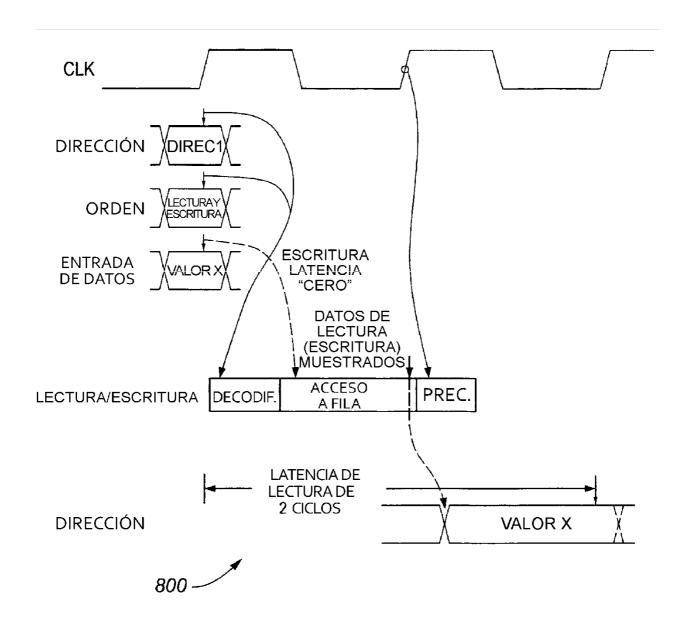

la figura 8 es un diagrama de flujo de temporización y canalización que ilustra la capacidad del circuito ilustrado en la figura 6 tanto para leer como para escribir sobre una única orden;

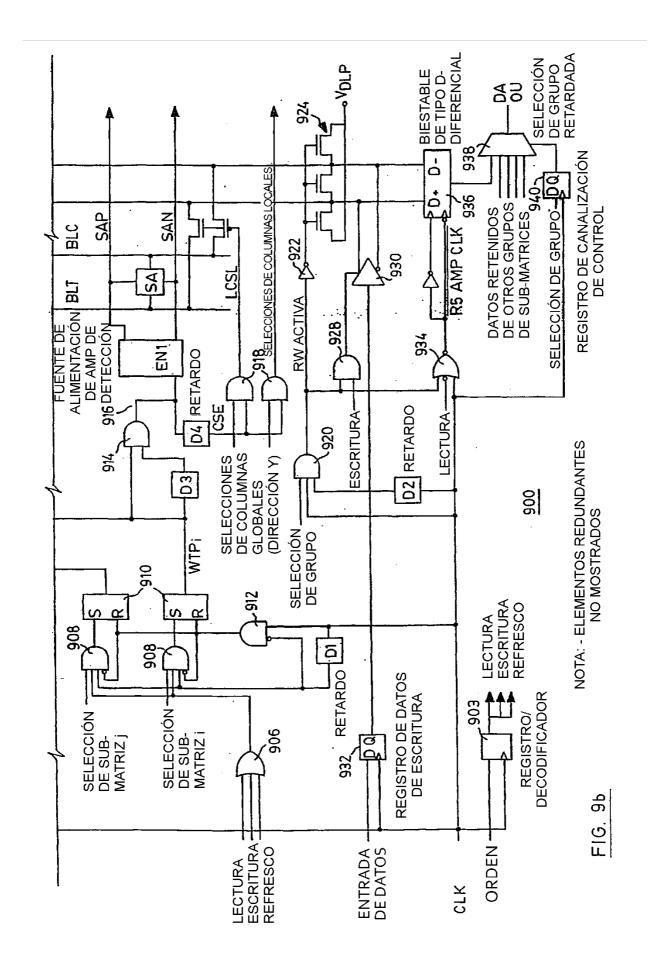

la figura 9 es un diagrama de bloques funcional que ilustra la arquitectura de memoria ilustrada en la figura 6;

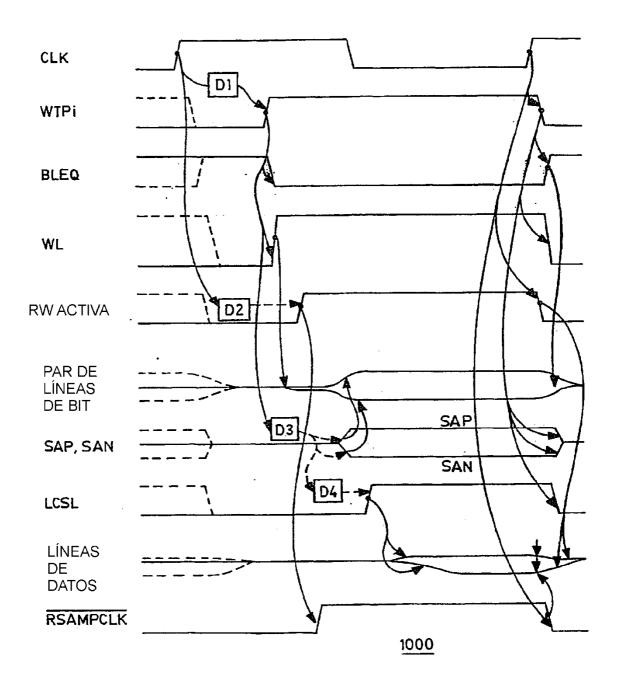

la figura 10a es un diagrama de temporización que ilustra la temporización para los bloques funcionales ilustrados en la figura 9;

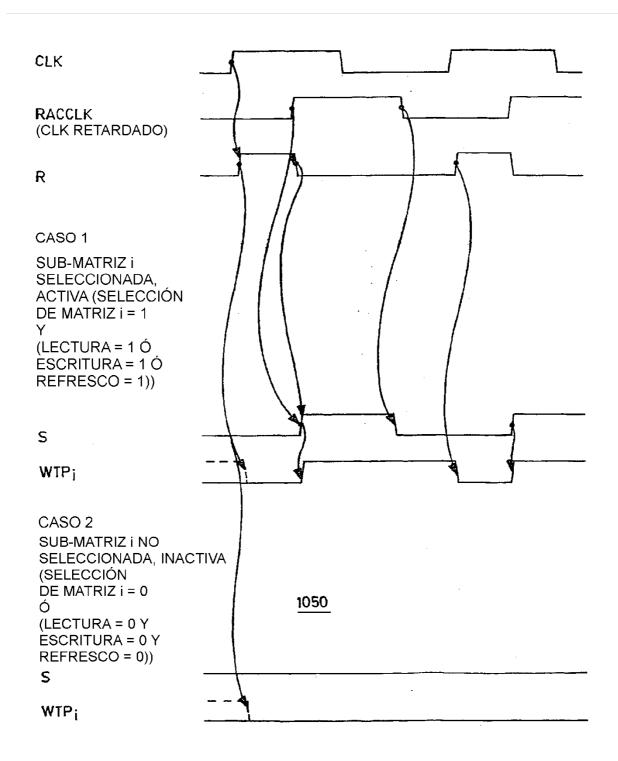

la figura 10b es un diagrama de temporización que ilustra la activación del impulso de temporización de líneas de palabra en casos en los que se selecciona y deselecciona una submatriz;

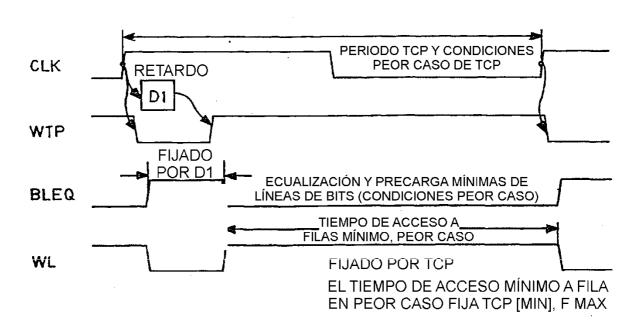

la figura 11 a es un diagrama de temporización que ilustra los requisitos de temporización mínimos para la ecualización y precarga de líneas de bit y para el tiempo de acceso;

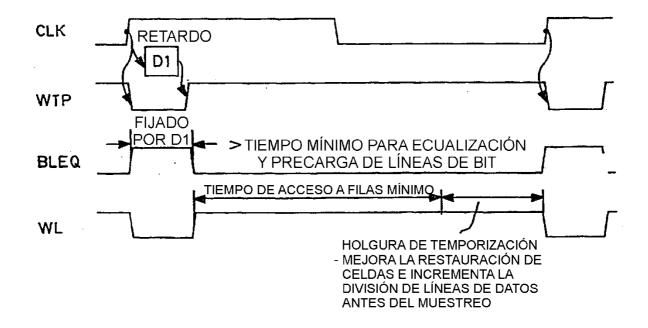

la figura 11b es un diagrama de temporización que ilustra la ventaja de un circuito que funciona con unas condiciones mejores que las mínimas;

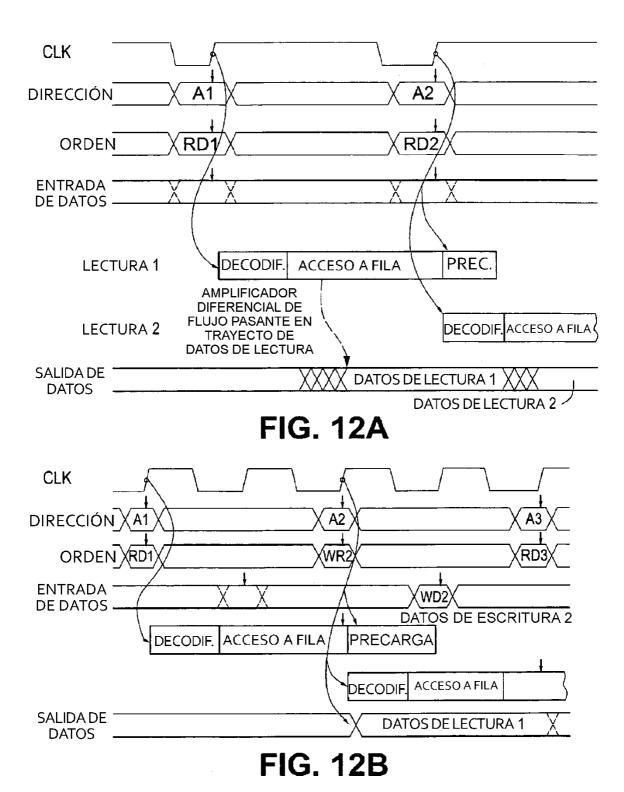

la figura 12a es un diagrama de flujo de temporización y canalización para una forma de realización asíncrona de la arquitectura de memoria ilustrada en la figura 6;

la figura 12b es un diagrama de flujo de temporización y canalización para una forma de realización que requiere dos ciclos de reloj para un acceso de submatriz;

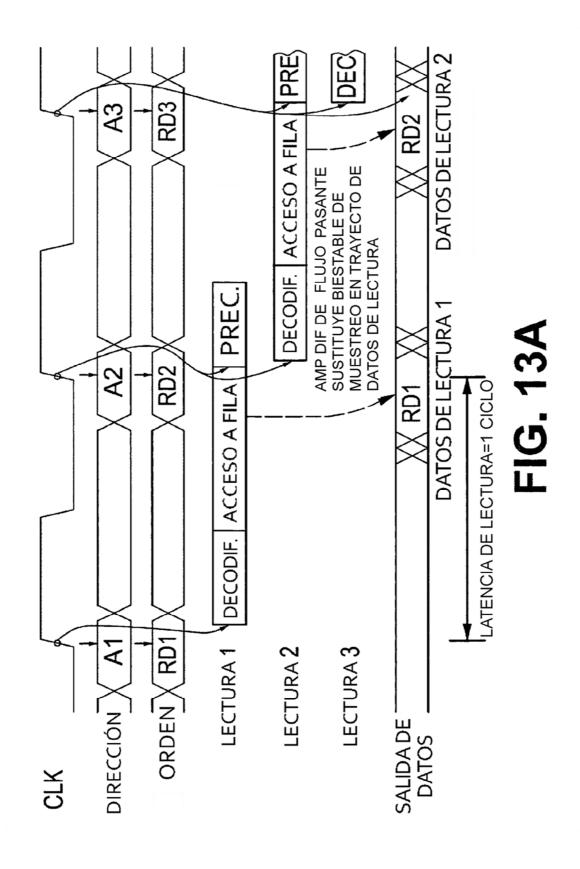

la figura 13a es un diagrama de flujo de temporización y canalización para una forma de realización que requiere un ciclo de reloj para el acceso de submatriz y tiene una latencia de un ciclo de reloj; y

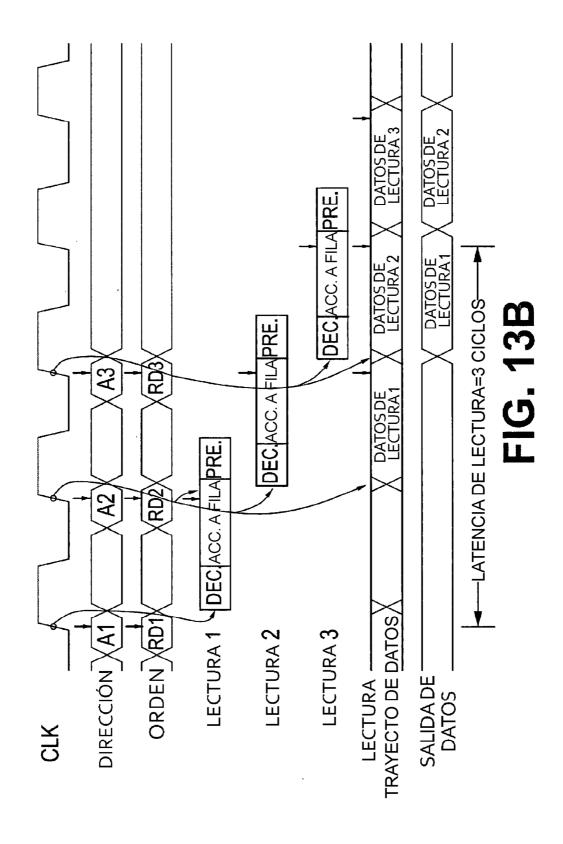

la figura 13b es un diagrama de flujo de temporización y canalización para una forma de realización que requiere un ciclo de reloj para el acceso de submatriz y tiene una latencia de tres ciclos de reloj.

#### Descripción detallada de las formas de realización preferidas

10

15

30

35

45

55

60

65

Se optimiza una arquitectura de DRAM para un rendimiento de alta velocidad con independencia del patrón de direcciones correspondiente a operaciones consecutivas de acceso a memoria. Cada operación de lectura, escritura o refresco presenta la misma temporización. Esto es diferente en comparación con arquitecturas de DRAM tradicionales en las cuales la temporización de las operaciones depende del valor de la dirección de destino así como del historial de operaciones de memoria previas.

La obtención de la misma temporización de acceso para todas las órdenes de memoria se logra llevando a cabo una operación completa de acceso a fila para cada orden recibida de lectura, escritura y refresco. La operación completa de acceso a fila incluye la puesta en estado activo de líneas de palabra, la lectura de celdas de memoria, la detección de líneas de bit, la restauración de contenidos de celdas, la puesta en estado inactivo de líneas de palabra, y la ecualización y precarga de líneas de bit. La siguiente descripción ilustra los detalles de implementación que permiten que dispositivos de memoria o macrobloques de memoria fabricados con el uso de una tecnología convencional de procesado de DRAM lleven a cabo accesos a datos con tiempos de latencia y de ciclo similares a los accesos a página llevados a cabo por DRAMs con arquitectura convencional.

40 No obstante, la presente arquitectura no depende del patrón con el cual se acceda a la memoria, como sí lo es la tecnología previa.

Los detalles de implementación clave de la presente forma de realización de la invención incluyen, aunque sin carácter limitativo, organización física, secuenciación y solapamiento de operaciones, niveles de señales, activación mediante impulsos de reloj, y técnicas de generación de temporización. La presente forma de realización describe una implementación que lleva a cabo un acceso completo de matriz de DRAM dentro de un periodo de una señal de reloj de una interfaz síncrona y puede aceptar una orden nueva en cada periodo de reloj.

No obstante, los expertos en la materia apreciarán que son posibles otras relaciones entre operaciones de memoria y la temporización del reloj de la interfaz. Además, bajo ciertas circunstancias, incluso puede que sean deseables otras relaciones de temporización, sin desviarse con respecto al alcance de la presente invención.

En relación con la figura 5, con el número de referencia 500 se ilustra en general la arquitectura general de una memoria de acuerdo con una forma de realización de la invención. Con el número de referencia 501 se ilustra en general una parte ampliada de una de las áreas en la memoria 500.

Un macrobloque de memoria o de dispositivo de DRAM 502 comprende una pluralidad de submatrices de DRAM rectangulares relativamente pequeñas, del mismo tamaño, 504 construidas con una arquitectura de líneas de bit plegadas. Para limitar el retardo introducido por dispositivos de aislamiento de líneas de bit, las submatrices adyacentes 504 no comparten dispositivos de amplificador de detección. Por el contrario, las submatrices adyacentes 504 tienen amplificadores de detección 506 dedicados, separados.

Adicionalmente, en la presente forma de realización, la submatriz 504 está organizada con aproximadamente un cuarto del número de celdas de memoria física por línea de bit de lo que estaría diseñada convencionalmente para una DRAM en la misma tecnología del proceso. El uso de menos celdas de memoria física por línea de bit reduce la capacidad eléctrica de las líneas de bit, lo cual, a su vez, reduce la relación de la capacidad eléctrica de las líneas de

bit con respecto a la capacidad eléctrica de las celdas de memoria. El diferencial de voltaje sobre una línea de bit viene dado por la expresión:

$\Delta V_{BL} = (V_{CELDA} - V_{BL}) * C_{CELDA} / (C_{BL} + C_{CELDA}).$

5

10

Por lo tanto, si la capacidad eléctrica de las líneas de bit CBL disminuye, entonces  $V_{CELDA}$  también se puede atenuar aunque alcanzando todavía el mismo diferencial de voltaje de línea de bit  $\Delta V_{BL}$ . Esta reducción de la relación permite que celdas de memoria que almacenan niveles de carga atenuados alcancen más rápidamente diferenciales de voltaje de línea de bit similares a los correspondientes de DRAMs diseñados convencionalmente, tal como se describirá de forma detallada posteriormente. Esto permite además que se finalice la restauración de las celdas de memoria o una parte de escritura de un acceso a filas antes de que la celda alcance un nivel de voltaje completo de VDD o VSS bajo condiciones lentas (temperatura alta, voltaje bajo, proceso lento) al mismo tiempo que logrando una detección de lectura robusta con diseños convencionales de los circuitos de los amplificadores de detección.

- En relación con la figura 4a y 4b, con los números de referencia 400 y 450 se ilustran de forma general respectivamente gráficas que ilustran el tiempo requerido para cargar una celda de DRAM convencional y una celda de DRAM de acuerdo con la invención. A efectos de este ejemplo, la DRAM convencional tiene 256 celdas por segmento de línea de bit. Para un voltaje de precarga V<sub>BLP</sub> de V<sub>DD</sub>/2 con un 95% de nivel de carga como escenario del peor de los casos, el voltaje de la celda es aproximadamente 0,025 VDD para almacenar un "0" lógico. Para almacenar un "1" lógico, el voltaje de la celda es aproximadamente 0,975 VDD. Alternativamente, el uso de niveles de almacenamiento con carga parcial de acuerdo con la invención permite un escenario del 60% en el peor de los casos, lo cual da como resultado un voltaje de 0,20 VDD para almacenar un "0" lógico, y 0,80 VDD para almacenar un "1"

- Por lo tanto, para una restauración o escritura de celdas, usando el 60% del nivel de carga como nivel de almacenamiento con carga aceptable, solamente es necesario una constante de tiempo τ para alcanzar el nivel requerido con respecto a aproximadamente las tres constantes de tiempo 3τ que se requieren para una DRAM convencional.

- 30 El número de pares de líneas de bit por matriz está limitado con el fin de lograr una propagación muy rápida de la señal por la submatriz para una línea de palabra dada, limitando así la diferencia de temporización. Para compensar este número relativamente pequeño de líneas de bit por matriz, la arquitectura puede usar submatrices relativamente amplias si las líneas de palabra se unen apropiadamente con una interconexión metálica a intervalos suficientemente próximos. Esto limita el retardo de propagación de las líneas de palabra introducido por efectos parásitos RC. Aunque, para simplificar, no se muestra específicamente en la figura 5, las líneas de palabra y los pares de líneas de bit están intercalados. Es decir, las líneas de palabra son controladas por controladores de líneas de palabra en lados alternos de una submatriz, y las líneas de bit están conectadas a una circuitería de amplificadores de detección y ecualización en lados alternos de la submatriz.

- 40 En relación con la figura 6, se ilustra, de manera general, con el número de referencia 600 un campo de dirección de memoria y sus correspondencias. Cada submatriz 602 comprende una matriz de líneas de palabra 604 y pares de líneas de bit 606. Un decodificador de filas (o X) 608 selecciona las líneas de palabra y un decodificador de columnas (o Y) 610 selecciona los pares de líneas de bit. El decodificador de columnas (o Y) 610 decodifica los N bits menos significativos de una dirección de memoria 612 para seleccionar una dirección de columna. El decodificador de filas (o X) decodifica los siguientes M bits más significativos de la dirección de memoria 612 para seleccionar una dirección de fila. Los LA bits más significativos de la dirección de memoria 612 se usan para generar señales de habilitación locales para la selección apropiada de la submatriz.

- Un primer segmento 612a de la dirección de memoria 612 comprende los N bits menos significativos para direccionar una palabra individual dentro de una fila. Por lo tanto, en cada línea de palabra hay contenidas 2<sup>N</sup> palabras. La longitud de una palabra se indica como W. Por lo tanto, cada línea de palabra controla el acceso a W \* 2<sup>N</sup> bits en cada fila. Para una operación de refresco se selecciona una fila completa, de manera que los N bits menos significativos esencialmente se ignoran o se tratan como "irrelevantes" ("don't cares") para esta orden.

- Un segundo segmento 612b de la dirección de memoria 612 comprende los siguientes M bits más significativos para direccionar una línea de palabra dentro de una submatriz. El número de líneas de palabra por submatriz es 2<sup>M</sup>. Según una forma de realización de la invención, M = 7 y, por lo tanto, cada submatriz tiene 128 líneas de palabra, sin incluir elementos de fila redundantes (no representados).

- 60 Un tercer segmento 612c de la dirección de memoria 612 comprende los LA bits más significativos, los cuales se usan para direccionar una submatriz particular dentro de la memoria. Un dispositivo o macrobloque de memoria completo consta de A submatrices. LA es el entero más pequeño tal que 2<sup>LA</sup> es mayor que o igual a A. Por lo tanto, la capacidad total de la memoria es (W\*2<sup>N</sup>) \* (2<sup>M</sup>) \* A = A\* W \* 2<sup>(M + N)</sup> bits. Además, la interfaz de memoria usa un tamaño de dirección de LA + M + N bits. Una forma de realización de la invención, N = 3, M = 7, A = 104, LA = 7, y

65 W = 24. Por lo tanto, se usan 17 bits de dirección para identificar una de entre 106.496 palabras de 24 bits y la memoria tiene una capacidad total de 2.555.904 bits.

El estado de reposo por defecto para todas las submatrices de DRAM es todas las líneas de palabra mantenidas en un nivel lógico bajo y todas las líneas de bit y todas las líneas de datos ecualizadas y precargadas con un nivel de voltaje de precarga predeterminado. Las operaciones de lectura, escritura y refresco afectan únicamente a la submatriz direccionada por los LA bits más significativos 612c dentro de la dirección de memoria 612. Las A submatrices dentro de un dispositivo o macrobloque de memoria se direccionan por medio de los valores 0,1,..., A-1. Durante una operación solamente se accede a la submatriz direccionada. La totalidad del resto de submatrices permanece en el estado de reposo por defecto. Las órdenes de lectura, escritura y refresco provocan una operación de fila dentro de la submatriz direccionada usando la línea de palabra seleccionada por el valor de los M bits en el segmento central 612b de la dirección de memoria 612. Las operaciones de lectura y escritura acceden a la palabra seleccionada por los N bits menos significativos 612a de la dirección de memoria 612.

10

15

20

25

40

45

50

55

65

En relación con la figura 7, se muestra un diagrama de flujo de temporización y canalización que ilustra el funcionamiento general de dos órdenes de lectura y una orden de escritura para la implementación descrita anteriormente de la arquitectura de memoria. En esta implementación particular, las entradas de órdenes, direcciones y datos de escritura se muestran en el flanco de subida de un reloj de interfaz síncrona CLK, y se pueden emitir órdenes nuevas en cada flanco de subida de reloj consecutivo. Una primera orden de lectura RD 1 inicia una lectura LECTURA 1 en la dirección AI en un primer flanco de subida del reloj CLK. De modo similar, en un segundo flanco de subida sucesivo del reloj, una segunda orden de lectura RD2 inicia una lectura LECTURA2 en la dirección A2. Subsiguientemente, una orden de escritura WR3 inicia una escritura ESCRITURA3 para escribir los datos WD3 presentes en la entrada de datos, en la celda de memoria en la dirección A3 al producirse un tercer flanco de subida sucesivo del reloj. A los datos DATOS LECTURA 1 y DATOS LECTURA 2 a los que acceden las órdenes de lectura se les da salida hacia una línea de salida de datos después de una latencia de lectura de dos ciclos.

Tal como puede observarse a partir de la figura 7, de acuerdo con una forma de realización de la invención, se lleva a cabo una operación completa de acceso a fila como respuesta a cada orden muestreada.

Aunque la operación de acceso a filas ocupa más que un único periodo de reloj del sistema, las órdenes se pueden introducir en cada flanco de subida del reloj por solapamiento. Por ejemplo, la puesta en estado inactivo de la línea de palabra y la ecualización y precarga de la línea de bit de la orden LECTURA 1 se solapa con la decodificación de direcciones y órdenes, la comparación de direcciones de redundancia de filas, y la propagación de señales de la orden LECTURA2, cuando las dos órdenes se emiten de manera sucesiva en ciclos de reloj consecutivos. De manera similar, la parte de precarga de la orden LECTURA 2 funciona simultáneamente con la parte de decodificación de la orden de escritura 3.

Al final de la operación se muestra cada una de las operaciones de precarga y ecualización para ilustrar que la misma se puede solapar con el establecimiento correspondiente a otra orden. La operación de precarga y ecualización se muestra pegada conceptualmente a la operación de lectura previa ya que en términos lógicos, la función de precarga y ecualización es la operación final de la orden previa requerida para llevar la submatriz de vuelta a un estado de espera. No obstante, en la implementación concreta, el flanco de reloj de subida está sincronizado con la etapa apropiada de precarga de ecualización para esa orden particular. Por ejemplo, en la figura 7, la orden LECTURA2 se muestra en el segundo flanco del reloj y su precarga y ecualización asociadas se muestrean también en este mismo momento, es decir, en el comienzo del segundo ciclo del reloj.

En relación con la figura 8, con el número de referencia 800 se representa de manera general un diagrama de flujo de temporización y canalización que ilustra la capacidad de prestar soporte a operaciones simultáneas de lectura y escritura en la misma dirección dentro de un ciclo del reloj del sistema. Una operación simultánea de lectura y escritura es útil en algunas aplicaciones de procesado de datos en la medida en la que permite que datos que se van a almacenar en memoria se reenvíen a una carga subsiguiente desde la misma dirección.

Típicamente, la técnica anterior requiere un trayecto externo de derivación, independiente, desde los pines o islas de entrada de datos y salida de datos de la memoria. En el flanco de subida de la señal de reloj CLK, los datos VALOR X presentados en una entrada de datos se escriben en una dirección seleccionada DIREC1. Hacia el final del tiempo asignado para un acceso a fila, los datos VALOR X escritos en la dirección DIREC1 se muestrean y presentan en una salida de datos. Los datos VALOR X están disponibles en la salida de datos después de una latencia de dos ciclos, la misma latencia que para las operaciones de lectura, escritura y refresco.

En relación con la figura 9, con el número de referencia 900 se ilustran de forma general elementos de circuitos de control y elementos de trayectos de datos para una submatriz de acuerdo con una forma de realización de la invención.

La temporización general de operaciones en una submatriz seleccionada se basa en una única señal de referencia de temporización maestra, a la que se hace referencia como impulso de temporización de línea de palabra (WTP<sub>I</sub>). En un registro de direcciones 902 se introduce una dirección de destino. En un registro/decodificador 903 se introduce una orden de operación. Tanto el registro de direcciones 902 como el registro/decodificador 903 son

activados mediante impulsos de reloj por la señal de reloj de interfaz síncrona CLK. El registro/decodificador 903 genera una señal de orden interna LECTURA, ESCRITURA o REFRESCO en función de la orden externa recibida.

La salida del registro de direcciones 902 se envía a una pluralidad de decodificadores de direcciones 904. Un primer decodificador 904a decodifica los N bits menos significativos de la dirección de entrada para generar una señal de selección de columna global o dirección Y. Un segundo decodificador 904b decodifica los siguientes M bits significativos para generar una dirección X predecodificada. Un tercer decodificador 904c decodifica los LA bits más significativos de la dirección de memoria para generar una señal de selección de submatriz. La señal de selección de submatriz habilita una de la pluralidad de submatrices en el dispositivo o macrobloque de memoria. Un cuarto de codificador 904d decodifica un grupo de submatrices. Dentro de la memoria hay grupos de submatrices. Un grupo de submatrices comparte las mismas líneas de datos, registro/multiplexor de datos de lectura y memoria intermedia de escritura, los cuales se describirán de forma más detallada posteriormente. Los LA bits más significativos de la dirección seleccionan un grupo de submatrices y una submatriz dentro de ese grupo.

10

20

25

30

35

40

45

50

55

60

65

Una puerta OR 906 combina las señales de lectura, escritura y refresco. La salida de la puerta OR 906 se introduce en una pluralidad de puertas AND 908 para generar el impulso de temporización de línea de palabra WTP<sub>s</sub>. El impulso de temporización de línea de palabra WTP<sub>i</sub> se genera localmente para cada submatriz.

Por lo tanto, la puerta AND 908 tiene la señal de selección de submatriz como entrada adicional, y la salida de la puerta AND 908 solamente se puede poner en estado activo si la señal de selección de submatriz selecciona la submatriz asociada. Otra entrada de la puerta AND 908 es la señal de reloj CLK retardada con el retardo D1.

La salida de la puerta AND 908 es una entrada S a un biestable SR 910. Una entrada R del biestable SR 910 se genera combinando la señal de reloj CLK con la inversa de la señal de reloj CLK retardada según el retardo D1 por medio de una puerta AND 912. La inversa de la señal proporcionada en la entrada R del biestable SR 910 se usa también como entrada adicional para la puerta AND 908 con el fin de garantizar que las entradas S y R del biestable SR no son nunca iguales, las dos, a uno. La salida del biestable SR 910 es el impulso de temporización de línea de palabra WTP para la submatriz i-ésima. El impulso de temporización de línea de palabra WTP<sub>i</sub> se combina lógicamente con las direcciones X predecodificadas del predecodificador 904b por medio de una pluralidad de puertas AND 911.

La salida de las puertas AND 911 es una señal de habilitación de línea de palabra WL para habilitar la línea de palabra seleccionada. El impulso de temporización de línea de palabra WTP<sub>i</sub> está acoplado además a un circuito de ecualización de líneas de bit 913 por medio de un inversor 915 para ecualizar y precargar los pares de líneas de bits a un voltaje de precarga de línea de bit VBLP cuando el WTP es bajo. A la señal invertida se le hace referencia como señal de ecualización de líneas de bit BLEQ.

El impulso de temporización de línea de palabra WTP<sub>i</sub> se combina además con una versión retardada de él por medio de la puerta AND 914 para proporcionar una señal de habilitación de fuente de alimentación de amplificadores de detección 916. La señal de habilitación de fuente de alimentación 916 del amplificador de detección alimenta amplificadores de detección SAP con el fin de proporcionar alimentación a los dispositivos PMOS de amplificadores de detección de líneas de bit y SAN con el fin de proporcionar alimentación a los dispositivos NMOS de amplificadores de detección de líneas de bit. El impulso de temporización de línea de palabra WTP se retarda por medio del elemento de retardo D3. La señal de habilitación de amplificadores de detección 916 habilita la fuente de alimentación de los amplificadores de detección para alimentar los amplificadores de detección a través de los pares de líneas de bit correspondientes a la submatriz seleccionada.

La señal de habilitación de fuente de alimentación de amplificadores de detección 916 se retarda además por medio del elemento de retardo D4 para generar una señal de habilitación de selección de columna CSE. La señal de habilitación de selección de columna CSE se combina con las señales de dirección de selección de columna global del decodificador de columna 904a por medio de una puerta AND 918 asociada a esa submatriz particular. La salida de la puerta AND 918 proporciona una señal de selección de columna local LCSL. La señal de selección de columna local LCSL habilita el par de líneas de bit apropiado por medio de un dispositivo de acceso a columnas para una operación ya sea de lectura, o de escritura o de refresco.

Una puerta AND 920 combina la señal de selección de grupo, la señal de reloj CLK, y la señal de reloj retardada por el retardo D2. La salida de la puerta AND 920 es una señal de lectura-escritura activa RWACTIVE. La señal RWACTIVE es invertida por el inversor 922 para controlar transistores de precarga y ecualización de líneas de datos 924, acoplados en serie, con el fin de precargar un par de líneas de datos 926 a un voltaje de precarga de línea de datos VDLP cuando no se selecciona la submatriz.

La señal RWACTIVE se combina también con la señal ESCRITURA por medio de la puerta AND 928. La salida de la puerta AND 928 habilita una memoria intermedia de escritura 930 para controlar datos de entrada recibidos, sobre el par de líneas de datos 926. La entrada a la memoria intermedia de escritura 930 se recibe desde un biestable de tipo D 932, el cual recibe datos de entrada externos como entrada propia y es activado mediante impulsos de reloj por la señal de reloj CLK. La señal RWACTIVE se combina además con la inversa de la señal de lectura y la señal de reloj

CLK por medio de una puerta NOR 934. La salida de la puerta NOR 934 es una señal de reloj de muestreo de lectura RSAMPCLK para habilitar un biestable de tipo D diferencial 936 con el fin de leer datos presentes en el par de líneas de datos 926. La salida del biestable de tipo D diferencial 936 está acoplada a un multiplexor de tamaños de palabra 938. El multiplexor 938 se muestra en un formato conceptual, aunque, en una implementación física, se construye usando una configuración de multiplexor distribuida. Desde la salida de un biestable D 940 se proporciona una señal de habilitación al multiplexor de tamaños de palabra 938. La entrada al biestable D 940 es la señal de selección de grupo, y el biestable D 940 es activado mediante impulsos de reloj por la señal de reloj CLK.

En relación con la figura 10a, con el número de referencia 1000 se ilustra de manera general un diagrama de temporización para temporizar señales asociadas en la figura 9 para una operación de lectura. La operación del circuito se describe de la manera siguiente en referencia a las figuras tano 9 como 10. El impulso de temporización de línea de palabra WTP se mantiene a un nivel lógico bajo cuando la memoria está en reposo. Cuando WTP está bajo, todas las líneas de palabra están a un nivel bajo y las líneas de bit y las líneas de datos dentro de la submatriz se mantienen activamente en un estado ecualizado y precargado. Cada submatriz tiene una señal dedicada de WTP que se selecciona a través de puertas de selección de submatrices 908. La señal WTP; asociada a una submatriz seleccionada se pone en estado activo después de un periodo de retardo fijo desde el flanco de subida del reloj que muestrea una orden válida en la interfaz de memoria. WTP; permanece a un nivel alto durante el resto del periodo del reloj hasta que la misma se reinicializa incondicionalmente por medio del siguiente flanco de subida del reloj. WTP actúa como una señal de control (gating) para los controladores de líneas de palabra regulares y redundantes (no mostrados). Cuando WTP; sube y baja, la línea de palabra dentro de la submatriz seleccionada por la dirección muestreada sube y baja con él. El flanco de subida de WTP; controla también una circuitería auto-temporizada para habilitar los amplificadores de detección de líneas de bit y dispositivos de acceso de selección de columna local.

10

15

20

25

30

35

40

55

60

65

Haciendo referencia una vez más a la figura 10, después de un retardo preestablecido programable D 1, el impulso de temporización de línea de palabra WTP; pasa a un nivel alto, provocando que la señal de ecualización de líneas de bit BLEQ y la señal de línea de palabra WL pasen a un nivel alto. Debería observarse que los retardos D1, D2, D3, D4 se implementan todos ellos usando un circuito de retardo novedoso descrito en la solicitud en trámite con la presente de MOSAID n.º 09/616.973. Después de un retardo preestablecido programable D2 desde el flanco de subida de la señal de reloj, la señal RWACTIVE se pone en estado activo, provocando que la señal RSAMPCLK pase a un nivel alto. Como respuesta a la puesta en estado activo de la señal de línea de palabra WL, comienza a desarrollarse un diferencial de voltaje a través del par de líneas de bit. Después de un retardo combinado D1 + D3, las señales de fuente de alimentación de amplificadores de detección SAP, SAN se ponen en estado activo, amplificando el diferencial de voltaje a través del par de líneas de bit. Después de un retardo combinado DI + D3 + D4, la señal de selección de columna local LSCL se pone en estado activo, seleccionando así una columna desde la cual se van a transferir datos. Como respuesta a la puesta en estado activo de la señal de selección de columna local LCSL, se transfieren datos desde la columna seleccionada a un par asociado de líneas de datos.

Es importante observar que cada una de las etapas antes descritas se inició por medio de señales autotemporizadas obtenidas a partir del impulso de temporización de línea de palabra maestra WTPI, permitiendo así una precisión de sintonización fina de la temporización de cada señal. Debería observarse también que, aunque la descripción anterior se refería genéricamente a una columna seleccionada y un par asociado de líneas de datos, los expertos en la materia apreciarán que, de hecho, se pueden seleccionar múltiples columnas por medio de una señal de selección de columna, presentando cada una de ellas líneas de datos asociadas.

Para operaciones de lectura, una versión retardada RSAMPCLK de la señal de reloj de entrada CLK proporciona entradas de muestreo complementarias a un conjunto de H biestables de tipo D, de entrada, diferenciales, de tamaño de palabra, 936, los cuales están conectados también a las líneas de datos 926 para un grupo de una o más submatrices. Los biestables de tipo D son preferentemente aquellos descritos en la solicitud de patente de MOSAID en trámite con la presente, n.º PCT/CA00/00879 presentada el 30 de julio de 2000. En el siguiente flanco de subida del reloj CLK, RSAMPCLK retiene las entradas del reloj de muestreo a los biestables de datos de lectura 936 que capturan los datos de lectura al final de la operación de acceso a filas. La salida de los biestables de datos de lectura 936 para el grupo de submatrices que contiene la submatriz a la que se accede se encamina a través de una red de multiplexores 938 para seleccionar los datos de salida finales de entre el grupo de submatrices apropiado antes de presentarlos a los pines o macropines del dispositivo.

La utilización de dicho esquema de temporización autoreferenciado para controlar operaciones de lectura da como resultado órdenes de lectura que se pueden emitir hacia la memoria en cada ciclo de reloj y tienen una latencia efectiva de dos ciclos. Es decir, una orden de lectura muestreada en un flanco de reloj de subida N presentará sus datos de salida en la interfaz con el tiempo suficiente de establecimiento para permitir que el controlador de la memoria los retenga usando el flanco de subida de reloj N+2.

Las operaciones de escritura también hacen uso de la circuitería autotemporizada para generar RWACTIVE, la cual remite a una versión retardada de la señal de reloj de entrada CLK tal como se muestra en la figura 9. La circuitería auto-temporizada apaga la circuitería de ecualización y precarga de líneas de datos 924 a través de la salida de nivel lógico bajo del inversor 922. Habilita la memoria intermedia de escritura 930 proporcionando un nivel lógico alto desde la salida de la puerta AND 928 para controlar los datos de escritura muestreados en la interfaz hacia las

líneas de datos 926. Los dispositivos de acceso a columnas dentro de una submatriz son controlados por señales de selección de columna local LCSL generadas por puertas AND 918 según se ha mencionado previamente.

El control preciso de la temporización relativa entre la detección de líneas de bit y la habilitación de los dispositivos de acceso a columnas es importante para llevar a cabo operaciones de escritura. Típicamente, una vez que se ha seleccionado una línea de palabra, se accederá a todas las celdas de memoria asociadas a esa línea de palabra particular y los datos almacenados se transferirán a las líneas de bit respectivas, por medio de transistores de acceso a líneas de palabra. Posteriormente, todos los amplificadores de detección asociados a la submatriz seleccionada comenzarán a detectar los datos sobre todas sus líneas de bit asociadas (para garantizar la integridad de los datos dentro de líneas de bit no seleccionadas dentro de la fila). En DRAMs convencionales, para una operación de escritura, una vez que se ha seleccionado una columna particular, los controladores de escritura sobrescribirán los datos detectados por los amplificadores de detección de líneas de bit. No obstante, de acuerdo con la invención, existe un breve intervalo en el comienzo de una operación de escritura entre el momento en el que los amplificadores de detección comienzan a incrementar la división del voltaje de la línea de bit como respuesta a la activación de una línea de palabra y la aproximación de la división de la línea de bit a niveles completos del voltaje de alimentación. Durante este intervalo, se puede llevar a cabo una operación de escritura a través de un control preciso de la temporización entre la activación de los amplificadores de detección de líneas de bit y la activación de dispositivos de acceso a columnas. Si los dispositivos de columnas se habilitan demasiado tarde, entonces una operación de escritura destinada a sobrescribir datos de fase opuesta en las líneas de bit tardará mucho tiempo debido a que los controladores de escritura tienen que superar una división de voltaje completa de la fase opuesta. Si los dispositivos de acceso a columnas se habilitan demasiado pronto, existe un riesgo de que se produzca una alteración de datos por el acoplamiento de ruido entre el bus de datos local (el cual, en esta forma de realización, se extiende paralelo a líneas de bit) y líneas de bit no seleccionadas para la operación de escritura. Las líneas no seleccionadas llevan a cabo de forma esencial solamente una operación de detección y restauración.

25

30

35

40

5

10

15

20

Por este motivo, el carácter autotemporizado de la presente invención permite un control muy ajustado entre la temporización de la activación de líneas de palabra, la activación de amplificadores de detección de líneas de bit, la activación de controladores de escritura y la activación de selección de columnas. Específicamente, la señal WTPI experimenta una autotemporización a partir de la señal de reloj CLK, a través del retardo D1, la puerta 912 y el biestable 910. A continuación, los amplificadores de detección se activan basándose en el circuito autotemporizado que comprende el retardo D3 y la puerta 914. A continuación, la misma señal autotemporizada 916 generada por la puerta 914 se usa para controlar el retardo D4 y las puertas 918 que, por lo tanto, experimentan una autotemporización a partir de la activación de los amplificadores de detección y se activarán de manera precisa al mismo tiempo después de que se hayan activado los amplificadores de detección de líneas de bit. Mientras tanto, los controladores de escritura 930 se activan también a través de la circuitería auto-temporizada formada por el retardo D2 y la puerta 920 y 928. De esta manera, los controladores de escritura pueden invertir un estado lógico de fase opuesta sobre líneas de bit en las cuales están escribiendo, más rápidamente que en implementaciones de DRAM convencionales. En relación con la figura 10b, con el número de referencia 1050 se ilustra de forma general un diagrama de temporización para generar el WTPi. Si la submatriz está activa, o seleccionada, la entrada S del biestable SR 910 pasa a un nivel alto. Consecuentemente, el WTP<sub>i</sub> pasa a un nivel alto y da comienzo a la secuencia de operaciones de control requeridas para la orden. El WTP; se reinicializa a un nivel bajo en el siguiente flanco de subida del reloj. Esta situación se ilustra como caso 1. No obstante, si la submatriz está inactiva, o deseleccionada, la entrada S al biestable SR 910 permanece a un nivel bajo y, por lo tanto, el WTP<sub>i</sub> permanece a un nivel bajo. Esta situación se ilustra como caso 2.

45

50

55

60

65

Haciendo referencia de nuevo a la figura 9, en relación con la canalización de órdenes y el rol de selección de grupos, si se lleva a cabo una operación de lectura dentro de un grupo de submatrices dado en el ciclo N, entonces su selección de grupo se pondrá en estado activo durante el ciclo N. El registro 940 retiene la señal de selección de grupo en el flanco de subida de reloj que separa los periodos de reloj N y N+1. La salida de 940 controla la selección del multiplexor 938 durante el periodo de reloj N+1.

El refresco de los contenidos de memoria del dispositivo o macrobloque 502 se controla mediante un controlador de memorias externo. El controlador de memorias externo organiza el patrón y la temporización de refresco de una manera óptima para una aplicación particular. No obstante, cada celda se debería refrescar por lo menos una vez en un intervalo de refresco predefinido. El intervalo de refresco depende de la implementación y la tecnología usadas.

Para refrescar periódicamente todas las celdas de la memoria, el controlador de memorias emite A \* 2M órdenes de refresco, una para cada dirección de fila, con una frecuencia no menor que una vez cada intervalo de refresco máximo. Las órdenes de refresco actúan sobre una fila completa de celdas cada vez dentro de una submatriz y tratan los N bits menos significativos 612a de la dirección de memoria 612 como "irrelevantes".

Cuando se llevan a cabo operaciones de lectura y escritura, se refresca el contenido de la fila completa que contiene la palabra direccionada. Por lo tanto, no es necesario que las aplicaciones que pueden garantizar que por lo menos una palabra dentro de cada fila será el objetivo de una orden de lectura o escritura a intervalos inferiores o iguales al intervalo de refresco máximo lleven a cabo órdenes de refresco explícitas.

La arquitectura y circuitos de DRAM que materializan la presente invención antes descrita son el objetivo de una pluralidad de aplicaciones de alto rendimiento. La arquitectura y circuitos de la presente invención sustituyen el modelo de clase de acceso dual de las arquitecturas adicionales de DRAM. Como secuencia, ya no existe ninguna división explícita de direcciones de memoria en componentes de fila y columna, y la interfaz de memoria no incluye ningún concepto de estado de fila. Sin estado de la fila, no existe ninguna subdivisión de la capacidad de la memoria en bancos, ni hay órdenes para abrir y cerrar explícitamente filas. La arquitectura presta soporte a órdenes de lectura, escritura y refresco y requiere las mismas. Por lo tanto, la latencia y el tiempo de ciclo de estas operaciones son constantes y no dependen del valor de la dirección de entrada.

Puesto que no se presta soporte a un estado de fila visible, el estado de todas las matrices de DRAM tiene el mismo aspecto en el inicio de cada operación. Las condiciones iniciales para todas las operaciones son todas las líneas de palabra precargadas a un nivel bajo y todas las líneas de bit y líneas de datos ecualizadas y precargadas a un voltaje de precarga. Cada operación de memoria lleva a cabo una operación de acceso a fila completa y la ecualización y precarga subsiguientes de líneas de bit y líneas de datos. Esto simplifica considerablemente el diseño del controlador externo de memorias puesto que el mismo ya no necesita realizar un seguimiento de bancos abiertos.

Además, no es necesario que el controlador externo de memorias compruebe la dirección de cada operación de lectura o escritura para seleccionar la secuencia de órdenes de DRAM apropiada con el fin de llevar a cabo la operación. Por comparación, en sistemas convencionales de DRAM, el controlador de memorias debe determinar si la dirección de memoria a la que desea acceder se corresponderá con una página abierta de un banco, un banco cerrado, o un banco abierto para una página diferente.

20

35

40

45

55

60

65

Aunque la implementación anterior se ha descrito en referencia a una forma de realización específica, se pondrán de manifiesto varias modificaciones para los expertos en la materia. Por ejemplo, la sustitución del biestable de muestreo diferencial 936 por un amplificador diferencial puede reducir la latencia de lectura desde dos a un ciclo de reloj dada una reducción suficiente de la velocidad de reloj operativa máxima. A la inversa, una DRAM de gran capacidad implementada usando la arquitectura antes descrita puede utilizar una o más etapas de registro de canalización adicionales en los trayectos internos de los datos de lectura o los datos de escritura dentro de la memoria.

Esto se puede efectuar con el fin de implementar el reloj máximo de la memoria o con el fin de incrementar el tiempo de establecimiento de datos de lectura a reloj, disponible para el controlador externo de memorias. La situación es similar para una DRAM con un grado muy alto de diezmado en muchas submatrices.

La presente forma de realización de la invención proporciona elementos adicionales de fila y columna dentro de cada submatriz de celda de memoria para la reparación, basada en la redundancia, de algunos tipos de defectos de fabricación. En general, esta práctica incrementa ligeramente el tamaño de una submatriz e introduce pequeños retardos en el acceso a memoria. Esto es debido a unas operaciones de submatrices más lentas y a la necesidad de comparar una dirección de entrada con respecto a una lista de direcciones defectuosas antes de poner en estado activo un controlador de líneas de palabra en caso de redundancia de filas o una columna en caso de redundancia de columnas. Las secuencias de temporización descritas en la presente forma de realización pueden eliminar parte o la totalidad del componente de retardo por comparación de redundancia de direcciones de fila, del tiempo de ciclo de la memoria, solapándolo con la ecualización y precarga de líneas de bit en el inicio de un ciclo de fila. No obstante, una posibilidad alternativa consiste en excluir elementos redundantes de una submatriz en su totalidad y, en su lugar, equipar el dispositivo o macrobloque de memoria con un excedente de submatrices con vistas a la reparación mediante sustitución redundante de submatrices defectuosas.

La redundancia de columnas se implementa colocando multiplexores (no mostrados en la figura 9) entre las líneas de datos de grupos de submatrices 926 y biestables de muestreo 936/memorias intermedias de escritura 930 para permitir la sustitución de elementos de datos regulares por elementos de columna redundantes.

Adicionalmente, pares de líneas de datos de elementos redundantes complementarios pueden sustituir a pares de líneas de datos regulares complementarios o bien de forma individual o bien como parte de grupos mayores. La circuitería de ecualización y precarga de líneas de datos está situada en el lado de los multiplexores de redundancia de línea de datos correspondiente a las matrices de memoria para minimizar el tiempo necesario para llevar a cabo esta operación.

La práctica de llevar a cabo una precarga y ecualización de líneas de bit en una primera parte de un ciclo de fila seguida por una secuencia de temporización iniciada por WTP; para acceder a una fila seleccionada presenta varias ventajas con respecto a formas de realización convencionales. El elemento de retardo D1 usado para retardar la puesta en estado activo del impulso de temporización de línea de palabra (WTP<sub>i</sub>) después del flanco de subida del reloj de entrada, está diseñado para generar la duración necesaria mínima durante la cual WTP<sub>i</sub> está en nivel bajo. Esta duración baja necesaria mínima del WTPi está diseñada para garantizar una ecualización y precarga adecuadas de líneas de bit bajo condiciones del peor de los casos de variación del proceso y de voltaje de alimentación y temperatura del dispositivo. Como consecuencia, el impulso de temporización de línea de palabra

WTP<sub>i</sub> es lo más preciso posible.

En relación con la figura 11 a se ilustra un diagrama de temporización que ilustra esta correlación entre el elemento de retardo DI y la ecualización de líneas de bit. La velocidad de reloj máxima de la memoria la fija la duración necesaria en nivel alto del WTP; en las condiciones del peor de los casos para llevar a cabo de manera fiable una operación de acceso a fila y de lectura o escritura. La fracción del periodo del reloj consumida por el periodo en nivel bajo del WTP<sub>i</sub>, y, por lo tanto, la ecualización y precarga de líneas de bit entre operaciones consecutivas, es un máximo para la operación de la memoria con una velocidad de reloj máxima bajo condiciones de retardo del peor de los casos para el proceso, el voltaje y la temperatura.

10

15

5

Para una operación con una velocidad de reloj menor, o en condiciones mejores que el retardo lógico correspondiente al peor de los casos, la fracción del periodo de reloj durante la cual WTP<sub>i</sub> está en nivel bajo entre operaciones consecutivas se reduce. Esto hace que aumente el tiempo en el que una línea de palabra seleccionada está en estado activo durante un acceso de fila de una submatriz. De este modo, se incrementa la calidad de la restauración de celdas de memoria para todas las operaciones y el voltaje dividido sobre las líneas de datos para operaciones de lectura. En relación con la figura 11b, se ilustra un diagrama de temporización que ilustra una memoria que está funcionando a una velocidad de reloj menor que la máxima o bajo condiciones mejores que el retardo lógico correspondiente al peor de los casos.

- La presente forma de realización describe también un sistema que usa una interfaz síncrona que acepta y ejecuta órdenes a una velocidad de una orden por periodo del reloj de entrada de la interfaz. No obstante, se pondrá de manifiesto para los expertos en la materia la implementación de la arquitectura de DRAM antes descrita usando una interfaz asíncrona. En la figura 12a se ilustra un diagrama de temporización para una interfaz asíncrona.

- Todavía en otra forma de realización alternativa, es también posible una interfaz síncrona que estira el acceso de submatriz a través de dos o más periodos del reloj de interfaz. En referencia a la figura 12b, se ilustra un diagrama de temporización correspondiente a una forma de realización del tipo mencionado.

- Todavía en otra forma de realización alternativa, es posible una interfaz síncrona que lleva a cabo operaciones a la velocidad de una por ciclo de reloj con una latencia de datos de lectura de un ciclo de reloj.

- En la figura 13a se ilustra una forma de realización de este tipo.

- Todavía en otra forma de realización alternativa, se implementa una interfaz síncrona que lleva a cabo operaciones a la velocidad de una por ciclo de reloj con una latencia de datos de lectura de tres o más ciclos de reloj. En la figura 13B se ilustra una forma de realización de este tipo.

- Aunque la invención se ha descrito haciendo referencia a ciertas formas de realización específicas, para los expertos en la materia se pondrán de manifiesto varias modificaciones de las mismas sin apartarse del alcance de la invención según se expone en las reivindicaciones adjuntas a la misma. Además, la invención es aplicable a cualquier tipo de memoria electrónica que utiliza elementos de almacenamiento redundantes para incrementar el rendimiento eficiente. Estas incluyen, aunque sin carácter limitativo, SRAM y varias memorias no volátiles, tales como EPROM, EEPROM, EPROM flash, y FRAM.

#### **REIVINDICACIONES**

- 1. Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

- 5 una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo de habilitación de líneas de palabra acoplado a la línea de palabra para poner en estado activo la línea de palabra;

un amplificador de detección acoplado al par de líneas de bit para detectar niveles de voltaje en el par de líneas de bit y restaurar una carga en la celda de memoria;

un circuito de ecualización de líneas de bit acoplado al par de líneas de bit para precargar el par de líneas de bit; y caracterizada por que la DRAM incluye

un circuito de temporización para recibir una señal de control y controlar el circuito de ecualización de líneas de bit, el dispositivo de habilitación de líneas de palabra, y el amplificador de detección;

en la que,

15

20

25

35

en un primer flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa;

después de un primer retardo desde el primer flanco de la señal de control, el circuito de ecualización de líneas de bits se desactiva y el dispositivo de habilitación de líneas de palabra se activa;

después del primer retardo más un segundo retardo desde el primer flanco de la señal de control, el amplificador de detección se activa; y

- 30 en un segundo flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa.

- 2. DRAM según la reivindicación 1, en la que, en el primer flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva y el circuito de ecualización de líneas de bit se activa.

- 3. DRAM según la reivindicación 2, que comprende además:

un par de dispositivos de acceso a columnas acoplados al par de líneas de bit;

40 un par de buses de datos acoplado al par de dispositivos de acceso a columnas;

en la que,

- después del primer retardo más el segundo retardo más un tercer retardo desde el primer flanco de la señal de control, el par de dispositivos de acceso a columnas se activa.

- 4. DRAM según la reivindicación 3, que comprende además:

- un circuito de ecualización de buses de datos acoplado al par de buses de datos para precargar el par de buses 50 de datos;

en la que,

- después del primer retardo más el segundo retardo más el tercer retardo más un cuarto retardo desde el primer flanco de la señal de control, el par de dispositivos de acceso a columnas se desactiva, el circuito de ecualización de buses de datos se activa, preferentemente en el segundo flanco de la señal de control, el circuito de ecualización de buses de datos se desactiva; y que incluye opcionalmente

- un biestable acoplado al par de buses de datos para retener datos del par de buses de datos;

en la que,

60

- en el segundo flanco de la señal de control, el biestable se activa por impulsos de reloj.

- 5. DRAM según la reivindicación 1, en la que la señal de control es o bien una señal de reloj o bien una señal estroboscópica.

- 6. DRAM según la reivindicación 5, en la que el primer flanco de la señal de control y el segundo flanco de la señal de control presentan la misma polaridad, preferentemente

- 5 el primer flanco de la señal de control y el segundo flanco de la señal de control son flancos de subida.

- 7. DRAM según la reivindicación 6, en la que el segundo flanco de la señal de control es el primer flanco que presenta la misma polaridad que el primer flanco de la señal de control tras el primer flanco de la señal de control, o

- el segundo flanco de la señal de control es el segundo flanco que presenta la misma polaridad que el primer flanco de la señal de control tras el primer flanco de la señal de control.

- 8. Método de lectura de datos en una Memoria Dinámica de Acceso Aleatorio (DRAM), que comprende:

- 15 recibir una orden de lectura y una dirección en un primer flanco de una señal de control;

- y caracterizado por que presenta las etapas siguientes:

- desactivar un dispositivo de habilitación de líneas de palabra para deseleccionar una línea de palabra en el primer flanco de la señal de control;

- activar el dispositivo de habilitación de líneas de palabra para seleccionar la línea de palabra de acuerdo con la dirección después de un primer retardo desde el primer flanco de la señal de control;

- activar un amplificador de detección acoplado a un par de líneas de bit para detectar datos en una celda de memoria acoplada a la línea de palabra y al par de líneas de bit después del primer retardo más un segundo retardo desde el primer flanco de la señal de control; y

- desactivar el dispositivo de habilitación de líneas de palabra para deseleccionar la línea de palabra en un segundo flanco de la señal de control.

- 9. Método según la reivindicación 8, que comprende además:

- activar un circuito de ecualización de líneas de bit y desactivar el dispositivo de habilitación de líneas de palabra en el primer flanco de la señal de control, y opcionalmente

- activar un circuito de ecualización de buses de datos acoplado a un par de buses de datos para precargar el par de buses de datos después de un tercer retardo desde el primer flanco de la señal de control.

- 40 10. Método según la reivindicación 9, que comprende además:

65

- desactivar el circuito de ecualización de buses de datos en el primer flanco de la señal de control, y opcionalmente

- desactivar el circuito de ecualización de buses de datos en el segundo flanco de la señal de control.

- 11. Método según la reivindicación 10, que comprende además:

- activar un par de dispositivos de acceso a columnas acoplados al par de líneas de bit y el par de buses de datos 50 después del primer retardo más el segundo retardo más un cuarto retardo desde el primer flanco de la señal de control, y opcionalmente

- retener datos del par de buses de datos en el segundo flanco de la señal de control.

- 55 12. Método según la reivindicación 8, en el que la señal de control es o bien una señal de reloj o bien una señal estroboscópica.

- 13. Método de escritura de datos en una Memoria Dinámica de Acceso Aleatorio (DRAM), que comprende:

- 60 recibir una orden de escritura, unos datos que se deben escribir, y una dirección en un primer flanco de una señal de control; y caracterizado por que presenta las etapas siguientes:

- desactivar un dispositivo de habilitación de líneas de palabra para deseleccionar una línea de palabra en el primer flanco de la señal de control;

- activar el dispositivo de habilitación de líneas de palabra para seleccionar la línea de palabra de acuerdo con

la dirección después de un primer retardo desde el primer flanco de la señal de control;

- activar un par de dispositivos de acceso a columnas acoplados a un par de líneas de bit y un par de buses de datos después del primer retardo más un segundo retardo más un tercer retardo desde el primer flanco de la señal de control;

- activar una memoria intermedia de escritura para escribir los datos que se deben escribir en el par de buses de datos después de un cuarto retardo desde el primer flanco de la señal de control; y

- desactivar el dispositivo de habilitación de líneas de palabra para deseleccionar la línea de palabra en un segundo flanco de la señal de control.

- 14. Método según la reivindicación 13, que comprende además:

5

- desactivar la memoria intermedia de escritura en el segundo flanco de la señal de control, o retener datos del par de buses de datos en el segundo flanco de la señal de control.

- 15. Método según la reivindicación 13, en el que la señal de control es o bien una señal de reloj o bien una señal 20 estroboscópica.

FIG. 3

FIG. 5

**FIG. 7**

FIG. 8

FIG. 10a

FIG. 10b

FIG. 11a

FIG. 11b