# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 523 878

61 Int. Cl.:

**G06F 9/312** (2006.01) **G06F 13/38** (2006.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 08.11.2010 E 10776345 (0)

(97) Fecha y número de publicación de la concesión europea: 22.10.2014 EP 2430524

- (54) Título: Instrucciones de almacenamiento/almacenamiento de bloque para la comunicación con adaptadores

- (30) Prioridad:

23.06.2010 US 821194

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: **02.12.2014**

(73) Titular/es:

INTERNATIONAL BUSINESS MACHINES CORPORATION (100.0%) New Orchard Road Armonk, NY 10504, US

(72) Inventor/es:

GREINER, DAN; CRADDOCK, DAVID; GREGG, THOMAS y FARRELL, MARK

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

#### **DESCRIPCIÓN**

Instrucciones de almacenamiento/almacenamiento de bloque para la comunicación con adaptadores

#### **Antecedentes**

5

10

15

20

25

30

35

40

50

Esta invención se refiere, en general, al procesamiento de entradas/salidas de un entorno informático y, en particular, a facilitar la comunicación con los adaptadores del entorno informático.

Un entorno informático puede incluir uno o más tipos de dispositivos de entrada/salida, incluyendo diversos tipos de adaptadores. Un tipo de adaptador es un adaptador de tipo interconexión de componentes periféricos (Peripheral Component Interconnect, PCI) o de tipo interconexión de componentes periféricos express (Peripheral Component Interconnect Express, PCIe). Este adaptador incluye uno o más espacios de direcciones usados en la comunicación de datos entre el adaptador y el sistema al cual está conectado el adaptador. La especificación PCI está disponible en la World Wide Web en www.pcisig.com/home.

La patente US Nº 6.704.831, presentada el 9 de Marzo de 2004, Avery, "Method and Apparatus for Converting Address Information Between PCI Bus Protocol and a Message-Passing Queue-Oriented Bus Protocol", describe que las operaciones de carga/almacenamiento PCI y las operaciones DMA se implementan a través de pares de colas de trabajo en una arquitectura de bus orientada a colas, con intercambio de mensajes. El espacio de direcciones PCI se divide en segmentos y cada segmento, a su vez, se divide en regiones. A cada segmento se le asigna una cola de trabajo independiente. Una primera parte de una dirección PCI es comparada con los rangos de direcciones representados por los segmentos y usados para seleccionar un segmento de memoria y su cola de trabajo correspondiente. Una entrada en la cola de trabajo contiene una segunda parte de la dirección PCI que especifica una región dentro del segmento seleccionado que es asignada a un dispositivo PCI específico. En una realización, las operaciones de carga/almacenamiento PIO se implementan seleccionando una cola de trabajo asignada a las operaciones PIO y creando una entrada de cola de trabajo con la dirección PCI de un registro en un dispositivo PCI y un puntero a los datos PIO. La entrada en la cola de trabajo es enviada a un puente PCI donde la dirección PCI es extraída y usada para programar el registro de dispositivo apropiado con los datos usando el puntero de datos. Las transferencias DMA son implementadas también seleccionando una cola de trabajo por medio de una comparación de una parte de la dirección PCI generada por el dispositivo PCI con una tabla de rangos de direcciones y seleccionando una cola de trabajo que proporciona servicio al rango de direcciones. Se crea una entrada de cola de trabajo con el resto de la dirección PCI y un puntero a los datos DMA. Se usa una operación RDMA para realizar la transferencia DMA. Los datos de región y página son usados en conexión con una tabla de protección de traducción en el adaptador de canal de servidor para acceder a la memoria física y realizar la transferencia DMA.

La patente US Nº 7.613.847, presentada el 3 de Noviembre de 2009, Kjos et al, "Partially Virtualizing an E/S Device for Use by Virtual Machines", describe un sistema de ordenador que comprende un ordenador físico y un monitor de máquina virtual ejecutable en el ordenador físico y configurado para crear una emulación de al menos un sistema operativo huésped adaptado para controlar el ordenador físico. El sistema de ordenador comprende además un servidor ejecutable en el ordenador físico que gestiona los recursos físicos acoplados al ordenador físico en nombre del monitor de máquina virtual y el al menos un sistema operativo huésped. El servidor está adaptado para virtualizar un espacio de direcciones de a configuración de interconexión de componentes periféricos (PCI) de manera que el al menos un sistema operativo huésped controla los dispositivos de entrada/salida (E/S) PCI directamente y en ausencia de emulación E/S.

En algunos sistemas, tales como los descritos en la publicación de patente internacional WO 02/41157 A2, una parte de un espacio de direcciones de la unidad central de procesamiento (CPU) acoplada al adaptador es asignada a un espacio de direcciones del adaptador permitiendo que las instrucciones de CPU que acceden al almacenamiento manipulen directamente los datos en el espacio de direcciones del adaptador.

# 45 Breve sumario

Según un aspecto de la presente invención, se proporciona una capacidad para facilitar la comunicación con los adaptadores, tales como adaptadores PCI o PCIe. Se proporcionan y usan para la comunicación instrucciones de control diseñadas específicamente para la comunicación de datos desde y hacia los adaptadores.

La provisión de un producto de programa de ordenador para ejecutar una instrucción de almacenamiento para almacenar datos en un adaptador supera los inconvenientes de la técnica anterior y proporciona una serie de ventajas. El producto de programa de ordenador incluye un medio de almacenamiento legible por ordenador, legible por un circuito de procesamiento, e instrucciones de almacenamiento para su ejecución por el circuito de procesamiento para realizar un procedimiento. El procedimiento incluye, por ejemplo, obtener una instrucción

máquina para su ejecución, en el que la instrucción máquina está definida para su ejecución por un ordenador según una arquitectura de ordenador, en el que la instrucción máquina incluye, por ejemplo, un campo de código de operación que identifica una instrucción de almacenamiento en adaptador; un primer campo que identifica una primera ubicación que incluye los datos a ser almacenados en un adaptador; un segundo campo que identifica una segunda ubicación, cuyos contenidos incluyen un descriptor de función que identifica el adaptador, una designación de un espacio de direcciones dentro del adaptador en el que deben almacenarse los datos, y un desplazamiento dentro del espacio de direcciones; y ejecutar la instrucción máquina, en el que la ejecución incluye usar el descriptor de función para obtener una entrada de la tabla de funciones asociada con el adaptador; obtener una dirección de datos del adaptador usando al menos uno de entre la información en la entrada de la tabla de funciones y el desplazamiento; y almacenar datos desde la primera ubicación en una ubicación específica en el espacio de direcciones identificado por la designación del espacio de direcciones, la ubicación específica identificada por la dirección de datos del adaptador.

Además, se proporciona un producto de programa de ordenador para ejecutar una instrucción de almacenamiento de bloque para almacenar datos en un adaptador. El producto de programa de ordenador incluye un medio de almacenamiento legible por ordenador, legible por un circuito de procesamiento, e instrucciones de almacenamiento para su ejecución por el circuito de procesamiento para realizar un procedimiento. El procedimiento incluye, por ejemplo, obtener una instrucción máquina para su ejecución, en el que la instrucción máquina está definida para su ejecución por un ordenador según una arquitectura de ordenador, en el que la instrucción máquina incluye, por ejemplo, un campo de código de operación que identifica una instrucción de almacenamiento de bloque en el adaptador; en el que un primer campo identifica una primera ubicación, cuyos contenidos incluyen un descriptor de función que identifica un adaptador, y una designación de un espacio de direcciones dentro del adaptador en el que deben almacenarse los datos; un segundo campo que identifica una segunda ubicación que incluye un desplazamiento dentro del espacio de direcciones; un tercer campo que identifica una tercera ubicación que incluye una dirección en la memoria que incluye los datos a ser almacenados en el adaptador; y ejecutar la instrucción máquina, en el que la ejecución incluye usar el descriptor de función para obtener una entrada de la tabla de funciones asociada con el adaptador; obtener una dirección de datos del adaptador usando la información en la entrada de la tabla de funciones y el desplazamiento; y almacenar los datos obtenidos desde la memoria en la dirección en el tercer campo en una ubicación específica en el espacio de direcciones identificado por la designación del espacio de direcciones, la ubicación específica identificada por la dirección de datos del adaptador.

También se describen y reivindican en la presente memoria procedimientos y sistemas relacionados con uno o más aspectos de la presente invención.

Las técnicas de la presente invención permiten conseguir características y ventajas adicionales. Otras realizaciones y aspectos de la invención se describen en detalle en la presente memoria, y se consideran parte de la invención reivindicada.

### Breve descripción de las diversas vistas de los dibujos

5

10

15

20

25

30

35

40

50

Uno o más aspectos de la presente invención se resaltan particularmente y se reivindican marcadamente como ejemplos en las reivindicaciones al final de la presente especificación. Lo indicado anteriormente y otros objetos, características y ventajas de la invención son evidentes a partir de la descripción detallada siguiente, tomada en conjunción con los dibujos adjuntos, en los que:

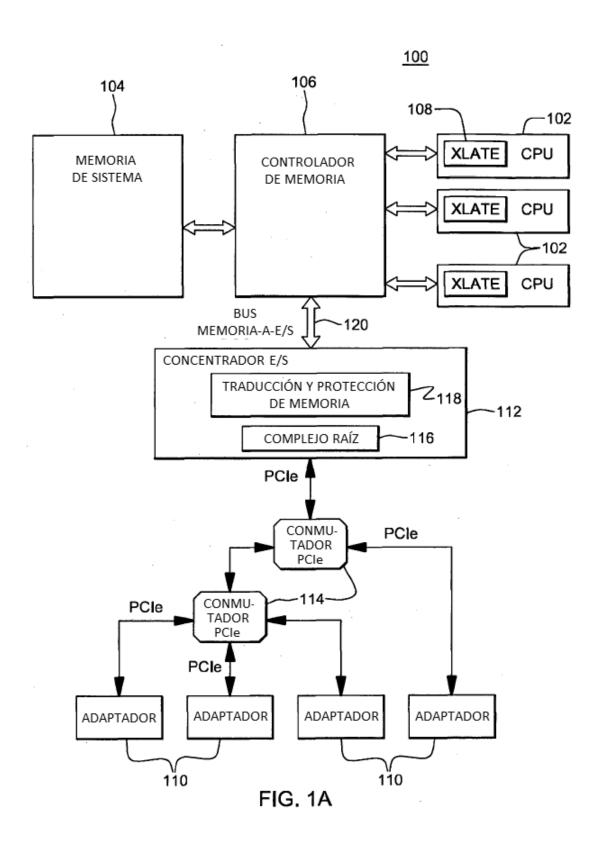

La Fig. 1A representa una realización de un entorno informático para incorporar y usar uno o más aspectos de la presente invención;

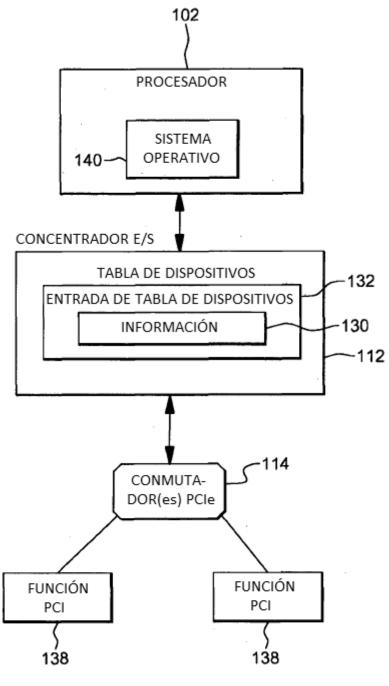

La Fig. 1B representa una realización de una entrada de la tabla de dispositivos situada en el concentrador de E/S de la Fig. 1A y usada según un aspecto de la presente invención;

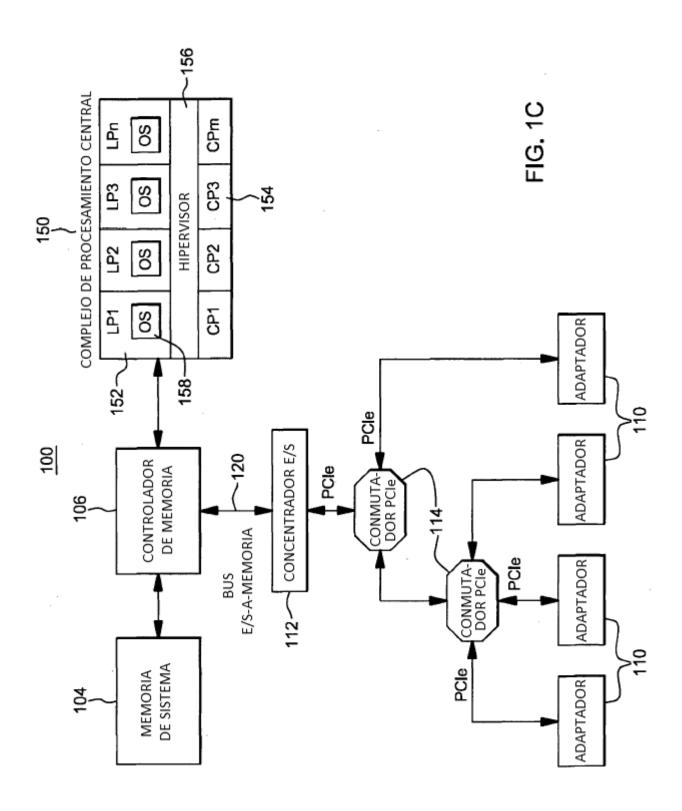

La Fig. 1C representa otra realización de un entorno informático para incorporar y usar uno o más aspectos de la presente invención;

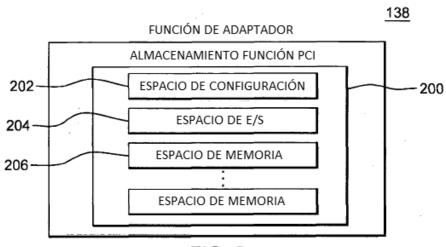

La Fig. 2 representa un ejemplo de espacios de direcciones de una función de adaptador, según un aspecto de la presente invención:

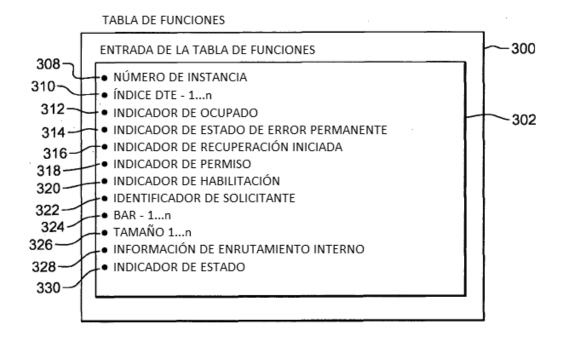

La Fig. 3A representa un ejemplo de una entrada de la tabla de funciones usada según un aspecto de la presente invención;

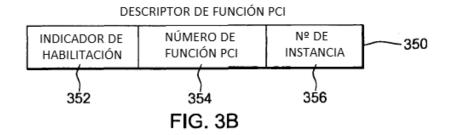

La Fig. 3B representa una realización de un descriptor de función usado según un aspecto de la presente invención;

## ES 2 523 878 T3

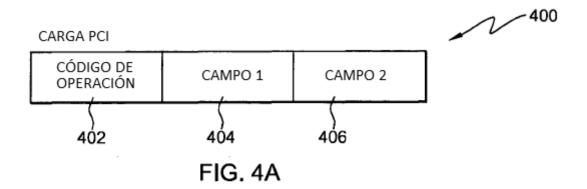

- La Fig. 4A representa una realización de una instrucción de carga PCI usada según un aspecto de la presente invención;

- La Fig. 4B representa una realización de un campo usado por la instrucción de carga PCI de la Fig. 4A, según un aspecto de la presente invención;

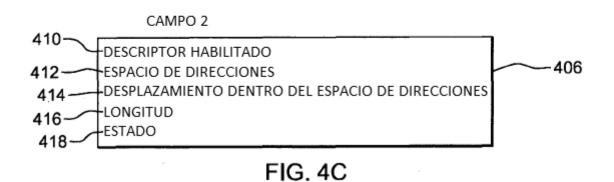

- La Fig. 4C representa una realización de otro campo usado por la instrucción de carga PCI de la Fig. 4A, según un aspecto de la presente invención;

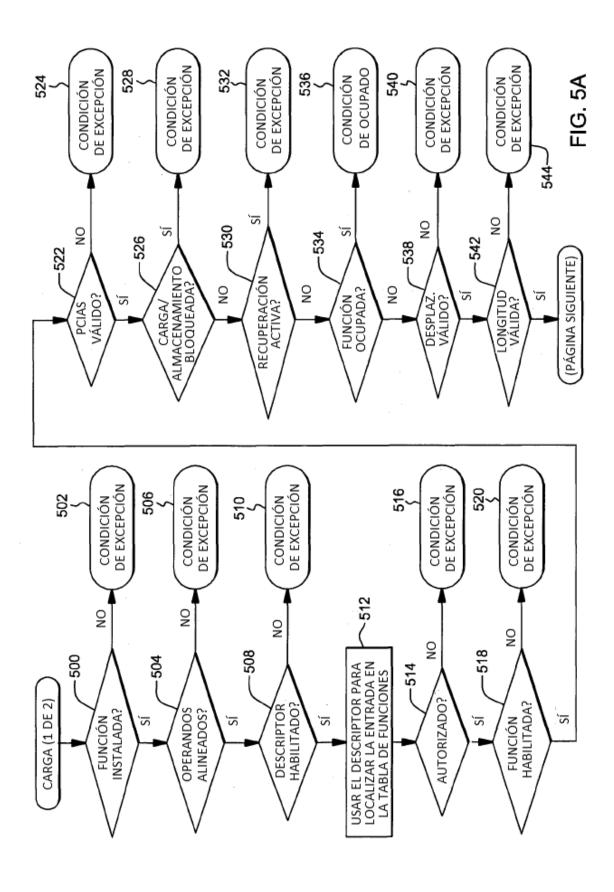

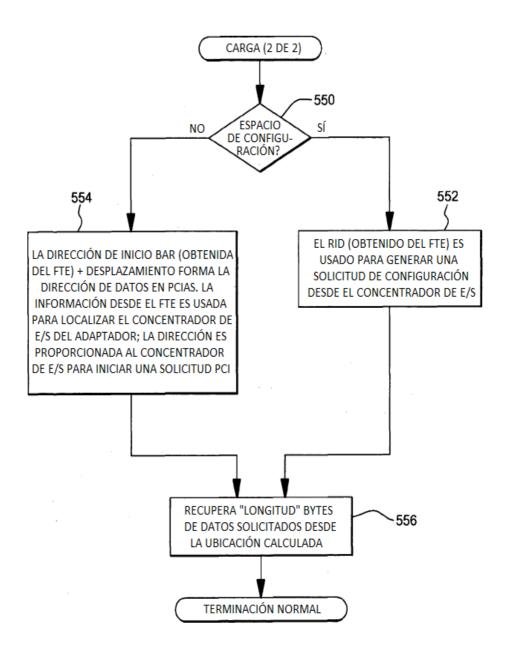

- Las Figs. 5A-5B representan una realización de la lógica para realizar una operación de carga PCI, según un aspecto de la presente invención;

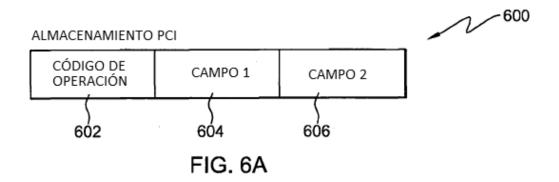

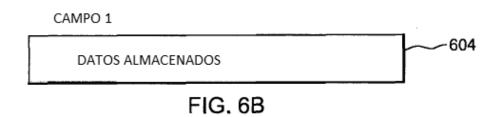

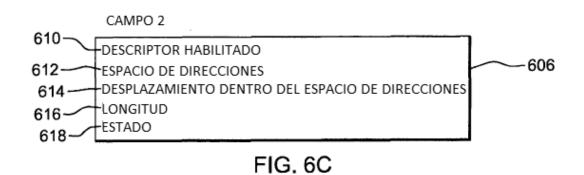

- La Fig. 6A representa una realización de una instrucción de almacenamiento PCI usada según un aspecto de la presente invención;

- La Fig. 6B representa una realización de un campo usado por la instrucción de almacenamiento PCI de la Fig. 6A, según un aspecto de la presente invención;

- La Fig. 6C representa una realización de otro campo usado por la instrucción de almacenamiento PCI de la Fig. 6A, según un aspecto de la presente invención;

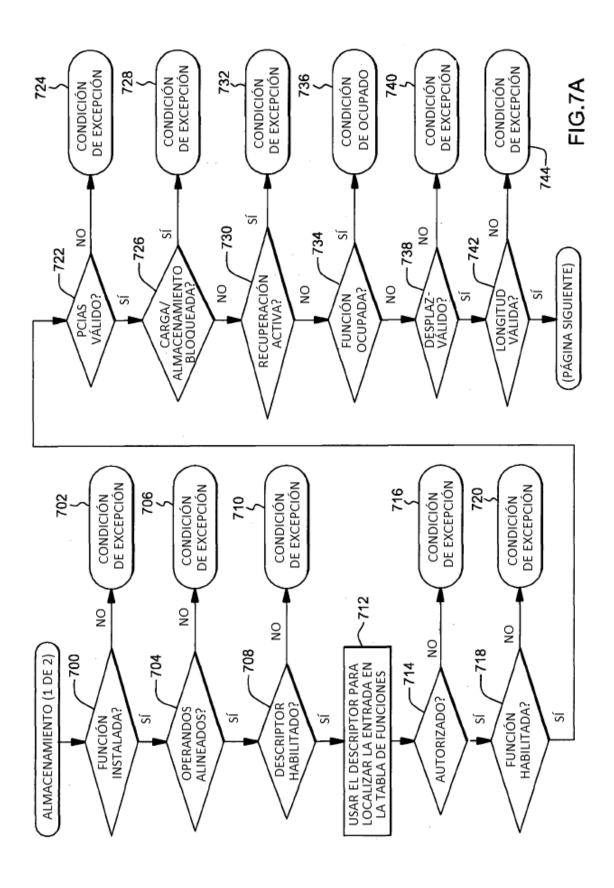

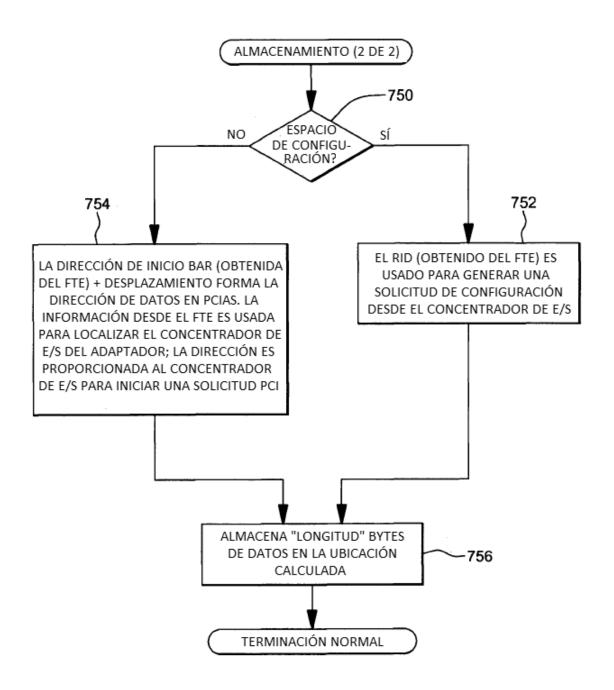

- Las Figs. 7A-7B representan una realización de la lógica para realizar una operación de almacenamiento PCI, según un aspecto de la presente invención;

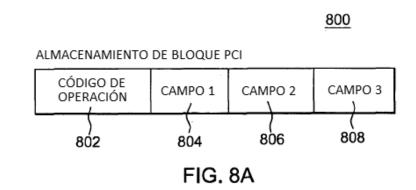

- La Fig. 8A representa una realización de una instrucción de almacenamiento de bloque PCI usada según un aspecto de la presente invención;

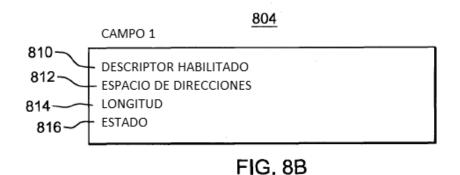

- La Fig. 8B representa una realización de un campo usado por la instrucción de almacenamiento de bloque PCI de la Fig. 8A, según un aspecto de la presente invención;

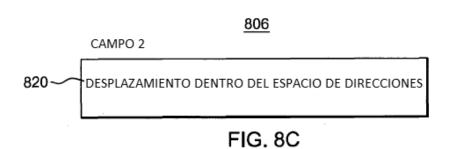

- La Fig. 8C representa una realización de otro campo usado por la instrucción de almacenamiento de bloque PCI de la Fig. 8A, según un aspecto de la presente invención;

- La Fig. 8D representa una realización de todavía otro campo usado por la instrucción de almacenamiento de bloque PCI de la Fig. 8A, según un aspecto de la presente invención;

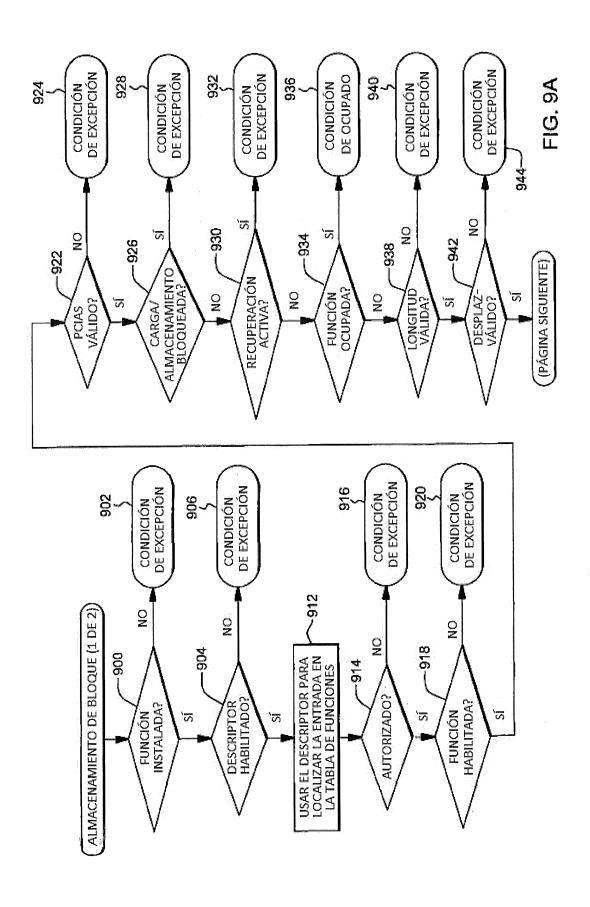

- Las Figs. 9A-9B representan una realización de la lógica para realizar una operación de almacenamiento de bloque PCI, según un aspecto de la presente invención;

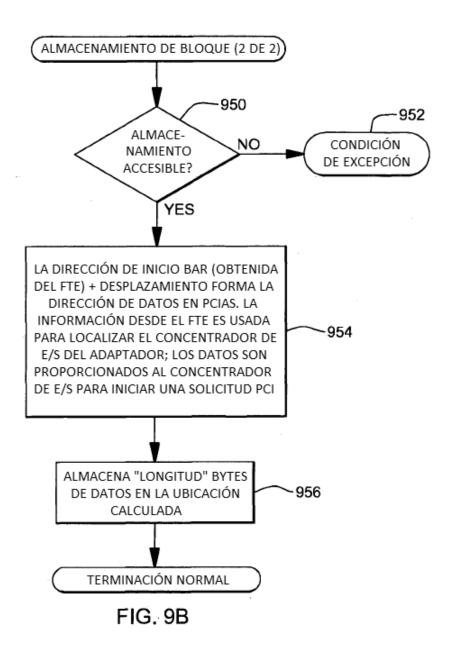

- La Fig. 10 representa una realización de un producto de programa de ordenador que incorpora uno o más aspectos de la presente invención;

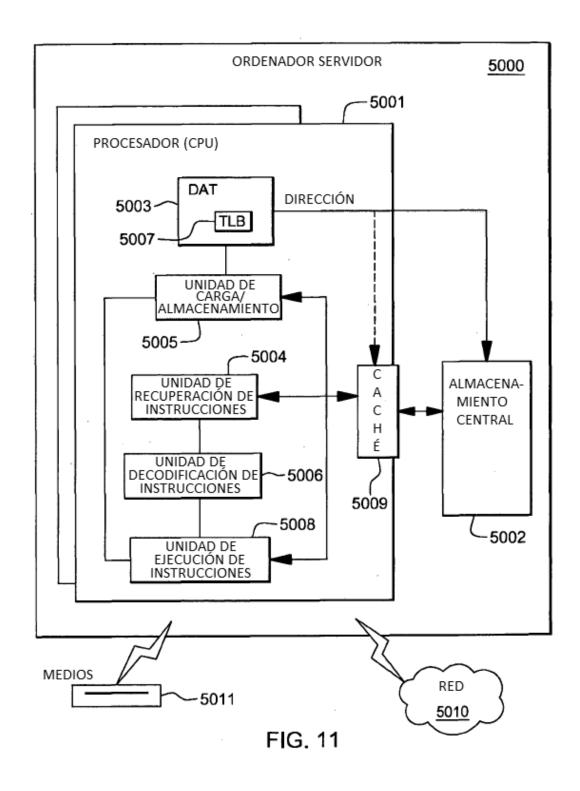

- La Fig. 11 representa una realización de un sistema de ordenador servidor para incorporar y usar uno o más aspectos de la presente invención;

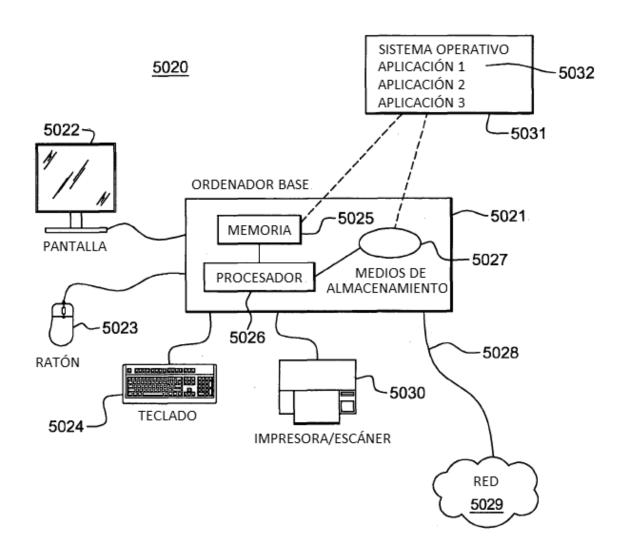

- La Fig. 12 representa un ejemplo adicional de un sistema de ordenador para incorporar y usar uno o más aspectos de la presente invención;

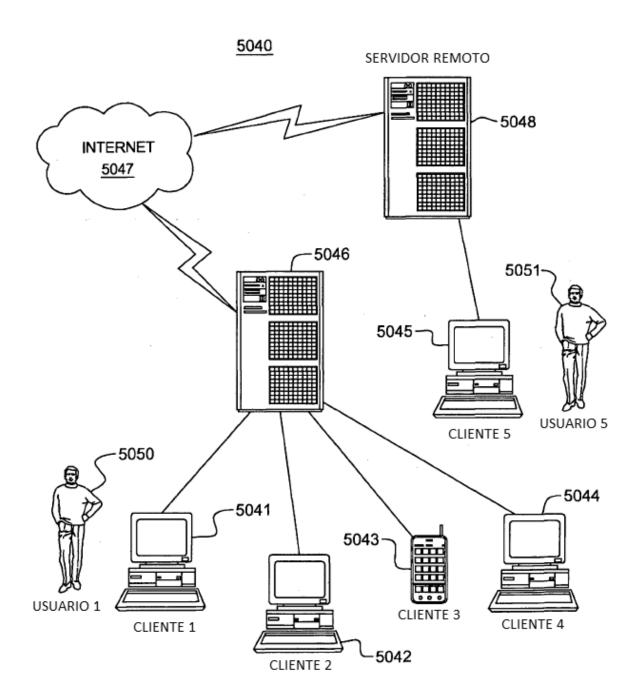

- La Fig. 13 representa otro ejemplo de un sistema de ordenador que comprende una red de ordenadores para incorporar y usar uno o más aspectos de la presente invención;

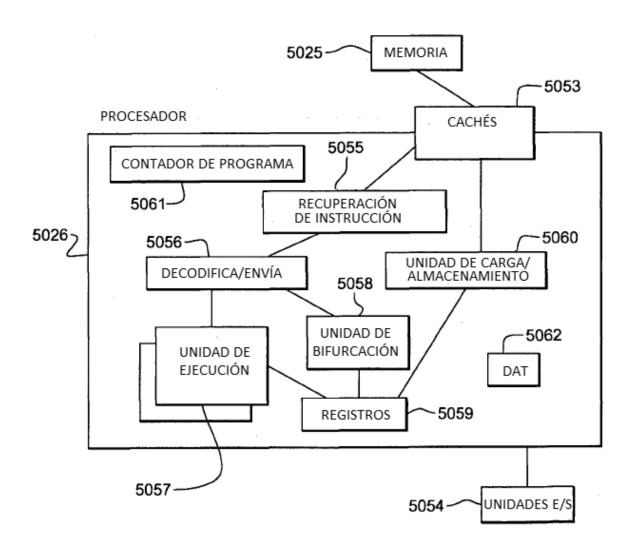

- La Fig. 14 representa una realización de diversos elementos de un sistema de ordenador para incorporar y usar uno o más aspectos de la presente invención;

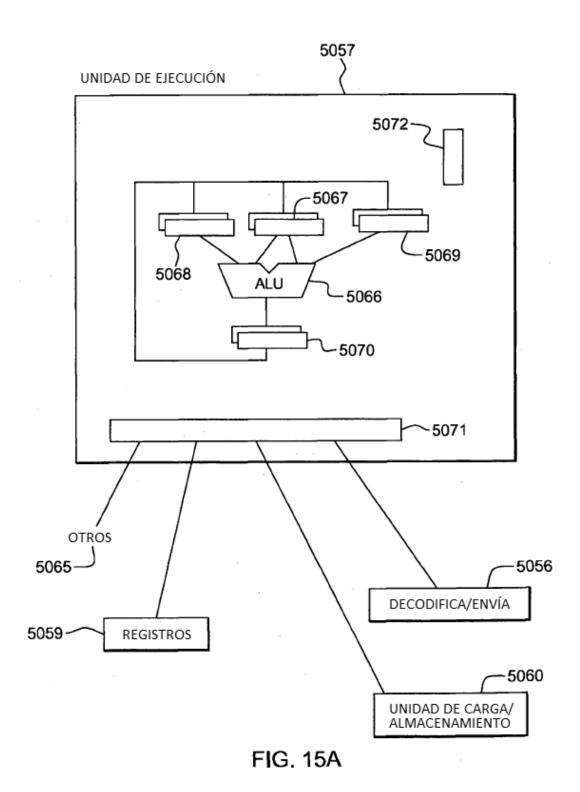

- La Fig. 15A representa una realización de la unidad de ejecución del sistema de ordenador de la Fig. 14 para incorporar y usar uno o más aspectos de la presente invención;

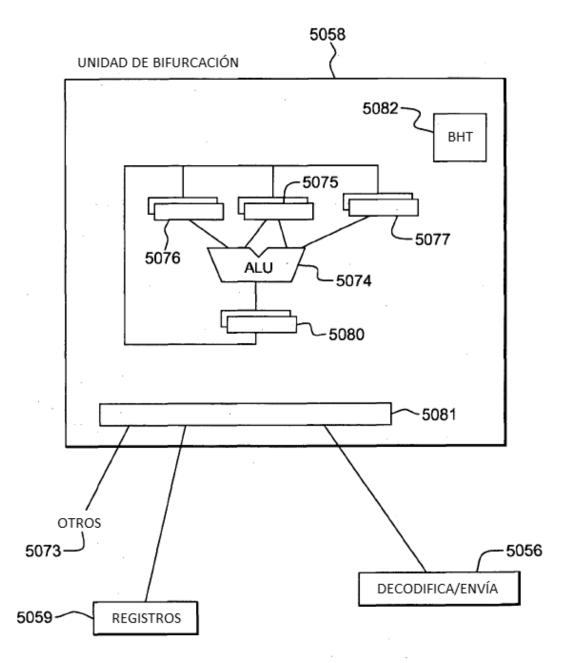

- La Fig. 15B representa una realización de la unidad de bifurcación del sistema de ordenador de la Fig. 14 para incorporar y usar uno o más aspectos de la presente invención;

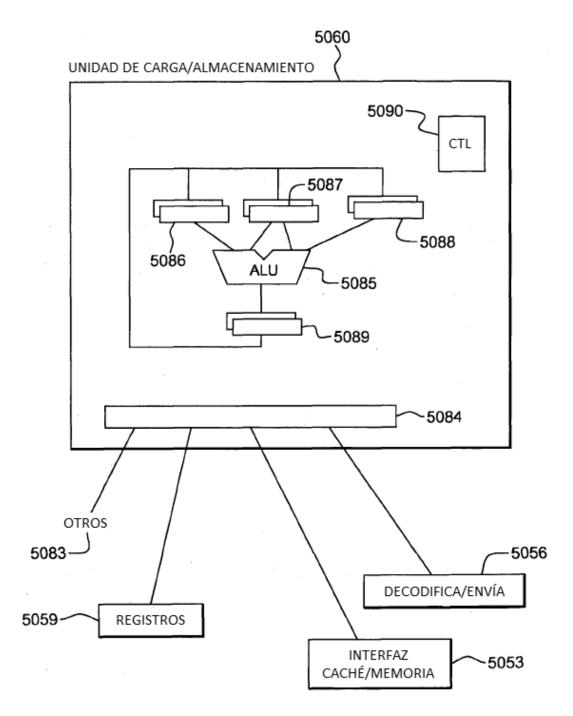

- La Fig. 15C representa una realización de la unidad de carga/almacenamiento del sistema de ordenador de la Fig. 14 para incorporar y usar uno o más aspectos de la presente invención; y

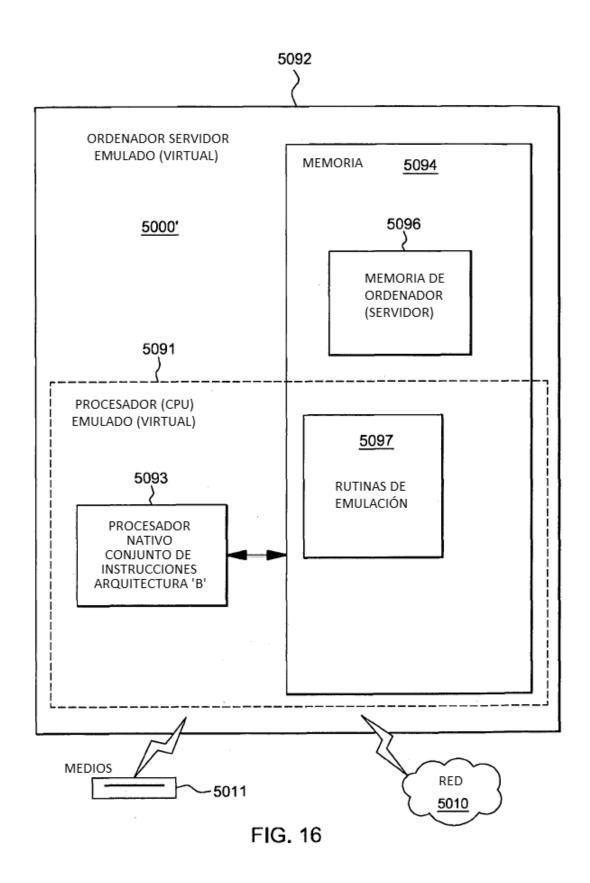

- La Fig. 16 representa una realización de un sistema de ordenador servidor emulado para incorporar y usar uno o más aspectos de la presente invención.

## Descripción detallada

5

10

15

20

25

30

35

40

45

50

55

Según un aspecto de la presente invención, se proporcionan una o más instrucciones de control para facilitar la comunicación con los adaptadores de un entorno informático. Las instrucciones de control están diseñadas específicamente para comunicar datos hacia y desde los espacios de direcciones de los adaptadores.

Tal como se usa en la presente memoria, el término adaptador incluye cualquier tipo de adaptador (por ejemplo, adaptador de almacenamiento, adaptador de red, adaptador de procesamiento, adaptador PCI, adaptador criptográfico, otro tipo de adaptadores de entrada/salida, etc.). En una realización, un adaptador incluye una función de adaptador. Sin embargo, en otras realizaciones, un adaptador puede incluir una pluralidad de funciones de adaptador. Uno o más aspectos de la presente invención son aplicables independientemente de si un adaptador incluye una función de adaptador o una pluralidad de funciones de adaptador. En una realización, si un adaptador incluye una pluralidad de funciones de adaptador, entonces cada función puede ser comunicada según un aspecto de la presente invención. Además, en los ejemplos presentados en la presente memoria, el adaptador se usa de manera intercambiable con la función de adaptador (por ejemplo, función PCI) a menos que se indique lo contrario.

Una realización de un entorno informático para incorporar y usar uno o más aspectos de la presente invención se describe con referencia a la Fig. 1 A. En un ejemplo, un entorno 100 informático es un servidor System z<sup>®</sup> ofrecido por International Business Machines Corporation. El System z<sup>®</sup> está basado en la arquitectura z/Architecture<sup>®</sup> ofrecida por International Business Machines Corporation. Los detalles relativos a la arquitectura z/Architecture<sup>®</sup> se describen en una publicación de IBM<sup>®</sup> titulada, "z/Architecture Principles of Operation", Publicación IBM Nº SA22-7832-07, Febrero de 2009. IBM<sup>®</sup>, System z<sup>®</sup> y z/Architecture<sup>®</sup> son marcas registradas de International Business Machines Corporation, Armonk, Nueva York. Otros nombres usados en la presente memoria pueden ser marcas comerciales registradas, marcas comerciales o nombres de productos de International Business Machines Corporation o de otras empresas.

En un ejemplo, el entorno 100 informático incluye una o más unidades de procesamiento central (CPUs) 102 acopladas a una memoria 104 de sistema (conocida también como memoria principal) a través de un controlador 106 de memoria. Para acceder a la memoria 104 de sistema, una unidad de procesamiento central 102 emite una solicitud de lectura o escritura que incluye una dirección usada para acceder a la memoria del sistema. Típicamente, la dirección incluida en la solicitud no es usable directamente para acceder a la memoria de sistema y, por lo tanto, es traducida a una dirección que es usable directamente para acceder a la memoria de sistema. La dirección es traducida por medio de un mecanismo de traducción (XLATE) 108. Por ejemplo, la dirección es traducida de una dirección virtual a una dirección real o absoluta usando, por ejemplo, traducción de direcciones dinámicas (Dynamic Address Translation, DAT).

La solicitud, que incluye la dirección (traducida, si es necesario), es recibida por el controlador 106 de memoria. En un ejemplo, el controlador 106 de memoria está compuesto de hardware y es usado para arbitrar el acceso a la memoria del sistema y para mantener la coherencia de la memoria. Este arbitraje es realizado para las solicitudes recibidas desde las CPUs 102, así como para las solicitudes recibidas desde uno o más adaptadores 110. Al igual que las unidades de procesamiento central, los adaptadores emiten solicitudes a la memoria 104 de sistema para acceder a la memoria de sistema.

En un ejemplo, el adaptador 110 es un adaptador de tipo interconexión de componentes periféricos (PCI) o PCI express (PCIe) que incluye una o más funciones PCI. Una función PCI emite una solicitud que es enrutada a un concentrador 112 de entradas/salidas (por ejemplo, un concentrador PCI) a través de uno o más conmutadores 114 (por ejemplo, conmutadores PCIe). En un ejemplo, el concentrador de entradas/salidas comprende hardware, incluyendo una o más máquinas de estado, y está acoplado al controlador 106 de memoria a través de un bus 120 E/S-a-memoria.

El concentrador de entradas/salidas incluye, por ejemplo, un complejo 116 raíz que recibe la solicitud desde un conmutador. La solicitud incluye una dirección de entrada/salida que es proporcionada a una unidad 118 de traducción y protección de direcciones que accede a la información usada para la solicitud. Como ejemplos, la solicitud puede incluir una dirección de entrada/salida usada para realizar una operación de acceso directo a memoria (Direct Memory Access, DMA) o para solicitar una interrupción señalizada por mensaje (Message Signaled Interrupt, MSI). La unidad 118 de traducción y protección de direcciones accede a la información usada para la solicitud MSI o DMA. Como un ejemplo particular, para una operación de DMA, la información puede ser obtenida para traducir la dirección. A continuación, la dirección traducida es reenviada al controlador de memoria para acceder a la memoria de sistema.

En un ejemplo, tal como se describe con referencia a la Fig. 1B, la información usada para la solicitud MSI o DMA emitida por un adaptador es obtenida desde una entrada 130 de la tabla de dispositivos de una tabla 132 de dispositivos situada en el concentrador de E/S (por ejemplo, en la unidad de traducción y protección de

direcciones). La entrada de la tabla de dispositivos incluye información para el adaptador, y cada adaptador tiene al menos una entrada de la tabla de dispositivos asociada con el mismo. Por ejemplo, hay una entrada en la tabla de dispositivos por cada espacio de direcciones (en la memoria del sistema) asignado al adaptador. Para una solicitud emitida desde un adaptador (por ejemplo, función 138 PCI), una entrada en la tabla de dispositivos es localizada usando un ID de solicitante proporcionado en la solicitud.

5

10

15

20

25

30

35

40

45

Con referencia ahora a la FIG. 1C, en una realización adicional de un entorno informático, además de o en lugar de una o más CPUs 102, un complejo de procesamiento central está acoplado al controlador 106 de memoria. En este ejemplo, un complejo 150 de procesamiento central incluye, por ejemplo, una o más particiones o zonas 152 (por ejemplo, particiones lógicas LP1-LPn), uno o más procesadores centrales (por ejemplo, CP1-CPm) 154, y un hipervisor 156 (por ejemplo, un gestor de particiones lógicas), cada uno de los cuales se describe a continuación.

Cada partición 152 lógica es capaz de funcionar como un sistema independiente. Es decir, cada partición lógica puede ser restablecida de manera independiente, cargada inicialmente con un sistema operativo o un hipervisor (tal como z/VM® proporcionado por International Business Machines Corporation, Armonk, Nueva York), si se desea, y funciona con diferentes programas. Un sistema operativo, un hipervisor o un programa de aplicación que se está ejecutando en una partición lógica parece tener acceso a un sistema total y completo, pero sólo está disponible una parte del mismo. Una combinación de hardware y código interno bajo licencia (Licensed Internal code) (conocido también como microcódigo o milicódigo) previene que un programa en una partición lógica interfiera con el programa en una partición lógica diferente. Esto permite que diversas particiones lógicas diferentes operen en un único procesador físico o múltiples procesadores físicos con una estrategia de división de tiempo. En este ejemplo particular, cada partición lógica tiene un sistema operativo 158 residente, que puede diferir para una o más particiones lógicas. En una realización, el sistema operativo 158 es un sistema operativo z/OS® o zLinux, proporcionado por International Business Machines Corporation, Armonk, Nueva York. z/OS® y z/VM® son marcas comerciales registradas de International Business Machines Corporation, Armonk, Nueva York.

Los procesadores 154 centrales son recursos de procesadores físicos que se asignan a las particiones lógicas. Por ejemplo, una partición 152 lógica incluye uno o más procesadores lógicos, cada uno de los cuales representa la totalidad o una parte del recurso 154 de procesador físico asignado a la partición. El recurso de procesador subyacente puede estar dedicado a esa partición o puede ser compartido con otra partición.

Las particiones 152 lógicas están gestionadas por un hipervisor 156 implementado mediante firmware que se ejecuta en los procesadores 154. Las particiones 152 lógicas y el hipervisor 156 comprenden, cada uno, uno o más programas residentes en partes respectivas del almacenamiento central asociado con los procesadores centrales. Un ejemplo de hipervisor 156 es el recurso de procesador/gestor de sistemas (Processor Resource/Systems Manager, PR/SM), proporcionado por International Business Machines Corporation, Armonk, Nueva York.

Tal como se usa en la presente memoria, el firmware incluye, por ejemplo, microcódigo, milicódigo y/o macrocódigo del procesador. Incluye, por ejemplo, instrucciones a nivel hardware y/o estructuras de datos usadas en la implementación de código de máquina de nivel superior. En una realización, incluye, por ejemplo, código propietario que típicamente es suministrado como microcódigo que incluye software de confianza o microcódigo específico del hardware subyacente y controla el acceso del sistema operativo al hardware del sistema.

Aunque en este ejemplo se describe un complejo de procesamiento central que tiene particiones lógicas, uno o más aspectos de la presente invención pueden ser incorporados en y usados por otras unidades de procesamiento, incluyendo unidades de procesamiento de un único procesador o de múltiples procesadores que no están particionados, entre otros ejemplos. El complejo central de procesamiento descrito en la presente memoria es sólo un ejemplo.

Tal como se ha descrito anteriormente, los adaptadores pueden emitir solicitudes a los procesadores solicitando diversas operaciones, tales como accesos directos a memoria, interrupciones señalizadas por mensajes, etc. Además, los procesadores pueden emitir solicitudes a los adaptadores. Por ejemplo, con relación a la Fig. 1B, un procesador 102 puede emitir una solicitud para acceder a una función 138 de adaptador. La solicitud es enrutada desde el procesador a la función de adaptador a través del concentrador 112 de E/S y uno o más conmutadores 114. En esta realización, no se muestra el controlador de memoria. Sin embargo, el concentrador de E/S puede estar acoplado al procesador directamente o a través de un controlador de memoria.

Como ejemplo, un sistema operativo 140 que se está ejecutando en el procesador emite una instrucción a la función de adaptador que solicita una operación particular. En este ejemplo, las instrucciones emitidas por el sistema operativo son específicas de la infraestructura de E/S. Es decir, debido a que la infraestructura de E/S está basada en PCI o PCIe (a los que, en la presente memoria, se hace referencia como PCI, a menos que se indique lo contrario), las instrucciones son instrucciones PCI. Las instrucciones PCI ejemplares incluyen carga PCI, almacenamiento PCI y almacenamiento de bloque PCI, por nombrar unas pocas. Aunque, en este ejemplo, la

infraestructura de E/S y las instrucciones están basadas en PCI, en otras realizaciones, pueden usarse otras infraestructuras e instrucciones correspondientes.

En un ejemplo particular, las instrucciones se dirigen a una ubicación específica dentro de un espacio de direcciones de la función de adaptador. Por ejemplo, tal como se muestra en la Fig. 2, una función 138 de adaptador incluye un almacenamiento 200, que está definido como una pluralidad de espacios de direcciones, incluyendo, por ejemplo: un espacio 202 de configuración (por ejemplo, el espacio de configuración PCI para una función PCI); un espacio 204 de E/S (por ejemplo, espacio PCI de E/S); y uno o más espacios 206 de memoria (por ejemplo, espacio PCI de memoria). En otras realizaciones, pueden proporcionarse más, menos espacios de direcciones o diferentes espacios de direcciones. Las instrucciones están dirigidas a un espacio de direcciones particular y una ubicación particular dentro del espacio de direcciones. Esto asegura que la configuración (por ejemplo, el sistema operativo, LPAR, procesador, huésped, etc.) que emite la instrucción está autorizada a acceder a la función de adaptador.

5

10

15

25

30

45

50

Para facilitar el procesamiento de las instrucciones, se usa la información almacenada en una o más estructuras de datos. Una de dichas estructuras de datos que incluye información relacionada con los adaptadores es una tabla 300 de funciones almacenada, por ejemplo, en una memoria segura. Tal como se muestra en la Fig. 3A, en un ejemplo, una tabla 300 de funciones incluye una o más entradas 302 de la tabla de funciones (Function Table Entries, FTEs). En un ejemplo, hay una entrada de la tabla de funciones por cada función de adaptador. Cada entrada 302 de la tabla de funciones incluye información a ser usada en el procesamiento asociado a su función de adaptador. En un ejemplo, la entrada 302 de la tabla de funciones incluye, por ejemplo:

20 Número 308 de instancia: Este campo indica una instancia particular del descriptor de función asociado con la entrada de la tabla de funciones;

Índice 310 de la entrada de tabla de dispositivos (Device Table Entry, DTE), 1 ... n: Puede haber uno o más índices de la tabla de dispositivos, y cada índice es un índice a una tabla de dispositivos para localizar una entrada de la tabla de dispositivos (DTE). Hay una o más entradas de la tabla de dispositivos por cada función de adaptador, y cada entrada incluye información asociada con su función de adaptador, incluyendo la información usada para procesar las solicitudes de la función de adaptador (por ejemplo, solicitudes DMA, solicitudes MSI) y la información relacionada con las solicitudes a la función de adaptador (por ejemplo, instrucciones PCI). Cada entrada de la tabla de dispositivos está asociada con un espacio de direcciones dentro de la memoria del sistema asignada a la función de adaptador.

Indicador 312 de ocupado: Este campo indica si la función de adaptador está ocupada;

Indicador 314 de estado de error permanente: Este campo indica si la función de adaptador está en un estado de error permanente;

Indicador 316 de recuperación iniciada: Este campo indica si se ha iniciado una recuperación para la función de adaptador;

Indicador 318 de permiso: Este campo indica si el sistema operativo que está tratando de habilitar la función de adaptador tiene autorización para hacerlo;

Indicador 320 de habilitación: Este campo indica si la función de adaptador está habilitada (por ejemplo, 1 = habilitada, 0 = deshabilitada);

Identificador (RID) 322 de solicitante: Este es un identificador de la función de adaptador y puede incluir, por ejemplo, un número de bus, un número de dispositivo y un número de función. Este campo se usa, por ejemplo, para los accesos de un espacio de configuración de la función de adaptador.

Por ejemplo, el espacio de configuración puede ser accedido especificando el espacio de configuración en una instrucción emitida por el sistema operativo (u otra configuración) para la función de adaptador. En la instrucción se especifican un desplazamiento en el espacio de configuración y un descriptor de función usado para localizar la entrada de la tabla de funciones apropiada que incluye el RID. El firmware recibe la instrucción y determina que es para un espacio de configuración. Por lo tanto, usa el RID para generar una solicitud al concentrador de E/S, y el concentrador de E/S crea una solicitud para acceder al adaptador. La localización de la función de adaptador se basa en el RID, y el desplazamiento especifica un desplazamiento en el espacio de configuración de la función de adaptador. Por ejemplo, el desplazamiento especifica un número de registro en el espacio de configuración.

Registro 324 de dirección base (Base Address Register, BAR) (1 a n): Este campo incluye una pluralidad de enteros sin signo, designados como BARO - BARN, que están asociados con la función de adaptador especificada

originalmente, y cuyos valores se almacenan también en los registros de dirección base asociados con la función de adaptador. Cada BAR especifica la dirección de inicio de un espacio de memoria o espacio de E/S dentro de la función de adaptador, e indica también el tipo de espacio de direcciones, es decir, si se trata de un espacio de memoria de 64 o 32 bits, o un espacio de E/S de 32 bits, por ejemplo;

En un ejemplo, se usa para accesos a un espacio de memoria y/o un espacio de E/S de la función de adaptador. Por ejemplo, un desplazamiento proporcionado en una instrucción para acceder a la función de adaptador es sumado al valor en el registro de dirección base asociado con el espacio de direcciones designado en la instrucción para obtener la dirección a ser usada para acceder a la función de adaptador. El identificador de espacio de direcciones en la instrucción identifica el espacio de direcciones dentro de la función de adaptador a ser accedida y el BAR correspondiente a ser usado;

Tamaño 326 (1 .... n): Este campo incluye una pluralidad de enteros sin signo, designados como SIZE0 - SIZEn. El valor de un campo Tamaño, cuando es diferente de cero, representa el tamaño de cada espacio de direcciones en el que cada entrada corresponde a un BAR descrito anteriormente.

A continuación, se describen detalles adicionales acerca de BAR y Tamaño.

- 1. Cuando un BAR no está implementado para una función de adaptador, el campo BAR y su campo de tamaño correspondiente se almacenan ambos como ceros.

- 2. Cuando un campo BAR representa un espacio de direcciones de E/S o un espacio de direcciones de memoria de 32 bits, el campo de tamaño correspondiente es diferente de cero y representa el tamaño del espacio de direcciones.

- 3. Cuando un campo BAR representa un espacio de direcciones de memoria de 64 bits,

- a. El campo BARn representa los bits menos significativos de la dirección.

- b. El próximo campo BARn + 1 consecutivo representa los bits más significativos de la dirección.

- c. El campo SIZEn correspondiente es diferente de cero y representa el tamaño del espacio de direcciones.

- d. El correspondiente campo SIZEn + 1 no es significativo y se almacena como cero.

Información 328 de enrutamiento interno: Esta información se usa para realizar un enrutamiento particular al adaptador. Incluye, por ejemplo, información de nodo, de chip procesador y de direccionamiento de concentrador de E/S, como ejemplos.

Indicador 330 de estado: Proporciona una indicación de si las operaciones de carga/almacenamiento están bloqueadas o no, así como otras indicaciones.

En un ejemplo, el indicador de ocupado, el indicador de estado de error permanente y el indicador de recuperación iniciada se establecen en base a una supervisión llevada a cabo por el firmware. Además, el indicador de permiso se establece, por ejemplo, en base a una política. La información de BAR se basa en información de configuración descubierta durante el uso del bus por el procesador (por ejemplo, el firmware del procesador). Otros campos pueden ser establecidos en base a la configuración, la inicialización y/o los eventos. En otras realizaciones, la entrada de la tabla de funciones puede incluir más, menos información o información diferente. La información incluida puede depender de las operaciones soportadas por o habilitadas para la función de adaptador.

Para localizar una entrada de la tabla de funciones en una tabla de funciones que incluye una o más entradas, en una realización se usa un descriptor de función. Por ejemplo, uno o más bits del descriptor de función son usados como un índice para la tabla de funciones para localizar una entrada particular en la tabla de funciones.

Con referencia a la Fig. 3B, en la misma se describen detalles adicionales con respecto a un descriptor de función. En un ejemplo, un descriptor 350 de funciones incluye un indicador 352 de habilitación que indica si el descriptor de función PCI está habilitado; un número 354 de función PCI que identifica la función (este es un identificador estático y, en una realización, es un índice en la tabla de funciones); y un número 356 de instancia que indica la instancia particular de este descriptor de función. Por ejemplo, cada vez que se habilita la función, se incrementa el número de instancia para proporcionar un nuevo número de instancia.

Según un aspecto de la presente invención, para acceder a una función de adaptador, una configuración emite una solicitud a la función de adaptador, que es ejecutada por un procesador. En los ejemplos de la presente memoria, la configuración es un sistema operativo pero, en otros ejemplos, puede ser un sistema, un procesador, una

8

25

30

15

20

35

40

partición lógica, un huésped, etc. Estas solicitudes se realizan a través de instrucciones específicas, que acceden al adaptador. Las instrucciones ejemplares incluyen instrucciones de carga PCI, de almacenamiento PCI y de almacenamiento de bloque PCI. Estas instrucciones son específicas de la arquitectura del adaptador (por ejemplo, PCI). A continuación, se describen detalles adicionales acerca de estas instrucciones. Por ejemplo, una realización de una instrucción de carga PCI se describe con referencia a las Figs. 4A-5B; una realización de una instrucción de almacenamiento PCI se describe con referencia a las Figs. 6A-7B; y una realización de una instrucción de almacenamiento de bloque PCI se describe con referencia a las Figs. 8A-9B.

5

10

25

Con referencia inicialmente a la Fig. 4A, en la misma se representa una realización de una instrucción de carga PCI. Tal como se muestra, una instrucción 400 de carga PCI incluye, por ejemplo, un código 402 de operación que indica la instrucción de carga PCI; un primer campo 404 que especifica una ubicación en la que será cargados los datos recuperados desde una función de adaptador; y un segundo campo 406 que especifica una ubicación en la que se incluye diversa información acerca de la función de adaptador desde la que deben cargarse los datos. A continuación, se describen adicionalmente los contenidos de las ubicaciones designadas por los campos 1 y 2.

En un ejemplo, el Campo 1 designa un registro general y, tal como se representa en la Fig. 4B, los contenidos de ese registro 404 incluyen un rango contiguo de uno o más bytes cargados desde la ubicación de la función de adaptador especificada en la instrucción. En un ejemplo, los datos se cargan en las posiciones de byte situadas más la derecha del registro.

En una realización, el Campo 2 designa un par de registros generales que incluyen diversa información. Tal como se muestra en la Fig. 4B, los contenidos de los registros incluyen, por ejemplo:

20 Descriptor 410 habilitado: Este campo es un descriptor de función habilitada de la función de adaptador desde la cual deben cargarse los datos;

Espacio 412 de direcciones: Este campo identifica el espacio de direcciones dentro de la función de adaptador desde el cual deben cargarse los datos;

Desplazamiento 414 dentro del espacio de direcciones: Este campo especifica el desplazamiento dentro del espacio de direcciones especificado desde el cual deben cargarse los datos;

Campo 416 de longitud: Este campo especifica la longitud de la operación de carga (por ejemplo, el número de bytes a cargar); y

Campo 418 de estado: Este campo proporciona un código de estado que es aplicable cuando la instrucción se completa con un código de condición predefinido.

- En una realización, los bytes cargados desde la función de adaptador deberán ser contenidos dentro de un límite integral en el espacio de direcciones PCI designado de la función de adaptador. Cuando el campo de espacio de direcciones designa un espacio de direcciones de memoria, el tamaño del límite integral es, por ejemplo, una palabra doble. Cuando el campo de espacio de direcciones designa un espacio de direcciones de E/S o un espacio de direcciones de configuración, el tamaño del límite integral es, por ejemplo, una palabra.

- Una realización de la lógica asociada con una instrucción de carga PCI se describe con referencia a las Figs. 5A-5B. En un ejemplo, la instrucción es emitida por un sistema operativo (u otra configuración) y ejecutada por el procesador (por ejemplo, firmware) que ejecuta el sistema operativo. En los ejemplos en la presente memoria, las instrucciones y funciones de adaptador están basadas en PCI. Sin embargo, en otros ejemplos, pueden usarse una arquitectura de adaptador diferente e instrucciones correspondientes.

- Para emitir la instrucción, el sistema operativo proporciona los siguientes operandos a la instrucción (por ejemplo, en uno o más registros designados por la instrucción): el descriptor de función PCI, el espacio de direcciones PCI (PCIAS), el desplazamiento en el espacio de direcciones PCI y la longitud de los datos a cargar. Tras completar con éxito la instrucción de carga PCI, los datos se cargan en la ubicación (por ejemplo, registro) designada por la instrucción.

- Con referencia a la Fig. 5A, inicialmente, se realiza una determinación de si está instalada o no la función que permite una instrucción de carga PCI, PREGUNTA 500. Esta determinación se realiza, por ejemplo, comprobando un indicador almacenado, por ejemplo, en un bloque de control. Si la función no está instalada, se proporciona una condición de excepción, ETAPA 502. De lo contrario, se realiza una determinación de si los operandos están alineados, PREGUNTA 504. Por ejemplo, si ciertos operandos necesitan estar en pares de registro pares/impares, se realiza una determinación de si se cumplen o no los requisitos. Si los operandos no están alineados, entonces se proporciona una excepción, ETAPA 506. De lo contrario, si la función está instalada y los operandos están alineados, se realiza una determinación de si el descriptor proporcionado en los operandos de la instrucción de

carga PCI está habilitado o no, PREGUNTA 508. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en el descriptor. Si el descriptor no está habilitado, entonces se proporciona una condición de excepción, ETAPA 510.

Si el descriptor está habilitado, el descriptor es usado para localizar una entrada en la tabla de funciones, ETAPA 512. Es decir, al menos una parte del descriptor es usada como un índice a la tabla de funciones para localizar la entrada en la tabla de funciones correspondiente a la función de adaptador desde la que se cargan los datos.

5

10

15

30

35

40

45

50

55

A continuación, si la configuración que emite la instrucción es un huésped, se realiza una determinación de si la función está configurada para su uso por un huésped, PREGUNTA 514. Si no está autorizada, entonces se proporciona una condición de excepción, ETAPA 516. Esta pregunta puede ser ignorada si la configuración no es un huésped o pueden comprobarse otras autorizaciones, si han sido designadas. (En un ejemplo, en la arquitectura z/Architecture®, se ejecuta interpretativamente un huésped paginable a través de la instrucción inicio de ejecución interpretativa (Start Interpretive Execution, SIE), en el nivel 2 de interpretación. Por ejemplo, el hipervisor de partición lógica (Logical Partition, LPAR) ejecuta la instrucción SIE para iniciar la partición lógica en una memoria física fija. Si z/VM® es el sistema operativo en esa partición lógica, emite la instrucción SIE para ejecutar sus máquinas huéspedes (virtuales) en su almacenamiento V = V (virtual). Por lo tanto, el hipervisor LPAR usa SIE nivel-1, y el hipervisor z/VM® usa SIE nivel-2).

A continuación, se realiza una determinación de si la función está habilitada, PREGUNTA 518. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en la entrada de la tabla de funciones. Si no está habilitado, entonces se proporciona una condición de excepción, ETAPA 520.

Si la función está habilitada, entonces se realiza una determinación de si el espacio de direcciones es válido o no, PREGUNTA 522. Por ejemplo, si el espacio de direcciones especificado es un espacio de direcciones designado de la función de adaptador y uno que sea apropiado para esta instrucción. Si el espacio de direcciones no es válido, entonces se proporciona una condición de excepción, ETAPA 524. De lo contrario, se realiza una determinación de si la carga/almacenamiento está bloqueada, PREGUNTA 526. En un ejemplo, esta determinación se realiza comprobando el indicador de estado en la entrada de la tabla de funciones. Si la carga/almacenamiento está bloqueada, entonces se proporciona una condición de excepción, ETAPA 528.

Sin embargo, si la carga/almacenamiento no está bloqueada, se realiza una determinación de si la recuperación está activa, PREGUNTA 530. En un ejemplo, esta determinación se realiza comprobando el indicador de recuperación iniciada en la entrada de la tabla de funciones. Si la recuperación está activa, entonces se proporciona una condición de excepción, ETAPA 532. De lo contrario, se realiza una determinación de si la función está ocupada, PREGUNTA 534. Esta determinación se realiza comprobando el indicador de ocupado en la entrada de la tabla de funciones. Si la función está ocupada, entonces se proporciona una condición de ocupado, ETAPA 536. Con una condición de ocupado, la instrucción puede intentarse de nuevo, en lugar de ser ignorada.

Si la función no está ocupada, entonces se realiza una determinación adicional de si el desplazamiento especificado en la instrucción es válido, PREGUNTA 538. Es decir, está el desplazamiento en combinación con la longitud de la operación dentro de la base y la longitud del espacio de direcciones, tal como se especifica en la entrada de la tabla de funciones. Si no, entonces se proporciona una condición de excepción, ETAPA 540. Sin embargo, si el desplazamiento es válido, entonces se realiza una determinación de si la longitud es válida, PREGUNTA 542. Es decir, en función del tipo de espacio de direcciones, el desplazamiento dentro del espacio de direcciones y un tamaño de límite integral, si la longitud es válida. Si no, entonces se proporciona una condición de excepción, ETAPA 544. De lo contrario, el procesamiento continúa con la instrucción de carga. (En una realización, el firmware realiza las comprobaciones anteriores).

Continuando con la Fig. 5B, el firmware realiza una determinación de si la carga es para un espacio de direcciones de configuración de la función de adaptador, PREGUNTA 550. Es decir, en base a la configuración de la memoria de la función de adaptador, es el espacio de direcciones especificado proporcionado en la instrucción de un espacio de configuración. Si es así, entonces el firmware realiza diversos procesamientos para proporcionar la solicitud a un concentrador acoplado a la función de adaptador; a continuación, el concentrador enruta la solicitud a la función, ETAPA 552.

Por ejemplo, el firmware obtiene el ID del solicitante a partir de la entrada de la tabla de funciones a la que apunta el descriptor de función proporcionado en los operandos de la instrucción. Además, el firmware determina, en base a la información en la entrada de la tabla de funciones (por ejemplo, la información de enrutamiento interno) del concentrador para recibir esta solicitud. Es decir, un entorno puede tener uno o más concentradores y el firmware determina el concentrador acoplado a la función de adaptador. A continuación, reenvía la solicitud al concentrador. El concentrador genera un paquete de solicitud de lectura de configuración que fluye en el bus PCI a la función de adaptador identificada por el RID, en la entrada de la tabla de funciones. La solicitud de lectura de configuración

incluye el RID y el desplazamiento (es decir, la dirección de datos) que se usan para recuperar los datos, tal como se describe a continuación.

Volviendo a la PREGUNTA 550, si el espacio de direcciones designado no es un espacio de configuración, entonces, una vez más, el firmware realiza diversos procesamientos para proporcionar la solicitud al concentrador, ETAPA 554. El firmware usa el descriptor para seleccionar una entrada de la tabla de funciones y, a partir de esa entrada, obtiene información para localizar el concentrador apropiado. También calcula una dirección de datos a ser usada en la operación de carga. Esta dirección se calcula sumando la dirección de inicio BAR (en el que el BAR es aquel asociado con el identificador de espacio de direcciones proporcionado en la instrucción) obtenida desde la entrada de la tabla de funciones al desplazamiento proporcionado en la instrucción. Esta dirección de datos calculada es proporcionada al concentrador. A continuación, el concentrador toma esa dirección y la incluye en un paquete de solicitud, tal como un paquete de solicitud de lectura DMA, que fluye a través del bus PCI a la función de adaptador.

5

10

15

50

En respuesta a la recepción de la solicitud a través de la ETAPA 552 o la ETAPA 554, la función de adaptador recupera los datos solicitados desde la ubicación especificada (es decir, en la dirección de datos) y devuelve esos datos en respuesta a la solicitud, ETAPA 556. La respuesta es reenviada desde la función de adaptador al concentrador de E/S. En respuesta a la recepción de la respuesta, el concentrador reenvía la respuesta al procesador iniciador. A continuación, el procesador iniciador toma los datos desde el paquete de respuesta y los carga en la ubicación designada especificada en la instrucción (por ejemplo, el campo 1 404). La operación de carga PCI concluye con una indicación de éxito (por ejemplo, estableciendo un código de condición de cero).

Además de una instrucción de carga que recupera datos desde una función de adaptador y los almacena en una ubicación designada, otra instrucción que puede ser ejecutada es una instrucción de almacenamiento. La instrucción de almacenamiento almacena datos en una ubicación especificada en la función de adaptador. Una realización de una instrucción de almacenamiento PCI se describe con referencia a la Fig. 6A. Tal como se muestra, una instrucción 600 de almacenamiento PCI incluye, por ejemplo, un código 602 de operación que indica la instrucción de almacenamiento PCI; un primer campo 604 que especifica una ubicación que incluye los datos a ser almacenados en una función de adaptador; y un segundo campo 606 que especifica una ubicación en la que se incluye diversa información relativa a la función de adaptador en la que deben almacenarse los datos. Los contenidos de las ubicaciones designadas por los Campos 1 y 2 se describen adicionalmente a continuación.

En un ejemplo, el Campo 1 designa un registro general y, tal como se representa en la Fig. 6B, los contenidos 604 de ese registro incluyen un rango contiguo de uno o más bytes de datos a ser almacenados en la ubicación especificada de una función de adaptador. En un ejemplo, se almacenan los datos en las posiciones de byte más a la derecha del registro.

En una realización, el Campo 2 designa un par de registros generales que incluyen diversa información. Tal como se muestra en la Fig. 6B, los contenidos del registro incluyen, por ejemplo:

Descriptor 610 activado: Este campo es un descriptor de función habilitado de la función de adaptador en el cual deben almacenarse los datos;

Espacio 612 de direcciones: Este campo identifica el espacio de direcciones dentro de la función de adaptador en el cual deben almacenarse los datos;

Desplazamiento 614 dentro del espacio de direcciones: Este campo especifica el desplazamiento dentro del espacio de direcciones especificado en el cual deben almacenarse los datos;

Campo 616 de longitud: Este campo especifica la longitud de la operación de almacenamiento (por ejemplo, el número de bytes a almacenar); y

Campo 618 de estado: Este campo proporciona un código de estado que es aplicable cuando la instrucción se completa con un código de condición predefinido.

Una realización de la lógica asociada con una instrucción de almacenamiento PCI se describe con referencia a las Figs. 7A-7B. En un ejemplo, la instrucción es emitida por un sistema operativo, y es ejecutada por el procesador (por ejemplo, firmware) que ejecuta el sistema operativo.

Para emitir la instrucción, el sistema operativo proporciona los siguientes operandos a la instrucción (por ejemplo, en uno o varios registros designados por la instrucción): el descriptor de función PCI, el espacio de direcciones PCI (PCIAS), el desplazamiento en el espacio de direcciones PCI, la longitud de los datos a almacenar y un puntero a los datos a almacenar. Tras completar con éxito la instrucción de almacenamiento PCI, los datos se almacenan en la ubicación designada por la instrucción.

Con referencia a la Fig. 7A, inicialmente, se realiza una determinación de si está instalada la función que permite una instrucción de almacenamiento PCI, PREGUNTA 700. Esta determinación se realiza, por ejemplo, comprobando un indicador almacenado, por ejemplo, en un bloque de control. Si la función no está instalada, se proporciona una condición de excepción, ETAPA 702. De lo contrario, se realiza una determinación de si los operandos están alineados, PREGUNTA 704. Por ejemplo, si ciertos operandos tienen que estar en pares de registros pares/impares, se realiza una determinación de si se cumplen o no esos requisitos. Si los operandos no están alineados, entonces se proporciona una excepción, ETAPA 706. De lo contrario, si la función está instalada y los operandos están alineados, se realiza una determinación de si el descriptor proporcionado en los operandos de la instrucción de almacenamiento PCI está habilitado o no, PREGUNTA 708. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en el descriptor. Si el descriptor no está habilitado, entonces se proporciona una condición de excepción, ETAPA 710.

5

10

15

25

40

45

50

55

Si el descriptor está habilitado, entonces el descriptor es usado para localizar una entrada de la tabla de funciones, ETAPA 712. Es decir, al menos una parte del descriptor es usada como un índice en la tabla de funciones para localizar la entrada de la tabla de funciones correspondiente a la función de adaptador en la que deben almacenarse los datos.

A continuación, si la configuración que emite la instrucción es un huésped, se realiza una determinación de si la función está configurada para su uso por un huésped, PREGUNTA 714. Si no está autorizada, entonces se proporciona una condición de excepción, ETAPA 716. Esta pregunta puede ser ignorada si la configuración no es un huésped o pueden comprobarse otras autorizaciones, si han sido designadas.

A continuación, se realiza una determinación de si la función está habilitada, PREGUNTA 718. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en la entrada de la tabla de funciones. Si no está habilitada, entonces se proporciona una condición de excepción, ETAPA 720.

Si la función está habilitada, entonces se realiza una determinación de si el espacio de direcciones es válido, PREGUNTA 722. Por ejemplo, si el espacio de direcciones especificado es un espacio de direcciones designado de la función de adaptador y uno que es apropiado para esta instrucción. Si el espacio de direcciones no es válido, se proporciona una condición de excepción, ETAPA 724. De lo contrario, se realiza una determinación de si la carga/almacenamiento está bloqueada, PREGUNTA 726. En un ejemplo, esta determinación se realiza comprobando el indicador de estado en la entrada de la tabla de funciones. Si la carga/almacenamiento está bloqueada, entonces se proporciona una condición de excepción, ETAPA 728.

Sin embargo, si la carga/almacenamiento no está bloqueada, se realiza una determinación de si la recuperación está activa, PREGUNTA 730. En un ejemplo, esta determinación se realiza comprobando el indicador de recuperación iniciada en la entrada de la tabla de funciones. Si la recuperación está activa, entonces se proporciona una condición de excepción, ETAPA 732. De lo contrario, se realiza una determinación de si la función está ocupada, PREGUNTA 734. Esta determinación se realiza comprobando el indicador de ocupado en la entrada de la tabla de funciones. Si la función está ocupada, entonces se proporciona una condición de ocupado, ETAPA 736. Con una condición de ocupado, la instrucción puede ser intentada de nuevo, en lugar de ser ignorada.

Si la función no está ocupada, entonces se realiza una determinación adicional de si el desplazamiento especificado en la instrucción es válido o no, PREGUNTA 738. Es decir, está el desplazamiento en combinación con la longitud de la operación dentro de la base y la longitud del espacio de direcciones, tal como se especifica en la entrada de la tabla de funciones. Si no, entonces se proporciona una condición de excepción, ETAPA 740. Sin embargo, si el desplazamiento es válido, entonces se realiza una determinación de si la longitud es válida, PREGUNTA 742. Es decir, en función del tipo de espacio de direcciones, el desplazamiento dentro del espacio de direcciones, y un tamaño de límite integral es la longitud válida. Si no, entonces se proporciona una condición de excepción, ETAPA 744. De lo contrario, el procesamiento continúa con la instrucción de almacenamiento. (En una realización, el firmware realiza las comprobaciones anteriores).

Continuando con la Fig. 7B, el firmware realiza una determinación de si el almacenamiento es para un espacio de direcciones de configuración de la función de adaptador, PREGUNTA 750. Es decir, en base a la configuración de la memoria de la función de adaptador, es el espacio de direcciones especificado en la instrucción de un espacio de configuración. Si es así, entonces el firmware realiza diversos procesamientos para proporcionar la solicitud a un concentrador acoplado a la función de adaptador; a continuación, el concentrador enruta la solicitud a la función, ETAPA 752.

Por ejemplo, el firmware obtiene el ID de solicitante a partir de la entrada de la tabla de funciones a la que apunta el descriptor de función proporcionado en los operandos de la instrucción. Además, el firmware determina, en base a la información en la entrada de la tabla de funciones (por ejemplo, la información de enrutamiento interno) el concentrador para recibir esta solicitud. Es decir, un entorno puede tener uno o más concentradores y el firmware

determina el concentrador acoplado a la función de adaptador. A continuación, reenvía la solicitud al concentrador. El concentrador genera un paquete de solicitud de escritura de configuración que fluye en el bus PCI a la función de adaptador identificada por el RID en la entrada de la tabla de funciones. La solicitud de escritura de configuración incluye el RID y el desplazamiento (es decir, dirección de datos) que se usan para almacenar los datos, tal como se describe a continuación.

5

10

Volviendo a la PREGUNTA 750, si el espacio de direcciones designado no es un espacio de configuración, entonces, una vez más, el firmware realiza diversos procesamientos para proporcionar la solicitud al concentrador, ETAPA 754. El firmware usa el descriptor para seleccionar una entrada de la tabla de funciones y a partir de esa entrada obtiene información para localizar el concentrador correspondiente. También calcula una dirección de datos a ser usada en la operación de almacenamiento. Esta dirección se calcula sumando la dirección de inicio BAR obtenida a partir de la entrada de la tabla de funciones al desplazamiento proporcionado en la instrucción. Esta dirección de datos calculada es proporcionada al concentrador. A continuación, el concentrador toma esa dirección y la incluye en un paquete de solicitud, tal como un paquete de solicitud de escritura DMA, que fluye a través del bus PCI a la función de adaptador.

- En respuesta a la recepción de la solicitud, a través de la ETAPA 752 o la ETAPA 754, la función de adaptador almacena los datos solicitados en la ubicación especificada (es decir, en la dirección de los datos), ETAPA 756. La operación de almacenamiento PCI concluye con una indicación de éxito (por ejemplo, estableciendo un código de condición de cero).

- Además de las instrucciones de carga y almacenamiento, que típicamente cargan o almacenan un máximo de, por ejemplo, 8 bytes, otra instrucción que puede ser ejecutada es una instrucción de almacenamiento de bloque. La instrucción de almacenamiento de bloque almacena grandes bloques de datos (por ejemplo, 16, 32, 64, 128 o 256 bytes) en una ubicación especificada en la función de adaptador; los tamaños de bloque no están limitados necesariamente a tamaños que son potencias de dos. En un ejemplo, la ubicación especificada está en un espacio de memoria de la función de adaptador (no un espacio de E/S o de configuración).

- Una realización de una instrucción de almacenamiento de bloque PCI se describe con referencia a la Fig. 8A. Tal como se muestra, una instrucción 800 de almacenamiento de bloque PCI incluye, por ejemplo, un código 802 de operación que indica la instrucción de almacenamiento de bloque PCI; un primer campo 804 que especifica una ubicación en la que se incluye diversa información acerca de la función de adaptador en la que deben almacenarse los datos; un segundo campo 806 que especifica una ubicación que incluye un desplazamiento dentro del espacio de direcciones especificado en el que deben almacenarse los datos; y un tercer campo 808 que especifica una ubicación que incluye una dirección en la memoria del sistema de los datos a ser almacenados en la función de adaptador. Los contenidos de las ubicaciones designadas por los Campos 1, 2 y 3 se describen adicionalmente a continuación.

- En una realización, el Campo 1 designa un registro general que incluye diversa información. Tal como se muestra en la Fig. 8B, los contenidos del registro incluyen, por ejemplo:

- Descriptor 810 habilitado: Este campo es un descriptor de función habilitado de la función de adaptador en la cual deben almacenarse los datos;

- Espacio 812 de direcciones: Este campo identifica el espacio de direcciones dentro de la función de adaptador en el cual deben almacenarse los datos;

- Campo 814 de longitud: Este campo especifica la longitud de la operación de almacenamiento (por ejemplo, el número de bytes a almacenar); y

- Campo 816 de estado: Este campo proporciona un código de estado que es aplicable cuando la instrucción se completa con un código de condición predefinido.

- En un ejemplo, el Campo 2 designa un registro general y, tal como se representa en la Fig. 8C, los contenidos del registro incluyen un valor (por ejemplo, un entero de 64 bits sin signo) que especifica el desplazamiento dentro del espacio de direcciones especificado en el cual deben almacenarse los datos.

- En un ejemplo, el Campo 3, tal como se representa en la Fig. 8D, incluye la dirección lógica en la memoria del sistema del primer byte de datos 822 a ser almacenado en la función de adaptador.

- Una realización de la lógica asociada con una instrucción de almacenamiento de bloque PCI se describe con referencia a las Figs. 9A-9B. En un ejemplo, la instrucción es emitida por un sistema operativo, y es ejecutada por el procesador (por ejemplo, firmware) que ejecuta el sistema operativo.

Para emitir la instrucción, el sistema operativo proporciona los siguientes operandos a la instrucción (por ejemplo, en uno o más registros designados por la instrucción): el descriptor de función PCI, el espacio de direcciones PCI (PCIAS), el desplazamiento en el espacio de direcciones PCI, la longitud de los datos a almacenar y un puntero a los datos a almacenar. El operando puntero puede comprender un registro y un desplazamiento con o sin signo. Tras completar con éxito la instrucción de almacenamiento de bloque PCI, los datos se almacenan en la ubicación en el adaptador designado por la instrucción.

5

10

20

35

40

45

50

Con referencia a la Fig. 9A, inicialmente, se realiza una determinación de si la función que permite una instrucción de almacenamiento de bloque PCI está instalada o no, PREGUNTA 900. Esta determinación se realiza, por ejemplo, comprobando un indicador almacenado, por ejemplo, en un bloque de control. Si la función no está instalada, se proporciona una condición de excepción, ETAPA 902. De lo contrario, si la función está instalada, se realiza una determinación de si el descriptor proporcionado en los operandos de la instrucción de almacenamiento de bloque PCI está habilitado, PREGUNTA 904. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en el descriptor. Si el descriptor no está habilitado, entonces se proporciona una condición de excepción, ETAPA 906.

Si el descriptor está habilitado, el descriptor es usado para localizar una entrada de la tabla de funciones, ETAPA 912. Es decir, al menos una parte del descriptor es usada como un índice en la tabla de funciones para localizar la entrada de la tabla de funciones correspondiente a la función de adaptador en que deben almacenarse los datos.

A continuación, si la configuración que emite la instrucción es un huésped, se realiza una determinación de si la función está configurada para su uso por un huésped, PREGUNTA 914. Si no está autorizada, entonces se proporciona una condición de excepción, ETAPA 916. Esta pregunta puede ser ignorada si la configuración no es un huésped o pueden comprobarse otras autorizaciones, si han sido designadas.

A continuación, se realiza una determinación de si la función está habilitada, PREGUNTA 918. En un ejemplo, esta determinación se realiza comprobando un indicador de habilitación en la entrada de la tabla de funciones. Si no está habilitada, entonces se proporciona una condición de excepción, ETAPA 920.

Si la función está activada, entonces se realiza una determinación de si el espacio de direcciones es válido, PREGUNTA 922. Por ejemplo, si el espacio de direcciones especificado es un espacio de direcciones designado de la función de adaptador y uno que sea apropiado para esta instrucción (es decir, un espacio de memoria). Si el espacio de direcciones no es válido, se proporciona una condición de excepción, ETAPA 924. De lo contrario, se realiza una determinación de si la carga/almacenamiento está bloqueada, PREGUNTA 926. En un ejemplo, esta determinación se realiza comprobando el indicador de estado en la entrada de la tabla de funciones. Si la carga/almacenamiento está bloqueada, entonces se proporciona una condición de excepción, ETAPA 928.

Sin embargo, si la carga/almacenamiento no está bloqueada, se realiza una determinación de si la recuperación está activada, PREGUNTA 930. En un ejemplo, esta determinación se realiza comprobando el indicador de recuperación iniciada en la entrada de la tabla de funciones. Si la recuperación está activa, entonces se proporciona una condición de excepción, ETAPA 932. De lo contrario, se realiza una determinación de si la función está ocupada, PREGUNTA 934. Esta determinación se realiza comprobando el indicador de ocupado en la entrada de la tabla de funciones. Si la función está ocupada, entonces se proporciona una condición de ocupado, ETAPA 936. Con una condición de ocupado, la instrucción puede ser intentada de nuevo, en lugar de ser ignorada.

Si la función no está ocupada, entonces se realiza una determinación adicional de si el desplazamiento especificado en la instrucción es válido, PREGUNTA 938. Es decir, está el desplazamiento en combinación con la longitud de la operación dentro de la base y la longitud del espacio de direcciones, tal como se especifica en la entrada de la tabla de funciones. Si no, entonces se proporciona una condición de excepción, ETAPA 940. Sin embargo, si el desplazamiento es válido, entonces se realiza una determinación de si la longitud es válida, PREGUNTA 942. Es decir, en función del tipo de espacio de direcciones, desplazamiento dentro del espacio de direcciones, y un tamaño límite integral es la longitud válida. Si no, entonces se proporciona una condición de excepción, ETAPA 944. De lo contrario, el procesamiento continúa con la instrucción de almacenamiento de bloque (en una realización, el firmware realiza las comprobaciones anteriores).

Continuando con la Fig. 9B, el firmware realiza una determinación de si el almacenamiento que incluye los datos a ser almacenados es accesible, PREGUNTA 950. Si no, se proporciona una condición de excepción, ETAPA 952. Si es así, entonces el firmware realiza diversos procesamientos para proporcionar la solicitud a un concentrador acoplado a la función de adaptador; a continuación, el concentrador enruta la solicitud a la función, ETAPA 954.

Por ejemplo, el firmware usa el descriptor para seleccionar una entrada de la tabla de funciones y desde esa entrada obtiene información para localizar el concentrador apropiado. También calcula una dirección de datos a ser usada en la operación de almacenamiento de bloque. Esta dirección se calcula sumando la dirección de inicio

BAR (en el que el BAR es identificado por el identificador de espacio de direcciones), obtenida a partir de la entrada de la tabla de funciones, al desplazamiento proporcionado en la instrucción. Esta dirección de datos calculada es proporcionada al concentrador. Además, los datos referenciados por la dirección proporcionada en la instrucción son recuperados de la memoria del sistema y proporcionados al concentrador de E/S. A continuación, el concentrador toma esa dirección y los datos y los incluye en un paquete de solicitud, tal como un paquete de solicitud de escritura DMA, que fluye a través del bus PCI a la función de adaptador.

5

20

25

30

35

40

45

50

55

En respuesta a la recepción de la solicitud, la función de adaptador almacena los datos solicitados en la ubicación especificada (es decir, en la dirección de datos), ETAPA 956. La operación de almacenamiento de bloque PCI concluye con una indicación de éxito (por ejemplo, estableciendo un código de condición de cero).

Se ha descrito detalladamente una capacidad de comunicación con los adaptadores de un entorno informático usando instrucciones de control diseñadas específicamente para dicha comunicación. La comunicación es realizada sin usar E/S mapeadas en memoria y no se limita a los registros de control en la función de adaptador. Las instrucciones aseguran que la configuración que emite la instrucción está autorizada a acceder a la función de adaptador. Además, para la instrucción de almacenamiento de bloque, asegura que la ubicación de almacenamiento principal especificada está dentro de la memoria de la configuración.

En las realizaciones descritas en la presente memoria, los adaptadores son adaptadores PCI. PCI, tal como se usa en la presente memoria, se refiere a cualquier adaptador implementado según una especificación basada en PCI según se define por el grupo de interés especial en interconexión de componentes periféricos (Peripheral Component Interconnect Special Interest Group, PCI-SIG), incluyendo pero sin limitarse a, PCI o PCIe. En un ejemplo particular, interconexión de componentes periféricos express (PCIe) es un estándar de interconexión a nivel de componente que define un protocolo de comunicación bidireccional para las transacciones entre los adaptadores de E/S y los sistemas servidor. Las comunicaciones PCIe se encapsulan en paquetes según el estándar PCIe para su transmisión en un bus PCIe. Las transacciones originadas en los adaptadores de E/S y dirigidas a los sistemas servidor se denominan transacciones salientes "upbound". Las transacciones originadas en los sistemas servidor y dirigidas a los adaptadores de E/S se denominan transacciones entrantes "downbound". La topología PCIe está basada en enlaces unidireccionales punto a punto que están emparejados (por ejemplo, un enlace "upbound", un enlace "downbound") para formar el bus PCIe. El estándar PCIe es mantenido y publicado por el PCI-SIG, tal como se ha indicado anteriormente en la sección de antecedentes.

Tal como apreciará una persona con conocimientos en la materia, los aspectos de la presente invención pueden realizarse como un sistema, procedimiento o producto de programa de ordenador. Por consiguiente, los aspectos de la presente invención pueden adoptar la forma de una realización totalmente en hardware, una realización totalmente en software (incluyendo firmware, software residente, microcódigo, etc.) o una realización que combina aspectos de software y hardware, todos los cuales pueden ser denominados, en general, en la presente memoria, como un "circuito", "módulo" o "sistema". Además, los aspectos de la presente invención pueden adoptar la forma de un producto de programa de ordenador realizado en un medio o medios legibles por uno o más ordenadores, que tienen un código de programa legible materializado en los mismos.

Puede utilizarse cualquier combinación de medio o medios legibles por uno o más ordenadores. El medio legible por ordenador puede ser un medio de almacenamiento legible por ordenador. Un medio de almacenamiento legible por ordenador puede ser, por ejemplo, pero sin limitarse a, un sistema, aparato o dispositivo electrónico, magnético, óptico, electromagnético, infrarrojo o semiconductor, o cualquier combinación adecuada de los anteriores. Los ejemplos más específicos (una lista no exhaustiva) del medio de almacenamiento legible por ordenador incluyen los siguientes: una conexión eléctrica que tiene uno o más cables, un disquete de ordenador portátil, un disco duro, una memoria de acceso aleatorio (RAM), una memoria de sólo lectura (ROM), una memoria de sólo lectura programable y borrable (EPROM o memoria Flash), una fibra óptica, una memoria de sólo lectura de disco compacto portátil (CD-ROM), un dispositivo de almacenamiento óptico, un dispositivo de almacenamiento magnético o cualquier combinación adecuada de los anteriores. En el contexto de la presente memoria, un medio de almacenamiento legible por ordenador puede ser cualquier medio tangible que pueda contener o almacenar un programa para su uso por o en conexión con un sistema, aparato o dispositivo de ejecución de instrucciones.

Con referencia ahora a la Fig. 10, en un ejemplo, un producto 1000 de programa de ordenador incluye, por ejemplo, uno o más medios 1002 de almacenamiento legibles por ordenador para almacenar medios o lógica 1004 de código de programa legible ordenador para proporcionar y facilitar uno o más aspectos de la presente invención.

El código de programa incorporado en un medio legible por ordenador puede ser transmitido usando un medio apropiado, incluyendo pero sin limitarse a tecnología inalámbrica, cable, cable de fibra óptica, RF, etc., o cualquier combinación adecuada de los anteriores.

El código de programa de ordenador para realizar las operaciones para los aspectos de la presente invención puede estar escrito en cualquier combinación de uno o más lenguajes de programación, incluyendo un lenguaje de programación orientado a objetos, tal como Java, Smalltalk, C++ o similares, y lenguajes de programación de procedimientos convencionales, tales como el lenguaje de programación "C", ensamblador o lenguajes de programación similares. El código de programa puede ser ejecutado por completo en el ordenador del usuario, en parte en el equipo del usuario, como un paquete de software independiente, en parte en el ordenador del usuario y en parte en un ordenador remoto o totalmente en el ordenador remoto o servidor. En el último escenario, el ordenador remoto puede estar conectado al ordenador del usuario a través de cualquier tipo de red, incluyendo una red de área local (LAN) o una red de área amplia (WAN), o la conexión puede realizarse a un ordenador externo (por ejemplo, a través de Internet usando un proveedor de servicios de internet).

5

10

15

20

25

30

35

40

55

En la presente memoria, los aspectos de la presente invención se describen con referencia a ilustraciones de diagramas de flujo y/o diagramas de bloques de procedimientos, aparatos (sistemas) y productos de programa de ordenador según las realizaciones de la invención. Se entenderá que cada bloque de las ilustraciones de diagramas de flujo y/o diagramas de bloques, y las combinaciones de bloques en las ilustraciones de diagramas de flujo y/o diagramas de bloques, pueden ser implementados por instrucciones de programa de ordenador. Estas instrucciones de programa de ordenador pueden ser proporcionadas a un procesador de un ordenador de propósito general, un ordenador de propósito especial u otro aparato de procesamiento de datos programable para producir una máquina, de manera que las instrucciones, que son ejecutadas por el procesador del ordenador u otro aparato programable de procesamiento de datos, crean medios para implementar las funciones/acciones especificadas en el diagrama de flujo y/o un bloque o bloques del diagrama de bloques.

Estas instrucciones de programa informático pueden ser almacenadas también en un medio legible por ordenador que puede dirigir un ordenador, otros aparatos programables de procesamiento de datos u otros dispositivos para que funcionen de una manera particular, de manera que las instrucciones almacenadas en el medio legible por ordenador produzcan un artículo de fabricación que incluye instrucciones que implementan la función/acción especificada en el diagrama de flujo y/o bloque o bloques del diagrama de bloques.

Las instrucciones de programa de ordenador pueden ser cargadas también en un ordenador, otro aparato de procesamiento de datos programable u otros dispositivos para causar una serie de etapas operacionales a ser realizadas en el ordenador, otro aparato programable u otros dispositivos para producir un procedimiento implementado por ordenador, de manera que las instrucciones que se ejecutan en el ordenador u otro aparato programable proporcionan procedimientos para implementar las funciones/acciones especificadas en el diagrama de flujo y/o bloque o bloques del diagrama de bloques.

El diagrama de flujo y los diagramas de bloques en las figuras ilustran la arquitectura, la funcionalidad y el funcionamiento de posibles implementaciones de sistemas, procedimientos y productos de programa de ordenador según diversas realizaciones de la presente invención. En este sentido, cada bloque en el diagrama de flujo o en los diagramas de bloques puede representar un módulo, segmento o parte de código, que comprende una o más instrucciones ejecutables para implementar la función lógica o funciones lógicas especificadas. Cabe señalar también que, en algunas implementaciones alternativas, las funciones indicadas en el bloque pueden realizarse en un orden diferente al indicado en las figuras. Por ejemplo, dos bloques mostrados en sucesión pueden ser ejecutados, de hecho, de manera sustancialmente simultánea, o algunas veces, los bloques pueden ser ejecutados en orden inverso, dependiendo de la funcionalidad implicada. Se observará también que cada bloque de los diagramas de bloques y/o la ilustración de diagrama de flujo, y las combinaciones de bloques en los diagramas de bloques y/o la ilustración de diagrama de flujo, puede ser implementado por sistemas basados en hardware, de propósito especial, que realizan las funciones o acciones especificadas, o combinaciones de hardware de propósito especial e instrucciones de ordenador.