# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 525 378

51 Int. Cl.:

**G06F 1/14** (2006.01) **G01R 19/165** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 24.03.2011 E 11714169 (7)

(97) Fecha y número de publicación de la concesión europea: 03.09.2014 EP 2553541

(54) Título: Monitor y alarma de oscilador a prueba de fallos

(30) Prioridad:

26.03.2010 US 732595

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 23.12.2014

(73) Titular/es:

MICROCHIP TECHNOLOGY INCORPORATED (100.0%)

2355 West Chandler Boulevard

Chandler, AZ 85224-6199, US

(72) Inventor/es:

ALEMAN, ENRIQUE; DILLON, JONATHAN; DELPORT, VIVIEN y JULICHER, JOSEPH

(74) Agente/Representante:

**CARPINTERO LÓPEZ, Mario**

## **DESCRIPCIÓN**

Monitor y alarma de oscilador a prueba de fallos

#### Campo técnico

La presente divulgación se refiere al campo de los dispositivos de circuito integrado que utilizan un oscilador de reloj externo y, más concretamente, a la vigilancia del oscilador de reloj externo y al disparo de una alarma y al disparo de una alarma si su operación falla.

#### **Antecedentes**

5

10

15

20

25

30

35

40

45

50

Las aplicaciones electrónicas que incorporan un dispositivo digital con un procesador a menudo utilizan un (unos) elemento(s) de determinación de la frecuencia externa y / o un oscilador externo, por ejemplo un resonador de cuarzo o de material cerámico y / o un circuito electrónico, para establecer una base de tiempo estable para determinar un modo periódico de despertar a partir de una potencia baja, por ejemplo, en espera o dormido. Si este (estos) elemento(s) / oscilador de determinación de la frecuencia externa se detienen por cualquier razón, el procesador del dispositivo digital permanecerá dormido a menos que sea despertado a un modo operacional por otro episodio de disparo. Una posible solución respecto de este problema consiste en habilitar un temporizador controlador de secuencia dispuesto en el dispositivo digital y utilizarlo como un seguro a prueba de fallos si se produce efectivamente un fallo en el oscilador externo. Sin embargo, el uso del temporizador controlador de secuencia en el dispositivo digital puede incrementar excesivamente el consumo de corriente en el modo dormido (en espera) del dispositivo digital y posiblemente de otras aplicaciones del dispositivo estrechamente interrelacionadas. Por tanto, para reducir el consumo de energía del dispositivo digital el temporizador controlador de secuencia es típicamente desactivado. Sin una señal de activación de despertar procedente del temporizador controlador de secuencia hacia el procesador del dispositivo digital, el procesador permanecerá dormido si el oscilador externo falla cuando el procesador está en el modo de potencia baja. Alternativamente (en un modo operacional) el procesador debe permanecer despierto durante el tiempo suficiente para verificar que el (los) elemento(s) / oscilador de determinación de la frecuencia externa esté operando. Este tiempo adicional invertido en el modo operacional incrementará el consumo de energía del dispositivo digital.

La Patente japonesa JP 2003 172762 A divulga un circuito de detección de anomalías en el que una señal de reloj es vigilada para determinar la operación adecuada de un circuito. El circuito de detección divulgado por el documento JP 2003 172762 A utiliza un condensador de carga conectado en paralelo con un resistor, de forma que, cuando no se produce ninguna operación del circuito, el condensador queda completamente descargado a través del resistor. Una anomalía es detectada cuando la tensión a través del condensador de carga cae por debajo del valor de referencia de un comparador conectado en paralelo con el condensador de carga.

#### **Sumario**

El problema referido se resuelve, y se obtienen beneficios adicionales, mediante la utilización de un sencillo circuito de retardo y vigilancia que es cargado con un primer nivel lógico cuando un (os) / oscilador de determinación de la frecuencia externa está funcionando, y se descarga (se desconecta automáticamente) con un segundo nivel lógico si el (los) elemento(s) / oscilador de determinación de la frecuencia externa falla.

De acuerdo con una forma de realización ejemplar específica de la presente divulgación, un dispositivo digital, de acuerdo con la reivindicación 1, que tiene un monitor y alarma de oscilador de reloj primario comprende: un procesador que tiene un modo operacional y un modo dormido de baja potencia; un contador temporizador que tiene una salida acoplada a una entrada del procesador, y una entrada para aceptar una pluralidad de pulsos de reloj; un oscilador de reloj primario acoplado a la entrada del contador temporizador y un elemento de determinación de la frecuencia externa, en el que el oscilador de reloj primario genera la pluralidad de pulsos de reloj a una frecuencia determinada mediante el elemento de determinación de la frecuencia externa; un condensador de bloqueo de corriente continua (cc) acoplado al oscilador de reloj primario; un diodo conectado al condensador de bloqueo de cc; un condensador de almacenamiento de tensión conectado al diodo, en el que el condensador de almacenamiento de tensión es cargado con una tensión a través del diodo y a partir de la pluralidad de pulsos de reloi; un sumidero de corriente conectado al condensador de almacenamiento de tensión, en el que el sumidero de corriente descarga la tensión sobre el condensador de almacenamiento de tensión cuando no está siendo cargado por la pluralidad de pulsos de reloi; y un comparador de tensión que tiene una salida conectada a una entrada del procesador, una primera entrada conectada al condensador de almacenamiento de tensión y una segunda entrada conectada a una tensión de referencia, en el que, cuando la tensión sobre el condensador de almacenamiento de tensión es mayor que la tensión de referencia, la salida del comparador de tensión está en un primer nivel lógico, y cuando la tensión del condensador de almacenamiento de tensión es igual o inferior a la tensión de referencia la salida del comparador de tensión está en un segundo nivel lógico.

De acuerdo con otra forma de realización ejemplar específica de la presente divulgación, un procedimiento, de acuerdo con la reivindicación 10, de vigilancia de un oscilador de reloj primario de un dispositivo digital y de generación de una alarma como consecuencia de su fallo comprende: cargar un condensador de almacenamiento de tensión a una tensión con una pluralidad de pulsos a partir de un oscilador de reloj primario; vigilar la tensión

sobre el condensador de almacenamiento de tensión con un comparador de tensión, en el que, cuando la tensión sobre el condensador de almacenamiento de tensión es mayor que una tensión de referencia no se emite ninguna alarma procedente del comparador de tensión, y cuando la tensión sobre el condensador de almacenamiento de tensión es igual o inferior a la tensión de referencia, se emite la alarma a partir del comparador de tensión; y el cambio con un reloj de salvaguarda después de que se ha emitido la alarma procedente del comparador de tensión. En el que un procesador tiene un modo operacional y un modo dormido de baja potencia, y el procesador despierta del modo dormido de baja potencia al modo operacional cuando la alarma es emitida por el comparador de tensión.

#### Breve descripción de los dibujos

5

10

15

20

25

30

35

40

45

50

55

Una comprensión más acabada de la presente divulgación se puede obtener con referencia a la descripción subsecuente tomada en combinación con los dibujos que se acompañan, en los que:

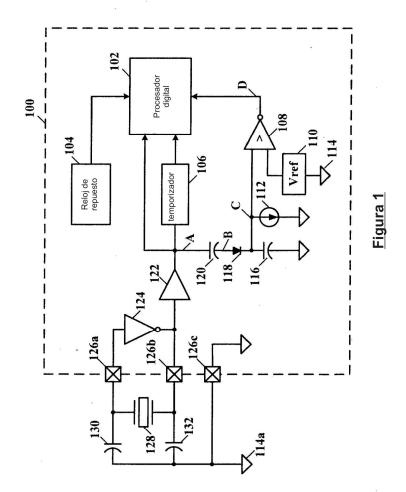

La Figura 1 ilustra un diagrama esquemático de un dispositivo digital que tiene un circuito para vigilar la operación de un (unos) elemento(s) / oscilador de determinación de la frecuencia externa y para señalar un procesador del dispositivo digital si el (los) elemento(s) / oscilador de determinación de la frecuencia externa falla(n), de acuerdo con una forma de realización ejemplar específica de la presente divulgación; y

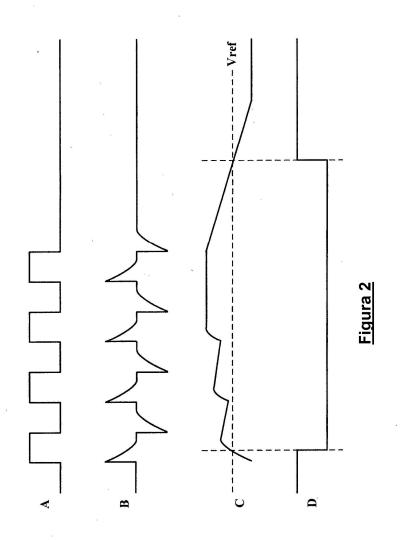

la Figura 2 ilustra unas formas de onda tensión - tiempo esquemáticas de diversos puntos de señal del diagrama esquemático del dispositivo digital mostrado en la Figura 1.

Aunque la presente divulgación es susceptible de diversas modificaciones y formas alternativas, sus formas de realización ejemplares específicas se han mostrado en los dibujos y en la presente memoria se describen con detalle. Se debe entender, sin embargo, que la descripción en la presente memoria de formas de realización ejemplares específicas no está concebida para limitar la divulgación a las formas concretas divulgadas en la presente memoria, definiéndose la presente divulgación por las reivindicaciones adjuntas.

#### Descripción detallada

Con referencia ahora a los dibujos, en ellos se muestra de forma esquemática una forma de realización específica. Los mismos elementos de los dibujos serán representados por los mismos números, y elementos similares serán representados por los mismos números con un sufijo con una letra en caracteres minúsculos diferente.

Con referencia a la Figura 1, en ella se representa un diagrama esquemático de un dispositivo digital que tiene un circuito para vigilar la operación de un (unos) elemento(s) / oscilador de determinación de la frecuencia externa y señalizar un procesador del dispositivo digital si falla(n) el (los) elemento(s) / oscilador de determinación de la frecuencia externa, de acuerdo con una forma de realización ejemplar específica de la presente divulgación. Un dispositivo 100 digital comprende un procesador 102, un reloj 104 de salvaguarda, un contador 106 temporizador, un comparador 108 de tensión, una referencia 110 de tensión, un sumidero 112 de corriente, un condensador 116 de almacenamiento de tensión, un diodo 118, un condensador 120 de bloqueo de corriente continua (cc), un búfer 122 v un inversor 124 oscilador. El inversor 124 oscilador está acoplado a un elemento 128 de determinación de la frecuencia externa, por ejemplo, un resonador de cuarzo, de material cerámico, etc., y unos condensadores 130 y 132 de carga. Uno o ambos condensadores 130 y 132 de carga pueden ser utilizados como componentes de ajuste de retroalimentación y / o de frecuencia para un oscilador de reloj primario formado por el inversor 124 oscilador y el elemento 128 de determinación de la frecuencia. Se prevé y se incluye en el alcance de la presente divulgación que el diodo 128 y / o el condensador 116 de almacenamiento de tensión y el condensador 120 de bloqueo pueden estar dispuestos por dentro o por fuera del dispositivo 100 digital, por ejemplo, no como parte de la matriz del circuito integrado y / o del paquete del circuito integrado (no mostrado) que comprende el dispositivo 100 digital, sino conectado por fuera del mismo.

Normalmente, el oscilador de reloj primario que comprende el inversor 124 oscilador y el elemento 128 de determinación de la frecuencia proporciona un tren de pulsos de señales de reloj, por ejemplo una pluralidad de pulsos de reloj, (diagrama de temporización A de la Figura 2) al procesador 102 y el contador 106 temporizador. El contador 106 temporizador cuenta un número determinado de pulsos a partir del oscilador de reloj primario y despertará el procesador 102 cuando haya sido contado ese número determinado de pulsos. Sin embargo, si cualquier componente del oscilador de reloj primario fallara por cualquier razón, por ejemplo, un fallo de un componente externo (el elemento 128 de determinación de la frecuencia, y / o uno o más de los condensadores 130 y 132 de carga), o fallara la conexión con la matriz o el paquete, entonces el contador 106 temporizador nunca contará hasta el número determinado de pulsos a partir del oscilador de reloj primario para despertar periódicamente al procesador 102.

De acuerdo con las enseñanzas de la presente divulgación, un circuito de retardo y vigilancia es cargado con un primer nivel lógico cuando el oscilador de reloj primario está operativo (funcionando correctamente), y se descarga (se desconecta automáticamente) con un segundo nivel lógico si el oscilador de reloj primario falla. La salida procedente de este circuito de retardo cuando se sitúa en el segundo nivel lógico puede ser utilizada para alertar (interrumpir) el procesador 102 para que se pueda iniciar una rutina de error de fallo de oscilador de reloj primario por parte del oscilador 102. El dispositivo 100 digital puede utilizar el oscilador 104 de reloj de salvaguarda interno si el oscilador de reloj falla. El circuito de retardo y vigilancia asegura que el procesador 102 despierte si está en un

modo dormido y sea alertado para utilizar el reloj 104 de salvaguarda cuando esté en su modo operacional. El oscilador 104 del reloj de salvaguarda puede también ser un reloj interno que el procesador normalmente utilice para su operación, y el oscilador de reloj primario (con el elemento 128 de determinación de la frecuencia de estabilidad elevada) puede ser utilizado como un temporizador de precisión en combinación con el oscilador interno del procesador (por ejemplo, el oscilador 104 de reloj de salvaguarda).

5

10

15

40

45

50

55

60

Con referencia ahora a la Figura 2, en ella se representan unas formas de onda tensión - tiempo esquemáticas de diversos puntos de señal en el esquema del dispositivo digital mostrado en la Figura 1. Una pluralidad de pulsos de reloj (forma de onda A) a partir del oscilador de reloj primario están acoplados a través del condensador 120 de bloqueo al diodo 118. El diodo 118 rectifica (pasa solo por los componentes de tensión - forma de onda B) positivos hasta el condensador 116 de almacenamiento de tensión, cargando de esta manera el condensador 116 de almacenamiento de tensión con una tensión positiva sustancialmente igual al valor de tensión de la pluralidad de pulsos (forma de onda C). El condensador 120 de bloqueo se utiliza también para bloquear la cc si la salida del búfer 122 resultara forzada hasta un estado constante de lógica alta ("1"). El sumidero 112 de corriente arrastra continuamente una corriente constante a partir del condensador 116 de almacenamiento de tensión, pero esta corriente constante es sustancialmente menor que la corriente de carga suministrada a partir del diodo 118 cuando la pluralidad de pulsos a partir del oscilador de reloj primario están operativos. Sin embargo, si el oscilador de reloj primario cesa de funcionar, esto es, no existe una pluralidad de pulsos para cargar el condensador 116 de almacenamiento de tensión, entonces el sumidero 112 de corriente rebajará linealmente la carga de tensión sobre el condensador 116 de almacenamiento de tensión (forma de onda C).

20 El comparador 108 de tensión es utilizado para generar una señal hacia el procesador 102 cuando el oscilador de reloj primario está funcionando y cuando no lo está. La salida del comparador 108 de tensión puede estar conectada al procesador 102 de forma que una entrada para una interrupción o un despertar en las que, cuando la salida del comparador 108 de tensión, está en un primer nivel lógico, por ejemplo una lógica baja ("0"). El procesador 102 funciona de una forma normal (el oscilador de reloi primario está en marcha), y cuando la salida del comparador 108 de tensión está en un segundo nivel lógico, por ejemplo una lógica alta ("1"), el procesador 102 es alertado de que el 25 oscilador de reloj primario ha dejado de funcionar (forma de onda D). Los niveles lógicos de salida a partir del comparador 108 de tensión son determinados comparando la tensión sobre el condensador 116 de almacenamiento de tensión con una tensión de referencia, Vref, a partir de la referencia 110 de tensión. Cuando la carga de tensión sobre el condensador 116 de almacenamiento de tensión es mayor que Vref la salida del comparador 108 de tensión está en el primer nivel lógico y cuando la carga de tensión sobre el condensador 116 de almacenamiento de tensión 30 es igual o menor que Vref la salida del comparador 108 de tensión está en el segundo nivel lógico. Inicialmente, durante la reinicialización del encendido (POR) o durante la reinicialización del apagado (BOR), la salida a partir del comparador 108 de tensión puede ser ignorada hasta que el condensador 116 de almacenamiento de tensión se haya cargado hasta una tensión operativa normal (reloj externo operativo) mediante la recepción de unos pocos pulsos de reloj procedentes del oscilador de reloj primario. La referencia 110 de tensión puede ser un divisor de 35 tensión de red de resistor acoplado entre una tensión de suministro y un suministro común, una referencia de tensión de salto de banda ("bandgap"), etc.

La salida del comparador 108 de tensión en el segundo nivel lógico puede ser utilizada para generar una interrupción que pueda entonces despertar el procesador 102 a partir de un estado (modo) dormido de baja potencia o, como alternativa, interrumpir la operación regular del procesador 102 y establecer una bandera de fallo del oscilador de reloj primario.

El comparador 108 y la referencia de tensión no necesitan ser precisos dado que solo se requiere una desviación grave respecto de la operación normal para cambiar la salida del comparador 108 al segundo nivel lógico. El sumidero 112 de corriente determina el periodo de tiempo de desconexión temporizada en combinación con el valor de capacitancia del condensador 116 de almacenamiento de tensión y la carga de tensión sobre él para un fallo del oscilador externo, y provocará que la carga de tensión sobre el condensador 116 de almacenamiento de tensión se desintegre linealmente. El sumidero 112 de corriente se situará en una corriente inferior que la corriente disponible a partir de la pluralidad de pulsos de reloj del oscilador de reloj primario para que el condensador 116 de almacenamiento de tensión pueda recargarse a partir de esta pluralidad de pulsos de reloj. El tiempo de descarga para la tensión sobre el condensador 116 de almacenamiento de tensión, para que sea igual o inferior a la tensión de referencia, es mayor que un periodo de reloj de la pluralidad de pulsos de reloj. El tiempo de descarga para alcanzar la tensión de referencia después de un fallo del oscilador de reloj primario puede ser de, por ejemplo, pero no limitado. 100 microsegundos.

La señal de reloj externo (pluralidad de pulsos de reloj) no puede ser utilizada directamente para cargar el condensador 116 de almacenamiento de tensión porque si la señal de entrada al diodo 118 está adherida en una lógica alta, por ejemplo de aproximadamente Vdd, el condensador 116 de almacenamiento de tensión podría no ser descargado por el sumidero 112 de corriente. Por tanto, el condensador 120 de bloqueo es utilizado para acoplar en corriente alterna (ac) los pulsos procedentes del oscilador de reloj primario al diodo 118 el cual solo permite que una tensión pase a través del mismo, bloqueando eficazmente cualquier tensión negativa. Como resultado de la utilización del condensador 120 de bloqueo, el condensador 116 de almacenamiento de tensión solo puede ser cargado cuando los pulsos procedentes de reloj primario estén activándose y desactivándose (existe una pluralidad de pulsos de reloj procedentes del oscilador de reloj primario).

# ES 2 525 378 T3

Aunque se han representado y descrito formas de realización de la presente divulgación, y se han definido con referencia a formas de realización ejemplares de la divulgación, dichas referencias no implican una limitación de la divulgación, y no debe inferirse de ellas dicha limitación. La materia objeto divulgada es susceptible de considerables modificaciones, alteraciones y equivalentes en cuanto a forma y función, como advertirán los expertos en la materia pertinente y que cuenten con el beneficio de la presente divulgación. Las formas de realización representadas y descritas de la presente divulgación son solo ejemplos, y no son exhaustivas con respecto al alcance de la divulgación.

5

#### **REIVINDICACIONES**

1.- Un dispositivo digital que tiene una alarma y un monitor de oscilador de reloj primario, que comprende:

un procesador (102) que tiene un modo operacional en un modo dormido de baja potencia;

un oscilador (124) de reloj primario acoplado a un elemento (128) de determinación de la frecuencia externa, en el que el oscilador (124) de reloj primario genera la pluralidad de pulsos de reloj a una frecuencia determinada por el elemento (128) de determinación de la frecuencia externa;

un condensador (120) de bloqueo de corriente continua (cc) acoplado al oscilador (124) de reloj primario;

un diodo (118) conectado al condensador (120) de bloqueo de cc;

5

10

15

20

25

30

35

40

45

un condensador (116) de almacenamiento de tensión conectado al diodo (118), en el que el condensador (116) de almacenamiento de tensión es cargado con una tensión a través del diodo (118) y a partir de la pluralidad de pulsos de reloj;

un sumidero (112) de corriente constante conectado al condensador (116) de almacenamiento de tensión, en el que el sumidero (112) de corriente descarga la tensión sobre el condensador (116) de almacenamiento de tensión cuando no está siendo cargado a partir de la pluralidad de pulsos de reloj con un tiempo de descarga superior a un periodo de reloj de la pluralidad de pulsos de reloj; y

un comparador (108) de tensión que tiene una salida conectada a una entrada del procesador (102), una primera entrada conectada al condensador (116) de almacenamiento de tensión y una segunda entrada conectada a una tensión (110) de referencia, en el que

cuando la tensión sobre el condensador (116) de almacenamiento de tensión es superior a la tensión (110) de referencia, la salida del comparador (108) de tensión está en un primer nivel lógico, y

cuando la tensión sobre el condensador (116) de almacenamiento de tensión es inferior o igual a la tensión (110) de referencia, la salida del comparador (108) de tensión está en un segundo nivel lógico.

- 2.- El dispositivo digital de acuerdo con la reivindicación 1, en el que, cuando el procesador (102) está en el modo dormido de baja potencia y la salida del comparador (108) de tensión está en el segundo nivel lógico, el procesador (102) retorna al modo operacional.

- 3.- El dispositivo digital de acuerdo con la reivindicación 1 o 2, que comprende además un reloj de salvaguarda y en el que, cuando el procesador (102) retorna al modo operacional o cuando el procesador (102) está en el modo operacional y la salida del comparador (108) de tensión conmuta al segundo nivel lógico, el procesador es operable para utilizar el reloj de salvaguarda para la operación del mismo.

- 4.- El dispositivo digital de acuerdo con la reivindicación 2 o 3, en el que cuando la salida del comparador (108) de tensión conmuta al segundo nivel lógico, el procesador es programado para ejecutar una rutina de programa de fallo de oscilador de reloj primario.

- 5.- El dispositivo digital de acuerdo con cualquiera de las reivindicaciones precedentes, que comprende además un contador (106) temporizador que tiene una salida acoplada a una entrada del procesador (102), y una entrada acoplada al oscilador (124) de reloj primario.

- 6.- El dispositivo digital de acuerdo con cualquiera de las reivindicaciones precedentes, en el que el elemento (128) de determinación de la frecuencia externa es un resonador de cuarzo o un material cerámico.

- 7.- El dispositivo digital de acuerdo con cualquiera de las reivindicaciones precedentes, en el que la tensión de referencia es suministrada por una referencia de tensión o una referencia de tensión de salto de banda o a partir de un divisor de tensión de red de resistor acoplado entre una tensión de suministro y un suministro común.

- 8.- El dispositivo digital de acuerdo con cualquiera de las reivindicaciones precedentes, en el que el sumidero de corriente constante descarga el condensador (116) de almacenamiento de tensión linealmente al hilo del tiempo.

- 9.- El dispositivo digital de acuerdo con cualquiera de las reivindicaciones precedentes, que comprende además el ignorar la salida del comparador (108) de tensión en el momento del arranque hasta que el condensador (116) de almacenamiento de tensión esté cargado a partir de la pluralidad de pulsos de reloj.

- 10.- Un procedimiento de vigilancia de un oscilador de reloj primario de un dispositivo (100) digital y de generación de una alarma en caso de fallo, comprendiendo dicho procedimiento:

cargar un condensador (116) de almacenamiento de tensión a una tensión con una pluralidad de pulsos procedentes de un oscilador (124) de reloj primario por medio de un condensador (120) de bloqueo de

## ES 2 525 378 T3

corriente continua (cc) acoplado al oscilador (124) de reloj primario y un diodo (118) conectado al condensador de bloqueo de cc;

descargar el condensador (116) de almacenamiento de tensión por medio de un sumidero (112) de corriente constante con un tiempo de descarga superior a un periodo de reloj de la pluralidad de pulsos:

vigilar la tensión sobre el condensador (116) de almacenamiento de tensión con un comparador (108) de tensión, en el que

cuando la tensión sobre el condensador (116) de almacenamiento de tensión es superior a una tensión de referencia no se emite ninguna alarma a partir del comparador (108) de tensión, y

cuando la tensión sobre el condensador (116) de almacenamiento de tensión es inferior o igual a la tensión de referencia, la alarma es emitida por el comparador (108) de tensión.

- 11.- El procedimiento de acuerdo con la reivindicación 10, en el que el dispositivo (100) digital comprende un procesador (102) que recibe los pulsos como reloj operativo y comprende además un reloj de salvaguarda y tras la emisión de la alarma, el procesador es operado por el reloj de salvaguarda.

- 12.- El procedimiento de acuerdo con la reivindicación 10, en el que el dispositivo (100) digital comprende un reloj de salvaguarda y un procesador (102) que recibe los pulsos del reloj de salvaguarda, como un reloj operativo.

- 13.- El procedimiento de acuerdo con la reivindicación 11 o 12, en el que el procesador (102) tiene un modo operacional y un modo dormido de baja potencia, comprendiendo además el procedimiento la etapa de despertar el procesador (108) para que pase del modo dormido de baja potencia al modo operacional cuando se emite la alarma por el comparador (108) de tensión.

- 20 14.- El procedimiento de acuerdo con las reivindicaciones 11 a 13, en el que un procesador (102) tiene una rutina de programa de excepción de fallo de reloj que se inicia cuando se emite la alarma por el comparador (108) de tensión.

- 15.- El procedimiento de acuerdo con las reivindicaciones 11 a 14, en el que tras el arranque del dispositivo (100) digital, la alarma emitida por el comparador (108) de tensión es ignorada hasta que el condensador (116) de almacenamiento de tensión sea cargado desde la pluralidad de pulsos de reloj.

25

5

10

15