### OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 527 228

(51) Int. CI.:

H01L 21/266 (2006.01) H01L 27/108 (2006.01) H01L 29/788 (2006.01) H01L 21/335 (2006.01) H01L 21/8242 H01L 27/12 B82Y 10/00 (2011.01) B82Y 40/00 (2011.01)

(12) TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 01.02.2002 E 11175118 (6) (97) Fecha y número de publicación de la concesión europea: EP 2387066 12.11.2014

- (54) Título: Método de fabricación de un dispositivo de memoria de un solo electrón utilizando una máscara submicrónica

- (30) Prioridad:

09.02.2001 US 779547

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 21.01.2015

(73) Titular/es:

CONVERSANT INTELLECTUAL PROPERTY **MANAGEMENT INC. (100.0%)** 390 March Road, Suite 100 Ottawa, ON K2K 0G7, CA

(72) Inventor/es:

FORBES, LEONARD v AHN, KIE Y

(74) Agente/Representante:

**CURELL AGUILÁ, Mireia**

#### **DESCRIPCIÓN**

Método de fabricación de un dispositivo de memoria de un solo electrón utilizando una máscara submicrónica.

#### 5 Campo de la invención

15

20

25

30

35

40

45

50

55

La presente invención se refiere al campo de los dispositivos de semiconductores y, en particular, a estructuras de almacenamiento de carga de dispositivos de memoria.

#### 10 Antecedentes de la invención

Una celda de una memoria dinámica de acceso aleatorio (DRAM) comprende típicamente un condensador de almacenamiento de carga (o condensador para celdas) acoplado a un dispositivo de acceso, tal como un Transistor de Efecto de Campo Metal-Óxido-Semiconductor (MOSFET). El MOSFET aplica o elimina carga en el condensador, lo cual influye en el estado lógico definido por la carga almacenada. En general, las condiciones de las operaciones de la DRAM, tales como voltaje de funcionamiento, tasa de fuga y frecuencia de refresco, exigirán que el condensador almacene una cierta carga mínima. En la tendencia continuada hacia una capacidad de memoria mayor, la densidad de compactación de las celdas de almacenamiento se debe incrementar, aunque cada una de ellas debe mantener niveles de capacidad requeridos para un área respectiva de celdas de memoria. Por consiguiente, está resultando extremadamente difícil producir un condensador con una capacidad de almacenamiento relativamente alta en el área disponible de celdas de memoria.

Con vistas a una miniaturización adicional de los dispositivos electrónicos, se han introducido componentes de un solo electrón, en los cuales los procesos de conmutación se efectúan con electrones individuales. De esta manera, se han dado a conocer técnicas para sistemas de memoria en tecnología de silicio basada en (1) atrapar electrones individuales en inclusiones de silicio en el óxido de puerta de los transistores; (2) atrapar electrones en trampas o defectos puntuales en el óxido de puerta; (3) atrapar electrones en los granos de polisilicio en transistores de película fina; o (4) atrapar electrones individuales en regiones de potencial mínimo en una película ultra-fina de silicio dotado de rugosidad en material aislante. No obstante, la mayoría de estas técnicas conlleva la tunelización de electrones a través de óxidos finos, lo cual a su vez requiere campos eléctricos elevados en dichos óxidos. Estos campos eléctricos tan elevados deterioran los óxidos y otorgan solamente un número limitado de tiempos de ciclos de memoria, típicamente del orden de 10³ veces. Otras técnicas de un solo electrón conllevan el atrapamiento de electrones en granos de polisilicio formados en dispositivos de película fina, aunque este proceso resulta difícil de controlar puesto que la aparición de rugosidad de polisilicio para formar los granos se produce de manera aleatoria.

Por consiguiente, existe una necesidad de un método mejorado de formación de dispositivos de un solo electrón usados en la fabricación de IC. Existe también una necesidad de proporcionar un procedimiento de fabricación de dispositivos de memoria de un solo electrón de alta densidad con canales de conducción y áreas de almacenamiento que sean reproducibles fácilmente y que no se produzcan de una manera aleatoria.

La patente US nº 5219783 propone un método de formación de regiones bien dopadas en una capa semiconductora. Por lo menos una región n-dopada y por lo menos una región p-dopada están formadas en la capa semiconductora. La región n-dopada está separada de la región p-dopada por una región de separación. La región de separación está formada realizando un diseño de una capa de nitruro en el sustrato y mediante ataque químico de la capa para proporcionar separadores que sirven como máscara de bloqueo de la implantación de dopante.

La patente US nº 6063688 propone un método que lleva a cabo espacios reducidos de tamaño característico en un sustrato semiconductor. Las partes separadoras pueden ser utilizadas para formar canales en el servicio de sustrato para realizar hilos cuánticos o puntos cuánticos.

En un estudio titulado "A Nano-Structure Memory with Silicon on Insulator Edge Channel and a Nano Dot" (G Park *et al*, Japanese Journal of Applied Physics, Japan Society of Applied Physics, JP, Vol. 37, nº 12 B, 1 de diciembre de 1998, páginas 7190-7192), los autores proponen una memoria con nano-estructura con canales de borde y no puntos de silicio sobre aislante (SOI), siendo la anchura del canal de borde determinada por el grosor de la capa rebajada de silicio superior de la oblea SOI y el tamaño del nanopunto de la pared lateral fue determinado por ataque químico con iones reactivos (RIE) y litografía por haz de electrones.

### Breve sumario de la invención

60 Según la presente invención, se proporciona un método tal como se expone en la reivindicación 1.

Ventajas adicionales de la presente invención se pondrán más claramente de manifiesto a partir de la descripción detallada y de los dibujos adjuntos, que ilustran formas de realización ejemplificativas de la invención.

#### Breve descripción de los dibujos

5

25

30

40

45

50

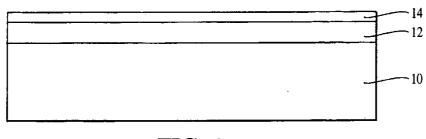

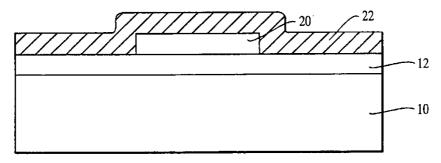

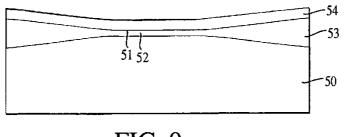

La Figura 1 ilustra una vista en sección transversal de una parte de un dispositivo de semiconductor en el cual está formada una estructura sublitográfica con bordes delimitados se formará según un método de la presente invención.

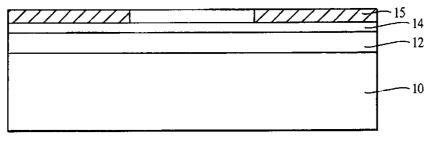

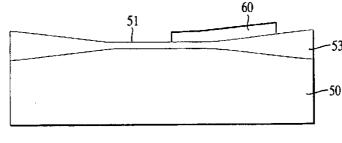

La Figura 2 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 1.

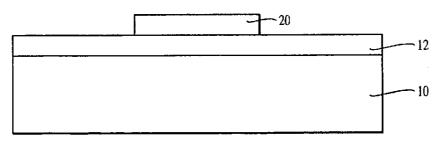

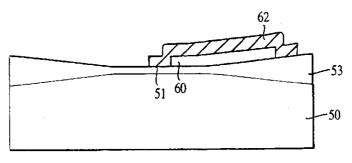

La Figura 3 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 2.

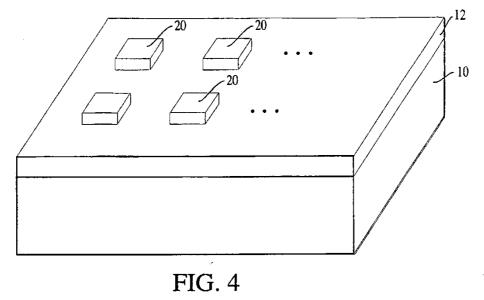

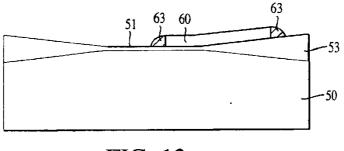

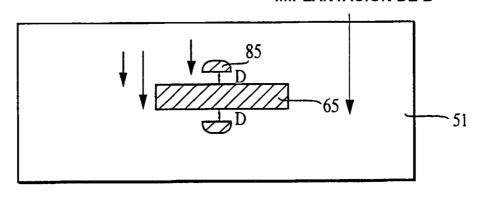

La Figura 4 ilustra una vista tri-dimensional superior del dispositivo de la Figura 3.

La Figura 5 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 4.

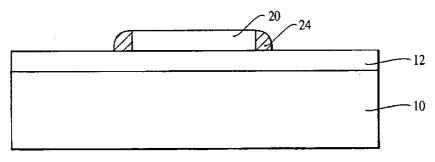

La Figura 6 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 5.

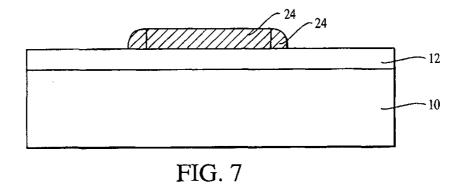

La Figura 7 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 6.

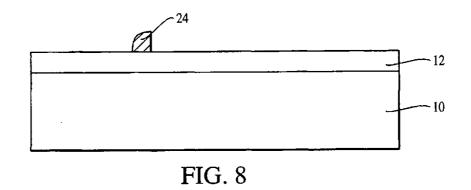

La Figura 8 ilustra una vista en sección transversal del dispositivo de la Figura 1 en una fase de procesado subsiguiente a la mostrada en la Figura 7.

La Figura 9 ilustra una vista en sección transversal de una parte de un dispositivo de DRAM de un solo electrón, en el cual se han formado estructuras con bordes delimitados, según un método de la presente invención.

La Figura 10 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 9.

La Figura 11 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 10.

La Figura 12 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 11.

La Figura 13 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 12.

La Figura 14 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 13.

La Figura 15 ilustra una vista superior del dispositivo de la Figura 14.

La Figura 16 ilustra una vista superior del dispositivo de la Figura 15 en una fase de procesado subsiguiente a la mostrada en la Figura 15.

La Figura 17 ilustra una vista en sección transversal del dispositivo de la Figura 16, tomada según la línea 17-17'.

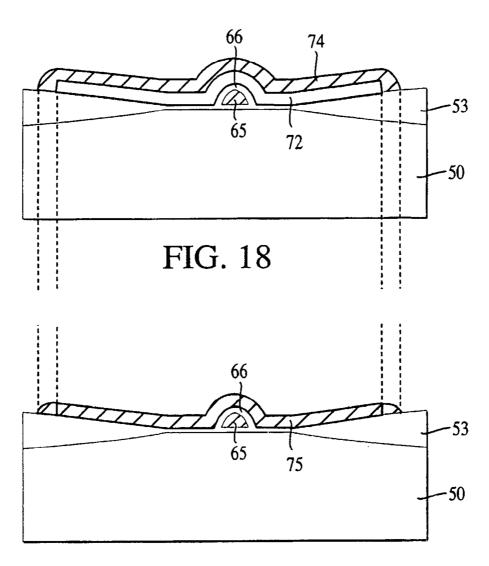

La Figura 18 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 17.

La Figura 19 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 18.

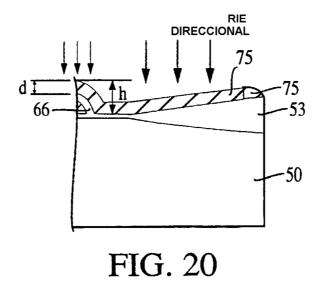

La Figura 20 ilustra una vista parcial en sección transversal del dispositivo de la Figura 19.

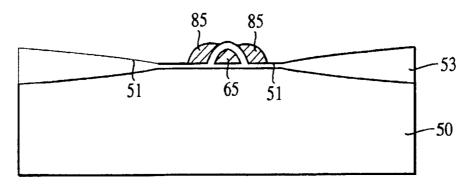

La Figura 21 ilustra una vista en sección transversal del dispositivo de la Figura 9 en una fase de procesado subsiguiente a la mostrada en la Figura 19.

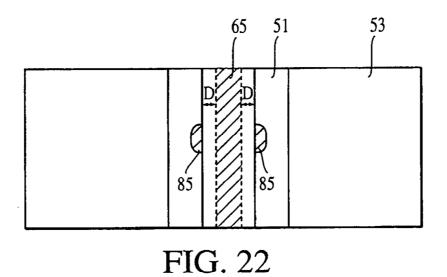

La Figura 22 ilustra una vista superior del dispositivo de la Figura 21.

La Figura 23 ilustra una vista superior a 90 grados del dispositivo de la Figura 22.

La Figura 24 ilustra una vista superior del dispositivo de la Figura 21 en una fase de procesado subsiguiente a la mostrada en la Figura 23.

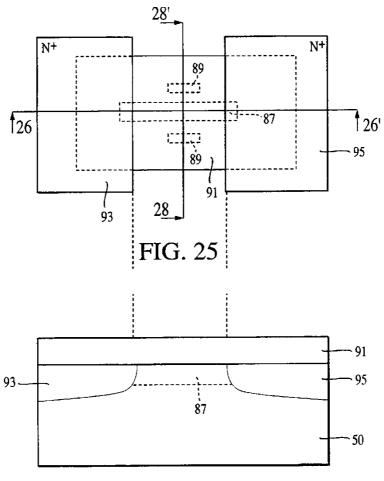

La Figura 25 ilustra una vista superior del dispositivo de la Figura 21 en una fase de procesado subsiguiente a la mostrada en la Figura 24.

La Figura 26 ilustra una vista en sección transversal del dispositivo de la Figura 25, tomada según la línea 26-26'.

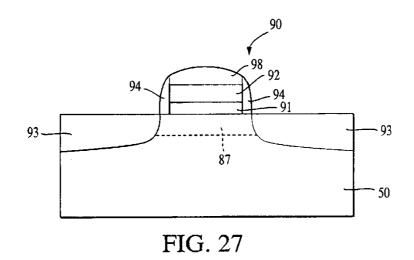

La Figura 27 una vista en sección transversal del dispositivo de la Figura 25 en una fase de procesado subsiguiente a la mostrada en la Figura 26.

La Figura 28 ilustra una vista en sección transversal del dispositivo de la Figura 25, tomada según la línea 28-28'.

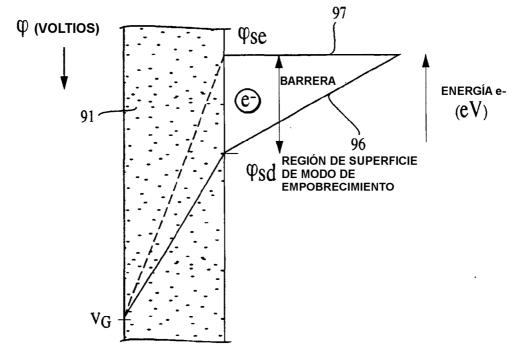

La Figura 29 ilustra las variaciones de potencial en la superficie y la barrera de energía en la dirección del eje y para un electrón almacenado en un punto de potencial mínimo formado según un método de la presente invención.

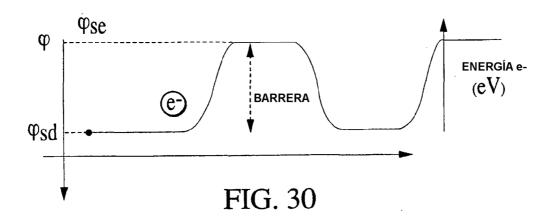

La Figura 30 ilustra las variaciones de potencial en la superficie y la barrera de energía en la dirección del eje x para un electrón almacenado en un punto de potencial mínimo formado según un método de la presente invención.

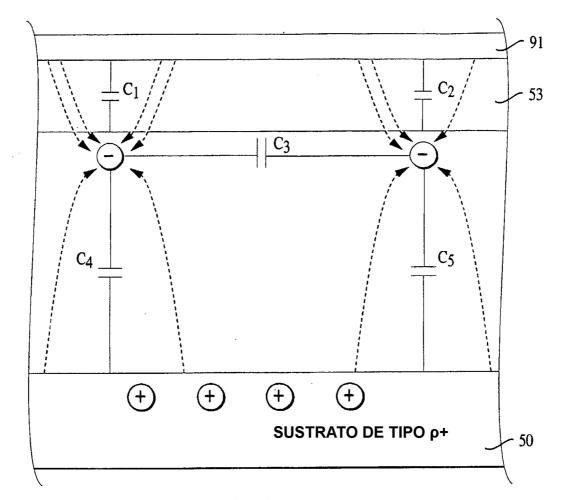

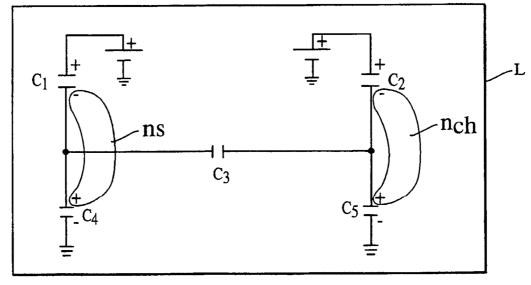

La Figura 31 ilustra un modelo de dispositivo basado en elementos capacitivos para el canal de conducción y los puntos de potencial mínimo del dispositivo de DRAM de un solo electrón formado según un método de la presente invención.

La Figura 32 ilustra otro modelo de dispositivo basado en elementos capacitivos para el canal de conducción y los puntos de potencial mínimo del dispositivo de DRAM de un solo electrón formado según un método de la presente invención.

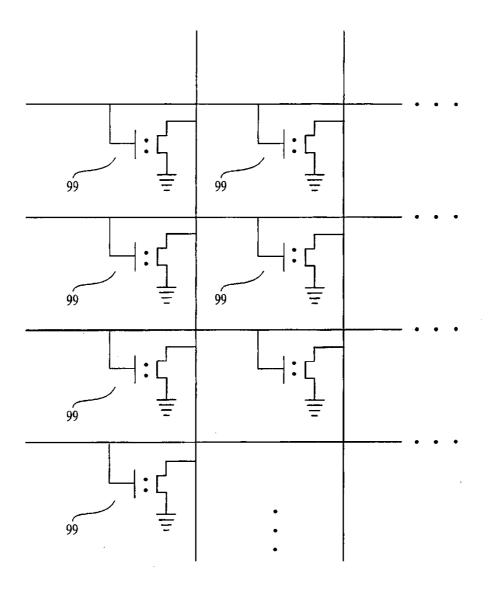

La Figura 33 ilustra una matriz de DRAM de un solo electrón que incluye transistores con canales de conducción y los puntos de potencial mínimo formado según un método de la presente invención.

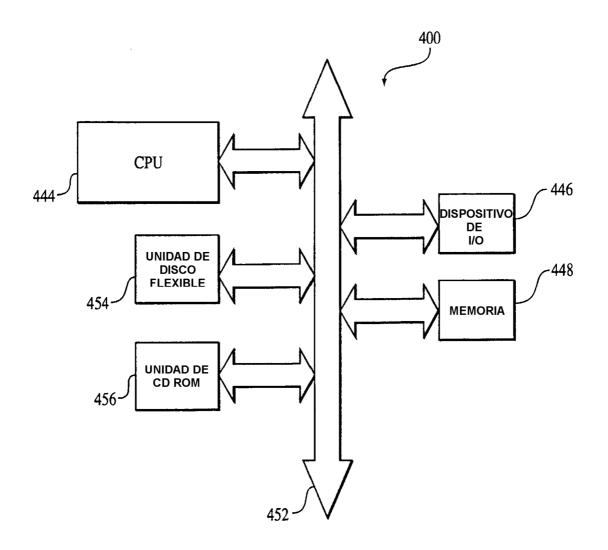

La Figura 34 es una ilustración de un sistema de ordenador que tiene un dispositivo de memoria de un solo electrón formado según un método de la presente invención.

## Descripción detallada de la invención

5

10

15

30

35

40

45

50

55

60

65

En la siguiente descripción detallada, se hace referencia a varias formas de realización ejemplificativas específicas en las cuales se puede llevar a la práctica la invención. Estas formas de realización se describen con detalle suficiente para permitir que aquellos versados en la técnica lleven a la práctica la invención, y debe entenderse que se pueden utilizar otras formas de realización, y que se pueden realizar cambios estructurales, lógicos y eléctricos.

Los términos "oblea" o "sustrato" usados en la siguiente descripción pueden incluir cualquier estructura basada en semiconductores que tenga una superficie de semiconductor expuesta. Debe entenderse que oblea y estructura incluyen silicio-sobre-aislante (SOI), silicio-sobre-zafiro (SOS), semiconductores dopados y no dopados, capas epitaxiales de silicio sustentadas por unos cimientos de semiconductor de base, y otras estructuras de semiconductores. No es necesario que el semiconductor se base en silicio. El semiconductor podría ser silicio-germanio, germanio, o arseniuro de galio.

En referencia a continuación a los dibujos, en donde los elementos similares se designan mediante numerales de referencia semejantes. Las Figuras 1 a 8 ilustran un método de formación de estructuras de bordes delimitados con dimensiones sublitográficas en tecnologías CMOS de 0,1 µ, que se pueden usar para formar adicionalmente estructuras de canales y/o almacenamiento en dispositivos de memoria. Las Figuras 9 a 27 ilustran una forma de realización ejemplificativa de una parte de un dispositivo de memoria de un solo electrón y de alta densidad para su uso en tecnologías de almacenamiento de carga, que utiliza las estructuras con bordes delimitados formadas de acuerdo con un método de la presente invención.

La Figura 1 representa una formación de una estructura con bordes delimitados, para un dispositivo de memoria en una fase intermedia de procesado y de acuerdo con un método de la presente invención. La estructura de la Figura 1 incluye un sustrato 10 y una capa de óxido 12 formada sobre el sustrato 10 mediante técnicas convencionales de procesado de semiconductores. A continuación se dispone una capa fina de nitruro de silicio 14 (Figura 1) de aproximadamente 500 Å y aproximadamente 1.000 Å (donde 1Å=0,1 nm) sobre el sustrato 10 y la capa de óxido 12. La capa de nitruro de silicio 14 es una capa sacrificial que, tal como se explica de forma más detallada posteriormente, se eliminará más adelante.

Según una forma de realización ejemplificativa de la presente invención, la capa de nitruro de silicio 14 (Figura 1) se forma utilizando un proceso de deposición de baja temperatura. Por ejemplo, se han depositado nitruros de silicio a baja temperatura mediante deposición química de vapor mejorada con plasma de resonancia ciclotrónica de

electrones (ECR PE CVD) para aplicaciones en micromecanización, según describen Panepucci, R. R. et al. en Silicon Nitride Deposited by Electron Cyclotron Resonance Plasma Enhanced Chemical Vapor Deposition for Micromachining Applications, Proc. of SPIE, vol. 3512, págs. 146-51 (1998), que, durante el proceso de deposición, usaron como reactivo para ataque químico una solución mixta de KOH:isopropilo:H<sub>2</sub>.

5

10

La capa de nitruro de silicio 14 (Figura 1) también se puede depositar a una baja temperatura y una baja potencia de microondas usando silano puro como gas precursor en un plasma de nitrógeno. Lapeyrade, M. *et al.* en *Silicon Nitride Films Deposited by Electron Cyclotron Resonance Plasma-Enhanced Chemical Vapor Deposition,* Journal of Vacuum Science and Technology A, vol. 17, n.º 2, págs. 433-44 (1999), exponen detalles de este proceso de deposición a baja temperatura. De esta manera, se pueden obtener películas de nitruro de silicio con una alta resistividad (aproximadamente 10<sup>15</sup> ohmios/cm y superiores) y con un campo de ruptura de aproximadamente 3 MV/cm, a una temperatura del sustrato de aproximadamente 300°C.

15

una capa fotorresistente 15 formada sobre la capa de nitruro de silicio 14 hasta un grosor de aproximadamente 5.000 Å a aproximadamente 10.000 Å. A continuación, a la capa fotorresistente 15 se le dota de un diseño con una máscara (no mostrada) usada como máscara de ataque químico durante una etapa de ataque químico con el fin de obtener una estructura de nitruro de silicio 20, tal como se muestra en la Figura 3. Para dimensiones mínimas, la estructura de nitruro de silicio 20 puede tener la topografía de un islote cuadrado, por ejemplo de aproximadamente 1.000 Å x 1.000 Å. Aunque la Figura 3 ilustra solamente una estructura de nitruro de silicio 20, debe entenderse, sin embargo, que, sobre la capa de óxido 12, se puede formar una pluralidad de dichas estructuras o islotes de nitruro de silicio. En la Figura 4 se ilustra, en una vista tridimensional, dicha pluralidad de estructuras de nitruro de silicio 20.

Seguidamente, tal como se ilustra en la Figura 2, a la capa de nitruro de silicio 14 se le dota de un diseño usando

20

25

El ataque químico de la capa fotorresistente 15 (Figura 2) para obtener la estructura de nitruro de silicio 20 (Figura 3) se puede lograr usando una técnica de ataque químico de alta resolución, tal como la descrita por Mescher, M.J. et al. en AS dry etch fabrication process for microelectromechanical devices using silicon nitride sacrificial layers, Proc. of InterPACK 97, vol. 1, págs. 435-38 (1997), donde revelaron una velocidad de ataque químico con nitruro de

aproximadamente 3 μm/min, en comparación con los 20 nm/min para óxido, usando un sistema comercial denominado Poly-Etch.

30

El ataque químico de la capa fotorresistente 15 (Figura 2) para obtener la estructura de nitruro de silicio 20 (Figura 3) se puede lograr además mediante un proceso altamente uniforme y selectivo de ataque químico para separadores de nitruro en tecnología avanzada sub-0,35 μm. Dicho proceso es descrito detalladamente por Regis, J.M. *et al.* en *Reactive ion etch of silicon nitride spacer with high selectivity to oxide,* Proceeding of 1997 IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop, págs. 252-56 (1997), de acuerdo con el cual los autores usaron un sistema comercial denominado *electric Etch M\*P+MERIE chamber.* Un proceso de ataque químico principal basado en CF<sub>3</sub>/Ar proporcionaba una velocidad controlable de ataque químico de nitruro de entre 80 y 170 nm/min con una buena uniformidad, al mismo tiempo que proporcionando un perfil apropiado y manteniendo la anchura del separador.

40

35

Alternativamente, el ataque químico de la capa fotorresistente 15 (Figura 2) para obtener la estructura de nitruro de silicio 20 (Figura 3) también se puede lograr usando un sistema de plasma de acoplamiento inductivo (ICP). Recientemente, en *High selectivity silicon nitride etch process*, Semiconductor Int., vol. 21, n.º 8, págs 235-40 (1998), Wang, Y. *et al.* han expuesto un proceso de ataque químico de nitruro de alta selectividad usando un plasma de acoplamiento inductivo, donde se logró una relación de selectividad del ataque químico de nitruro por LPCVD con respecto a óxido térmico mayor que 40:1, a una velocidad de ataque químico de nitruro de 50 nm/min.

45

50

Después de la formación de las estructuras de silicio 20, se forma una capa de polisilicio 22 (Figura 5) sobre la estructura de nitruro de silicio 20 y la capa de óxido 12, tal como se representa en la Figura 5. Para simplificar, la Figura 5 ilustra una vista en sección transversal de la estructura de la Figura 4 y representa solamente una estructura de nitruro de silicio 20. No obstante, debe entenderse que la capa de polisilicio 22 se forma sobre la pluralidad de estructuras de nitruro de silicio 20 de la Figura 4.

55

60

En una forma de realización ejemplificativa de la invención, la capa de polisilicio 22 (Figura 5) se deposita mediante deposición química de vapor (CVD) usando precursor de silano hasta un grosor de entre aproximadamente 1.500 Å y aproximadamente 1.800 Å. Un ejemplo de dicho proceso de deposición viene dado por Boswell, E. C. et al. en *Polysilicon field emitters*, Journal of Vacuum Science and Tech. B, vol. 14, n.º 3, págs. 1910-13 (1996), de acuerdo con el cual se depositaron películas de polisilicio a 645°C sobre sustratos grandes mediante CVD, seguida por un ataque químico en húmedo usando un ataque químico de HF:HNO<sub>3</sub> ácido acético para formar las estructuras deseadas. La oxidación de las estructuras se llevó a cabo en un horno de oxígeno húmedo a 950°C durante aproximadamente 90 minutos. Subsiguientemente, a este óxido se le aplicó un ataque químico en HF tamponado. Esta combinación de procesos de deposición, ataque químico y oxidación produjo estructuras de polisilicio más definidas para obtener una emisión de campo eficiente.

65

Posteriormente a la formación de la capa de polisilicio 22 (Figura 5), se forman estructuras de polisilicio con bordes delimitados 24 (Figura 6) mediante ataque químico direccional de la capa de polisilicio 22 por RIE, tal como se

muestra en la Figura 6. Las dimensiones de las estructuras de polisilicio con bordes delimitados 24 son aproximadamente 100 Å de achura y aproximadamente 1.000 Å de longitud. El ataque químico direccional de la capa de polisilicio 22 se puede lograr mediante una variedad de métodos, tales como el descrito por Horioka, K. et al. en Highly selective and directional etching of phosphorous doped polycrystalline silicon with tri-level resist mask employing magnetron plasma, 1998 Symposium on VLSI Technology, Digest of Technical Papers, págs. 81-82 (1998). Horioka, K. et al. dieron a conocer un ataque químico tanto altamente selectivo como direccional de polisilicio n+ mediante el uso de un plasma magnetrónico de Cl<sub>2</sub>SiCl<sub>4</sub> utilizando una máscara protectora de tres niveles a una temperatura del sustrato por debajo de 0°C.

Alternativamente, la formación de las estructuras de polisilicio con bordes delimitados 24 (Figura 6) se puede lograr usando un aparato de ataque químico con plasma por resonancia ciclotrónica de electrones (ECR) ultra-limpio, tal como el descrito por Matsuura *et al.* en *Directional etching of Si with perfect selectivity to SiO<sub>2</sub> using an ultraclean electron cyclotron resonance plasma,* Appl. Phys. Letters, vol. 56, n.º 14, págs. 1.339-41 (1990). Se usaron un plasma de cloro a una presión de entre 0,6 y 4,0 Torr con una potencia de microondas de entre 300 y 700 vatios para atacar químicamente de manera selectiva películas de silicio. Bajo las condiciones altamente selectivas, se obtuvieron diseños submicrónicos inferiores anisótropos de polisilicio con un rebaje en exceso mínimo.

20

25

30

35

40

45

60

65

Todavía adicionalmente, las estructuras de polisilicio con bordes delimitados 24 (Figura 6) también se pueden obtener mediante ataque químico profundo direccional de la capa de polisilicio 22 realizando un ataque químico criogénico por iones reactivos con el uso de gas de SF<sub>6</sub> de acuerdo con un método expuesto por Esashi, M. *et al.* en *High-rate directional deep dry etching for bulk silicon micromachining*, Journal of Micromechanics and Microengineering, vol. 5, n.º 1, págs. 5 a 10 (1995). El sistema desarrollado por Esashi, M. *et al.* se podría usar para un ataque químico a través de una oblea de silicio de un grosor de 200 μm a una velocidad típica de ataque químico de 0,8 μm/min con paredes verticales tan finas como 20 μm.

En cualquier caso, el polisilicio de la capa de polisilicio 22 (Figura 5) se elimina de la parte superior de la estructura de nitruro de silicio 20 y en las áreas del óxido de campo, para obtener las estructuras de polisilicio con bordes delimitados 24 (Figura 6) a lo largo de las paredes laterales de la estructura de nitruro de silicio 20. Puesto que cada una de las estructuras de nitruro de silicio 20 (Figura 4) tiene cuatro paredes laterales, cada estructura de nitruro de silicio 20 tendrá cuatro estructuras de polisilicio con bordes delimitados 24 respectivas, formada cada una de ellas en una pared lateral respectiva. Típicamente, las dimensiones de las estructuras de polisilicio con bordes delimitados 24 son aproximadamente una décima parte del tamaño característico mínimo, o aproximadamente 100 Å de anchura y aproximadamente 1.000 Å de longitud, y las mismas se puede hacer variar cambiando los grosores relativos de la estructura de nitruro de silicio 20 y los correspondientes de la capa de polisilicio 22.

Una vez que se ha completado el ataque químico direccional de la capa de polisilicio 22, la estructura de nitruro de silicio 20 se elimina mediante un ataque químico en húmedo, por ejemplo, para obtener la estructura de la Figura 7 conservando las cuatro estructuras de polisilicio con bordes delimitados 24. Un ejemplo de ataque químico en húmedo de nitruro de silicio es descrito por Alkaisi, M. M. et al. en Nanolithography using wet etched nitride phase mask, Journal of Vacuum Science and Tech., B, vol. 16, n.º 6, págs. 3.929-33 (1998), donde se aplica un ataque químico a nitruro de silicio usando HF o H<sub>3</sub>PO<sub>4</sub> caliente.

En caso de que sea necesaria una estructura de polisilicio con bordes delimitados 24 (como en la forma de realización ejemplificativa que se describe posteriormente), se utiliza una etapa adicional de aplicación de máscaras para eliminar las otras tres estructuras de polisilicio con bordes delimitados 24 y obtener la estructura de la Figura 8. La estructura de polisilicio con bordes delimitados 24 de la Figura 8 tiene un tamaño característico de un valor tan pequeño como 100 Å, o según se ha explicado anteriormente, aproximadamente una décima parte del tamaño característico mínimo, es decir el grosor de la estructura de nitruro de silicio 20.

La estructura de polisilicio con bordes delimitados 24 de la Figura 8 se puede diseñar de manera que presente varias geometrías, por ejemplo tiras y/o puntos, que se pueden usar adicionalmente para una máscara para una implantación de voltaje de umbral que ajuste el voltaje de umbral de un dispositivo de memoria (por ejemplo, un dispositivo NMOS) en un proceso CMOS convencional. La expresión "punto de polisilicio" usada en esta solicitud se refiere a cualquier estructura de polisilicio que tenga una estructura geométrica definida, incluyendo, aunque sin carácter limitativo, estructuras circulares o esféricas, estructuras semiesféricas, o estructuras rectangulares, entre otras.

En una forma de realización ejemplificativa de la invención, el método ejemplificativo de formación de estructuras de polisilicio con bordes delimitados, tales como la estructura de polisilicio con bordes delimitados 24 de la Figura 8, se utiliza para formar tiras de polisilicio y puntos de polisilicio adyacentes en el área de la puerta de óxido fino de un dispositivo CMOS normal de canal n. Tal como se explicará de forma detallada posteriormente, la tira de polisilicio se usará para formar un canal de conducción con un bajo voltaje de umbral entre la región de fuente y de drenaje y los puntos de polisilicio adyacentes se usarán para formar regiones de potencial mínimo con el fin de almacenar electrones. La presencia o ausencia de electrones en estas regiones de potencial mínimo se utiliza como una función de memoria en una DRAM de un solo electrón de muy alta densidad. A continuación se describe, en referencia a las Figuras 9 a 32, la formación de un dispositivo CMOS de canal n para DRAMs de un solo electrón y

de alta densidad con tiras y puntos de polisilicio como regiones de canal y almacenamiento formadas de acuerdo con un método de la presente invención.

La Figura 9 ilustra una vista en sección transversal del área de un dispositivo CMOS de canal n en la cual se forman regiones de óxido de campo 53 sobre el sustrato 50 mediante técnicas convencionales de procesado de semiconductores. A efectos de la presente invención, se supone implícitamente que las regiones de fuente/drenador (no mostradas) de un transistor convencional ya se han formado y que también ya se ha formado el apilamiento de puerta para dopar las regiones de fuente y drenador y que se ha eliminado. Las regiones de óxido de campo 53 rodean y aíslan completamente un área de dispositivo de óxido de puerta fino 51, en cuyo centro se formarán una tira de polisilicio fina 65 (Figura 13) y dos puntos de polisilicio adyacentes 85 (Figura 21), tal como se ha explicará de forma más detallada posteriormente.

10

15

20

25

40

45

50

55

60

65

Seguidamente, mediante los métodos de deposición a baja temperatura antes descritos en referencia a la formación de la capa de nitruro de silicio 14 (Figura 2), se deposita una primera capa de nitruro de silicio 54 (Figura 9). A la primera capa de nitruro de silicio 54 se le aplica un diseño y un ataque químico mediante litografía óptica para obtener un primer islote de nitruro de silicio 60 que tiene el extremo proximal en el centro del área de dispositivo de óxido de puerta fino 51, tal como se muestra en la Figura 10. Seguidamente, sobre el primer islote de nitruro de silicio 60 y el área de dispositivo de óxido de puerta fino 51, se forma una primera capa de polisilicio 62 (Figura 11) mediante cualquiera de los procesos de deposición expuestos anteriormente con respecto a la formación de la capa de polisilicio 22 (Figura 5). Subsiguientemente, a la primera capa de polisilicio 62 se le aplica un ataque químico direccional mediante RIE para formar cuatro tiras de polisilicio con bordes delimitados 63 (Figura 12) de una manera similar a la formación de las estructuras de polisilicio con bordes delimitados 24 antes explicadas en referencia a la Figura 6. Aunque la Figura 12 ilustra una vista en sección transversal de solamente dos tiras de polisilicio con bordes delimitados 63, debe entenderse que, de hecho, se forman cuatro de estas tiras de polisilicio con bordes delimitados 63, cada una de ellas en cada pared lateral del primer islote de nitruro de silicio 60. Cada una de las cuatro tiras de polisilicio con bordes delimitados 63 tiene una anchura de aproximadamente 100 Å y una longitud de aproximadamente 1.000 Å.

Tras el ataque químico direccional de la primera capa de polisilicio 62, el primer islote de nitruro de silicio 60 (Figura 12) se elimina mediante un ataque químico en húmedo usando, por ejemplo, H<sub>3</sub>PO<sub>4</sub> o HF caliente. Puesto que solamente son necesarias las tiras de polisilicio con bordes delimitados 63 en el centro del área de óxido de puerta fino 51, las otras tres tiras de polisilicio con bordes delimitados 63 también se eliminan para obtener una tira de polisilicio 65 por el centro del área de óxido de puerta fino 51, tal como se ilustra en la Figura 13. Tal como se explicará de forma detallada posteriormente, la tira de polisilicio 65 formará una región de canal de conducción sub-litográfica 87 (Figuras 24 a 27) entre la fuente y el drenador del dispositivo CMOS de canal n.

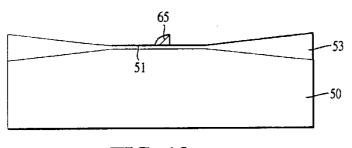

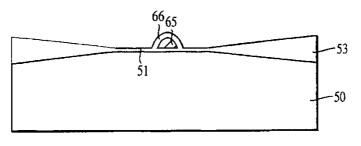

Posteriormente a la eliminación del primer islote de nitruro de silicio 60 y las tres tiras de polisilicio con bordes delimitados 63, la tira de polisilicio 65 se puede oxidar y cubrir con una capa de óxido 66 con un grosor de aproximadamente 100 Å, tal como se muestra en la Figura 14. Para obtener una mejor comprensión, la Figura 15 ilustra una vista superior de las estructuras de la Figura 14.

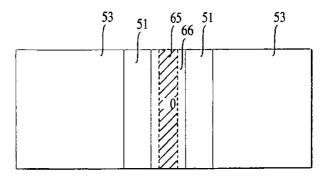

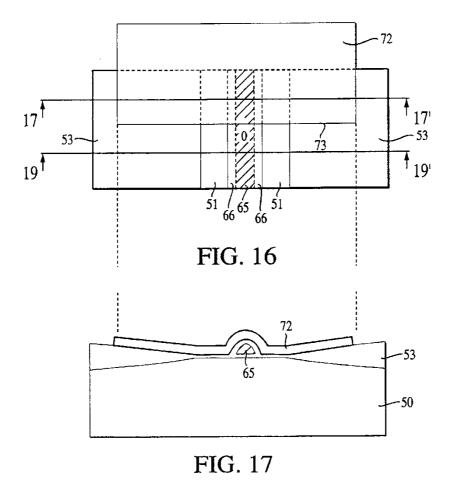

La técnica de formación de la tira de polisilicio 65 se aplica nuevamente para la formación de puntos de polisilicio adyacentes 85 (Figura 21) en el área de óxido de puerta fino 51 del dispositivo CMOS. Los puntos de polisilicio 85 se usarán además para formar áreas de potencial mínimo con el fin de almacenar electrones adyacentes al canal de conducción 87 (Figura 24) formado por la tira de polisilicio 65, y estos electrones almacenados reducirán la conductividad o corriente de drenaje en el canal de conducción 87. Como tal, se realiza una deposición, un diseño y un ataque químico de una segunda capa de nitruro de silicio (no mostrada) para obtener un segundo islote de nitruro de silicio 72, mostrado en las vistas superior y en sección transversal de las Figuras 16-17. Tal como se ilustra en las Figuras 16-17, al segundo islote de nitruro de silicio 72 se le dota de un diseño tal que una de sus paredes laterales, por ejemplo, su pared lateral proximal 73 (Figura 16), se sitúe en intersección perpendicularmente con la tira de polisilicio 65 aproximadamente por el centro O de la tira de polisilicio 65, extendiéndose durante aproximadamente la mitad del área de óxido de puerta fino 51.

Seguidamente se forma una segunda capa de polisilicio 74 (Figura 18) sobre el segundo islote de nitruro de silicio 72 mediante cualquiera de los métodos de deposición expuestos anteriormente con respecto a la formación de la capa de polisilicio 22 (Figura 5). A continuación, a la segunda capa de polisilicio 74 se le aplica un ataque químico direccional mediante RIE para formar las tiras de polisilicio con bordes delimitados 75 (Figura 19) de una manera similar a la formación de las estructuras de polisilicio con bordes delimitados 24 (Figura 6). No obstante, en este caso, se forma una estructura tri-dimensional compleja en la que la pared lateral proximal 73 de la segunda capa de polisilicio 74 se cruza con la tira de polisilicio 65, dando como resultado un grosor adicional de polisilicio al que se aplicará posteriormente un ataque químico. Esto se ilustra mejor en la Figura 20, que, por motivos de simplicidad, representa únicamente el lado derecho de la estructura de la Figura 19, y que representa cómo el ataque químico direccional por RIE tiene una distancia grande "h" en la que aplicar una taque químico a través de la tira de polisilicio 65, mucho más grande que el grosor "d" de la tira de polisilicio 75. Por consiguiente, se puede diseñar y aplicar un ataque químico direccional adicional de manera que, después de la eliminación del segundo islote de nitruro de silicio 72, se forman únicamente dos puntos cuadrados de polisilicio 85 (Figura 21) en cada lado de la tira de

polisilicio 65. Para entender mejor la invención, la Figura 22 ilustra una vista superior de la estructura de la Figura 21. Cada uno de los puntos de polisilicio 85 tiene una longitud de aproximadamente 200 Å y una anchura de aproximadamente 200 Å. Cada uno de los puntos de polisilicio 85 está también separado con respecto a la tira de polisilicio 65 por una distancia D (Figura 22) de aproximadamente 100 Å.

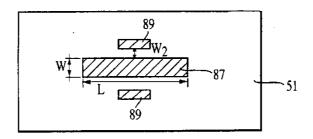

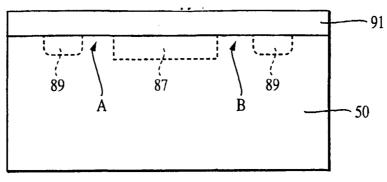

Las Figuras 22-23 ilustran etapas de procesado restantes para el procesado CMOS, donde la Figura 23 tiene una orientación de 90 grados con respecto a la Figura 22. El área de óxido de puerta fino 51 experimenta una implantación de boro para el ajuste de voltaje de umbral VT, exceptuando que la tira de polisilicio 65 y los dos puntos de polisilicio adyacentes 85 se usan para la máscara de la implantación de boro. De esta manera, después de la eliminación de la tira de polisilicio 65 (Figura 23), se forma un canal de conducción 87 por debajo de la tira de polisilicio 65, tal como se muestra en la Figura 24. El canal de conducción 87 es un área de puerta de óxido fino con una anchura de aproximadamente 100 Å y una longitud de aproximadamente 1.000 Å y con un voltaje de umbral bajo de modo de empobrecimiento. De manera similar, después de la eliminación de los puntos de silicio 85, se forman dos puntos de potencial mínimo 89, de aproximadamente la mitad del área del canal de conducción 87, o aproximadamente 200 Å x 200 Å, por debajo de los dos puntos de polisilicio 85, que tienen también un voltaje de umbral del modo de empobrecimiento inferior a las otras áreas de óxido de puerta fino sin máscara.

10

15

20

35

40

45

50

55

60

65

Una vez que se han eliminado la tira de polisilicio 65 y los dos puntos de polisilicio 85, se deposita un óxido de puerta convencional 91 con un grosor de aproximadamente 100 Å sobre el área de puerta de óxido fino 51 que incluye el canal de conducción 87, los dos puntos de potencial mínimo 89, y las regiones de fuente y drenador 93, 95 formadas previamente de acuerdo con técnicas convencionales, según se ilustra en las Figuras 25, 26. La Figura 27 ilustra un apilamiento de puerta 90 que incluye óxido de puerta 91, una capa conductora 92, formada con polisilicio, por ejemplo, separadores de nitruro 94 y un casquete de nitruro 98.

A continuación se hace referencia a las Figuras 28 a 32 para explicar las características eléctricas del dispositivo CMOS de canal n que tiene el canal de conducción 87 y los puntos de potencial mínimo 89 formados según se han descrito anteriormente en referencia a las Figuras 9 a 27. La Figura 28 es una vista en sección transversal según la línea 28-28' de la estructura de la Figura 25, que representa el canal de conducción 87 separado de los dos puntos de potencial mínimo 89 por dos áreas de barrera A, B, a la distancia D de aproximadamente 100 Å. Tal como se ha explicado anteriormente, en las regiones fuera del canal de conducción 87 y los puntos de potencial mínimo 89 se ha implantado boro para ajustar el voltaje de umbral VT con el fin de hacerlo más positivo, y por lo tanto estas regiones de implantación son regiones de modo de enriquecimiento del dispositivo. Por contraposición, en el canal de conducción 87 y los puntos de potencial mínimo 89 no se implanta boro, los mismos tienen un voltaje de umbral más negativo y, subsiguientemente, son regiones de modo de empobrecimiento del dispositivo.

Los electrones se pueden almacenar en los puntos de potencial mínimo 89 así como en el canal de conducción 87 siempre que el voltaje de puerta VG se ajusta apropiadamente y no sea demasiado grande. La Figura 29 ilustra las variaciones de potencial φ (voltios) en la superficie y la barrera de energía E (eV) en la dirección del eje y para un electrono almacenado en los puntos de potencial mínimo 89. La región de superficie de modo de empobrecimiento 96 se corresponde con un umbral de voltaje bajo, es decir el voltaje de umbral de modo de empobrecimiento VTD, donde los electrones pueden quedar atrapados fácilmente porque las bandas se doblan de manera fácil. La región de superficie de modo de enriquecimiento 97 se corresponde con un umbral de voltaje alto, es decir, el voltaje de umbral de modo de enriquecimiento VTE, dos los electrones no quedan atrapados ya que las bandas no se doblan fácilmente. De manera similar, la Figura 29 ilustra las variaciones de potencial φ en la superficie y la barrera de energía en la dirección del eje x para un electrón almacenado en los puntos de potencial mínimo 89.

Si la puerta de voltaje VG está por encima del voltaje de umbral de modo de enriquecimiento VTE, y bastante por encima del voltaje de umbral de modo de empobrecimiento VTD, entonces la superficie se invertirá y los electrones estarán presentes sobre el área de superficie completa. Así es cómo los puntos de potencial mínimo 89 se llenan con electrones, y cuando se aplica un voltaje de puerta VG grande y a continuación el mismo se reduce gradualmente, los electrones quedarán atrapados en los puntos de potencial mínimo 89. El borrado se puede lograr aplicando voltaje negativo y acumulando la carga en la superficie. La presencia de electrones con carga negativa en los puntos de potencial mínimo 89 adyacentes al canal de conducción 87 modulará el número medio de electrones o cargas negativas en el canal de conducción, puesto que las cargas negativas se repelen entre sí. Una barrera razonable para electrones almacenados en los puntos de potencial mínimo 89 puede ser de hasta 0,5 eV.

A continuación se hace referencia a las Figuras 31-32, que ilustran un modelo de dispositivo de almacenamiento basado en elementos capacitivos. Los condensadores C1 y C2 representan las capacidades de óxido de puerta sobre un punto de potencial mínimo 89 y el canal de conducción 87. Los condensadores C4 y C5 representan las capacidades de semiconductor de las regiones de empobrecimiento por detrás del punto de potencial mínimo 89 y el canal de conducción 87. El condensador C3 representa la capacidad de semiconductor de la región de barrera, por ejemplo la región de barrera A de la Figura 28, entre el punto de potencial mínimo 89 y el canal de conducción 87. El número de electrones almacenados en el punto de potencial mínimo 89 viene representado por la carga negativa neta en la superficie, ns (Figura 32), y el número de electrones almacenados en el canal de conducción 87 viene representado por la carga negativa neta en la superficie, nch (Figura 32). La estructura completa, circundada por la línea exterior L (Figura 32), debe tener una carga neutra, se debe aplicar la conservación de carga, y se deben tener

en cuenta todas las cargas en este modelo de capacidad. Debido al acoplamiento entre el número de electrones en el canal de conducción 87, nch, y el número de electrones en el punto de potencial mínimo 89, ns, a través del condensador C3, el número de electrones en el canal de conducción 87 viene modulado por el número de electrones en el punto de potencial mínimo 89. Una mayor carga negativa en el punto de potencial mínimo 89 reducirá el número de electrones en el canal de conducción 87, modulando así la conductividad del canal de conducción 87.

A efectos ilustrativos, considérese que el canal de conducción 87 tiene una anchura W (Figura 24) de aproximadamente 100 Å y una longitud L (Figura 24) de aproximadamente 1.000 Å, y que los puntos de potencial mínimo 89 tienen aproximadamente la mitad del área del canal de conducción 87, es decir aproximadamente 200 Å por 200 Å, y están separados con respecto al canal de conducción 87 por una barrera de potencial que tiene una anchura W<sub>2</sub> (Figura 24) de aproximadamente 100 Å. La capacidad de óxido de puerta es aproximadamente 3,2x10<sup>-7</sup> F/cm² y con el área del canal de conducción de 10<sup>-11</sup> cm², esto proporciona una capacidad de puerta sobre el canal de conducción de aproximadamente 3,2 aF. La capacidad de óxido de puerta sobre el punto de potencial mínimo 89 es aproximadamente la mitad del valor de la capacidad de puerta sobre el canal de conducción, o aproximadamente 1,6 aF. Si se coloca una puerta sobre estas regiones, el voltaje de umbral en estas regiones es VT y el exceso del voltaje de puerta con respecto al voltaje de umbral es VGS – VTD = 0,1 V, entonces el canal de conducción tendrá una carga de aproximadamente 3,2x10<sup>-19</sup> C, o, por término medio, almacenará 2 electrones. Los puntos de potencial mínimo tienen aproximadamente la mitad de la capacidad, de manera que con un voltaje de puerta de 0,1 V por encima del voltaje de umbral, tendrán una carga de aproximadamente 1,6x10<sup>-19</sup> C, o, por término medio, cada uno de ellos almacenará 1 electrón.

Considerando que el número mínimo medio de electrones en el canal de conducción 87 es dos, y que la relación del canal de conducción es W/L = 1/10, entonces con un exceso del voltaje de puerta por encima del voltaje umbral de 0,1 V, la conductividad del canal de conducción 87 vendrá dada por la siguiente fórmula:

IDS/VDS =  $(\mu Co)$  (W/L) (VGS - VTD) =  $(100 \mu A/V^2)$  (1/10)

$(0,1) = 1 \mu S$ , donde

10

15

20

25

30

40

45

55

IDS = corriente de drenaje en el canal de conducción;

VDS = voltaje;

W = anchura del canal de conducción;

L = longitud del canal de conducción;

VGS = voltaje de puerta; y

35 VTD = voltaje de umbral del modo de empobrecimiento.

Cuando los dispositivos de DRAM de un solo electrón están dispuestos en una matriz, por ejemplo como dispositivos de memoria flash, entonces se lee la conductividad del canal de conducción 87. El resultado demuestra que cambios significativos de la conductividad, del orden de fracciones de micro siemens (µS), se verán afectados por la ausencia o presencia de electrones en los puntos de potencial mínimo 89.

Adicionalmente, se pueden llevar a cabo otras etapas para crear una celda de memoria funcional en el sustrato 50. De este modo, se podrían formar capas de interconexión multinivel adicionales y capas dieléctricas asociadas para crear trayectos eléctricos operativos desde la estructura de puerta de transistor 90 (Figura 27) en el sustrato 50, adyacente a las regiones de fuente/drenador 93, 95 y el canal de conducción 87 y los puntos de potencial mínimo 89. El sustrato que contiene el canal de conducción 87 y los dos puntos de potencial mínimo 89 se puede usar en la formación de muchos tipos de memorias de un solo electrón, por ejemplo, DRAMs, procesadores, etcétera.

En la Figura 33 se ilustra esquemáticamente una matriz de memoria de DRAM que comprende transistores 99 que incluyen canales de conducción y regiones de potencial mínimo, tales como el canal de conducción 87 y los puntos de potencial mínimo 89 formados mediante el método de la presente invención. Cada transistor 99 de la matriz se ilustra de manera que incluye dos puntos, para los dos puntos de potencial mínimo 89.

En la Figura 34 se ilustra un sistema basado en un procesador 400 típico, que incluye un circuito de memoria 448, por ejemplo una DRAM. Un sistema de procesador, tal como un sistema de ordenador, comprende en general una unidad de procesado central (CPU) 444, tal como un microprocesador, un procesador de señal digital, u otros dispositivos lógicos digitales programables, que se comunican con un dispositivo de entrada/salida (I/O) 446 a través de un bus 452. La memoria 448 se comunica con el sistema a través del bus 452.

En el caso de un sistema de ordenador, el sistema de procesador puede incluir dispositivos periféricos tales como una unidad de disco flexible 454 y una unidad de disco compacto (CD) ROM 456 que se comunican también con la CPU 444 a través del bus 452. La memoria 448, la CPU 444 u otras de las estructuras eléctricas ilustradas se pueden considerar como un circuito integrado, el cual incluye uno o más canales de conducción y puntos de potencial mínimo adyacentes de acuerdo con la invención. Si se desea, la memoria 448 se puede combinar con el procesador, por ejemplo la CPU 444, en un único circuito integrado.

La descripción y dibujos anteriores deben considerarse únicamente como ilustrativos de formas de realización ejemplificativas que materializan las características y ventajas de la presente invención. Se pueden realizar modificaciones y sustituciones en las estructuras y condiciones del proceso específicas sin apartarse del alcance de la presente invención. Por consiguiente, la invención no debe considerarse como limitada por la descripción y dibujos anteriores, sino que está limitada únicamente por el alcance de las reivindicaciones adjuntas.

#### REIVINDICACIONES

- 1. Método de fabricación de un dispositivo de memoria de almacenamiento de carga, que comprende:

- formar una máscara submicrónica mediante las etapas siguientes:

10

15

20

35

- formar un primer islote de nitruro de silicio (60) sobre un sustrato (10, 50);

- formar una capa de polisilicio (62) sobre dicho primer islote de nitruro de silicio (60);

- atacar químicamente el material de polisilicio de dicha capa de polisilicio para formar cuatro estructuras de polisilicio (63) en las paredes laterales de dicho primer islote de nitruro de silicio (60);

- eliminar dicho primer islote de nitruro de silicio (60); y

- atacar químicamente tres de dichas cuatro estructuras de polisilicio (63) para dejar una primera estructura de polisilicio que comprende una tira de polisilicio (65) sobre el sustrato;

- formar un segundo islote de nitruro de silicio (72) en el sustrato, presentando el segundo islote de nitruro de silicio (72) una pared lateral (73) que interseca dicha tira de polisilicio (65);

- formar una segunda capa de polisilicio (74) sobre dicho segundo islote de nitruro de silicio (72);

- atacar químicamente el material de polisilicio de dicha segunda capa de polisilicio (74) para formar unas 25 estructuras de polisilicio (75) situadas en dicha pared lateral de dicho segundo islote de nitruro de silicio (72);

- atacar químicamente además las estructuras de polisilicio (75) formadas en la pared lateral del segundo islote de nitruro de silicio para dejar un punto de polisilicio (85) en ambas caras de dicha tira de polisilicio; y

- 30 eliminar dicho segundo islote de nitruro de silicio (72) para formar dicha máscara submicrónica;

- dopar dicho sustrato (10, 50) para formar unas regiones dopadas adyacentes a unas regiones no dopadas, estando por lo menos una de dichas regiones no dopadas situada debajo de dicha por lo menos una tira de polisilicio (65), y estando por lo menos dos de dichas regiones no dopadas situadas debajo de dichos puntos de polisilicio (85),

- en el que dicha por lo menos una de dichas regiones no dopadas situada debajo de dicha por lo menos una tira de polisilicio (65) forma un canal de conducción (87) entre una región de fuente y una región de drenaje de dicho sustrato (10, 50); y

- en el que dichas por lo menos dos de dichas regiones no dopadas situadas debajo de dichos puntos de polisilicio (85) forman por lo menos dos regiones de potencial mínimo (89) situadas entre la región de fuente y una región de drenaje de dicho sustrato (10, 50);

- 45 en el que dicho canal de conducción (87) almacena por lo menos un portador de carga; y

- en el que cada una de dichas por lo menos dos regiones de potencial mínimo (89) almacena por lo menos un portador de carga;

- comprendiendo el método además eliminar la tira de polisilicio (65) y los puntos de polisilicio (85), y formando un óxido de puerta y un apilamiento de puerta (90) sobre el canal de conducción (87), dichas por lo menos dos regiones de potencial mínimo y las regiones de fuente y drenaje (93, 95).

- 2. Método según la reivindicación 1, en el que dicho canal de conducción (87) tiene una anchura de 10 nanómetros y una longitud de 100 nanómetros.

- 3. Método según la reivindicación 1, en el que cada una de dichas por lo menos dos regiones de potencial mínimo (89) tiene una anchura de 20 nanómetros y una longitud de 20 nanómetros.

FIG. 1

FIG. 2

FIG. 3

FIG. 5

FIG. 6

.

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 19

FIG. 21

IMPLANTACIÓN DE B

FIG. 23

FIG. 24

FIG. 26

FIG. 28

FIG. 29

FIG. 31

FIG. 32

FIG. 33

FIG. 34