## OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 527 937

51 Int. Cl.:

G06F 12/00 (2006.01) G06F 11/00 (2006.01) G06F 9/30 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- (96) Fecha de presentación y número de la solicitud europea: 12.07.2004 E 10191073 (5)

(97) Fecha y número de publicación de la concesión europea: 26.11.2014 EP 2284709

- (54) Título: Procesador programable y método con operaciones amplias

- (30) Prioridad:

10.07.2003 US 616303

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 02.02.2015

(73) Titular/es:

MICROUNITY SYSTEMS ENGINEERING, INC. (100.0%)

4 Main Street, Suite 100

Los Altos, CA 94022, US

(72) Inventor/es:

HANSEN, CRAIG; MOUSSOURIS, JOHN y MASSALIN, ALEXIA

(74) Agente/Representante:

PONTI SALES, Adelaida

## **DESCRIPCIÓN**

Procesador programable y método con operaciones amplias

#### 5 Campo de la invención

[0001] La presente invención se refiere a arquitecturas de procesador de propósito general, y en particular se refiere a arquitecturas de operandos amplios.

#### 10 ANTECEDENTES DE LA INVENCIÓN

[0002] Los productos de comunicaciones requieren un mayor rendimiento computacional para procesar señales digitales en software en tiempo real. Los incrementos del rendimiento han pasado por mejoras en la tecnología de procesos y por mejoras en el diseño de los microprocesadores. Un mayor paralelismo, mayores frecuencias de reloj, mayores densidades, acoplados con herramientas de diseño mejoradas y compiladores los han hecho más prácticos. Sin embargo, muchas de estas mejoras suponen una sobrecarga adicional en memoria y latencia, debido a la ausencia del ancho de banda necesario que está estrechamente acoplado con las unidades computacionales.

[0003] El nivel de rendimiento de un procesador, y en particular de un procesador de propósito general, se puede estimar a partir de varios de una serie de factores independientes: frecuencia de reloj, puertas por reloj, número de operandos, anchura del camino de operandos y de datos, y división del camino de operandos y de datos. La frecuencia de reloj está influida en gran parte por la elección de la tecnología lógica y de circuitos, pero está influida asimismo por el número de puertas por reloj. Las puertas por reloj consisten en cuántas puertas en una segmentación pueden cambiar de estado en un solo ciclo de reloj. Esto se puede reducir al introducir cerrojos en el camino de datos: cuando se reduce el número de puertas entre cerrojos, es posible un reloj más rápido. Sin embargo, los cerrojos adicionales producen una mayor longitud de segmentación, y por lo tanto tienen el coste de una mayor latencia de instrucciones. El número de operandos es sencillo; por ejemplo, sumando con técnicas de ahorro de acarreo, se pueden sumar juntos tres valores con poco más retardo del necesario para sumar dos valores. La anchura del camino de operandos y de datos define cuántos datos se pueden procesar a la vez; caminos de datos más amplios pueden realizar funciones más complejas, pero en general esto supone un mayor coste de implementación. La división de los caminos de operandos y de datos se refiere a la utilización eficiente del camino de datos cuando se aumenta la anchura, con el objetivo de mantener sustancialmente el uso máximo.

[0004] La última división del camino de factores, operandos y datos se trata extensivamente en las patentes U.S.A. asignadas en común con la presente, de números 5 742 840, 5 794 060, 5 794 061, 5 809 321 y 5 822 603, que describen sistemas y métodos para mejorar la utilización de un procesador de propósito general añadiendo clases de instrucciones. Estas clases de instrucciones utilizan los contenidos de registros de propósito general como fuentes de caminos de datos, dividen los operandos en símbolos de un tamaño especificado, realizan operaciones en paralelo, concatenan los resultados y colocan los resultados concatenados en un registro de propósito general. 40 Éstas patentes, la totalidad de las cuales están asignadas al mismo cesionario de la presente invención, muestran un microprocesador de propósito general que se ha optimizado para procesar y transmitir flujos de datos multimedia mediante un paralelismo significativo.

[0005] Si bien las patentes anteriores han ofrecido mejoras significativas en la utilización y el rendimiento de un 45 microprocesador de propósito general, en particular para manejar comunicaciones de banda ancha tales como flujos de datos multimedia, son posibles otras mejoras.

[0006] Muchos procesadores de propósito general tienen registros generales para almacenar operandos para instrucciones, haciéndose coincidir la anchura del registro con el tamaño del camino de datos. Los diseños de los procesadores limitan, en general, el número de registros accesibles por instrucción, debido a que el hardware para acceder a estos registros es relativamente costoso en términos de energía y superficie. Mientras que el número de registros accesibles varía entre los diseños de procesadores, a menudo está limitado a dos, tres o cuatro registros por instrucción cuando dichas instrucciones están diseñadas para funcionar en un solo ciclo de reloj del procesador o en un solo flujo de segmentación. Algunos procesadores, tales como el Motorola 68000, tienen instrucciones para guardar y reestablecer un número ilimitado de registros, pero requieren múltiples ciclos para realizar dicha instrucción.

[0007] El Motorola 68000 intenta asimismo superar un camino de datos estrecho combinado con un archivo de registros estrecho tomando múltiples ciclos o flujos de segmentación para realizar una instrucción, y emulando de 60 ese modo un camino de datos más amplio. Sin embargo, dichas técnicas de precisión múltiple ofrecen solamente una mejora marginal, en vista de los ciclos de reloj adicionales requeridos. Por lo tanto, la anchura y el número accesible de los registros de propósito general limita fundamentalmente la cantidad de procesamiento que puede ser realizado mediante una única instrucción en una máquina basada en registros.

65 **[0008]** Los procesadores existentes pueden proporcionar instrucciones que aceptan operandos, para las que se leen uno o varios operandos desde un sistema de memoria de un procesador de propósito general. Sin embargo,

dado que estos operandos de memoria están especificados generalmente mediante operandos de registro, y el camino de datos del sistema de memoria no es más amplio que el camino de datos del procesador, no se mejora la anchura y el número accesible de operandos de propósito general por ciclo de instrucción o flujo de segmentación.

5 [0009] El número de operandos de registro de propósito general accesibles por instrucción está limitado generalmente por la complejidad lógica y el tamaño de las instrucciones. Por ejemplo, se podrían implementar ciertas funciones deseables pero complejas, especificando un número mayor de registros de propósito general, pero habría que haber añadido una cantidad sustancial de lógica adicional a un diseño convencional, para permitir la lectura y omisión simultáneas de los valores de registro. Si bien en algunos diseños de la técnica anterior se han utilizado registros dedicados para aumentar el número o el tamaño de resultados u operandos fuente, instrucciones explícitas cargan o almacenan valores en estos registros dedicados, y se requieren instrucciones adicionales para guardar y reestablecer estos registros tras un cambio de contexto del procesador.

[0010] El tamaño de un resultado de la unidad de ejecución puede estar limitado al de un registro general, de 15 manera que no se requiere un almacenamiento dedicado u otro especial para el resultado. Especificar un gran número de registros de propósito general como un resultado, requeriría análogamente añadir una cantidad sustancial de lógica adicional a un diseño convencional, para permitir la escritura y omisión simultáneas de los valores de registro.

20 [0011] Cuando el tamaño de un resultado de la unidad de ejecución está limitado, éste puede limitar la cantidad de computación que puede ser gestionada razonablemente por una sola instrucción. Como consecuencia, es necesario implementar los algoritmos como una serie de etapas de una sola instrucción, en las que todos los resultados intermedios se pueden representar dentro de los límites. Eliminando este límite, se pueden desarrollar conjuntos de instrucciones en los que un componente mayor de un algoritmo se implementa como una sola instrucción, y la representación de los resultados intermedios deja de estar limitada en tamaño. Además, no es necesario que algunos de estos resultados intermedios se retengan tras la finalización del componente mayor de un algoritmo, de manera que un procesador liberado de estas limitaciones puede mejorar el rendimiento y reducir la potencia de funcionamiento al no almacenar y recuperar estos resultados desde el archivo de registros generales. Cuando los resultados intermedios no se retienen en el archivo de registros generales, los conjuntos de instrucciones del 30 procesador y los algoritmos implementados tampoco están limitados por el tamaño del archivo de registros generales.

[0012] Por lo tanto, ha existido la necesidad de un sistema de procesador que pueda manejar eficientemente operandos y resultados de mayor anchura que el sistema de memoria o cualquier registro de propósito general accesible. Existe asimismo la necesidad de un sistema de procesador que pueda manejar eficientemente operandos y resultados de mayor tamaño global que todo el archivo de registros generales.

[0013] El documento WO 00/23875 describe un procesador de propósito general que puede ejecutar una instrucción de matriz de multiplicación amplia que toma de un registro general una dirección para recuperar de la 40 memoria un operando grande (amplio), recuperar de un registro general un segundo operando, realizar un grupo de operaciones sobre bits divididos en los operandos, y concatenar juntos los resultados, colocando el resultado en un registro general.

[0014] Un documento de Pitsianis NP y otros, titulado "High-performance FFT implementation on the BOPS ManArray parallel DSP", publicado en los documentos de Advanced Signal Processing Algorithms, Architectures, and Implementations 1X, 19 al 21 de julio de 1999, conferencia SPIE, volumen 3807, páginas 164 a 171, describe una implementación de alto rendimiento de un algoritmo de FFT que, para poner de manifiesto el paralelismo inherente a un algoritmo FFT, utiliza una factorización de la matriz DFT en productos de Kronecker, permutación y matrices diagonales.

**[0015]** La patente U.S.A. asignada en común y relacionada, número 6 295 599, describe en detalle un método y un sistema para mejorar el rendimiento de procesadores de propósito general expandiendo por lo menos un operando fuente de hasta una anchura mayor que cualquiera de la anchura del registro de propósito general o la anchura del camino de datos. Se pueden conseguir mejoras adicionales en el rendimiento mediante

## RESUMEN DE LA INVENCIÓN

**[0016]** Un aspecto de la invención da a conocer un procesador tal como el definido en la reivindicación 1. Un segundo aspecto de la invención da a conocer un método tal como el definido en la reivindicación 25. Las 60 realizaciones de la invención se exponen en las reivindicaciones dependientes.

## BREVE DESCRIPCIÓN DE LOS DIBUJOS

#### [0017]

65

50

55

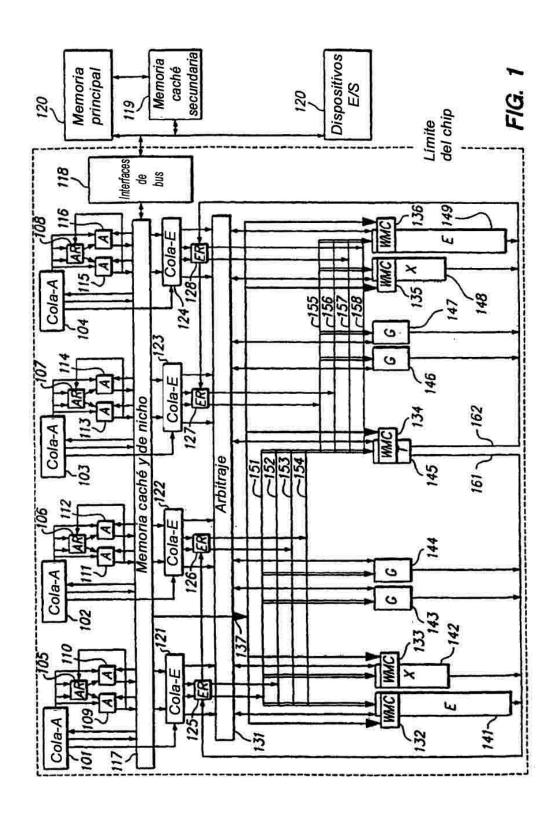

La figura 1 es un diagrama a nivel de sistema que muestra los bloques funcionales de un procesador de propósito

general.

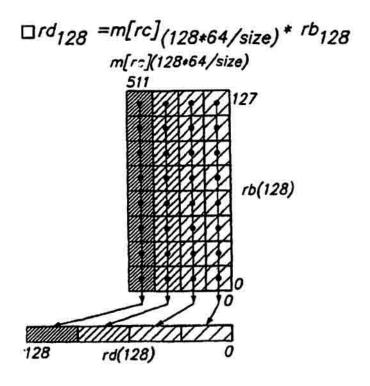

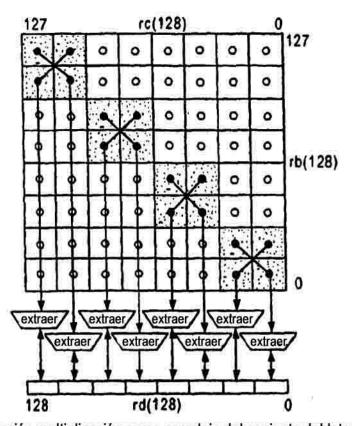

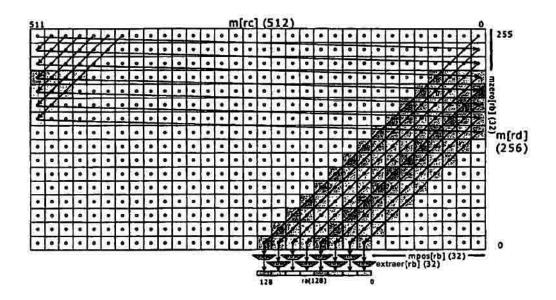

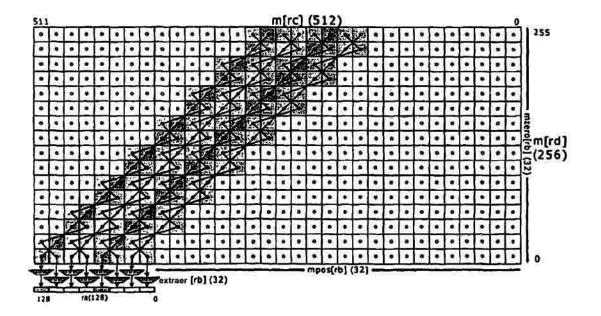

La figura 2 es una representación matricial de una multiplicación de matriz amplia.

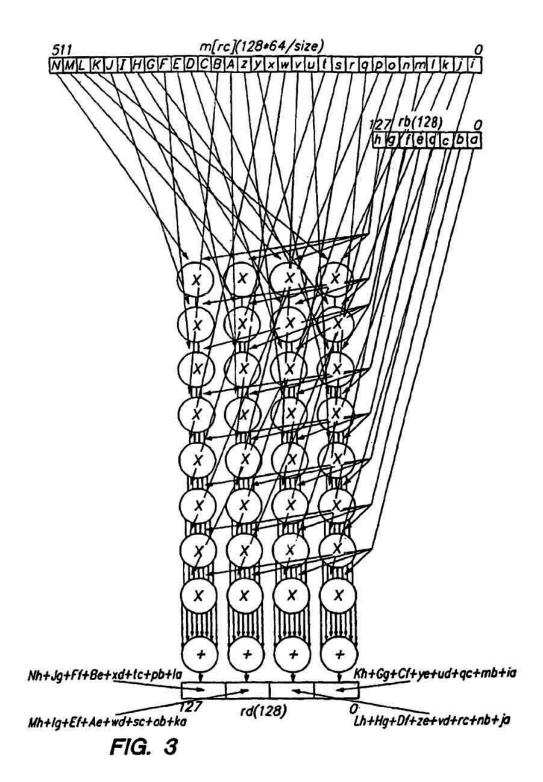

5 La figura 3 es otra representación de una multiplicación de matriz amplia.

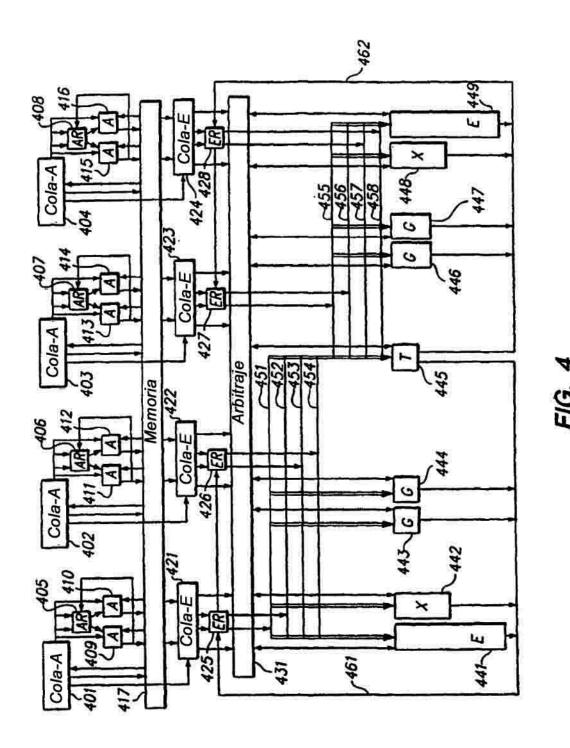

La figura 4 es un diagrama a nivel de sistema que muestra los bloques funcionales de un sistema que incorpora un procesador de multihilos simultáneos y acceso desacoplado de la ejecución.

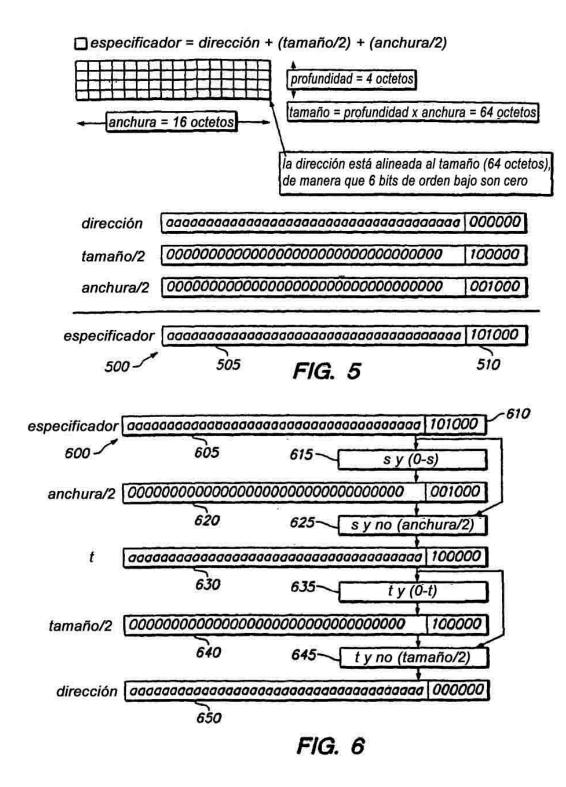

10 La figura 5 muestra un operando amplio.

La figura 6 muestra un enfoque para la descodificación del especificador.

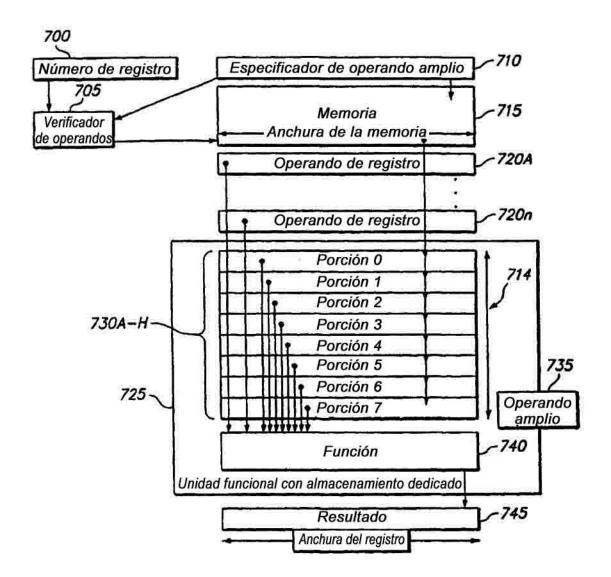

La figura 7 muestra un bloque operacional a partir de una unidad de función amplia.

15

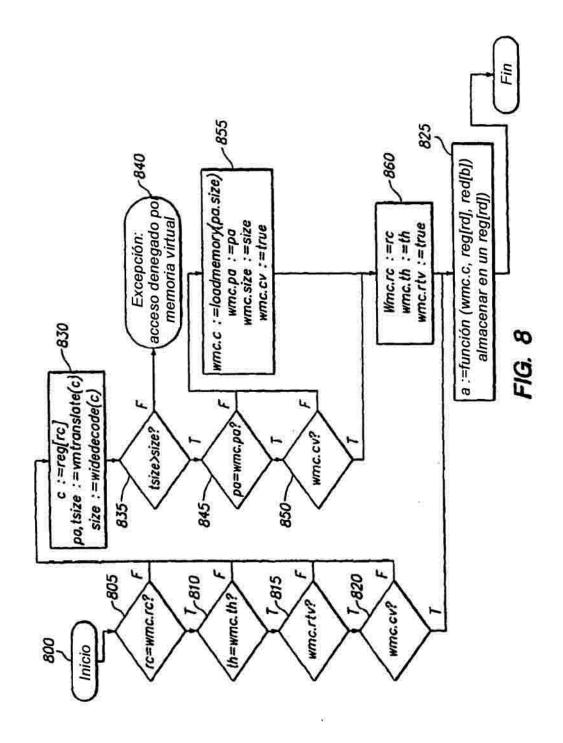

La figura 8 muestra, en forma de diagrama de flujo, la función de control de microcaché amplia.

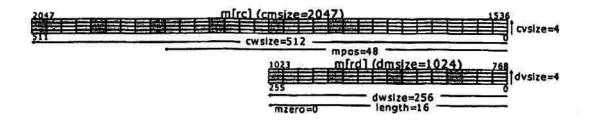

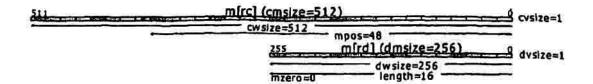

La figura 9 nuestra estructuras de datos de microcaché amplia.

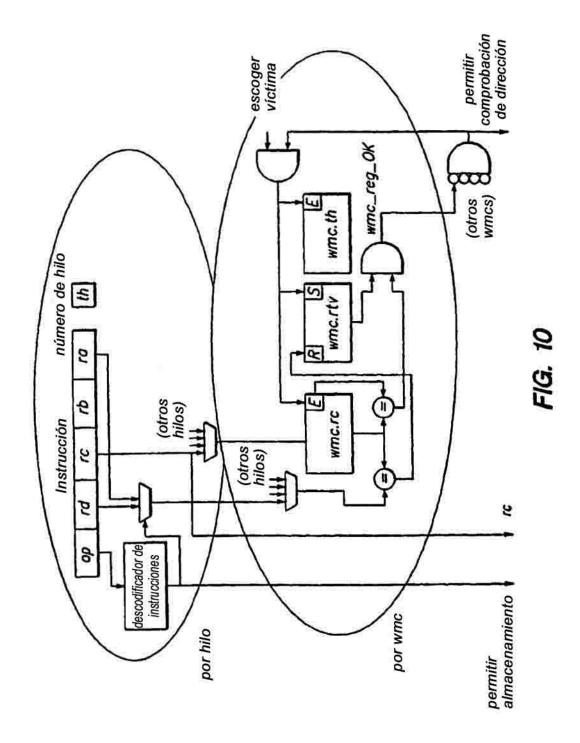

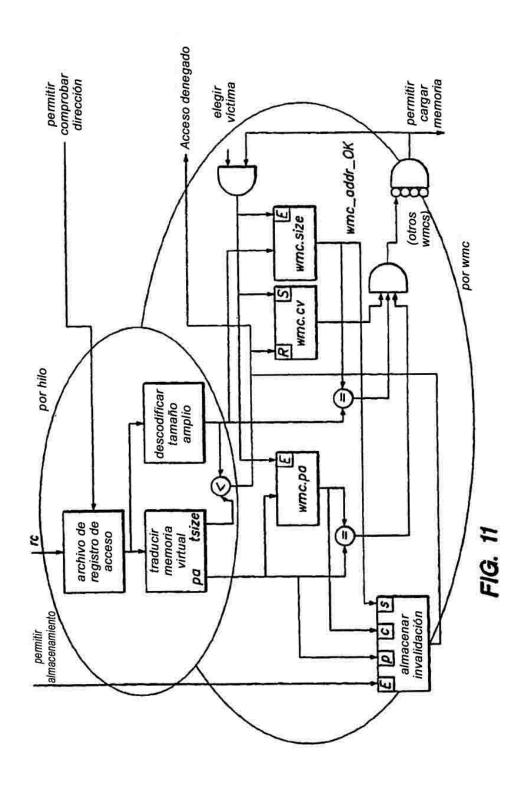

20 Las figuras 10 y 11 muestran un control de microcaché amplia.

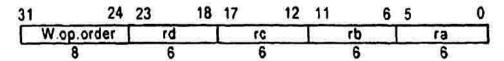

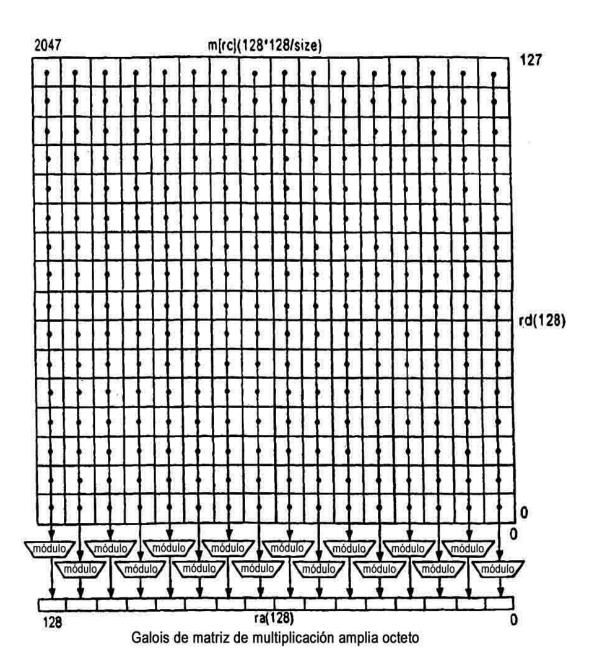

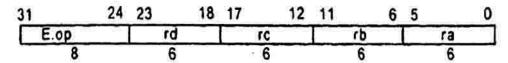

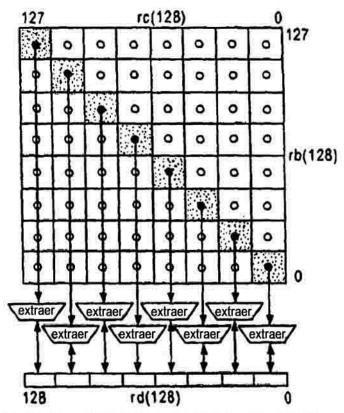

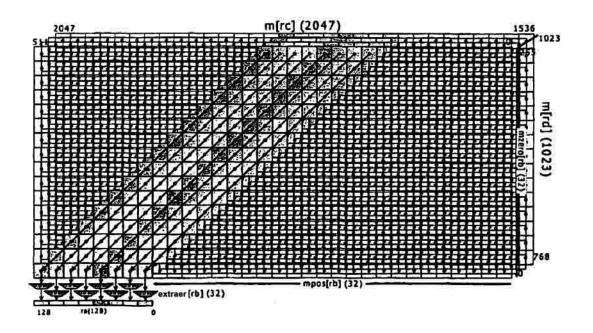

Las figuras 12A a 12D muestran una instrucción de Galois de matriz de multiplicación amplia.

Las figuras 13A a 13G muestran una instrucción de extracción de conjunto in situ.

25

Las figuras 14A a 14J muestran una instrucción de extracción de conjunto.

Las figuras 15A a 15C muestran una instrucción booleana de grupo.

30 Las figuras 16A a 16C muestran instrucciones de suma de grupo.

Las figuras 17A a 17C muestran instrucciones de establecimiento de grupo e instrucciones de resta del grupo.

Las figuras 18A a 18C muestran instrucciones de convolución de conjunto, división de conjunto, multiplicación de 35 conjunto y suma de multiplicaciones de conjunto.

La figura 19 muestra funciones a modo de ejemplo que se definen para su utilización dentro de las definiciones detalladas de instrucciones, en otras secciones.

40 Las figuras 20A a 20C muestran instrucciones suma con coma flotante de conjunto, división con coma flotante de conjunto y multiplicación con coma flotante de conjunto.

Las figuras 21A a 21C muestran instrucciones de resta con coma flotante de conjunto.

45 Las figuras 22A a 22D muestran instrucciones de compresión, expansión, rotación y desplazamiento de barras cruzadas.

Las figuras 23A a 23D muestran instrucciones de extracción.

50 Las figuras 24A a 24B muestran instrucciones de Galois de solución amplia.

Las figuras 25A a 25B muestran instrucciones de rebanada de transformada amplia, de acuerdo con una realización a modo de ejemplo de la presente invención.

55 Las figuras 26A a 26K muestran instrucciones de extracción convolución amplia.

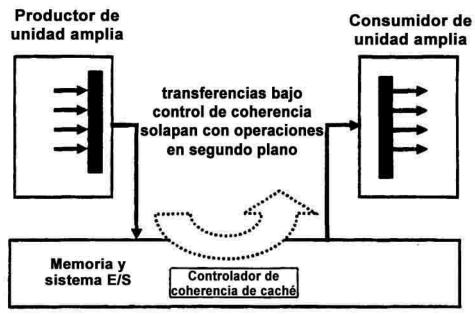

La figura 27 muestra transferencias entre memorias de operandos amplios.

## **DESCRIPCIÓN DETALLADA DE LA INVENCIÓN**

60

## Distribución del procesador

[0018] Haciendo referencia en primer lugar a la figura 1, se muestra en la misma un procesador de propósito general en forma de diagrama de bloques. En la figura 1, se muestran cuatro copias de una unidad de acceso, cada una con una cola de recuperación de instrucciones de acceso cola-A 101 a 104. Cada cola de recuperación de instrucciones de acceso, cola-A 101 a 104 está acoplada a un archivo de registros de acceso AR 105 a 108, estando

acoplados cada uno de estos a dos unidades funcionales de acceso A 109 a 116. En una realización habitual, cada hilo del procesador puede tener del orden de sesenta y cuatro registros de propósito general (por ejemplo, los AR 105 a 108 y ER 125 a 128). Las unidades de acceso funcionan independientemente para cuatro hilos simultáneos de ejecución, y cada una calcula el flujo de control del programa realizando instrucciones aritméticas y de ramificación, y accede a la memoria realizando instrucciones de carga y almacenamiento. Estas unidades de acceso proporcionan asimismo especificadores de operandos amplios para instrucciones de operandos amplios. Estas ocho unidades funcionales de acceso A 109 a 116 producen resultados para archivos de registros de acceso AR 105 a 108, y direcciones de memoria para un sistema de memoria compartido 117 a 120.

10 [0019] En una realización, la jerarquía de memoria incluye memoria de datos e instrucciones en chip, cachés de instrucciones y datos, una instalación de memoria virtual e interfaces a dispositivos externos. En la figura 1, el sistema de memoria se compone de una memoria combinada caché y de nicho 117, una interfaz de bus externo 118, y, externamente al dispositivo, una caché secundaria 119 y un sistema de memoria principal con dispositivos E/S 120. Los contenidos de memoria recuperados del sistema de memoria 117 a 120 se combinan con instrucciones de ejecución no realizadas por la unidad de acceso, y se introducen en las cuatro colas de instrucción de ejecución colas-E 121 a 124. Para instrucciones amplias, los contenidos de memoria recuperados del sistema de memoria 117 a 120 se proporcionan asimismo a microcachés de operandos amplios 132 a 136 mediante el bus 137. Los datos de memoria e instrucciones de la cola-E 121 a 124 se presentan a archivos de registros de ejecución 125 a 128, que recuperan operandos fuente de archivo de registros de ejecución. Las instrucciones se acoplan a la unidad de arbitraje de las unidades de ejecución Arbitraje 131, que selecciona qué instrucciones de los cuatro hilos se tienen que encaminar a las unidades funcionales de ejecución disponibles E 141 y 149, X 142 y 148, G 143 a 144 y 146 a 147 y T 145. Cada una de las unidades funcionales de ejecución E 141 y 149, las unidades funcionales de ejecución X 142 y 148 y la unidades funcionales de ejecución T 145 contiene una microcaché de operandos amplios 132 a 136, cada una de las cuales está acoplada al sistema de memoria 117 mediante el bus 137.

[0020] Las unidades funcionales de ejecución G 143 a 144 y 146 a 147 son unidades aritméticas y lógicas de grupos que realizan instrucciones aritméticas y lógicas simples, incluyendo operaciones de grupos en las que los operandos de fuentes y de resultado representan un grupo de valores de un tamaño de símbolo especificado, que se dividen y se manejan por separado, concatenándose juntos los resultados. En una realización preferida actualmente, 30 el camino de datos tiene 128 bits de amplitud, aunque la presente invención no desea limitarse a ningún tamaño específico del camino de datos.

[0021] Las unidades funcionales de ejecución X 142 y 148 son unidades de conmutador de barras cruzadas que realizan instrucciones de conmutación de barras cruzadas. Las unidades de conmutación de barras cruzadas 142 y 148 realizan operaciones de manipulación de datos en el flujo de datos proporcionado sobre los buses de operandos fuente del camino de datos 151 a 158, incluyendo transacciones, aleatorizaciones, desplazamientos, expansiones, compresiones, mezclas, permutaciones e inversiones, más las operaciones amplias descritas en adelante. En un elemento clave de un primer aspecto de la invención, por lo menos una de dichas operaciones será expandida a una anchura mayor que la anchura del camino de registros generales y de datos.

[0022] Las unidades funcionales de ejecución E 141 y 149 son unidades de conjunto que realizan instrucciones de conjunto utilizando un multiplicador matricial grande, que incluye multiplicación de grupos o de vectores y multiplicación de matrices, de operandos divididos desde los buses 151 a 158 de operandos fuente del camino de datos, y tratados como valores enteros, de coma flotante, polinómicos o de campos de Galois. Las instrucciones de multiplicación de matrices y otras operaciones utilizan un operando amplio cargado en la microcaché de operandos amplios 132 y 136.

**[0023]** La unidad funcional de ejecución T 145 es una unidad de traducción que realiza operaciones de búsqueda en tablas, sobre un grupo de operandos divididos desde un operando de registro, y concatena el resultado. La 50 instrucción de traducción amplia utiliza un operando amplio cargado en la microcaché de operandos amplios 134.

[0024] Las unidades funcionales de ejecución E 141, 149, las unidades funcionales de ejecución X 142, 148 y la unidad funcional de ejecución T contienen, cada una, un almacenamiento dedicado para permitir el almacenamiento de operandos fuente que incluyen operandos amplios, tal como se describe más adelante. El almacenamiento dedicado 132 a 136, que se puede considerar como una microcaché amplia, tiene habitualmente una anchura que es un múltiplo de la anchura de los operandos del camino de datos relacionados con los buses 151 a 158 de operandos fuente del camino de datos. De este modo, si la anchura del camino de datos 151 a 158 es de 128 bits, el almacenamiento dedicado 132 a 136 puede tener una anchura de 256, 512, 1024 ó 2048 bits. Los operandos que utilizan toda la anchura del almacenamiento dedicado se denominan en el presente documento operandos amplios, aunque no es necesario en todos los casos que un operando amplio utilice íntegramente la anchura del almacenamiento dedicado; es suficiente que el operando amplio utilice una parte mayor que la anchura del datos de memoria de la salida del sistema de memoria a 117 a 120 y del camino de datos de la unidad funcional de la entrada de las unidades funcionales de ejecución 141 a 149, aunque no necesariamente mayor que la anchura de los dos combinados. Debido a que la anchura del almacenamiento dedicado 132 a 136 es mayor que la anchura del bus 137 de operandos de memoria, se cargan secuencialmente partes de los operandos amplios en el almacenamiento dedicado 132 a 136. Sin embargo, una vez cargados, a continuación los operandos amplios

pueden ser utilizados sustancialmente al mismo tiempo. Se puede observar que las unidades funcionales 141 a 149 y los registros de ejecución asociados 125 a 128 forman una unidad funcional de datos, cuyos elementos exactos pueden variar con la implementación.

5 [0025] Los operandos fuente del archivo de registros de ejecución 125 a 128 se acoplan a las unidades de ejecución 141 a 145 utilizando buses 151 a 154 de operandos fuente, y a las unidades de ejecución 145 a 149 utilizando buses 155 a 158 de operandos fuente. Los operandos resultado de unidades de función, procedentes de las unidades de ejecución 141 a 145, se acoplan al archivo de registros de ejecución ER 125 a 128 utilizando el bus de resultados 161, y los operandos de resultado de unidades de función, procedentes de las unidades de ejecución 145 a 149, se acoplan al archivo de registros de ejecución utilizando el bus de resultados 162.

#### Matriz de multiplicación amplia

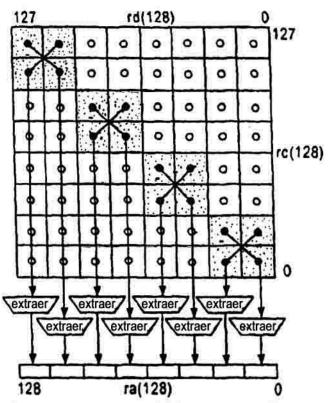

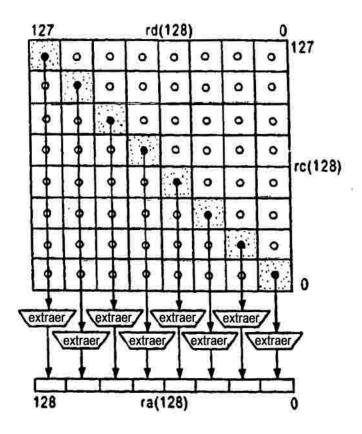

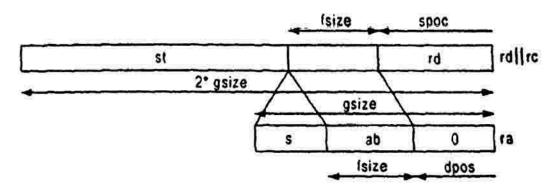

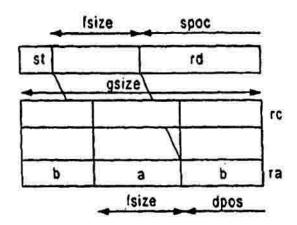

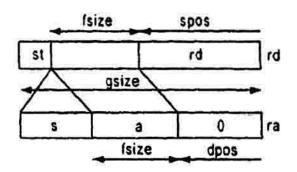

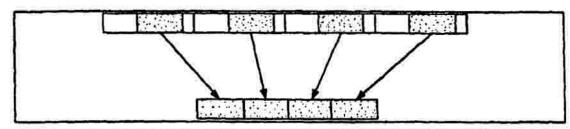

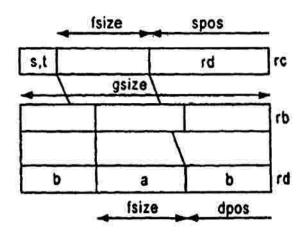

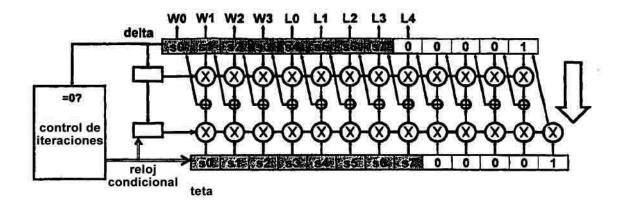

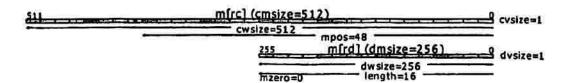

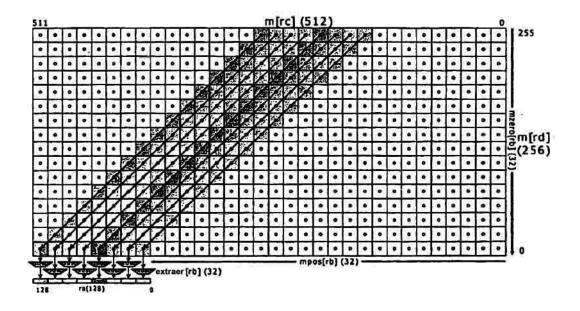

[0026] Los operandos amplios proporcionan la capacidad de ejecutar instrucciones complejas, tales como la instrucción de matriz de multiplicación amplia mostrada en la figura 2, que se puede apreciar asimismo en una forma alternativa en la figura 3. Tal como se puede apreciar por las figuras 2 y 3, un operando amplio permite, por ejemplo, la multiplicación matricial de varias formas y tamaños que exceden la anchura del camino de datos. El ejemplo de la figura 2 involucra una matriz especificada por el registro rc que tiene 128\*64/tamaño bits (512 bits en este ejemplo), multiplicada por un vector contenido en el registro rb que tiene 128 bits, para proporcionar un 20 resultado, colocado en el registro rd, de 128 bits.

[0027] La notación utilizada en la figura 2 y siguientes figuras similares muestra una multiplicación como un área sombreada en la intersección de dos operandos proyectados en las dimensiones horizontal y vertical. Un nodo de sumación se muestra como un segmento de línea que conecta puntos en negrita en la posición de los productos de multiplicador que se suman. Los productos que se restan en el nodo de sumación se indican con un símbolo menos en el interior del área sombreada.

[0028] Cuando la instrucción aplica a valores de coma flotante, las multiplicaciones y las sumaciones mostradas son multiplicaciones y sumaciones de coma flotante. Una realización a modo de ejemplo puede realizar estas operaciones sin redondear los resultados intermedios, calculando por lo tanto el resultado final como si se hubiera calculado con precisión infinita, y redondeando a continuación solamente una vez.

[0029] Se puede apreciar que una realización a modo de ejemplo de los multiplicadores puede calcular el producto en modo de ahorro de acarreo, y puede codificar el multiplicador rb utilizando codificación de Booth para minimizar el área y el retardo del circuito. Se puede apreciar que una realización a modo de ejemplo de dichos nodos de sumación puede llevar a cabo la sumación de los productos en cualquier orden, prestando especial atención a minimizar el retardo de computación, tal como realizando las sumas en un árbol binario o de una base mayor, y puede utilizar sumadores con ahorro de acarreo para realizar la suma a efectos de minimizar el retardo de la sumación. Se puede apreciar asimismo que una realización a modo de ejemplo puede llevar a cabo la sumación utilizando la precisión intermedia suficiente para que no se produzcan desbordamientos de punto fijo o de coma flotante en los resultados intermedios.

[0030] Se puede utilizar una comparación de las figuras 2 y 3 para aclarar la relación entre la notación utilizada en la figura 2 y la notación esquemática más convencional de la figura 3, dado que se muestra la misma operación en 45 estas dos figuras.

#### Operando amplio

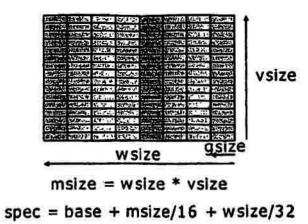

[0031] Los operandos que son sustancialmente mayores que la anchura del camino de datos del procesador se proporcionan utilizando el registro de propósito general para especificar un especificador de memoria desde el que se puede leer, en el almacenamiento dedicado, datos de más de una, y en algunas realizaciones de varias, anchuras del camino de datos. El especificador de memoria incluye habitualmente la dirección de memoria junto con el tamaño y la forma de la matriz de datos sobre la que se está operando. El especificador de memoria o el especificador del operando amplio se pueden apreciar mejor en la figura 5, en la que se ve que un especificador 500 es una dirección, más un campo representativo del tamaño/2 y un campo adicional representativo de la anchura/2, donde el tamaño es el producto de la profundidad por la anchura de los datos. La dirección está alineada a un tamaño específico, por ejemplo sesenta y cuatro octetos, de manera que una serie de los bits de orden bajo (por ejemplo, seis bits) son cero. De este modo, se puede ver que el especificador 500 comprende un primer campo 505 para la dirección, más dos índices de campo 510 dentro de los seis bits de orden bajo, para indicar tamaño y anchura.

## Descodificación del especificador

[0032] La descodificación del especificador 500 se puede apreciar mejor en la figura 6, para un especificador dado 65 600 que se compone de un campo de dirección 605 junto con un campo 610 que comprende varios bits de orden bajo. Mediante una serie de operaciones aritméticas mostradas en las etapas 615 y 620, se desarrolla la parte del

campo 610 representativa de anchura/2. En una serie similar de etapas mostrada en 625 y 630, se descodifica el valor de t, que se puede utilizar a continuación para descodificar tanto el tamaño como la dirección. La parte del campo 610 representativa de tamaño/2 se descodifica tal como se muestra en las etapas 635 y 640, mientras que la dirección se descodifica de manera similar a las etapas 645 y 650.

#### Unidad de función amplia

[0033] La unidad de función amplia se puede apreciar mejor en la figura 7, en la que se proporciona un número de registro 700 a un verificador de operandos 705. El especificador de operandos amplios 710 comunica con el verificador de operandos 705 y asimismo con la dirección de memoria 715 que tiene una anchura de memoria definida. La dirección de memoria incluye una serie de n operandos de registro 720A, que se acumulan en una parte de almacenamiento dedicado 714 de una unidad funcional de datos 725. En la realización a modo de ejemplo mostrada en la figura 7, se puede ver que el almacenamiento dedicado 714 tiene una anchura igual a ocho anchuras del camino de datos, de tal modo que ocho porciones 730A-H del operando amplio se cargan secuencialmente en el almacenamiento dedicado para formar el operando amplio. Aunque en la figura 7 se muestran ocho porciones, la presente invención no se limita a ocho ni a ningún otro múltiplo específico de anchuras del camino de datos. Una vez que las porciones 730A-H del operando amplio se cargan secuencialmente, pueden ser utilizadas como un único operando amplio 735 por el elemento funcional 740, que puede ser cualquier elemento o elementos de la figura 1 conectados al mismo. A continuación, el resultado del operando amplio se proporciona a un registro de resultados 745, que en una realización actualmente preferida tiene la misma anchura que la anchura de la memoria.

[0034] Una vez que el operando amplio se ha cargado satisfactoriamente en el almacenamiento dedicado 714, se puede apreciar un segundo aspecto de la presente invención. La ejecución posterior de esta instrucción o de otras instrucciones similares que especifican la misma dirección de memoria, puede leer el almacenamiento dedicado para obtener el valor del operando bajo condiciones específicas que determinan si el operando de memoria ha sido modificado por instrucciones intermedias. Asumiendo que se satisfacen estas condiciones, el operando de memoria recuperado del almacenamiento dedicado se combina con uno o varios operandos de registro en la unidad funcional, produciendo un resultado. En algunas realizaciones, el tamaño del resultado está limitado al de un registro general, de manera que no se requiere un almacenamiento dedicado similar para el resultado. Sin embargo, en algunas realizaciones diferentes, el resultado puede ser un operando amplio, para mejorar adicionalmente el rendimiento.

**[0035]** Para permitir que el valor del operando amplio sea direccionado mediante instrucciones posteriores especificando la misma dirección de memoria, se tienen que comprobar y confirmar varias condiciones.

35 [0036] Estas condiciones incluyen:

45

Cada instrucción de almacenamiento de memoria comprueba la dirección de memoria frente a las direcciones de memoria registradas para el almacenamiento dedicado. Cualquier coincidencia provoca que el almacenamiento se marque como no valido, dado que una instrucción de almacenamiento de memoria dirigida a alguna dirección de 40 memoria almacenada en el almacenamiento dedicado 714 significa que se han sobrescrito datos.

**[0037]** Se registra el número de registro utilizado para direccionar el almacenamiento. Si no se ha escrito ninguna instrucción intermedia en el registro, y se utiliza el mismo registro en la instrucción posterior, el almacenamiento es válido (salvo que se haya marcado como no valido mediante la regla #1).

[0038] Si el registro ha sido modificado o se utiliza un número de registro diferente, el valor del registro se lee y se compara con la dirección registrada para el almacenamiento dedicado. Esto utiliza más recursos que #1 debido a la necesidad de recuperar los contenidos del registro, y debido a que la anchura del registro es mayor que la del propio número del registro. Si la dirección coincide, el almacenamiento es válido. El nuevo número de registro se registra 50 para el almacenamiento dedicado.

[0039] Si no se satisfacen las condiciones #2 ó #3, se utilizan los contenidos del registro para dirigirse a la memoria del procesador de propósito general y cargar el almacenamiento dedicado. Si el almacenamiento dedicado está ya totalmente cargado, es necesario descartar (sacrificar) una porción del almacenamiento dedicado para dejar espacio para el nuevo valor. A continuación se realiza la instrucción utilizando el almacenamiento dedicado recién actualizado. La dirección y el número de registro se registra para el almacenamiento dedicado.

[0040] Al comprobar las condiciones anteriores, se elimina la necesidad de guardar y restablecer el almacenamiento dedicado. Además, si se varía el contexto del procesador y el nuevo contexto no utiliza 60 instrucciones amplias que hacen referencia al mismo almacenamiento dedicado, cuando se restablece el contexto original, se permite utilizar los contenidos del almacenamiento dedicado sin refrescar el valor desde la memoria, utilizando la regla de verificación #3. Debido a que los valores en el almacenamiento dedicado se leen desde la memoria y no se modifican directamente realizando operaciones amplias, los valores se pueden desechar en cualquier momento sin guardar los resultados en la memoria general. Esta propiedad simplifica la implementación de 65 la regla #4 anterior.

[0041] Una realización alternativa de la presente invención puede sustituir la anterior regla #1 con la regla siguiente:

1a. Cada instrucción de almacenamiento de memoria comprueba la dirección de memoria frente a las direcciones de

5 memoria registradas para el almacenamiento dedicado. Cualquier coincidencia provoca que se actualice el almacenamiento dedicado, así como la memoria general.

[0042] Mediante la utilización de la anterior regla 1.a, las instrucciones de almacenamiento en memoria pueden modificar el almacenamiento dedicado, actualizando solamente la pieza del almacenamiento dedicado que ha cambiado, dejando intacto el resto. Continuando con la actualización de la memoria general, sigue siendo cierto que los contenidos de la memoria dedicada se pueden desechar en cualquier momento sin guardar los resultados en la memoria general. Esta regla #4 no se complica mediante esta opción. La ventaja de esta realización alternativa es que no es necesario desechar (invalidar) el almacenamiento dedicado mediante operaciones de almacenamiento en memoria.

#### Estructuras de datos de microcaché amplia

15

[0043] Haciendo referencia a continuación a la figura 9, se puede apreciar mejor una disposición a modo de ejemplo de las estructuras de datos de la microcaché amplia o almacenamiento dedicado 114. Se puede ver que los contenidos de la microcaché amplia, wmc.c, forman una serie de anchuras del camino de datos 900A-n, aunque en el ejemplo mostrado el número es de ocho. La dirección física, wmc.pa, se muestra como 64 bits en el ejemplo mostrado, si bien la invención no se limita a una anchura específica. El tamaño de los contenidos, wmc.size, se proporciona asimismo en un campo que se muestra como de 10 bits en una realización a modo de ejemplo. Se incluye asimismo en la estructura de datos un indicador de "contenido válido", wmc.cv, de un bit, junto con un campo de de dos bits para el último hilo utilizado, o wmc.th. Además, en una realización a modo de ejemplo se proporciona un campo de seis bits para el último registro utilizado, wmc.reg. Adicionalmente, se puede disponer un indicador de un bit para registro e hilo válido, o wmc.rtv.

#### Control de microcaché amplia - software

[0044] El proceso mediante el que la microcaché se escribe inicialmente con un operando amplio, y a continuación se verifica como válida para las operaciones posteriores, se puede apreciar mejor en la figura 8. El proceso comienza en 800, y avanza a la etapa 805 en la que se realiza una verificación de los contenidos del registro frente al valor almacenado wmc.rc. Si es correcta, se realiza una comprobación en la etapa 810 para verificar el hilo. Si es 35 correcta, el proceso avanza a continuación a la etapa 815 para verificar si el registro y el hilo son válidos. Si la etapa 815 indica correcto, se realiza una comprobación en la etapa 820 para verificar si los contenidos son válidos. Si todas las etapas 805 a 820 indican correcto, la instrucción posterior puede utilizar el operando amplio existente tal como se muestra en la etapa 825, después de lo cual el proceso finaliza. Sin embargo, si alguna de las etapas 805 a 820 indica falso, el proceso se bifurca a la etapa 830, donde se establece el contenido, la dirección física y el 40 tamaño. Dado que las etapas 805 a 820 conducen todas a alguna de las etapas 825 u 830, las etapas 805 a 820 se pueden realizar en cualquier orden o simultáneamente, sin alterar el proceso. El proceso avanza a continuación a la etapa 835, donde se comprueba el tamaño. Esta comprobación asegura básicamente que el tamaño de la unidad de traducción es mayor o igual que el tamaño del operando amplio, de tal modo que una dirección física puede sustituir directamente la utilización de una dirección virtual. La cuestión es que, en algunas realizaciones, los operandos 45 amplios pueden ser mayores que la zona mínima que es capaz de mapear el sistema de memoria virtual. Como resultado, sería posible que un único rango de direcciones virtuales contiguas fuera mapeado a múltiples rangos de direcciones físicas disjuntas, complicando la tarea de comparar direcciones físicas. Determinando el tamaño del operando amplio y comparando este tamaño con el tamaño de la zona de mapeo de direcciones virtuales a la que se hace referencia, si el operando amplio es mayor que la zona de mapeo la instrucción se aborta con una interrupción 50 de excepción. Esto garantiza el funcionamiento seguro del procesador. El software puede volver a mapear la zona utilizando un mapa de mayor tamaño para continuar la ejecución, si se desea. Por lo tanto, si se notifica el tamaño como inaceptable en la etapa 835, se genera una excepción en la etapa 840. Si el tamaño es aceptable, el proceso avanza a la etapa 845, donde se comprueba la dirección física. Si la comprobación indica que es satisfactoria, el proceso avanza a la etapa 850, donde se realiza una comprobación del indicador de contenido válido. Si alguna 55 comprobación en las etapas 845 ú 850 indica falso, el proceso se bifurca y se escribe contenido nuevo en el almacenamiento dedicado 114, ajustándose en consecuencia los campos del mismo. Si la comprobación de la etapa 850 indica verdadero, o si se ha escrito contenido nuevo en la etapa 855, el proceso avanza a la etapa 860, en la que se configuran los campos adecuados para indicar la validez de los datos, después de lo cual se puede llevar a cabo la función solicitada, en la etapa 825. A continuación, el proceso finaliza. 60

## Control de microcaché amplia – hardware

[0045] Haciendo referencia a continuación a las figuras 10 y 11, que muestran juntas el funcionamiento del controlador de la microcaché desde el punto de vista del hardware, se puede comprender mejor el funcionamiento del controlador de la microcaché. En la implementación del hardware, resulta evidente que las condiciones que se indican como etapas secuenciales en las anteriores figuras 8 y 9 se pueden llevar a cabo en paralelo, reduciendo el

retardo para dicha verificación de operando amplio. Además, se puede incluir una copia del hardware indicado para cada microcaché amplia, y de ese modo la totalidad de dichas microcachés, a las que se puede hacer referencia alternativamente mediante una instrucción, se pueden verificar en paralelo. Se considera que no es necesaria ninguna discusión adicional de las figuras 10 y 11 en vista de la discusión extensiva de las anteriores figuras 8 y 9.

[0046] Existen varias alternativas al enfoque anterior para la utilización de los operandos amplios, incluyendo una implementación en la que una única instrucción puede aceptar dos operandos amplios, la división de los operandos en símbolos, multiplicar juntos símbolos correspondientes, y sumar los productos para producir un único valor escalar o un vector de valores divididos de la anchura del archivo de registros, posiblemente después de la extracción de una parte de las sumas. Dicha instrucción puede ser valiosa para la detección de movimiento o la estimación de movimiento en la compresión de video. Una mejora adicional de dicha instrucción puede actualizar incrementalmente el almacenamiento dedicado si la dirección de un operando amplio está dentro del intervalo de operandos amplios especificados anteriormente en el almacenamiento dedicado, mediante cargar solamente la parte que no está ya dentro del intervalo y desplazar según se requiera la parte comprendida en el intervalo. Dicha mejora permite que el funcionamiento se realice sobre una "ventana móvil" de posibles valores. En una instrucción semejante, un operando amplio está alineado y suministra la información de tamaño y forma, mientras que el segundo operando amplio, actualizado incrementalmente, no está alineado.

[0047] La siguiente tabla muestra la notación aritmética y descriptiva utilizada en el pseudocódigo de las figuras a 20 las que se hace referencia a continuación:

| x + y                    | suma de dos complementos, de x e y. El resultado tiene el mismo tamaño que los operandos, y los         |

|--------------------------|---------------------------------------------------------------------------------------------------------|

|                          | operandos tienen que tener el mismo tamaño.                                                             |

| x - y                    | resta de dos complementos, de y respecto de x. El resultado tiene el mismo tamaño que los               |

|                          | operandos, y los operandos tienen que tener el mismo tamaño.                                            |

| x * y                    | multiplicación de dos complementos, de x e y. El resultado tiene el mismo tamaño que los operandos,     |

|                          | y los operandos tienen que tener el mismo tamaño.                                                       |

| x / y                    | división de dos complementos, de x por y. El resultado tiene el mismo tamaño que los operandos, y       |

|                          | los operandos tienen que tener el mismo tamaño.                                                         |

| x & y                    | operación bit a bit AND, de x e y. El resultado tiene el mismo tamaño que los operandos, y los          |

|                          | operandos tienen que tener el mismo tamaño.                                                             |

| x   y                    | operación bit a bit OR, de x e y. El resultado tiene el mismo tamaño que los operandos, y los           |

|                          | operandos tienen que tener el mismo tamaño.                                                             |

| x ^ y                    | operación bit a bit OR exclusiva, de x e y. El resultado tiene el mismo tamaño que los operandos, y los |

|                          | operandos tienen que tener el mismo tamaño.                                                             |

| ~X                       | inversión bit a bit de x. El resultado tiene mismo tamaño que el operando.                              |

| x = y                    | comparación de la igualdad de dos complementos, entre x e y. El resultado es un solo bit, y los         |

| -                        | operandos tienen que ser del mismo tamaño.                                                              |

| x≠y                      | comparación de la desigualdad de dos complementos, entre x e y. El resultado es un solo bit, y los      |

| -                        | operandos tienen que ser del mismo tamaño.                                                              |

| x < y                    | comparación de menor que, de dos complementos, entre x e y. El resultado es un solo bit, y los          |

|                          | operandos tienen que ser del mismo tamaño.                                                              |

| x ≥ y                    | comparación de mayor o igual que, de dos complementos, entre x e y. El resultado es un solo bit, y los  |

|                          | operandos tienen que ser del mismo tamaño.                                                              |

| √x                       | raíz cuadrada con coma flotante, de x.                                                                  |

| x    y<br>x <sup>y</sup> | concatenación del campo de bits x a la izquierda del campo de bits y.                                   |

| $x^y$                    | dígito binario x repetido, concatenado y veces. el tamaño del resultado es y.                           |

| Xy                       | extracción del bit y (utilizando numeración de bits con comienzo por el extremo bajo) del valor x. El   |

| ,                        | resultado es un solo bit.                                                                               |

| X <sub>yz</sub>          | extracción del campo de bits formado por los bits y hasta z del valor x. El tamaño de los resultados es |

| ,                        | de - z+1; si z > y, el resultado es una cadena vacía.                                                   |

| x?y:z                    | valor de y, si x es cierto, de lo contrario valor de z. El valor de x es de un solo bit.                |

| x ← y                    | asignación bit a bit, de x al valor de y.                                                               |

| x.y                      | campo secundario del campo de bits estructurado x.                                                      |

| Sn                       | formato de datos binarios de dos complementos, con signo, de n octetos.                                 |

| Un                       | formato de datos binarios sin signo, de n octetos.                                                      |

| Fn                       | formato de datos con coma flotante, de n octetos.                                                       |

|                          | 1                                                                                                       |

## Operaciones amplias

5

25 **[0048]** Los ejemplos particulares de operaciones amplias incluyen Galois de matriz de multiplicación amplia. Si bien la discusión siguiente se centra en tamaños particulares para las instrucciones a modo de ejemplo, se apreciará que la invención no se limita a una anchura particular.

### Galois de matriz de multiplicación amplia

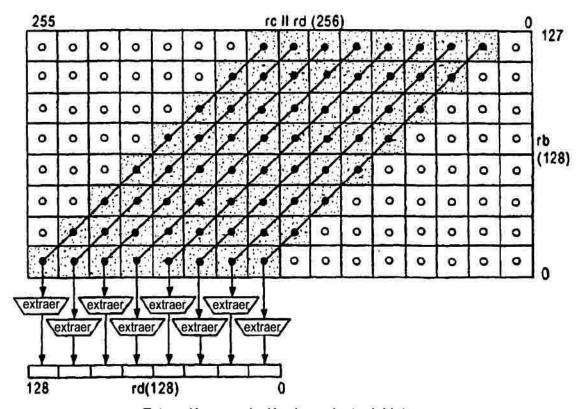

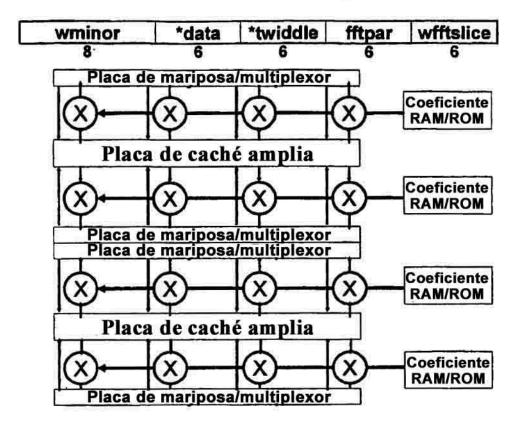

[0049] En las figuras 12A a 12D se muestra una realización a modo de ejemplo de la instrucción de Galois de matriz de multiplicación amplia. En una realización a modo de ejemplo, la instrucción de Galois de matriz de multiplicación amplia realiza una multiplicación de matrices de la misma forma que anteriormente, excepto en que las multiplicaciones y sumas se realizan en aritmética de campos de Galois. Se puede especificar un tamaño de 8 bits dentro de la instrucción. Los contenidos de un registro general especifican el polinomio con el que llevar a cabo la operación del resto en campos de Galois. La naturaleza de la multiplicación de matrices es nueva y se describe en detalle a continuación.

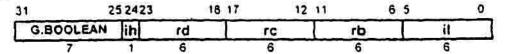

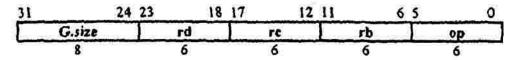

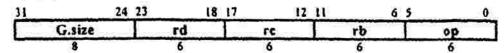

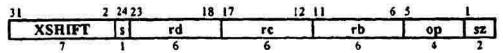

10 **[0050]** En una realización a modo de ejemplo, estas instrucciones toman una dirección desde un registro general para recuperar de la memoria un operando grande, un segundo y tercer operandos desde los registros generales, realizan un grupo de operaciones en divisiones de bits en los operandos, y concatenan juntos los resultados, colocando el resultado en un registro general. En la figura 12A se muestra una realización a modo de ejemplo del formato 1810 de la instrucción de Galois de matriz de multiplicación amplia.

15

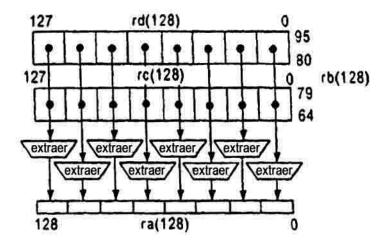

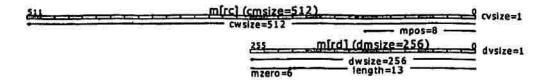

[0051] En la figura 12B se muestra una realización a modo de ejemplo del esquema 1830 de la instrucción de Galois de matriz de multiplicación amplia. En una realización a modo de ejemplo, los contenidos de un registro re se utilizan como dirección virtual, y se carga desde la memoria un valor de un tamaño específico. Un segundo y un tercer valores son los contenidos de los registros de rd y rb. Los valores se dividen en grupos de operandos del tamaño específicado. Los segundos valores se multiplican como polinomios por el primer valor, produciendo un resultado que se reduce al campo de Galois específicado por el tercer valor, produciendo un grupo de valores de resultado. El grupo de valores de resultado se concatena y se coloca en el registro ra.

[0052] En una realización a modo de ejemplo, la instrucción de octetos de Galois de matriz de multiplicación amplia (W.MUL.MAT.G.8) realiza una multiplicación matricial dividida de hasta 16 384 bits, es decir 128 x 128 bits. La anchura de la matriz se puede limitar a 128, 64, 32 ó 16 bits, pero sin ser menor que el doble del tamaño de grupo de 8 bits, añadiendo la mitad del tamaño deseado en octetos al operando de dirección virtual: 8, 4, 2 ó 1. La matriz se puede limitar verticalmente a 128, 64, 32 ó 16 bits, pero sin ser menor que el doble del tamaño del grupo de 8 bits, añadiendo la mitad del tamaño de operando de memoria deseado en octetos, al operando de dirección virtual.

[0053] En una realización a modo de ejemplo, la dirección virtual tiene que estar alineada a 256 octetos, o bien ser la suma de una dirección alineada y la mitad del tamaño del operando de memoria en octetos y/o la mitad del tamaño del resultado en octetos. Una dirección alineada tiene que ser un múltiplo exacto del tamaño expresado en octetos. Si la dirección no es válida se produce una excepción de "acceso denegado por dirección virtual".

[0054] Tal como se muestra en la figura 12B, una realización a modo de ejemplo de una instrucción de octetos de Galois de matriz de multiplicación amplia (W.MUL.MAT.G.8) multiplica la memoria [m255 m254 ... m1 m0] por el vector [ponmlkjihgfedcba], reduciendo el módulo polinómico [q] del resultado, proporcionando los productos [(pm255 40 + om247 + ... + bm31 + am15 mod q) (pm254 + om246 + ... + bm30 + am14 mod q) ... (pm248 + om240 + ... + bm16 + am0 mod q)].

[0055] En la figura 12C se muestra una realización a modo de ejemplo del pseudocódigo 1860 de la instrucción de Galois de matriz de multiplicación amplia. En la figura 12D se muestra una realización a modo de ejemplo de las excepciones 1890 de la instrucción de Galois de matriz de multiplicación amplia.

## Operandos de memoria de ordenación convencional de octetos con comienzo por el extremo bajo o bien con comienzo por el extremo alto

50 **[0056]** Se facilitan operandos de memoria de ordenaciones de octetos convencionales con comienzo por el extremo bajo o bien con comienzo por el extremo alto. Por consiguiente, todas las instrucciones de operandos amplios se especifican en dos formas, una para ordenación de octetos con comienzo por el extremo bajo y una para ordenación de octetos con comienzo por el extremo alto, tal como se especifica mediante una parte de la instrucción. El orden de los octetos especifica al sistema de memoria el orden en el que entregar los octetos dentro de unidades de la anchura del camino de datos (128 bits), así como el orden para colocar múltiples palabras de memoria (128 bits) dentro de un operando amplio mayor.

#### Extracción de una parte de orden superior de un producto o suma de productos de multiplicador

60 [0057] La extracción de una parte de orden superior de un producto o suma de productos de multiplicador, es una manera de utilizar eficientemente una matriz grande de multiplicadores. La patente U.S.A. 5 742 840 y la patente U.S.A. 5 953 241 relacionadas describen un sistema y un método para mejorar la utilización de una serie de multiplicadores, añadiendo clases específicas de instrucciones a un procesador de propósito general. Esto aborda el problema de realizar la máxima utilización de una matriz grande de multiplicadores que se utiliza totalmente para 65 aritmética de gran precisión - por ejemplo un multiplicador de 64 x 64 bits se utiliza por completo mediante una multiplicación de 64 bits por 64 bits, pero se utiliza solamente una cuarta parte para una multiplicación de 32 bits por

## ES 2 527 937 T3

32 bits) para (en relación con la anchura de datos del multiplicador y los registros) operaciones aritméticas de baja precisión. En particular, se especifican operaciones que realizan multiplicaciones de precisión muy baja que se combinan (suman) juntas de varias maneras. Una de las consideraciones de anulación en la selección del conjunto de operaciones es una limitación del tamaño del operando de resultado. En una realización a modo de ejemplo, por ejemplo, ese tamaño se puede limitar al orden de 128 bits, o de un único registro, aunque no existe una necesidad de limitación específica del tamaño.

[0058] El tamaño de un resultado de multiplicación, un producto, es generalmente la suma de los tamaños de los operandos, de los multiplicandos y del multiplicador. Por consiguiente, las instrucciones de multiplicación especifican operaciones en las que el tamaño del resultado es el doble del tamaño de operandos de entrada de idéntico tamaño. Para nuestro diseño de la técnica anterior, por ejemplo, una instrucción de multiplicación acepta dos fuentes de registro de 64 bits y produce un único resultado de un par de registros de 128 bits, utilizando una matriz entera de 64 x 64 multiplicadores para símbolos de 64 bits, o la mitad de la matriz de multiplicadores para pares de símbolos de 32 bits, o una cuarta parte de la matriz multiplicadora para cuádruplas de símbolos de 16 bits. Para todos estos 15 casos, se debe observar que se combinan dos fuentes de registro de 64 bits, produciendo un resultado de 128 bits.

[0059] En algunas de las operaciones, incluyendo multiplicaciones complejas, convolución, y multiplicación de matrices, se suman juntos productos de multiplicadores de baja precisión. Las sumas incrementan más la precisión requerida. La suma de dos productos requiere un bit adicional de precisión; sumar cuatro productos requiere dos, sumar ocho productos requiere tres, sumar dieciséis productos requiere cuatro. En algunos diseños anteriores, se pierde parte de esta precisión, lo que requiere escalar los operandos multiplicadores para evitar desbordamiento, reduciendo adicionalmente la precisión del resultado.

[0060] La utilización de los pares de registros crea una complejidad no deseable, porque tanto el par de registros como los valores individuales de los registros tienen que ser omitidos en las instrucciones subsiguientes. Como resultado, con las técnicas de la técnica anterior solamente la mitad de los valores del registro de 128 bits de operando fuente se podrían utilizar para producir un resultado de 128 bits de un solo registro.

[0061] Una parte de orden superior del producto o suma de productos de multiplicador es extraída, ajustada por una cantidad de desplazamiento dinámica procedente de un registro general o de un ajuste especificado como parte de la instrucción, y redondeada mediante un valor de control a partir de un registro o parte de instrucción como redondeo al entero/par más cercano, hacia cero, techo o piso. Los desbordamientos se tratan limitando el resultado a los valores máximo y mínimo que se pueden representar con precisión en el resultado de salida.

## 35 Extracción controlada por un registro

[0062] Cuando la extracción está controlada por un registro, el tamaño del resultado se puede especificar, lo que permite el redondeo y la limitación a un número menor de bits que pueden caber en el resultado. Esto permite escalar el resultado para su utilización en operaciones posteriores sin preocuparse del desbordamiento o el 40 redondeo, mejorando el rendimiento.

[0063] Cuando la extracción está controlada por un registro, un único valor de registro define el tamaño de los operandos, la cantidad de desplazamiento y el tamaño del resultado, y el control de redondeo. Colocando toda esta información de control en un único registro, se reduce el tamaño de la instrucción respecto del número de bits que 45 dicha instrucción requeriría de otro modo, mejorando el rendimiento e incrementando la flexibilidad del procesador.

**[0064]** Las instrucciones particulares son extracción convolución de conjunto, extracción multiplicación de conjunto, extracción multiplicación suma de conjunto y extracción suma escalar de conjunto.

## 50 Extracción de conjunto in situ

60

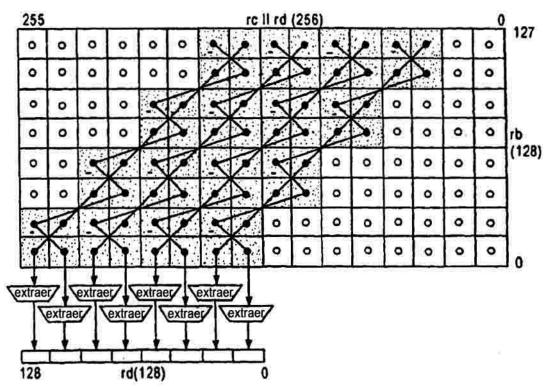

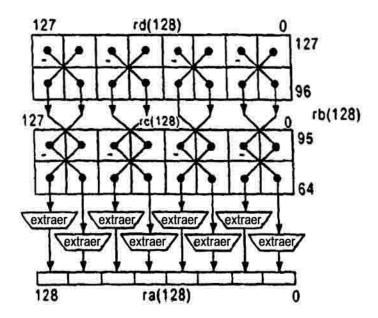

[0065] Las figuras 13A a 13G muestran una instrucción de extracción de conjunto in situ. En una realización a modo de ejemplo, varias de estas instrucciones (extracción convolución de conjunto, extracción multiplicación suma de conjunto) están disponibles habitualmente solamente en formas en las que la extracción se especifica como parte de la instrucción. Una alternativa puede incorporar formas de operaciones en las que el tamaño del operando, la cantidad de desplazamiento y el redondeo pueden estar controlados por los contenidos de un registro general (tal como lo están en la instrucción de extracción multiplicación de conjunto). La definición de esa clase de instrucción para extracción convolución de conjunto, y extracción multiplicación suma de conjunto requeriría cuatro registros fuente, lo que incrementa la complejidad al requerir puertos adicionales de lectura de registros generales.

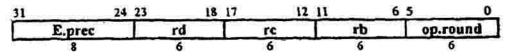

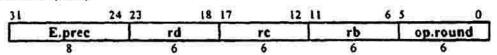

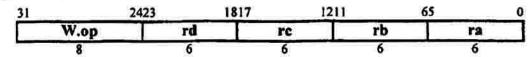

**[0066]** Estas operaciones toman operandos desde cuatro registros, realizan operaciones sobre divisiones de bits en los operandos, y colocan los resultados concatenados en un cuarto registro. En la figura 13A se muestra una realización a modo de ejemplo del formato y de los códigos de operación 1910 de la instrucción de extracción de conjunto in situ.

[0067] Los esquemas 1930, 1945, 1960 y 1975 de la instrucción de extracción de conjunto in situ se muestran en

11

las figuras 3C, 13D, 13E y 13F. En una realización a modo de ejemplo, se recuperan los contenidos de los registros rd, rc, rb y ra. La operación especificada se lleva a cabo sobre estos operandos. El resultado se coloca en el registro rd.

5 [0068] En una realización a modo de ejemplo, para la instrucción E.CON.X, se concatenan los contenidos de los registros rd y rc, como c // d, y se utilizan como un primer valor. Un segundo valor consisten los contenidos del registro rb. Los valores se dividen en grupos de operandos del tamaño especificado y se convolucionan, produciendo un grupo de valores. El grupo de valores es redondeado, limitado y extraído tal como se especifica, produciendo un grupo de resultados de tamaño especificado. El grupo de resultados es concatenado y colocado en 10 el registro rd.

[0069] Para la instrucción E.MUL.ADD.X, los contenidos de los registros rc y rb se dividen en grupos de operandos del tamaño especificado y se multiplican, produciendo un grupo de valores a los que se suman los contenidos divididos extendidos del registro rd. El grupo de valores es redondeado, limitado y extraído tal como se especifica,

proporcionando un grupo de resultados de tamaño especificado. El grupo de resultados es concatenado y colocado en el registro rd.

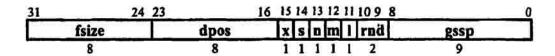

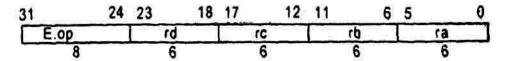

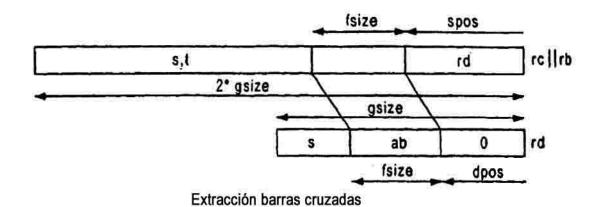

[0070] Tal como se muestra en la figura 13B, los bits 31..0 de los contenidos del registro ra especifican varios parámetros que controlan la manera en que se extraen los datos y, para ciertas operaciones, la manera en que se 20 lleva a cabo la operación. La posición de los campos de control permite que la posición de la fuente se sume a un valor de control fijo para computación dinámica, y permite que los 16 bits inferiores del campo de control se configuren para alguno de los casos de extracción más simples, mediante una única instrucción GCOPYI.128. Los campos de control están dispuestos además de tal modo que es si solamente los 8 bits de orden bajo son distintos de cero, se realiza una extracción de 128 bits con truncado y sin redondeo.

[0071] La siguiente tabla describe el significado de cada etiqueta:

| etiqueta | bits | significado                                      |

|----------|------|--------------------------------------------------|

| fsize    | 8    | tamaño del campo                                 |

| dpos     | 8    | posición de destino                              |

| Х        | 1    | resultado extendido vs. tamaño de grupo          |

| S        | 1    | con signo vs. sin signo                          |

| n        | 1    | multiplicación compleja vs. real                 |

| m        | 1    | multiplicación de signo mezclado vs. mismo signo |

| I        | 1    | límite: saturación vs. truncado                  |

| rnd      | 2    | redondeo                                         |

| gssp     | 9    | tamaño del grupo y posición de la fuente         |

[0072] En una realización a modo de ejemplo, el campo gssp de 9 bits codifica tanto el tamaño del grupo, gsize, 30 como la posición de la fuente, spos, de acuerdo con la fórmula gssp = 512 - 4\*gsize + spos. El tamaño del grupo, gsize, es una potencia de dos comprendida en el intervalo de 1..128. La posición de la fuente, spos, está comprendida en el intervalo de 0..(2\*gsize) - 1.

[0073] En una realización a modo de ejemplo, los valores en los campos x, s, n, m, l y rnd tienen el siguiente 35 significado:

| valores | Х         | S         | n        | m           | 1        | rnd |

|---------|-----------|-----------|----------|-------------|----------|-----|

| 0       | grupo     | sin signo | real     | mismo signo | truncado | F   |

| 1       | extendido | con signo | complejo | signo       | saturar  | Z   |

|         |           | -         |          | mezclado    |          |     |

| 2       |           |           |          |             |          | N   |

| 3       |           |           |          |             |          | С   |

## Extracción multiplicación suma de conjunto

- 40 **[0074]** Tal como se muestra en la figura 13C una instrucción de extracción multiplicación suma de conjunto dobletes (E.MULADDX) multiplica el vector rc [h g f e d c b a] por el vector rb [p o n m l k j i], y suma el vector rd [x w v u t s r q], proporcionando el vector resultado rd [hp+x go+w fn+v em+u dl+t ck+s bj+r ai+q], redondeado y limitado tal como se especifica mediante ra31..0.

- 45 **[0075]** Tal como se muestra en la figura 13D, una instrucción de extracción multiplicación suma de conjunto dobletes complejos (E.MUL.X con n activado) multiplica el vector operando rc [h g f e d c b a] por el vector operando rb [p o n m l k j i], proporcionando el vector resultado rd [gp + ho go hp en + fm em fn cl + dk ck dl aj + bi ai bj], redondeado y limitado tal como se especifica mediante ra31..0. Se debe observar que esta instrucción prefiere una organización de números complejos en la que la parte real esté situada a la derecha (menor precisión) de la parte

imaginaria.

15

50

#### Extracción convolución de conjunto

5 [0076] Tal como se muestra en la figura 13E, una instrucción de extracción convolución de conjunto dobletes (ECON.X con n = 0) convoluciona el vector rc // rd [x w v u t s r q p o n m l kj i] con el vector rb [h g f e d c b a], proporcionando el vector de productos rd

[ax + bw + cv + du + et + fs + gr + hq ... as + br + cq + dp + eo + fn + gm + hl ar + bq + cp + do + en + fm + gl + hk aq 10 + bp + co + dn + em + fl + gk + hj], redondeado y limitado tal como se especifica por ra31..0.

**[0077]** Tal como se muestra en la figura 13F, una instrucción de extracción convolución de conjunto dobletes complejos (ECON.X con n=1) convoluciona el vector rd // rc [x w v u t s r q p o n m l k j i] con el vector rb [h g f e d c b a], proporcionando el vector de productos rd

[0078] [ax + bw + cv + du + et + fs + gr + hq ... as - bt + cq - dr + eo - fp + gm - hn ar + bq + cp + do + en + fm + gl + hk aq - br + co - dp + em - fn + gk + hl], redondeado y limitado tal como se específica por ra31..0.

[0079] El pseudocódigo 1990 de la instrucción de extracción de conjunto in situ se muestra en la figura 13G. 20 Puede no haber excepciones para la instrucción de extracción de conjunto in situ.

#### Extracción de conjunto

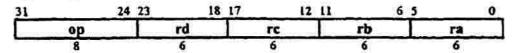

[0080] En las figuras 14A a 14J se muestra una instrucción de extracción de conjunto. Estas operaciones toman operandos de tres registros, realizan las operaciones sobre divisiones de bits en los operandos, y colocan los resultados concatenados en un cuarto registro. El formato y los códigos de operación 2010 de la instrucción de extracción conjunto se muestran en la figura 14A.

[0081] En las figuras 14C, 14D, 14E, 20F, 20G, 20H y 20I se muestra a un esquema 2020, 2030, 2040, 2050, 30 2060, 2070 y 2080 de la instrucción de extracción de conjunto in situ. Los contenidos de los registros rd, rc y rb son recuperados. La operación especificada se lleva a cabo sobre estos operandos. El resultado se coloca en el registro ra.

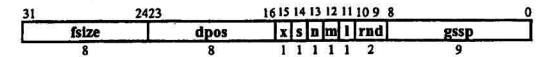

[0082] Tal como se muestra en la figura 14B, los bits 31..0 de los contenidos del registro rb especifican varios parámetros que controlan la manera en que se extraen los datos y, para ciertas operaciones, la manera en que se lleva a cabo la operación. La posición de los campos de control permite que la posición de la fuente se sume a un valor de control fijo para computación dinámica, y permite que los 16 bits inferiores del campo de control se configuren para alguno de los casos de extracción más simples, mediante una única instrucción GCOPYI.128. Los campos de control están dispuestos además de tal modo que es si solamente los 8 bits de orden bajo son distintos 40 de cero, se realiza una extracción de 128 bits con truncado y sin redondeo.

[0083] La siguiente tabla describe el significado de cada etiqueta:

| etiqueta | bits | significado                                                              |

|----------|------|--------------------------------------------------------------------------|

| fsize    | 8    | tamaño del campo                                                         |

| dpos     | 8    | posición de destino                                                      |

| Х        | 1    | resultado extendido vs. tamaño de grupo                                  |

| S        | 1    | con signo vs. sin signo                                                  |

| n        | 1    | multiplicación compleja vs. real                                         |

| m        | 1    | fusionar vs. extraer, o multiplicación de signo mezclado vs. mismo signo |

| I        | 1    | límite: saturación vs. truncado                                          |

| rnd      | 2    | redondeo                                                                 |

| gssp     | 9    | tamaño del grupo y posición de la fuente                                 |

45 **[0084]** El campo gssp de 9 bits codifica tanto el tamaño del grupo, gsize, como la posición de la fuente, spos, de acuerdo con la fórmula gssp = 512 4\*gsize + spos. El tamaño del grupo, gsize, es una potencia de dos comprendida en el intervalo de 1..128. La posición de la fuente, spos, está comprendida en el intervalo de 0..(2\*gsize) - 1.

[0085] Los valores en los campos x, s, n, m, l y rnd tienen el significado siguiente:

| valores | Х         | S         | n        | m                       | I        | rnd |

|---------|-----------|-----------|----------|-------------------------|----------|-----|

| 0       | grupo     | sin signo | real     | extraer/mismo signo     | truncado | F   |

| 1       | extendido | con signo | complejo | fusionar/signo mezclado | saturar  | Z   |

| 2       |           |           |          |                         |          | N   |

| 3       |           |           |          |                         |          | С   |

13

[0086] Para la instrucción E.SCAL.ADD.X, los bits 127..64 de los contenidos del registro rb especifican los multiplicadores para los multiplicandos en los registros rd y rc. Específicamente, los bits 64 + 2\*gsize-1 .. 64 + gsize consisten en el multiplicador para los contenidos del registro rd, y los bits 64 + gsize-1 .. 64 consisten en el multiplicador para los contenidos del registro rc.

#### Extracción multiplicación de conjunto

[0087] Tal como se muestra en la figura 14C, una instrucción de extracción multiplicación de conjunto dobletes 10 (E.MULX) multiplica el vector rd [h g f e d c b a] por el vector rc [p o n m l kj i], proporcionando el vector de resultado ra [hp go fn em dl ck bj ai], redondeado y limitado tal como se especifica mediante rb<sub>31...0</sub>.

[0088] Tal como se muestra en la figura 14D, una instrucción de extracción multiplicación de conjunto dobletes complejos (E.MUL.X con n activado) multiplica el vector rd [h g f e d c b a] por el vector rc [p o n m l k j i], 15 proporcionando el vector de resultado ra [gp + ho go - hp en + fm em - fn cl + dk ck - dl aj + bi ai - bj], redondeado y limitado tal como se especifica mediante rb<sub>31...0</sub>. Se debe observar que esta instrucción prefiere una organización de números complejos en la que la parte real esté situada a la derecha (menor precisión) de la parte imaginaria.

## Extracción suma escalar de conjunto

20

[0089] La instrucción de extracción suma escalar de conjunto, combina la información de control de extracción en un registro, con dos valores que se utilizan como multiplicadores escalares para los contenidos de dos multiplicandos vectoriales.

25 **[0090]** Esta combinación reduce el número de registros que serían necesarios en otro caso, o el número de bits que de lo contrario requeriría la instrucción, mejorando el rendimiento. Otra ventaja de la presente invención es que la operación combinada se puede llevar a cabo mediante una realización a modo de ejemplo con la suficiente precisión interna en el nodo de sumación como para que no se produzca redondeo o desbordamiento intermedio, mejorando la precisión sobre la operación de la técnica anterior, en la que era necesario llevar a cabo más de una 30 instrucción para este cálculo.

[0091] Tal como se muestra en la figura 14E, una instrucción de extracción de suma escalar de conjunto dobletes (E.SCAL.ADD.X) multiplica el vector rd [h g f e d c b a] por rb<sub>95.80</sub> [r] y suma el producto al producto del vector rc [p o n m l k j i] por rb<sub>79.64</sub> [q], proporcionando el resultado [hr + pq gr + oq fr + nq er + mq dr + lq cr + kq br + jq ar + iq], 35 redondeado y limitado tal como se especifica por rb<sub>31...0</sub>.

[0092] Tal como se muestra en la figura 14F, una instrucción de extracción suma escalar de conjunto dobletes complejos (E.SCLADD.X con n activado) multiplica el vector rd [h g fe d c b a] por rb<sub>127..96</sub> [t s] y suma el producto, al producto del vector rc [p o n m l k j i] por rb<sub>95..64</sub> [r q], proporcionando el resultado [hs + gt + pq + or gs-ht + oq - pr fs 40 + et + nq + mr es - ft + mq - nr ds + ct + lq + kr cs - dt + kq - lr bs + at + jq + ir as - bt + iq - jr], redondeado y limitado tal como se especifica mediante rb<sub>31..0</sub>.

#### Extracción de conjunto

- 45 **[0093]** Tal como se muestra en la figura 14G, para la instrucción E.EXTRACT, cuando m=0 y x=0, los parámetros especificados por los contenidos del registro rb se interpretan para seleccionar campos de símbolos de doble tamaño de los contenidos concatenados de los registros rd y rc, extrayendo valores que son concatenados y colocados en el registro ra.

- 50 **[0094]** Tal como se muestra en la figura 14H, para una extracción fusión de conjunto (E.EXTRACT cuando m=1), los parámetros especificados por los contenidos del registro rb se interpretan para fusionar campos a partir de símbolos de los contenidos del registro rd con los contenidos del registro rc. Los resultados son concatenados y colocados en el registro ra. El campo x no tiene ningún efecto cuando m=1.

- 55 **[0095]** Tal como se muestra en la figura 14I, para una extracción expansión de conjunto (E.EXTRACT cuando m=0 y x=1), los parámetros especificados por los contenidos del registro rb se interpretan para extraer campos de símbolos de los contenidos del registro rd. Los resultados son concatenados y colocados en el registro ra. Se debe observar que no se utiliza el valor de rc.

- 60 **[0096]** En la figura 14J se muestra el pseudocódigo 2090 de la instrucción de extracción de conjunto. No existen excepciones para la instrucción de extracción de conjunto.

#### Reducción de puertos de lectura de registros

65 [0097] Es posible reducir el número de puntos de lectura de registro necesarios para la implementación de instrucciones en las que el tamaño, el desplazamiento y el redondeo de los operandos están controlados por un

registro. El valor del registro de control de extracción puede ser recuperado utilizando un ciclo adicional de una ejecución inicial, y retenido dentro de la unidad funcional o cerca de la misma para ejecuciones subsiguientes, reduciendo de este modo la cantidad de hardware necesario para la implementación con una pequeña penalización adicional sobre el rendimiento. El valor retenido se marcaría como no válido, provocando una nueva recuperación del registro de control extraído, mediante instrucciones que modifican el registro o, alternativamente, el valor retenido se puede actualizar mediante dicha operación. Una nueva recuperación del registro del control de la extracción sería necesaria asimismo si se especificara un número de registro diferente en una ejecución posterior. Debería resultar evidente que las propiedades de las anteriores dos realizaciones alternativas se pueden combinar.

#### 10 Aritmética de campos de Galois

[0098] En la aritmética de campos de Galois, las multiplicaciones se llevan a cabo mediante una multiplicación polinómica binaria inicial (multiplicaciones binarias sin signo con acarreos suprimidos), seguida por una operación de modulo polinómico/resto (división binaria sin signo con acarreos suprimidos). La operación de resto es relativamente costosa en superficie y retardo. En la aritmética de campos de Galois, la suma se lleva a cabo mediante la adición binaria con acarreos suprimidos o, de manera equivalente, una operación OR exclusiva bit a bit. Se puede llevar a cabo una multiplicación de matrices utilizando aritmética de campos de Galois, donde las multiplicaciones y las sumas son multiplicaciones y sumas de campos de Galois.

- 20 **[0099]** Utilizando métodos de la técnica anterior, la multiplicación de un vector de 16 octetos por una matriz de 16 x 16 octetos se puede realizar como 256 multiplicaciones de campos de Galois de 8 bits y 16\* 15=240 sumas de campos de Galois de 8 bits. En las 256 multiplicaciones de campos de Galois están incluidas 256 multiplicaciones polinómicas y 256 operaciones de resto polinómico.

- 25 [0100] El cálculo total se reduce significativamente llevando a cabo 256 multiplicaciones polinómicas, 240 sumas polinómicas 16 bits y 16 operaciones de resto polinómico. Se debe observar que el coste de las sumas polinómicas se ha duplicado en comparación con las sumas de campos de Galois, dado que estas son ahora operaciones de 16 bits en lugar de operaciones de 8 bits, pero el coste de las funciones de resto polinómico se ha reducido en un factor de 16. En conjunto, esto constituye una solución favorable, dado que el coste de la suma es mucho menor que el 30 coste del resto.

#### Acceso desacoplado de los segmentos de ejecución y multihilos simultáneos

[0101] Tal como se muestra mejor en la figura 4, la presente invención utiliza un acceso desacoplado respecto de las segmentaciones de ejecución y multihilos simultáneos, de una manera única. Las segmentaciones multihilos simultáneas se han utilizado en la técnica anterior para mejorar la utilización de las unidades de camino de datos permitiendo que se emitan instrucciones desde uno de varios hilos de ejecución a cada unidad funcional (por ejemplo Dean M. Tullsen, Susan J. Eggers, y Henry M. Levy, "Simultaneous Multithreading: Maximizing On Chip Parallelism," Proceedings of the 22nd Annual International Symposium on Computer Architecture, Santa Margherita 40 Ligure, Italia, junio de 1995).

[0102] El acceso desacoplado respecto de las segmentaciones de ejecución se ha utilizado en la técnica anterior para mejorar la utilización de las unidades de camino de datos de ejecución, mediante almacenar en memoria tampón resultados procedentes de una unidad de acceso, que calcula direcciones para una unidad de memoria que, a su vez, recupera de la memoria los elementos solicitados, y presentarlos a continuación a una unidad de ejecución (por ejemplo, J. E. Smith, "Decoupled Access/Execute Computer Architectures", Proceedings of the Ninth Annual International Symposium on Computer Architecture, Austin, Tejas (26 a 29 de abril de 1982), páginas 112 a 119).

- [0103] En comparación con las segmentaciones convencionales, la técnica anterior de Eggers utilizada en el ciclo de segmentación adicional antes de las instrucciones podría ser emitida para unidades funcionales, el ciclo adicional siendo necesario para determinar a qué hilos se debería permitir emitir instrucciones. Por consiguiente, en relación con las segmentaciones convencionales, el diseño de la técnica anterior tenía un retardo adicional, incluyendo un retardo dependiente de las ramificaciones.

- 55 **[0104]** En el presente documento se describen unidades de camino de datos de acceso, con archivos de registros asociados, para cada hilo de ejecución. Estas unidades de acceso producen direcciones, que se agregan juntas a una unidad de memoria común, que recupera todas las direcciones y coloca los contenidos de la memoria en una o varias memorias tampón. Las instrucciones para las unidades de ejecución, que se comparten en grados variables entre los hilos, son asimismo almacenadas en memoria tampón para su ejecución posterior. Las unidades de ejecución llevan a cabo a continuación operaciones desde todos los hilos activos utilizando unidades de camino de datos funcionales que son compartidas.

- [0105] Para las instrucciones llevadas a cabo por las unidades de ejecución, el ciclo adicional requerido por los diseños multihilo simultáneos de la técnica anterior se solapa con el tiempo de acceso a los datos de memoria del acceso desacoplado de la técnica anterior, de los ciclos de ejecución, de tal modo que las unidades funcionales no incurren en ningún retardo adicional para planificar recursos. Para las instrucciones llevadas a cabo por las unidades

de acceso, al utilizar unidades de acceso individuales para cada hilo se elimina asimismo el ciclo adicional para planificar recursos compartidos.

[0106] Ésta constituye una solución favorable debido a que, si bien los hilos no comparten las unidades 5 funcionales de acceso, estas unidades son relativamente pequeñas en comparación con las unidades funcionales de ejecución, que son compartidas por los hilos.