# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 539 712

51 Int. Cl.:

G06F 1/32 (2006.01) G06F 9/445 (2006.01) H04W 52/02 (2009.01)

(12)

# TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 07.09.2010 E 10826159 (5)

(97) Fecha y número de publicación de la concesión europea: 29.04.2015 EP 2494423

(54) Título: Dispositivo no volátil

(30) Prioridad:

27.10.2009 US 606842

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 03.07.2015

(73) Titular/es:

NOKIA TECHNOLOGIES OY (100.0%) Karaportti 3 02610 Espoo, FI

(72) Inventor/es:

**VOUTILAINEN, MARTTI KALEVI**

(74) Agente/Representante:

VALLEJO LÓPEZ, Juan Pedro

## **DESCRIPCIÓN**

Dispositivo no volátil

#### Antecedentes

5

10

15

20

25

Los consumidores desean tener servicios disponibles en sus dispositivos en todo momento y en todos los lugares. Para satisfacer estos deseos usando tecnologías de semiconductores complementarios de óxido metálico convencionales (CMOS), toda la circuitería correspondiente de un dispositivo tiene que estar siempre encendida consumiendo energía de este modo, incluso cuando no está en uso. Alimentar siempre circuitos utilizados con poca frecuencia desperdicia energía y afecta negativamente el rendimiento de la batería. Por otra parte, los dispositivos móviles convencionales a menudo no pueden ejecutar tareas de manera eficiente con la energía en procesadores de propósito general. Tareas muy simples pueden ser realizadas por procesadores potentes, mientras que en tiempo real, tareas de baja latencia pueden ser realizadas por los procesadores menos potentes lo que resulta en un retraso no deseado.

El documento EP1335291A1 describe un sistema y un método de gestión de energía. La actual especificación ACPI define los datos que se deben guardar en un medio de almacenamiento no volátil para permitir la recuperación de un estado durmiente. Sin embargo, la especificación ACPI no se ocupa de la restauración del contexto del sistema después de un fallo de alimentación durante un estado durmiente. La imagen de RAM incluye todas las aplicaciones y datos que residen actualmente en la memoria RAM, junto con valores de registro de dispositivo que se pueden perder durante un estado de menor consumo de energía del sistema informático. Se apreciará que se necesita una cantidad significativa de tiempo para recopilar y guardar los datos requeridos para mantener el contexto del sistema de la máquina del cliente. Adecuadamente, el sistema y método de gestión de energía proporcionan la compresión de datos que representan el contexto memoria del sistema antes de que los datos de contexto de memoria del sistema se guarden en un medio de almacenamiento no volátil. Los resultados de compresión en un menor número de bytes necesitan ser guardados en el medio de almacenamiento no volátil. Esto, a su vez, ahorra energía ya que el medio de almacenamiento no volátil es operable por un período de tiempo más corto. Hay menos operaciones de lectura/escritura y preferentemente menos movimiento del disco de cabeza en el caso de un HDD.

30

El documento US2005/0132239A1 describe un sistema para controlar la ejecución de las tareas en un sistema procesador múltiple, que contiene un procesador de alto rendimiento y un procesador de alta eficiencia energética. Tras la recepción de una tarea que se ejecutará en el sistema procesador múltiple, el sistema determina si se debe ejecutar la tarea en el procesador de alto rendimiento o en el procesador energéticamente eficiente basado en los requisitos de rendimiento para las tareas y/o consideraciones de uso de energía para el sistema procesador múltiple. A continuación, el sistema ejecuta la tarea en el procesador de alto rendimiento o el procesador energéticamente eficiente basado en la determinación.

## Sumario

40

35

A continuación se presenta un resumen simplificado de algunas realizaciones de ejemplo para proporcionar una comprensión básica. Este resumen no es una extensa información general, y no pretende identificar elementos clave o críticos, o delimitar el alcance de las reivindicaciones. El siguiente sumario sólo presenta algunos conceptos y realizaciones de ejemplo en una forma simplificada como preludio a la descripción más detallada que se proporciona a continuación.

50

45

Aparatos y métodos pueden proporcionar un mejor consumo de energía apagando uno o más subsistemas de varios procesadores cuando no estén en uso. Los subsistemas de varios procesadores tienen cada uno una memoria no volátil que almacena datos de estado que se pueden recuperar con rapidez cuando sea necesario volver a encenderlos. Los subsistemas de varios procesadores pueden así parecer que están encendidos cuando, en realidad, no lo están.

60

55

Según al menos algunas realizaciones, aparatos y métodos incluyen la recepción de un comando de apagado en un primer subsistema que comprende un primer procesador, una primera memoria volátil, una primera memoria no volátil, un primer compresor/descompresor, y un primer circuito de control de potencia, estando la primera memoria volátil configurada para almacenar datos de estado relativos a las condiciones de funcionamiento del primer subsistema. En respuesta a la recepción de la orden de apagado, los aparatos y métodos pueden hacer que el primer compresor/descompresor comprima los datos de estado para generar datos de estado comprimido y para hacer que los datos de estado comprimido sean almacenados en la primera memoria no volátil. En respuesta al almacenamiento de los datos de estado comprimido en la primera memoria no volátil, los aparatos y métodos pueden hacer que el primer circuito de control de potencia apague el primer subsistema.

La invención tal como se define de acuerdo con el aparato de la reivindicación 1 y el método de la reivindicación 9.

## Breve descripción de los dibujos

Una comprensión más completa de la presente descripción y las ventajas de la misma pueden ser adquiridas por referencia a la siguiente descripción en la consideración de los dibujos adjuntos, en los que los números de referencia indican características iguales y en los que:

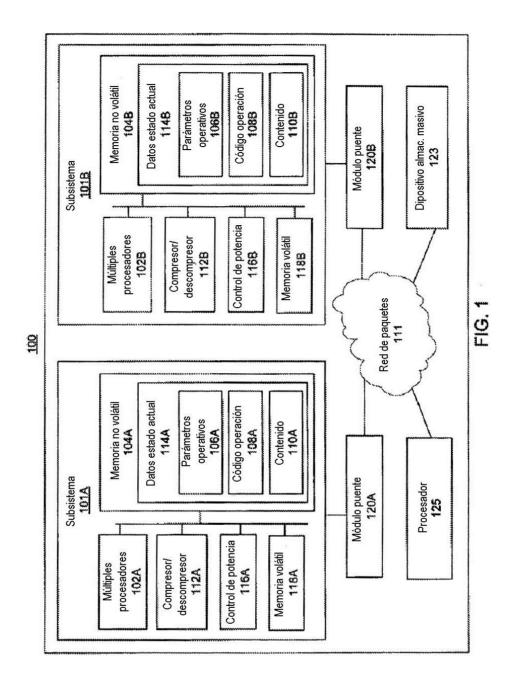

La figura 1 muestra un dispositivo ejemplar que tiene múltiples subsistemas de varios procesadores.

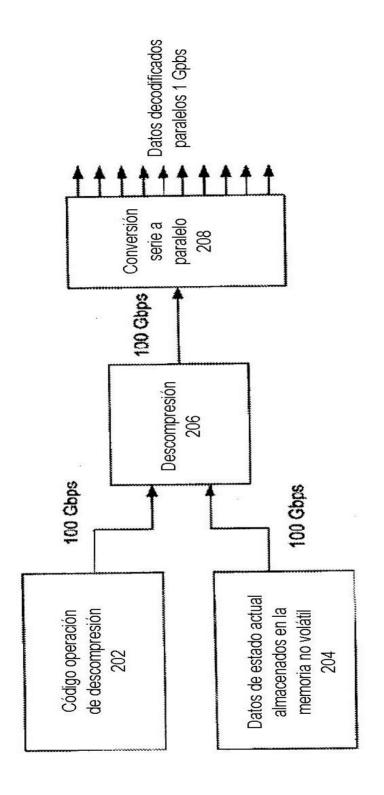

La figura 2 ilustra un diagrama de flujo de ejemplo para descomprimir los datos de estado actuales al volver a encender un subsistema.

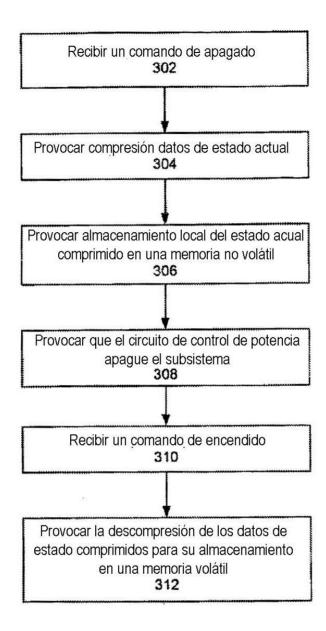

La figura 3 ilustra un diagrama de flujo de ejemplo de un método para activar y desactivar un subsistema.

#### Descripción detallada

15

10

En la siguiente descripción de las diversas realizaciones, se hace referencia a los dibujos adjuntos que forman parte de la misma, y en los que se muestran a modo de ilustración varias realizaciones en las que puede ponerse en práctica la invención. Es de entenderse que otras realizaciones pueden ser utilizadas y las modificaciones estructurales y funcionales se pueden hacer sin apartarse del alcance de la presente invención.

20

25

La figura 1 muestra un dispositivo de ejemplo 100 configurado para tener sus subsistemas de procesadores múltiples 101 A y 101B que aparecen como encendidos cuando en realidad ciertos subsistemas se han apagado. Los subsistemas 101 pueden recuperar los datos de estado almacenados localmente para volver a encenderse rápidamente. El dispositivo 100 puede ser, por ejemplo, un teléfono móvil, un ordenador, un PDA, un ordenador portátil u otro dispositivo informática. El dispositivo 100 puede incluir un procesador 125 y un dispositivo de almacenamiento masivo 123 que almacena instrucciones legibles por ordenador que, al ejecutarse, hacen que el dispositivo 100 realice las funciones descritas en el presente documento. Ejemplos de un dispositivo de almacenamiento masivo 123 incluyen un disco duro y una memoria Flash, así como otros tipos de dispositivos de almacenamiento masivo.

30

El dispositivo 100 también puede incluir múltiples subsistemas de procesadores múltiples 101. La figura 1, por ejemplo, representa un dispositivo 100 que tiene dos subsistemas 101A y 101B, pero el dispositivo 100 puede incluir cualquier número de subsistemas. El dispositivo 100 puede encender y apagar selectivamente uno o más de los subsistemas de procesador múltiple 101 en respectivos tiempos para controlar el consumo de energía. Por ejemplo, un teléfono móvil puede apagar un subsistema de procesador múltiple 101 que suministra una cámara cuando no esté en uso.

35

40

45

Los subsistemas de procesador múltiple 101 pueden incluir hardware y/o software optimizado para realizar una tarea informática particular basada en, por ejemplo, requisitos de latencia y ancho de banda de procesamiento. Un subsistema 101 puede ser una unidad de propósito limitado que se comunica con otros subsistemas con mensajes, como el descrito en la solicitud US 11/999.314, presentada el 4 de diciembre de 2007, titulada "Arquitectura de multiprocesador para un dispositivo", y publicada como US 2009/0141654. Cada subsistema 101 puede ser optimizado para uno o un número limitado de propósitos. Como tal, un subsistema 101 puede usar el procesamiento de hardware muy eficiente en lugar de software. El hardware de procesamiento puede usar la lógica fija con una pequeña cantidad de software almacenado en la memoria no volátil 104 para dar cierta flexibilidad. Por ejemplo, el dispositivo 100 puede ser un teléfono móvil que ejecuta un sistema operativo sencillo (por ejemplo, Symbian) que proporciona principalmente un controlador de interfaz de usuario. El sistema operativo puede procesar la entrada del usuario (por ejemplo, tomar un clip de vídeo) recibida por el controlador de interfaz de usuario para generar y asignar solicitudes de tareas a los subsistemas optimizados 101.

50

55

60

El dispositivo 100 puede asignar tareas a los subsistemas de procesador múltiple 101 basado en las características de rendimiento requeridas para realizar una tarea informática particular. Por ejemplo, el dispositivo 100 puede recibir una solicitud para realizar una tarea, puede determinar qué subsistema de procesador múltiple 101 es adecuado para llevar a cabo la tarea solicitada, y puede hacer que el subsistema de procesador múltiple 101 identificado realice la tarea. Por ejemplo, un subsistema 101A se puede optimizar para realizar la descompresión y puede recibir una solicitud de tarea con instrucciones para descomprimir un número predeterminado de tramas de datos en una imagen de 1920x1080 píxeles y enviarla a un subsistema de visualización 101B. Como otro ejemplo, un subsistema 101A puede ser capaz de realizar una tarea que requiere una latencia de tiempo real, muy baja, y la informática de ancho de banda alto, tales como para el tratamiento de los datos gráficos en aplicaciones de juegos. Un subsistema 101B diferente puede ser capaz de realizar una tarea que soporta la manipulación de datos del sensor que normalmente tiene latencias muy largas sin degradación del rendimiento. Ejemplo de subsistemas de procesadores múltiples 101 pueden incluir ordenadores, procesadores de video, ordenadores de nanotecnología, un subsistema Audio Codec, un Audio Codec que incluye un amplificador de potencia de altavoces estéreo con un amplificador de auriculares estéreo.

65

Con realizaciones tales como las mostradas en la figura 1, los subsistemas de procesador múltiple 101 pueden ser

de varios tipos, incluyendo: (1) un bus multipunto que utiliza multiplexación por división de tiempo para los subsistemas de procesador múltiple para aplicaciones que tienen una pequeña cantidad de datos a transmitir entre procesadores, pero tiene conexiones entre todos los procesadores de la unidad de procesador múltiple; (2) subsistemas de procesador múltiple de red conmutada (circuito conmutado) utilizando conexiones punto a punto de muy baja latencia a través de una red de tipo interruptor de barra cruzada; (3) un subsistema de procesador múltiple de red de paquetes conmutados para aplicaciones que toleran una larga latencia pero requieren muy gran ancho de banda; y (4) un dispositivo de bloque compartido para procesadores múltiples. Un ejemplo de implementación de un dispositivo de bloque compartido es el uso compartido de un SDRAM o FIFO por varios procesadores que ejecutan el mismo sistema operativo. La memoria compartida permite que dos o más procesos accedan a estructuras de datos comunes colocándolas en un segmento de memoria compartida. El dispositivo de bloque compartido puede ser utilizado como un soporte de hardware o una aceleración de hardware de la mensajería OS (por ejemplo, un sistema de comunicación entre procesos V (IPC)).

10

15

20

25

30

35

40

45

50

55

60

65

Los subsistemas de procesador múltiple 101 se pueden conectar entre sí a través de módulos de puente 120, en el que uno de los lados (hacia la red de paquetes 111) utiliza un protocolo de red de paquetes y el hardware (por ejemplo, SpaceWire o UniPro2) y el otro (hacia el subsistema de procesador múltiple 101) utiliza un protocolo y un hardware específico para el subsistema procesador múltiple 101 asociado. Un ejemplo de la arquitectura del dispositivo 100, incluyendo módulos de puente, tales como el descrito en la solicitud US 17/999.314, presentada el 4 de diciembre de 2007, titulada "Arquitectura de multiprocesador para un dispositivo", y publicada como US 2009/0141654.

Los subsistemas de procesadores múltiples 101 pueden conectarse a la red central de paquetes 111 usando una interfaz como SpaceWire (CESS-E50-04A) o la industria móvil de interfaz del procesador (MIPI) de protocolo de alianza universal (UniPro2). UniPro2 y SpaceWire son sólo ejemplos de los protocolos de red de paquetes. Otros protocolos de red de paquetes (por ejemplo, Internet) pueden ser utilizados. Muchos métodos de comunicación (por ejemplo, MIPI D-PHY y M-PHY que se utilizan con UniPro2) puede tener múltiples modos de comunicación con diferentes velocidades, y el dispositivo 100 pueden instruir a un subsistema 101 para utilizar un modo particular. Por ejemplo, el dispositivo 100 puede utilizar un sistema de supresión de ruidos para despertar un subsistema 101, y especificar los modos de baja velocidad o de alta velocidad para el control y súper velocidad para la transmisión de gran ancho de banda.

Un dispositivo 100 que es un teléfono móvil, por ejemplo, puede incluir subsistemas relativamente independientes 101 que se comunican a través de la red de paquetes central 111 usando métodos basados en paquetes de bajo consumo como MIPI UniPro y M-PHY. La red de paquetes central 111 puede ser sin conexión (es decir, los datos se envían desde un punto a otro sin acuerdo previo). Sin embargo, se pueden usar otros protocolos de red sin conexión y orientados a la conexión.

Mientras que la realización mostrada en la figura 1 incluye una única red de paquetes central 111, algunas realizaciones de la invención pueden utilizar una red de comunicación que tiene cualquier número de redes, en el que ninguna red particular puede ser considerada central dado que las redes están simplemente conectadas entre sí. Las conexiones pueden formar una cadena de redes o una red de redes.

Cada subsistema 101 puede incluir procesadores múltiples 102, una memoria no volátil 104, un compresor/descompresor 112, un circuito de control de potencia 116, y una memoria volátil 118. Los procesadores múltiples 102 pueden interactuar entre sí mediante un bus, una red de paquetes, un conmutador de barras cruzadas, u otra ruta de comunicación. La memoria volátil 118 y/o la memoria no volátil 104 pueden almacenar instrucciones ejecutables por ordenador que, cuando son ejecutadas por uno o más de los procesadores múltiples 102, hacen que el subsistema 101 realice las funciones descritas en el presente documento. En un ejemplo de realización, la memoria no volátil 104 puede ser una memoria espintrónica compuesta de transistores de grafeno. Una memoria espintrónica también puede ser denominada como una memoria de transferencia de par de giro. Empresas que desarrollan la memoria de acceso aleatorio de par de transferencia de giro (STT-RAM) incluyen Everspin, Grandis, Hynix, IBM, Samsung, TDK y Toshiba. La memoria no volátil 104 también puede ser una de cambio de fase (PCM) disponible comercialmente en Numonyx, una memoria de acceso aleatorio ferroeléctrico (FeRAM), un biestable magnético (MFF), o un dispositivo de efecto de campo de grafeno.

Por ejemplo, la memoria no volátil 104 puede ser un almacenamiento FeRAM capaz de almacenar 128 Megabits y que tiene velocidades de lectura/escritura de 1,6 Gigabytes por segundo. La memoria no volátil 104 puede ser también un MFF donde las operaciones del MFF se producen mediante la integración del biestable de datos (DFF) con uniones magnéticas de túnel (MTJ), además de los circuitos que cambian la dirección de la magnetización de las MTJ. Durante el funcionamiento, el MFF puede estar diseñado para evitar que la MTJ afecte la frecuencia de reloj MFF, ya que puede funcionar a la misma frecuencia (por ejemplo, 3,5 GHz) como el DFF. La memoria no volátil 104 también puede ser una memoria no volátil de efecto de campo grafeno y, en un ejemplo, puede tener una diferencia de 5 órdenes de magnitud en la resistividad entre los estados activado y desactivado. Otras tecnologías de memoria no volátil también se pueden utilizar.

El circuito de control de potencia 116 puede apagar y encender el subsistema 101 en respuesta a los comandos

recibidos desde el procesador 125 u otros subsistemas 101. En un ejemplo, el circuito de control de potencia 116 puede incluir un inversor CMOS y un interruptor de alimentación, donde el inversor CMOS que enciende/apaga un interruptor de potencia que controla la distribución de energía al subsistema 101. Un inversor CMOS puede consumir poca energía (por ejemplo, nanovatios o microvatios). En otra realización, se puede utilizar un bus de circuito interintegrado (I<sup>2</sup>C). También se pueden usar otros tipos de circuitos de control de potencia. El circuito de control de potencia 116 se puede utilizar para apagar completamente el subsistema 101, o puede haber varios niveles de estados de ahorro de energía, que se definen, por ejemplo, en los estándares MIPI D-PHY y M-PHY.

Antes de apagarse, un subsistema 101 puede almacenar datos de estado actuales 114 en la memoria no volátil 104 para la recuperación rápida y la restauración de un estado anterior en la memoria volátil 118 al ser alimentado de nuevo. Los datos de estado actuales 114 se pueden almacenar en la memoria no volátil local 104 cuando el subsistema 101 está apagado o cuando un estado de ahorro de energía perdería información importante. Los datos de estado actuales 114 pueden incluir condiciones de funcionamiento tales como, pero no limitadas a, los parámetros de operación 106, el código de operación 108, y el contenido110. El funcionamiento de los parámetros 106 pueden ser parámetros en los que se iniciará el modo comunicación en el siguiente encendido. Parámetros de ejemplo pueden ser utilizados en la compresión JPEG basada en hardware. El código de operación 108 puede ser un código de tiempo de ejecución ejecutable. El código de operación de ejemplo incluye un sistema operativo (OS), tal como, pero no limitado a, Symbian, Linux o DOS. El código de operación 108 es un ejemplo de instrucciones ejecutables por ordenador. El contenido 110 puede ser un sistema operativo Symbian OS.

20

25

30

35

40

65

10

Los subsistemas de varios procesadores 101 pueden acceder a sus respectivas memorias no volátiles 104 significativamente más rápido de lo que pueden acceder a un dispositivo de almacenamiento masivo 123 compartido por todos los subsistemas de varios procesadores 101. Al encender, puede tomar mucho más tiempo para los subsistemas de varios procesadores 101 cargar los datos desde el dispositivo de almacenamiento masivo 123 en comparación con el tiempo necesario para cargar datos de sus respectivas memorias no volátiles locales 104. Por ejemplo, si el dispositivo 100 es un ordenador personal de la empresa (PC) que tiene varios subsistemas 101, pero sin memorias no volátiles 104, a continuación, cada uno tendría que cargar datos desde el dispositivo de almacenamiento masivo 123 cuando el PC se enciende y de ese modo consume mucho tiempo acceder a los datos, independientemente de la frecuencia con que se utiliza un determinado subsistema 101. Proporcionar cada subsistema 101 con una memoria no volátil local 104 ventajosamente no requiere encender enlaces en serie para leer datos desde el dispositivo de almacenamiento masivo 123.

En otro ejemplo, el uso de los canales de transmisión compartidos, como la implementación de la red de paquetes 111 como una red UniPro2, puede crear latencia ya que debido a las dificultades en el uso eficiente del ancho de banda disponible cuando el dispositivo 100 se compone de dos subsistemas lento y rápido 101 que son dinámicamente lógicamente conectados y desconectados del dispositivo 100 (es decir, apagados/encendidos o incluso físicamente desconectados quitando el cable). Por ejemplo, cargar un sistema operativo de 200 MB utilizando la red de 1 Gbps UniPro2 sólo podrá exigir (200Mbit x 8 = 1600) 1,6 segundos, pero cuando el ancho de banda se comparte con otras aplicaciones, el tiempo de carga puede aumentar significativamente. Al almacenar localmente el contenido del sistema operativo en la memoria no volátil 104 en el mismo paquete de circuito integrado (IC) como procesadores múltiples 102, una interfaz paralela de 128 bits podría cargar 1600 Mbits de contenido de sistema operativo en 62.5 ms utilizando una interfaz de memoria de 200 Mbps. Por lo tanto, un subsistema 101 que tiene su propia memoria no volátil 104 puede producir mejoras significativas.

Por otra parte, un cuello de botella podría ocurrir en los sistemas convencionales al encender el PC cuando múltiples 45 subsistemas 101 podría intentar simultáneamente acceder al dispositivo de almacenamiento masivo 123. Proporcionar a cada subsistema 101 con su propia memoria no volátil 104 como se describe aquí ventajosamente disminuye el tiempo de encendido cuando los subsistemas 101 pueden intentar acceder simultáneamente a sus respectivas memorias no volátiles locales 104, en lugar de competir entre sí para acceder al dispositivo de almacenamiento masivo 123 como en los sistemas convencionales. Un tiempo de encendido se refiere a la cantidad 50 de tiempo entre el momento en que un subsistema 101 es provisto primero con energía cuando el subsistema 101 puede procesar los datos recibidos desde o enviar datos a través de la red de paquetes 111. Además, en el arranque, el dispositivo 100 puede alimentar individualmente los subsistemas de procesador múltiple 101, según sea necesario, dejando otros apagados lo que resulta en ahorros de energía por no alimentar subsistemas 101 55 innecesarios. Además, al tener memorias no volátiles 104 distribuidas, una cantidad significativa de la transferencia de datos hacia y desde el dispositivo de almacenamiento masivo 123 puede ser evitada. La cantidad total de la capacidad de almacenamiento también se puede reducir debido a que cada subsistema de procesador múltiple 101 almacena localmente sus datos en su memoria no volátil 104. La reducción se puede lograr cuando los procesadores múltiples 102 de cada subsistema 101 están optimizados para las tareas que realizan y el sistema 60 operativo se puede adaptar a la tarea y el hardware del procesador.

Para apagar un subsistema 101, el dispositivo 100 puede comunicar un comando de apagado para instruir a un determinado subsistema 101 para que se apague. Un subsistema 101 también puede comunicar los comandos de encendido y apagado de otros subsistemas. En un ejemplo de realización, el dispositivo 100 puede supervisar la actividad de los subsistemas 101 para determinar si se debe encargar a uno o más que se apague. El dispositivo 100 puede emitir un comando de apagado en respuesta a la actividad monitorizada de un subsistema 101 que cae

por debajo de un nivel umbral de actividad, al terminar el usuario una aplicación proporcionada por el subsistema 101, expiración de un temporizador, que el usuario apaque el dispositivo 100, o en respuesta a otros eventos. Por ejemplo, los subsistemas no críticos en el tiempo 101 pueden apagarse si no hay tareas activas y no hay solicitudes de tareas que se hayan recibido dentro del período de tiempo predeterminado. Antes de apagar, el subsistema 101 puede almacenar los datos de estado actuales 114 incluyendo el código de operación 108, el contenido 110, y los parámetros 106 en su memoria no volátil local 104, y no en el dispositivo de almacenamiento masivo en todo el dispositivo 123. Si la memoria no volátil local 104 está completamente llena, sin embargo, el subsistema de procesador múltiple 101 puede almacenar los datos del estado actuales que permanecen en el dispositivo de almacenamiento masivo 123.

10

25

30

35

40

45

60

65

En algunas realizaciones, tras la recepción de la orden de apagado, un subsistema 101 instruye al compresor/descompresor 112 para comprimir los parámetros de operación, el contenido, y el código de operación almacenado en la memoria volátil 118, y el compresor/descompresor 112 hace que el código de operación, contenido y parámetros comprimidos se almacenen en la memoria no volátil 104. La compresión puede ser omitida si una memoria no volátil 104 tiene suficiente capacidad de almacenamiento con un tiempo de lectura lo suficientemente rápido. Si la memoria no volátil 104 tiene un tiempo de lectura demasiado lento, puede ser más rápido para leer una pequeña cantidad de datos comprimidos y luego descomprimir los datos comprimidos con un circuito de descompresión rápida. Por ejemplo, si la memoria no volátil 104 tiene un tiempo de lectura lenta, puede ser más rápido para leer un archivo de imagen comprimido y descomprimirlo en una imagen de alta resolución en

20 lugar de leer una versión comprimida del archivo de imagen.

Almacenar localmente los datos de estado actuales en una memoria no volátil 104 puede reducir el consumo de energía y el tiempo necesario para encender de nuevo porque el subsistema 101 no tiene que recuperar los datos del estado actuales 114 desde el dispositivo de almacenamiento masivo 123. Además, una memoria no volátil 104 puede almacenar datos incluso cuando está apagado reduciendo así el consumo de energía del dispositivo 100. Por ejemplo, la lectura del dispositivo de almacenamiento masivo 123 requiere encender enlaces en serie (por ejemplo, UniPro2) entre un subsistema 101 y el almacenamiento masivo 123. Esto puede llevar mucho tiempo y requiere un suministro de energía tanto para el subsistema 101 y el almacenamiento masivo 123 durante una transferencia que podría tomar segundos. Después del almacenamiento, el subsistema 101 hace que el circuito 116 de control de potencia apague el subsistema 101.

Debido a que las tareas de cálculo pueden ser asignados a un determinado subsistema 101 y llevarse a cabo localmente en el subsistema asignado 101, la cantidad de código de operación 108 normalmente es lo suficientemente pequeño que los compresores basados en hardware/descompresores locales 112 pueden comprimir/descomprimir el código de operación 108 dentro de una cantidad limitada de tiempo (por ejemplo, dentro de un microsegundo) dando al usuario del dispositivo 100 la impresión de que cada uno de los subsistemas de procesador múltiple 101 está encendido todo el tiempo, cuando, de hecho, no lo están. Por ejemplo, el código de operación local 108 dedicado a hardware y software de un subsistema 101 puede incluir sólo unos cientos de líneas de código, pero en algunos casos, el código de operación para un sistema operativo (por ejemplo, Symbian OS) puede ser grande (por ejemplo, 1 GB o más), lo que requiere una gran cantidad de almacenamiento en la memoria no volátil local 104.

El compresor/descompresor 112 también puede implementarse en software dependiendo de los requisitos de rendimiento. Tiempos de compresión/descompresión largos se pueden tolerar, siempre y cuando la tarea informática a ser realizada por un subsistema 101 es relativamente mayor que el tiempo requerido para la compresión/descompresión para dar al usuario la impresión de que están disponibles los servicios prestados por los subsistemas 101 sin dilaciones indebidas. Cuando está apagado, el circuito 116 de control de potencia puede controlar la red de paquetes 111 para un comando de encendido.

En algún momento posterior, el dispositivo 100 u otro subsistema 101 pueden decidir usar la energía de seguridad 50 de un subsistema 101 y comunicar un comando de encendido al subsistema 101 a través de la red de paquetes 111. Por ejemplo, el dispositivo 100 puede determinar que el usuario ha solicitado una tarea informática adecuada para ser realizada por un subsistema de apagado 101. También, un subsistema 101 puede despertar en períodos de tiempo predeterminados cuando se programa una tarea a realizar. Por ejemplo, los subsistemas de módem celular o 55 WLAN pueden tener un intervalo de tiempo predefinido cuando se transmiten datos a un usuario particular en la interfaz de aire.

Cuando se utiliza la energía de seguridad, el subsistema 101 puede recuperar los datos actuales del estado comprimido 114 de la memoria no volátil 104 e instruir al compresor/descompresor 112 para llevar a cabo la descompresión para recuperar los datos de estado actuales. El subsistema 101 puede entonces provocar que los datos de estado actuales sean almacenados en la memoria volátil 118 para recuperar su estado antes de que se apague. Por ejemplo, los datos de estado actuales 114 pueden ser sin comprimir y se carga en la memoria volátil 118 que puede ser una memoria de acceso aleatorio estática (SRAM). Además, la memoria volátil 118 se puede omitir y los datos de estado actual se pueden comprimir y usarse directamente desde la memoria no volátil 104 si están concebidos para funcionar como la memoria ejecutable similar a una RAM.

La figura 2 ilustra un diagrama de flujo de ejemplo para descomprimir los datos actuales del estado 114 al volver a encender un subsistema 101. La realización representada ofrece una descompresión ultra-rápida del código de operación comprimido almacenado en un formato de serie utilizando transistores de grafeno de terahercios (THz) y la conversión en datos en paralelo para un Sistema de 1 gigahercio (GHz) CMOS. Tradicionalmente, la descompresión se hace usando datos en paralelo y procesadores paralelos usando buses paralelos anchos funcionando a 100 MHz a 4 GHz (por ejemplo, en PCs).

El compresor/descompresor 112 puede realizar cálculos utilizando el contenido de datos de 1-bit en serie y el código de 1 bit con una frecuencia ultra alta. El compresor/descompresor 112 puede realizar directamente la compresión o descompresión de datos (por ejemplo, vídeo) con datos en serie procedentes de una memoria no volátil IC que tiene un puerto de serie de ultra alta frecuencia. Por ejemplo, el puerto serie de ultra alta frecuencia proporciona datos a 5-50 Gbps o incluso en tasas de bits Tbps o superiores. Ventajosamente, la realización de cálculos utilizando contenido de datos de 1 bit serial y el código de 1 bit a una frecuencia de ultra alta permite el uso de elementos de informática ultra-rápidos, y la serie de datos se convierte entonces en una forma paralela para su uso por los procesadores CMOS. Debido a que los elementos de informática ultra rápidos actuales aún no pueden ser lo suficientemente madura para la producción en serie a gran escala similar a CMOS de silicio, estructuras informáticas especiales para el compresor/descompresor 112, así como las otras unidades de procesamiento (por ejemplo, procesadores 102, etc.), pueden estar compuestas de un pequeño número de elementos activos, tales como, pero no limitados a, el grafeno/nanotubos de transistores de tipo FET, nanotubos de carbono (CNT), o diodos túnel de resonancia (IDT) basados en puertas lógicas.

10

20

25

30

35

40

45

50

En el bloque 202, el compresor/descompresor 112 puede recuperar el código de operación descompresor de código de operación 108 almacenado en la memoria no volátil 104. En el bloque 204, el compresor/descompresor 112 puede recuperar los datos actuales del estado 114 almacenados en la memoria no volátil 104 en un formato comprimido a una velocidad de 100 Gigabits por segundo (Gbps). En el bloque 206, el compresor/descompresor 112 puede descomprimir los datos de estado actuales comprimidos a una velocidad de 100 Gbps. En el bloque 208, el compresor/descompresor 112 puede realizar la conversión de serie a paralelo de los datos descomprimidos a una velocidad de 100 Gbps para producir 1 Gpbs paralelo de datos descomprimidos. En algunos sistemas, los procesadores CMOS y otras estructuras informáticas están diseñados para utilizar los datos en paralelo. La conversión de contenido descomprimido desde un formato de serie en formato paralelo permite utilizar los procesadores CMOS y otras estructuras informáticas.

Para reducir aún más el consumo de energía, el dispositivo 100 puede limitar la cantidad de información transmitida entre subsistemas de procesador múltiple 101 a través de la red de paquetes 111. Cuando un subsistema de procesador múltiple 101 realiza una tarea que cambia cualquiera de los parámetros de operación, el contenido y el código de operación utilizados por al menos otro subsistema 101, el subsistema de procesador múltiple 101 puede comunicar un mensaje de cambio a través de la red de paquetes 111 al por lo menos otro subsistema 101. El mensaje de cambio puede incluir sólo la información que describe el cambio ("información de cambio") en un formato comprimido, y no todos los datos afectados por el cambio.

En un ejemplo, un dispositivo 100 puede ser un teléfono móvil que tiene un subsistema de cámara de video 101A y un subsistema de pantalla 101B. El subsistema de cámara de vídeo 101A inicialmente capta datos de contenido de imagen y comunica los datos del contenido de la imagen al subsistema 101B de pantalla para la visualización. Con el tiempo, la cámara de vídeo del subsistema 101A capta nuevos datos de contenido de la imagen y determina la diferencia con los datos del contenido de la imagen anterior. El subsistema de cámara de vídeo 101A comunica entonces los datos modificados (por ejemplo, los píxeles modificados), y no todos los nuevos datos de contenido de imagen, al subsistema de pantalla 101B. El subsistema de pantalla 101B luego modifica los datos de contenido de imagen anteriores utilizando los datos de cambio para generar datos de contenido de imagen actualizados para su visualización. Este método también puede usarse para otros tipos de dispositivos que muestran contenido, tales como, pero no limitados a, la transmisión de contenido de la televisión digital terrestre/cable/satélite que comunica imágenes a intervalos predeterminados (por ejemplo, cada 20 ms) y los marcos de referencia con menos frecuencia. Los cambios en un marco de referencia no pueden ser enviados hasta que se envía un marco de referencia siguiente.

La figura 3 ilustra un diagrama de flujo de ejemplo de un método para encender y apagar un subsistema. En el bloque 302, el método puede incluir recibir una orden de apagado. El dispositivo 100 puede determinar que uno de sus subsistemas 101 se utiliza con poca frecuencia y puede ser apagado. El dispositivo 100 puede comunicar un comando de apagado al subsistema 101 a través de la red de paquetes 111.

En el bloque 304, el método puede incluir causar la compresión de datos de estado actuales para los subsistemas. El subsistema 101 puede hacer que los datos de estado actuales sean proporcionados al compresor/descompresor 112 de la memoria volátil 118 junto con una instrucción de compresión para hacer que el compresor/descompresor 112 comprima los datos de estado actuales. Por ejemplo, un conjunto de datos actuales del estado podría ser un sistema operativo (OS), parámetros de comunicación especificando qué tasa de bits utilizar cuando enciende el siguiente, y una fotografía de pantalla para mostrar.

En el bloque 306 el método puede incluir causar el almacenamiento local de los datos actuales del estado comprimido en una memoria no volátil. El compresor/descompresor 112 puede comunicar los datos de estado actuales comprimidos para su almacenamiento en la memoria no volátil 104.

5 En el bloque 308, el método puede incluir hacer que un circuito de control de potencia apague el subsistema 101 en respuesta a los datos de estado actuales comprimidos que se almacenan en la memoria no volátil 104.

En el bloque 310, el método puede incluir recibir una orden de encendido. El dispositivo 100 puede determinar que un subsistema 101 es adecuado para llevar a cabo una determinada tarea informática, y puede comunicar un comando de encendido a ese subsistema 101. El circuito de control de potencia 116 puede causar que el subsistema se encienda en respuesta a recibir el comando de encendido. El comando de encendido puede identificar el tipo de tarea a realizar o el subsistema 101 puede informar al dispositivo 100 de la tarea después de que se haya encendido.

10

25

30

En el bloque 312, el método puede incluir la recuperación y descompresión de datos de estado actuales para restaurar el estado del subsistema en respuesta a recibir el comando de encendido. El subsistema 101 puede hacer que el compresor/descompresor 112 recupere los datos de estado actuales comprimidos 114 desde la memoria no volátil 104 y descomprimir los datos de estado actuales. El compresor/descompresor 112 puede entonces provocar que los datos de estado actuales para ser almacenados en la memoria volátil 118 para recrear el estado anterior antes de apagarse. El método de la figura 3 puede entonces terminar.

En consecuencia, el dispositivo 100 puede instruir a uno o más subsistemas de procesadores múltiples 101 que no se están utilizando actualmente para apagarse, reduciendo así el consumo de energía estática que se produciría cuando un determinado subsistema 101 se enciende a pesar de que actualmente no está en uso. Una memoria no volátil 104 puede almacenar localmente datos de estado actuales 114 que permiten a un subsistema 101 restaurar rápidamente su estado anterior a aparecer como si estuviera encendido a pesar de estar apagado.

Como puede apreciarse por un experto en la técnica, un sistema informático con un medio que contiene instrucciones legibles por ordenador asociadas para controlar el sistema informático puede ser utilizado para implementar las realizaciones ejemplares que se dan a conocer en el presente documento. El sistema de ordenador puede incluir al menos un ordenador tal como un microprocesador, procesador de señal digital, y circuitería electrónica periférica asociada.

#### REIVINDICACIONES

1. Un aparato (100), que comprende:

15

20

25

45

- un primer subsistema (101A) que comprende un primer procesador (102A), una primera memoria volátil (118A), una primera memoria no volátil (104A), un primer compresor/descompresor (112A) y un primer circuito de control de potencia (116A), estando configurada la primera memoria volátil (118A) para almacenar unos primeros datos (114A), relativos a las condiciones operativas del primer subsistema (101A);

- un segundo subsistema (101B) que comprende un segundo procesador (102B), una segunda memoria volátil (118B), una segunda memoria no volátil (104B), un segundo compresor/descompresor (112B) y un segundo circuito de control de potencia (116B), estando configurada la segunda memoria volátil (118B) para almacenar unos segundos datos (114B) relativos a las condiciones operativas del segundo subsistema (101 B); y un tercer procesador (125) acoplado al primer (101A) y al segundo (101B) subsistemas, en donde el tercer

- procesador (125) está configurado para generar un comando de apagado al primer subsistema (101A) al determinar que el primer subsistema (101A) no es necesario, y

- en donde el primer procesador (102A) está configurado para realizar:

- tras la recepción del comando de apagado, hacer que el primer compresor/descompresor (112A) comprima los primeros datos (114A) para generar unos primeros datos comprimidos (114A), para hacer que los primeros datos comprimidos (114A) se almacenen en la primera memoria no volátil (104A) y para hacer que el primer circuito de control de potencia (116A) apague el primer subsistema (101A).

- 2. El aparato (100) de la reivindicación 1, en el que el primer procesador (102A) está configurado además para realizar:

- al recibir un comando de encendido del tercer procesador (125), hacer que el primer compresor/descompresor (112A) descomprima los primeros datos comprimidos (114A) desde la primera memoria no volátil (104A) y para hacer que los primeros datos descomprimidos (114A) se almacenen en la primera memoria volátil (118A).

- 30 3. El aparato (100) de la reivindicación 2, en el que el primer subsistema (101A) está configurado para realizar una tarea de cálculo utilizando los primeros datos descomprimidos (114A) después del almacenamiento en la primera memoria volátil (118A).

- 4. El aparato (100) de la reivindicación 1, en el que el primer subsistema (101A) está configurado para:

- realizar una tarea que cambia los segundos datos (114B); y comunicar al segundo subsistema (101B) un mensaje de cambio que identifica el cambio en los segundos datos (114B).

- 40 5. El aparato (100) de la reivindicación 1, en el que la primera memoria no volátil (104A) es una memoria espintrónica.

- 6. El aparato (100) de la reivindicación 1, en el que el primer subsistema (101A) está configurado para comunicar un segundo comando de apagado al segundo subsistema (101B).

- 7. El aparato (100) de la reivindicación 1, en el que el tercer procesador (125) está configurado para monitorizar un nivel de actividad del primer subsistema (101A), y en el que el tercer procesador (125) genera el comando de apagado en respuesta al nivel de actividad que cae por debajo de un nivel de actividad umbral.

- 8. El aparato (100) de la reivindicación 1, en el que los primeros datos (114A) comprenden uno o más de parámetros de operación (106A), un código de operación (108A) y contenido (110A) asociado al primer subsistema (101A), y los segundo datos (114B) comprenden uno o más de parámetros de operación (106B), un código de operación (108B) y contenido (110B) asociado al segundo subsistema (101B).

- 9. Un método de uso de un aparato (100), comprendiendo el aparato (100):

- un primer subsistema (101A) que comprende un primer procesador (102A), una primera memoria volátil (118A), una primera memoria no volátil (104A), un primer compresor/descompresor (112A) y un primer circuito de control de potencia (116A), estando configurada la primera memoria volátil (118A) para almacenar unos primeros datos (114A) relativos a las condiciones operativas del primer subsistema (101A); un segundo subsistema (101B) que comprende un segundo procesador (102B), una segunda memoria volátil (118B), una segunda memoria no volátil (104B), un segundo compresor/descompresor (112B) y un segundo circuito de control de potencia (116B), estando configurada la segunda memoria volátil (118B) para almacenar

- 65 unos segundos datos (114B) relativos a las condiciones operativas del segundo subsistema (101B); y un tercer procesador (125) acoplado al primer (101A) y al segundo (101B) subsistemas,

#### comprendiendo el método:

recibir un comando de apagado desde el tercer procesador (125) en el primer subsistema (101A); en respuesta a la recepción del comando de apagado, haciendo que el primer compresor/descompresor (112A) comprima los primeros datos (114A) para generar unos primeros datos comprimidos (114A) y para hacer que los primeros datos comprimidos (114A) se almacenen en la primera memoria no volátil (104A); y en respuesta al almacenamiento de los primeros datos comprimidos (114A) en la primera memoria no volátil (104A), hacer que el primer circuito de control de potencia (116A) apague el primer subsistema (101A).

10

15

30

5

10. El método de la reivindicación 9, que comprende además:

recibir un comando de encendido; y

- en respuesta al comando de encendido, hacer que el primer compresor/descompresor (112A) descomprima los primeros datos comprimidos (114A) desde la primera memoria no volátil (104A) y provocar el almacenamiento de los primeros datos descomprimidos (114A) en la primera memoria volátil (118A).

- 11. El método de la reivindicación 10, que comprende además realizar, mediante el primer subsistema (101A), una tarea de cálculo utilizando los primeros datos descomprimidos (114A) después de su almacenamiento en la memoria

volátil (118A).

- 12. El método de la reivindicación 9, que comprende además:

- realizar, mediante el primer subsistema (101A), una tarea que cambia los segundos datos (114B); y comunicar al segundo subsistema (101B) un mensaje de cambio que identifica el cambio en los segundos datos (114B).

- 13. El método de la reivindicación 9, que comprende además la comunicación, mediante el primer subsistema (101A), de un segundo comando de apagado al segundo subsistema (101B).

- 14. El método de la reivindicación 9, que comprende además la monitorización de un nivel de actividad del primer subsistema (101A), en donde el comando de apagado se genera en respuesta al nivel de actividad que cae por debajo de un nivel de actividad umbral.

- 15. Un medio legible por ordenador que tiene instrucciones ejecutables por ordenador que, al ejecutarse, hacen que un procesador (125) realice el método de cualquiera de las reivindicaciones 9 a 14.

FIG. 2

FIG. 3