# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 549 687

51 Int. Cl.:

H04L 27/227 (2006.01) H04B 1/7085 (2011.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

**T3**

- (96) Fecha de presentación y número de la solicitud europea: 28.07.2006 E 06788632 (5)

(97) Fecha y número de publicación de la concesión europea: 15.07.2015 EP 1913748

- (54) Título: Demodulación de datos QPSK o DQPSK mejorada para señales en sistemas de ensanchamiento por secuencia directa (DSS) utilizando secuencias de ensanchamiento ortogonales o cuasi-ortogonales

- (30) Prioridad:

21.12.2005 US 314123 28.07.2005 US 703316 P

Fecha de publicación y mención en BOPI de la traducción de la patente: **30.10.2015**

(73) Titular/es:

EXELIS INC. (100.0%) 2235 Monroe Street Herndon, VA 20171, US

(72) Inventor/es:

RASMUSSEN, DONALD, JOHN

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

#### **DESCRIPCIÓN**

Demodulación de datos QPSK o DQPSK mejorada para señales en sistemas de ensanchamiento por secuencia directa (DSS) utilizando secuencias de ensanchamiento ortogonales o cuasi-ortogonales

#### CAMPO TÉCNICO

5

10

15

20

25

30

La presente invención se refiere, en general, a sistemas de comunicaciones. De manera más específica, se refiere a demodulación de datos QPSK o DQPSK para señales en sistemas de ensanchamiento por secuencia directa (DSS, direct sequence spreading) que utilizan secuencias de ensanchamiento ortogonales o cuasi-ortogonales.

#### ANTECEDENTES DE LA INVENCIÓN

La Modulación de datos por Desplazamiento de Fase en Cuadratura (QPSK, *Quadrature Phase Shift Keying*) se utiliza para aumentar la velocidad de transmisión de datos en comparación con la Modulación de datos por Desplazamiento de Fase Binaria (BPSK, *Binary Phase Shift Keying*). Para mejorar el rendimiento de datos en condiciones de canales multi-trayecto y para reducir la densidad espectral de potencia transmitida, se utilizan las técnicas de ensanchamiento por secuencia directa en la modulación de datos. La detección diferencial de datos se lleva a cabo para simplificar el proceso de demodulación, dando como resultado una recepción QPSK diferencial (DQPSK). La señal 802.11b existente proporciona modulación de datos tanto DBPSK como DQPSK utilizando una señal BPSK para el ensanchamiento por secuencia directa, proporcionando una capacidad de datos de 1 y 2 Mbps.

Para conseguir las velocidades de transmisión de datos de 1 y 2 Mbps, se utilizan 11 chips para ensanchar la señal de datos modulada. Como secuencia de ensanchamiento se utiliza una secuencia Barker de 11 chips. La secuencia Barker de 11 chips posee excelentes propiedades de autocorrelación, proporcionando un máximo nivel de correlación del lóbulo lateral de 1/11 del valor del pico de correlación. Para conseguir esta excelente propiedad de correlación en cada símbolo de datos, se utiliza la misma secuencia Barker de 11 chips para ensanchar cada símbolo de datos.

Como alternativa al uso de secuencias cortas repetidas, puede utilizarse la modulación BPSK para ensanchar los datos. La modulación BPSK proporciona un medio simple y directo para ensanchar datos modulados bien en BPSK o en QPSK. Para cumplir los requerimientos espectrales de la norma 802.11, la señal BPSK ensanchada es conducida a través de un filtro de paso bajo para reducir el nivel del lóbulo lateral del espectro de potencia. La señal BPSK filtrada es procesada en el seno de la región lineal de un amplificador de potencia para minimizar el recrecimiento del espectro de salida del amplificador de potencia de radiofrecuencia.

Existen, sin embargo, algunas limitaciones en el uso de las técnicas mencionadas anteriormente. En primer lugar, las señales que utilizan secuencias de ensanchamiento cortas, tales como la secuencia Barker de 11 chips utilizada en las señales 802.11b, limitan el intervalo de ensanchamiento del retardo para ecualización de canales multitrayecto, ya que dos símbolos adyacentes pueden tener polaridades opuestas. Más aún, secuencias de ensanchamiento cortas y repetidas permiten también a oyentes no autorizados recuperar fácilmente el flujo de símbolos de datos. Las secuencias más largas eliminan estas limitaciones. Sin embargo, secuencias de ensanchamiento más largas no proporcionan propiedades de autocorrelación excelentes a lo largo de secciones cortas (11 chips para las señales 802.11b) de la secuencia de ensanchamiento. La degradación en la propiedad de autocorrelación degrada de manera directa el rendimiento del sistema en términos de tasa de error binario (BER, bit error rate).

En segundo lugar, las señales ensanchadas con BPSK limitan el rendimiento de potencia del amplificador de potencia de radiofrecuencia, ya que obligan al amplificador a funcionar en un modo lineal para evitar el recrecimiento de los lóbulos laterales del espectro. Sin embargo, el ensanchamiento de datos utilizando señales de modulación de envolvente constante, tales como Modulación por Desplazamiento Mínimo (MSK, *Minimum Shift Keying*) o modulación de envolvente cuasi-constante, tales como MSK de Banda Cuasi-Limitada (QBL-MSK, *Quasi-Bandlimited MSK*) y Modulación por Desplazamiento de Fase en Cuadratura con Corrimiento por Filtrado de Coseno Alzado (RC-OQPSK, *Raised Cosine filtered Offset Quadrature Phase Shift Keying*), permiten al amplificador de potencia de radiofrecuencia funcionar en modo no lineal, aumentando el rendimiento de potencia.

Las técnicas de demodulación paralela estándar para MSK, QBL-MSK, y RC-OQPSK desensanchan la señal utilizando secuencias I y Q independientes, y necesitan dos secuencias de ensanchamiento ortogonales o cuasi-ortogonales. Típicamente se utilizan códigos Gold debido a que tienen buenas propiedades de correlación y correlación cruzada. Sin embargo, los códigos Gold también necesitan, como mínimo, 31 chips (mínima longitud para un código Gold) de ensanchamiento tanto en los datos I como en los datos Q, y un aumento en el número de chips da como resultado una velocidad de transmisión de datos reducida para la misma velocidad de transmisión de chips operativa. Para reducir el número de chips de ensanchamiento requeridos por estas señales demodulación de envolvente constante o cuasi constante, se utiliza el formateado serie en la señal de ensanchamiento. El formateado serie combinado con la demodulación serie permite que estas señales sean demoduladas de manera similar a la BPSK.

65

50

55

Para un desensanchamiento serie de una señal MSK, QBL-MSK, o RC-OQPSK, la secuencia Barker de 11 chips repetitiva puede utilizarse para la secuencia de ensanchamiento. Las propiedades de autocorrelación para la secuencia Barker de 11 chips son excelentes, posibilitando la eliminación del término de demodulación serie no deseado. Para evitar las limitaciones asociadas a la secuencia de ensanchamiento corta, se utiliza una secuencia de ensanchamiento más larga. Tal como se describió anteriormente, las secuencias de ensanchamiento más largas no proporcionan unas propiedades de autocorrelación excelentes a través de las secciones cortas (11 chips para las señales 802.11b) de la secuencia de ensanchamiento. Las propiedades de autocorrelación pobres asociadas a la secuencia de ensanchamiento larga dan como resultado que el término de demodulación serie no deseado no se elimina.

10

15

5

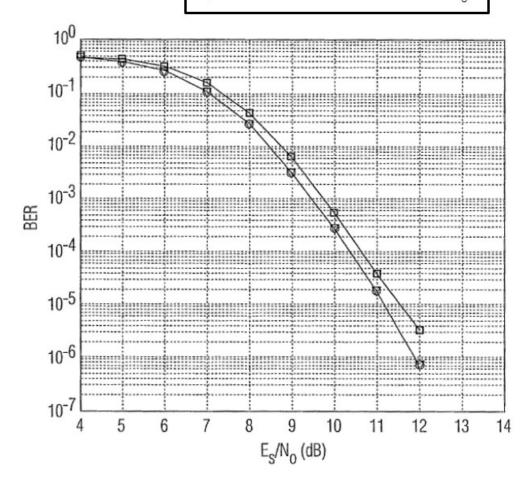

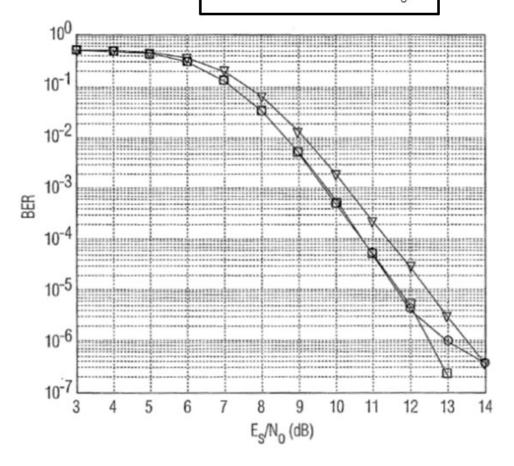

En la FIGURA 1 se muestra una curva de rendimiento de tasa de error binario (BER) con un máximo error de temporización de un cuarto chip (muestreando al doble de la velocidad de transmisión de chips) para modulación de datos DQPSK con ensanchamiento QBL-MSK para una secuencia Neuman-Hoffman corta (00001101) de 8 chips. Tal como se muestra en la FIGURA 1, para una temporización ideal (0 a 0,5 Tc), se consigue una tasa de error binario de  $10^{-6}$  cuando el valor de  $E_s/N_o$  es aproximadamente igual a 11,9 dB, mientras que la condición de máximo error de temporización de Tc/4 requiere de un aumento de  $E_s/N_o$  hasta un valor aproximado de 12,5 dB para proporcionar la misma tasa de error binario.

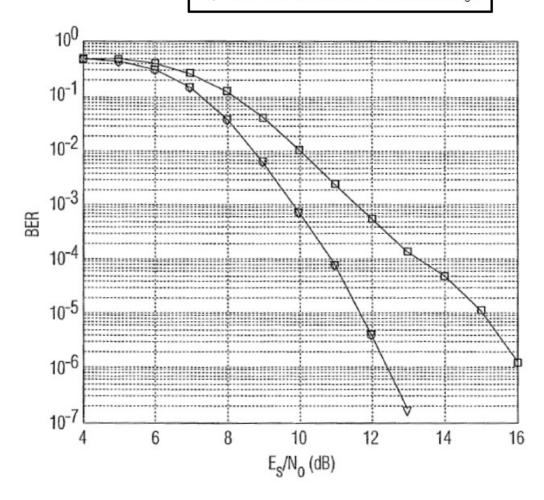

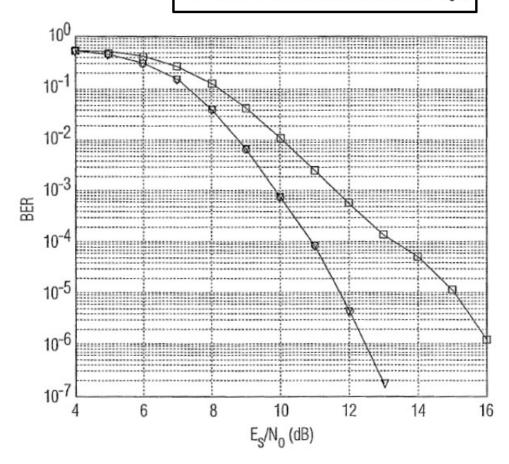

- La FIGURA 2 muestra la curva de rendimiento de tasa de error binario con un error máximo de temporización de un 20 cuarto de chip (muestreando al doble de la velocidad de transmisión de chips) para modulaciones DQPSK con ensanchamiento QBL-MSK para una secuencia de ensanchamiento larga y aleatoria. Tal como se muestra en la FIGURA 2, para una temporización ideal (0 a 0,5 Tc), se consigue una tasa de error binario de 10<sup>-6</sup> cuando el valor de E<sub>s</sub>/N<sub>o</sub> es aproximadamente igual a 12,5 dB, mientras que la condición de máximo error de temporización para Tc/4 requiere de un aumento de E₅/N₀ hasta un valor aproximado de 16 dB para proporcionar la misma tasa de error 25 binario. Para una temporización ideal, el valor de E<sub>s</sub>/N<sub>o</sub> adicional necesario para la secuencia larga en comparación con la secuencia corta es de sólo 0,6 dB. Para la condición de error máximo de temporización de Tc/4, el valor de E<sub>s</sub>/N<sub>o</sub> adicional necesario para la secuencia larga en comparación con la secuencia corta es de 3,5 dB. Esta degradación significativa en el rendimiento de la tasa de error binario para el error de temporización debe reducirse bien aumentando la resolución de temporización o bien compensando las propiedades de autocorrelación más 30 pobres de la secuencia de ensanchamiento larga en comparación con la longitud más corta de ensanchamiento de símbolo. Para aumentar la resolución de temporización es necesario aumentar la frecuencia de muestreo, lo que aumenta la complejidad del demodulador y el consumo de potencia de corriente continua.

- En el documento WO 03/084080 A2, se describe un método y un sistema para el alineamiento temporal con la señal 35 de reloj del receptor de una señal transmitida recibida. El alineamiento temporal se consigue mediante la aplicación de los coeficientes de filtro sintonizado apropiados para tener en cuenta la diferencia temporal entre la señal transmitida recibida y la señal de reloj del receptor. Para señales de secuencia directa, se consigue un alineamiento temporal entre los chips de ensanchamiento. En señales que no son de secuencia directa, el alineamiento temporal se consigue entre los símbolos. El alineamiento temporal se obtiene aplicando los coeficientes de filtro sintonizado 40 apropiados para añadir o restar un retardo en la propagación para tener en cuenta la diferencia temporal entre la señal transmitida recibida y la señal de reloj recibida. La forma de la curva de correlación de sincronización recibida se utiliza para determinar la elección de los coeficientes de filtro sintonizado apropiados para una corrección fina de tiempo. Los coeficientes de filtro sintonizado se seleccionan durante la sincronización y son actualizados a lo largo de la recepción de la señal. Para señales de secuencia directa con receptores RAKE (rastrillo), el alineamiento 45 temporal se aplica con facilidad a múltiples ramas del RAKE. El documento US 5.867.525 A se refiere a usuarios o suscriptores de un sistema de comunicaciones síncrono de espectro ensanchado que suministra señales a la estación central o a la unidad base de ese sistema, y que reciben señales de la misma. Se necesita una sincronización correcta entre estos usuarios (y sus señales) para garantizar el correcto funcionamiento del sistema. Para garantizar una sincronización correcta entre estos usuarios, la señal producida por cada usuario es 50 comprobada para determinar la presencia y la cantidad de cualquier error de desplazamiento (offset). Esto se consigue utilizando tres desensanchadores para la señal por cada usuario. Para un usuario tal, cada desensanchador tal para ese usuario recibe el código de ensanchamiento para ese usuario. Sin embargo, el código de ensanchamiento tal como se recibe por cualquier desensanchador está retardado en el tiempo con respecto al código de ensanchamiento tal como se recibe por los otros dos desensanchadores. Cada uno de tales 55 desensanchadores recibe el código de ensanchamiento con un retardo diferente impuesto sobre ese código de ensanchamiento. Las salidas de los tres desensanchadores están combinadas digitalmente (por ejemplo, comparadas), o comparadas, para calcular una estimación del desplazamiento para ese usuario. Para reducir los efectos del ruido, la estimación del desplazamiento es promediada sobre una duración temporal predeterminada; de manera alternativa, tal promediado puede llevarse a cabo en las salidas de los desensanchadores, o bien en algún 60 paso de procesado intermedio. La estimación del desplazamiento es enviada al usuario, para ser utilizada en la corrección de la sincronización de ese usuario. Las estimaciones del desplazamiento que son demasiado pequeñas para resultar útiles son silenciadas y no son enviadas al usuario, para reducir el uso del canal y para, por lo tanto, ahorrar ancho de banda.

- 65 Para minimizar la complejidad y el consumo de potencia del demodulador, la presente invención proporciona una

estrategia de compensación, entre otras características propias de la misma.

#### SUMARIO DE LA INVENCIÓN

temporización estimado.

35

40

45

55

65

- Para afrontar esta necesidad y otras necesidades, y en vista de sus propósitos, la presente invención proporciona un método para corregir el error de fase de una señal modulada por desplazamiento de fase (PSK), en un receptor. El método incluye los pasos de (a) recibir una señal modulada mediante una secuencia de ensanchamiento; (b) desenensanchar la señal recibida utilizando una secuencia de ensanchamiento del receptor similar a la secuencia de ensanchamiento del paso (a); (c) calcular un perfil de correlación cruzada entre la secuencia de ensanchamiento del receptor y la señal recibida; (d) calcular un perfil de autocorrelación de la secuencia de ensanchamiento del receptor para determinar una propiedad de código de ensanchamiento (SCP, Spreading Code Property); (e) estimar un error de temporización en el alineamiento entre los perfiles de autocorrelación y de correlación cruzada; y (f) corregir un error de fase de la señal desensanchada en el paso (c) mediante la utilización de la SCP y del error de

- Otra realización más de la invención es un receptor. El receptor incluye un módulo de desensanchamiento para desensanchar una señal en banda base, utilizando una secuencia de ensanchamiento generada por un generador de código, un módulo de correlación cruzada para calcular un perfil de correlación cruzada entre la señal en banda base y la secuencia de ensanchamiento, un módulo de autocorrelación para calcular un perfil de autocorrelación de la secuencia de ensanchamiento para determinar un valor de la SCP de la secuencia de ensanchamiento. El receptor también incluye un módulo de estimación de error de temporización, acoplado a los módulos de correlación cruzada y autocorrelación, para estimar un error de alineamiento entre el perfil de autocorrelación y el perfil de correlación cruzada; y un módulo de corrección de fase, acoplado al módulo de estimación de error de temporización y al módulo de desensanchamiento, para corregir un error de fase en la señal en banda base desensanchada.

- 25 Se entiende que la descripción general anterior y la descripción detallada que sigue son ejemplos de la invención, pero no son restrictivas de la misma.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

La invención se entiende mejor a partir de la descripción detallada que sigue cuando se lee en relación con los dibujos adjuntos. En los dibujos se incluyen las figuras siguientes:

La FIGURA 1 es una curva de rendimiento de tasa de error binario (BER) con un máximo error de temporización de un cuarto de chip (muestreando al doble de la velocidad de transmisión de chips) para modulaciones de datos DQPSK con ensanchamiento QBL-MSK para una secuencia Neuman-Hoffman corta de 8 chips;

La FIGURA 2 es una curva de rendimiento de tasa de error binario con un máximo error de temporización de un cuarto de chip (muestreando al doble de la velocidad de transmisión de chips) para modulaciones de datos DQPSK con ensanchamiento QBL-MSK para una secuencia de ensanchamiento larga y aleatoria;

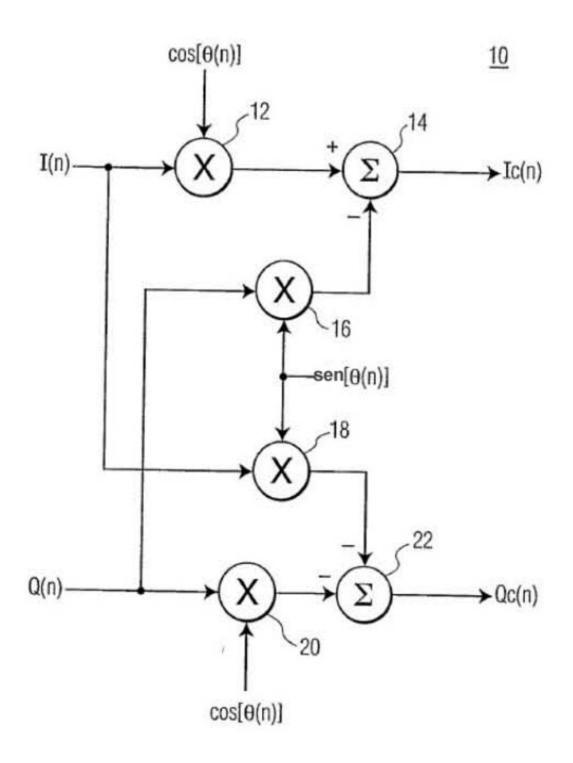

La FIGURA 3 es un diagrama de bloques de un módulo de corrección de fase, de acuerdo con una realización de la presente invención;

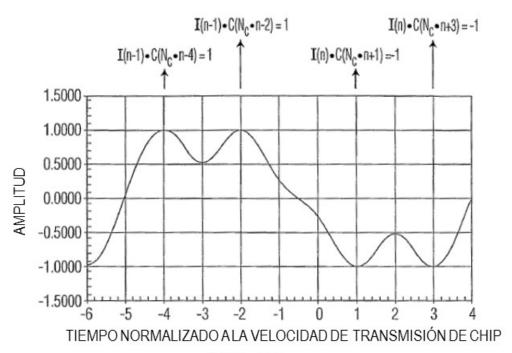

Las FIGURAS 4A y 4B son gráficas que describen un rendimiento de tasa de error binario mejorado para detección de datos DQPSK utilizando el módulo de corrección de fase de la FIGURA 3 en comparación con DQPSK sin corrección de fase;

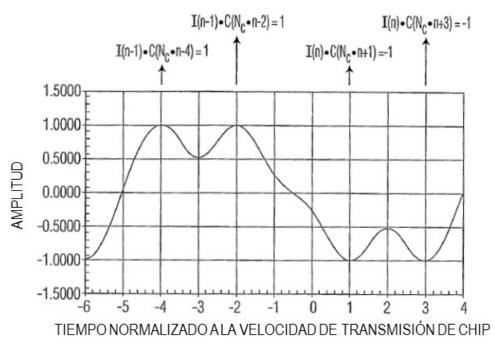

Las FIGURAS 5A, 5B y 5C son gráficos que ilustran distorsiones de envolvente severas que se producen cuando tanto la señal I cómo la señal Q se anulan en el mismo instante;

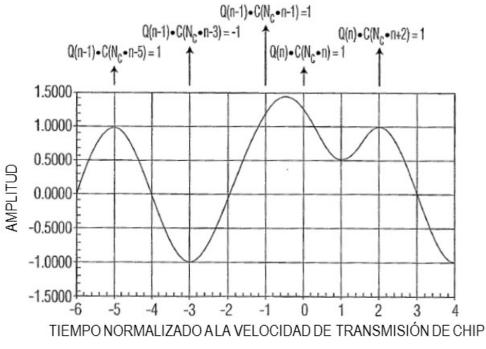

Las FIGURAS 6A, 6B y 6C son gráficos que ilustran desviaciones de envolvente de radiofrecuencia mínimas que se producen cuando las señales I y Q no se anulan en el mismo instante;

La FIGURA 7 es un diagrama de bloques de un módulo SQBL-MSK en un transmisor, de acuerdo con una realización de la presente invención;

La FIGURA 8 es un diagrama de bloques de una etapa de entrada de un demodulador SQBL-MSK de un receptor, de acuerdo con una realización de la presente invención;

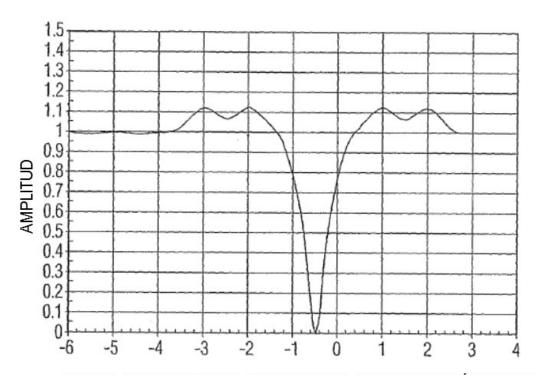

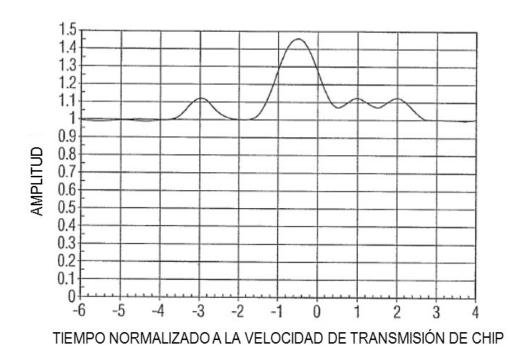

La FIGURA 9 es una representación gráfica de una función de autocorrelación QBL-MSK, de acuerdo con una realización de la presente invención;

La FIGURA 10 es un diagrama de bloques de una operación de desensanchamiento SQBL-MSK, de acuerdo con una realización de la presente invención;

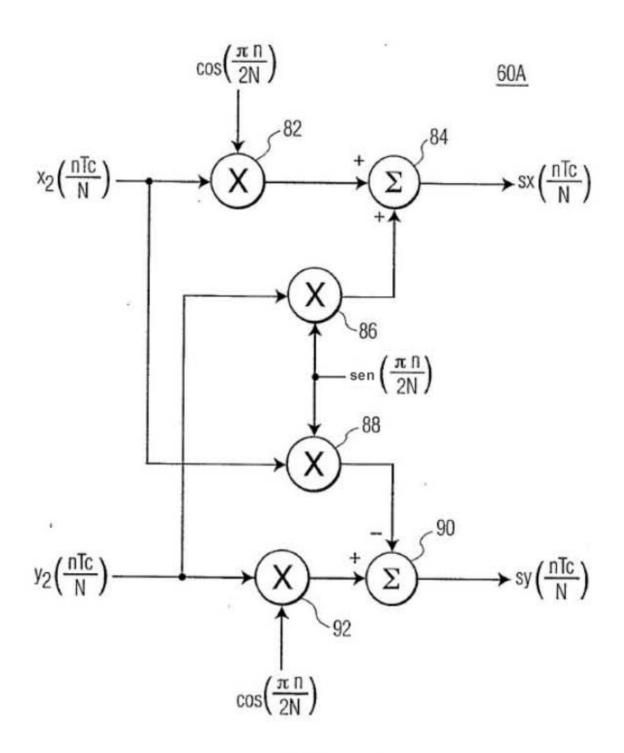

La FIGURA 11 es un diagrama de bloques de un rotador de fase, de acuerdo con una realización de la presente invención;

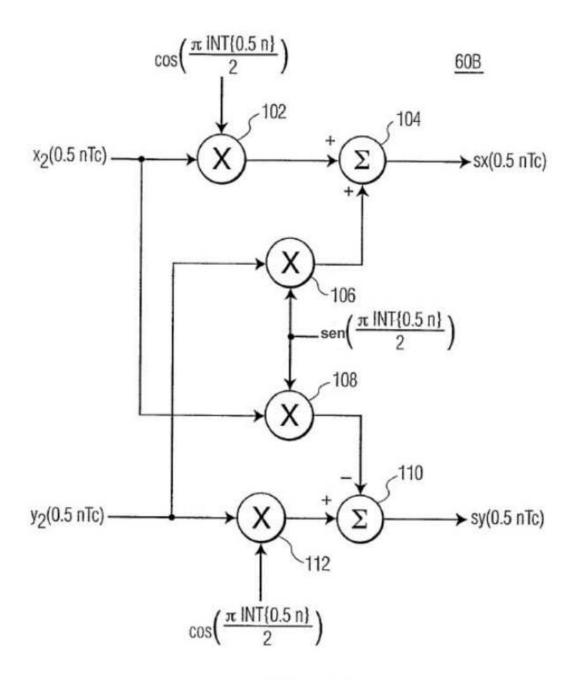

La FIGURA 12 es un diagrama de bloques de un rotador de fase modificado, de acuerdo con una realización de la presente invención;

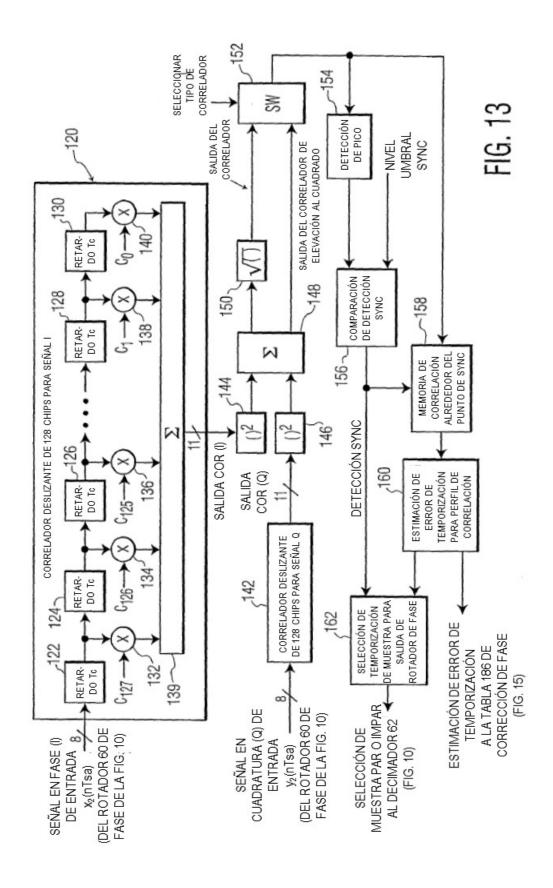

La FIGURA 13 es un diagrama de bloques de un módulo de detección SYNC, de acuerdo con una realización de la presente invención;

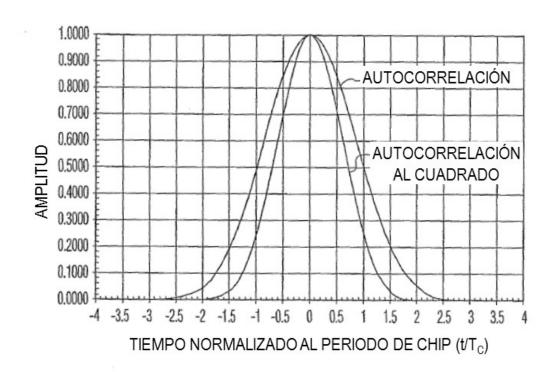

La FIGURA 14 es una representación gráfica de una curva de correlación SYNC, para ser utilizada con el módulo de detección SYNC de la FIGURA 13; y

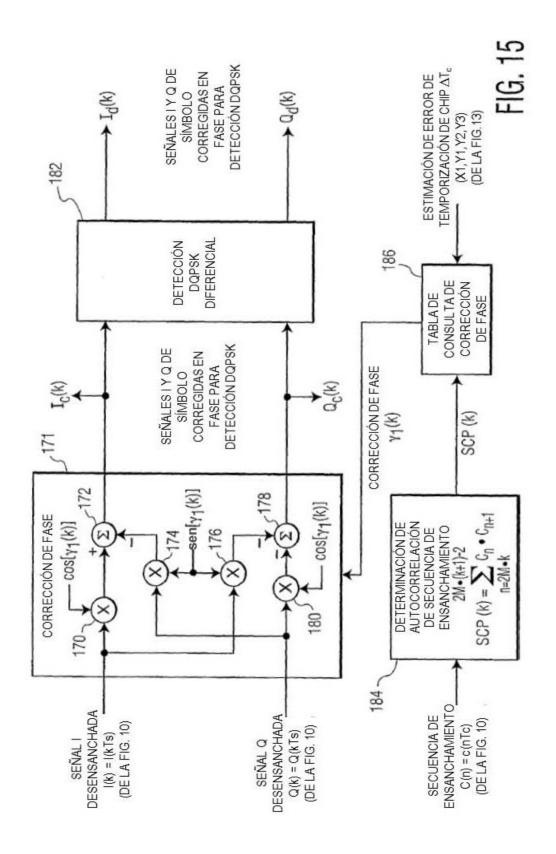

La FIGURA 15 es un diagrama de bloques de un detector de símbolo con módulo de corrección de fase, de acuerdo con una realización de la presente invención.

#### DESCRIPCIÓN DETALLADA DE LA INVENCIÓN

Con el fin de posibilitar el funcionamiento de un demodulador serie con secuencias de ensanchamiento largas, la operación de ensanchamiento del demodulador serie se aprovecha del hecho de conocer la secuencia de ensanchamiento larga. Las propiedades de ensanchamiento para la secuencia de ensanchamiento larga se determinan para cada secuencia de ensanchamiento corta utilizada para desensanchar los datos. Conociendo la propiedad de secuencia de ensanchamiento para el símbolo de datos desensanchado junto con una estimación del error de temporización de chip a partir de la función de correlación de sincronización, se aplica una corrección de fase apropiada a las señales I y Q desensanchadas, reduciendo de manera significativa el término de demodulación serie indeseado.

La FIGURA 3 muestra el módulo 10 de corrección de fase. El módulo 10 se aplica a la señal desensanchadas en fase (I) en cuadratura (Q) para generar las señales I(Ic) y Q (Qc) corregidas en fase. Tal como se muestra en la FIGURA 3, las señales I y Q desensanchadas, I(n) y Q(n), entran en el módulo 10 de corrección de fase y son mezcladas con una señal  $\cos[\Theta(n)]$  en los mezcladores 12 y 20 y con una señal  $\sin[\Theta(n)]$  en los mezcladores 16 y 18. Las salidas de los mezcladores 12 y 16 se combinan entonces en el sumador 14. Del mismo modo, las salidas de los mezcladores 18 y 20 se combinan en el sumador 22. Las señales Ic y Qc corregidas en fase son generadas entonces cómo señales de salida en los sumadores 14 y 22. Los términos de corrección de fase que utilizan señales coseno y seno dependen de la propiedad de correlación cruzada de un chip de la secuencia de ensanchamiento a través del símbolo desensanchado.

Se entenderá que tal como se utiliza en la presente memoria, un "sumador" incluye funciones de suma y resta.

La eliminación del término de demodulación serie no deseado da como resultado una mejora significativa en el rendimiento de la tasa de error binario (BER). Las FIGURAS 4A y 4B muestran el rendimiento de la tasa de error binario mejorado para la detección de datos DQPSK utilizando el módulo de corrección de fase en comparación con DQPSK sin utilizar corrección de fase. De manera específica, la FIGURA 4a muestra el rendimiento de la tasa de error binario DQPSK con corrección de fase y la FIGURA 4B muestra el rendimiento de la tasa de error binario DQPSK sin corrección de fase. La mejora se muestra para diferentes errores de temporización de chip. Por ejemplo, para un error de temporización Tc/4, se necesitan aproximadamente 13,5 dB para proporcionar una tasa de error binario de 10<sup>-6</sup> para DQPSK con corrección de fase mientras que se necesitan 16 dB para proporcionar la misma tasa de error binario sin corrección de fase. Esto supone una reducción de 2,5 dB en E<sub>s</sub>/N<sub>o</sub>. Más aún, para un error de temporización Tc/4, la secuencia larga con corrección de fase necesita un incremento de 1 dB en E<sub>s</sub>/N<sub>o</sub> en comparación con una secuencia corta para situarse en una tasa de error binario de 10<sup>-6</sup> (compárense las FIGURAS 4 y 1).

Una realización de la presente invención utiliza QBL-MSK serie para modulación por ensanchamiento para proporcionar una modulación de radiofrecuencia de envolvente cuasi-constante y para permitir el uso de desensanchamiento serie. Aunque se elige QBL-MSK como señal de ensanchamiento para esta realización particular, pueden utilizarse otras modulaciones de envolvente constante o cuasi-constante, tales como MSK, MSK Gaussiana, OQPSK, y RC-OPSK.

El desensanchamiento serie, al contrario que el desensanchamiento paralelo, utiliza una operación de desensanchamiento BPSK simplificada y separa la señal desensanchada en dos códigos: en fase (I) y en cuadratura (Q). El desensanchamiento serie reduce el ratio de chip a símbolo hasta 8 chips por símbolo. Ratios de desensanchamiento menores, tales como 8 chips/símbolo, son deseables para obtener velocidades de transmisión de datos más elevadas cuando el canal de comunicaciones puede admitirlo. Para modulación de datos BPSK o QPSK en SQBL-MSK, puede escribirse una señal demodulación por ensanchamiento de la manera siguiente:

$$\begin{split} s(t) &= \sum_{k=0}^{N} \left\{ \left[ \sum_{i=0}^{M-1} (-1)^{i} \, c_{2i+2kM} \bullet p(t - \left[2i + 2kM\right] T_{c}) \right] \cos \left(2\pi \, f_{o}t + \theta_{k}\right) \right. \\ &+ \left. \left[ \sum_{i=0}^{M-1} (-1)^{i} \, c_{2i+2kM+1} \bullet p(t - \left[2i + 2kM + 1\right] T_{c}) \right] sen\left(2\pi \, f_{o}t + \theta_{k}\right) \right\} \end{split} \tag{ec 1}$$

50

5

10

15

20

40

45

y

$$p(t) = \begin{cases} \left[\frac{sen\left(\frac{\pi t}{2T_c}\right)}{\left(\frac{\pi t}{2T_c}\right)}\right]^3; -2T_c \le t \le 2T_c \\ 0; & \text{en otro caso} \end{cases}$$

(ec 2)

Donde T<sub>c</sub> representa el periodo de chip, c<sub>i</sub> representa el chip en el instante iT<sub>c</sub>, 2M es el número de chips por cada símbolo de datos en la señal modulada, p(t) es la función de conformación de pulso QBL, f<sub>o</sub> es la frecuencia central de portadora, y los términos (-1)<sup>i</sup>, que multiplican al valor de chip, representan el formateado serie. Los chips (c<sub>i</sub>), que ensanchan los símbolos de modulación de datos (BPSK o QPSK), tienen un valor de +1 o de -1.

La modulación de datos (BPSK o QPSK), representada por el término de fase de portadora  $\Theta_k$ , es 0 ó  $\pi$  para modulación de datos en BPSK y -0,5  $\pi$ , 0, 0,5  $\pi$ , ó  $\pi$  para modulación de datos en QPSK. La aplicación de codificación diferencial para la modulación de datos BPSK o QPSK no afecta a esta ecuación, solamente lo hace al mapeo del término de fase de portadora expresado en la siguiente ecuación:

$$\theta_{k} = \sum_{m=0}^{k} \Delta \theta_{m} \; ; \tag{ec 3}$$

donde  $\Delta\Theta$  es el cambio de fase introducido por la codificación diferencial.

10

20

25

40

50

Para modulación de datos en BPSK, la señal de ensanchamiento SQBL-MSK no se ve afectada por la modulación de datos. Para modulación de datos en QPSK, sin embargo, la señal de ensanchamiento SQBL-MSK sí se ve afectada por la modulación de datos en las condiciones de frontera de símbolo cuando se produce un cambio de fase bien de -0,5 π (-90 grados) ó bien de 0,5 π (90 grados) entre símbolos. Para mostrar dos efectos significativamente diferentes en la envolvente de radiofrecuencia, pueden examinarse dos fronteras diferentes de cambio de fase de 90 grados asociadas a modulación de datos en QPSK, donde el símbolo QPSK anterior está a 0 grados y el símbolo QPSK actual está a 90 grados. En las FIGURAS 5A-5C se muestra una distorsión severa de la envolvente de radiofrecuencia. Tal como se muestra, cuando tanto la señal I cómo la señal Q se anulan en el mismo instante de tiempo, la envolvente de radiofrecuencia adopta un valor cero. En las FIGURAS 6A-6C, por el contrario, se muestra una desviación mínima de la envolvente de radiofrecuencia. Tal como se muestra, las señales I y Q no se anulan en el mismo instante de tiempo.

Tal como se muestra en las FIGURAS 5A-5C, el comportamiento de envolvente de radiofrecuencia cuasi-constante de SQBL-MSK no se conserva. Para conservar el comportamiento de envolvente de radiofrecuencia cuasi-constante de SQBL-MSK, puede disponerse un módulo de mapeo de fase en el transmisor. El módulo de mapeo de fase cambia la trayectoria de fase solamente alrededor de la frontera de símbolo. Puesto que este cambio se produce sólo en la condición de frontera, puede utilizarse la ecuación de la modulación de datos SQBL-MSK sin ajuste de mapeo de fase para proporcionar corrección de fase en el receptor por medio del módulo de corrección de fase mostrado en la FIGURA 15 (por ejemplo).

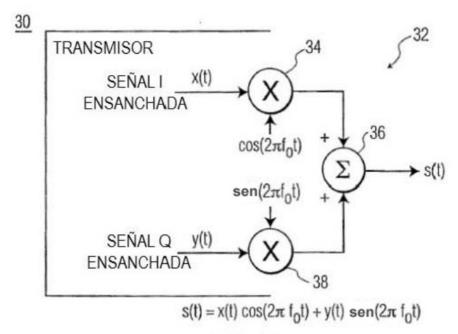

La FIGURA 7 muestra un diagrama de bloques de un modulador 32 SQBL-MSK de un transmisor 30, con modulación de datos I  $\{x(t)\}$  y Q  $\{y(t)\}$  de BPSK o QPSK con ensanchamiento SQBL-MSK en los símbolos de datos. Tal como se muestra, las señales de datos I y Q se mezclan con una señal portadora en los mezcladores 34 y 38. Las salidas de los mezcladores 34 y 38 se combinan entonces en el sumador 36. La señal resultante es una señal en banda base, s(t), representada por la siguiente ecuación:

$$s(t) = x(t)\cos(2\pi f_0 t) + y(t)\sin(2\pi f_0 t).$$

El transmisor 30 transmite una señal s(t) de radiofrecuencia modulada. La señal s(t) de radiofrecuencia modulada se recibe entonces en el receptor 40 mostrado en la FIGURA 8.

Las ecuaciones para las señales I  $\{x(t)\}$  y Q  $\{y(t)\}$  que modulan la portadora pueden obtenerse a partir de la ecuación 1 obteniéndose la siguiente expresión:

$$\begin{split} x(t) &= \sum_{k=0}^{N} \left\{ \left[ \sum_{i=0}^{M-1} (-1)^{i} c_{2i+2kM} \bullet p(t - [2i + 2kM] T_{c}) \right] \cos(\theta_{k}) \right. \\ &+ \left. \left[ \sum_{i=0}^{M-1} (-1)^{i} c_{2i+2kM+1} \bullet p(t - [2i + 2kM + 1] T_{c}) \right] sen(\theta_{k}) \right\} \end{split}$$

(ec 4)

у

5

10

15

20

25

$$y(t) = \sum_{k=0}^{N} \left\{ -\left[ \sum_{i=0}^{M-1} (-1)^{i} c_{2i+2kM} \bullet p(t - [2i + 2kM] T_{c}) \right] sen(\theta_{k}) + \left[ \sum_{i=0}^{M-1} (-1)^{i} c_{2i+2kM+1} \bullet p(t - [2i + 2kM + 1] T_{c}) \right] cos(\theta_{k}) \right\}.$$

(ec 5)

Puesto que la fase del símbolo de datos para QPSK o DQPSK es igual a -90, 0, 90, ó 180 grados sobre cada período de símbolo, o bien los chips de secuencia de ensanchamiento pares están en la señal I y los chips impares en la señal Q (condiciones de símbolo de 0 y 180 grados), o bien los chips de secuencia de ensanchamiento impares están en la señal I y los chips pares en la señal Q (condiciones de símbolo de -90 y 90 grados).

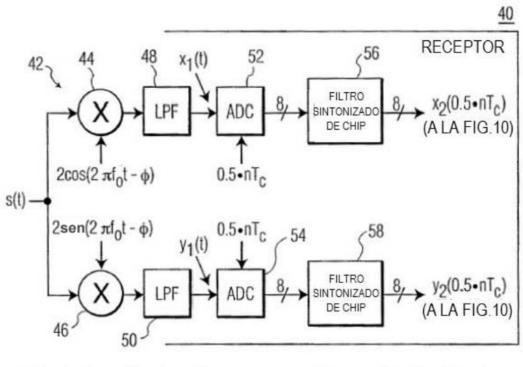

La FIGURA 8 muestra un diagrama de bloques de un demodulador 42 SQBL-MSK del receptor 40. La etapa de entrada del demodulador realiza una conversión descendente de la señal recibida a las señales en banda base I y Q, digitaliza las señales I y Q, y filtra digitalmente las señales I y Q con filtros sintonizados de chip. Tal como se muestra, las señales recibidas se mezclan en los mezcladores 44 y 46 con señales en cuadratura respectivas a la frecuencia de portadora, dando como resultado las señales en banda base I y Q deseadas (término de diferencia de mezcla), y la señal no deseada a una frecuencia doble de la frecuencia de portadora (término de suma de mezcla). Un filtrado de paso bajo mediante el filtro 48 LPF (filtro de paso bajo) y el filtro 50 LPF sigue a la función de conversión reductora para eliminar el término de suma de mezcla no deseado. Las señales I y Q en banda base son digitalizadas mediante los convertidores de analógico a digital (ADC) para las señales I y Q, mostrados como ADC 52 y ADC 54. Tal como se muestra, la frecuencia de muestreo de los convertidores de analógico a digital es igual al doble de la velocidad de transmisión de chips. Después de la digitalización, las señales I y Q son filtradas, respectivamente, por los filtros 56 y 58 sintonizados de chip, que maximizan la relación señal-ruido (SNR, *Signal to Noise Ratio*). Las señales de salida de los filtros sintonizados de chip para las señales I y Q son enviadas a continuación a la operación de desensanchamiento mostrado en la FIGURA 10.

Los coeficientes del filtro sintonizado de chip QBL-MSK están basados en la función de conformación de pulso QBL-MSK definida mediante la siguiente ecuación:

$$p(t) = \begin{cases} \frac{\left[sen\left(\frac{\pi[t-2T_c]}{2T_c}\right)\right]^3}{2T_c}; 0 \le t \le 4T_c \\ \frac{\left[\frac{\pi[t-2T_c]}{2T_c}\right]}{2T_c} \end{cases}; 0 \le t \le 4T_c \end{cases}$$

(ec 6)

30

donde T<sub>c</sub> corresponde al periodo de chip o de símbolo.

Puesto que la función de conformación de pulso QBL-MSK tiene un valor diferente de cero sobre un intervalo de cuatro periodos de chip, el filtro sintonizado de chip QBL-MSK digital que funciona al doble de la velocidad de transmisión de chips puede incluir 9 muestras, definidas mediante la siguiente ecuación:

$$p(t) = \left[ \frac{sen\left(\frac{\pi[0.5 \cdot k - 2]}{2}\right)}{\left(\frac{\pi[0.5 \cdot k - 2]}{2}\right)} \right]^{3}; \quad k = 0, 1, 2, 3, ..., 8.$$

(ec 7)

Reconociendo que el valor del filtro para k igual a 0 y 8 es cero, la respuesta del filtro sintonizado de chip QBL-MSK puede simplificarse a 7 muestras, tal como se define en la siguiente ecuación:

$$p(k) = \left[ \frac{sen\left(\frac{\pi[0.5 \cdot k - 1.5]}{2}\right)}{\left(\frac{\pi[0.5 \cdot k - 1.5]}{2}\right)} \right]^{3} ; k = 0, 1, 2, 3, \dots, 6.$$

(ec. 8)

5

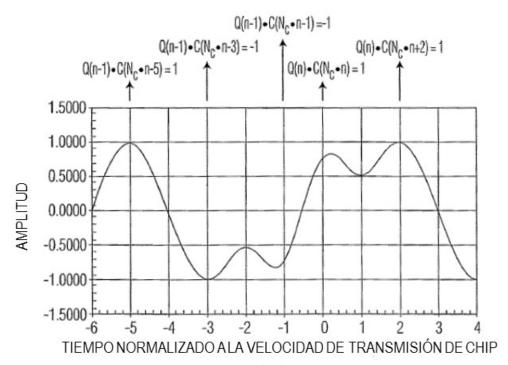

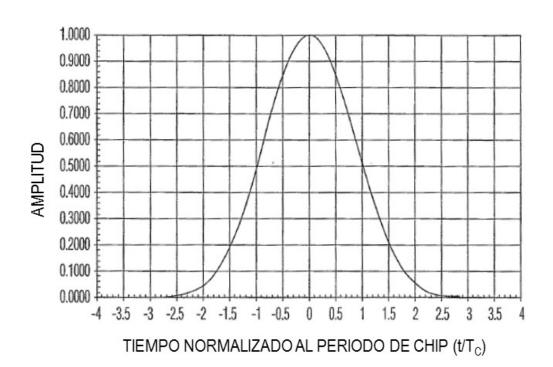

La convolución de la forma del pulso de chip QBL-MSK con el filtro sintonizado de chip QBL-MSK da como resultado una función {g(t)} de autocorrelación QBL-MSK. Tal como se muestra, la función de autocorrelación es cero en el instante 2,5Tc en relación al punto de muestreo óptimo deseado (tiempo 0).

10

Utilizando la función  $\{g(t)\}$  de autocorrelación QBL-MSK, las señales I y Q, mostradas en la FIGURA 8 como  $x_2(0.5*nT_c)$  e  $y_2(0.5*nT_c)$ , respectivamente, presentes en la salida de los filtros 56 y 58 sintonizados de chip (sobre la base de las ecuaciones 4 y 5) son las siguientes:

$$\begin{aligned} \mathbf{x}_{2}(0.5\,\mathrm{nT_{c}}) &= \sum_{k=0}^{N} \left\{ \left[ \sum_{i=0}^{M-1} \left(-1\right)^{i} \mathbf{c}_{2i+2kM} \bullet \mathbf{g}(0.5\,\mathrm{nT_{c}} - \left[2i+2kM\right] \mathbf{T}_{c}) \right] \cos(\theta_{k} + \phi) \right. \\ &+ \left[ \sum_{i=0}^{M-1} \left(-1\right)^{i} \mathbf{c}_{2i+2kM+1} \bullet \mathbf{g}(0.5\,\mathrm{nT_{c}} - \left[2i+2kM+1\right] \mathbf{T}_{c}) \right] \sin(\theta_{k} + \phi) \right\} \end{aligned}$$

(ec 9)

15

У

$$\begin{split} y_2(0.5\,\text{nT}_c) &= \sum_{k=0}^N \biggl\{ - \biggl[ \sum_{i=0}^{M\text{-}1} \bigl(-1\bigr)^i \, c_{2i+2kM} \bullet g(0.5\,\text{nT}_c - \bigl[2i+2kM\bigr] T_c) \biggr] \, \text{sen} \bigl(\theta_k + \phi \bigr) \\ &+ \biggl[ \sum_{i=0}^{M\text{-}1} \bigl(-1\bigr)^i \, c_{2i+2kM+1} \bullet g(0.5\,\text{nT}_c - \bigl[2i+2kM+1\bigr] T_c) \biggr] \cos \bigl(\theta_k + \phi \bigr) \biggr\}; \end{split} \tag{ec 10}$$

20

donde ∮ es el error de fase de portadora y O<sub>k</sub> es la fase introducida por la modulación de los símbolos de datos.

25

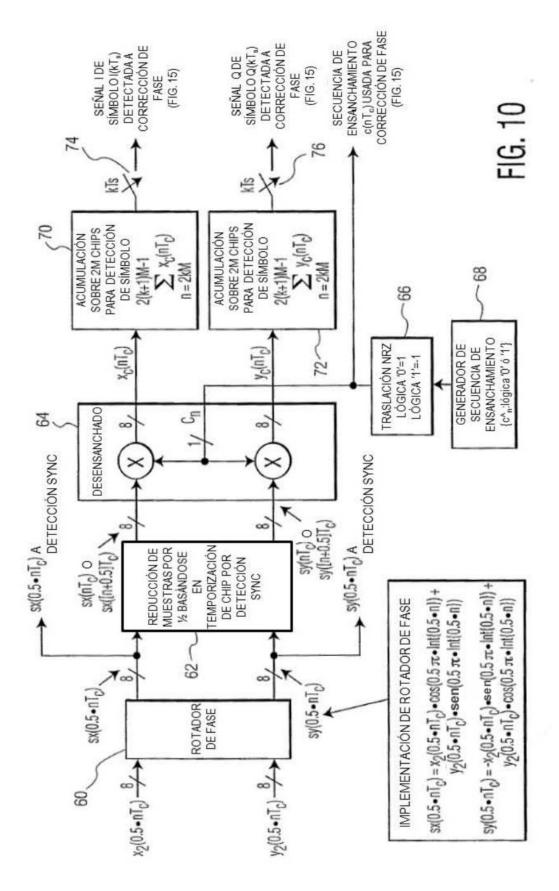

La FIGURA 10 muestra un diagrama de bloques de una operación de desensanchamiento SQBL-MSK, que lleva a cabo un proceso de demodulación serie utilizando un rotador 60 de fase y desensanchando los símbolos de datos a través del desensanchador 64. Tal como se muestra en la FIGURA 10, las salidas de los filtros sintonizados de chip I y Q, mostrados en la FIGURA 8, entran en el rotador 60 de fase, que se describirá con detalle más abajo. El rotador 60 de fase permite la demodulación serie de señal ensanchada SQBL-MSK.

30

Por lo tanto, la presente invención permite el desensanchamiento tanto de la señal I como de la señal Q utilizando la misma secuencia de ensanchamiento, eliminando la necesidad de separar la secuencia de ensanchamiento en chips pares y chips impares, tal como resulta necesario en los desensanchadores paralelo. Tal como se muestra en la FIGURA 10, el módulo 64 desensanchador utiliza la misma secuencia (cn) de ensanchamiento para desensanchar tanto la señal I como la señal Q.

35

Las señales I y Q de dos muestras por chip son generadas por el rotador de fase y enviadas al módulo de detección SYNC mostrado en la FIGURA 13, que determina el control de temporización para seleccionar la muestra correcta y enviarla al decimador 62, que reduce la frecuencia de muestreo para la operación de desensanchamiento a la velocidad de transmisión de chips. El decimador 62 decima las señales I y Q por 2, generando señales a la velocidad de transmisión de chips. Las señales son enviadas entonces al desensanchador 64, donde las señales I y Q son mezcladas con un único código, c<sub>n</sub>, que proviene del generador 68 de secuencia de ensanchamiento (el módulo 66 proporciona una traslación sin retorno a cero (NRZ) del código c<sub>n</sub>).

40

45

Las señales I y Q desensanchadas son entonces acumuladas, a lo largo del período de símbolo de datos, que puede consistir en 2M chips por símbolo, por ejemplo, mediante los acumuladores 70 y 72. En este ejemplo, con 8 chips por símbolo, M es igual a 4, lo que corresponde con 4 chips por símbolo pares y 4 chips por símbolo impares. Los interruptores 74 y 76 están cerrados a la velocidad de transmisión de símbolo, kT<sub>s</sub>, proporcionando las señales

de símbolo I y Q detectadas. Los símbolos detectados son enviados al módulo de corrección de fase mostrado en la FIGURA 15.

- El módulo rotador de fase mostrado en la FIGURA 10 puede implementarse de manera sencilla para detección de símbolos DQPSK. Se necesita la implementación del rotador de fase para permitir una demodulación serie. Una descripción de rotadores de fase que pueden implementarse para la presente invención se ofrece haciendo referencia a las FIGURAS 11 y 12.

- La FIGURA 11 muestra un rotador 60A de fase para demodulación serie en torno a una frecuencia de un cuarto de la velocidad de transmisión de chips por debajo de la frecuencia de portadora, representada por -0,25\*R<sub>c</sub>, donde R<sub>c</sub> representa la velocidad de transmisión de chips. El muestreo a una frecuencia doble de la velocidad de transmisión de chips corresponde a N igual a 2. Tal como se muestra en la FIGURA 11, las señales de salida de los filtros sintonizados de chip I y Q de la FIGURA 8, representados por x<sub>2</sub>(nT<sub>c</sub>/N) e y<sub>2</sub>(nT<sub>c</sub>/N), entran en el rotador de fase para ser mezclados con una señal cos(,π/2N) en los mezcladores 82 y 92 y con una función sen(,π/2N) en los mezcladores 86 y 88. Las señales de salida de los mezcladores 82 y 86 se combinan en el sumador 84 y las señales de salida de los mezcladores 88 y 92 se combinan en el sumador 90. Las señales de salida serie I{sx(n)} and Q{sy(n)} entregadas por el rotador de fase para N muestras por chip, son enviadas al módulo de detección SYNC mostrado en la FIGURA 13 y al decimador mostrado en la FIGURA 10.

- Las señales de salida serie  $I\{sx(n)\}$  and  $Q\{sy(n)\}$  entregadas por el rotador de fase para N muestras por chip están relacionadas con las señales  $I\{x_2(n)\}$  y  $Q\{y_2(n)\}$  mediante la siguiente ecuación compleja:

$$sx \! \left( \frac{nT_c}{N} \right) + j \, sy \! \left( \frac{nT_c}{N} \right) = \! \left[ x_2 \! \left( \frac{nT_c}{N} \right) \! + j \, y_2 \! \left( \frac{nT_c}{N} \right) \right] \bullet exp \! \left( -j \, 2\pi \! \left[ \frac{R_c}{4} \right] \! \left[ \frac{nT_c}{N} \right] \right). \quad (\text{ec 11})$$

Tal como se muestra en esta ecuación, el rotador de fase proporciona un vector rotador exponencial a la frecuencia deseada -0,25\*R<sub>c</sub>, representada por el término exponencial. Dado que R<sub>c</sub>\*T<sub>c</sub> = 1, la ecuación para las señales serie I y Q entregadas por el rotador de fase puede reescribirse como sigue, para N igual a 2:

$$sx(0.5 \, nT_c) + j \, sy(0.5 \, nT_c) = \left[x_2(0.5 \, nT_c) + j \, y_2(0.5 \, nT_c)\right] \bullet \exp\left(-j \frac{\pi \, n}{4}\right). \quad (\text{ec 12})$$

30

35

50

- Cuando la presente invención utiliza una velocidad de muestreo de receptor igual al doble de la velocidad de transmisión de chips, el vector rotador cambia en -45 grados para cada muestra. En el caso de un receptor con una velocidad de muestreo igual a la velocidad de transmisión de chips, el vector rotador exponencial cambia en -90 grados para cada muestra. Para N = 1, el funcionamiento del rotador de fase requiere solamente una operación de multiplicación por +1 ó -1 sobre las señales de entrada I y Q, seguida de un módulo de mapeo a la señal de salida I y Q apropiada. Esta estructura de rotador de fase puede implementarse de manera sencilla mediante hardware.

- La presente invención puede utilizar una velocidad de muestreo que sea igual al doble de la velocidad de transmisión de datos, que corresponde a N = 2. Para N = 2, el rotador de fase para muestras pares es el mismo que se describió para N = 1. Las muestras impares requieren una multiplicación por 0,7071 ó -0,7071 junto con una operación de suma, lo que resulta en una estructura de rotador de fase más compleja.

- Puesto que las señales serie I y Q entregadas por el rotador de fase están decimadas por 2 antes del desensanchamiento mediante la selección bien de las muestras pares o bien de las muestras impares, la misma rotación de fase puede aplicarse tanto a las muestras pares como las muestras impares. La presente invención simplifica el módulo rotador de fase para N = 2 mediante la introducción de un término de fase, tal como se muestra en la siguiente ecuación:

$$sx(0.5 \text{ nT}_c) + j \, sy(0.5 \text{ nT}_c) = \left[x_2(0.5 \text{ nT}_c) + j \, y_2(0.5 \text{ nT}_c)\right] \bullet \exp\left(-j \frac{\pi \, \text{INT}\{0.5 \bullet \text{n}\}}{2}\right).$$

(ec 13)

donde INT representa una función que toma solamente el valor entero de su argumento. La separación de las muestras en muestras pares y muestras impares da como resultado las dos ecuaciones siguientes:

$$sx(nT_{_{\text{\tiny C}}}) + j\,sy(nT_{_{\text{\tiny C}}}) \,= \, \left[x_{_{2}}(nT_{_{\text{\tiny C}}}) + j\,y_{_{2}}(nT_{_{\text{\tiny C}}})\right] \bullet \, \exp\!\left(-\,j\,\frac{\pi\,n}{2}\,\right); \ \ \text{para muestras pares}$$

(ec 14)

У

$$\begin{split} sx(\big[0.5+n\big]T_{\rm c}) + j\,sy(\big[0.5+n\big]T_{\rm c}) &= \big[x_2(\big[0.5+n\big]T_{\rm c}) + j\,y_2(\big[0.5+n\big]T_{\rm c})\big] \\ &\bullet \exp\!\left(-\,j\frac{\pi\,n}{2}\,\right) \end{split} \qquad ; \quad \text{para muestras impares} \end{split}$$

(ec 15)

5

10

Comparando el rotador de fase modificado de las ecuaciones 14 y 15 con el rotador de fase mostrado en la FIGURA 11, las muestras pares entregadas por ambos rotadores son las mismas. Sin embargo, las muestras impares entregadas por el rotador de fase modificado están rotadas en 45 grados ( $\pi$ /4 radianes) con respecto a las muestras impares del rotador de fase de la FIGURA 11. Sumando el término de fase, que tiene un valor de cero grados para muestras pares y de 45 grados ( $\pi$ /4 radianes) para muestras impares, puede obtenerse la misma estructura de rotador de fase simplificada asociada con el rotador de fase N = 1. La FIGURA 12 muestra esta estructura de rotador de fase modificada.

Tal como se muestra en la FIGURA 12, las señales de salida de los filtros sintonizados de chip I y Q de la FIGURA 8, representados por x₂(0,5nTc) e y₂(0,5nTc), entran en el rotador 60B de fase para mezclarse con una señal cos(πINT{0,5n}/2) en los mezcladores 102 y 112 y con una señal sen(πINT{0,5n}/2) en los mezcladores 106 y 108. Las señales de salida de los mezcladores 102 y 106 son entonces enviadas al sumador 104 y las señales de salida de los mezcladores 108 y 112 son enviadas al sumador 110. Las señales serie I {sx(0,5n)} y Q {sy(0,5n)} entregadas por el rotador 60B de fase, representadas en la FIGURA 12 por sx(0,5nTC) and sy(0,5nTC), son enviadas al módulo de detección SYNC mostrado en la FIGURA 13 y al decimador 62 mostrado en la FIGURA 10.

El rotador 60B de fase modificado proporciona una estructura de mapeo repetitiva de 8 muestras tanto en la señal I como en la señal Q, tal como se muestra a continuación:

25

$$sx(0.5 \text{ nT}_c) = \{x_2(0), x_2(0.5 \text{ T}_c), y_2(\text{T}_c), y_2(1.5 \text{ T}_c), -x_2(2\text{T}_c), -x_2(2.5 \text{ T}_c), -y_2(3\text{T}_c), -y_2(3.5 \text{ T}_c), ...$$

(ec 16)

У

$$sy(0.5 \text{ nT}_{c}) = \{y_{2}(0), y_{2}(0.5 \text{ T}_{c}), -x_{2}(\text{T}_{c}), -x_{2}(1.5 \text{ T}_{c}), -y_{2}(2\text{T}_{c}), -y_{2}(2.5 \text{ T}_{c}), x_{2}(3\text{T}_{c}), x_{2}(3.5 \text{ T}_{c}), .$$

(ec 17)

30

después de la operación del rotador de fase se lleva a cabo la reducción de la velocidad de muestreo por parte del decimador 62 de la FIGURA 10. El decimado permite la selección bien de las muestras impares,  $[(n + 0,5)T_c]$ , o bien de las muestras pares,  $(nT_c)$ . La temporización está determinada por la operación de detección SYNC.

35

40

La operación de detección SYNC utilizada para determinar la temporización correcta se describirá ahora haciendo referencia a la FIGURA 13. El módulo de detección SYNC determina la elección correcta de las muestras I y Q para la operación de desensanchamiento y la información de error de temporización que será utilizada por el módulo de corrección de fase mostrado en la FIGURA 15. Se apreciará que en el ejemplo de la FIGURA 13, se muestran 128 chips. Puede también utilizarse un número de chips diferente.

La reducción en la complejidad de la detección SYNC de los correladores I y Q se consigue mediante el decimado de las muestras I y Q por un factor de 2. El decimado reduce la velocidad de muestreo I y Q de tal manera que se iguala a la velocidad de transmisión de chips. Este decimado se consigue seleccionando bien las muestras pares o bien las muestras impares que serán enviadas a la detección SYNC.

5

10

15

20

25

30

45

60

Tal como se muestra en la FIGURA 13, el periodo de muestreo para la señal del correlador de entrada se especifica mediante  $T_{sa}$ , que es igual a la mitad del período de chip ( $T_{sa}$  = 0,5\* $T_c$ ) para el funcionamiento de la detección SYNC al doble de la velocidad de transmisión de chips. Para el funcionamiento del módulo de detección SYNC a la velocidad de transmisión de chips, el periodo de muestreo es igual al periodo de chip ( $T_s$  =  $T_c$ ). Para el funcionamiento de la detección SYNC, bien a la velocidad de transmisión de chips o bien al doble de la velocidad de transmisión de chips, los elementos de retardo en los correladores 120 y 142 se especifican por el período de chip ( $T_c$ ). Para hacer funcionar el algoritmo de detección SYNC al doble de la velocidad de transmisión de chips, el elemento de retardo se implementa mediante dos periodos de retardo de muestra ( $2*T_{sa}$ ). Para hacer funcionar el algoritmo de detección SYNC a la velocidad de transmisión de chips, el elemento de retardo se implementa mediante un único periodo de retardo de muestra ( $T_{sa}$ ).

Los correladores 120 y 142 deslizantes de chip para las señales de entrada I y Q, tal como se ejemplifican en la FIGURA 13, incluyen una longitud de deslizamiento de 128 chips, representados por los elementos 122, 124, 126, 128 y 130 de retardo en la FIGURA 13, que están acoplados, respectivamente, a los mezcladores 132, 134, 136, 138 y 140 para ser multiplicados por las señales de código ensanchado respectivas C<sub>127</sub>, C<sub>126</sub>, C<sub>125</sub>, ..., C<sub>0</sub>. Las 128 señales mezcladas se suman entre sí en el sumador 139. Esta longitud SYNC no es exclusiva de la presente invención y puede hacerse más corta o más larga. Además, la correlación completa de 128 chips no necesita ser combinada de manera coherente sobre la secuencia completa de 128 chips. Por ejemplo, la correlación de 128 chips puede ser combinada de manera coherente sobre segmentos de 32 chips seguidos de una combinación no coherente de los cuatro segmentos de 32 chips. Ni la longitud de secuencias SYNC, ni la estructura de correlación, son exclusivas del proceso de corrección de fase QPSK/DQPSK.

Tal como se muestra en la FIGURA 13, las señales I y Q de salida de correlador están elevadas al cuadrado, respectivamente, por funciones 144 y 146 de elevación al cuadrado, y a continuación son combinadas en el sumador 148. La detección SYNC, como se entenderá, puede estar determinada mediante la utilización de bien el cuadrado de la salida de correlación o bien por la salida de correlación (generada por el módulo 150 de extracción de la raíz cuadrada). Puede utilizarse cualquiera de las dos salidas de correlación.

Típicamente, la salida de correlación se selecciona mediante el conmutador 152, ya que puede ser implementado de manera sencilla utilizando la aproximación siguiente:

$$\begin{aligned} & \text{COR}(n) = \text{Max}\{\text{MAG}[\text{ICOR}(n)], \text{MAG}[\text{QCOR}(n)]\} \\ & + \frac{1}{2} \bullet \text{Min}\{\text{MAG}[\text{ICOR}(n)], \text{MAG}[\text{QCOR}(n)]\}; \end{aligned} \tag{ec 18}$$

donde Max{ } es el máximo valor entre sus dos argumentos, Min{ } es el mínimo valor entre sus dos argumentos, y Mag[ ] es la magnitud de su argumento.

La señal utilizada como señal de entrada para el módulo 154 de detección de pico, para cada una de las dos salidas de correlación diferentes, se muestra en la FIGURA 14. Para la salida de raíz cuadrada, la señal de correlación entregada al detector de pico es la función de autocorrelación QBL-MSK, mientras que la salida de elevación al cuadrado es el cuadrado de la función de autocorrelación QBL-MSK. Como puede observarse, la respuesta de correlación para la función de autocorrelación QBL-MSK al cuadrado es más picuda que la función de autocorrelación QBL-MSK, tal como era de esperar.

Puesto que la respuesta de correlación es diferente dependiendo de la señal de entrada, la estimación del error de temporización también depende de la señal que se utilice. Comparando la amplitud de tres muestras adyacentes, el módulo 154 de detección de pico determina si se ha producido un pico en la muestra central. Si la muestra central es declarada como pico, la magnitud de la muestra (muestra pico) se compara con el umbral SYNC mediante el módulo 156 de comparación de detección SYNC. Si la magnitud de la muestra pico es mayor que el umbral SYNC, se declara SYNC por parte de la señal de detección SYNC enviada al módulo 162 de selección de temporización de muestra.

SYNC determina la posición temporal del primer chip y también determina si se deben procesar las muestras pares o las muestras impares en el desensanchador. Si el proceso SYNC se hace funcionar al doble de la velocidad de transmisión de chips, un punto SYNC dentro del intervalo  $\pm 0.25^*T_c$  se determina directamente mediante la detección de pico. Si el proceso SYNC se hace funcionar a la velocidad de transmisión de chips, el punto de detección SYNC junto con el perfil de correlación se utilizan para establecer el punto SYNC con una resolución de  $\pm 0.25^*T_c$ , tal como se describe más adelante.

Utilizando la salida de correlación basada en la respuesta de autocorrelación QBL-MSK de la FIGURA 14 y haciendo funcionar la detección SYNC a la velocidad de transmisión de chips, se obtiene un mapeo a modo de ejemplo para obtener una resolución temporal más fina  $(\pm 0,25^*T_c)$ , tal como se resume a continuación:

- (a) seleccionar la muestra  $nT_C 0.5 T_C$  si  $COR(n-1) \ge 2 \cdot COR(n+1)$ ; corrección  $-T_c/2$  implementada (se utiliza la muestra impar antes que la muestra par en la detección SYNC)

- (b) seleccionar la muestra  $nT_C + 0.5 T_C$  si  $COR(n+1) \ge 2 \cdot COR(n-1)$ ; corrección  $+T_c/2$  implementada (se utiliza la muestra impar después de la muestra par en la detección SYNC)

- (c) seleccionar la muestra nT<sub>C</sub>; sin corrección si no se cumple ninguna de las dos condiciones anteriores;

- donde las entradas SYNC I y Q son las muestras pares solamente, COR(nT<sub>c</sub>) es la posición del pico, COR[(n+1)T<sub>c</sub>] es la muestra que antecede al pico. De este modo, el módulo 162 de selección de temporización de muestra elige las muestras pares o las muestras impares, basándose en estas tres relaciones. Adicionalmente, las muestras de salida correctas entregadas por el rotador 60 de fase en la FIGURA 10 pueden ser enviadas al desensanchador 64 a partir de estas tres relaciones.

- 20 Se describirá a continuación la estimación del error de temporización proporcionado por el módulo 160 de estimación de error de temporización, mostrado en la FIGURA 13. Para la corrección de fase cuando SYNC funciona a una frecuencia de muestreo igual a la velocidad de transmisión de chips, se determinan 7 condiciones de correlación únicas definidas por X1, X2, y así sucesivamente, hasta X7 a partir de COR(n), COR(n-1), y COR(n+1). Las definiciones de las siete condiciones de correlación se ofrecen a continuación:

$$X1 = \begin{cases} 1; \text{ si } COR(n-1) > COR(n+1) \\ 0; \text{ si } COR(n-1) \le COR(n+1) \end{cases}$$

(ec 19)

$$X2 = \begin{cases} 1; \text{ si } COR(n-1) > 2 \cdot COR(n+1) \\ 0; \text{ si } COR(n-1) \le 2 \cdot COR(n+1)' \end{cases}$$

(ec 20)

$$X3 = \begin{cases} 1; \text{ si } COR(n+1) > 2 \bullet COR(n-1) \\ 0; \text{ si } COR(n+1) \le 2 \bullet COR(n-1) \end{cases}$$

(ec 21)

$$X4 = \begin{cases} 1; \text{ si } COR(n-1) > 3 \bullet COR(n+1) \\ 0; \text{ si } COR(n-1) \le 3 \bullet COR(n+1) \end{cases}$$

(ec 22)

$$X5 = \begin{cases} 1; \text{ si } COR(n+1) > 3 \cdot COR(n-1) \\ 0; \text{ si } COR(n+1) \le 3 \cdot COR(n-1) \end{cases}$$

(ec 23)

$$X6 = \begin{cases} 1; & \text{si } 1.25 \bullet \text{COR}(n+1) < \text{COR}(n-1) < 2 \bullet \text{COR}(n+1) \\ 0; & \text{en otro caso} \end{cases}$$

(ec 24)

$$X7 = \begin{cases} 1; & \text{si } 1.25 \bullet \text{COR}(n-1) < \text{COR}(n+1) < 2 \bullet \text{COR}(n-1) \\ 0; & \text{en otro caso} \end{cases}$$

(ec 25)

У

30

5

10

Estas siete condiciones de correlación diferentes son procesadas adicionalmente utilizando las tres relaciones digitales siguientes:

$$Y1 = X2 \circ X3$$

, (ec 26)

$$Y2 = X4 \text{ o } X5$$

, (ec 27)

Los cuatro parámetros X1, Y1, Y2 e Y3 de corrección de fase son enviados a la tabla 186 de corrección de fase, mostrada en la FIGURA 15.

Se entiende que SYNC establece una temporización inicial para los procesos de desensanchamiento y demodulación. Para mantener la temporización a lo largo de la señal, pueden utilizarse bien seguimiento de chip (chip tracking) o bien secuencias de prueba serie (serial probes). El seguimiento de chip utiliza desensanchamiento temprano, tardío, y en tiempo para estimar el error de temporización y llevar a cabo la corrección de temporización correcta. Para la implementación de seguimiento de chip, también puede utilizarse información proveniente de los desensanchadores temprano, tardío, y en tiempo para proporcionar la estimación de error de temporización al módulo de corrección de fase.

La estrategia basada en secuencia de prueba en serie se implementa de manera sencilla, ya que se lleva a cabo de la misma manera que el proceso de detección SYNC mostrado en la FIGURA 13. Se utiliza una secuencia conocida para la secuencia de prueba en serie, exactamente igual que en la detección SYNC. La secuencia de prueba en serie se inserta en la señal y se utiliza para proporcionar una actualización de la temporización de chip y una estimación del error de temporización para el modelo de corrección de fase. La ventaja de la detección SYNC y de la estrategia basada en secuencia de prueba en serie consiste en que puede utilizarse una secuencia conocida para determinar las posiciones de rama para detección RAKE con el fin de mejorar el rendimiento en un canal multitrayecto.

Durante la detección SYNC, se determina un perfil de correlación basado en los niveles de pico de correlación alrededor del punto SYNC establecido por el módulo 158 de memoria de correlación. El intervalo temporal sobre el que se genera este perfil se denomina ventana multi-trayecto. Basándose en el nivel de pico de magnitud del perfil de correlación, se seleccionan ramas de RAKE multi-trayecto con temporización de chip y estimación de error de temporización para el módulo de corrección de fase para cada rama.

Volviendo a la FIGURA 10, el desensanchamiento de los símbolos I y Q se lleva a cabo a la velocidad de transmisión de chips y con la temporización fijada por la detección SYNC y la secuencia de prueba en serie, asumiendo que la secuencia de prueba en serie se utiliza para mantener la temporización de chip. Tal como se muestra en la FIGURA 10, la misma secuencia (cn) de ensanchamiento se utiliza para desensanchar las señales I y Q. Las señales I y Q desensanchadas se acumulan sobre el período de símbolo de datos, e incluye 2M chips por símbolo, por ejemplo. Para una implementación RAKE, la temporización de chip en el decimador 62, el desensanchamiento en el desensanchador 64, y la acumulación en los módulos 70 y 72 de acumulación, mostrados en la FIGURA 10, puede implementarse de manera individual para cada rama del RAKE basándose en temporizaciones de chips independientes. De manera similar, el alineamiento del código de ensanchamiento puede basarse en el cálculo de una rama del RAKE en una función SYNC/secuencia de prueba en serie. Cada rama del RAKE, cómo se apreciará, genera una salida de señal de símbolo I y Q detectada.

Se ofrece a continuación una descripción general del proceso de corrección de error de fase o más implementado por la presente invención. Las salidas serie I y Q entregadas por el rotador 60 de fase y el decimador 62 pueden ser reescritas de la manera siguiente:

$$sx(nT_c) = x_2(nT_c + \Delta T_c) \cdot cos\left(\frac{\pi n}{2}\right) + y_2(nT_c + \Delta T_c) \cdot sen\left(\frac{\pi n}{2}\right)$$

(ec 29)

55

У

15

20

35

40

45

$$sy(nT_c) = -x_2(nT_c + \Delta T_c) \cdot sin\left(\frac{\pi n}{2}\right) + y_2(nT_c + \Delta T_c) \cdot cos\left(\frac{\pi n}{2}\right); \quad (ec 30)$$

donde ΔT<sub>c</sub> es el error de temporización (máximo ±T<sub>c</sub>/4) no eliminado por la corrección de temporización SYNC cuando, se seleccionan las muestras pares o impares, basándose en el módulo 162 de selección de temporización 5 de la FIGURA 13. Insertando las ecuaciones para  $x_2(nT_c)$  e  $y_2(nT_c)$  y llevando a cabo simplificaciones de estas ecuaciones, se llega a las siguientes expresiones:

$$sx(nT_c) = \sum_{k=0}^{N} \left\{ \left[ \sum_{i=0}^{2M-l} c_{i+2kM} \bullet g([nT_c + \Delta T_c] - [i+2kM]T_c) \bullet cos \left( \frac{\pi[nT_c - [i+2kM]T_c]}{2T_c} \right) \right] cos(\theta_k + \phi) - \left[ \sum_{i=0}^{M-l} c_{i+2kM} \bullet g([nT_c + \Delta T_c] - [i+2kM]T_c) \bullet sen \left( \frac{\pi[nT_c - [i+2kM]T_c]}{2T_c} \right) \right] sen(\theta_k + \phi) \right\}$$

$$(ec 31)$$

10 У

30

$$\begin{split} sy(nT_c) &= -\sum_{k=0}^{N} \Biggl\{ \Biggl[ \sum_{i=0}^{2M-1} c_{i+2kM} \bullet g ( \left[ nT_c + \Delta T_c \right] - \left[ i + 2kM \right] T_c ) \bullet \cos \left( \frac{\pi \left[ nT_c - \left[ i + 2kM \right] T_c \right]}{2T_c} \right) \Biggr] \ sen \left( \theta_k + \phi \right) \\ &+ \Biggl[ \sum_{i=0}^{M-1} c_{i+2kM} \bullet g ( \left[ nT_c + \Delta T_c \right] - \left[ i + 2kM \right] T_c ) \bullet sen \left( \frac{\pi \left[ nT_c - \left[ i + 2kM \right] T_c \right]}{2T_c} \right) \Biggr] cos \left( \theta_k + \phi \right) \Biggr\}. \end{split}$$

$$(ec 32)$$

- A partir de estas expresiones, pueden apreciarse dos características propias clave de la demodulación serie. En 15 primer lugar, se elimina el factor (-1) de formateado serie mostrado en la ecuación demodulación (ecuación 1). En segundo lugar, las señales I y Q en banda base consisten en la secuencia de ensanchamiento filtrada multiplicada por una función de ponderación de tipo coseno o de tipo seno. Para detección coherente, la secuencia de ensanchamiento filtrada ponderada por coseno es el término deseado tanto en la señal I como en la señal Q.

- 20 La función de autocorrelación QBL-MSK tiene un valor diferente de cero en un intervalo de ±2.5 T<sub>c</sub> alrededor de la temporización SYNC ideal de cero (ver FIGURA 9). Puesto que la función de ponderación de tipo coseno fuerza a la función de autocorrelación QBL-MSK a adoptar un valor cero en los instantes  $-T_c+\Delta T_c$  y  $T_c+\Delta T_c$ , solamente se consideran los términos QBL-MSK en los instantes  $-2T_c+\Delta T_c$ ,  $\Delta T_c$ ,  $\Delta T_c$ ,  $\Delta T_c$  para cada respuesta de chip de autocorrelación QBL-MSK ponderada por coseno. 25

De manera similar, la función de ponderación de tipo seno fuerza a la función de autocorrelación QBL-MSK a adoptar un valor cero en los instantes  $-T_c+\Delta T_c$ ,  $\Delta T_c$  y  $2T_c+\Delta T_c$ , de manera que sólo se consideran los términos QBL-MSK en los instantes  $-T_c+\Delta T_c$  y  $T_c+\Delta T_c$  para cada respuesta de chip de autocorrelación QBL-MSK ponderada por seno. Utilizando esta información, las ecuaciones para la señal I y Q serie pueden reescribirse de la manea siguiente:

$$\begin{split} sx(nT_c) &= \sum_{k=0}^{N} \left\{ \left[ \sum_{i=0}^{2M-1} c_{i+2kM} \bullet \left\{ g(\Delta T_c) \delta(n - [i + 2kM]) - g(-2T_c + \Delta T_c) \delta(n + 2 - [i + 2kM]) - g(2T_c + \Delta T_c) \delta(n - 2 - [i + 2kM]) \right\} \right] \bullet \cos(\theta_k + \phi) \\ &- \left[ \sum_{i=0}^{M-1} c_{i+2kM} \bullet \left\{ -g(-T_c + \Delta T_c) \delta(n + 1 - [i + 2kM]) + g(T_c + \Delta T_c) \delta(n - 1 - [i + 2kM]) \right\} \right] \bullet \sin(\theta_k + \phi) \right\} \\ &+ g(T_c + \Delta T_c) \delta(n - 1 - [i + 2kM]) \right\} \right] \bullet \sin(\theta_k + \phi) \right\} \end{split}$$

(ec 33)

у

$$\begin{split} sy(nT_c) = -\sum_{k=0}^{N} & \left\{ \left[ \sum_{i=0}^{2M-1} c_{i+2kM} \bullet \left\{ g(\Delta T_c) \delta(n - [i + 2kM]) - g(-2T_c + \Delta T_c) \delta(n + 2 - [i + 2kM]) - g(2T_c + \Delta T_c) \delta(n - 2 - [i + 2kM]) \right\} \right] \bullet sen(\theta_k + \phi) \\ & + \left[ \sum_{i=0}^{M-1} c_{i+2kM} \bullet \left\{ -g(-T_c + \Delta T_c) \delta(n + 1 - [i + 2kM]) + g(T_c + \Delta T_c) \delta(n - 1 - [i + 2kM]) \right\} \right] \bullet cos(\theta_k + \phi) \right\} \\ & + g(T_c + \Delta T_c) \delta(n - 1 - [i + 2kM]) \right\} \right] \bullet cos(\theta_k + \phi) \right\} \end{split}$$

(ec. 34)

5

donde  $\delta(n)$  es la función impulso unidad, que es igual a 1 para n igual a cero igual a 0 para cualquier otro valor de n. Desensanchando las señales serie I y Q y acumulando sobre un símbolo, se obtiene la siguiente ecuación para las señales I y Q de símbolo desensanchadas:

$$\begin{split} I(kT_s) &= \sum_{k=0}^{N} \bigg\{ \cos(\theta_k + \phi) \bigg[ 2M \bullet \alpha_0 - \sum_{i=2}^{2M-3} c_{i+2kM} \bullet \big\{ c_{i-2+2kM} \bullet \alpha_{.2} + c_{i+2+2kM} \bullet \alpha_2 \big\} \bigg] \\ &- \bigg[ \sum_{i=0}^{1} c_{i+2kM} \bullet \big\{ c_{i-2+2kM} \bullet \alpha_{.2} \cos(\theta_{k-1} + \phi) + c_{i+2+2kM} \bullet \alpha_2 \cos(\theta_k + \phi) \big\} \bigg] \\ &- \bigg[ \sum_{i=2M-2}^{2M-1} c_{i+2kM} \bullet \big\{ c_{i-2+2kM} \bullet \alpha_{.2} \cos(\theta_k + \phi) + c_{i+2+2kM} \bullet \alpha_2 \cos(\theta_{k+1} + \phi) \big\} \bigg] \\ &- sen \left( \theta_k + \theta_0 \right) \bigg[ \sum_{i=1}^{2M-2} c_{i+2kM} \bullet \big\{ c_{i-1+2kM} \bullet \alpha_{.1} - c_{i+1+2kM} \bullet \alpha_1 \big\} \bigg] \\ &+ c_{2kM} \bullet \big[ c_{2kM-1} \bullet \alpha_{.1} \cos(\theta_{k-1} + \phi) - c_{2kM+1} \bullet \alpha_1 \cos(\theta_{k+1} + \phi) \big] \bigg\} \end{split}$$

$$(ec. 35)$$

10

У

$$\begin{split} Q(kT_s) &= -\sum_{k=0}^{N} \bigg\{ \text{sen} \left( \theta_k + \phi \right) \bigg[ 2M \bullet \alpha_0 - \sum_{i=2}^{2M-3} c_{i+2kM} \bullet \left\{ c_{i-2+2kM} \bullet \alpha_{-2} + c_{i+2+2kM} \bullet \alpha_2 \right\} \bigg] \\ &- \bigg[ \sum_{i=0}^{1} c_{i+2kM} \bullet \left\{ c_{i-2+2kM} \bullet \alpha_{-2} \cos(\theta_{k-1} + \phi) + c_{i+2+2kM} \bullet \alpha_2 \cos(\theta_k + \phi) \right\} \bigg] \\ &- \bigg[ \sum_{i=2M-2}^{2M-1} c_{i+2kM} \bullet \left\{ c_{i-2+2kM} \bullet \alpha_{-2} \cos(\theta_k + \phi) + c_{i+2+2kM} \bullet \alpha_2 \cos(\theta_{k+1} + \phi) \right\} \bigg] \\ &+ \cos(\theta_k + \theta_0) \bigg[ \sum_{i=1}^{2M-2} c_{i+2kM} \bullet \left\{ c_{i-1+2kM} \bullet \alpha_{-1} - c_{i+1+2kM} \bullet \alpha_1 \right\} \bigg] \\ &+ c_{2kM} \bullet \bigg[ c_{2kM-1} \bullet \alpha_{-1} \cos(\theta_{k-1} + \phi) - c_{2kM+1} \bullet \alpha_1 \cos(\theta_{k+1} + \phi) \bigg] \bigg\} \end{split}$$

$$(ec. 36)$$

15

donde

$$\alpha_{n} = g(nT_{c} + \Delta T_{c}). \tag{ec 37}$$

Estas ecuaciones muestran que las propiedades de correlación cruzada de la secuencia de ensanchamiento a lo largo de la señal influyen en ambas señales I y Q de símbolo desensanchadas. Tal como muestran las ecuaciones, la propiedad de código de ensanchamiento para la propiedad de correlación cruzada con retardo de 1 y 2 chips para los 2M chips influye en las señales I y Q desensanchadas. Detectando el primer símbolo y despreciando los términos de ensanchamiento de símbolo cruzados, se obtienen las siguientes ecuaciones para las señales I y Q de primer símbolo desensanchadas:

$$I(0) = \cos(\theta_0 + \phi) \left[ 2M \bullet \alpha_0 - (\alpha_{-2} + \alpha_2) \sum_{i=0}^{2M-3} c_i \bullet c_{i+2} \right]$$

$$-\operatorname{sen}(\theta_0 + \phi) \left[ (\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_i \bullet c_{i+1} \right]$$

(ec 38)

10

у

5

$$Q(0) = -\left\{ sen(\theta_0 + \phi) \left[ 2M \bullet \alpha_0 - (\alpha_{-2} + \alpha_2) \sum_{i=0}^{2M-3} c_i \bullet c_{i+2} \right] + cos(\theta_0 + \phi) \left[ (\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_i \bullet c_{i+1} \right] \right\}.$$

(ec 39)

- Estas ecuaciones muestran que las propiedades de la secuencia de ensanchamiento y del error de temporización de chip, que influye en los términos α<sub>n</sub>, afecta a la magnitud y la fase de las señales I y Q de símbolo desensanchadas. La correlación cruzada con retraso de 2 chips para secuencia de ensanchamiento reduce la magnitud del término deseado tanto en la señal I como en la señal Q. La correlación cruzada con retraso de 1 chip para la secuencia de ensanchamiento introduce un desplazamiento de fase ya que es ortogonal al término deseado tanto en la señal I como en la señal Q. Como se aprecia en la FIGURA 9, el valor de autocorrelación QBL-MSK para los términos α<sub>-2</sub> y α<sub>2</sub> es menor o igual a 0,1, mientras que los términos α<sub>-1</sub> y α<sub>1</sub> tienen un valor tan alto como 0,67. Puesto que los términos α<sub>-1</sub> y α<sub>1</sub> son mucho mayores que los términos α<sub>-2</sub> y α<sub>2</sub> e introducen un desplazamiento de fase no deseado, estas ecuaciones pueden simplificarse despreciando los términos α<sub>-2</sub> y α<sub>2</sub>.

- Los resultados de la simulación computacional para 8 chips por símbolo (M = 4) confirmaron que los términos  $\alpha_{\cdot 2}$  y  $\alpha_{2}$  pueden despreciarse sin causar una degradación significativa en el rendimiento. Por lo tanto, el proceso de corrección de fase utilizado en la presente invención se basa solamente en los términos  $\alpha_{\cdot 1}$  y  $\alpha_{1}$ . En otra realización, sin embargo, este proceso de corrección de fase puede ser fácilmente modificado para incorporar los términos  $\alpha_{\cdot 2}$  y  $\alpha_{2}$ .

Utilizando sólo los términos  $\alpha_{-1}$  y  $\alpha_1$  (asumiendo que  $\alpha_0$  es aproximadamente 1) en esta realización a modo de ejemplo, las señales I y Q de primer símbolo desensanchadas se reducen a la expresión siguiente:

$$I(0) = 2M \bullet \cos(\theta_0 + \phi) - \operatorname{sen}(\theta_0 + \phi) \left[ (\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_i \bullet c_{i+1} \right]$$

(ec 40)

35

У

$$Q(0) = -\left\{2M \bullet \operatorname{sen}(\theta_0 + \phi) + \cos(\theta_0 + \phi)\left[\left(\alpha_{\cdot 1} - \alpha_1\right)\sum_{i=0}^{2M-2} c_i \bullet c_{i+1}\right]\right\}.$$

(ec 41)

La aplicación de las ecuaciones del primer símbolo I y Q a las señales I y Q de símbolo desensanchadas da como resultado las siguientes ecuaciones para las señales I y Q de símbolo desensanchadas:

$$\begin{split} I(kT_s) &= 2M \bullet \cos(\theta_k + \phi) - \operatorname{sen}(\theta_k + \phi) \bigg[ (\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_{i+2kM} \bullet c_{i+2kM+1} \bigg] \\ &= A(k) \bullet \cos(\theta_k + \phi + \gamma(k)) \end{split}$$

(ec 42)

у

$$\begin{split} Q(kT_s) &= -\bigg\{2M \bullet \text{sen}\big(\theta_k + \phi\big) + \cos(\theta_k + \phi)\bigg[\big(\alpha_{-1} - \alpha_1\big)\sum_{i=0}^{2M-2} c_{i+2kM} \bullet c_{i+2kM+1}\bigg]\bigg\} \\ &= -A(k) \bullet \text{sen}\big(\theta_k + \phi + \gamma(k)\big); \end{split} \tag{ec 43}$$

donde

$$A(k) = \sqrt{4M^2 + \left[ (\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_{i+2kM} \cdot c_{i+2kM+1} \right]^2}$$

(ec 44)

10 y

5

$$\gamma(k) = \tan^{-1} \left[ \frac{(\alpha_{-1} - \alpha_1) \sum_{i=0}^{2M-2} c_{i+2kM} \cdot c_{i+2kM+i}}{2M} \right].$$

(ec 45)

El término γ(k) de fase representa el desplazamiento de fase producido por el error de temporización de chip y la propiedad de secuencia de ensanchamiento. Haciendo referencia ahora a la FIGURA 15, las señales I y Q de símbolo desensanchadas son enviadas al módulo de corrección de fase, designado genéricamente como módulo 171, para eliminar este término de error de fase y recuperar los símbolos I y Q transmitidos.

Tal como se muestra, las señales I y Q desensanchadas son corregidas en fase en primer lugar utilizando la propiedad de código de ensanchamiento (SCP) y la estimación del error de temporización de chip para la función SYNC/secuencia de prueba en serie. Para modulación de datos QPSK, los símbolos I y Q detectados se obtienen directamente de las salidas I y Q del módulo 171 de corrección de fase. Para ello se asume que el seguimiento de fase de portadora coherente se lleva a cabo en la señal para eliminar el error de frecuencia de portadora y el error de fase. Para modulación de datos DQPSK, se lleva a cabo una detección diferencial mediante el módulo 182 de detección diferencial para recuperar los símbolos I y Q. La demodulación DQPSK no necesita de la frecuencia de portadora y el seguimiento de fase que sí necesita la modulación QPSK.

El módulo 171 de corrección de fase utiliza la propiedad de código de ensanchamiento (SCP) y estimaciones de temporización de chip para determinar el término de corrección de fase apropiado. La propiedad de código de ensanchamiento (SCP) se determina en el módulo 184 de determinación de autocorrelación de secuencia de ensanchamiento mediante la generación de una propiedad de correlación cruzada con retardo de 1 chip para los 2M chips utilizados para ensanchar el símbolo. Para el símbolo k, la propiedad de código de ensanchamiento es la siguiente:

$$SCP(k) = \sum_{i=2kM}^{2M^{\bullet}(k+1)-2} c_i \cdot c_{i+1};$$

(ec 46)

35

40

donde los valores (c<sub>i</sub>) de chip son iguales a -1 ó a +1 y el ensanchamiento es de 2M chips por símbolo tal como se muestra en la FIGURA 10. Para 8 chips por símbolo, por ejemplo, M es igual a 4, lo que corresponde a 4 chips pares y 4 chips impares por símbolo, dando como resultado la siguiente ecuación de propiedad de código de ensanchamiento:

$$SCP(k) = \sum_{i=8^{4}k}^{8^{4}(k+1)\cdot 2} c_{i} \bullet c_{i+1}. \qquad (ec 47)$$

La propiedad  $\{SCP(k)\}$  de código de ensanchamiento determinada en el módulo 184 junto con la información  $\{X1, Y1, Y2, e Y3\}$  de error de temporización de chip de la función SYNC/secuencia de prueba en serie de la FIGURA 13 se utilizan para proporcionar un término  $\gamma_i(k)$  de corrección de fase, que idealmente es igual a  $\gamma(k)$ . La función SYNC/secuencia de prueba en serie establece la información de error de temporización de chip a lo largo del bloque de mensaje entre SYNC y la secuencia de prueba en serie o entre dos secuencias de prueba en serie, mientras que la propiedad de código de ensanchamiento se calcula para cada símbolo en el módulo 184 de secuencia de ensanchamiento.

Como ejemplo, para un ensanchamiento de 8 chips por símbolo, para un símbolo k dado, el valor de SCP(k) toma el valor de -7, -5, -3 -1, 1, 3, 5, ó 7. Utilizando el valor de la propiedad de código de ensanchamiento para cada símbolo junto con la estimación {X1, Y1, Y2, e Y3} de temporización de chip, se selecciona la corrección de fase apropiada para el símbolo basándose en una tabla de consulta, tal como la TABLA 1, a la que se hace referencia como Tabla 186 de corrección en la FIGURA 15. La salida de la tabla de corrección de fase, γ<sub>i</sub>(k), es una estimación del error γ(k) real de fase.

Las señales I y Q de símbolo corregidas en fase  $\{l_c(k) \ y \ Q_c(k)\}$  están dadas por las siguientes ecuaciones:

$$I_{c}(kT_{s}) = A(k) \bullet \left[\cos(\theta_{k} + \phi) \bullet \cos(\gamma_{1}(k)) + \sin(\theta_{k} + \phi + \gamma(k)) \bullet \sin(\gamma_{1}(k))\right]$$

$$= A(k) \bullet \cos(\theta_{k} + \phi + \gamma(k) - \gamma_{1}(k))$$

(ec 48)

20 y

30

$$Q_{c}(kT_{s}) = A(k) \bullet \left[ sen(\theta_{k} + \phi) \bullet cos(\gamma_{1}(k)) - cos(\theta_{k} + \phi + \gamma(k)) \bullet sen(\gamma_{1}(k)) \right]$$

$$= A(k) \bullet sen(\theta_{k} + \phi + \gamma(k) - \gamma_{1}(k)). \tag{ec 49}$$

- Tal como muestran estas ecuaciones, si γ<sub>i</sub>(k) es igual a γ(k), el término de error de fase se hace nulo. Puesto que la Tabla 186 de corrección de fase tiene valores finitos, existe un término de error de fase pequeño tal como se muestra en la curva de rendimiento de tasa de error binario mejorado de la FIGURA 4. Para simplificar adicionalmente el proceso de corrección de fase, las tablas simplificadas de coseno y seno, mostradas en las TABLAS 2 y 3, respectivamente, pueden utilizarse en el proceso de corrección de fase llevado a cabo por el módulo 171 de corrección de fase.

- La implementación de la corrección de fase para cada símbolo se lleva a cabo en el módulo 171 de corrección de fase utilizando rotadores de fase, tal como se muestra en la FIGURA 15. En otra realización, tal como en un receptor RAKE, la operación de corrección de fase puede llevarse a cabo para cada rama del RAKE. Los parámetros {X1, Y1, Y2, e Y3} de corrección de fase para cada rama del RAKE independiente junto con la propiedad de código de ensanchamiento para cada símbolo pueden utilizarse para elegir la corrección de fase apropiada para cada símbolo en cada rama del RAKE en el demodulador.

- Volviendo la FIGURA 15, las señales I y Q desensanchadas, I(k) y Q(k), respectivamente, entran en el módulo 171 de corrección de fase y son multiplicadas por la señal cos[γ<sub>i</sub>(k)] de corrección de fase en los mezcladores 170 y 180 y por la señal sen[γ<sub>i</sub>(k)] de corrección de fase en los mezcladores 174 y 176. Las señales resultantes que provienen de los mezcladores 170 y 174 son entonces combinadas por un sumador 172 y las señales resultantes que provienen de los mezcladores 176 y 180 son combinadas en el sumador 178.

- Después de la corrección de fase, se determinan los símbolos I y Q de datos. Para modulación de datos QPSK, los símbolos I y Q detectados se obtienen directamente de las salidas I y Q del módulo 171 de corrección de fase. Para ello se asume que el seguimiento de fase de portadora coherente se lleva a cabo en la señal para eliminar el error de frecuencia de portadora y el error de fase (término \$\phi\$ en las ecuaciones 48 y 49). Las señales I y Q de símbolo {Ic(k) y Qc(k)} corregidas son comparadas con cero independientemente una de otra para determinar si se recibió un +1 (lógica 0) o un -1 (lógica 1) para ese símbolo correspondiente. Para demodulación DQPSK, las señales I y Q de símbolo {Ic(k) y Qc(k)} corregidas son procesadas por el detector 182 diferencial DQPSK para determinar las señales I y Q de símbolo {Id(k) y Qd(k)} detectadas. Las señales I y Q de símbolo detectadas obtenidas en la salida del detector diferencial son comparadas con cero independientemente una de otra para determinar si se recibió un +1 (lógica 0) o un -1 (lógica 1) para ese símbolo correspondiente.

- En resumen, un aspecto de la presente invención reduce la degradación del rendimiento de la tasa de error binario (BER) asociada con modulación de datos QPSK o DQPSK en señales de espectro ensanchado de secuencia directa, tales como QBL-MSK, proporcionando un término de corrección de fase basado en la propiedad de

secuencia de ensanchamiento y en una estimación del error de temporización de chip. El término de corrección de fase también puede utilizarse para mejorar la detección de datos QPSK o DQPSK en receptores que funcionan a una velocidad de muestreo igual a la velocidad de transmisión de chips o en receptores que funcionan a frecuencias de muestreo mayores que el doble de la velocidad de transmisión de chips. El funcionamiento a frecuencias de muestreo diferentes necesita simplemente un cambio apropiado en la tabla de corrección de fase.

El proceso de corrección de fase descrito en la presente memoria para QPSK/DQPSK puede extenderse para incluir órdenes superiores de modulación de fase, tales como 8-PSK y 8-PSK Diferencial. Además, la técnica de corrección de fase puede utilizarse para reducir la degradación del rendimiento de la tasa de error binario asociada a la utilización de modulación de datos π/4-QPSK o π/4-QPSK diferencial en una señal de espectro ensanchado de secuencia directa serie, tal como QBL-MSK.

Además de permitir cambios en el tipo de modulación de datos, el proceso de corrección de fase puede utilizarse mediante la aplicación de formateo serie a otras señales de modulación de ensanchamiento en cuadratura, tales como esquemas de Modulación por Desplazamiento de Fase en Cuadratura con Corrimiento (OQPSK, Offset Quadrature Phase Shift Keying), Modulación por Desplazamiento Mínimo (MSK, Minimum Shift Keying), MSK Gaussiana, Modulación de Frecuencia Moderada (TFM, Tamed Frequency Modulation), Modulación por Desplazamiento de Fase en Cuadratura con Corrimiento Libre de Fluctuaciones Inter-símbolo (IJF-OQPSK, Intersymbol Jitter Free Offset Quadrature Phase Shift Keying), Modulación por Desplazamiento de Fase en Cuadratura con Corrimiento por Filtrado de Coseno Alzado (RC-OQPSK, Raised Cosine filtered Offset Quadrature Phase Shift Keying), y Modulación de Fase Continua (CPM, Continuous Phase Modulation) eficiente en ancho de banda.

Las referencias para encontrar otras descripciones similares y no similares son las siguientes: US 7.630.428 A, US 7.822.100A, US 7.609.755A, US 7.801.255A y US 7.715.505A.

Tabla 1. Corrección de Fase (grados) para Diferentes Propiedades de Código de Ensanchamiento.

| ΔTc         | X1 | Y1=X2<br>o X3 | Y2=X4<br>o X5 | Y3=X6<br>o X7 | Corrección de Fase (grados) para los Diferentes<br>Valores de Sumación de Retardo 1 * Tc |     |    |    |    |    |     |     |

|-------------|----|---------------|---------------|---------------|------------------------------------------------------------------------------------------|-----|----|----|----|----|-----|-----|

|             |    |               |               |               | 7                                                                                        | 5   | 3  | 1  | -1 | -3 | -5  | -7  |

| -<br>0.5000 | 0  | 1             | 1             | 0             | -5                                                                                       | -3  | -2 | 0  | 0  | 2  | 3   | 5   |

| -<br>0.4375 | 0  | 1             | 1             | 0             | -5                                                                                       | -3  | -2 | 0  | 0  | 2  | 3   | 5   |

| -<br>0.3750 | 0  | 1             | 0             | 0             | -15                                                                                      | -10 | -5 | -2 | 2  | 5  | 10  | 15  |

| -<br>0.3125 | 0  | 1             | 0             | 0             | -15                                                                                      | -10 | -5 | -2 | 2  | 5  | 10  | 15  |

| -<br>0.2500 | 0  | 1             | 0             | 0             | -15                                                                                      | -10 | -5 | -2 | 2  | 5  | 10  | 15  |

| -<br>0.1875 | 0  | 0             | 0             | 1             | 15                                                                                       | 10  | 5  | 2  | -2 | -5 | -10 | -15 |

| -<br>0.1250 | 0  | 0             | 0             | 1             | 15                                                                                       | 10  | 5  | 2  | -2 | -5 | -10 | -15 |

| -<br>0.0625 | 0  | 0             | 0             | 0             | 5                                                                                        | 3   | 2  | 0  | 0  | -2 | -3  | -5  |