## OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11 Número de publicación: 2 551 883

(51) Int. Cl.:

H03F 1/30 (2006.01) H03F 1/34 (2006.01) H03F 1/56 (2006.01) H03F 3/185 (2006.01) H03F 1/26 (2006.01) H03F 3/195 (2006.01)

(12) TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: 01.02.2012 E 12153472 (1) (97) Fecha y número de publicación de la concesión europea: 19.08.2015 EP 2624448

(54) Título: Amplificador de bajo ruido

ig(45ig) Fecha de publicación y mención en BOPI de la traducción de la patente: 24.11.2015

(73) Titular/es:

TELEFONAKTIEBOLAGET L M ERICSSON (PUBL) (100.0%) 164 83 Stockholm, SE

(72) Inventor/es:

MATTISSON, SVEN y ANDERSSON, STEFAN

(74) Agente/Representante:

DE ELZABURU MÁRQUEZ, Alberto

### **DESCRIPCIÓN**

Amplificador de bajo ruido

#### 5 Campo técnico

La presente invención se refiere al campo de los amplificadores de bajo ruido para receptores, tales como receptores de radio.

#### Antecedentes

20

40

45

65

10 Cuando se diseña un amplificador de bajo ruido (LNA). es importante considerar la necesaria adaptación de la impedancia de entrada (es decir, a 50 Ω), la coincidencia del ancho de banda, la cifra de ruido, la linealidad y el consumo de energía. Si el LNA tiene una impedancia de entrada apropiada, la adaptación de la red facilitará el diseño y una fabricación consistente. Si el componente resistivo de la impedancia de entrada del LNA está muy adaptación deseada impedancia de (es 15 Ω) es muy difícil adaptarla adecuadamente sin añadir pérdidas resistivas extra, y, por consiguiente, ruido. También una red de adaptación de banda ancha será más compleja que una de banda más estrecha. Para mantener bajos el costo y el tamaño es importante que un LNA se pueda adaptar a diversas frecuencias de entrada. Esto requiere estructuras de LNA de banda ancha. Finalmente, normalmente es deseable disponer de un punto de compresión de entrada del LNA muy alto, sin sacrificar el consumo de energía.

Son dos los métodos comunes que se usan para ajustar la parte resistiva de la impedancia de entrada del LNA: degradación resistiva paralelo o degradación inductiva serie.

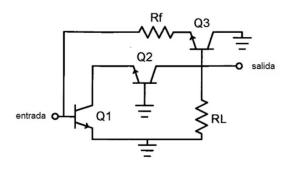

En el caso de un LNA de degradación resistiva paralelo, ilustrado en la figura 1, la resistencia de entrada R<sub>in</sub> se fija por medio de la ganancia en tensión del circuito y de la resistencia Rf. Suponiendo que la carga esté dominada por RL, se ajusta la transconductancia por medio de Q1, y al ser alta la impedancia de entrada de lazo abierto, entonces se puede obtener R<sub>in</sub> ≈ Rf/(1+gm1·RL), en donde gm1 es la transconductancia de Q1. Un valor típico de Rf es de alrededor de 500 Ω. El transistor en montaje base común Q2 aísla la resistencia de carga de Q1 para aumentar la ganancia en tensión, y el Q3 en montaje seguidor de emisor aísla Rf de RL para minimizar la carga. Tal combinación de una etapa en emisor común y una etapa en base común se llama cascodo, y es un método común para mejorar la ganancia y el aislamiento inverso de una etapa sencilla en montaje emisor común. Los cascodos se pueden formar por medio de cualquier combinación de transistores MOS, BJT y MESFET, incluyendo la mezcla de tipos. Una desventaja con el LNA de degradación resistiva paralelo es la presencia de la resistencia Rf, que degrada la cifra de ruido. Un posible camino para mejorar la cifra de ruido es aumentar la ganancia. Sin embargo, al hacerlo así se degrada normalmente la linealidad.

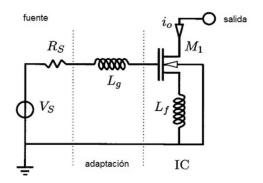

En los circuitos con MOS y MESFET, la degradación inductiva serie, ilustrada en la figura 2 es más corriente que la degradación resistiva paralelo. De acuerdo con la terminología común, la resistencia de entrada será Rin ≈ gm·Lf/Cgs), en donde gm y Cgs son respectivamente la transconductancia y la capacidad entre puerta y fuente del transistor M1. Un valor típico de Lf es 1 nH. La degradación inductiva serie es inherentemente de banda más estrecha ya que la impedancia de entrada corresponde básicamente a un resonador RLC en serie, típicamente con al menos un Q moderado (por ejemplo, 1 << Q <10, que puede obtenerse típicamente por medio de una reactancia integrada en el chip). Una desventaja de la degradación serie de la figura 2 es que la transconductancia en lazo cerrado del LNA se reduce típicamente a la mitad del valor de M1 solo, y que se necesita una inductancia de adaptación de Lg, que normalmente es externa y su valor depende de la frecuencia real de trabajo. El tamaño de Lf, cuando está integrada en el chip, puede también ser otra cuestión. Además, la estructura es inherentemente de banda estrecha así como que la impedancia de entrada corresponde aproximadamente a un resonador serie.

El artículo Adabi et al, "CMOS Low Noise Amplifier with capacitive feedback matching", Proc. IEEE 2007 Custom Integrated Circuits Conference, páginas 643-646 (a continuación referido como "Adabi et al") muestra en la figura 1 en ese documento un LNA con realimentación capacitiva.

El documento WO 02/15397 A2 describe un amplificador de ganancia conmutable. El amplificador incluye una entrada, una salida y un primer transistor que tiene una región de control, una primera región y una segunda región.

La conducción desde la primera región a la segunda región del primer transistor responde a la tensión en la región de control con respecto a la segunda región. Una red de adaptación de impedancia de entrada está acoplada con la entrada y con la región de control y una red de adaptación de impedancia de salida está acoplada con la salida y la primera región. Un primer circuito de polarización conmutable está acoplado con la región de control para polarizar conmutablemente al transistor entre un estado de conducción y un estado de no conducción. Una red pasiva de desvío tiene un conmutador para acoplar conmutablemente la red de adaptación de impedancia de entrada con la red de adaptación de impedancia de salida a través de la red pasiva de desvío.

#### Sumario

Los inventores han comprobado que el uso de un LNA de realimentación capacitiva tal como ilustra la figura 1 de Adabi et al puede subsanar al menos alguna de las desventajas del LNA de degradación resistiva paralelo y del LNA

de degradación inductiva serie, citados anteriormente. Sin embargo, los inventores han comprobado además que, incluso si tal LNA de realimentación capacitiva proporciona una impedancia de entrada resistiva adaptada con relativo amplio ancho de banda, el ancho de banda utilizable del LNA está limitado a pesar de todo porque el ancho de banda de la ganancia es relativamente bajo en comparación con el ancho de banda de la impedancia de entrada resistiva. Un objetivo de la presente invención es, por consiguiente, proporcionar un amplificador de bajo ruido mejorado con realimentación capacitiva para usarlo en un circuito receptor.

De acuerdo con un primer aspecto, se proporciona un circuito receptor que consta de un circuito amplificador de bajo ruido (LNA) en montaje de fuente común o emisor común para amplificar las señales a la frecuencia de trabajo f en un circuito receptor. El circuito del LNA comprende un transistor de entrada dispuesto para, en funcionamiento, estar polarizado para tener una transconductancia *gm* a la frecuencia de trabajo *f* que tiene un primer terminal, que es un terminal de puerta o base, conectado operativamente a un terminal de entrada del circuito del LNA. El circuito del LNA comprende además un condensador de realimentación paralelo conectado operativamente entre el primer terminal del transistor de entrada y un segundo terminal, que es el terminal de drenaje o de colector del transistor de entrada. Además, el circuito del LNA comprende un condensador de salida conectado operativamente entre el segundo terminal del transistor de entrada y un terminal de salida del circuito del LNA. El condensador de salida tiene una capacidad de valor  $C_L < gm/f$ .

- El circuito receptor consta además de un circuito de terminación con un terminal de entrada de corriente conectado al terminal de salida del circuito del LNA. El circuito de terminación es o comprende un amplificador en base común, un amplificador en puerta común, un amplificador de transimpedancia, un amplificador operacional conectado en realimentación y un nodo de tierra virtual como terminal de entrada de corriente, un transformador o un mezclador en modo de corriente.

- El transistor de entrada puede ser un transistor MOS, por lo cual el primer terminal es un terminal de puerta, el segundo terminal es un terminal de drenaje y el circuito del LNA es un circuito del LNA en fuente común. El condensador de realimentación paralelo puede ser o puede comprender la capacidad de puerta MOS obtenida con un transistor MOS del mismo tipo que el transistor de entrada. El condensador de realimentación puede ser o puede comprender la capacidad entre puerta y drenaje del transistor de entrada.

El transistor de entrada puede ser un transistor de unión bipolar, por lo cual el primer terminal es la base, el segundo terminal es el colector y el circuito del LNA es un circuito del LNA en emisor común.

El circuito del LNA puede comprender una inductancia en serie conectada operativamente entre el primer terminal del transistor de entrada y el terminal de entrada del circuito del LNA 30.

La magnitud  $|Z_{in}(f)|$  dela impedancia de entrada  $Z_{in}$  del circuito de terminación a la frecuencia f puede ser menor de 1/10 de la magnitud  $|Z_{CL}(f)| = 1/(2\pi f \cdot C_L)$  de la impedancia  $Z_{CL}(f)$  del condensador de salida del circuito del LNA.

40 El circuito receptor puede ser un circuito receptor de radio.

De acuerdo con un segundo aspecto, se proporciona un aparato de radiocomunicación que consta de circuito receptor de acuerdo con el primer aspecto. El aparato de radiocomunicación puede por ejemplo ser, pero no se limita a, un terminal móvil, un módem de datos inalámbrico o una estación base de radio.

De acuerdo con un tercer aspecto, se proporciona un aparato de comunicación cableada que consta del circuito receptor de acuerdo con el primer aspecto. El aparato de comunicación cableada puede por ejemplo ser, pero no se limita a, un módem de cable.

- Las realizaciones adicionales se definen en las reivindicaciones dependientes. Se debe enfatizar que el término "comprende/que comprende" cuando se usa en esta especificación se considera que especifica la presencia de características establecidas, integrados, etapas o componentes, pero no excluye la presencia o la adición de una o más de otras características, integrados, etapas, componentes o grupos de los mismos.

- 55 Breve descripción de los dibujos

5

30

45

60

Objetivos, características y ventajas adicionales de las realizaciones de la invención serán evidentes a partir de la siguiente descripción detallada, con referencia a los dibujos que se acompañan, en los cuales:

La figura 1 ilustra un amplificador de bajo ruido de realimentación paralelo resistiva;

La figura 2 ilustra un amplificador de bajo ruido degradado serie inductivo;

La figura 3 ilustra esquemáticamente un terminal móvil en comunicación con una estación base de radio:

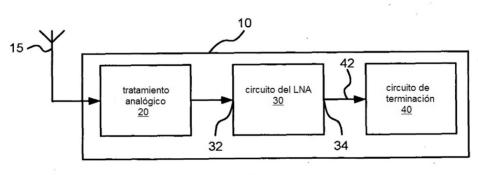

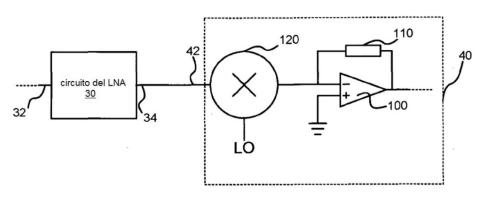

La figura 4 muestra un diagrama de bloque simplificado de un circuito receptor de radio de acuerdo con algunas realizaciones de la presente invención;

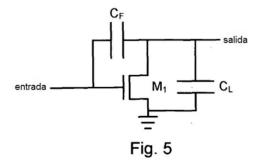

La figura 5 ilustra un amplificador de realimentación paralelo capacitiva convencional;

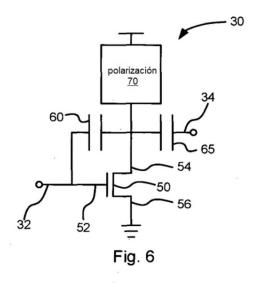

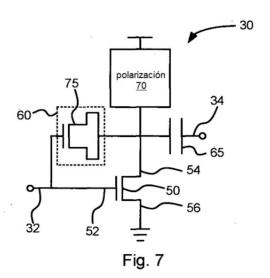

Las figuras 6 a 9 son diagramas esquemáticos de circuitos simplificados de realizaciones de un circuito amplificador de bajo ruido; y

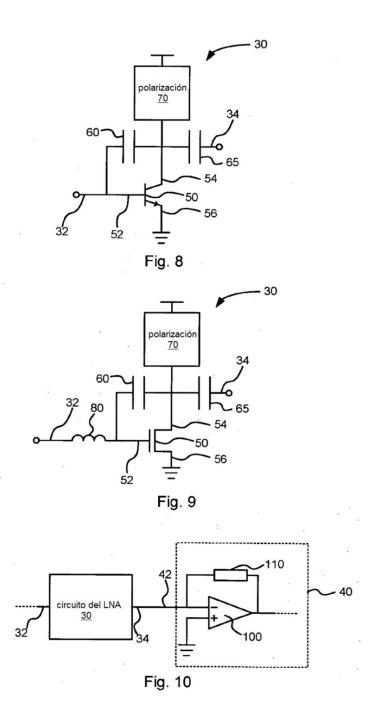

Las figuras 10 a 11 ilustran parte de un circuito receptor de radio de acuerdo con una realización de la presente invención.

#### Descripción detallada

5

10

15

35

50

55

60

La figura 3 ilustra esquemáticamente un entorno en el cual se pueden emplear realizaciones de la presente invención. En la figura 3 un terminal móvil 1, ilustrado en la figura 3 como un teléfono 1 móvil, o celular, está en comunicación inalámbrica con una estación base de radio 2, por ejemplo, en una red de comunicación celular. El teléfono móvil 1 y la estación base de radio 2 son ejemplos no limitativos de lo que se referirá más adelante genéricamente con el término aparato de radiocomunicación. Otro ejemplo no limitativo de tal aparato de radiocomunicación es un módem de datos inalámbrico, por ejemplo, un módem de datos inalámbrico para ser empleado en una red de comunicación celular. Las realizaciones de la presente invención se pueden también emplear en aparatos de radiocomunicación para trabajar en otros tipos de redes de comunicación, tales como, pero sin estar limitadas a, redes inalámbricas de área local (WLANs) y redes de área personal (PANs). Las realizaciones de la presente invención pueden además emplearse también en otros tipos de aparatos de comunicación, por ejemplo, aparatos de comunicación cableada, tales como, pero sin estar limitados a, módems con cable.

Los aparatos de comunicación puede constar de uno o más circuitos receptores, tales como uno o más circuitos radio receptores en el caso de aparatos de radiocomunicación. Un ejemplo de tal circuito radio receptor se describe brevemente a continuación con referencia a la figura 4. La figura 4 es un diagrama de bloques simplificado de un circuito 10 radio receptor de acuerdo con una realización de la presente invención. En la figura 4, el circuito 10 radio receptor está conectado a una antena 15 para recibir señales electromagnéticas de radiofrecuencia (RF). Aunque se muestra una única antena 15 en la figura 4, se pueden utilizar múltiples antenas en otras realizaciones. En la realización ilustrada en la figura 4, el circuito radio receptor comprende la circuitería 20 de tratamiento analógico para la conexión operativa a la antena 15. La circuitería 20 de tratamiento analógico está adaptada para realizar tratamiento de la señal (analógico) sobre la señales de RF de la antena 15. La circuitería 20 de tratamiento analógico puede comprender uno o más filtros y/o otra circuitería para tratar las señales de RF. Tal circuitería es, per se, bien conocida en la técnica de los radio receptores y por consiguiente no se describirá en este documento con mayor detalle.

Adicionalmente, la realización del circuito 10 radio receptor ilustrado en la figura 4 comprende un circuito 30 amplificador de bajo ruido (LNA), que tiene un terminal de entrada 32 y un terminal de salida 34. Las realizaciones del circuito del LNA 30 se describen a continuación, con más detalle. La realización del circuito radio receptor ilustrado en la figura 4 comprende además un circuito de terminación 40 que tiene un terminal de entrada 42 conectado al terminal de salida 34 del circuito del LNA 30. El término "circuito de terminación" se refiere en este contexto a cualquier circuito conectado al terminal de salida 34 del circuito del LNA 30 y que actúa consecuentemente como una terminación del circuito del LNA 30.

Como se ha indicado anteriormente, las realizaciones del circuito del LNA 30 se pueden emplear en otros tipos de circuitos receptores diferentes de los circuitos radio receptores, por ejemplo, circuitos para aparatos de comunicación cableada. En tal caso, en lugar de la antena, dicho circuito receptor se puede conectar a un conector para su conexión a una red de comunicación cableada. La estructura básica indicada en la figura 4, con circuitería de tratamiento analógico 20, un circuito del LNA 30 y un circuito de terminación 40 se puede asimismo utilizar en tal circuito receptor (no de radio).

Antes de describir las realizaciones del circuito del LNA 30 con más detalle, se proporciona una descripción del análisis adicional de los inventores de los circuitos en las figuras 1 y 2 para facilitar la comprensión de las realizaciones de la presente invención. En lo que sigue,  $\omega$  significa la pulsación y  $s=j\omega$ , donde J es la unidad imaginaria.

Un inconveniente del circuito de realimentación resistiva paralelo (figura 1) es que requiere relativamente altos niveles de corriente a través de Q3 para trabajar apropiadamente y que Q3 añade carga parásita (fuera del lazo de realimentación, Rf) del nodo de salida que limita el rendimiento a altas frecuencias. La resistencia de realimentación también añade pérdidas capacitivas al sustrato (tierra) que influye en el rendimiento a altas frecuencias. Si no se usa Q3 (por ejemplo, Rf se conecta directamente a RL) la ganancia será ligeramente menor ya que algo de la corriente de colector de Q1 fluirá a través de Rf. A menos que Rf >> Rin (por ejemplo, cuando la ganancia en tensión sea muy alta), Rf degradará la cifra de ruido (NF) significativamente. El ruido del colector de Q1, o el ruido de drenaje en el caso de transistor MOS,  $i_n^2$  se realimentará también a la entrada y añadirá ruido. Como aproximación básica podemos decir que la degradación por ruido (aumento) debido a R f y  $i_n^2$  es,

$$\Delta NF \approx 10 \log_{10} \left( 1 + \frac{\gamma}{g_{ml} R_{in}} \left( \frac{A}{2+A} \right)^2 + \frac{1}{1+A} \right)$$

EC.1

En la ecuación 1, A significa la ganancia en tensión del circuito,  $\gamma$  es aproximadamente la mitad para un transistor de unión bipolar (BJT) y aproximadamente 2/3 para un transistor MOS, y  $R_{in}$  y  $g_{m1}$  son la resistencia de entrada del circuito y la transconductancia del transistor Q1, respectivamente. Para un BJT trabajando a 5 mA sobre  $R_{in}$  = 50 $\Omega$  y A = 10, la degradación de la cifra de ruido  $\Delta NF$  es alrededor de 0,65 dB. La correspondiente degradación de la cifra de ruido  $\Delta NY$  para un montaje con transistor MOS a la misma corriente es alrededor de 0,9 dB y obtener una  $\Delta NF$  similar como en el caso del transistor BJT requeriría alrededor del doble de corriente en el montaje con transistor MOS.

10

15

20

5

Se necesita una alta ganancia en tensión en el LNA para bajo ruido pero al mismo tiempo se reducirá linealmente y se recortará el nodo de salida que está a un nivel fijo, limitado por la corriente de polarización o la tensión de alimentación, y el correspondiente punto de compresión de entrada será, por consiguiente, inversamente proporcional a la ganancia del LNA. Por ejemplo, suponiendo que el recorte en la salida del LNA tenga la amplitud de 1v, entonces, con A = 10 se obtendrá un punto de compresión de entrada en  $50\Omega$  de alrededor -10 dBm. Una amplitud de un voltio corresponde casi a la diferencia de tensión entre los dos terminales de alimentación para un transistor bipolar típico, mientras que es casi el doble de la tensión de alimentación de los dispositivos MOS. Por consiguiente, esto es ya es mayor en la práctica y no puede ser fácilmente aumentado; la ganancia tiene que está limitada para una linealidad razonable. Es decir, existe un conflicto añadido entre la linealidad y la cifra de ruido para un LNA de realimentación paralelo resistiva. Elevar el paralelo insertando una inductancia en serie con RL o utilizar un resonador paralelo en lugar de RL no cambiará fundamentalmente este problema, sólo proporcionará un ancho de banda o una frecuencia de trabajo ligeramente mayores respectivamente con un menor consumo de energía pero con una relativamente alta penalización de tamaño y costo.

Un inconveniente de la degradación en serie de la figura 2 es que la transconductancia en lazo cerrado del LNA se reduce, típicamente a la mitad del valor de la transconductancia de M1 solo. Además, se necesita una inductancia Lg de adaptación. Típicamente esto consiste en una inductancia externa (fuera del chip) cuyo valor depende de la frecuencia real de trabajo. El tamaño de Lf, cuando se encuentra integrada en un chip, puede ser también otro inconveniente. Además, inherentemente la estructura tiene un ancho de banda relativamente estrecho y la impedancia de entrada es aproximadamente

$$Z_{in}(s) = Z_{match}(s) + Z_{IC}(s) \approx sL_g + \frac{1}{sC_{gs}} + (1 + \beta(s))sL_f = \frac{1}{sC_{gs}} + s(L_f + L_g) + g_m \frac{L_f}{C_{gs}}$$

FC

35

40

Esto corresponde a un resonador serie. El parámetro  $\beta(s)$  es la ganancia en corriente dependiente de la frecuencia del transistor M1, gm significa la transconductancia del transistor M1,  $C_{gs}$  significa la capacidad entre puerta y fuente del transistor M1 y  $Z_{match}(s)$  y  $Z_{IC}(s)$  significan la impedancia de la parte etiquetada adaptación y de la parte etiquetada IC (Circuito Integrado), respectivamente, en la figura 2. Este resonador serie necesita ser sintonizado para cada banda de frecuencia de interés, y aunque las partes integradas, M1 y  $L_{fr}$ , pueden soportar un amplio margen de frecuencias, la inductancia  $L_{g}$  tiene que ser optimizada para cada configuración de banda. A veces  $L_{g}$  se reemplaza por una red de adaptación más compleja para compensar los parásitos (no mostrada en la figura 2), por ejemplo, protección ESD (Descarga Electrostática), pero esto no aumenta significativamente el margen de frecuencias para un conjunto dado de valores de los componentes.

45

50

La realimentación serie inductiva se basa en la ganancia de corriente dependiente de la frecuencia  $(A_I)$  del transistor de entrada para obtener una adaptación de impedancias resistiva. Esto se cumple para la mayoría de los MOSFET con  $A_I \approx g_{rr}/(sC_{gs})$ , y por consiguiente tiene un comportamiento capacitivo, para todas las frecuencias de interés. Una adaptación de impedancias resistiva similar, sin la necesidad de una bobina  $L_f$ , se puede obtener con un LNA de realimentación paralelo capacitiva (tal como el que se muestra en la figura 1 de Adabi). Un diagrama esquemático simplificado de tal circuito LNA de realimentación paralelo capacitiva se ilustra en la figura 5 para referencia. Este circuito convierte la impedancia de realimentación capacitiva en una impedancia de entrada resistiva por medio de la ganancia en tensión dependiente de la frecuencia (oc  $1/\omega$ ).

La impedancia de entrada del circuito de la figura 5 es aproximadamente

$$Z_{in}(s) \approx \frac{\frac{1}{g_m} \left( 1 + \frac{C_L}{C_F} \right)}{1 + s \frac{C_{gs}}{g_m} \left( 1 + \frac{C_L}{C_F} \right)}$$

EC. 3

La impedancia de entrada tiene una característica de paso bajo con una parte resistiva aproximadamente igual a (1 +  $C_L/C_F)/g_m$  y un ancho de banda aproximadamente igual a  $\omega_T/(1 + C_L/C_F)$ , en donde  $\omega_T$  significa la pulsación de tránsito del transistor que normalmente es mucho mayor que la frecuencia de trabajo.

La ganancia en tensión A<sub>V</sub> del circuito de la figura 5 depende de la frecuencia con un carácter de paso bajo

$$A_{\nu} \approx \frac{sC_F - g_m}{sC_F + sC_L} \approx -\frac{g_m}{sC_F + sC_L}$$

EC. 4

10

15

5

Las aproximaciones de la figura 4 son válidas para valores típicos de componentes y frecuencias típicas de interés alcanzables y se usan en los LNA de circuito integrado. De modo que, a pesar de proporcionar una impedancia de entrada resistiva de banda ancha, con la ganancia no sucede lo mismo, lo cual limita el margen utilizable de frecuencias. De acuerdo con las realizaciones de la presente invención, esta limitación se atenúa por medio del concepto de utilizar la corriente a través de  $C_L$  como la salida más que la tensión a través de él. Esto se puede realizar por medio de terminar el extremo de tierra de  $C_L$  en un nodo de baja impedancia, de modo que la corriente a través de  $C_L$  es esencialmente independiente de estar terminación, produciendo una transconductancia

$$G \approx A_{\nu} s C_{L} \approx \frac{s C_{F} - g_{m}}{s C_{F} + s C_{L}} s C_{L} \approx -\frac{g_{m} C_{L}}{C_{F} + C_{L}}$$

EC. 5

20

Esto es aproximadamente una transconductancia independiente de la frecuencia cuando  $\omega \ll q_m/C_F$ .

30

40

45

En las figuras 6 a 9 se muestran diagramas esquemáticos simplificados del circuito del LNA 30 de acuerdo con las realizaciones de la presente invención, dispuestos para operar de acuerdo con el concepto mencionado anteriormente. En las realizaciones de la presente invención, el circuito del LNA 30 es capaz de amplificar las señales a una frecuencia de trabajo f (correspondiente a una pulsación  $\omega = 2\pi f$ ), o en una banda continua de tales frecuencias de trabajo. En algunas realizaciones, la frecuencia de trabajo (o banda continua) es una frecuencia predeterminada fija (o banda continua). En otras realizaciones, el circuito del LNA es sintonizable a diversas tales frecuencias de trabajo f (o bandas continuas). En las realizaciones de la presente invención, el circuito del LNA 30 consta de un transistor de entrada 50 que tiene un primer terminal 52, un segundo terminal 54 y un tercer terminal 56. El transistor de entrada 50 puede ser un transistor MOS o un BJT. En el caso de que sea transistor MOS, el primer terminal 52 es el terminal puerta, el segundo terminal 54 es el terminal drenaje y el tercer terminal 56 es el terminal fuente. En el caso de un BJT, el primer terminal 52 es el terminal base, el segundo terminal 54 es el terminal colector y el tercer terminal 56 es el terminal emisor. El transistor de entrada 50 está dispuesto para, en funcionamiento, estar polarizado para tener una transconductancia  $g_m$  a la frecuencia de trabajo f. Además, en las realizaciones de la presente invención, el circuito del LNA comprende un condensador de realimentación paralelo 60 conectado operativamente entre el primer terminal 52 del transistor de entrada 50 y el segundo terminal 54 del transistor de entrada 50. Adicionalmente, en las realizaciones de la presente invención, el circuito del LNA comprende un condensador de salida 65 conectado operativamente entre el segundo terminal 54 del transistor de entrada 50 y el terminal de salida 34 del circuito del LNA 30. Utilizando una anotación coherente con la figura 5, la capacidad del condensador de realimentación paralelo 60 figura en lo que sigue como C<sub>F</sub> y la capacidad del condensador de salida 65 figura en lo que sigue como C<sub>L</sub>. Aunque el condensador de realimentación paralelo 60 se muestra en las figuras como un componente individual, separado del transistor de entrada 50, se debe tener en cuenta que la capacidad parásita puerta/drenaje del transistor de entrada 50 puede proporcionar una contribución no despreciable a la capacidad C<sub>F</sub>. Por tanto, el condensador de realimentación paralelo 60 puede en muchos casos ser considerado como que comprende la capacidad puerta/drenaje del transistor de entrada 50 así como un condensador específico en paralelo con ella. En casos extremos, el condensador de realimentación paralelo 60 puede incluso formar parte de, (o, simplemente "ser") la capacidad puerta/drenaje del transistor de entrada 50 solo.

La figura 6 ilustra una realización del circuito del LNA 30 en el que el transistor de entrada 50 es un transistor MOS y el circuito del LNA 30 es un circuito del LNA de fuente común. En la figura 6, se incluye una unidad de polarización 70 adaptada para polarizar el circuito del LNA 30 en un punto adecuado de trabajo. La unidad de polarización 70 puede estar comprendida en el circuito del LNA 30 o puede ser externa al circuito del LNA 30. Alternativamente, parte del circuito de polarización 70 puede estar comprendido en el circuito del LNA 30 mientras que el resto del circuito de polarización 70 puede ser externo al circuito del LNA 30. El circuito de polarización 70 puede, por ejemplo, comprender una red pasiva y/o una red activa dispuesta para proporcionar una corriente de polarización en CC adecuada para el transistor de entrada 50. Típicamente, la unidad de polarización 70 podría diseñarse de manera de proporcionar un circuito abierto a la frecuencia de trabajo f (o la banda contínua de tales frecuencias de trabajo). El circuito de polarización 70 se incluye también en las realizaciones ilustradas en las figuras 7 a 9. El diseño de una unidad de polarización adecuada 70 para una realización en particular sería una tarea sencilla para los expertos en diseño de amplificadores y por consiguiente no se describirá en este documento con mayor detalle.

Por razones de ruido, la transconductancia  $g_m$  debe ser típicamente mayor, normalmente mucho mayor que  $1/R_s$  (la recíproca de la resistencia de fuente, vista desde el LNA, que es también la resistencia de adaptación). Por ello, la capacidad de realimentación paralelo  $C_F$  se puede hacer relativamente pequeña (es decir, con pequeña capacidad, que también se traduce en un espacio pequeño) y típicamente menor, normalmente mucho menor que la capacidad  $C_L$  del condensador de salida 65. Además, el factor del lazo de realimentación, o relación de retorno, puede ser relativamente pequeño. Esto implica que la reducción de ganancia debida a  $C_F$  sea típicamente relativamente pequeña.

20

35

40

65

Como se indicó anteriormente, dependiendo de los parámetros de diseño elegidos del transistor de entrada 50 y de la capacidad del condensador de salida 65, la capacidad puerta/drenaje mencionada anteriormente (o "la capacidad de realimentación paralelo interna") del transistor de entrada 50 puede proporcionar una contribución significativa a C<sub>F</sub>. En consecuencia, se puede necesitar un espacio adicional relativamente pequeño para el condensador de realimentación paralelo 60 con objeto de alcanzar el valor C<sub>F</sub> que se necesita para obtener la resistencia de entrada deseada.

En un entorno integrado, los transistores y los condensadores se pueden hacer de la misma tecnología y  $g_m$ ,  $C_F$  y  $C_L$  están correlacionados dando lugar a tolerancias ajustadas. Si el condensador de realimentación paralelo 60 (o la parte del condensador de realimentación paralelo 60 que no es la capacidad puerta/drenaje del transistor de entrada 50) forma parte del condensador de puerta MOS, la condición de adaptación dependerá sólo de una relación de capacidades (por ejemplo las características de las medidas del dibujo del circuito) y de la transconductancia  $g_m$  del transistor de entrada 50. En la práctica esto reduce el trabajo de diseño para controlar la  $g_m$  del transistor de entrada 50 y para asegurarse de que las capacidades parásitas estén incluidas razonablemente también en la modelización de  $C_F$  y  $C_L$ , y por ello proporciona una complejidad de diseño relativamente baja, lo cual es una ventaja. De acuerdo con ello, en algunas realizaciones de la presente invención, en las que el transistor de entrada 50 es un transistor MOS, el condensador de realimentación 60 es, o comprende, un condensador de puerta MOS realizado con un transistor MOS del mismo tipo del transistor de entrada 50. Esto se ilustra con un ejemplo en la figura 7, en la que el condensador de realimentación paralelo de la realización de la figura 6 ha sido realizado con un transistor MOS 75.

Como se mencionó anteriormente, se pueden utilizar otros tipos de transistores que no sean MOS para el transistor de entrada 50 del amplificador principal. Esto se ilustra en la figura 8, que muestra una realización del circuito del LNA 30 en el que el transistor de entrada 50 es un transistor de unión bipolar (BJT) en configuración de emisor común.

Sí se necesita, se puede utilizar una inductancia serie relativamente pequeña para ensanchar el ancho de banda haciendo la característica paso bajo de impedancia de entrada de segundo orden, en lugar de una característica paso bajo de primer orden, que es el caso sin tal inductor (véase, por ejemplo, la ecuación 3). Tal inductancia cumpliría todavía la estructura paso bajo, y por consiguiente no dependería de la frecuencia de trabajo, y podría por tanto estar integrada o ser parte del conjunto o de la placa de circuito impreso. Por ello, de acuerdo con algunas realizaciones, el circuito del LNA 30 consta de una inductancia serie conectada operativamente entre el primer terminal 56 (es decir, puerta o base) del transistor de entrada 50 y el terminal de entrada 32 del circuito del LNA 30. Esto se ilustra en la figura 9 con una realización de ejemplo en la que se ha añadido una inductancia serie 80 (conectada entre el primer terminal 52 del transistor de entrada 50 y el terminal 32 del circuito del LNA 30) a la realización ilustrada en la figura 6.

En las realizaciones de la presente invención, el condensador de salida 65 es relativamente pequeño. Esto contrasta con los llamados condensadores de bloqueo de CC, para los cuales se seleccionan normalmente capacidades relativamente grandes para bloquear con eficacia el nivel de CC propagado y proporcionar esencialmente un cortocircuito a la frecuencia de interés. Más específicamente, de acuerdo con las realizaciones de la presente invención, el condensador de salida 65 tiene un valor de capacidad  $C_L < g_m/f$ , que es significativamente menor que el

que se usaría para un condensador de bloqueo de CC. Con esta elección del valor de la capacidad habrá alguna tensión residual de la señal a través del condensador que actúa como un convertidor tensión a corriente dependiente de la frecuencia. Esta acción de convertidor en combinación con la ganancia en tensión dependiente de la frecuencia en el nodo 54 proporciona una ganancia independiente de la frecuencia (es decir, la transconductancia) desde la entrada del LNA para cargar la corriente del condensador. Cuando esta ganancia es independiente de la frecuencia se facilita una operación de banda ancha.

5

10

15

20

35

40

45

50

55

60

65

Como se mencionó anteriormente en el contexto de la figura 4, el circuito del LNA 30 puede estar comprendido en un circuito receptor de radio 10, junto con un circuito de terminación 40. De acuerdo con algunas realizaciones de la presente invención, el terminal de entrada 42 del circuito de terminación 40, que está conectado al terminal de salida 34 del circuito del LNA 30, es un terminal de entrada de corriente, es decir, un terminal que está diseñado específicamente (o "dispuesto particularmente") para recibir una corriente eléctrica como entrada. Esta propiedad puede por ejemplo, ser definida, o cuantificada, en términos de impedancia de entrada o parámetros dispersos. Por ejemplo, de acuerdo con algunas realizaciones, la magnitud |Zin(f)| de la impedancia de entrada  $Z_{in}$  del circuito de terminación 40 a la frecuencia f es menor que 1/10 de la magnitud  $|ZCL(f)| = 1/(2\pi f \cdot CL)$  de la impedancia ZCL(f) del condensador de salida 65 del circuito del LNA 30. (Obsérvese que  $Z_{in}$  en la afirmación precedente se utiliza para nombrar la impedancia de entrada del circuito de terminación 40, en cambio, en las ecuaciones 2-3, ella se usa para nombrar la impedancia de entrada del circuito del LNA. Una vez remarcado esto, no debe haber riesgo de confusión.) La relación 1/10 es sólo un ejemplo; se pueden emplear otras cifras dependiendo de la aplicación. Una relación adecuada para una aplicación dada, con determinados requisitos de rendimiento del circuito del LNA 30, puede, por ejemplo, determinarse utilizando simulaciones por ordenador. La relación 1/10 puede ser un punto de partida adecuado para tales simulaciones.

La impedancia de entrada del circuito de terminación 30 afecta por su parte al parámetro disperso s11 del circuito del LNA 30, que puede a su vez por ello utilizarse para caracterizar la viabilidad del circuito de terminación para recibir una corriente eléctrica como señal de entrada. Por ejemplo, de acuerdo con algunas realizaciones, la magnitud | s11(f) | del parámetro disperso s11 en el terminal de entrada 32 del circuito del LNA 30 es menor que -10 dB a la frecuencia f. El valor de -10 dB del parámetro s11 es sólo un ejemplo; se pueden utilizar otras cifras dependiendo de la aplicación. Un valor adecuado del parámetro s11 para una aplicación dada con determinados requisitos de rendimiento en el circuito del LNA 30, puede, por ejemplo, determinarse utilizando simulaciones por ordenador. El valor de -10 dB del parámetro s11 puede ser un punto de partida apropiado para tales simulaciones.

La figura 10 ilustra con un ejemplo como se puede realizar un circuito de terminación 40 con tal terminal de entrada de corriente. En la figura 10, el circuito de terminación 40 consta de un amplificador operacional 100 conectado en realimentación. En la figura 10, la realimentación negativa del amplificador operacional 100 proporciona un nodo de tierra virtual en el terminal de entrada negativo del amplificador operacional 100. Hablando cualitativamente, variar la entrada de corriente al terminal de entrada 42 sólo daría lugar a una variación de tensión relativamente pequeña (no la ideal para un amplificador operacional de ganancia infinita) en el terminal de entrada 42, por lo que el terminal entrada 42 es apropiado para recibir una corriente de entrada. En la figura 10, el nodo de tierra virtual del amplificador operacional 100 conectado en realimentación se usa como terminal de entrada de corriente. El ejemplo ilustrado en la figura 10 es sólo un ejemplo. Otro ejemplo de circuitos que se pueden diseñar para tener un valor de impedancia de entrada apropiado, o para proporcionar un valor de s11 adecuado para el circuito del LNA 30, que sean válidos para recibir una corriente eléctrica como señal de entrada son los mezcladores en modo corriente. Esto se ilustra en la figura 11, que muestra un mezclador 120, controlado por la señal de un oscilador local "LO", conectado en el circuito entre el circuito del LNA y el amplificador operacional 100 conectado en realimentación. Otros ejemplos de circuitos que pueden ser diseñados para tener un valor de impedancia de entrada apropiado, o para proporcionar un valor s11 adecuado para el circuito del LNA 30, que sean adecuados para recibir una corriente eléctrica como señal de entrada son, por ejemplo, los amplificadores en base común, los amplificadores en puerta común, los amplificadores de transimpedancia y los transformadores. Por ello, de acuerdo con algunas realizaciones de la presente invención, el circuito de terminación 40 es o consta de un amplificador en base común, un amplificador en puerta común, un amplificador de transimpedancia, un amplificador operacional 100 conectado en realimentación con un nodo de tierra virtual como terminal de entrada de corriente, un transformador o un mezclador en modo corriente.

La presente invención se ha descrito anteriormente con referencia a realizaciones específicas. Sin embargo, son posibles otras realizaciones distintas de las anteriormente descritas dentro del alcance de la invención. Las diferentes características de las realizaciones se pueden combinar en otras combinaciones que las descritas. Por ejemplo, incluso aunque la inductancia serie 80 (figura 9) y el condensador de puerta MOS 75 (figura 7) se hayan mostrado junto con un transistor MOS como transistor de entrada 50, se pueden también usar juntos con un BJT como transistor de entrada 50. Además, incluso aunque la inductancia serie 80 (figura 9) y el condensador de puerta MOS 75 (figura siete) se hayan mostrado en realizaciones separadas, pueden por supuesto usarse juntos en otras realizaciones. Más aún, por simplicidad de ilustración, el circuito del LNA 30 se ha ilustrado en las figuras 6 a 9 con realizaciones de una sola entrada. Sin embargo, estas realizaciones se pueden ampliar a realizaciones diferenciales de una manera sencilla para expertos en diseño de circuitos LNA, por ejemplo, combinando dos circuitos de LNA 30 de una sola entrada. La utilización de realizaciones de una sola entrada para ilustrar esta descripción detallada no

# ES 2 551 883 T3

trata por consiguiente de limitar su alcance, y se debe observar en este contexto que un amplificador diferencial puede ser considerado como que consta de un amplificador de una sola entrada como un subcomponente. Adicionalmente, en las figuras, el condensador de realimentación paralelo 60 y el condensador de salida 65 se han mostrado como conectados directamente al segundo terminal del transistor de entrada 50. Sin embargo, en algunas realizaciones, pueden ser asimismo componentes intervinientes o aislados conectados entre el segundo terminal del transistor de entrada y cada uno o ambos de los condensador de realimentación paralelo 60 y el condensador de salida, tal como uno o más transistores en cascodo, transistores intermedios y/o amplificadores intermedios. El alcance de esta invención sólo está limitado por las reivindicaciones de patente adjuntas.

10

5

#### **REIVINDICACIONES**

1. Un circuito receptor (10), que comprende:

10

15

45

55

- 5 Un amplificador de bajo ruido en fuente común o emisor común, circuito LNA (30), para amplificar señales a una frecuencia de trabajo *f* en el circuito receptor (10), que comprende:

- un transistor de entrada (50) dispuesto para, en funcionamiento, estar polarizado para tener una transconductancia  $g_m$  a la frecuencia de trabajo, y que tiene un primer terminal (52), que es un terminal de puerta o de base, conectado operativamente a un terminal de entrada (32) del circuito del LNA (30);

- un condensador de realimentación paralelo (60) conectado operativamente entre el primer terminal (52) del transistor de entrada (50) y un segundo terminal (54), que es un terminal de drenaje o de colector, del transistor de entrada (50); y

- un condensador de salida (65) conectado operativamente entre el segundo terminal (54) del transistor de entrada (50) y un terminal de salida (34) del circuito del LNA; en el que

- el condensador de salida (65) tiene un valor de capacidad  $C_L < g_m/f$ , y

un circuito de terminación (40) con un terminal de entrada de corriente conectado al terminal de salida (34) del circuito del LNA (30); en el que el circuito de terminación (40) es o comprende un amplificador en base común, un amplificador en puerta común, un amplificador de transimpedancia, un amplificador operacional (100) conectado en modo de realimentación con un nodo de tierra virtual como terminal de entrada de corriente, un transformador o un mezclador en modo corriente.

- 2. El circuito receptor (10) de acuerdo con la reivindicación 1, en el que el transistor de entrada (50) es un transistor MOS, el primer terminal (52) es el terminal de puerta, el segundo terminal (54) es el terminal de drenaje y el circuito del LNA (30) es un circuito de LNA en fuente común.

- 3. El circuito receptor (10) de acuerdo con la reivindicación 2, en el que el condensador de realimentación paralelo (60) es o consiste en un condensador de puerta MOS realizado con un transistor MOS (75) del mismo tipo que el transistor de entrada (50).

- 4. El circuito receptor (10) de acuerdo con las reivindicaciones 2 o 3, en el que el condensador de realimentación (60) es o comprende una capacidad puerta a drenaje del transistor de entrada (50).

- 5. El circuito receptor (10) de acuerdo con la reivindicación 1, en el que el transistor de entrada (50) es un transistor de unión bipolar, el primer terminal (52) es el terminal base, el segundo terminal (54) es el terminal colector y el circuito del LNA (0) es un circuito de LNA en emisor común.

- 6. El circuito receptor (10) de acuerdo con cualquiera de las reivindicaciones precedentes, que comprende adicionalmente una inductancia serie (80) conectada operativamente entre el primer terminal (56) de transistor de entrada (50) y el terminal de entrada (32) del circuito del LNA (30).

- 7. El circuito receptor (10) de acuerdo con cualquiera de las reivindicaciones precedentes, en el que la magnitud |Zin(f)| de la impedancia de entrada  $Z_{in}$  del circuito de terminación (40) a la frecuencia f es menor que 1/10 de la magnitud  $|ZCL(f)| = 1/(2\pi f \cdot CL)$  de la impedancia  $Z_{CL}(f)$  del condensador de salida (65) del circuito del LNA 30.

- 8. El circuito receptor (10) de acuerdo con cualquiera de las reivindicaciones precedentes, en el que el circuito receptor (10) es un circuito receptor de radio (10).

- 50 9. Un aparato de radiocomunicación (1,2) que comprende el circuito receptor (10) de acuerdo con la reivindicación 8.

- 10. El aparato de radiocomunicación (1) de acuerdo con la reivindicación 9, en el que el aparato de comunicación (1) es un terminal móvil (1) o un módem de datos inalámbrico.

- 11. El aparato de comunicación (2) de acuerdo con la reivindicación 9, en el que el aparato de comunicación (2) es una estación base de radio (2).

- 12. Un aparato de comunicación cableada que comprende el circuito receptor de acuerdo con cualquiera de las reivindicaciones 1 a 8.

- 13. El aparato de comunicación cableada de acuerdo con la reivindicación 12, en el que el aparato de comunicación cableada es un módem por cable.

Fig. 1(técnica anterior)

Fig. 2(técnica anterior)

Fig. 4

Fig. 11